## **Boderc**

## Citation for published version (APA):

Heemels, W. P. M. H., & Muller, G. J. (2006). Boderc: model-based design of high-tech systems : a collaborative research project for multi-disciplinary design analysis of high-tech systems. Embedded Systems Institute.

Document status and date: Published: 01/01/2006

### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# Boderc: Model-based design of high-tech systems

A collaborative research project for multi-disciplinary design analysis of high-tech systems.

Embedded Systems Institute (The Netherlands)

## **Boderc: Model-based design of high-tech systems**

A collaborative research project for multi-disciplinary design analysis of high-tech systems.

## **Editors:**

Maurice HeemelsEindhoven University of TechnologyGerrit MullerEmbedded Systems Institute

**Publisher:** Embedded Systems Institute, Eindhoven, The Netherlands

Embedded Systems

**Publisher:**

Embedded Systems Institute TU/e Campus, Den Dolech 2 P.O. Box 513, 5600 MB Eindhoven Eindhoven, The Netherlands

First edition:November 2006,presented at symposium 2006.Second edition:March 2007,updated version.

#### **Keywords:**

system design; system engineering; high-tech systems; modeling; high-level method; performance; multi-disciplinary

ISBN-13: 978-90-78679-01-1 ISBN-10: 90-78679-01-8

© Embedded Systems Institute, Eindhoven, The Netherlands 2006

All rights reserved. Nothing from this book may be reproduced or transmitted in any form or by any means (electronic, photocopying, recording or otherwise) without the prior written permission of the publisher.

The Boderc project has been executed under the responsibility of the Embedded Systems Institute, and is partially supported by the Netherlands Ministry of Economic Affairs under the Senter TS program.

ii

## Foreword

Around 2001 Océ Research & Development experienced a paradox regarding the future role of informatics in product design. In those days the world was at the summit of the internet hype. Océ, which is in the business of professional printing and document management, handled these challenges in a prudent way - it was careful not to be diverted from its bread and butter business. However, it did not pass unnoticed that product development became more and more dependent on the results and challenges of embedded software technology, as well as on the effective interplay of software, electrical, and mechanical engineering. Software engineers were exposed to two fundamentally conflicting roles. On the one hand, they had to be aware of the organisational risks that relate to new business development, while the sky seemed the limit in the world of their peers. On the other hand, they were exposed to the daily operational pressure to solve hard engineering problems in embedded systems. So it was felt that, besides facilitating Océ's entrance in the software and services business, there was a significant need to improve the multidisciplinary interaction between the embedded software, electrical and mechanical engineering disciplines, starting from the very early phases of printer development.

It was in this period that the Embedded Systems Institute was scouting for their first project ideas. This helped us to amplify the abovementioned challenges. An analysis of the state of affairs led us to the hypothesis that multidisciplinary design interaction in the earliest project stages, with full involvement of the IT discipline, should create significant value. The possibility to explore this assumption together with the Embedded Systems Institute, was considered a major opportunity.

This was one of the motivations to start the Boderc project, in which Océ participated with research groups from the three technical universities, other industrial partners, and ESI. The shared problem statement was the 'multidisciplinary design of print engines'. A central theme from the start of this project was the role of models in multidisciplinary design, or, alternatively stated, a shared (formal) language across disciplines. Models support the process of sharing knowledge; models allow to perform analyses; models can be applied to validate expected results. Still, it was not clear what information those models should provide and how we should build them. The search for an answer to these questions was considered the main challenge of the Boderc research program.

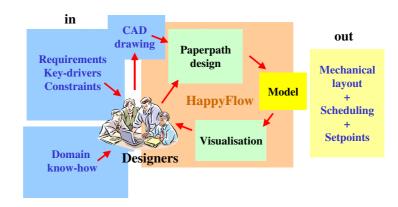

And now, here we are with the results: a book that summarizes the research findings of the Boderc project. So, what has happened with the project in the context of Océ R&D? In my opinion this project has brought us both useful, specific results, and promising general directions. It is also the start of a much longer lasting process that aims to further pervade our R&D and the other partners. Some results entirely fulfilled our initial expectations, the best known example being the 'Happy Flow' model. This enabled us to skip at least one complete physical machine-build iteration, because paper path designs could now be explored virtually. The savings from this result alone already amount to many man-years of effort. Nevertheless, the process creating such models systematically is not yet very transparent, although the positive influence of having research projects like Boderc, and therefore room for exploration, is crystal clear.

All in all, we are very happy to have embarked upon this collaborative research project. Product development has gained significantly from the results and our engineers have become more effective in the early design phases of new printers. We value our encounter with the Embedded Systems Institute, knowing that Boderc was the first project of this organization, and wish them many more successful innovations. We are confident they will further their impact, pursuing the cross-fertilization between industry and their problems and the fundamental insights of academia. Together we are currently exploring the possibilities for continuing our fruitful cooperation. Learning from each other has to become *the* contributing factor, and we are proud to have taken the first steps towards this goal!

Ir. W. Orbons Senior Vice President Research & Development Océ Technologies B.V. Venlo, The Netherlands October 2006

## Preface

This book is the result of a team effort in the truest sense. It reports on the results of the Boderc project, which was the very first collaborative research project of the Embedded Systems Institute that has been carried out in an 'Industry-as-Laboratory' setting. This is a unique research formula that combines the strengths of industrial companies, universities, and research institutes, with the objective to create breakthrough applied research under realistic industrial constraints.

This book summarizes the key results of the Boderc project and represents the collective work of researchers and engineers from the companies Océ-Technologies, Chess, and Imtech, together with research groups at the Technical University Eindhoven, University of Twente, Radboud University Nijmegen and the Embedded Systems Institute. Representatives from these organizations have worked together for about five years, focusing their research on an industrial problem statement from Océ-technologies. In effect, this book constitutes the accumulated knowledge and experience of this unique multidisciplinary community.

Publishing the project results in this book cannot be done without expressing our gratitude to those who contributed to the success of Boderc. Many have participated in the project, including at least six PhD-student advisors, six university professors, and three industrial managers to guide the work. We would like to express our gratitude to all our partners in both industry and academia, as it was their contribution that enabled the success of this ambitious project. The funding by Océ Technologies and the Dutch Ministry of Economic Affairs provided the essential financial means to carry out the project. We are confident that it has brought significant benefits to the partners and will be a source of inspiration for them, as well as all other interested parties in the future.

Prof. dr. Ed Brinksma Scientific Director & Chair Embedded Systems Institute The Netherlands October 2006

vi

## Contents

| 1  | Introduction                                             | 1   |

|----|----------------------------------------------------------|-----|

| 2  | A design methodology for high-tech systems               | 11  |

| 3  | The key driver method                                    | 27  |

| 4  | Threads of reasoning                                     | 43  |

| 5  | Budget-based design                                      | 59  |

| 6  | Effective industrial modeling: The example of Happy Flow | 77  |

| 7  | Heat modeling in copiers                                 | 89  |

| 8  | Modeling of performance                                  | 101 |

| 9  | Virtual printer modeling                                 | 115 |

| 10 | Using stepper motors in printers                         | 129 |

| 11 | Simulating the environment of embedded software          | 141 |

| 12 | Evaluating embedded system architectures                 | 151 |

| 13 | Model-driven design of real-time systems                 | 161 |

| 14 | Time-varying delays in control                           | 171 |

| 15 | Sheet feedback control in a printer paper path           | 183 |

| 16 | Event-driven control                                     | 193 |

| 17 | Design trajectory and controller-plant interaction       | 203 |

## viii CONTENTS

| 18 | Impact, lessons learned and conclusions | 213 |

|----|-----------------------------------------|-----|

| A  | List of Boderc publications             | 225 |

| B  | List of authors                         | 231 |

## Chapter 1

## Introduction

Authors: W.P.M.H. Heemels, G.J. Muller and P.F.A. van den Bosch

The design of high-tech mechatronic systems like wafer steppers, electron microscopes, copiers, et cetera, is a complex process. Multiple 'classical' engineering disciplines need to make the overall design in close co-operation. Typically, electrical, mechanical, software and other engineering disciplines together determine the functioning of the final product. Especially in the early design phases, the design of the product is vulnerable for erroneous design choices as many others will be based on it subsequently. These erroneous choices tend to show up in later phases during the integration or even the manufacturing itself. Late in a project, the 'repairs' are more difficult and can lead to a much longer development period than planned and/or a less optimal product.

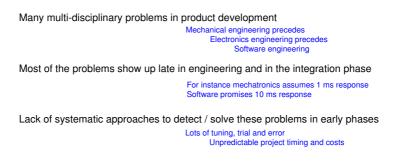

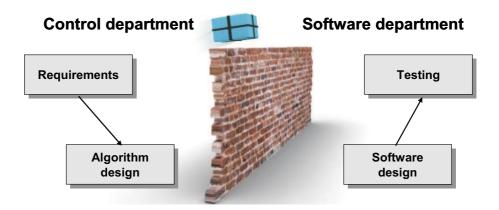

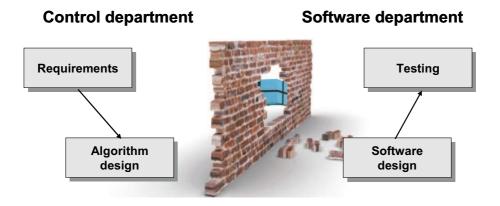

The main reasons for non-optimal design choices, of which some are illustrated in Figure 1.1, are summarized below.

- A common language and background between multiple engineering disciplines, which enable the reasoning about system properties, are lacking. As a result, the consequences of a choice, made by one discipline, cannot be overseen for other disciplines; wrong assumptions are made on the sub-designs of other disciplines; confusions and misunderstanding are present about definitions of specific terms and priorities differ over disciplines.

- Many design choices are made in an implicit way, based on experience, intuition

and 'gut-feeling.' That way, it is hard to communicate the reasons and to discuss

the design or particular choices in it. Decisions are sometimes not well-founded

by quantitative arguments, but can be forced by seniority and 'shouting loudest.'

- Especially dynamic, time depending aspects of a system are complex to grasp. There are not many tools and methods available to support the time varying aspects in a design, in contrast to many static or steady-state aspects.

### 2 INTRODUCTION

• Out-of-phase project evolution is another important factor. A typical example of the latter is that the mechanical design often precedes the electronic design, which on its turn precedes the software design.

Figure 1.1: Typical industrial problems in mechatronics systems

The effects of the above design complications are amplified by the size and complexity of high-tech machines (typically millions lines of codes, tens of thousands mechanical components like pinches, springs, belts, motors, bolts, et cetera). The more complex the machine and the more people involved in the design, the stronger the effects. Of course, the four mentioned reasons are not the only ones that complicate the design. Other factors like organizational or political, or geographically scattering of the design team contribute too. Those latter issues are important as well, but are of a different dimension and more related to business management. We believe that the aforementioned reasons can be relieved by the use of models that capture the system behavior and a reasoning method that indicates how and when to use them. That is why the Bode-RC project was initiated by the Embedded Systems Institute, Océ Technologies, Imtech, Chess and 6 academic groups of the universities of Eindhoven, Nijmegen and Twente.

## **1.1 The Boderc project**

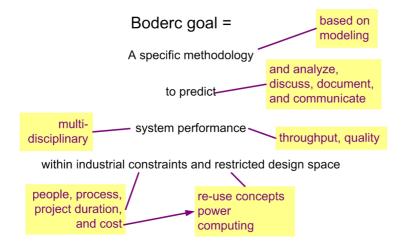

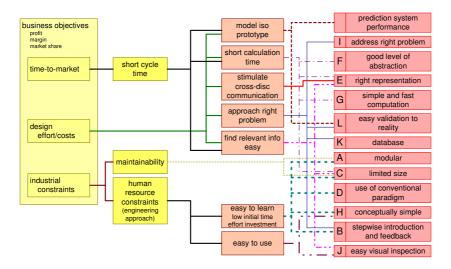

Early on in the Boderc project, the goal was defined as shown in annotated form in Figure 1.2. The goal of Boderc is to develop a model-based methodology that supports multi-disciplinary design (space exploration) by predicting system performance. The developed models, methods and techniques should in particular be applicable in the early design phases and must satisfy industrial application constraints. They should be usable in the industrial context with its particular people, processes and economic constraints related to design time, effort and costs. Moreover, the economic constraints and the traditional processes of the manufacturer of the product restrict the design space a priori by posing constraints on the design. Most parts in a new design will not be revolutionary, existing solutions and technologies and way of working will be

re-used, which constrains the design space. The methodology should be effective for this constrained design space.

Figure 1.2: Boderc research project goal

During the Boderc project the awareness emerged that it is not only about *predict-ing* system performance. The methodology and models force to make design choices quantitative and explicit which enables the analysis of various design options, communication between engineers from different disciplines and to commence the design with all disciplines involved in the beginning of a project. Also modeling of (parts of) the system increases the understanding and insight in the design. All these factors lead to shorter design iterations and more confidence in the consequences of design choices. In the end, better products are delivered faster.

#### **Boderc: name and logo**

The Boderc name and logo deserve also some explanation, especially considering the various gimmicks being in it. Boderc stands for Beyond the Ordinary: Design of Embedded Real-time Control. In the logo depicted in Figure 1.3 one can observe that the first 4 letters 'Bode' are separated from 'RC.' Bode refers to the frequency response functions in the form of Bode plots [14], one of the fundamental means to indicate the performance of linear control systems in control theory. The 'RC' are capitalized and indicate the letters that stand for resistors and capacitors, important components in many electrical circuits. Also the letter '0' has an integral through it denoting a so-called circle integral, which is well-known in mathematics. This reflects the desirable connection of the Boderc results to scientific foundations (next to industrial applicability). Moreover, in this manner the Boderc logo indicates the multi-disciplinary nature of the project. As Boderc aims at developing a *model*-based design methodology, the

#### 4 INTRODUCTION

pronunciation of Boderc refers to the actress Bo Derek, who after all is also a kind of model.

Figure 1.3: Boderc logo

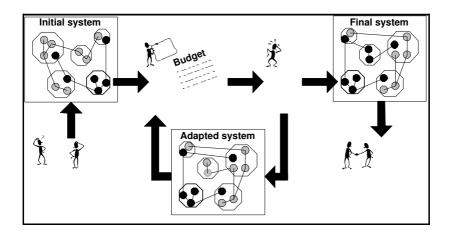

## **Research method: Industry-as-Laboratory**

The Boderc project uses the *industry-as-laboratory* approach, as proposed by Colin Potts [94] and visualized in Figure 1.4.

Figure 1.4: Industry as Laboratory: Research of engineering methods

The industry-as-laboratory approach exploits the actual industrial setting as a test environment, which warrants that the research question is based on real industrial problems. The Boderc research team, consisting of a mix of academic and industrial people, investigates a new product engineering methodology. A research hypothesis is formulated on the new methodology. The methodology is applied in the industrial setting and the results of these experiments are observed and used to evaluate the hypothesis. Coupled to the multi-disciplinary design problems for high-tech systems discussed in the beginning of this chapter, the research hypothesis of the Boderc project was chosen as:

The product creation lead time will be reduced significantly by the use of multi-disciplinary models during the early product development phases.

The term *Carrying Industrial Partner (CIP)* is used for the company that provides the problem and the industrial setting. The CIP of Boderc is Océ Technologies, which creates high-volume document printing systems.

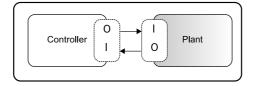

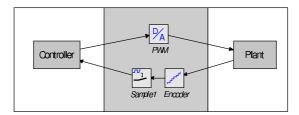

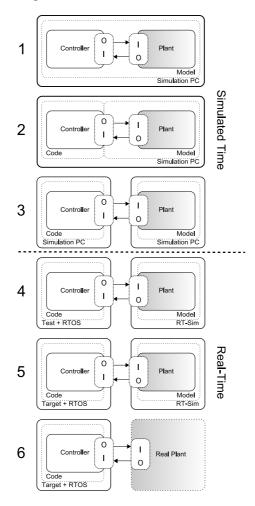

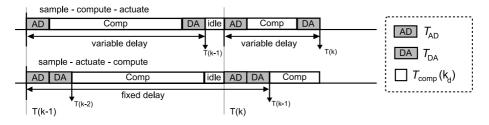

#### The industrial context

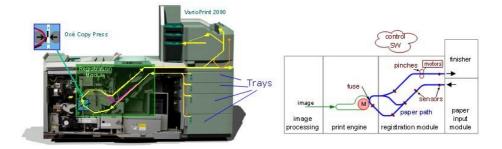

One of the product families that is designed by Océ technologies is a range of high-volume printers and copiers, see Figure 1.5.

Figure 1.5: The Domain: Printers and copiers by Océ

The application context is best characterized by document printing systems that are highly productive, reliable, and user-friendly. These systems can print on several sizes of media, different weights, automatically on both sides and include stapling, booklet production, or other types of finishing. In order to be perceived as reliable devices, such copiers must be very robust with respect to variations in media. As the printing speed is rather high (typically above 1 image per second), timing requirements are tight and advanced mechatronics are indispensable. This indicates that variations in timing parameters that relate to paper and image transport must be controlled up to a high degree. This becomes the more apparent if one realizes that the positioning of images on paper has tolerances well below 1 mm.

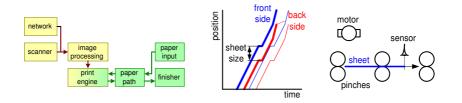

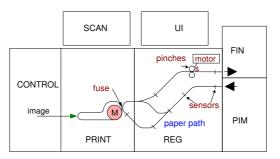

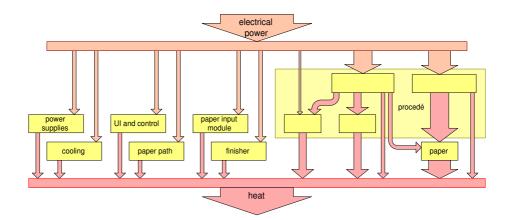

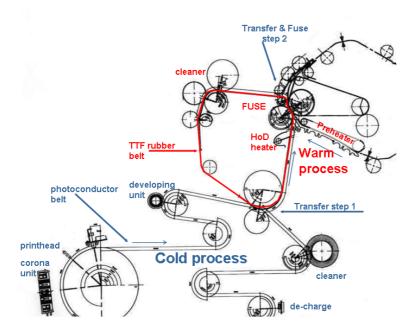

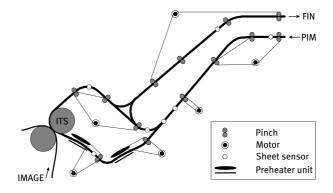

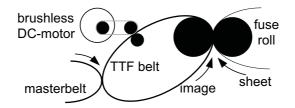

When considering the embedded control of these systems, one should think of controlling multiple sheets that travel the paper path simultaneously and synchronizing this sheet flow with the imaging process. In Figure 1.6 overviews of a copier are presented. When the copier is in normal operation, a sheet is separated from the trays in the paper input module (PIM), after which it is sent to the paper path that transports the sheets accurately in the direction of the print engine, where the image is fused on a sheet of paper. After that, the sheet is turned for duplex printing, or transported by the paper path to the finisher.

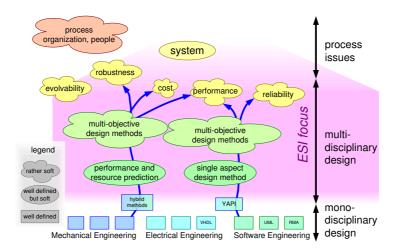

## **1.2 Multi-disciplinary methods**

The Boderc research falls typically within the category of multi-disciplinary design methods as opposed to the more conventional mono-disciplinary research areas like mechanical, electrical or software engineering. The latter research fields are relatively mature, although some doubts exist about the maturity of software engineering [91]. Some bi-disciplinary approaches exist, for instance hybrid systems theory [103] that

#### 6 INTRODUCTION

Figure 1.6: Illustration and schematic picture of a copier

combine continuous dynamical models (using e.g. differential equations) typically describing the physical part of a high-tech machine and discrete models (e.g. finite state machines or automata) to described the software behavior. The hybrid field is relatively immature and many issues are at present unsolved (at least at the large-scale needed for industrial usefulness). However, the industrial need for analysis / synthesis methods for high-tech machines in which this 'hybrid interaction' plays an important role, will stimulate the research in this domain over the years to come.

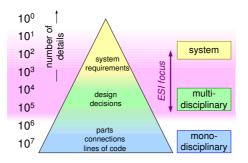

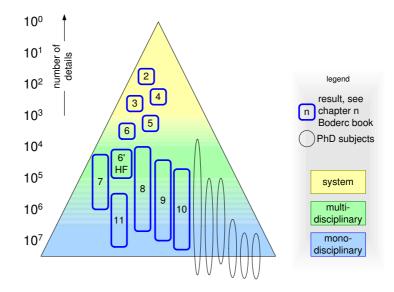

Researchers in the mono-disciplinary areas are used to well-defined problems that can be studied in depth with solutions most often based on mathematical rigor. A lot of uncertainty pops up when we move to multi-disciplinary problem solving. The problem itself is only partially defined, while at the solution side different formalisms have to inter-operate, such as discrete (software) and continuous (mechanical) models. Figure 1.7 shows a categorization of the design methods with as vertical axis the degree of multi-disciplinary interaction. The form of the method is an indication how well the method is defined and how much uncertainty is left.

In the industrial context the *system* level is often relatively well-defined in a systems requirement specification. Such a specification describes the functionality of the system and quantifies the main performance characteristics. The translation of these requirements into mono-disciplinary design choices, however, is still full of uncertainty. A lot of uncertainty is caused by the many (dependent and interfering) design dimensions that have to be managed at the same time. In Figure 1.7 the methods at this level are called *multi-objective design methods*.

The translation of system requirements to detailed mono-disciplinary design decisions spans many orders of magnitude. The few statements of performance, cost and size in the system requirements specification ultimately result in millions of details in the technical product description: million(s) of lines of code, connections, and parts. Figure 1.8 shows this dynamic range as a pyramid with the system at the top and the millions of technical details at the bottom.

The methodologies to be established by ESI, including the Boderc results, address the multi-disciplinary area and aim at coupling the academic research to industrial

### MULTI-DISCIPLINARY METHODS 7

Figure 1.7: From mono-disciplinary to system design

Figure 1.8: Exponential pyramid

practice. In Figure 1.7 this is the range from *single aspect* to *multi-objective* design methods. In the pyramid, Figure 1.8, it is the area of translating hundreds of system level requirements into tens of thousands of design choices.

#### The Embedded Systems Institute

Boderc is the first project in a long line of ESI projects within the field of multidisciplinary creation methods. This is a young research field, which is called *embedded systems engineering* (ESE) by ESI. The existing scientific disciplines have little experience in this field, most experience can be found in industry.

The mission of ESI is to advance industrial innovation and academic excellence in embedded systems engineering (ESE) with its vision to create and apply together with

#### 8 INTRODUCTION

*its partners world-class ESE methods.* The developed methodologies must support all aspects of the creation: specification, design, integration, test and validation.

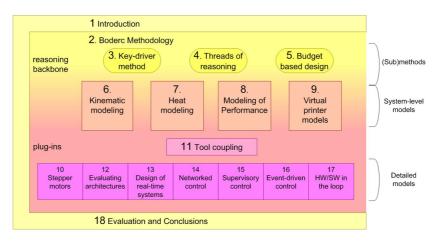

## **1.3 Reading guidelines**

This book contains a selection of the main outcomes of the Boderc project. In the Figure 1.9 an overview of the book is presented that can be used as a reading guide. The introduction (Chapter 1) has almost ended. After the introduction we present in Chapter 2 the Boderc design methodology, which consists of a system-level reasoning framework and plug-ins (modeling formalisms and techniques) that are used during the reasoning to get more in-depth insight. The Boderc methodology consists of a method part, which forms together with sub-methods like the key driver method (Chapter 3), threads of reasoning (Chapter 4) and budget-based design (Chapter 5) the reasoning backbone of the Boderc methodology.

Figure 1.9: Overview of the contents of the book

This reasoning backbone is mainly qualitative. Once important design choices are identified and the tension and conflict in the choice are known, often quantitative information is needed to make a well-founded tradeoff. Chapter 2 discusses this process in detail. To obtain the quantitative information one can retrieve this from previous projects, figures of merit, rules of thumb, data sheets, et cetera. If this information and resulting insight are not sufficient to make a proper design tradeoff, an in-depth model-based study is often used. This is where the plug-ins come into play.

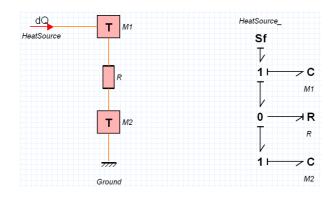

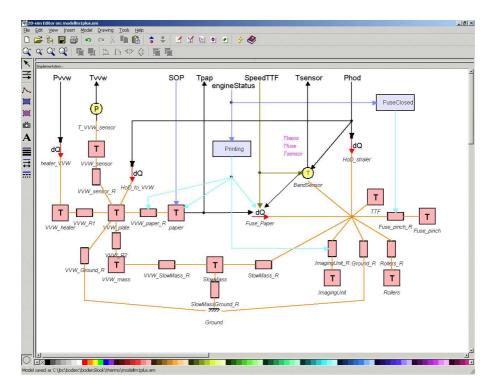

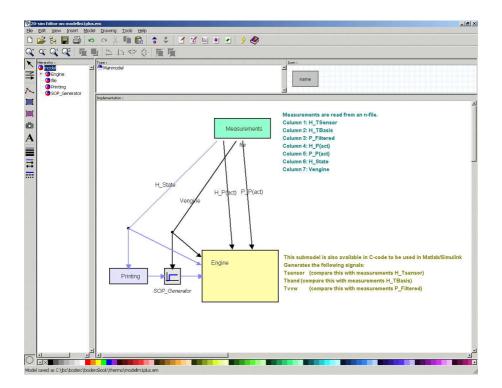

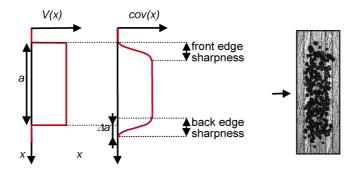

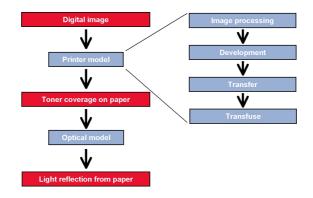

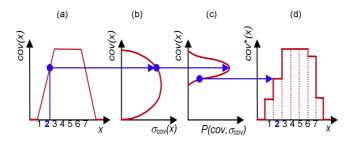

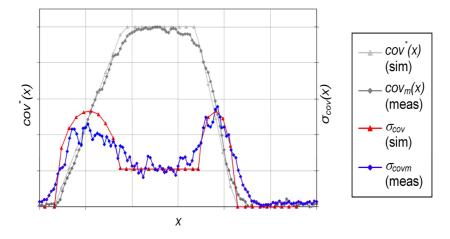

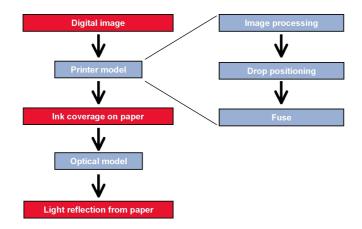

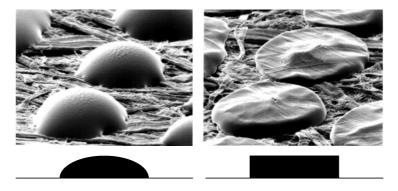

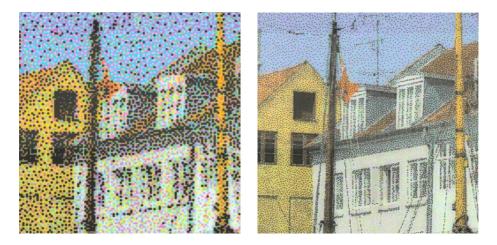

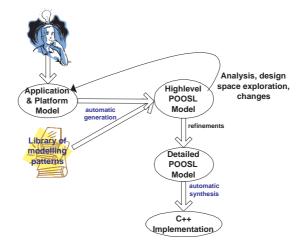

Chapter 6 describes one of the most successful models of the Boderc project being the Happy Flow model that studies the design of the mechanical lay-out of the paper transport system and the scheduling of print jobs. This chapter presents the main characteristics of the Happy Flow model and identifies the main industrial success factors. These factors can be used as a stepping stone towards guidelines on how to create models that are industrially successful. Important aspects of a copier are the heat and power flows, especially since environmental constraints are becoming tighter and tighter. In Chapter 7 a modeling approach is presented that studies these issues. How to evaluate the overall control architecture in terms of response times, CPU load, et cetera, is discussed in Chapter 8. Chapter 9 describes models that are related to printing quality. New printer technologies are assessed via 'virtual' printer models on their printing quality. The models described in Chapter 6-9 are positioned higher in Figure 1.9, when compared to Chapters 12-17. The reason is that these models have a more 'system-level character' as they describe system aspects or large subsystems of the copier. Roughly speaking, the models presented in Chapters 10-17 have a more mono-disciplinary and detailed nature.

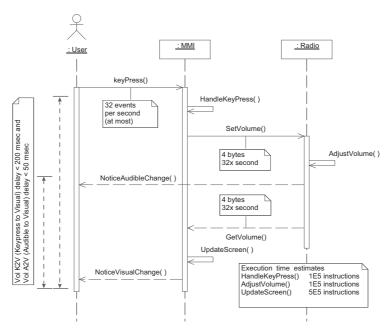

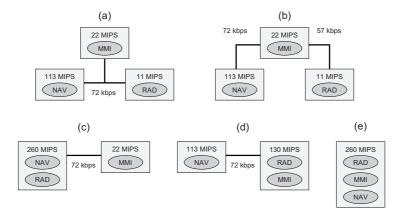

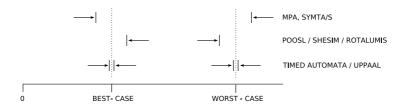

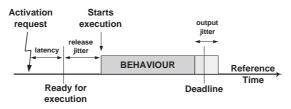

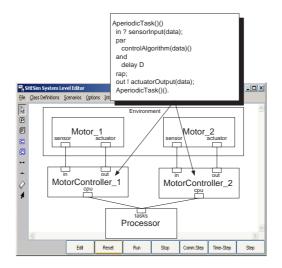

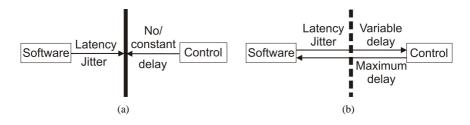

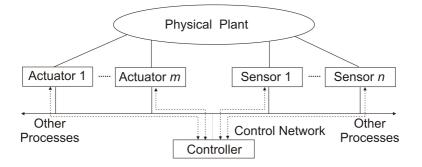

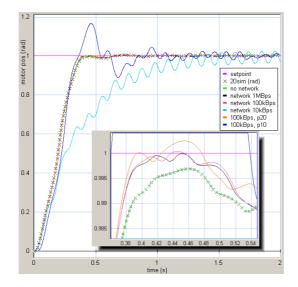

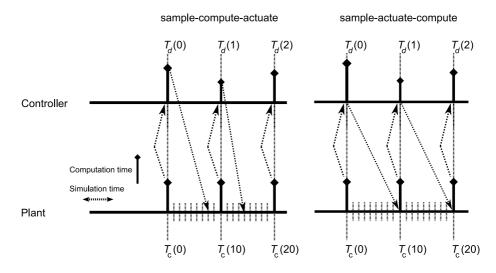

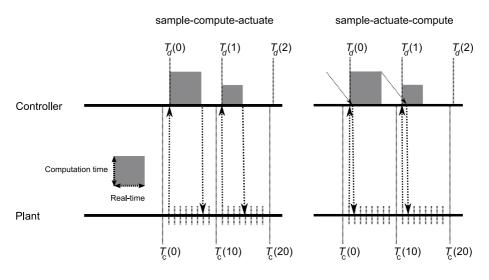

Océ Technologies traditionally used DC motors as drives in the paper transport system. However, there were important reasons to replace the DC motors by stepper motors. Chapter 10 investigates the feasibility of stepper motors for this purpose and aims at building an understanding of stepper motors that lead to practical design rules. Chapter 12, gives an overview of several state-of-the-art performance analysis for embedded system architectures for real-time systems. A case study inspired from industrial practice will be used to compare the performance analysis techniques. Based on these experiences, an indication will be given which method is best used under which circumstances to successfully support the decision making process for the architecture. Chapter 13 presents a model-driven design approach for real-time systems. This approach enables the analysis of real-time systems and allows automatic software code generation from the model that preserves the properties analyzed in the model. Chapter 14 has a more control engineering view as it analyses the effects of jitter and latencies (communication and computation delays present in any real-time system) on the control (servo) loops present in copiers. Latencies are inevitable and their effects can be disadvantageous with respect to stability and control performance. This chapter gives analysis methods and techniques for the synthesis of controllers that are robust against jitter and latencies.

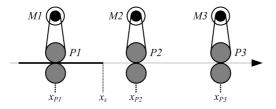

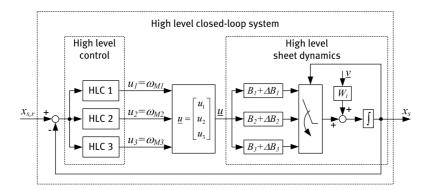

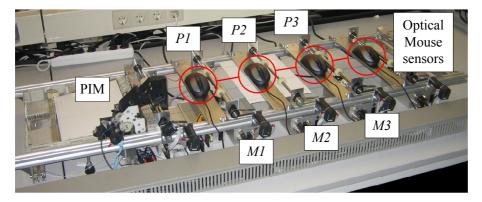

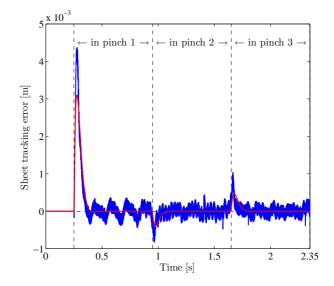

For the control design of the drives of the paper transport system (based on the schedules as computed via the Happy Flow model of Chapter 6) in Chapter 15 a hierarchical control paradigm based on supervisory control is proposed. A systematic analysis and design procedure based on low-level controllers for the motors in combination with high-level sheet control is proposed and verified via both simulations and experiments.

Chapter 16 describes the design and application of event-driven control. Eventdriven control abandons one of the severe requirements that are often posed by control engineers on the real-time implementation of their algorithms. The conventional fixed sample time is removed and novel control algorithms are described, which allow for control updates being triggered by events (e.g. the arrival of new measurement data), rather than by progression of time. Event-driven control can have major benefits with respect to resource utilization like processor and communication load, while still main-

### 10 INTRODUCTION

taining a good control performance. A particular event-driven controller was experimentally validated for the image control in a printer prototype with good control and software performance.

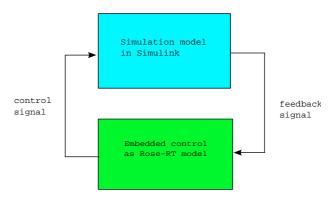

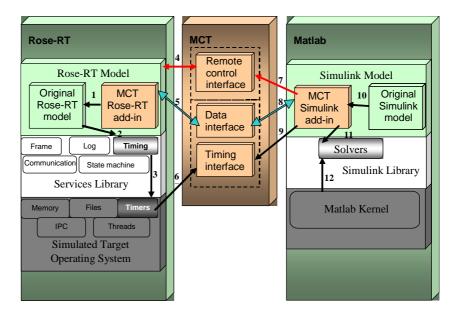

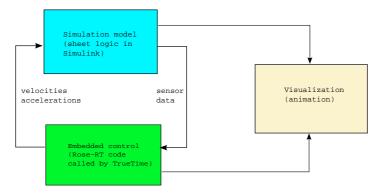

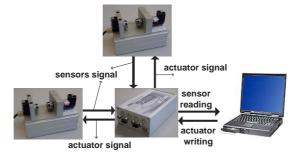

In the next chapter, Chapter 17, a systematic design trajectory is proposed for the combination of real-time controllers and the physical / mechanical process. On several levels the interactions between the hardware (processing platforms and implementation) and software aspects of controller-plant interaction are studied. A design path is indicated in which stepwise the original (simulation) models of both plant and controller are replaced by their real implementations. Chapter 11 is related to Chapter 17 as it discusses ways to simulate real-time embedded software together with its environment being of a physical / mechanical nature. Via the coupling of tools from software engineering (that model the control software of the system) and simulation tools from the mechanical/physical domain (modeling the physical part of the system) one can inspect if the software-plant combination is functioning properly. In this sense Chapter 11 is positioned closer to the system level than the detailed models in Chapters 15-17.

In the last chapter we will evaluate the overall project results and discuss its impact, spin-off and lessons learned.

## Chapter 2

## A design methodology for high-tech systems

Authors: W.P.M.H. Heemels, E.H. van de Waal and G.J. Muller

This chapter is a re-worked version of a paper for the Conference on System Engineering Research (CSER) 2006 by the same authors and with the same title.

## 2.1 Introduction

As already mentioned in Chapter 1, there is a need for a framework that supports efficient evaluation of design choices over multiple disciplines. Actually, evaluation of design choices over multiple disciplines is one of the important features of the emerging field of Embedded Systems Engineering (ESE). Typically, ESE for high-tech machines is performed by highly experienced individuals, using mostly intuition and 'gut feeling'. The experience of these individuals is hard to transfer, thereby limiting the speed with which companies can develop new products. This way of working is effective when the project remains small and limited to one location, where a relatively small number of people are involved in the design. However, to enable the co-operation for larger projects across multiple sites, an ESE framework is needed. Even for smaller projects, such a framework is expected to speed up the design process and to reduce integration time. Moreover, an ESE framework that captures the way of working of the experienced architects should enable junior architects to learn the skill of system engineering faster. Hence, in this respect the formulation of the design methodology has both an educational as an industrial application character.

In System Architecting (SA) research, some frameworks have been established (see, e.g. [89], [77] or Chapter 4 in [81] for an overview). Also, academic research has produced techniques that could be useful in industry. However, these find very

## 12 A DESIGN METHODOLOGY FOR HIGH-TECH SYSTEMS

limited use, see e.g. [94] and [83], and the need for multi-disciplinary methodologies is still large as expressed in [82]. In [82] several reasons are mentioned that hamper the creation of such methodologies. Lack of description and lack of connection of the higher level design methodology to mono-disciplinary methods are just two. The lack of connection hampers the use of frameworks and methodologies for (very) large scale systems (e.g. aerospace and military) in the *technical* development and realization of high tech systems like a copier. This also reflects the slight difference between SA and ESE as ESE particularly focusses on the connection between the system level and mono-disciplinary methods. By lack of description we mean that although multidisciplinary methods exist and are in use in the industry in various domains, their use is very implicit - typically 'gut-feeling'-based as mentioned before. The consolidation of these industrial methods is very poor. The lack of explicit description means that a lot of open issues remain. Open issues erode the value of these multi-domain methods. To tackle the lack of description and connection to mono-disciplinary techniques, this chapter presents an attempt to explicitly describe such a multi-disciplinary methodology and give place to mono-disciplinary design techniques. As [77] states, at high levels of complexity, analytical methods are no longer sufficient and heuristics come into play. In this design methodology, heuristics and analytic rigor find their place in the high-level method and the mono-disciplinary techniques, respectively. The usefulness of the proposed methodology here is largely due to the connection between the two. Moreover, by making the methodology explicit, discussions should be triggered on the open issues that require future research.

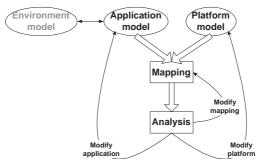

This chapter proposes the Boderc *model-based* design methodology that consists of formalisms, techniques, methods and tools:

- **Formalisms** are languages / syntax used for system modeling. Formalisms exist for modeling behavior, but also to formalize system requirements. Instances of formalisms are called *Models*. Examples of formalisms are differential equations, (timed and hybrid) automata, finite state machines, temporal logic and queuing formalisms.

- **Techniques** are used to retrieve information from models or to transform models. Examples of analysis techniques are model checking, performance analysis and program analysis techniques. Examples of transformation techniques are high-level synthesis and software compilation.

- **Methods** ('reasoning frameworks') provide guidelines and can be seen as a 'recipe book' how and in which order to apply certain *Formalisms*, *Techniques*, *Submethods* and *Tools* to solve the design problem at hand. *Methods* are ways to 'capture' design and reasoning knowledge of experienced modelers and designers. A method indicates for instance decomposition in steps (possibly techniques) and an order in which the step should be performed.

- **Tools:** Software *Tools* support the efficient application of *formalism*, *techniques* and *submethods*.

## 2.2 Boderc design methodology

When developing high-tech machines as described in the introduction, industrial constraints like project duration and available man power are paramount and as such they were explicitly stated in the Boderc goal, see Figure 1.2. These constraints must be deeply integrated in any successful methodology. To meet these constraints, a careful selection has to be made on how to invest design effort and time. The methodology provides two means:

- Focus the in-depth analysis (via modeling) on the most critical issues, preventing 'wasting' effort on less relevant problems. For this, one has to identify the *most essential* conflicts and tensions from the design decisions to be made.

- Using simple models that create insight in a design decision within a reasonable time (hours, weeks), instead of detailed models that requires months or even years to develop. The right level of detail must be chosen, which can range from back-of-the-envelope calculations to very detailed models depending on the accuracy of the answer needed. Stepwise refinement of models, typically starting with back-of-the-envelope and then extending towards more detailed models, can be useful for this.

Even when using models, physical prototypes are essential because of the confrontation with physical reality, where overlooked issues will inevitably pop up. However, it is difficult to quickly evaluate different designs through physical prototypes because a new prototype is needed for each design. Through analysis of models different designs can be evaluated much faster. As a consequence, both models and prototypes are indispensable.

Another benefit of the methodology is that it gives place to formalisms and techniques (which can be seen as 'plug-ins' in the method) and when they should be applied. Documenting the conditions under which academic formalisms/techniques and industrial state-of-the-practice are applicable and effective and their level of prediction accuracy form valuable information. Moreover, gaps can also be identified that require future research (e.g. extending state-of-practice and 'industrializing' state-of-the-art academic techniques) to obtain the right abstraction level for industrial practice.

## 2.3 Linear stepwise version of the method

The high-level 'method'-part of the methodology is given as the collection of the following steps:

### 1. Preparation of the design

- (a) Identify (customer) key drivers and requirements

- (b) Identify realization aspects of concern

### 14 A DESIGN METHODOLOGY FOR HIGH-TECH SYSTEMS

(c) Make core domain knowledge explicit

#### 2. Selection of critical design aspects

- (a) Identify tensions and conflicts (qualitative)

- (b) Gather facts and identify uncertainties to quantify tensions and conflicts

### 3. Evaluation of design aspects

- (a) Build small models (small = hours to weeks of effort)

- (b) Perform measurements

Note that there can be other (sub)methods that are a part of the design methodology that support the design of subsystems, e.g. control engineering has its own methods to synthesize control algorithms. These submethods can be used when the control system of the high-tech machine has to be designed.

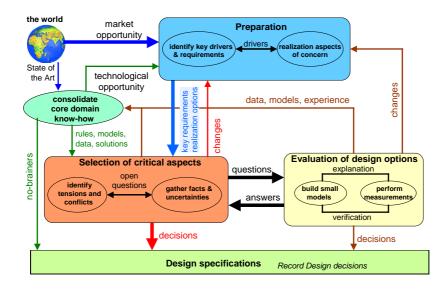

The above steps in the (high-level) method are to be used iteratively, so that progressive knowledge can be used. In Figure 2.7 the iterative nature and the dynamic flow of information between the steps is reflected better. Below, the steps and corresponding submethods, techniques and formalisms will be explained in more detail. Good visualization of the outcomes of the steps is important to create insight and overview. The design of a high-volume copier will serve as a means to illustrate the individual steps.

## 2.4 Step 1: Preparation of the design

In step 1, a good understanding of the product to be developed has to be achieved and existing knowledge is gathered to be available for the new design.

## 2.4.1 Step 1a: Identify (customer) key drivers and requirements

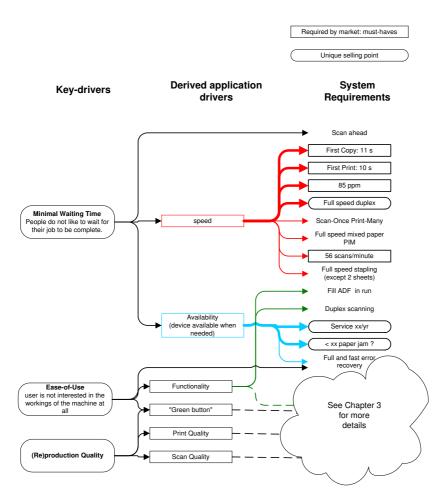

In step 1a, the goal is to identify why a customer (or other stake holders like the internal business strategist) would want the new product. The main drivers for the stake holders should be identified and insightfully related to system requirements. This is linked to the product business case. This can be achieved using activities like interviewing marketing experts, interviews and workshops with customers, story telling [81], et cetera. The results of these activities can then be summarized using a high-level requirements engineering technique. The *key-driver model* has been found to be very useful for this purpose (see Chapter 3).

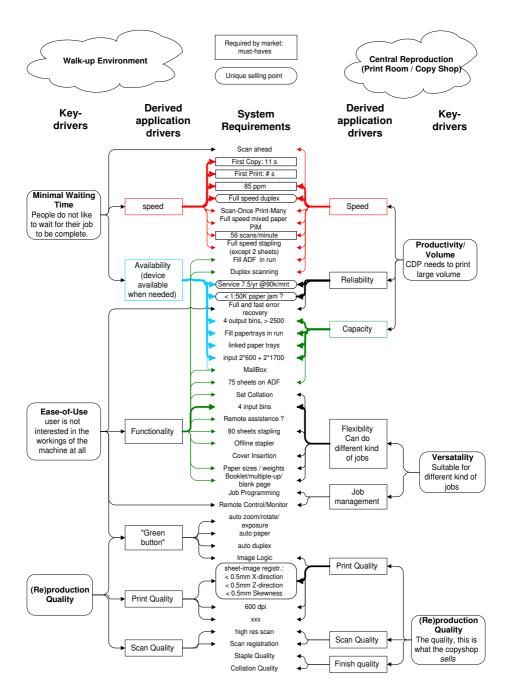

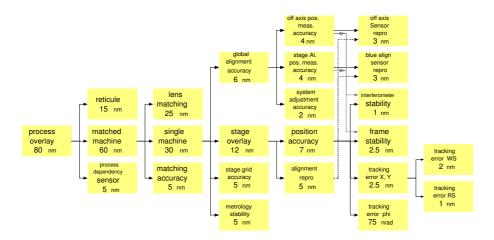

**Example:** As part of the Boderc project, the submethod of key driver analysis (see Chapter 3) was applied to a high-volume copier. The key drivers of the copier were identified and refined into application drivers and finally into system requirements. This analysis is explained further in Chapter 3. Already a part of the key driver model is shown in Figure 2.1 below. The complete key driver model can be found in Figure 3.6.

#### STEP 1: PREPARATION OF THE DESIGN 15

Figure 2.1: Part of a key driver model for a copier.

## 2.4.2 Step 1b: Identify realization aspects of concern

In step 1b, the goal is to identify which designs aspects of the machine are of concern for its marketing success. In practice, typical the issues or worries that are hot during (coffee or lunch) discussions between the design engineers form good starting points. Some of them might be non- issues caused by non-rational fears, uncertainty, rumors, et cetera, others might be critical and jeopardizing the success of the product. This has to be found out in steps 2 and 3. In step 1b they are only identified. Currently, there are not many concrete (sub)methods and techniques that can be used for this activity; thus this is an interesting area for further research. Methods like 'story telling' [81] and scenario or use case based reasoning (see e.g. [23]) can be used for this activity.

### 16 A DESIGN METHODOLOGY FOR HIGH-TECH SYSTEMS

Checklists with problematic issues in previous projects (typically input coming from step 1c) can be used in step 1b. The introduction of new technology, new (more strict) environmental regulations and successful or failing competitors (and in particular the reasons of success of failure) should always be considered with caution.

**Example:** Based on experience of previous projects and the more stringent power norms nowadays, maximum power usage was an issue in the design of the copier. Also the introduction of stepper motors in the copier is a worry as traditionally DC motors were used.

## 2.4.3 Step 1c: Make core domain knowledge explicit

In step 1c, the goal is to make the most important lessons that were learned during the design of previous machines explicit. In most companies, this knowledge is only known implicitly: it is stored in the minds of key designers. By making this knowledge explicit, a common understanding can be achieved amongst engineers. Capturing the *context* in which a certain design was successful, can be useful to solve similar problems in a same manner in a new machine without much efforts (in Figure 2.7 indicated by 'no-brainers'). It prevents re-inventing the wheel. Going outside the context with a particular solution should be done with caution, which could require to consider it as an 'aspect of concern' and thus part of step 1b. Context is an important factor in design success.

The goals of this step can be achieved by investigating the models, design solutions, methodologies, and so on, used in previous designs. Especially designs that were not successful are useful to investigate (see also 1b above). The main question is why things were done in a certain way. The results of this investigation must then be summarized, e.g. by identifying design patterns, by writing tutorials and white-papers, determining rules-of-thumb, et cetera. Of course, part of this information is hopefully consolidated at the end of previous projects, so that this is readily available. Industrial practice often turns out otherwise.

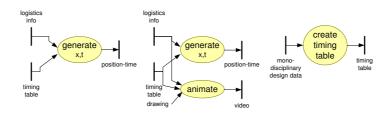

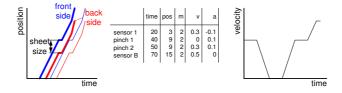

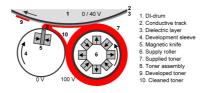

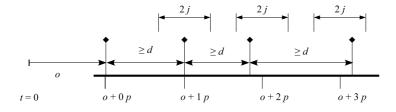

**Example:** Figure 2.2 shows some core technologies for designing copiers: the main system architecture, the paper-time diagram used for analysis of the timing of print jobs in the paper path, and the main components used in the paper path.

Figure 2.2: Examples of core domain knowledge for a copier manufacturer.

This information is very well known for most experienced copier designers, and

these items are always used. However, the familiarity has subtle dangers in that people forget the reason why these technologies are used, what the limitations and advantages are, and when alternatives should be used. Thus there is benefit in formally 'documenting' this knowledge. Of course, this has to be done in an effective and structured manner. Models can also be used to capture this knowledge. A good example is the Happy Flow model (see Chapter 6), which is used for the design of the layout of the paper path and the scheduling of print jobs. One of the reasons for industrial success is that it contains a lot of core domain knowledge in an easily accessible model.

## 2.5 Step 2: Selection of critical design aspects

When designing a new product, issues arise constantly. It is imperative to differentiate between important issues, which imply a great risk to the project if not dealt with adequately, and non-issues. Otherwise much time is lost over unimportant issues making development prohibitively expensive. In step 2 the design aspects of concern found in 1b are prioritized by their importance or value for a customer (as analyzed in step 1a), by how hard it is to solve the problem, and how sensitive or vulnerable the overall system is to this challenge.

## 2.5.1 Step 2a: Identify tensions and conflicts (qualitative)

In step 2a, the goal is to identify *qualitatively* the design tradeoffs and essential tensions that are coupled to a certain aspect of concern (1b). The fact that a design issue is of concern implies that it must have both benefits and drawbacks (in terms of key drivers and system requirements found in step 1a). Making the tensions and conflicts between benefits and drawbacks explicit allows them to be treated systematically throughout the design process.

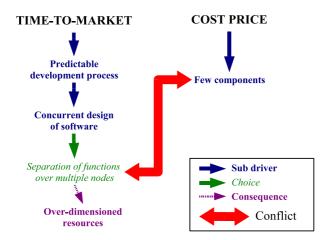

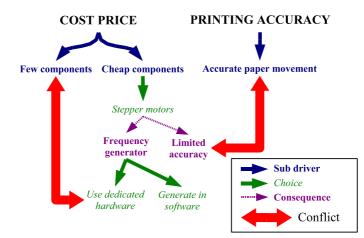

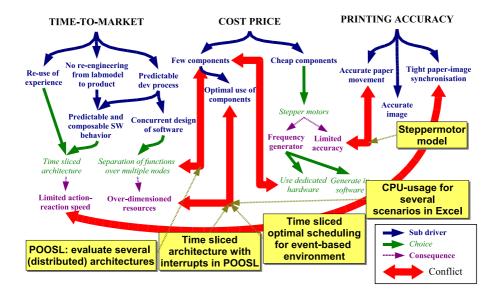

A good submethod to find these tensions and conflicts is *threads of reasoning*, which investigates where the real tradeoffs are in a design. Concrete design choices are linked to key-drivers and negative side-effects pop-up. In Chapter 4 the submethod is described and applied for the digital control architecture in a copier. The threads of reasoning diagram for the case study is presented in Figure 2.3. Also the 'question generator' [81, Section 9.2.3] supports the exploration of design tensions. Organizing workshops and brainstorm sessions is another means. In a workshop, several experts from different disciplines are invited to work together on the main concepts of the machine. They will very quickly find the tensions and conflicts in the design by bringing their own concerns and worries across and connecting them.

Figure 2.3 is at the heart of the Boderc methodology. For several design choices (e.g. the use of stepper motors instead of DC motors) the relations to the drivers for the copier are displayed. The main benefit for the use of steppers is its low cost price. However, a drawback is the limited positioning accuracy and thus possible problems for the printing accuracy, which is a customer application driver (see Figure 2.1). The

Figure 2.3: Visualization of threads of reasoning for the control architecture of a copier.

conflict between cost price and printing accuracy and several other conflicts are indicated in the figure (see legend for color use). These require further investigation in step 2b. If the results from 2b are inconclusive, an in-depth study is required according to the steps 3a and 3b. The rectangles indicate the models that have been used to create more insight in the conflicts.

## 2.5.2 Step 2b: Gather facts and identify uncertainties to quantify tensions and conflicts

In step 2a, tensions and conflicts were identified qualitatively. In step 2b, the goal is to select those tensions and conflicts that require further study. Often, the tensions and conflicts are a result of worries, uncertainty, lack of facts, non-rational fears and turn out to be non-issues. These can often be unmasked by quantifying the issues with rough estimates, using simple facts to weed out the fears, thereby diminishing the worries in the organization and enabling it to focus on the important issues. However, there will be some issues where there is insufficient knowledge to make an intelligent decision. In those cases, further study is warranted (step 3).

There are many ways to find the facts needed besides using the core domain knowledge of step 1c. For instance, an expert can be asked (use the question generator mentioned above), or rough orders of magnitude can be estimated. Also, figures of merit from previous designs can be used. Finally, much knowledge is readily available through existing literature. Facts from all these sources can be used to discard irrelevant conflicts. Note that making quantitative assumptions, which all engineers have in their mind, explicit will also reveal the (qualitative) tension. So, step 2b often also precedes step 2a in practice.

Risk assessment (see e.g. Chapter 6 in [89]) is one way to select the tensions that should be addressed more thoroughly as they consider both the impact and the probability of occurrence of a particular issue. Also back-of-the-envelope calculations can be a good starting point as they do not require much effort and time and give first estimates. Iterative refinement to more complicated models is a good means to progressively analyze a tension. Determining a budget (see Chapter 5 for details) which distributes a resource over different parts of the machine is a formalism that is often used in practice to determine the real magnitude of a problem which is too complex to analyse at the top level. Of course, there is no strict boundary between the current steps 2b and 3a: it is not always clear when to categorize a back-of-the-envelope calculation in step 2 and when to associate a model to step 3a. But in order to keep track of issues, e.g. to allow proper project management, it is helpful to make an *explicit* decision to further study an issue by placing it in step 3a.

**Example:** In the Boderc project, it was investigated if it were better to use stepper motors or DC motors in a specific copier configuration. For an initial investigation, the thread of reasoning was extended with numerical data on cost price, life time, et cetera. To assess the consequences of the implementation of steppers for important machine characteristics, a risk assessment matrix model (see [89], Chapter 6) was created (Figure 2.4). From this matrix, issues that required in-depth investigation were identified.

| τ                     | Incertainties | Impact | Result |

|-----------------------|---------------|--------|--------|

| Cost price            | 1             | 10     | 10     |

| Lifetime              | 3             | 3      | 9      |

| Accuracy (reliable)   | 10            | 9      | 90     |

| Ease of design (time) | 7             | 5      | 35     |

| Noise                 | 5             | 6      | 30     |

| Efficiency (power)    | 3             | 3      | 9      |

Figure 2.4: Quantified threads of reasoning for the use of stepper motors in a copier.

## 2.6 Step 3: Evaluation of design aspects

If the facts in step 2 are not sufficient to make a decision, the issue needs to be evaluated properly. There are two ways to do this: either using a model-based approach or measurements on prototypes. Of course, it can also be a mixture of the two, e.g. to validate models. A final validation of a product is of course always the final integration before production.

## 2.6.1 Step 3a: Build small models

In step 3a, the goal of this stage is to resolve an open conflict found in step 2 using simple (small) models. As mentioned, models are often very efficient in evaluating design options, as models can be readily modified whereas prototypes are harder to modify. Also models might create a deeper understanding of the relationships in the tension.

A key issue when using models is which formalism to use to answer the question at hand. Often, model formalisms are suggested in the core domain knowledge gathered in step 1c. If this is not the case, some literature study or research may be required to find the right formalism.

A second key issue is to find the right abstraction level and model boundary to answer the question with the right certainty. The goal is to keep the modeling effort as small as possible.

An interesting question is whether the model is based on theoretical (physical) knowledge (sometimes called first principle or white box modeling), or on empirical facts (regression, identification or black box modeling). Depending on the case at hand, one might prefer one over the other.

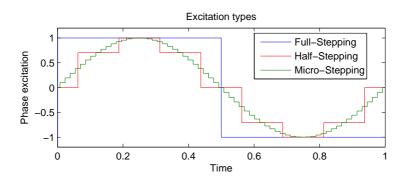

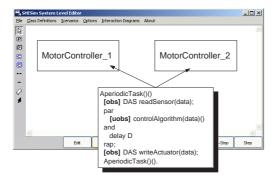

**Example:** Below are some examples of models used in the Boderc project. Already in Figure 2.3 some models have been mentioned that were used to analyze specific tensions further. Other modeling formalisms and techniques that have been used include:

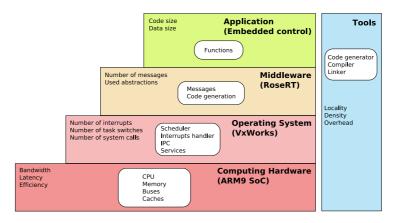

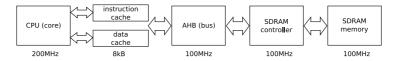

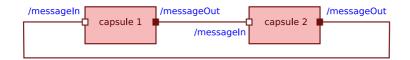

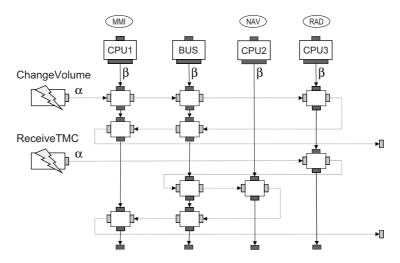

- Performance analysis techniques to predict and evaluate the real-time behavior of the copier control software running on hardware platforms (see e.g. Chapters 8, 12 and 13).

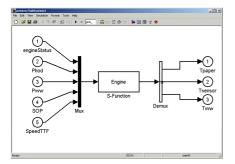

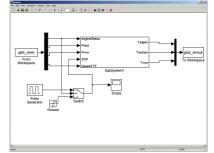

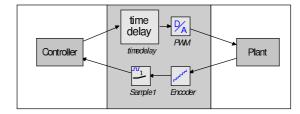

- Evaluation of real-time embedded control software via model-based simulation of its environment is discussed in Chapter 11.

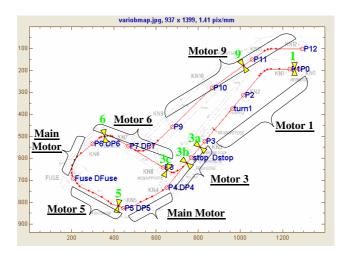

- The Happy Flow model, which supports the design of the paper transport systems in the copier. Strong visualization and animation complement the models. These are based on 'good weather' conditions: lower level (dynamical) phenomena of motors, slip, jitter and delays in control loops, et cetera, are not included. See Chapter 6 for an explanation of this model.

- Dynamical models including software execution times of part of the paper path around the fuse, where paper and image meet and accurate synchronization is needed [25].

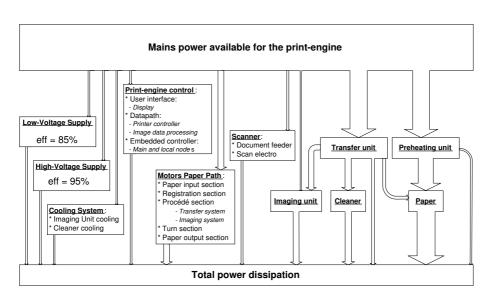

- Power budgets as visualized in Figure 2.5 are also used to understand power flows through a copier. Thickness of arrows in the figure is related to the amount of power flow. See Chapter 5 for more details. Note that a budget itself is a model with an underlying modeling formalism. In Chapter 5 a (sub)method is even described on how to create budgets.

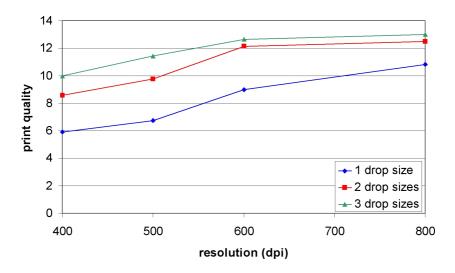

- Virtual printer models to assess the printing quality of new printer technologies are presented in Chapter 9

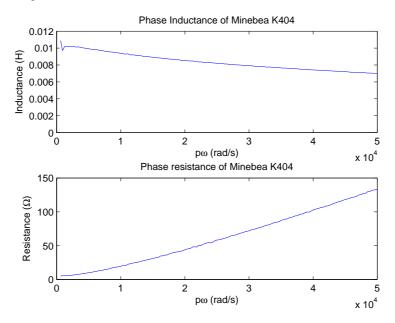

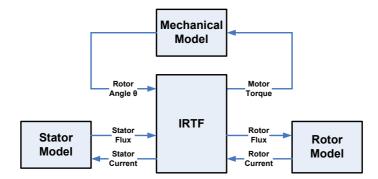

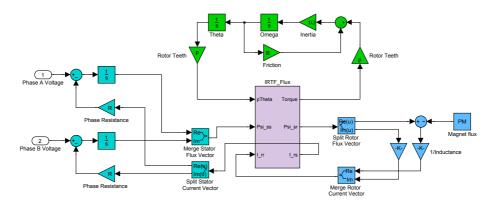

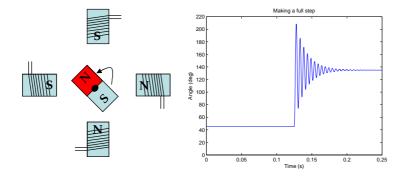

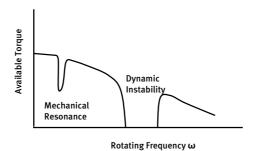

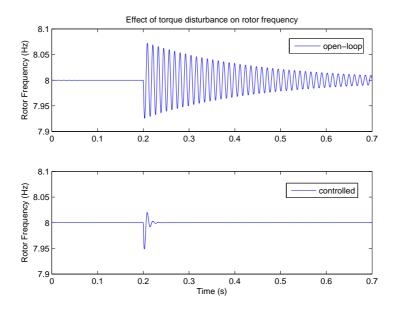

- Dynamical models and techniques that analyse and predict the behavior of stepper motors (power usage, vibrations and resonances, positioning accuracy, et cetera). In Chapter 10 an overview of the modeling activities is given.

- Event-driven control models (Chapter 16) are derived to study the control performance and the processor load of a new type of controllers that are used to control the motion of the image.

• And many others as documented in this book.

Figure 2.5: Visualization of the power flow through a copier.

## 2.6.2 Step 3b: Perform measurements

In step 3b - just as 3a - the goal is to gather the facts with which issues from step 2 can be dismissed by using measurements. Measurements can play two roles. Either they are used to tune the models to describe practice closely (parameter estimation, identification, model validation) or try to resolve a conflict directly - without a model - by using dedicated experiments. As measurements are from the 'real world', they are usually more authoritative than results from models. However, not every phenomenon can be measured readily, for example because sensors can not be inserted (the place where you would like to measure cannot be reached) or sensors disturb the phenomenon. It is difficult to determine the effects of parameter variation from measurements. Also, measurements can be faulty. Thus sanity checks are always required.

#### 22 A DESIGN METHODOLOGY FOR HIGH-TECH SYSTEMS

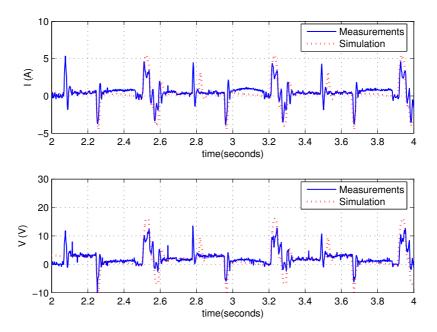

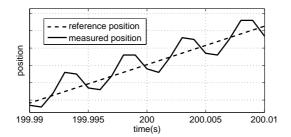

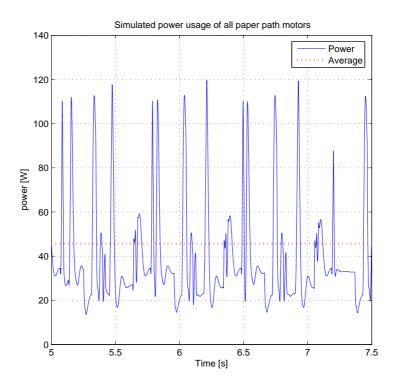

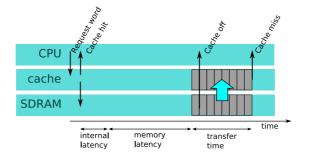

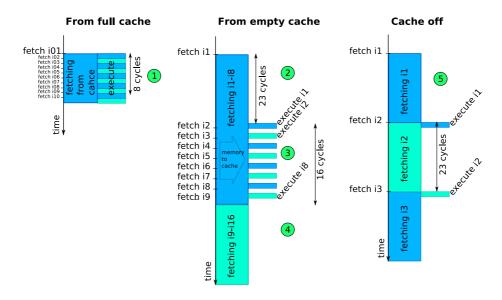

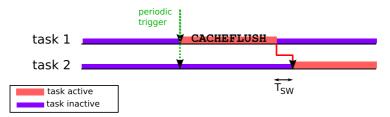

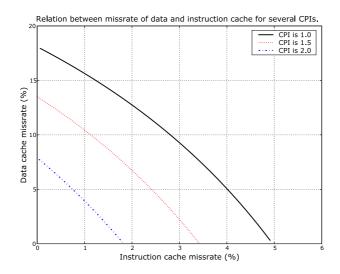

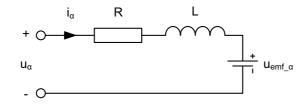

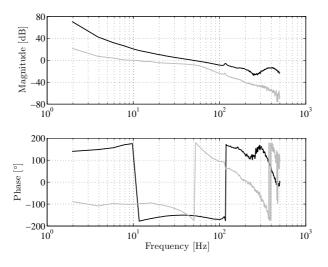

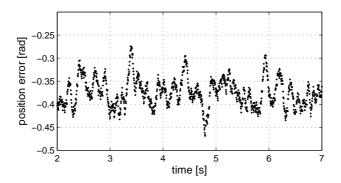

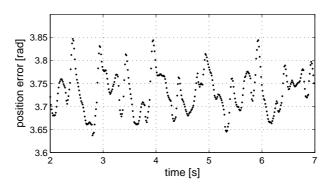

**Example:** A model was made of the dynamic behavior of the motors in the paper path [18], as mentioned before. This model was validated with measurements from a real motor in the copier being modeled (see Figure 2.6). Within the Boderc project, also measurements have been performed on hardware platforms to evaluate their real-timing behavior (e.g. the influence of caching in micro processors), see Chapter 8.

Often, it is very beneficial to have short iterative loops where measurements and modeling activities follow each other. The measurements show where the models can be improved and the models explain the measurements and show how design choices would influence the results. Models can often capture the relationships between system properties better than a finite number of measurements. Towards the end of a development project more and more the emphasis will shift from modeling (step 3a) towards prototyping and building the actual system (step 3b).

Figure 2.6: Simulation versus measurements for a single motor in the paper path.

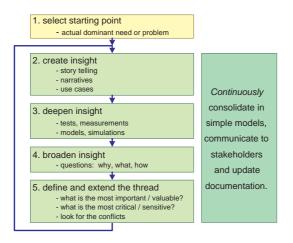

## 2.7 The method as a structured chart

The nice step-plan shown in the previous section is iterative as depicted in Figure 2.7. This figure contains the same steps, but shows the dynamic flow of information and the making of decisions. For instance, once step 3 has given conclusive answers on a particular issue of concern coming from 1b via step 2, a design decision can be taken.

The iteration now proceeds to a next issue of concern. However, also important information obtained during the in-depth study of the previous issues (e.g. data, models, design patterns) should be consolidated in the core domain knowledge (step 1c).

Figure 2.7: Dynamic flow of information in the method.

## 2.7.1 A 'schoolbook' example of Boderc reasoning

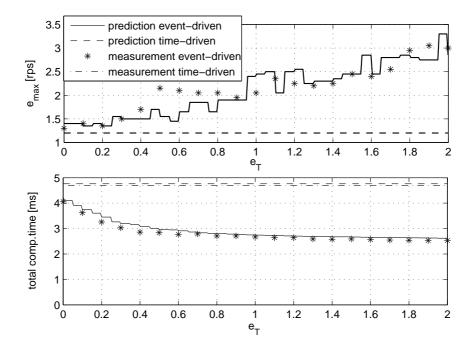

To give a good example on how the Boderc methodology and reasoning works we give a quick preview of the selection of the parameters of an event-driven control algorithm to control the position of sheets in the copier. Details on the particular case can be found in Chapter 16 on event-driven control. This particular problem might at some point be identified in step 1b as a realization aspect of concern. In step 2a the tension in this design issue can be found using threads of reasoning. It turned out that a trade-off had to made between control performance (e.g. tracking errors and disturbance attenuation), which is related to the key driver printing quality on one hand, and software performance (processor load of its implementation), which is related to the cost price (as a smaller CPU or fewer CPUs can be used) on the other. After collecting some figures-of-merit in step 2b it was concluded that more quantitative information

#### 24 A DESIGN METHODOLOGY FOR HIGH-TECH SYSTEMS

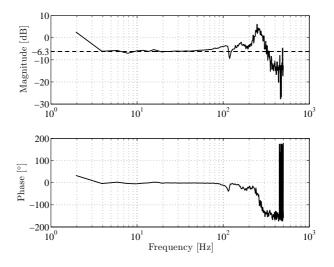

would be necessary. A detailed dynamical model (using Matlab/Simulink) was made that could predict the control performance (in terms of maximal tracking error  $e_{max}$ ) given the controller. By varying the main control parameter ( $e_T$ ) we could express the control performance as a function of this parameter. Using the outcomes of this simulation model, also the number of control computations could be derived. Together with micro-measurements (step 3b) on the platform the controller would be implemented on, a prediction could be made of the processor load (in terms of total computation time over a given time interval). Both graphs are given in Figure 2.8.

Figure 2.8: Both control performance and software performance as function of the main control parameter  $e_T$ .

These two graphs are returned to phase 2b in which this is the necessary quantitative information to make a well-founded trade-off by a system architect as he can now oversee the consequence in both domains. Actually, the predictions in Figure 2.8 were validated later by measurements on a prototype.

Typically, in the way of working above, in-depth detailed models were used to make predictions. Not the whole model was given to step 2, but only system-level abstractions of it. Of course, both the models as well as the curves leading to the decision can now be consolidated and documented as core domain knowledge (step 1c) and another realization aspect of concern can be considered next. Sometimes the in-

depth study might also trigger new questions and new aspects of concern. For instance, maybe there is not a satisfactory value for the control design parameter that satisfies the requirements. This might trigger a reconsideration of the processing platform on which the controller is implemented. As only micro-measurements (or benchmark numbers) are needed to perform the prediction of the processor load, the modeling effort can also support the selection of the processing platform.

## 2.7.2 Placing the Boderc activities in the Boderc methodology

Figure 1.9 in the Introduction has already given a rough positioning of the Boderc activities within the methodology. Typically, the modeling formalisms and corresponding techniques for studying particular aspects or subsystems of the to-be-developed machine can be seen as 'plug-ins' that are used in the steps of the method. For several aspects (e.g. printing quality, power usage, throughput, et cetera) and different parts of the copier (e.g. ranging from detailed models for particular stepper motors and parts of the digital control architecture to system level models of the complete paper track), models and corresponding techniques were are applied. In view of the design pyramid in Figure 1.8 these models have various levels of detail. Typically, Chapters 6-9 are more system level models and Chapter 10-16 describe the more detailed models. Both categories can be used as 'plug-ins' in step 3a to get quantitative information and insight in the qualitative tensions identified in step 2a. Next to the overall method of the Boderc design methodology given in Section 2.3 there are three submethods: Key driver method (Chapter 3), Threads of reasoning (Chapter 4) and Budget-based design (Chapter 5). However, when designing subsystems one might use mono-disciplinary submethods. For instance, for the synthesis of control algorithms one might use typical design methods as available within control engineering.

## 2.8 Conclusions

As we are all aware, there is a strong need for multi-disciplinary methodologies that support the system architecting process. In [82] various reasons are mentioned that hamper the creation of such methodologies. In this chapter we presented research to overcome two of them: lack of description and lack of connection to mono-disciplinary techniques. This resulted in an emerging design methodology that was stated in an explicit manner. The methodology consists of a reasoning framework in the form of a multi-step method, modeling formalisms, analysis techniques and tools. By giving place to modeling and analysis activities, which can be mono-disciplinary, a first step is made in connecting the multi-disciplinary method to mono-disciplinary techniques.

Previous to writing this chapter, some steps were taken to validate the methodology. Although various issues remain open, we can already draw the following conclusions:

• The Boderc methodology mimics the way of working of a senior system architect. For instance in [70] the steps of the method can be recognized in the

### 26 A DESIGN METHODOLOGY FOR HIGH-TECH SYSTEMS

evaluation of an architecture for a DVD hard-disk recorder. As shown by [70], applying the steps of the methodology can prevent system architects from falling prey to ill-founded non-quantitative reasoning, which can lead to trade-offs based on incorrect assumptions instead of on quantitative arguments and facts.

- Discussions with junior and senior system architects from Philips revealed that there is a clear recognition of the steps in the method. It matches their way of working and it makes that more explicit. They acknowledged the value of the methodology. Of particular interest for them were the visualizations, e.g. the key driver model in Figure 2.1 and tensions and conflicts in a thread of reasoning diagram (Figure 2.3). Documenting design decisions and capturing the main arguments in insightful overviews were considered particularly valuable. Also various models as, for instance, the Happy Flow model (Chapter 6) contain a lot of implicit design decision, which can be extracted.

- The application of individual modeling activities (using formalisms and techniques) on particular industrial problems (e.g. paper flow scheduling, stepper motor dynamics analysis, et cetera) were considered beneficial by Océ.

Of course, many issues are still open within this methodology, as in the whole field of multi-disciplinary design. For instance, finding the right level of abstraction for modeling formalisms in an industrial setting is hard. Many academic (monodisciplinary) formalisms are too complex and many state-of-practice formalisms are too coarse. Finding the right balance between them is an important issue for future research. Extending the design methodology by further formalisms and tools (especially selecting design aspects of concern in step 1b and selecting critical design issues in step 2b) is also open. Hence, by making an attempt to be explicit, this chapter hopefully initiates many discussions, allows further validation of the design methodology and stimulates future ESE research.

## Chapter 3

# The key driver method

Authors: W.P.M.H. Heemels, L. Somers, P.F.A. van den Bosch, Z. Yuan, B. van der Wijst, A. van den Brand and G.J. Muller

This chapter is a re-worked version of a paper for the International Conference on System Engineering and Applications (ICSSEA) 2006.

## 3.1 Introduction

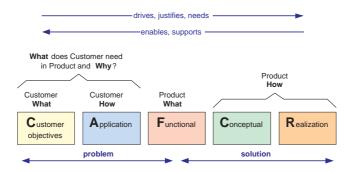

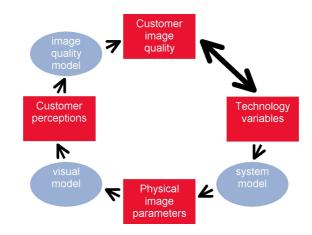

The complexity of the products being designed by industry today is increasing at an astonishing rate. To keep the design of complex machines focused, it is important to know the essential customer objectives and to relate these to those system requirements that have the largest influence. A structured graph showing these relations helps to keep an overview of the overall design. In particular, specifications can be easily traced back to the objectives of the customer. The key driver method is one of the possible means to obtain the system requirements in a systematic way and to provide such a structured overview. The key driver method fits in the broader framework of the CAFCR methodology [81], which is a decomposition of a system architectural description into five views, shown in Figure 3.1. The customer objectives view (what does the customer want to achieve) and the *application* view (how does the customer realize his goals) capture the needs of the customer. These needs provide the justification ('why') for the specification and the design of the product. The *functional* view describes the 'what' of the product, which includes (despite its name) functional and non-functional requirements. The 'how' of the product (the technical solution) is described in the *con*ceptual and realization views. In this way CAFCR is focused on the relation between the customer world and the product. The functional view can be seen as the interface between the problem and solution world. Another dimension in specification and design is the *manufactural* view. This view describes operational aspects of the product

#### 28 THE KEY DRIVER METHOD

manufacturer (not the operational aspects of the customer that belong to the A view) like preferred way of designing and producing, culture, type and number of employees, et cetera, The job of the system architect is to integrate all views in a consistent and balanced way to get a valuable, usable and feasible product.

Figure 3.1: CAFCR views

The key driver method can be considered a 'CAF submethod' of CAFCR. The key *drivers* represent the main customer objectives (C view). The key driver method helps to derive the more detailed and quantified system requirements (F view). It translates a few (three to six) customer key drivers into maybe hundreds of system requirements. For instance, in the copier case study, 3 key drivers will be expanded to some 40 system requirements. A bridge between key drivers and requirements is a layer of application drivers, typically representing the A view. The key and application drivers in the customer views (CA) will be linked via requirements (F) to design choices in the other views (CR). Structuring this information graphically helps to keep a good overview over the design process. It is useful for the designers to see why a certain requirement is important from a customer perspective: to understand the 'why' behind the requirements they have to realize (traceability). The final system requirements are determined on one hand by the customer side (the objectives coming from CA views), but on the other hand just as much by the technical (im)possibilities and solutions side (CR) and the manufactural view. The key driver method focuses on the CAF views, but, as the final key driver model is a living entity, the influence of the CR views grows during the design process. Closely related to the key driver method is Goal Oriented Design [6, 74, 129], which is also based on analysis of the customer needs and goals in a hierarchical fashion. A goal oriented approach like KAOS [74] or GRL [115] starts with goals and derives requirements from them. URN [5] combines use case maps [23, 33, 114] (manufactural and functional requirements) and GRL (nonfunctional requirements). Also in Quality Function Deployment [96], where the term 'benefit' is used for key driver, the link between benefits, engineering requirements and design concepts is emphasized. The key driver method gains its value from relating a few sharply articulated key drivers to a much longer list of requirements. By capturing these relations, a much better understanding of customer and product requirements is

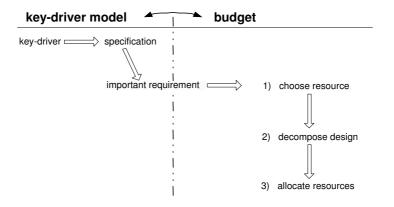

achieved. The 'why' behind requirements is documented and the focus is maintained on the most important issues and the trivial ones are left out. Other important values are its conceptual simplicity and the fact that all product creation phases and corresponding views are taken into account. This chapter describes the key driver method and provides guidelines how to obtain a key driver model. Its application and effectiveness are shown for a high-volume copier. The goal of the industrial case study is to understand the end user requirements by building a key driver model. Moreover, the key driver method is extended by a matrix that links the functional decomposition of the copier to the requirements obtained via the key driver method. This extension offers the possibility to have an overview of the 'responsible' functions for realizing a specific requirement as the matrix provides a first breakdown of a requirement into the functional subsystems. This gives a means to monitor the progress or can even be a starting point for further design support techniques, like budget-based design [96]. The outline of the chapter is as follows. In Section 2 the key driver method is presented. Section 3 explains the case study of the copier and applies the key driver method. In Section 4 the final graphical overview of the key driver model is shown and discussed. In Section 5 we combine the results of the key driver model with a breakdown of all the requirements with respect to the functional decomposition of the copier. Section 6 gives the strengths and limitation of the model and the lessons learned. We end with the conclusions in Section 7.

## 3.2 Key driver method

The key driver method couples the customer side captured in the key drivers (Customer Objectives view) to the product side (Conceptual and Realization view) via the application driver (Application view) and system requirements (Functional view). The following ingredients play an important role:

- *Key drivers* (C view): the top three to six driving customer objectives: what does the customer want? For instance, a copier in a copy shop must print large volumes in a short time. Thus, productivity is a key driver.

- *Application drivers* (A view): Drivers that describe how the customer is realizing the key drivers: how does the customer achieve his goals? Application drivers are closer to the solution space than the key drivers. For instance, the productivity of a copier can be achieved by a.o. speed of printing and reliability. Speed and reliability are typical derived application drivers for productivity.

- System requirements (F view): Detailed (often quantitative) specifications of the product or its subsystems. For instance, the speed of printing can be related to the system requirement of 85 pages per minute (for A4 paper) in full production.

The C(ustomer objectives), A(pplication) and F(unctional) views are explicitly included in the key driver model. However, it does not explicitly include the C(onceptual)

#### 30 THE KEY DRIVER METHOD

and the R(ealization) views (solution side) although these views have a strong influence on the final system requirements as well. Also the operational constraints and preferences of the manufacturer and other stake holders than the main customers determine the final requirements. This information is implicitly included via the process of setting up the key driver model as described below e.g. via interviews with engineers or system architects and using core domain knowledge from the manufacturer's previous projects.

| Define the scope specific.                                  |                       | in terms of stakeholder                            | or market segments                                               |

|-------------------------------------------------------------|-----------------------|----------------------------------------------------|------------------------------------------------------------------|

| Acquire and analyze facts                                   | and ask why questions |                                                    | product specification<br>of existing products .                  |

| Build a graph of relations be<br>by means of brainstorms an |                       |                                                    | where requirements<br>have multiple drivers                      |

| Obtain feedback                                             | dise                  | cuss with customers, o                             | bserve their reactions                                           |

| Iterate many times                                          |                       | nderstanding often trig<br>r to requirement or vic | gers the <b>MOVE</b> of issues<br>be versa and <b>rephrasing</b> |

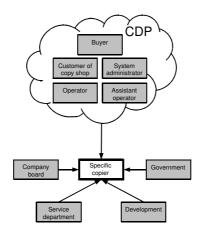

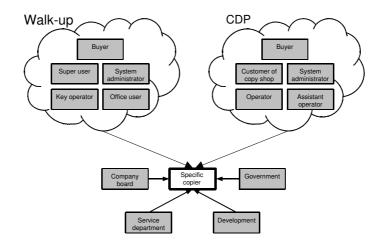

Figure 3.2: Method to link key drivers to requirements by iterating over four steps

Figure 3.2 gives an outline of the key driver technique. The *first step* is to define the scope of the key driver graph. From which customer or other stake holders do we want to understand the objectives or needs? For the choice of the customer it is important to determine the market segment of the product. Also the system boundary plays an important role. For instance, for a copier, do we want to consider a stand-alone copier (with for example an office user as user) or do we consider a complete copy shop (with multiple networked copiers) for which the main operator or the director of the shop might be the main stakeholder? The *second step* is to acquire facts, for example by extracting functionality and performance figures out of the product specification (for the predecessors of the to-be-developed system). Analysis of this information recovers implicit and hidden facts. The requirements of an existing system can be analyzed by asking 'why questions' and mapping this to the new product. For example: 'Why does the copier need additional turning of sheets?' At this point one might have an unstructured collection of various key and application drivers together with requirements. The *third step* is to bring more structure in the facts, by building a graph, which connects requirements to key drivers. A workshop with brainstorms and discussions is an effective way to obtain such a graph. In this case, it is important to get the right people around the table representing the different views: marketing, strategic planning, system architecting and involved engineering disciplines. Also, interviews with people from previous projects or the current development project can be very beneficial in this stage. The *fourth step* is to obtain feedback from customers. The total graph can have a lot of many-to-many relations, i.e. requirements that serve many drivers and drivers that are supported by many requirements. The graph is good if it is as simple as possible and the customers are enthusiastic about the key drivers and the

derived application drivers. If a lot of explanation is required, then the understanding of the customer is far from good. Frequent iterations over these steps improve the quality of the understanding of the customer viewpoint. Each iteration causes some movements of elements in the graph in driver or requirement direction and also causes rephrasing of elements in the graph. The use of the key driver technique benefits from the following guidelines:

- The most important goals of the customer are obtained by limiting the number of key drivers. In this way the participants in the discussion are forced to make choices.

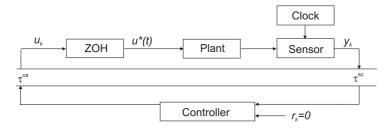

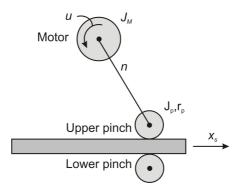

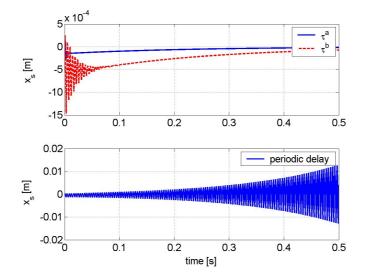

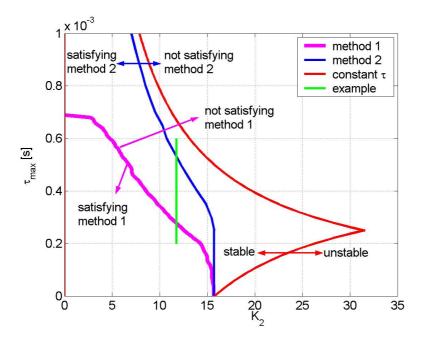

- The focus in product innovation is often on differentiating features, or unique selling points. As a consequence, the core functionality from the customer point of view may get insufficient attention. For instance, consider cell phones that are overloaded with features, but have a poor user interface for making calls. The core functionality must be dominantly present in the graph.