# Cad of masks and wiring

Citation for published version (APA): van Lier, M. C., & Otten, R. H. J. M. (1974). Cad of masks and wiring. (EUT report. E, Fac. of Electrical Engineering; Vol. 74-E-44). Technische Hogeschool Eindhoven.

### Document status and date:

Published: 01/01/1974

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 04. Oct. 2023

th

ារី១ ស្មាធ្លាល ទាំបង្គោះបាល ១០ ឯក្រោញស្រា ១៨១ ឧទ្ទទ

land that the first section and has been

C.A.D. OF MASKS AND WIRING

by

Ir. M.C. van Lier and

Ir. R.H.J.M. Otten

Department of Electrical Engineering, Eindhoven University of Technology, Eindhoven, The Netherlands.

C.A.D. OF MASKS AND WIRING

bу

Ir. M.C. van Lier

and

Ir. R.H.J.M. Otten

T.H. Report 74-E-44

February 1974

ISBN 90 6144 044 0

# CONTENTS

|      | INTRODUCTION                                                   | 1   |

|------|----------------------------------------------------------------|-----|

| ı.   | GRAPHTHEORETICAL NOTIONS                                       | 3   |

| II.  | ROUTING ALGORITHMS                                             | 10  |

|      | 1. Simple connection algorithm on a grid                       | 10  |

|      | 2. Simple connection algorithm on a graph                      | 12  |

|      | 3. Simple multilayer connection algorithm                      | 1.5 |

|      | 4. Generalizations                                             | 18  |

| III. | THE MATHEMATICAL FORMULATION OF THE WIRING PROBLEM             | 22  |

|      | 1. Introduction                                                | 22  |

|      | 2. Graphtheoretical base                                       | 23  |

|      | 3. The mathematical formulation                                | 29  |

|      | 4. Examples                                                    | 32  |

|      | 5. Concluding remarks                                          | 35  |

| IV.  | MODIFICATIONS OF A MONOLITHIC IC                               | 43  |

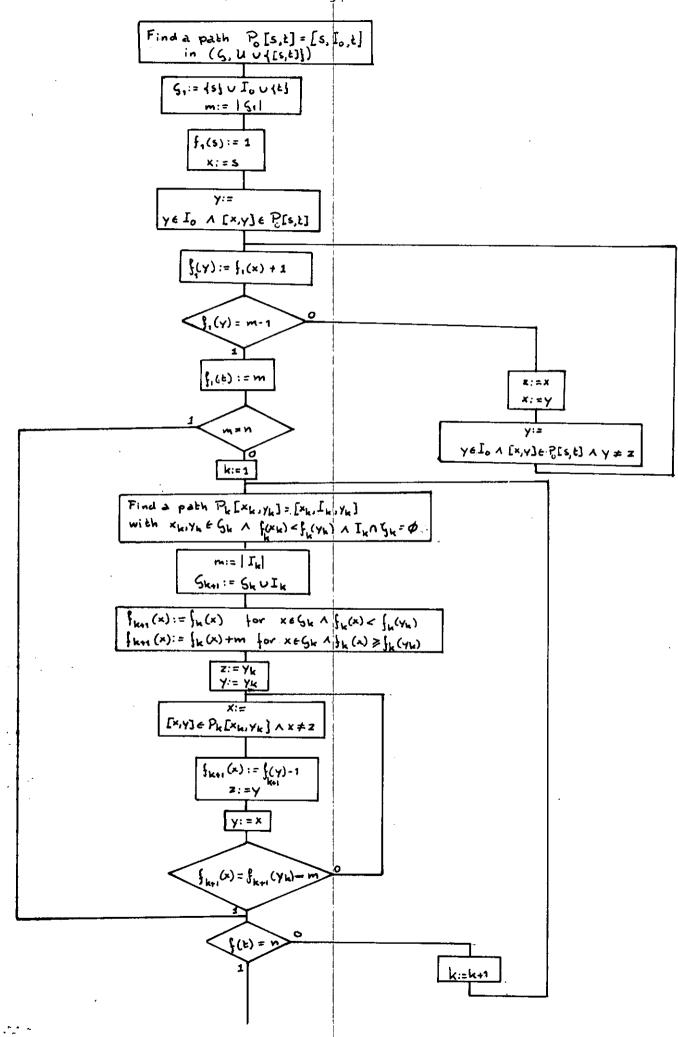

| v.   | THE CEL-ALGORITHM                                              | 49  |

|      | 1. Assigning a drain function to a graph                       | 49  |

|      | 2. Deltas and their formulas                                   | 55  |

|      | 3. The CEL-algorithm                                           | 60  |

|      | 4. Two examples                                                | 65  |

| VI.  | OTHER PLANARITY ALGORITHMS                                     | 70  |

|      | 1. A planarity-test based on an iterative decomposition method |     |

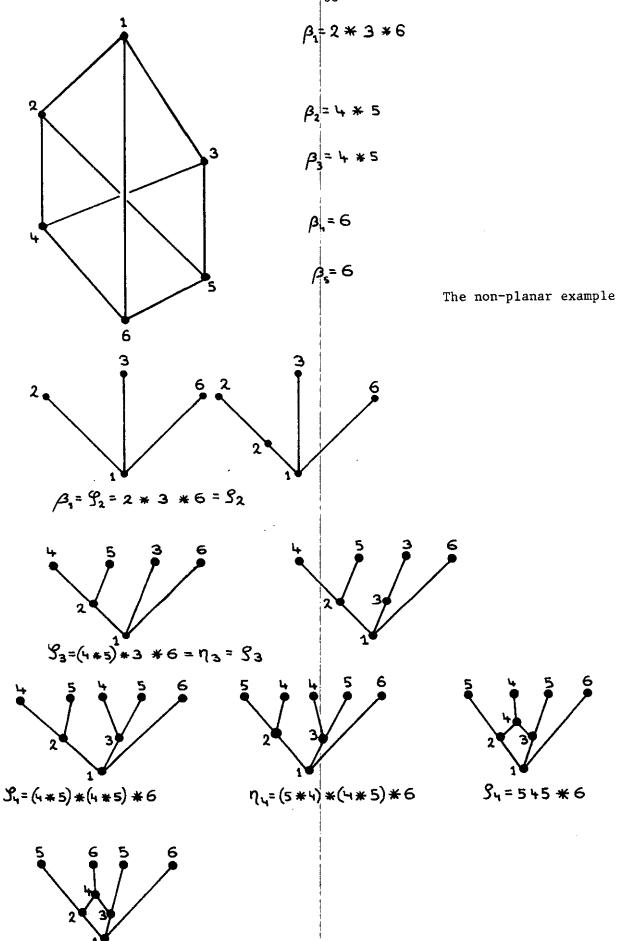

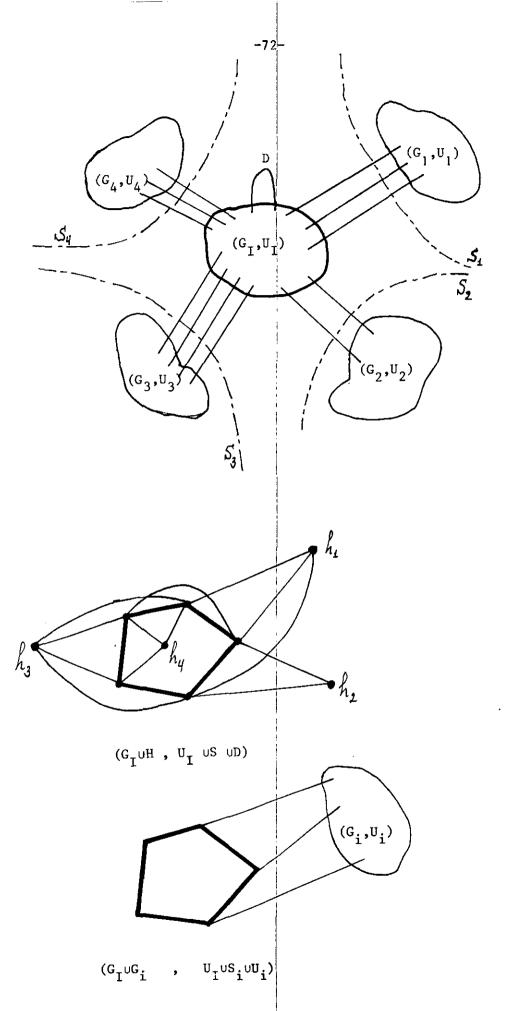

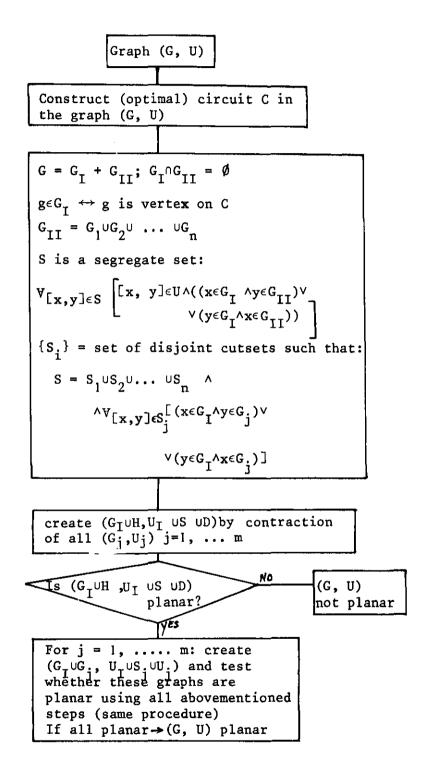

|      | ("pseudo-Hamiltonian method")                                  | 70  |

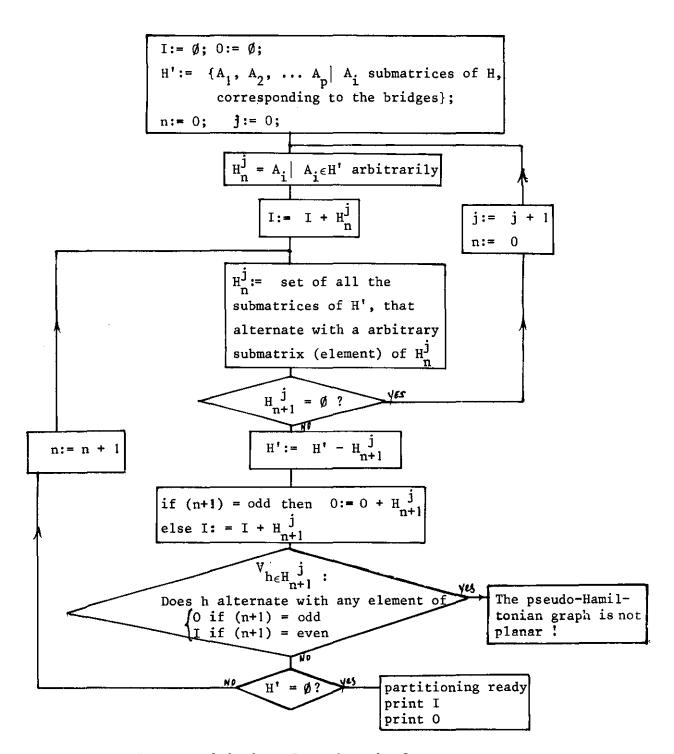

|      | 2. Planarity-tests based on matrix methods                     | 78  |

|      | 3. The whirl-method                                            | 86  |

|      |                                                                | •   |

| VII. | THE PLANARISATION OF NONPLANAR NETWORKS                        | 89  |

|      | 1. Terminalvalues                                              | 89  |

|      | 2. Planar equivalents of polygons                              | 94  |

|      | 3. Concluding remarks                                          | 97  |

|      | Appendix                                                       | 98  |

#### INTRODUCTION

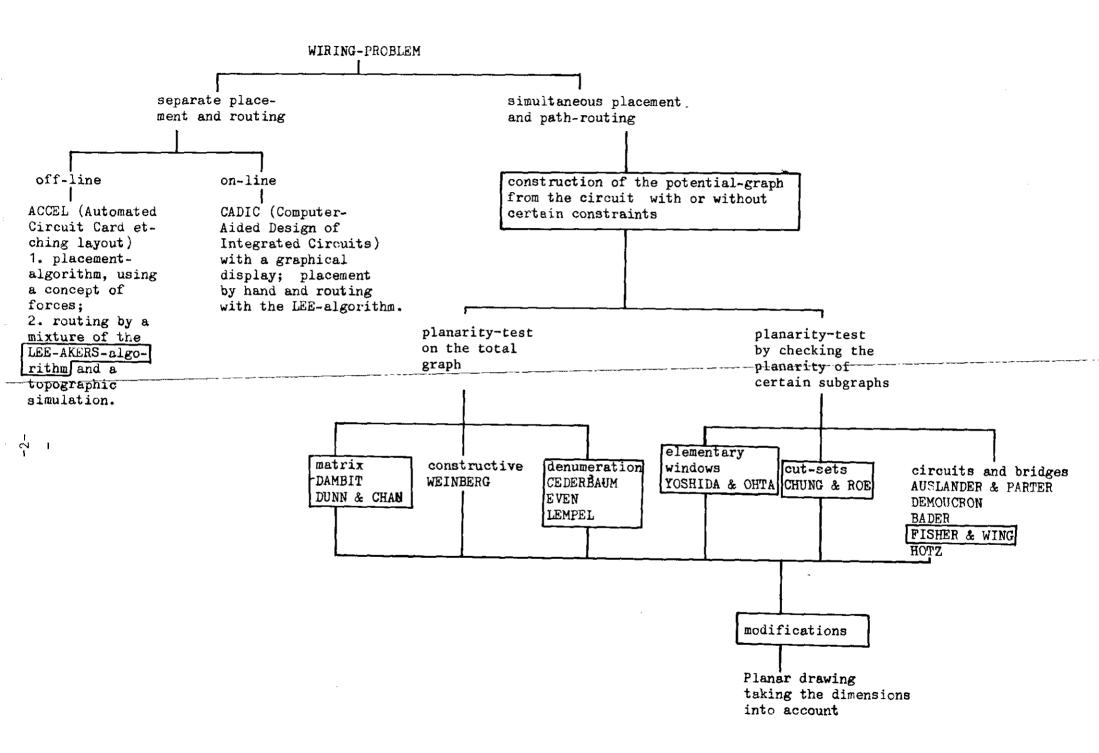

This report emanates from a seminar of the group EEC, held in spring 1972, and it reflects our knowledge in the field of automatic wiring design, built up during the first months of that year. At the second session the participants discussed the schematic overview of page 2. The framed subjects in this scheme were pointed out as topics of the sessions to follow. In the seminar the simultaneous "placement-and-routing"-part was emphasized, so that only the Lee-Akers-algorithm was presented (by Prof. Jess at the third session), since it was the most representative and general of all routing algorithms. A flaw was elicited during this session and a correction seemed to be difficult. Our ideas about this algorithm are more mature now

Next in this report we have a short introduction to notions in graph theory, although this was a subject of the fourth session. This reordering was necessary, because of the final description of routing algorithms and problem formulations in which some of the notions are employed.

and that is why the treatment of the subject is different in this report.

Starting from a simple "minimum-distance" algorithm we generalize as far as

The mathematical formulation is published as an article in the "International Journal of Circuit Theory and Applications". The fourth and the fifth constraint were presented in the formulation for the whirl problem, but the solutions given during the session were basically wrong. We added some directives for technological modifications.

Four planarity tests were given then

possible ending up with an abstract model.

- CEL-algorithm: preceded by the treatment of "drain functions" and "deltas

and their formulas";

- 2. pseudo-hamiltonian method;

- 3. methods using matrices;

- 4. whirl method.

The last session was concerned with planarization of networks. It concludes also this report.

M.C.van Lier, R.H.J.M. Otten, "On the mathematical formulation of the wiring problem", Int.Journ. of Circuit Theory and Applications, Vol.1,137-147, March, 1973.

### I. GRAPHTHEORETICAL NOTIONS

We start from a non-empty set G, the so-called set of vertices. On this set we define a binary relation:  $\Gamma \subseteq G \times G$ . The elements of  $\Gamma$  are called arcs. Our notation of an arc will be [x,y] with x and y as terminal vertices. In the following the set of arcs will be designated by V.

The pair consisting of G and V is called a digraph, and is denoted by (G,V). We assume the relation  $\Gamma$  to be antireflexive (this means  $[x,x] \notin \Gamma$ ). A digraph is finite, when G is finite. We will restrict ourselves to finite digraphs. If the relation  $\Gamma$  is symmetric  $([x,y] \in \Gamma + \{y,x\} \in \Gamma)$ , we speak of a graph, here denoted by (G,U) with  $U = \{[x,y] \mid [x,y] \in \Gamma\}$ . W is a set of non-ordered pairs of vertices, called edges. We speak of a multigraph, when U is a family.

The relation  $\Gamma$  can be treated as any other binary relation: We write  $y \in \Gamma(x)$ , when  $\{x,y\} \in \Gamma$ .

The inverse of  $\Gamma$  is denoted by  $\Gamma^{-1}$ , and is defined by  $\Gamma^{-1}(y) = \{x | y \in \Gamma(x)\}$ . We define the powers of  $\Gamma$  in the following way:

$$\Gamma^{0}(\mathbf{x}) = \{\mathbf{x}\}$$

$$\Gamma^{1}(\mathbf{x}) = \Gamma(\mathbf{x})$$

$$\Gamma^{i}(\mathbf{x}) = \Gamma(\Gamma^{i-1}(\mathbf{x}))$$

$$\Gamma^{-i}(\mathbf{x}) = (\Gamma^{-1})^{i}(\mathbf{x})$$

(i is a non-negative integer)

The transitive closure  $\hat{\Gamma}$  of  $\Gamma$  is defined by  $\hat{\Gamma}$   $(x) = \{x\} \cup \Gamma(x) \cup \Gamma^2(x) \cup \Gamma^3(x)$  ..... For digraphs we have also the following notions:

$|\Gamma(x)|$  is called the out-degree of x and is denoted by  $\gamma^+(x)$ .  $|\Gamma^{-1}(x)|$  is called the in-degree of x and is denoted by  $\gamma^-(x)$ .  $\gamma(x) = \gamma^+(x) + \gamma^-(x)$  is the degree of x. xeG is a source, when  $\Gamma^{-1}(x) = \emptyset$  or equivalently  $\gamma^-(x) = 0$  xeG is a sink, when  $\Gamma(x) = \emptyset$  or equivalently  $\gamma^+(x) = 0$  For graphs we have only the degree of xeG:  $\gamma(x) = |\{y \mid [x,y] \in U\}|$ .

Suppose we have two digraphs  $(G_1,V_1)$  and  $(G_2,V_2)$ , and a bijective mapping : from  $G_1$  into  $G_2$ . Then  $\phi$  is called an isomorphic mapping (or an isomorphism), if

$$[x,y>\epsilon V_1 \leftrightarrow [\phi(x), \phi(y)>\epsilon V_2]$$

If such a mapping exists, then  $(G_1,V_1)$  and  $(G_2,V_2)$  are called isomorphic. For graphs we have a similar definition.

A graph (G,U) is called topological if:

- 1. G is a set of points in a topological space R, and U is a set of open Jordancurves in R,

- 2. the terminal points of an edge of U are in G,

- 3. the edges of U have no other points in common than terminalpoints.

In the case of digraphs we give the Jordancurve [x,y> an orientation in the direction of y.

(G',U') is a topological representation of (G,U), if (G,U) and (G',U') are isomorphic and (G',U') is a topological graph.

A graph is called planar, when it has a topological representation in a plane.

The graph (G',U') is a subgraph of (G,U), when  $G' \subset G$  and  $\forall_{u \in U'} [u \in U]$ .

The name chain is given to a sequence  $v_1, v_2, \ldots, v_k$  of arcs of (G,V) such that, if  $v_i = [x_i, y_i]$ , then  $y_i = x_i$  for  $i = 1, 2, \ldots, k-1$ . A chain is simple, if no arc occurs twice in the sequence. It is called elementary, if it does not contain a vertex twice. We denote a chain by  $C[x_i, y_k]$ . A cycle is a chain in which  $x_i = y_k$ . A cycle is elementary if, apart from  $x_i$  and  $y_k$ , every vertex in it is distinct from the others. A digraph is called acyclic, when it has no cycles. The length of a chain is the number of its arcs.

A path is a sequence  $u_1, u_2, \ldots, u_k$  of edges of a graph (G,U) in which we have with  $u_i = [x_i, y_i]$ , that  $y_i = x_i + 1$  and  $y_{i-1} = x_i$  for  $i = 2, 3, \ldots, k-1$ . A path is simple, when all its edges are different, and elementary, when every vertex in it appears only once. A path is denoted by  $P[x_1, y_k]$ . A circuit is a path with  $x_1 = y_k$ , and it is called elementary, when all its vertices  $x_1, x_2, \ldots, x_k$  are distinct.

A graph (G,U) is connected, if for every pair of vertices in G there is a path between them. A component of (G,U) is a maximal connected subgraph of (G,U). A vertex x of G is an articulation point of (G,U), if the number of components of the subgraph obtained by deleting x and all the edges incident to x is one higher than in (G,U).

The orem 1: A vertex a is an articulation point of a connected graph, if and only if there exist two vertices x and y such that every path joining x and y contains a.  $(x \neq a \neq y)$ .

The proof of this theorem is trivial.

A graph (G,U) is said to be biconnected, if it is connected, and it contains more than one edge and no points of articulation.

Theorem 2: Given any elementary path  $P[a_0,a_1,\ldots,a_k]$  joining two distinct vertices  $a_0$  and  $a_k$  of a biconnected graph (G,U), we can associate with it two elementary paths P' and P" such that:

- 1. P' and P" join both a and ak,

- 2.  $a_0$  and  $a_k$  are the only vertices which P' and P" have in common,

- 3. if P' or P" is followed from a<sub>0</sub> to a<sub>k</sub>, the indices of the vertices of P encountered on route are in increasing order.

<u>Proof:</u> The theorem is trivially true, when P has length 1 ( $P = [a_0, a_1]$ ), for U contains at least two edges, and neither  $a_0$  nor  $a_1$  can be an articulation point.

Let us assume the theorem to be true for all elementary paths of length k, and deduce from this that it is also true for the elementary path

$$P[a_0, a_{k+1}] = [a_0, a_1, \dots, a_k, a_{k+1}].$$

By hypothesis there exist two disjoint paths  $P_0'$  and  $P_0''$  joining  $a_0$  and  $a_k$ , and satisfying the conditions of the theorem. We now have to show the existence of two paths P' and P'' between  $a_0$  and  $a_k + 1$  with analogous properties.

From theorem 1 we know that there is a path  $Q[a_0, a_{k+1}]$ , which does not contain  $a_k$ . Let us denote by q the vertex of  $Q[a_0, a_{k+1}]$  nearest to  $a_{k+1}$ , and which is also in  $P[a_0, a_k]$  or  $P[a_0, a_k]$  or  $P[a_0, a_k]$ .

We distinguish four cases:

- I.  $q = a_0$ : This case is simple:  $P'[a_0, a_k + 1] = P[a_0, a_{k+1}]$  $P''[a_0, a_k + 1] = Q[a_0, a_{k+1}]$

- II.  $q = a_{k+1}$ :

This means that  $q \notin P[a_0, a_k]$ . This leaves two analogous cases:  $q \in P_0'[a_0, a_k]$  or  $q \in P_0''[a_0, a_k]$ . Take for example  $q \in P_0'[a_0, a_k]$ , then

$$P'[a_0,a_k] + 1] = P'_0[a_0,q]$$

$P''[a_0,a_k] + 1] = P''[a_0,a_k] + [a_k, a_{k+1}]$

III.  $q \ell P[a_0, a_{k+1}]$ :

This means that either  $q \epsilon P_0'[a_0, a_k]$  or  $q \epsilon P_0''[a_0, a_k]$ . In the latter case (the former isanalogous), we take

$$P'[a_0,a_k + 1] = P'_0[a_0,a_k] + [a_k,a_k + 1]$$

$P''[a_0,a_k + 1] = P''_0[a_0,q] + Q[q,a_k + 1]$

IV.  $q \in P[a_1, a_k]$ :

Then we can write  $q = a_m$  with m<k. Let p be the highest index with  $a_p \in P[a_0, a_{k+1}]$ ,  $a_p \in P_0'[a_0, a_{k+1}]$  ( $a_p \in P_0'[a_0, a_k]$  is analogous) and p<m.

In such a case we take

$$P'[a_0,a_k+1] = P'_0[a_0,a_k] + [a_k,a_k+1]$$

$P''[a_0,a_k+1] = P''_0[a_0,a_p] + P[a_p,a_m] + Q[a_m,a_k+1]$

Theorem 3: Given two arbitrary edges  $u_1$  and  $u_2$  of a connected graph, we can construct an elementary path, which starts with  $u_1$  and finishes with  $u_2$ .

Proof: If u<sub>1</sub> = [a,x] and u<sub>2</sub> = [b,y], then since the graph is connected, the

vertices a and b can be joined by an elementary path P[a,b] =

[a, a<sub>1</sub>, a<sub>2</sub>, ... a<sub>k</sub> = b].

Again four cases (the required path is denoted by P<sub>0</sub>):

I.

$$xtP[a,b]$$

,  $ytP[a,b]$ :

$$P_0 = [x,a] + P[a,b] + [b,y]$$

II.  $x \notin P[a,b]$ ,  $y \in P[a,b]$ :

$$P_0 = [x,a] + P[a,y] + [y,b]$$

III. xεP[a,b], yέP[a,b]:

$$P_0 = [a,x] + P[x,b] + [b,y]$$

IV.  $x \in P[a,b]$ ,  $y \in P[a,b]$ :

$$P_0 = [a,x] + P[x,y] + [y,b]$$

Theorem 4: Given two arbitrary edges u<sub>1</sub> and u<sub>2</sub> of a biconnected graph, an elementary circuit exists which contains u<sub>1</sub> and u<sub>2</sub> both.

<u>Proof</u>:  $P[a_0, a_k]$  is an elementary path with  $u_1 = [a_0, a_1]$  and  $u_2 = [a_k - 1, a_k]$ . Such a path exists, as is said by theorem 3. From theorem 2 we know that in such a case there exist two disjoint paths  $P'[a_0, a_k]$  and  $P''[a_0, a_k]$  with the properties advertised there.

Let us denote by p the first vertex of  $P[a_0,a_k]$  after  $a_0$ , which is also in  $P'[a_0,a_k]$  or in  $P'[a_0,a_k]$  and by q the last vertex before  $a_k$  with the same properties.

We have three cases this time:

I.  $p = a_k$ :

Necessarily  $q = a_0$  then. The required circuit is  $P[a_0, a_k] + P'[a_k, a_0]$

II.  $p \neq a_k$  and thus  $q \neq a_0$ ; further  $p \in P'[a_0, a_k]$  and  $q \in P'[a_0, a_k]$ . (The case  $p \in P''[a_0, a_k]$  and  $q \in P''[a_0, a_k]$  is analogous). Now we take

$$P[a_0,p] + P'[p,q] + P[q,a_k] + P''[a_k,a_0]$$

III. Again  $p \neq a_k$  and  $q \neq a_0$ , but now  $p \in P'[a_0, a_k]$  and  $q \in P''[a_0, a_k]$ .

(The case  $p \in P''[a_0, a_k]$  and  $q \in P'[a_0, a_k]$  is analogous).

$$P[a_0,p] + P'[p,a_k] + P[a_k,q] + P''[q,a_0]$$

We have a biconnected graph (G,U). Let H be a subset with  $|H| \ge 2$ . We suppose that (G,U) has the following property:

(G,U) has a topological representation (G',U') in a plane such that H is completely contained in a circuit C' that (of course) divides the rest of the plane into two connected open domains and one of these domains contains no edge of U'.

Such a graph is called H-accessible and the representation (G',U') is called an H-periphere representation. Two elements  $h_1$  and  $h_2$  of H are said to be G'-adjacent, if there is a path  $P[h_1',h_2']$  between  $h_1'$  and  $h_2'$  which is on the periphery C' of (G',U') and which contains no vertex of  $H'\setminus\{h_1',h_2'\}$ .

Theorem 5: If (G',U') and (G",U") are both H-periphere representations of an H-accessible graph (G,U), then every G'-adjacent pair is also a G"-adjacent pair.

Proof: If |H|≤3, then there is nothing to prove. Thus, suppose |H|>3 and that h<sub>1</sub> and h<sub>2</sub> (both elements of H) are G'-adjacent and not G"-adjacent. This means that there is a path P'[h<sub>1</sub>',h<sub>2</sub>'] on C' in which no element of H'\{h<sub>1</sub>',h<sub>2</sub>'} appears. P"[h<sub>1</sub>",h<sub>2</sub>"] is the corresponding path in (G",U") and this path contains at least one edge which is not on C".

Let  $P_a^{"}[h_1^{"},h_2^{"}]$  and  $P_b^{"}[h_1^{"},h_2^{"}]$  be two disjoint paths, together covering the whole C". On  $P_a^{"}[h_1^{"},h_2^{"}]$  there must be an  $h_a^{"}$  not equal to  $h_1^{"}$  or  $h_2^{"}$ . On  $P_b^{"}[h_1^{"},h_2^{"}]$  there must be an  $h_b^{"}$ , which is also unequal to  $h_1^{"}$  or  $h_2^{"}$ . From the Jordancurves-theorem we know that there is no path from  $h_a^{"}$  to  $h_b^{"}$  not containing a vertex of  $P^{"}[h_1^{"},h_2^{"}]$  in  $(G^{"},U^{"})$ . In  $(G^{'},U^{'})$  however, there is clearly a path from  $h_a^{"}$  to  $h_b^{"}$  which contains no vertex of  $P^{"}[h_1^{"},h_2^{"}]$ . This is a contradiction.

# REFERENCES

[1] C.Berge, "Théorie des graphes et ses applications", Paris, Dunod, 1966.

### II. ROUTING ALGORITHMS

### 1. SIMPLE CONNECTION ALGORITHM ON A GRID

Consider two sets of natural numbers:  $R = \{n \mid n \in \mathbb{N} \mid \land (0 < n \le r)\}$  $K = \{ n \mid n \in \mathbb{N} \mid \land (0 \le n \le k) \}$

We define the set C as being R×K and we call its elements "cells". On this set we define a relation n⊂C×C in the following way:

$$\forall_{c_i \in C} \forall_{c_j \in C} [(c_i, c_j) \in n \leftrightarrow (|r_i - r_j| + |k_i - k_j| = 1]$$

where  $c_i = (r_i, k_i)$  and  $c_j = (r_j, k_j)$ . By  $c_i n$  we mean  $\{c \mid (c_i, c) \in n\}$ . Clearly, n is symmetric, and it is easy to see that

$$V_{c, \in C}$$

[2 $\leq |c_i\eta| \leq 4$ ]

At the initialization of the socalled "connection"-procedure, we suppose that C is partitioned into two subsets A and B. A is called the set of admissible cells, while B consists of these cells which are "prohibited". Further two elements of A are pointed out: one as being the origin c\*, the other as the target c\*\*.

The procedure is a search routine followed by a trace-routine: in the first routine we split A in three sets: P, Q and A\(PUQ); in the second step we select a sequence S of elements of P and Q which are added to B. This sequence is called "the shortest path from c to c to c to c.

The procedure is built in such a way that

- 1. S⊂A

- 2.  $S = (c_1, c_2, ..., c_m) \rightarrow (c_1 = c^* \land c_m = c^{**} \land \forall c_i \in S \quad [(c_i, c_{i+1}) \in \eta])$ 3. For every sequence S' that satisfies 1. and 2., we have  $|S'| \ge |S|$

We must emphasize that the solution need not be unique. In the blocks marked by an asterisk the determination of the new c may give some difficulties. We can meet here two situations:

- 1.  $|\mathbf{P} \cap \mathbf{\bar{c}}_n| = 1$ : the procedure can proceed in a unique way.  $|Q \cap \overline{c}n| = 1$

- 2. |Pnēn| ≥ 2 : the procedure needs a rule to decide which cell will be  $|Q \cap \overline{c} \eta| \geq 2$ the next c.

For the missing rule in the second case one may take the following one: if possible, do not change the coordinate that was changed in the preceding step;

if possible, make the coordinate that must be changed as low as possible.

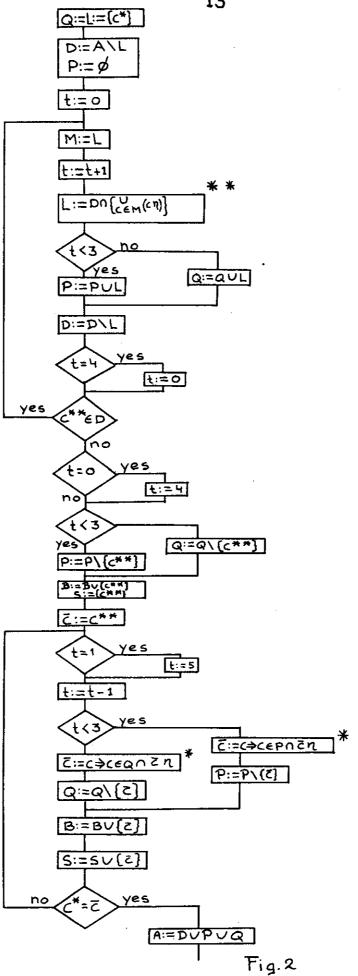

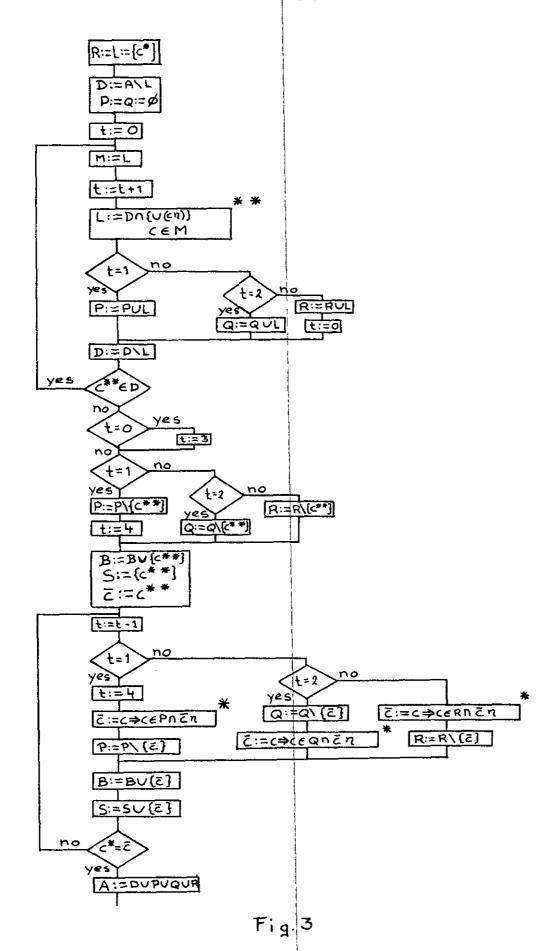

The procedure gets stuck in the block marked by two asterisks when this set is empty: this means that no solution exists. (Fig. 2.)

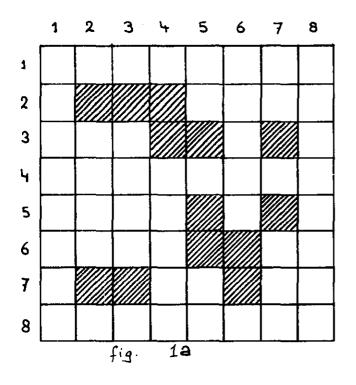

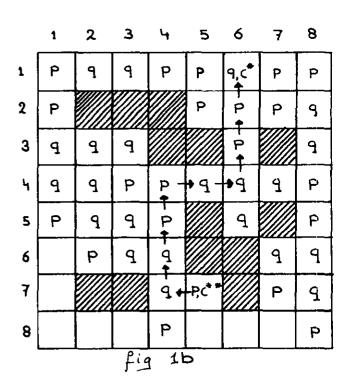

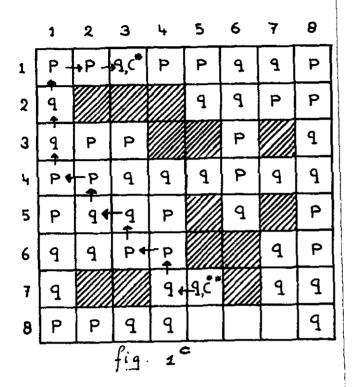

As an application of the described procedure we consider the rectangular grid of fig. 1a. The cells are here the little squares of the grid determined by the coordinates at the top and at the left side. The cells belonging to B are shaded.

Let the origin be (1,6) and the target (7,5).

After the first part of the procedure the partition gives the result as given in fig. 1b. The set P consists of the cells containing the character "p" and the set Q is the set of all cells containing the "q".

During the "trace-routine", the second step, we meet only the situation  $|P \cap \overline{c}n| = 1$  or  $|Q \cap \overline{c}n| = 1$ , and thus, the solution is unique.

However, when we choose (1,3) instead of (1,6) as the origin, a rule like the one given above is necessary to obtain a unique solution. The results are depicted in fig. 1c.

Fig.1: Example of a routing algorithm on a grid.

# 2. SIMPLE CONNECTION ALGORITHM ON A GRAPH

The connection algorithm on a graph has a more general nature and the procedure described in the preceding section, must be modified. The main principle, however, is still the same.

The set C is now equal to the set of vertices G, while the relation  $\eta$  is now to same as the relation  $\Gamma$ . Again, C is partitioned into two sets A and B, and an origin and a target are pointed out.

However, the first step splits A in four sets: P, Q, R and A\(P $\cup$ Q $\cup$ R).

Again, the blocks marked by an asterisk make uniqueness uncertain. One has to add a "decision-rule" to eliminate this flaw, e.g. when the vertices are labeled with different integers one may demand that the vertex with the lowest label of all possible vertices is taken. But when the labels were not assigned in a special way, this will be an arbitrary choice.

Connection procedure for the grid problem

Connection procedure for the graphproblem

# 3. SIMPLE MULTILAYER CONNECTION ALGORITHM

In the preceding section we generalized the algorithm of section 1 by admitting an arbitrary relation n. In this section we want to generalize not on the relation n, but on the number of "layers". Every layer has the same "grid structure". In every layer we have a partition of C into two sets: for layer i f.e.  $A_i$  and  $B_i$ . Again, we have in C an origin and a target. The procedure consists also of a search routine and a trace routine. In the first one C is partitioned into four sets P, Q, R and T and in the second part the sequence S is selected where  $S \subset C \times L$  (L is the set of "layers", |L| = 2).

In the description of the algorithm the following arrays are used to store the sets:

F[1:r, 1:k, 1: $\boldsymbol{L}$ ] is an array which is not changed during the connection procedure. It is only changed after such a procedure to add the cells of S to the proper  $B_i$ 's. During the procedure the array F is as follows:

F[i, j, h] =

$$\chi_{A_h}$$

((i, j)) dwz F[i, j, h] = 1  $\leftrightarrow$  (i, j) $\in A_h$  F[i, j, h] = 0  $\leftrightarrow$  (i, j) $\in B_h$

The array E[1:r, 1:k] keeps track of the partition of C into P, Q, R and T

$$E[i, j] = 0 \leftrightarrow (i, j) \in T$$

$$E[i, j] = 1 \leftrightarrow (i, j) \in P$$

$$E[i, j] = 2 \leftrightarrow (i, j) \in \mathbb{Q}$$

$$E[i, j] = 3 \leftrightarrow (i, j) \in \mathbb{R}$$

At the initialization of the procedure all cells are in T and thus all E[i, j] are zero.

t is an variable, which can take the values 1, 2 and 3.

Further we have two "projection" functions:

$$\pi_1(c) = i \leftrightarrow \pi_{j \in K}[c = (i, j)]$$

$$\pi_2(c) = j \leftrightarrow \pi_{i \in R}[c = (i, j)]$$

The search procedure can be described as follows:

Step 1: D:=

$$\{c^*\}$$

,  $E[\pi_1(c^*), \pi_2(c^*)]$ := 3; t:=3

Step 2:

$$t := t+1 \pmod{3}$$

Step 3:

$$DD := \bigcup_{c \in D} \{c_{\eta}\}$$

Step 4: For every c in the set DD we determine whether  $E[\pi_1(c), \pi_2(c)] = 0$  and whether there is an h such that

$$FL\pi_1(c), \pi_2(c), h] = 1 \land \exists_{c' \in cn} [ f[\pi_1(c'), \pi_2(c'), h] = 1 \land E[\pi_1(c'), \pi_2(c')] \neq 0]$$

If both conditions are satisfied, then  $\mathbb{E}[\pi_1(c), \pi_2(c)] := t$  else  $DD := DD \setminus \{c\}$

Step 5: D: = DD

Step 6: If  $c^{**} \in D$  then the search routine is completed, else go back to step 2.

After the search routine we have some data for the trace routine available, i.e. t, F and E. With these data we can determine the sequence S, but in general this sequence will not be uniquely determined, so that additional decision rules have to be applied.

An example of this procedure is given in fig. 4.

The array E does not supply all the information necessary for the trace routine. Suppose we have reached cell c and  $E[\pi_1(c),\pi_2(c)]=t$ . The next cell c' must be chosen such that

- 1. c' ∈ cη

- 2.  $E[\pi_1(c'), \pi_2(c')] = t-1 \pmod{3}$

- 3.  $\pi_{h \in L}[F[\pi_1(c), \pi_2(c), h] = 1 \land F[\pi_1(c'), \pi_2(c'), h] = 1]$

| 3 | 2   |    | 1 | 2 |

|---|-----|----|---|---|

| 2 | 1   |    | 3 | 1 |

| 1 | * 3 | 1  | 2 | 3 |

|   |     |    |   | 1 |

| 3 | 2   | 3  |   | 2 |

| 1 | 3   | 1  |   | 3 |

|   |     |    |   | 1 |

|   |     | ** |   | 2 |

|   |     |    |   |   |

|   |     |    |   |   |

| 3 | 2   | 3  | 1 |   |

|---|-----|----|---|---|

| 2 | 1   | 2  | 3 |   |

| 1 | * 3 | 1  | 2 |   |

| 2 | 1   | 2  | 3 |   |

| 3 | 2   | 3  | 1 |   |

| 1 | 3   | 1  | 2 |   |

|   |     |    |   |   |

|   |     | ** | 3 | 2 |

|   |     |    | 1 | 3 |

|   |     |    |   | 1 |

|    |   | 1              |   |                | 2              |   |                | 3              |   |                | 4              |   |                | 5              |   |

|----|---|----------------|---|----------------|----------------|---|----------------|----------------|---|----------------|----------------|---|----------------|----------------|---|

|    | F | F <sub>2</sub> | E | F <sub>1</sub> | F <sub>2</sub> | E |

| 1  | 1 | 1              | 3 | 1              | 1              | 2 | 0              | 1              | 3 | 1              | 1              | 1 | 1              | 0              | 2 |

| 2  | 1 | l              | 2 | 1              | 1              | 1 | 0              | 1              | 2 | 1              | 1              | 3 | 1              | 0              | 1 |

| 3  | ŀ | 1              | 1 | 1              | 1              | 0 | 1              | 1              | 1 | 1              | 1              | 2 | 1              | 0              | 3 |

| 4  | 0 | 1              | 2 | 0              | l              | 1 | 0              | 1              | 2 | 0              | 1              | 3 | 1              | 0              | 1 |

| 5  | 1 | 1              | 3 | 1              | 1              | 2 | 1              | 1              | 3 | 0              | i              | 1 | 1              | 0              | 2 |

| 6  | 1 | 1              | 1 | 1              | 1              | 3 | 1              | 1              | 1 | 0              | 1              | 2 | 1              | 0              | 3 |

| 7  | 0 | 0              |   | 0              | 0              |   | 0              | 0              |   | C <sub>2</sub> | 0              |   | 1              | 0              | 1 |

| 8  | 1 | 1              |   | 1              | 0              |   | 1              | 1              | t | 0              | 1              | 3 | 1              | 1              | 2 |

| 9  | 1 | 1              |   | 1              | 0              |   | i              | 1              |   | 0              | 1              | 1 | 0              | 1              | 3 |

| 10 | 1 | Ì              |   | 1              | 0              |   | 1              | 1              |   | ì              | 1              |   | 1              | 1              | 1 |

Fig.4: Example of a multilayer problem.

### 4. GENERALIZATIONS

In the two preceding sections we have generalized the procedure of section 1 in two different ways. In section 2 the n-relation became unrestricted (except for finiteness, of course); in section 3 we introduced a multilayer procedure. Another possibility is to allow for a more complex optimality criterion. The criterion was up to now "the shortest path between the origin and the target", where shortest meant: "passing through a minimum number of cells". One could solve the problem also by assigning "cell masses" instead of partitioning into sets P, Q, (R) and D. The "cell mass" of c is in such a case the smallest number of cells one has to pass through before reaching c started in c\*. By allowing a more "general cell mass" one may think to have improved the procedure greatly. One can take for example as a "cell mass" a weighed sum of penalties:

$$f(c) = \sum_{i=1}^{n} \alpha_i f_i(c)$$

f<sub>i</sub>(c) are the penalty functions, f.e. the number of cells one has to pass through to reach c from c\*, the number of crossings one has met, etc..

Two complications are then introduced. Firstly, our strategy has to be changed (one must assign "cell masses" only to those cells that obtain the lowest possible mass, which means that one has to remember all neighbour cells which didn't get a mass) and secondly, the penalty function has to satisfy special conditions (the minimum corner problem is not solvable by this algorithm). We will give the description of the algorithm, and then these difficulties will be apparent.

### The model

$$S = S^{\dagger} \setminus \{b\}$$

$$\eta \qquad \eta \in C \times C \wedge \forall_{c \in C} \forall_{c' \in C} [(c,c) \not\in \eta \wedge ((c,c') \in \eta \leftrightarrow (c',c) \in \eta)]$$

n is called the neighbour relation

$$\sigma \qquad \sigma \in \mathbb{C} \times \mathbb{S}^{1} \wedge \mathbb{Y}_{\mathbf{c} \in \mathbb{C}} \exists \mathbf{s} \in \mathbb{S}^{1} [(\mathbf{c}, \mathbf{s}) \in \sigma]$$

$\sigma$  is called the labeling relation

$$\begin{array}{ll} \mu & \mu \subset R_{+} \times S \times R_{+} \\ & \forall (n,s) \in R_{+} \times S & \exists !_{m \in R_{+}} [(n,s,m) \in \mu] \\ & \forall_{n \in R_{+}} \forall_{s \in S} \forall_{m \in R_{+}} [(n,s,m) \in \mu \rightarrow n \leq m] \\ & \forall_{n \in R_{+}} \forall_{n' \in R_{+}} \forall_{s \in S} [n \leq n' \rightarrow (n,s) \mu \leq (n',s) \mu] \end{array}$$

u is called the weighing relation

### Auxiliary entities

A A

$$\subseteq$$

C  $\land$   $\forall$

$c \in$ C  $[c \in A \leftrightarrow (c,b) \notin \sigma]$

A is the set of admissable cells

$$\mathbf{P}^{\star} \qquad \mathbf{P}^{\star} = \{(\mathbf{c}_{1}, \mathbf{c}_{2}, \dots, \mathbf{c}_{n}) \mid (\mathbf{c}_{1}, \mathbf{c}_{2}, \dots, \mathbf{c}_{n}) \in \bigcup_{i=1}^{n} \mathbf{A}^{i} \land \\ \wedge \forall_{1 \leq i < n} [(\mathbf{c}_{i}, \mathbf{c}_{i+1}) \in \eta \land \forall_{i < j \leq n} [i \neq j \leftrightarrow \mathbf{c}_{i} \neq \mathbf{c}_{j}]]\}$$

P\* is the set of paths

$$\begin{split} \delta & \quad \delta \in \textbf{P}^{\bigstar} \times \textbf{R}_{+} \\ \forall & \quad \forall_{\textbf{n} \in \textbf{R}_{+}} \textbf{[((c),n)} \in \delta \rightarrow \textbf{n} = \textbf{0}]} \\ \forall & \quad (\textbf{c}_{1},\textbf{c}_{2},\ldots,\textbf{c}_{n}) \in \textbf{P}^{\bigstar} \textbf{[((c_{1},c_{2},\ldots,c_{n}),\textbf{m})} \in \delta \leftrightarrow (\textbf{(c}_{1},c_{2},\ldots,c_{n-1})\delta,\textbf{c}_{n}\sigma,\textbf{m}) \in \mu} \textbf{]} \\ \delta & \text{is called the cellmass relation} \end{split}$$

$$P_{c}^{c'}$$

$P_{c}^{c'} = \{(c_{1}, c_{2}, \dots, c_{n}) | (c_{1}, c_{2}, \dots, c_{n}) \in P^{*} \land c_{1} = c \land c_{n} = c'\}$

$$\tau \qquad \tau \subset A \times P^* \times P^*$$

$$(p \in P^* \wedge p = (c_1, c_2, \dots, c_n) \wedge c \not\in p \wedge c \in c_1 \cap p) \rightarrow (c, p) \tau = (c, c_1, c_2, \dots, c_n)$$

# The problem

Find a path P such that:

$$p \in P_{c}^{c**} \wedge \forall p' \in P_{c}^{c**} [((p, m_{o}) \in \delta \wedge (p', m) \in \delta) \rightarrow m_{o} \leq m]$$

# The algorithm

1. L:={

$$c^*$$

},L':=L'':=I:= $\emptyset$ ,f( $c^*$ ):= $\mathcal{I}(c^*)$ :=0, $\forall c \in \mathbb{C} \setminus \{c^*\} \cap \mathbb{I}(c):=\emptyset$ ], $\mathcal{I}:=0$

3.

$$\forall_{c \in L} [\forall_{c' \in c \eta \cap A} [f(c') = \infty \rightarrow (c' : \in L' \land (f(c), c' \sigma) \mu : \in I)]]$$

4.

$$m_0: \rightarrow (m_0 \in I \land \exists m \in I [m < m_0])$$

5.

$$\forall_{c \in L}, [\exists_{c' \in c \cap \cap L} [(f(c'), c\sigma, m_o)] \in \mu] \rightarrow (f(c) := m_o \land c: L'' \land l(c) := l)]$$

6. L:=

$$(L \cup L'') \setminus \{c \mid c \in A \land \forall c \in G \mid f(c') \neq \infty \lor c' \sigma = b\}$$

7. L= $\emptyset \rightarrow P_c^{\star \star} = \emptyset$  (no solution)

8.  $f(c^{\star \star}) = \infty \rightarrow r.2$

7.

$$L=\emptyset \rightarrow P_c^{c*} = \emptyset$$

(no solution)

8.

$$f(c^{**})=\infty \rightarrow r.2$$

9.

$$p := (c^{**}), c^{*} := c^{**}$$

10.

$$\bar{c}: \rightarrow ((\bar{c}, \bar{c}) \in \eta \land \forall_{c \in c\eta} [l(c) \ge l(\bar{c})])$$

11.

$$p := (\bar{c}, p)_{\tau}$$

12.

$$\overset{\circ}{c} := \overset{-}{c}$$

### REFERENCES

- [1] C.Y.Lee, "An Algorithm for Path Connections and Its Applications", IRE Transactions on Electronic Computers, EC-10, pp.346-365, September 1961.

- [2] S.B.Akers, Jr, "a Modification of Lee's Path Connection Algorithm", IEEE Transactions on Electronic Computers, EC-16, pp.97-98, February 1967.

- [3] J.M. Geyer, "Connection Routing Algorithm for Printed Circuit Boards", IEEE Transactions on Circuit Theory, Vol CT-18, no. 1, pp. 95-100, January 1971.

### III. THE MATHEMATICAL FORMULATION OF THE WIRING PROBLEM

### 1. INTRODUCTION

The wiring problem which occurs in the design of printed boards and integrated circuits, arises from the restriction of the number of wiring layers. In many cases this number will be one. The problem is usually translated into a graph-theoretical formulation [1, 2, 3] in such a way that a certain graph has to be tested for planarity. When the result of such a test is negative, technical modifications should be applied in order to obtain a planar graph.

Besides the one layer constraint there are other requirements. They are listed below.

C<sub>1</sub>: The terminals of the circuit are to be placed on the periphery of the chip or the board.

The connection of the printed board with the other parts of the system is simplified by satisfying this requirement. In the case of circuit integration the same applies for the bondation of the circuit to its package, but here we have the additional advantage of keeping the bonding pads out of the region in which the elements are placed (thermal effects).

C<sub>2</sub>: The terminals are to be positioned on the periphery in a previously specified sequence.

This constraint is dictated by standardization rules and the desire to avoid special precautions for isolation.

With  $C_1$  and  $C_2$  a practical layout algorithm for integrated circuits is possible. The formulation for printed boards, however, is not complete. It should be extended by the following three constraints  $(C_3, C_4, C_5)$ .

C<sub>3</sub>: The contacts of a certain component must appear in a given sequence.

As to its treatment this constraint is equivalent to a combination of  $C_1$  and  $C_2$ . Components with more than three pins in a fixed order make the implementation of  $C_3$  necessary. However, in order to match the pins of the components to the contacts on the board, the sequence of the contacts has to have a specific orientation, namely clockwise or counterclockwise. Therefore we introduce the following constraint.

$C_4$ : The orientation of the contacts on the board must be the same for all the components with more than two pins in a fixed order.

The last requirement makes an a priori choice of the side on which the components are to be placed, possible:

$C_5$ : The orientation of the components described in  $C_4$  is defined with respect to the orientation of the terminal sequence at the periphery.

In order to adapt our notions to those in literature we will start section 2 with some definitions and statements whose proofs are either trivial or to be found in books on graph theory and analytic topology [4, 5, 6]. Section 2 ends with the statement and the proofs of the five crucial theorems necessary for the justification of the mathematical formulation of the problem with the above-mentioned five constraints. This formulation is described in section 3, and in section 4 an example is presented for printed board layout. The last section contains some concluding remarks.

## 2. THE GRAPHTHEORETICAL BASE

A graph (G, U) consists of a finite set of vertices G and a finite family of edges U such that  $G \cap U = \phi$ . G and U define an incidence relation which associates with each edge [x, y] two vertices, x and y, called its ends. Parallel edges are associated with the same pair of vertices. A loop is an edge of which the associated vertices are not distinct. The number of edges incident with vertex x is called the degree  $\gamma(x)$  of x. We call a graph simple, when there are no vertices of degree less than 3, no parallel edges and no loops. With every graph we associate a simple graph by applying the following rules as many times as possible:

- 1. Delete a loop

- 2. Delete a vertex of degree 1 with its incident edge

- 3. Replace two parallel edges by one edge in such a way that every pair of vertices which was associated with an edge remains so

- 4. Replace a vertex of degree 2 and the two edges incident with it by one edge in such a way that the degree of the other vertices is not changed.

A path  $P[x_1, y_k]$  is a sequence  $[x_1, y_1]$ ,  $[x_2, y_2]$ , ...  $[x_k, y_k]$  of edges in which we have

$$\forall_{1 \le i < k} \ \forall_{1 < j \le k} \ [(x_i = x_j \leftrightarrow i = j)] \land (y_i = x_{i+1}) \land (x_j \ne y_k)]$$

A circuit is a path with  $x_1 = y_k$ . A graph is called connected, when there is a path between every pair of vertices. The maximal connected subgraphs of a graph are called components. The intersection of two graphs consists of all the edges they have in common and their associated vertices. The union of two graphs is the graph consisting of all the edges and vertices of the original graphs. Two graphs are said to meet each other, if they have an edge in common. Otherwise they are called disjoint. The complement of a subgraph (H, V) in the graph (G, U) is the graph consisting of all the edges in U\V and all their associated vertices, denoted by G7H. The set  $H\cap (G7H)$  is called the attachment set of (H, V). The number of elements in this set is called the attachment number.

Let (C, W) be a circuit of (G, U). We call a subgraph (H, V) of  $(GTC, U \setminus W)$  C-bounded, when all its vertices of attachment are vertices of C. It is clear that  $(GTC, U \setminus W)$ , the complement of any C-bounded subgraph in  $(GTC, U \setminus W)$ , and the intersection of any two C-bounded subgraphs, are all C-bounded. A C-bounded subgraph of  $(GTC, U \setminus W)$  is called a bridge of (C, W) if none of the subgraphs of this graph is C-bounded. In other words a bridge of (C, W) is a minimal C-bounded subgraph of  $(GTC, U \setminus W)$ . When  $[x, y] \in U \setminus W$ , then the intersection of all the C-bounded subgraphs of  $(GTC, U \setminus W)$  containing [x, y], is a bridge.  $(GTC, U \setminus W)$  is thus the union of all the bridges of (C, W). Clearly, a bridge is connected, because it is minimal [T].

A graph is called n-separable, where n is a non-negative integer, when it can be partitioned into two disjoint subgraphs, each having at least one vertex which is not a vertex of the other, such that the attachment number is not more than n. A graph is properly n-separable, when its simple graph is n-separable. The graph is n-connected when it is not properly m-separable for any m<n. An articulation set is a set of n vertices being the vertices of attachment of a subgraph of an n-separable and n-connected graph. In a 2-connected graph a circuit can be found such that it contains an arbitrary edge (or vertex) [7, 8, 9].

A graph is called planar, when it has a topological representation in a plane (or equivalently on a sphere). This definition is the link between graph theory and analytic topology. For the details we refer to the literature [4, 5, 6].

Here we confine ourselves to some facts from these areas.

A graph is planar if and only if its simple graph is planar. Further, every subgraph of a planar graph is planar. The most famous criterion for the planarity of a graph is due to Kuratowski [10]: A graph is planar if and only if it has no subgraphs whose simple graphs are isomorphic to  $(\{x_i \mid 1 \le i \le 5\})$ ,  $\{[x_i, x_j], 1 \le i \le 5 \land i < j \le 5\}$  or  $(\{x_i \mid 1 \le i \le 6\}, \{[x_i, x_j], 1 \le i \le 5 \land i < j \le 5\})$ .

A planar 2-connected graph (G, U) is called H-accessible where H c G, when there exists a circuit (C, W) in (G, U) such that H C C and there is a planar representation (G', U') of (G, U) in which every point of C'∪W' can be connected with a point xéG'∪U' by disjoint Jordan curves without intersecting G'∪U'. (G', U') is called an H-periphere representation of (G, U). It is clear that one of the regions in which C'UW' divides the plane, contains no edges of U'. We call this region a face in this particular representation. The circuit  $C' \cup W'$  forms the boundary of this face. Two elements  $h_1$  and  $h_2$  of H are called G'-adjacent in H when they can be connected by a Jordan curve in this face without intersecting other Jordan curves in this face connecting two elements of H. The notation for this relation will be:  $h_1 \circ h_2$ . Every planar representation automatically defines an adjacency relation on H, when it is H-periphere. In a planar representation every vertex and every edge is on the boundary of some face. The whole graph is contained in the interior region of one of the boundaries. This boundary is called the outer boundary. For every face there can be found a planar representation on a plane such that its boundary is the outer boundary. Suppose namely that the graph is mapped onto the surface of a sphere. Call an arbitrary point of the face in question the north pole P. Stereographic projection from P on the tangent plane through the south pole will project the north pole on the infinite of the plane and the projection of the face concerned will form the outer region of the plane.

Suppose we have a simple closed Jordan curve C (dividing the plane into two regions; Jordan curve theorem) on which two pairs of distinct points  $C_1$ ,  $C_2$  and  $C_3$ ,  $C_4$  are selected ( $C_1 \neq C_2$  and  $C_3 \neq C_4$ ). These pairs are said to alternate when there is no section of C connecting  $C_1$  with  $C_2$  without containing  $C_3$  or  $C_4$ . It is possible to connect  $C_1$  with  $C_2$  and  $C_3$  with  $C_4$  by disjoint Jordan curves in one region if and only if ( $C_1$ ,  $C_2$ ) and  $C_3$ ,  $C_4$ )do not alternate [6]. An equivalent definition of G'-adjacent in H is now: two vertices  $h_1$  and  $h_2$  of H are G'-adjacent in H if they do not alternate with any other pair of vertices of H on C' $\cup$ W'.

From now on in this section (G, U) is a 2-connected graph. In the case of 1-connectedness the according statements are easy to derive from the results below. Only theorem 3 undergoes a slight modification.

Theorem 1:  $H_i \subset G$ ,  $x_i \notin G' \cup U'$   $(G, U) \text{ has a planar representation } (G', U') \text{ that is } H_i\text{-periphere}$   $\text{for } 1 \leq i \leq m \text{ if and only if the graph}$   $(K, V) = (G \cup (\bigcup_{i=1}^m \{x_i\}), U \cup (\bigcup_{i=1}^m \{[x_i, h^i] | h^i \in H_i\}))$   $\text{is planar for some } \{x_1, x_2, \dots, x_m\}$

Proof: Suppose (K, V) is planar, then it has a planar representation (K', V') We consider a face with  $x_i$  on its boundary. Since  $x_i$  is only connected with elements of  $H_i$ ,  $h_1^i$  and  $h_2^i$  must also be on this boundary. Thus the boundary consists of  $[h_2^i, x_i]$ ,  $[x_i, h_1^i]$  and  $P_1[h_1^i, h_2^i]$ . None of the pairs  $(x_i, y)$  where  $y \in P_1[h_1^i, h_2^i]$ , are mutually alternating, so every point of  $P_1[h_1^i, h_2^i]$  can be connected with  $x_i$  by a Jordan curve in the face without meeting one of the other connecting curves. The same applies for the points of  $P_2[h_2^i, h_3^i]$ ,  $P_3[h_3^i, h_4^i]$ , etc. The curves connecting the points of  $P_1[h_1^i, h_1^i]$  with  $x_i$  are in another face as the curves belonging to  $P_k[h_k^i, h_{k+1}^i]$  ( $k \neq j$ ). The Jordan curves  $[h_1^i, x_i]$  are disjoint from each other because (K', V') is a planar representation, and disjoint from the constructed curves, because they are on the boundary of the faces. So we conclude that every point of the circuit  $P_1[h_1^i, h_2^i] \cup P_2[h_2^i, h_3^i] \cup \ldots \cup P_k[h_k^i, h_1^i] \cup H$ . can be connected with the point  $x_i$  by disjoint Jordan curves. This means that  $(K' \setminus (\bigcup_{i=1}^m \{x_i\}), V' \setminus (\bigcup_{i=1}^m \{[x_i, h^i] \setminus h^i] \cap H^i \in H^i\}))$  is a  $H_1$ -periphere representation of (G, U) for all  $1 \leq i \leq m$ .

Conversely, when (G, U) has a planar representation which is  $H_1$ -periphere

Conversely, when (G, U) has a planar representation which is  $H_i$ -periphere for  $1 \le i \le m$ , then every  $h^i \in H_i$  can be connected to an  $x_i$  with mutually disjoint Jordan curves, and without intersecting any edge. We only have to consider the points  $x_i$  as new vertices, and the connecting Jordan curves as new edges, and we have a planar representation of  $(G \cup (\bigcup_{i=1}^m \{x_i\}), U \cup (\bigcup_{i=1}^m \{[x_i, h^i] | h^i \in H_i\}))$

Theorem 2:  $H \subseteq G$ ,  $x \not\in G$   $H = \{h_1, h_2, \dots, h_k\}$

(G, U) has an H-periphere representation (G', U') with the property

$$\forall_{1 \leq i < k} [h_i \land h_{i+1}]$$

if and only if

$(K, V) = (G \cup \{x\}, U \cup \{[x,h] \mid h \in H\} \cup \{[h_1,h_k]\} \cup \{[h_i,h_{i+1}] \mid 1 \le i < k\})$  is planar.

Proof: For  $|H| \le 3$  the theorem reduces to theorem 1. So we suppose  $|H| \ge 4$ . For the first part of the proof we start from the planar H-periphere representation (G', U') with the proposed properties. We can connect  $h_i$  with  $h_{i+1}$  and  $h_i$  with  $h_k$  by disjoint Jordan curves in the face with H on its boundary. The new edges form together a circuit containing H completely and being the boundary of a new face. The new represented graph is thus H-periphere. From theorem 1 we know that the graph (K, V) is planar.

Now we suppose we have anH-periphere representation (G', U') but with a wrong adjacency relation on H. This means that there is a subset  $\{h_a, h_b, h_c, h_d\}$  of H with a<b<c<d and  $h_a h_c$  and  $h_b h_d$  in  $\{h_a, h_b, h_c, h_d\}$ . Further, we suppose that (K, V) is planar, and thus we have a planar representation of

$(M, W) = (G, U \cup \{[h_i, h_k]\} \cup \{[h_i, h_{i+1}] | 1 \le i \le k\})$

since this is a subgraph of (K', V'). From the first part of this proof we also know that this representation is still H-periphere with the same adjacency relation.

From theorem 1 and the first part of this proof we conclude that the graph  $(M \cup \{x\}, W \cup \{[h_a, h_c], [h_b, h_d], [h_a, x], [h_b, x], [h_c, x], [h_d, x]\})$  must also be planar.

However this graph contains the subgraph

$$(\mathtt{H} \cup \{\mathtt{x}\}, \ \{[\mathtt{h}_{a},\mathtt{x}], \ [\mathtt{h}_{b},\mathtt{x}], \ [\mathtt{h}_{c},\mathtt{x}], \ [\mathtt{h}_{d},\mathtt{x}], \ [\mathtt{h}_{a},\mathtt{h}_{c}], \ [\mathtt{h}_{b},\mathtt{h}_{d}], \ [\mathtt{h}_{1},\mathtt{h}_{k}]\} \cup \\ \ \, \cup \{[\mathtt{h}_{i},\mathtt{h}_{i+1}] \mid 1 \leq i < k\})$$

whose simple graph is isomorphic to one of the graphs in the theorem of Kuratowski. So (K, V) cannot be planar, which implies a contradiction.

Theorem 3: When a graph (G, U) is H-accessible, there is only one adjacency relation on H possible.

Proof: Again we suppose that |H|≥4.

Since (G, U) is H-accessible it has an H-periphere representation (G', U'). Suppose it has another H-periphere representation (G", U") such that there is a pair  $h_1$ ,  $h_2$  in H, which is G'-adjacent and not G"-adjacent. This means there is a path  $P'[h_1,h_2]$  in (C', W') in which there is no element of  $H\setminus\{h_1,h_2\}$ .  $P''[h_1,h_2]$  is the corresponding path in (G", U"), and this path contains at least one edge not in (C", W"). Let  $P''[h_1,h_2]$  and  $P''[h_1,h_2]$  be two disjoint paths, together covering the whole (C", W"). On  $P''[h_1,h_2]$  there must be an  $h_a\in H$  and not equal to  $h_1$  or  $h_2$ , and on  $P''[h_1,h_2]$  there must be an  $h_b\in H$ , not equal to  $h_1$  or  $h_2$ . In (G', U')we can easily find a path  $P'[h_a,h_b]$  not containing a vertex of  $P'[h_1,h_2]$  (for example in  $(C'\cup W)\setminus P'[h_1,h_2]$ ). However, in (G", U") there is not such a path, since  $h_a,h_b$  and  $h_1,h_2$  are alternating on  $C''\cup W''$ .

Theorem 4: A planar graph (G, U) is properly 2-separable if and only if there is at least one face boundary in an arbitrary planar representation of its simple graph which has more than one bridge.

Proof: There is a planar representation of the simple graph of (G, U). Suppose one of the face boundaries has more than one bridge. Bridges are connected. thus attachment vertices of a bridge B cannot alternate with vertices of attachment of another bridge B'. So all the vertices of attachment of B are on a path P[c,,c,] of the boundary and none of the attachment vertices of B' is. Then the graph is separated by c, and c2. Conversely let the planar graph (G, U) be properly 2-separable with articulation set {c1,c2}. Then separate the graph at c1 and c2. We have now two components:  $(H_1^{\dagger}, U_1^{\dagger})$  and  $(H_2^{\dagger}, U_2^{\dagger})$ . Since  $c_1$  and  $c_2$  are connected in  $(H_2', U_2')$ ,  $(H_1', U_1')$  must be  $\{c_1, c_2\}$ -periphere (apply theorem 1 after choosing an arbitrary point on a path  $P_2[c_1,c_2]$  in  $(H_2',U_2')$ , so we can connect c, and c, by a Jordan curve in the new face. The same is possible in  $(H_2, U_2)$ . After identifying  $[c_1, c_2]$  in both components we have a Jordan curve between c, and c, in (G', U') and from theorem I we know that c, and c, must be on the same boundary (C', W'). (This fact is obvious from a picture, but as many theorems of analytical topology hard to prove).

The theorem is usually referred to as the Jordan-Schönflies theorem [6]) Since the graph (G, U) was properly 2-separable, there must be a vertex not in C in  $H_1$  as well in  $H_2$ . This means that  $(H_1^{7C}, U_1^{W})$  and  $(H_2^{7C}, U_2^{W})$  contain each at least one bridge of (C, W), since they are not empty.

Theorem 5: A graph (G, U) has a unique planar representation (i.e. the boundaries of the faces consist of the same edges for every planar representation of (G, U)) if and only if (G, U) is planar and not properly 2-separable ([11, 12]).

Proof: The necessity is easy to see., for one can, without spoiling the planarity, obtain the mirror -image of every subgraph with attachment number two, by twisting it around its attachment vertices.

The sufficiency follows from theorem 4:

Suppose we have two planar representations(G', U') and (G", U") of (G, U).

(C', W') is the boundary of a face in (G', U') and (C", W"), the corresponding circuit in (G", U"), is not the boundary of a face. In (G", U"), (C", W") must contain inner and outer bridges, so at least two bridges. Thus the corresponding circuit in (G', U'), (C', W') must also have at least two bridges. Since (C', W') was the boundary of a face. The graph (G, U) must be properly 2-separable.

# 3. THE MATHEMATICAL FORMULATION

In this section we want to construct a graph from a given network and some additional design data (constraints) such that it is suitable for a number of tests which are necessary and sufficient to yield  $C_1$  to  $C_5$ , and a practical implementation on a computer is possible. In the case of integrated circuits where  $C_4$  and  $C_5$  have lost their relevance a planarity test proves to be efficient. However, with printed board layout we have chosen for a combination of two tests, a planarity test followed by a connectivity test. Of course it will be advantageous that the output of the first test is adapted to the other. We will come back to these subjects in section 5.

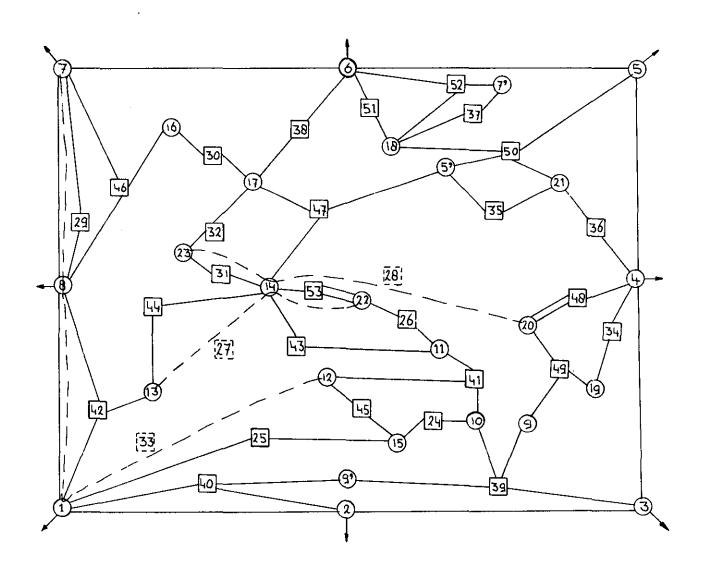

The starting point is the schematic diagram of the network consisting of components and conductive interconnections. In the set of components we distinguish between components that can be crossed by wires and those that cannot be crossed. Resistors on a printed board are usually big enough to allowfor one or more crossings. In IC-technology a diffusion resistor of more than 1 k $\Omega$  can also be crossed without difficulty. These components belong to the first set. A transistor is an example of the second kind of components. Its contacts are too close to each other to permit a crossing (In IC-technology the distance between the contacts is sometimes big enough, but here we want to avoid crossings too, since parasitic capacitors are introduced then). With every component of the second kind we associate a vertex in the graph to be constructed. We refer to such a vertex as a c-vertex. The conductive interconnections in the diagram form a set of "trees". These trees can never be crossed without special measures ("jumpers" for printed boards, "cross-under resistors" for IC's). With every conductive tree we associate a vertex, called a t-vertex. Whenever a component belonging to a c-vertex c of the graph has one of its contacts on a conductive tree associated with t-vertex t we connect c with t by an edge [c,t]. Note that the graph so constructed is bipartite. This means that the set of vertices can be partitioned into two subsets, such that every edge of the graph connects a vertex of one subset with a vertex of the other.

Remark: Some components with a special shape (f.e. IC with a "dual in line"-package) should be implemented in a special way.

The graph generated by the described procedure is called the potential graph. We assert that, when the potential graph is planar, then there exists a planar wiring and a non-overlapping component placement. It is easy to get a layout with these properties by "growing" the covertices until they have reached the size of their components. The wiring between the components is (for example) the rest of the graph. Of course this is not a practical layout. In one of the subsequent stages of the program one has to minimize the chip area or to place everything on a board (mostly with standardized dimensions). These procedures are not the subject of this paper.

After the construction of the potential graph we have to implement C<sub>1</sub> to C<sub>5</sub>. The treatment of the first constraint is immediately clear from theorem 1. There are several conductive trees which contain terminals. The set of vertices H is the set of their t-vertices. What in fact we want to know now is whether the graph is H-accessible. We therefore connect every vertex in H with a new vertex x, (The graph is still bipartite; we consider the vertex x as a c-vertex). Planarity of the graph thus obtained is necessary and sufficient for the H-accessibility.

The introduction of  $C_2$  seems to be obvious from theorem 2. Acting in the sense of this theorem we connect every pair of "adjacent" terminals by a new "adjacency edge" (bipartiteness is preserved by laying a vertex on every new edge; these vertices can be considered as c-vertices). The potential graph is now extended by a so-called wheel (the "terminal wheel" in this particular case): the adjacency edges form together the "rim" of the wheel, x is called the "hub" and the edges incident with x are called the "spokes". Planarity of the obtained graph is necessary and sufficient for a planar potential graph constrained by  $C_1$  and  $C_2$ . However, theorem 3 makes the usefulness of the implementation of  $C_2$  questionable. (We will explain this in section 5). Nevertheless we maintain the addition of the adjacency edges, because most planarity tests yield directives as to the set of edges whose deletion planarizes the graph and then the adjacency edges may be useful. Besides the implementation of  $C_4$  becomes easier as we will see later in this section.

${\rm C}_3$  is treated in an analogous manner. Here the hub is the c-vertex associated with the respective component. The set H is formed by the t-vertices directly connected with the hub. We only have to add new edges between adjacent contacts, and again a complete wheel is introduced. We can make the same remarks on the introduction of  ${\rm C}_3$  as we did with  ${\rm C}_2$ . The graph so obtained is called the extended potential graph.

The question now is, whether this graph is planar or not. In case of planarity a layout constrained by  $\mathbf{C}_1$ ,  $\mathbf{C}_2$  and (eventually)  $\mathbf{C}_3$  exists. Otherwise the graph should be modified by using possibilities given by the technology until planarity is obtained. The problem which is left now can be formulated as: "Does a planar representation of the (eventually modified) graph exist in which  $C_{\underline{\lambda}}$  and  $C_{\underline{5}}$  are satisfied?". This is very unlikely to occur, and thus in most cases modifications should be carried out. It is immediately clear that methods searching all planar representations(f.e. by applying the theory described in [12], [16] or [17]) are not recommendable. Firstly because of the computational effort involved, and secondly because we don't obtain any indication for executing the necessary modifications. The next thought can be to invalidate these objections by using a "constructive" planarity test. By constructive we mean that the starting point is a planar subgraph which is extended until the graph at hand is obtained. The extension-steps consist of transformations, which do not spoil the planarity and take the orientations into account. Nevertheless we prefer a connectivity test (subsequent to the planarity test) on a planar representation of the (eventually modified) extended potential graph which accounts for  $C_L$  and  $C_5$ . The reason for this choice will be given in section 5. The connectivity test implies a partitioning of the graph into maximal not properly 2-separable subgraphs. Before executing the test we add the three adjacency edges of each component with three pins whose orientation has to be considered. They may not

have been inserted into the extended potential graph, since they are not essential for the sequence of the contacts (it always is the same in the case of three contacts) and they may complicate the modification steps.

Yet, in the connectivity test, these edges are important, because the graph has to be subjected to a simplification procedure in which a c-vertex associated with an orientated three-pin-component may disappear.

Furthermore, wheels are clearly not properly 2-separable. This means that its hub cannot be in an articulation set with less than three elements. Thus wheels will not be split apart by the connectivity test procedure.

According to theorem 5 the subgraphs generated by the test have unique planar representations. So the orientations of the components in such a subgraph are fixed with respect to each other. Consequently, a necessary condition for satisfying C<sub>4</sub> is that the orientations of the components in such a subgraph are all clockwise or all counterclockwise. This is also sufficient, because some subgraph with all its wheels oriented in the same way may be adjusted with respect to the orientation in another subgraph by twisting it around its articulation points.

The orientation of the "terminal wheel" referred to in constraint  $C_5$ , can easily be incorporated into the procedure to check  $C_4$ .

#### 4. EXAMPLE

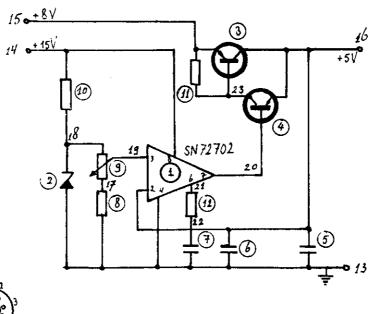

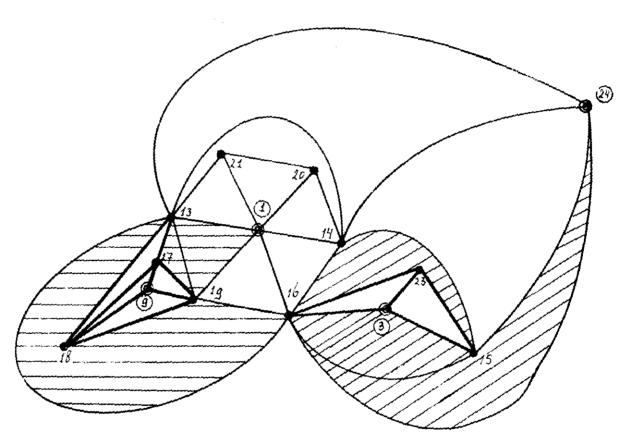

In this section the described method is demonstrated with a printed board layout design.

The circuit diagram is given in figure 1 (voltage stabilizer). The components are numbered (1) up to (12) inclusively, and the conductive trees 13 up to 23 inclusively. The constraints are specified as follows:

- C<sub>1</sub>: The terminals 13, 14, 15 and 16 are to be placed on the periphery of the board.

- C<sub>2</sub>: The following sequential position of the terminals around the periphery is required: 13, 14, 15, 16.

- The contacts of component (1) (the operational amplifier) must appear in the following sequence: 16, 19, 13, 21, 20, 14.

- C<sub>4</sub>: The orientation of the components (1), (3), (4) and (9) has to be the same: when walking along the rim of the respective wheels in clockwise direction the hub has to be in the region at the right. The t-vertices on the rims

then have to occur in the following sequence:

- a) for the operational amplifier ((1)):

- 16, 19, 13, 21, 20, 14

- b) for the transistors ((3) respectively (4))

- (3): 15, 23, 16 (emitter-base-collector)

- (4): 16, 20, 23 (idem)

- c) for the potentiometer ((9)):

- 17, 18, 19

- C<sub>5</sub>: When walking along the rim of the "terminal wheel" in the sequence 13, 16, 15, 14, the hub has to be at the right.

The potential graph can easily be constructed by connecting the c-vertices ((1)-(12)) with the t-vertices (13-23) according to the schematic diagram of figure 1. For the moment we consider all the components to be non-crossable. If necessary all the components may be crossed except the transistors, operational amplifier, and the potentiometer. (The op-amp has a TO-5-TYPE package; see bottomview).

We take care of constraint  $C_1$  and  $C_2$  by adding a new vertex ((24); c-vertex) and adding the edges [24, 13], [24, 14], [24, 15], [24, 16] and the edges [13, 14], [14, 15], [15, 16], [16, 13].

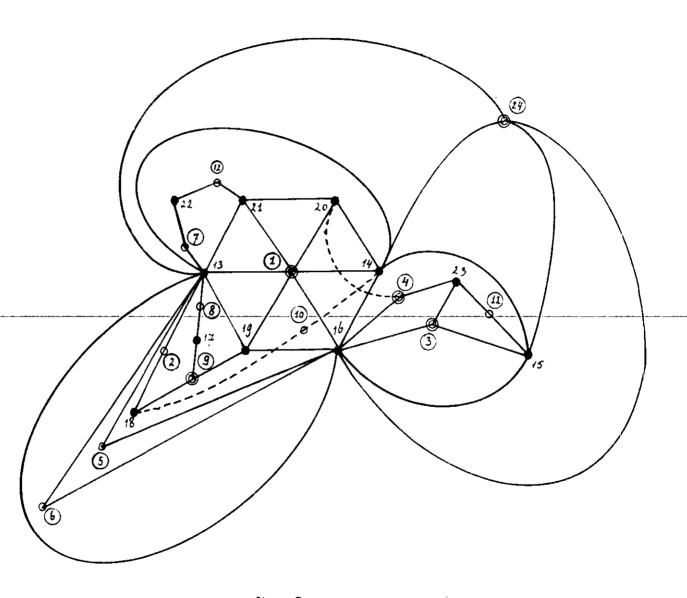

The treatment of C<sub>3</sub> requires the addition of the edges [16, 19], [19, 13], [13, 21], [21, 20], [20, 14], [14, 16]. The graph obtained now, is the extended potential graph and has to be tested on planarity. The test discloses the extended potential graph to be non-planar. Planarity can be obtained by deleting two edges. A possible choice can be:

- a) edge [4, 20] (the base of transistor (4)); Technologically this connection can be established as a "jumper".

- b) One of the edges [14, 10] and [10, 18]; In this case, the modification is simple, since vertex (10) is associated with a component (resistor) that may be crossed.

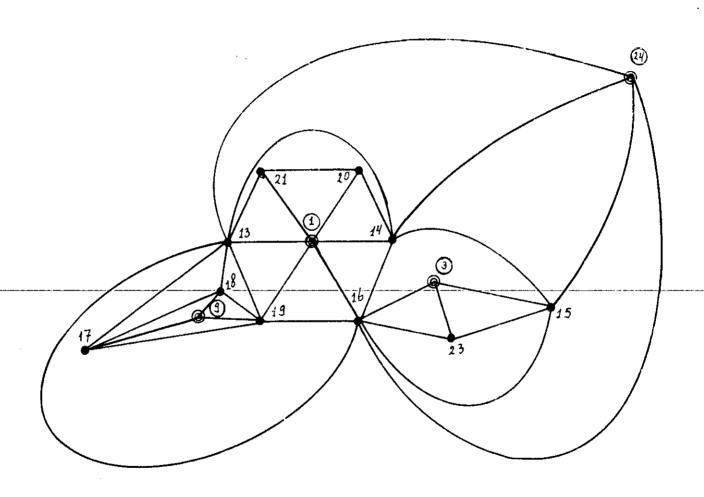

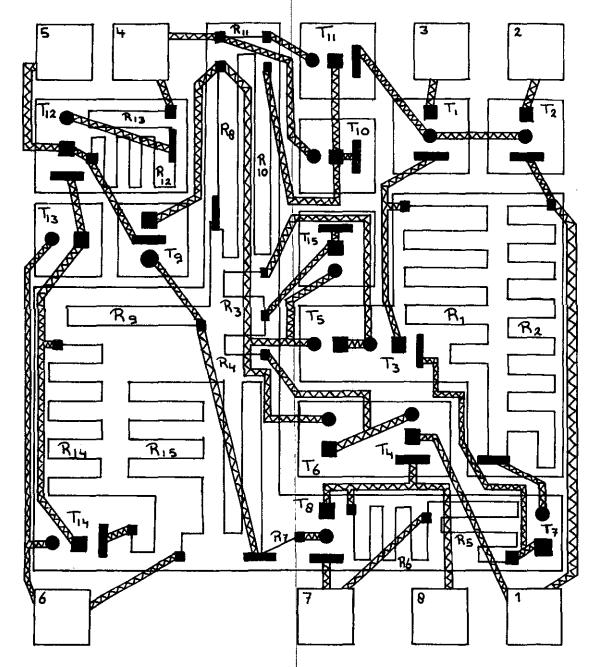

Since the planar representation in figure 2 does not satisfy the constraints  $\mathrm{C}_L$  and  $\mathrm{C}_5$ , the connectivity test has to be executed.

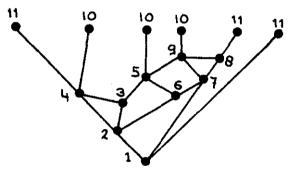

The starting point for this test is the extended potential graph (figure 2, without dotted lines) with addition of all the "adjacency edges" of each 3-pin-component whose orientation has to be considered. The first thing to do is simplifying this graph. The result is depicted in figure 3.

Theorem 4 indicates that we have to determine which faces of this graph have more

than one bridge. The following faces (shaded in figure 3) have this property:

16 - 15 - 24

Faces with two vertices in common are grouped together and enclose a maximal subgraph of the simple graph, that is not properly 2-separable. The orientations of the components that are placed in the same subgraph, are fixed. If these relative orientations are not according to the constraints  $C_4$  and  $C_5$ , some additional modifications have to be carried out to satisfy the constraints. If the (relative) orientations of the components in distinct subgraphs are not according to the constraints, then the orientations in some subgraph may be changed by twisting the subgraph around its eventual articulation points. In our case we have 3 maximal subgraphs that are not properly 2-separable:

a) ({13, 17, 19, 18, 9}, {[13, 17], [17, 19], [18, 19], [13, 18], [9, 17], [9, 18], [9, 19]}).

This subgraph contains the wheel associated with the potentiometer (9).

- b) ({16, 23, 15, 3}, {[16, 23], [23, 15], [3, 15], [3, 23]}).

This subgraph contains the wheel associated with transistor (3).

- c) The subgraph containing all the edges of the graph in question except those edges that are contained in the graphs a) and b).

This subgraph contains two wheels, namely the terminal-wheel (hub 24) and the wheel associated with the operational amplifier (1).

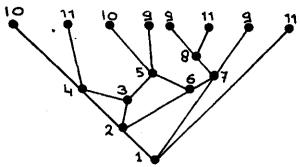

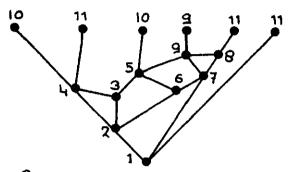

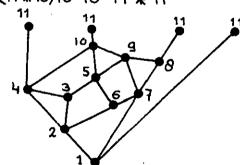

The orientation of transistor (4) is of course always ensured since one of its pins is connected with a jumper. The relative orientation of the two wheels in c) is according to the constraints, so no additional modifications have to be carried out. The subgraphs a) and b) have to be rotated to get the planar representation of the graph as given in figure 4. From this graph it is easy to construct the planar representation of the modified potential graph that satisfies the given constraints.

#### 5. CONCLUDING REMARKS

In the preceding sections we have shown how the wiring problem in a general form (taking into account the five design requirements  $C_1$  tot  $C_5$ ) can be formulated in a graph theoretical way such that implementation on a computer is possible.

The construction of the potential graph as described here is in fact the same as in [13], but we do not want to adopt the cumbersome notion of the generalised graph [14], which is only a bipartite graph from the topological point of view. Of the five constraints the first two did appear in literature before [15, 16, 13, 17. The step to  $C_3$  is then evident. In [13, 1] the implementation was also the same as described here but the actual content of theorem 3 is not noted. From this theorem it is tempting to conclude that the adjacency edges are superfluous, and indeed, in the planarity test they are. The planarity test on the graph extended with adjacency edges even yields less information than the test on the graph that does not contain these edges. However, when the graph turns out to be non-planar modifications have to be applied. The importance of the adjacency edges at this stage depends on how these modifications are carried out. Of course the potential graph need not be biconnected, but separability only has influence on the preceding when an articulation point is in one of the sets H;. In practice this case will not occur; besides this influence can easily be seen from the planar representation.

In the construction we indicated how to preserve the bipartiteness of the graph. This only is advantageous when this property is used in the operations carried out on this graph, for example in the planarity test.

After the planarity test a connectivity test is necessary for treating the orientations of the components as fixed in  $C_4$  and  $C_5$ . In the case that such a test has to be carried out it is recommendable to apply a planarity test that gives adequate output for the connectivity test. We have at our disposal a planarity test that yields the planar representation in a face-oriented way. After the planarisation a check on the orientations can be executed very easily. Another advantage is that the terminal wheel need not be added since  $C_1$  and  $C_2$  can be taken care of by starting the procedure with a face that contains the terminals in the required sequence.

More facts about splitting a graph in not properly 2-separable subgraphs are given in [17]. This paper, however, does not contain an algorithm for the splitting procedure in spite of Weinbergs statement [16] that it does.

In section 3 we mentioned as a thought that a constructive searching for a planar representation could solve the problem. Then, one can investigate the graph upon the requirements  $C_1$  to  $C_5$  by one test. However the problem remains to find a practical implementation. Weinbergs algorithm [16] for example can be alterned easily for this purpose, but is as planarity test already difficult to implement. Several other "constructive" algorithms have a simpler implementation, but the required alterations are complicated. This is the reason of preferring the method presented in section 3.

#### REFERENCES

- [1] W.L. Engl and D.A. Mlynski, "Embedding a graph in a plane with certain constraints", IEEE Transactions on circuit theory, CT-17, pp. 250-252, May, 1970.

- [2] K. Yoshida and T. Nakagawa, "Topological Layout Design of Monolithic IC in Computer-Aided Design", IEEE International Solid State Circuits Conference, University of Pennsylvania, 1969, Digest of technical papers, pp. 136-139.

- [3] N. Sugiyama, S. Nemoto, K. Kani, T. Oktsuki and H. Watanabe, "An Integrated Circuit Layout Design Program Based on a Graph-Theoretical Approach", IEEE International Solid-State Circuits Conference, University of Pennsylvania, Digest of technical papers, pp. 86-87, 188, 1970.

- [4] C. Berge, "Théorie des graphes et ses applications", Paris, Dunod, 1966.

- [5] K. Wagner, "Graphentheorie", Mannheim, Bibliographisches Institut AG, 1970.

- [6] G.D. Whyburn, "Analytic topology", New York, American Mathematical Society, 1942.

- [7] W.T. Tutte, "A theorem on planar graphs", Trans. of Am. Math. Soc., Vol. 82, pp. 99-116, 1956.

- [8] W.T. Tutte, "A theory of 3-connected graphs", Proc. Nederl. Akad. Wetensch., 64 pp. 441-445, 1961.

- [9] W.T. Tutte, "Connectivity in graphs", London, Oxford University Press., 1966.

- [10] C. Kuratowski, "Sur le problème des courbes gauches en topologie", Fund. Math., Vol. 15, pp. 271-283, 1930.

- [11] H. Whitney, "Non-separable and planar graphs", Trans.Am.Math.Soc. 34, pp. 339-362, 1932.

- [12] H. Whitney, "2-Isomorphic graphs", Am. Journ. of Math. 55, pp. 245-254, 1933.

- [13] W.L. Engl and D.A. Mlynski, "Topological Synthesis Procedure for circuit integration", IEEE International Solid State Circuits Conference, University of Pennsylvania, 1969, Digest of technical papers, pp. 138-139.

- [14] W.L. Engl and D.A. Mlynski, "Mengentheorie verallgemeinerter Graphen", Archiv für Elektrotechnik 54, Heft 5, pp. 278-284, 1972.

- [15] G. Hotz, "Einbettung von Streckenkomplexen in die Ebene", Math. Annalen, Vol. 167, pp. 214-223, 1966.

- [16] L. Weinberg, "Two new characterizations of planar graphs", Proc. 5<sup>th</sup> Allerton Conference on Circuit ans System Theory, (University of Illinois, Urbana, October 1967).

- [17] S. Mac Lane, "A structural characterization of planar combinatorial graphs", Duke Math. J., Vol. 3, no. 3, pp. 460-472, September, 1937.

fig.1

fic 2

fig. 3

fig 4

#### IV. MODIFICATIONS FOR MONOLITHIC IC'S

From the modifications we demand that

- a. they do not increase the number of masks

- b. they do planarize the extended potential graph.

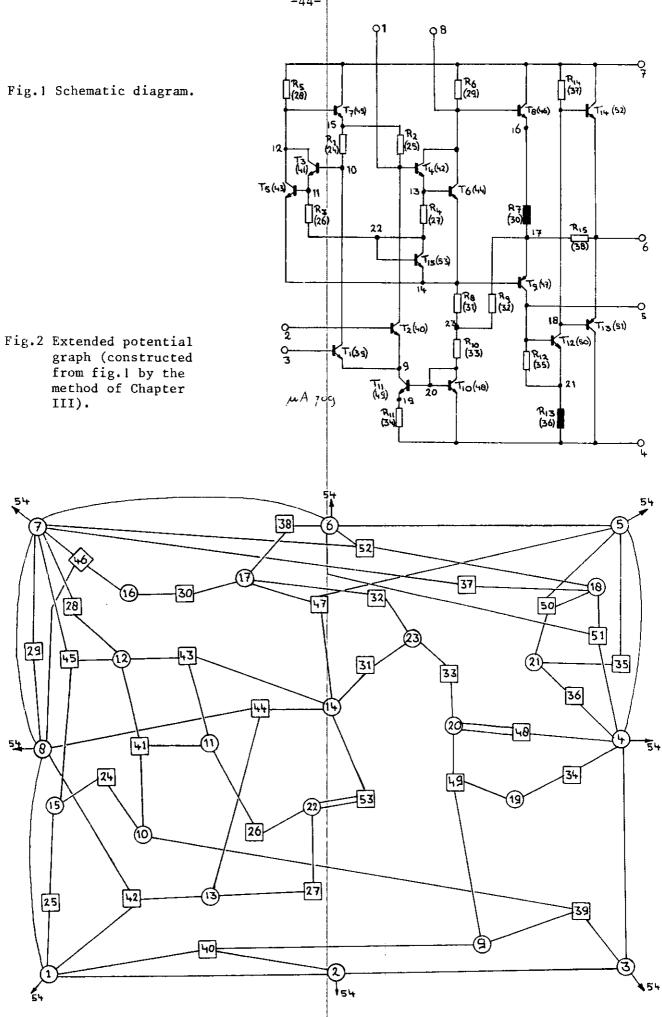

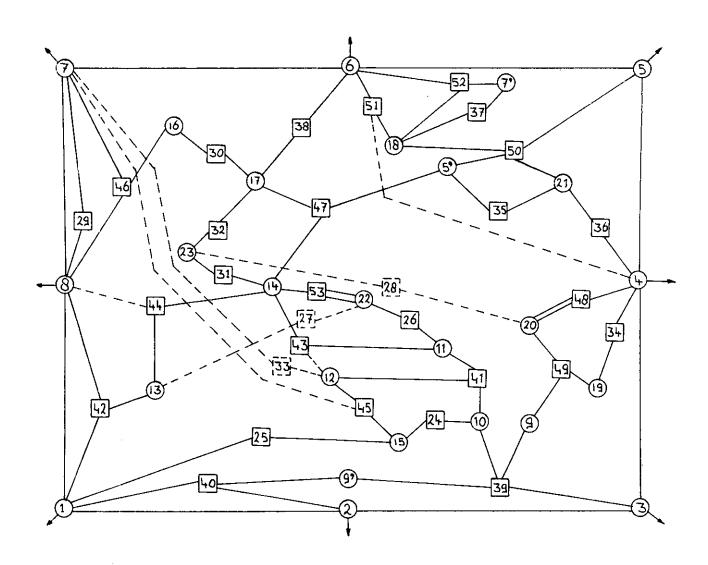

The following modifications are used to obtain the modified potential graph of fig. 3 from the extended potentialgraph of fig. 2:

- M1: When the collectors of some npn-transistors are connected with the same "potential tree" they may be placed in the same isolated region. This means that we need only one contact between this region and the conductive interconnection. In the graph this is reflected by a possible deletion of all the corresponding edges except one (arbitrary chosen) edge.

The disadvantages of this modification are not very important:

- restriction of the "layout-freedom"

- parasitic capacitance between the isolators and connections crossing the region

- field effects (when there is no buried layer, the expected decrease of the collector resistance is often held off because of these effects.

In the example the deletion of [45,7] is necessary for planarization, but also [43,12] and [44,8] are deleted.

- M2: For pnp-transistors the same possibility occurs, when their bases are connected with the same potential tree. In the graph all the corresponding edges except one arbitrary edge can be deleted. In the example no pnp-base-contacts are connected with each other, so in this case M2 cannot be applied.

- M3: The "lateral" realization of a pnp-transistor is the most common and better one, but in case the collector is connected with the lowest potential in the circuit one may choose for the substrate-pnp-transistor, since the substrate is always on the lowest potential. However, there are severe objections against this modification, which causes a deletion of the corresponding edge in the graph. Normally the p-diffusion is so undeep that the current gain is too low. Making the diffusion deeper causes many other components to have a parasitic pnp-transistor which is almost always disadvantageous. Besides the depth of the diffusion is difficult to handle.

Using this modification, [51,4] is deleted in fig. 3.

Fig.3 Modified extended potential graph.

#### Ad fig.3:

The following modifications have been applied:

M1: 7,45, 8,44, and 12,43 are deleted;

M3: 4,51 is deleted;

M4: 27, 28, and 33 are deleted;

M5: 7 is doubled;

M6: emitter contact (9) of T1 (39) is doubled; base contact (5) of T12 (50) is doubled.

M4: The greater the resistance, the larger is the possible distance between its contacts. When this resistorlength is large enough conductive interconnections may cross the resistor between its contacts. Their number is limited by the distance of the contacts. In this stage of the design, however, we make this number unlimited for resistors with a value greater than five times the "square resistance". In a later stage we incorporate the resistors taking into account their length and other criteria using the algorithm of Chapter II section 4. (When problems arise by the number of crossing connections, this can always be solved by a  $n^{\dagger}$ -diffusion series resistor (ca.  $10\Omega$ )). In the graph the modification is effected by deleting the corresponding vertex and its associated edges. The only objection is the restriction of the "layout-freedom". In fig. 3 the vertices 27, 28 and 33 with their associated edges are deleted. In fig. 4 they are introduced again. The same modification is possible in case of capacitors, but the series resistance of a SiO2-capacitor will increase.

M5: Beside deleting edges a graph may be planarised by increasing the number of vertices by doubling: this means replacing a t-vertex by two new vertices t<sub>1</sub> and t<sub>2</sub> such that:

The number of "potential trees" is increased, but both new "trees" should have the same potential. Therefore they are connected by a crossunder resistor (which is an as small as possible n -diffusion resistor permitting a crossing) or by a connection with the same isolated region. Of the last kind is the modification to obtain a doubling of vertex 7 in fig. 3. The n diffusion resistor must be applied only when it is absolutely necessary, because:

- its value is not always neglectible (ca.  $10\Omega$ ) and depends on the potential difference

- parasitic capacitance is introduced and we have field effects that may increase the resistance

- a separate isolated region may be necessary.

M6: Another is the doubling of a transistor contact. In the graph this is a doubling of a t-vertex as described above. Both new vertices, however must be connected with the c-vertex corresponding with the transistor. When a contact of a transistor is doubled no other contact of the same transistor can be doubled. Transistor T<sub>12</sub> of fig. 1 has got a double base contact and transistor T<sub>1</sub> a double emitter contact, which means a doubling of vertex 5 and vertex 9.

A disadvantage is the increase of the capacitance between the base- or emitter lead and the collector region and - in the latter case - the base region.

Fig.4 Embedding of the resistors.

Fig.5 Symbolic layout.

# Ad fig.4 and fig.5:

In fig.4 one can see which potentials cross the deleted resistors. The resistor are embedded such that they only cross t-vertices taking into account optimalization criteria e.g. the least possible number. In fig.5 a symbolic layout of the schematic diagram of fig.1 is depicted in correspondence with the modifications of fig.3.

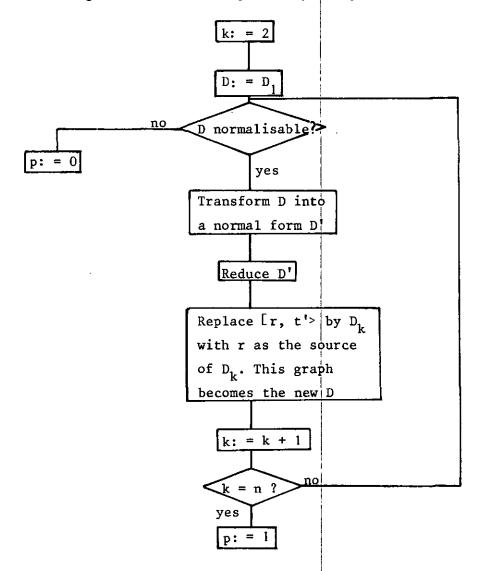

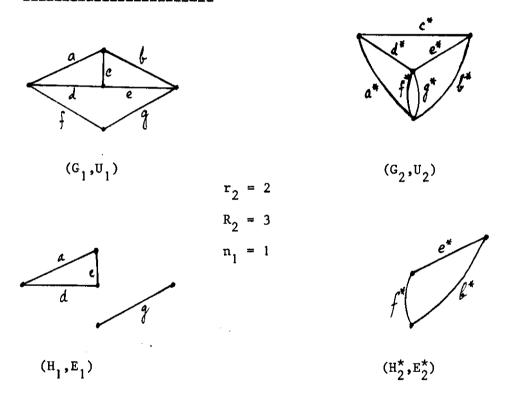

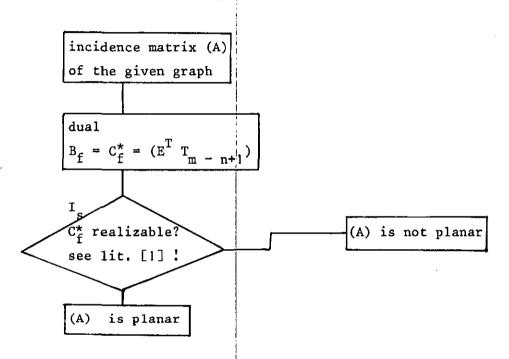

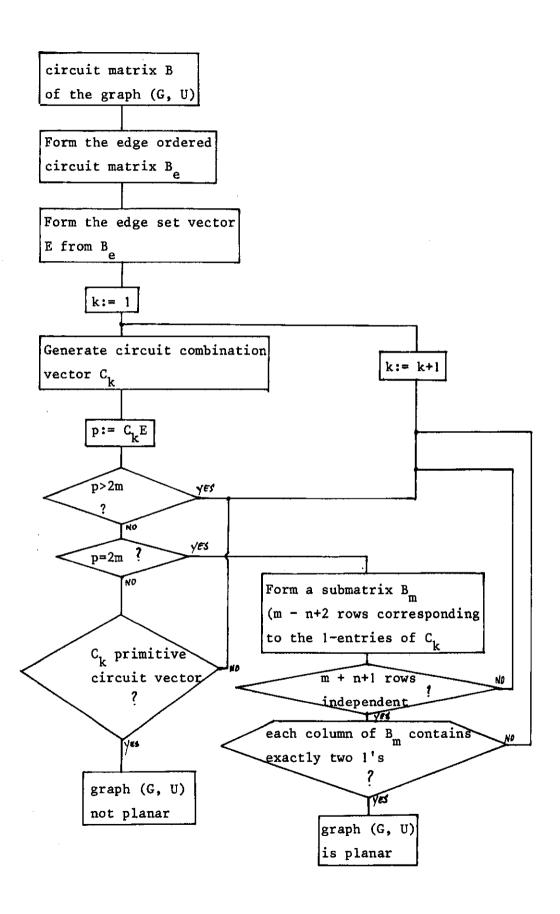

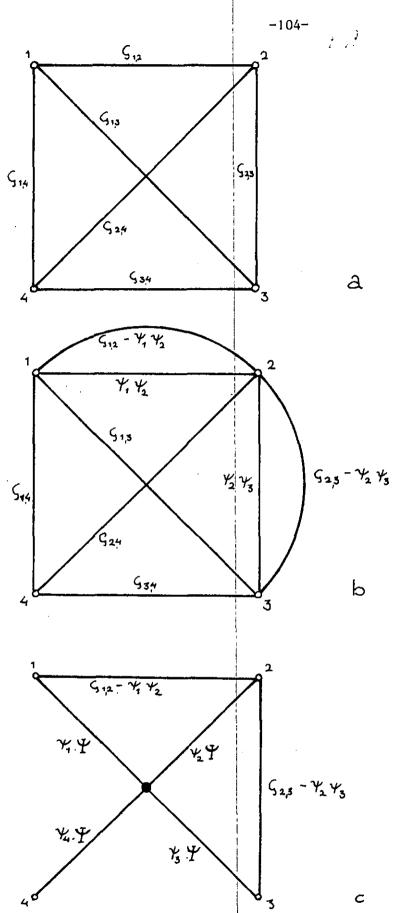

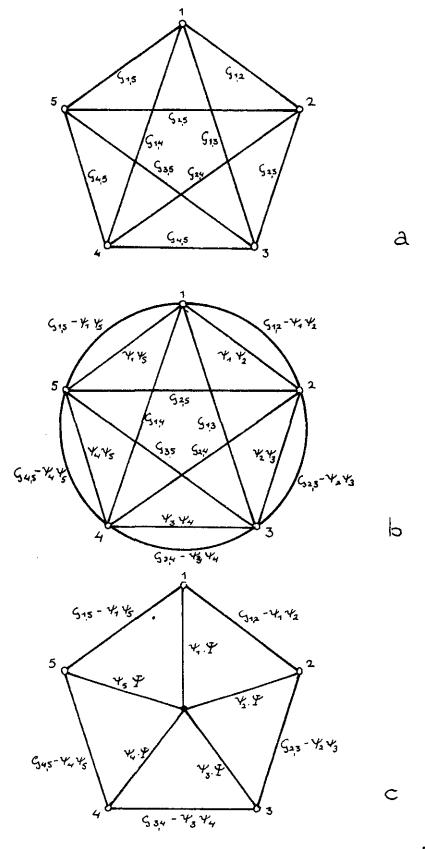

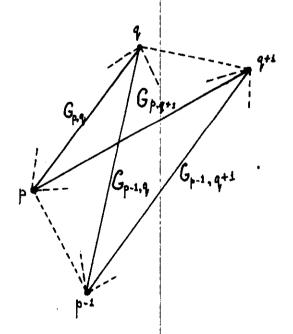

#### V.THE "CEL"-PLANARITY ALGORITHM

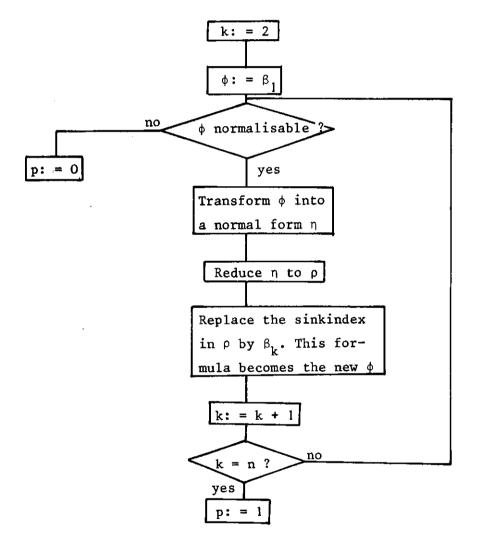

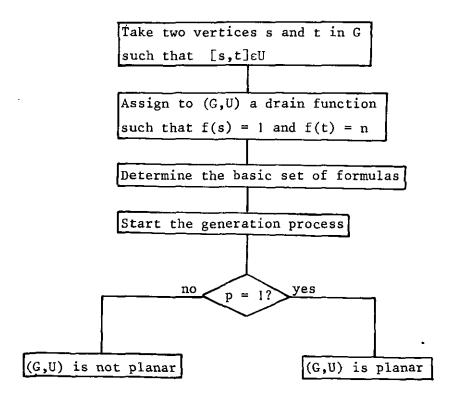

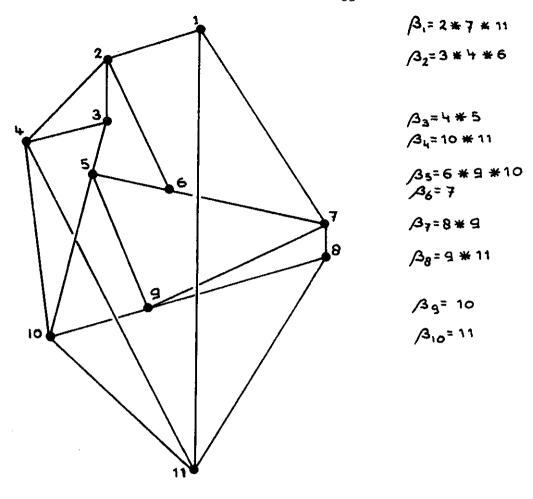

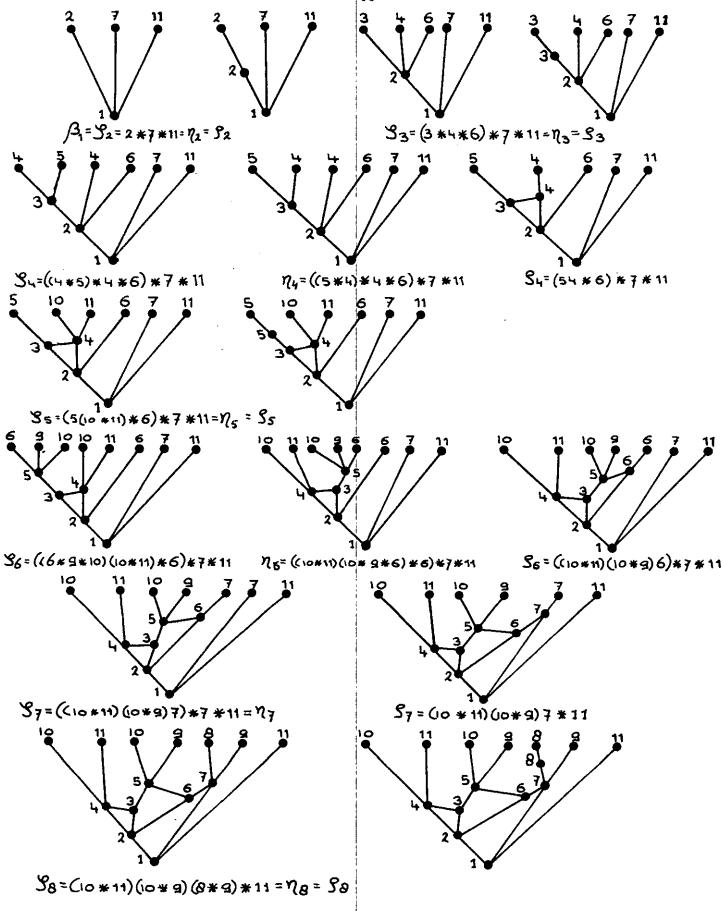

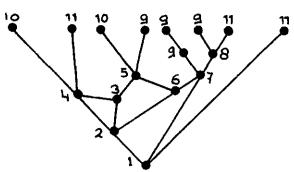

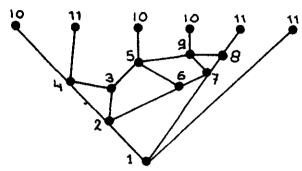

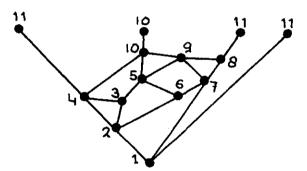

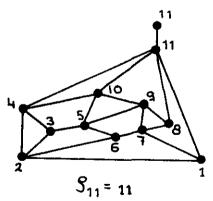

## 1. Assigning a drain function to a graph