# Design of digital systems

Citation for published version (APA):

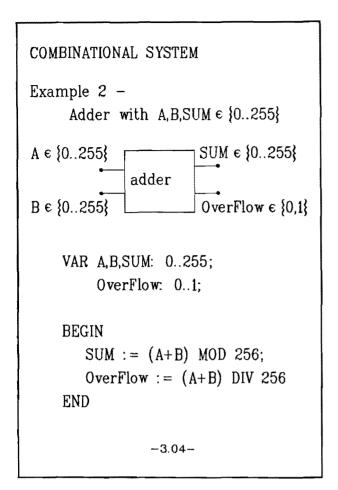

Weert, van, M. J. M. (1993). *Design of digital systems*. (Eindhoven University of Technology : Eindhoven International Institute; Vol. 276/2). Technische Universiteit Eindhoven.

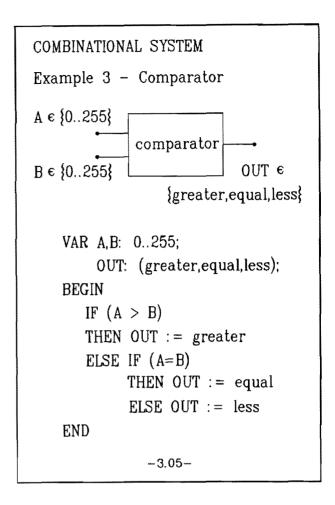

# Document status and date:

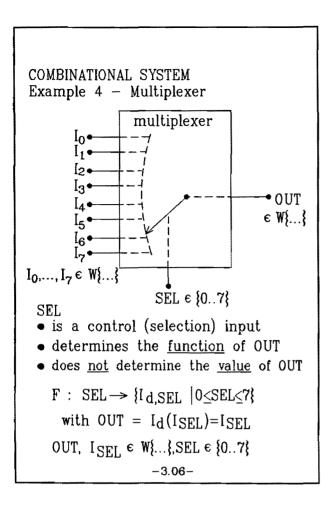

Published: 01/01/1993

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 04. Oct. 2023

#### Eindhoven International Institute

# Course In Electronic Engineering

Survey

Course:

Nr 276/2

: INTRODUCTORY SEMESTER 1993

- Electronic Engineering -

Subject

: DESIGN OF DIGITAL SYSTEMS

Lecturer

:lr M.J.M. van WEERT

Author

: Ir M.J.M. van WEERT

Copy

vo

Copyright Ir M.J.M. van Weert

Reproduction in any form whatsoever is forbidden without written consent of the author.

Problems:

Problem numbers in parentheses refer to the problem numbers in the Dutch edition of this survey (edition January 1992)

# Table of Contents

| 1 | Introduction                                                                                                                                                                                                                                                                                                           | 1.1                                         |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 2 | Digital Systems  2.1 What is a digital system?  2.2 The design of a digital system  2.3 Combinational, sequential and binary systems  2.4 Numbers and number systems  2.5 Summary                                                                                                                                      | 2.1<br>2.7<br>2.12<br>2.22                  |

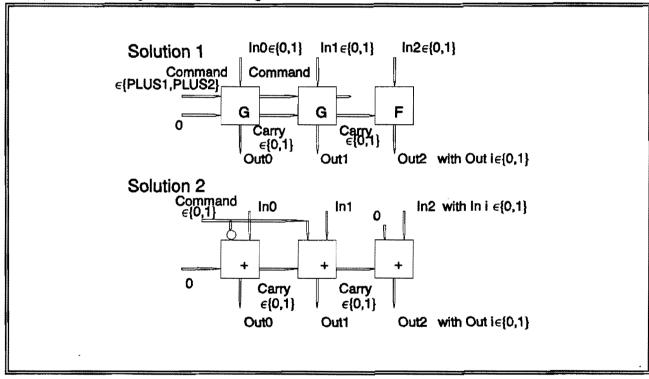

| 3 | Combinational systems  3.1 Behavioural description; specification  3.2 From behavioural description to system realization  3.3 Iterative networks  3.4 Tree structured networks  3.5 Summary                                                                                                                           | 3.2<br>3.6<br>3.7<br>3.16                   |

| 4 | Binary systems and Boolean algebra  4.1 Boolean algebra and switching algebra  4.2 Switching algebra and binary systems  4.3 Minterms, standard normal form and maxterms  4.4 Summary                                                                                                                                  | 4.4<br>4.11<br>4.17                         |

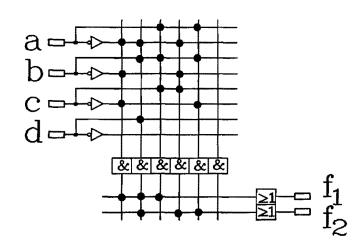

| 5 | Realization of switching functions  5.1 Realization of a sum of minterms  5.2 Sum Of Products (SOP) and the function table  5.3 Realization of an SOP form; programmable logic  5.4 Realization with NAND and NOR gates  5.5 The multiplexer as a universal building block  5.6 The exclusive OR function  5.7 Summary | 5.2<br>5.10<br>5.19<br>5.24<br>5.27<br>5.31 |

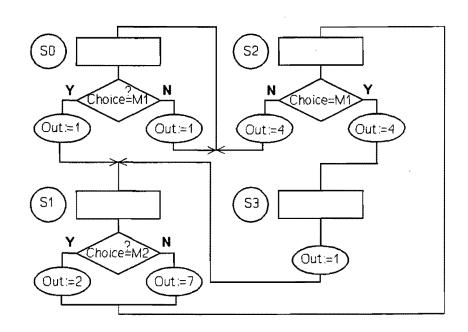

| 6 | Sequential systems  6.1 Finite State Machine (FSM)  6.2 Behavioural description of finite state machines  6.3 ASM chart  6.4 State diagram and state table  6.5 Standard architecture; canonical form  6.6 Summary                                                                                                     | 6.3<br>6.9<br>6.17<br>6.21<br>6.26          |

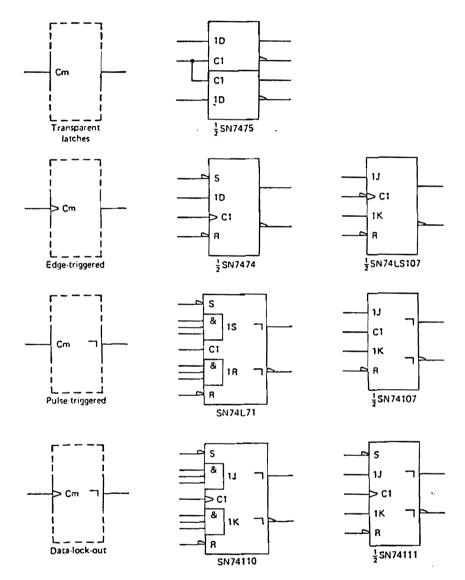

| 7 | Realization of finite state machines 7.1 Realization of memory; the flip-flop 7.2 Binary sequential systems 7.3 Standard functions; standard FSMs 7.4 Summary                                                                                                                                                          | 7.2<br>7.9<br>7.16                          |

| Α | ppendix A. Examinations                                                                                                                                                                                                                                                                                                | A.1                                         |

| Α | ppendix B. Literature                                                                                                                                                                                                                                                                                                  | B.1                                         |

| Α | ppendix C. IEC Symbols                                                                                                                                                                                                                                                                                                 | C.1                                         |

# 1 Introduction

This course deals with the design of digital systems, being systems having discrete rather than continuous inputs and outputs.

The central -but certainly not trivial - question in this course is how to design such systems.

# Ultra Large Scale Integration

# Texas Instruments TMS320C30

- Digital signal processor

- 700,000 transistors

# Intel 80860

- RISC processor

- 1,000,000 transistors

# Intel 80486

- CISC processor

- 1,180,000 transistors

# Motorola 68040

- CISC processor

- 1,200,000 transistors

-1.02-

# As a result of the progress of IC-technology we are able to build continually larger and more complex. but still economic, digital systems. Figure 1.02 shows an example of the state of the art in 1990. We see four examples of a pre-eminent digital system: the microprocessor. The first one is a digital signal processor with 700,000 transistors, a RISC processor with 1,000,000 transistors (RISC = Reduced Instruction Set Computer). The second one is a Complex Instruction Set Computer, a so-called CISC-processor, with 1,180,000 transistors and another CISC-processor with 1,200,000 transistors. Figure 1.02 lets us see that the complexity of a digital system, expressed in the number of transistors on a single IC, has exceeded the 1,000,000 transistor boundary. We have entered the era of Ultra Large Scale Integration (ULSI). Furthermore, we do not expect development to stop here, and time should bring a continually growing complexity.

Up till now we have considered digital systems on a single IC. The complexity of digital systems realized on one or more printed circuit boards, with the help of more integrated circuits, will exceed multiples of this complexity.

This course deals with the state of the art of the design of such gigantic systems.

The central question remains: "How do we design

# DIGITAL SYSTEMS

Current and new technical systems with increasing complexity can be ECONOMICALLY realized using DIGITAL methods.

- New products with unprecedented possibilities

- Analog techniques are being replaced by digital ones.

-1.03-

such a complex digital system?". However, before we answer this question, or point to possible directions, we will first take a look at the importance of digital systems.

The importance of these systems can not be separated from the powerful technological development that is due to the production of integrated circuits. Actually, the high standard of the microelectronics technology is what enables us, the digital system builders, to economically realize complex digital systems. This means, as figure 1.03 shows, that for existing or new technical problems we can still realize economically feasible (i.e. affordable), complex digital solutions. This will lead to new products with unlimited possibilities. This will also lead to systems where previous analog solutions are replaced by digital ones. Digital systems, hand in hand with microelectronics, are becoming increasingly important in all sorts of subjects and are infiltrating more fields. It is difficult not to fall in the temptation of filling a whole chapter with all sorts of criteria without thinking of an example. However, we shall limit ourselves to discussing examples in the field of audio-visual applications; the field of consumer electronics.

## EXAMPLES-CONSUMER ELECTRONICS

### COMPACT DISC

- Digital storage of information

- sampling

- modulation

- Error detection and correction

- error correcting codes

- interpolation of signal samples

- Digital to analog conversion

sample rate conversion

- Servo systems

CAR Information and Navigation System (CARIN)

-1.04-

An example in the consumer electronics area is the compact disc, see figure 1.04. In the compact disc system, audio signals, music and speech are digitally written on a medium, the compact disc. They are digitally read back with the help of light. Digital storage means that audio signals being analog by nature, have to be translated to digital signals. The sampling and quantizing of the signal does not belong to the field of this course. Some aspects of coding will be discussed later. Once we have the signal in digital form we can do with it all sorts of things using digital systems. We can process the signal; examples being filtering and modulation. Because the signal is digital we can always reconstruct the original signal.

When writing or reading information to/from a compact disc something may go wrong, errors can occur. A solution is the use of error detection/correction codes and the interpolation of signal samples. This is also an example of the application of advanced techniques in a digital system. The servo system in a compact disc is also very important, i.e. the control system of the laser head and motors. There are also many digital techniques applied there.

Besides the compact disc, there are other derived products, such as the CD-ROM, and the Car Information and Navigation System (CARIN), where digital systems play an important role.

# EXAMPLE - CONSUMER ELECTRONICS

# DIGITAL TELEVISION

Everything behind the MF stage becomes digital

- A/D and D/A conversion

- frequency up to 17 MHz per

8 bits sample

- Digital colour decoder

- Image memory and image processing

- Teletext

- Picture in picture

-1.05-

# EXAMPLE - CONSUMER ELECTRONICS

#### DIGITAL AUDIO

- Digital signal processor

- Digital audio via satellite

- Teledata

- programme identification

- traffic information

-1.06-

Another example in the field of consumer electronics is the digital television, figure 1.05. The expectation is that base band audio and video signals will be processed digitally. Video signals occupy a larger frequency range than audio signals. This is expressed in higher sampling frequencies in digital television, up to 17 MHz. In the processing of digital video signals we can first consider items such as digital colour decoders. This will lead to a better quality of the decoding process with lower costs. Also, we can consider saving an image in memory and processing it later on: image processing. The plans for high definition TV can only be realized by reducing the required bandwidth through the use of image processing techniques.

Other examples of the application of digital techniques in consumer-TV are Teletext and "picture in picture".

As a third example in the field of consumer electronics we mention digital audio. In figure 1.06 we see that digital signal processors are currently in a state that allows them to be used in all sorts of audio signal applications. These digital system processors could be more general, or specifically designed for a special purpose application. We have arrived at a state where a digital system processor can replace the classical sound controls of an amplifier. Another application of digital audio is the transmitting of radio programs, digitally, via a satellite. It is also possible to transmit other information in addition to the program information. We are then talking of tele-data. Examples of applications could be program identification, as well as traffic information. For example, information can be distributed via such a system in the from of files. This information can then be used in a system, such as the previous mentioned CARIN system, to point out alternative routes. These are examples of applications where digital systems play an important are currently technically and that implementable.

## **EXAMPLES**

#### • BUSINESS

- Point of sale terminals

- Banking terminals

- Credit card verification

- Automatic transactions

- Access monitoring

- Stock control

- Word processing

## INDUSTRY

- Process control

- Numerically controlled machines

- Robots with sensors and vision

- Process monitoring

- Data acquisition systems

# CONSUMER

- Home computers

- Computer aided learning

- Intelligent toys

- Programmable applications:

kitchen: washing machine,

microwave oven

- Cars

-1.07-

## **EXAMPLES**

## INSTRUMENTATION

- Automatic test equipment

- Electronic instruments

- Chemical/medical analysis

#### COMMUNICATION

- Remote terminals

- Programmable controllers

- Switching equipment

- Multiplexers

- Message handling

- Error control

# • DATA PROCESSING

- Programmable calculators

- Office computers

- Input/Output processors

- Intelligent peripheral equipment

- Communication interfaces

- Performance monitoring

- ETC, ETC, ETC, ETC, ETC.

-1.08-

In addition to consumer electronics, there are many other fields where digital systems are applied. Figures 1.07 and 1.08 mention a number of them. We see first examples from the commercial field, such as cashier terminals, banking terminals, identification of credit cards, automatic banking transactions etc., collectively known as point of sales systems. We also see applications in building security, stock control, word-processing etc. As examples of industrial applications we can think of things such as process control, numerically controlled machines, robots with sensory and vision capabilities, automatic assembly lines etc. In general: process control and data acquisition systems.

As examples of other consumer applications one could name home computers, game computers, tutoring systems, intelligent toys, programmable home appliances such as washing machines, microwave ovens etc. Also applications in automobiles such as the ignition and break systems. From the field of instrumentation we think of testing devices where many functions could be automated, for example continuous automatic calibration. By instrumentation we mean electronic as well as chemical and medical analysis instruments.

One of the roots of digital techniques lies in the field of telecommunication. There we find yet another important application field of digital systems. For programmable example. remote terminals, controllers, switching devices for telephones, multiplexers for data transmission etc. A second important application area of digital techniques is the field of processing and storage of data and information, i.e. the field of data processing. Such applications include programmable calculators, office computers, I/O processors, intelligent terminals and large computers connected to local area networks.

In this overview we did not pursue completeness; there are still many unmentioned fields.

Thus far we have discussed a large number of application fields of digital systems, having a complexity of millions of transistors. This complexity will continually increase in the future.

We now return to the central question of this course: "How do I design a digital system with such a complexity?". It will be clear that designing large systems by starting with a network of a few transistors, and then expanding it until the total system is realized, will not yield acceptable results.

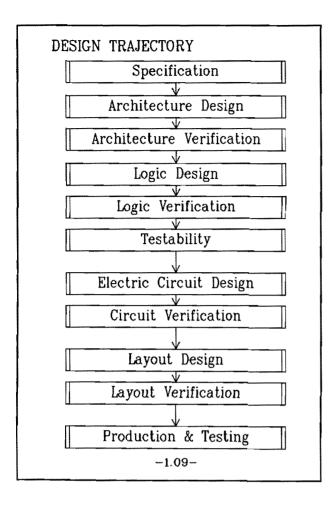

This is a methodology that would probably lead to disappointment. A better strategy is shown in figure 1.09.

Digital design is a structured and planned occupation according to a checklist. The whole design comprises a number of phases, beginning with an idea and ending with the production and testing of the final system. We begin by specifying what we want to build. Next follows the so-called architecture phase. In this phase we consider how the digital system should behave in order to satisfy our requirements. The activity of whether the chosen architecture satisfies our specifications is called verification. After the architecture phase we start the logic design phase. In this phase the building blocks of the architecture are translated into realizable logic circuits. We utilize a computer simulation system to check that the logic circuitry is indeed an implementation of the specified architecture.

We are then speaking of logical verification. An important aspect of the design is testability. How do we ensure that an IC with 1.000.000 transistors functions correctly after production?. During the logical design we have to take measures that will guarantee this testability. That is to say making testing simpler. At the end of the logical design phase we have a number of schemes with logical building bricks. These schemes must be translated into schemes with transistors, resistors, diodes, and similar components. This translation process we call the electronic circuit design, being the next phase in our design trajectory. In this phase we start a new specification. After the transistor schemes have been designed we start the layout phase in which we make the IC layout. That is, we show where the transistors should be placed on the IC, how they are connected etc. After the layout verification follows the production and the testing. Figure 1.09 suggests that all these activities in the design process, are carried out by one person. In reality this is generally not true. The specification is made by the customer. mostly in cooperation with the system designer. The architecture and logic design are generally made by the digital system designer. The electrical circuit design and the detailed layout is the domain of the IC designer. The digital system designer will remain globally involved in this phase. The testing of the finished product is carried out by the test engineer. In this course we will be occupied with the design of digital systems. That is to say: we are considering methods for systems specifications. We will direct out attention towards architecture. Another important topic in this course is the methodology and techniques used in logic design.

# 2 Digital Systems

# 2.1 What is a digital system?

As previously mentioned this course covers the design and realization of digital systems.

This should be seen in the context of the design trajectory mentioned in the previous chapter.

# DIGITAL SYSTEMS

- WHAT is a digital system?

- HOW do I design and realize a digital system?

-2.01-

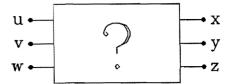

# SYSTEM

- Black Box

- Inputs u, v, w

have a value

voltage, current, angle, ...

- Outputs x, y, z are given a value by the system

- The system shows a behaviour: the output values vary in time

- A relation exists:

(u,v,w)R(x,y,z)

which describes the behaviour

of the system, with u ... z

being functions of time

-2.02-

The topic of design presents two questions (see figure 2.01):

- What is a digital system?

- How do I design and realize a digital system?

Before we discuss the design and realization of a digital system, we must first know what a digital system? Fortunately we have notion as to what that is. If I ask you what a digital system is, you will frequently come with answers such as: a computer, (parts of) an automaton, such as a coffee machine, traffic light controllers, systems in consumer electronics, etc. And also clocks, such as those hanging all over the university, are examples of digital systems. We shall limit ourselves, in this course, to digital systems that are built using electronic building bricks.

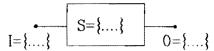

The question: "What is a digital system?", comprises two sub-questions. First: "What is a system?", and "What are the special characteristics of a digital system?". Formally speaking we can think of a system as an object, or a black box, with inputs and outputs (see figure 2.02). We shall limit ourselves, in this course, to systems with a finite number of inputs and outputs. The inputs (here called u, v, and w) have a value. This could be a voltage, a current, an angle etc. The outputs (called here x, y, and z) are assigned a value by the system. This could also be a voltage, a current etc. A system displays its behaviour. That is to say the output values change in time due to the change of one or more of its inputs. The outputs of the systems we consider are not arbitrary. They are systematic, rule governed, and the outputs change their values in time according to a deterministic behaviour. We could say that the temporal behaviour (behaviour with respect to time) is described by the system as a relation between the input and output values.

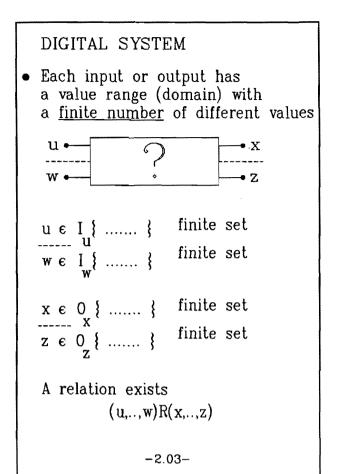

A digital system (figure 2.03) is a system with the (extra) property that all inputs and outputs have a value domain with a finite number of values. The value domains of u, v, and w form a finite set, i.e. a set with a finite number of elements. Furthermore, the values of the outputs x, y, and z form a set with a finite number of elements. Moreover, it still holds, for digital systems, that there is a relation between inputs and outputs.

This relation, R, specifies the behaviour of the system in time, and shows the response of the system to the change in input values. We observe, however, that a specific set of input values does not necessarily give a fixed response. Even the system itself does not change in time. The system remains the same but it can have memory (it can remember), involving the existence of system states. In this case, we are considering a sequential system. We shall return to this topic later in this course. We remind ourselves that we shall limit our discussion to systems that do not change their behaviour in time, the so-called time-invariant systems.

In figure 2.04 we have two examples of what could be, and what is not a digital system. The first example shows a relation, or a function where the input and output values belong to the set of real values between 0 and 1, and the relation is given by  $z=\sqrt{x}$

This is not a digital system because the value domains of input and output do not contain a finite number of values. In our second example we have a system with two inputs, u and v, where the values of u and v belong to the set of whole numbers from 0 to 9. We are going to use, throughout this course. a Pascal-like notation to denote such sets. Furthermore, the system has an output z, with a value domain of "yes" and "no". The relation is given by a function, F, defined by z = "yes" if u > w and "no" otherwise. This is an example of a digital system because input and output values form finite sets. Clocks, such as those hanging all over the university, are examples of digital systems. The input is composed of a minute pulse or, more accurately, its presence or absence. The set of output values contains all the possible positions of the minute and hour hands: sixty positions for the minutes hand and twelve for the hours hand. Thus finite sets in both cases.

# BLACK BOX MODEL

DIGITAL SYSTEM

I R O

Input - Relation - Output

- R: Specifies the behaviour of the system

- R: Changes in inputs values

Changes in output values

- R: Is a specification

-2.05-

ALGORITHMIC MODEL

input

data

object

transformation

- transformation rules describe conversion of data object from input domain to output domain

- a number of more simple transformations

prescription, "algorithm"

- system behaviour specified by algorithmic description, "programme"

-2.06-

To summarize (see figure 2.05) a digital system is one with several inputs and outputs where all inputs and outputs have their own domain. Furthermore, these value domains have a finite number of elements. In addition, there is a relation, R, between inputs and outputs, i.e. between input domains I and output ranges O. This relation, R, defines and specifies the behaviour of the system. Thus R defines how the system changes its output values, when the input values change. We also call R a specification of the system. This relational view of the system behaviour and system specification is called the black box model, or sometimes the system model.

If we look at a digital system from a different perspective, we can, rightfully, say that it samples its inputs before generating the corresponding outputs (see figure 2.06).

The system processes the input values to produce new output values, i.e. transforms input values (from the set of possible input values) to output values (from the set of possible output values). Thus, the digital system performs a transformation of data objects from the input domain to data objects of the output domain. The rules defining this transformation accurately describe the conversion of objects from the input domain to objects from the output domain. These transformation rules specify the behaviour of the system. In general the transformations, executed by digital systems, are very complex. We shall have to decompose such transformations into simpler ones. These simple transformations may be (partly) carried out in parallel or in series, so that the same overall result is obtained.

We receive a recipe or prescription for the production of the output data from the input data. We shall call such a prescription an *algorithm*. In this view towards the system, the behaviour is defined by a formal algorithmic description, a program. Now we shall consider the algorithmic model. We can regard such an algorithmic description as a specification of the system and also as a realizable description.

## ALGORITHMIC MODEL

The algorithmic description can be executed by a machine comprising:

- control

- data path (operators)

- memory

# Example:

A computer system constitutes the data path and the memory. The programme containing the description of the algorithm constitutes the control

-2.07-

An algorithmic description is, indeed, executable by a machine comprising the following elements (see figure 2.07):

- Management or control

- Operators or data path

- Memory or data storage

The control defines when each (partial) transformation may take place. The data path or operators carry out the transformation. The memory or data storage serves for the preservation of the intermediate results and inputs.

Consider as an example a computer system running a program. The computer system forms, from our viewpoint, the data path and the memory of the system. The program which describes the algorithm, forms the control. Thus, following this model, we can easily make a system that satisfies the specification. A disadvantage, however, is that such a realization will be slow and expensive in comparison with tailored realizations.

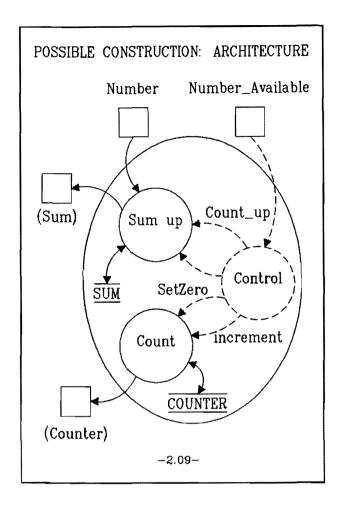

Let us look at an example of an algorithmic system description. Consider a system that adds a list of successive numbers and displays, as a result, the running sum and the count of added ALGORITHMIC MODEL - EXAMPLE

Sum := 0; Counter := 0;

REPEAT

WAIT\_FOR Number\_Available;

{Wait for next number}

Sum := Sum + Number;

{Compute next sum}

Counter := Counter + 1

{Increment counter}

FOREVER {Repeat this loop infinitely}

-2.08-

numbers. A description of the system's behaviour is given in figure 2.08. We have used a Pascal-like language to describe the system, we shall do so throughout this course. Achieving an absolute fluency in a programming language, such as Pascal, is not the purpose of this course. However, we shall use a Pascal-like language for the communication of behavioral descriptions. For this purpose, we do not need too much language knowledge and fluency.

We can notice the following in the behavioral description of figure 2.08. The system begins by initializing its memory. That is to say, Sum and Counter are set to 0. The next construct is a "REPEAT FOREVER" construct. Throughout this course we shall use similar constructs to denote that the system behaviour changes in time, hence that the system has memory. The system will respond differently to the same input. For example, the same input, e.g. 5, will produce the successive Sum output: 0, 5, 10, 15, etc. Furthermore, we see from the system description that it (obviously) waits until the following input number is ready. Next, the number is added to the running sum and the counter is incremented by 1. This is the whole system behaviour.

Figure 2.09 shows a sketch of a possible architecture. Here we make use of the three previously mentioned elements: control, operators and memory. The control is denoted by a dashed circle, the operators by a solid circle and the memory by two horizontal lines. Examples are the memory of the sum and counter. We observe that behavioral description introduces transformations, which leads to equivalent operators or data paths in our model, namely the summation operator and the count operator. The new running sum is computed by the summation operator. The count operator increments the counter by one when activated. The total system in managed by a controller. When the controller receives an external command, indicating that a new number is available. it will signal the sum and count operators to start work. Later in this course we shall go deeper into the use of these models.

We have seen a short global answer of the question of "What is a digital system?". A digital system's input and output elements belong to finite sets of possible values. Furthermore, in this course we shall limit ourselves to digital systems that can be realized with electronic components and that are time invariant. The behaviour of such a system can be described by the relation between input and output values. In this case we are considering a black box model. Moreover, this behaviour could be described by a set of transformation rules or algorithms. In this case we are considering an algorithmic model. In the latter case, the realization in a data-path/control model is possible, where each part could be described by a black box model.

# HOW

Do I Design And Realize

a Digital System ?

-2.10-

# 2.2 The design of a digital system

After having discussed the question "What is a digital system?" we have arrived at the central topic of this course: "How do I design a digital system?". The ultimate purpose of a design process is the realization of a digital system built of easily available, trustworthy, standard components such as transistors, resistors,

logic gates, flip-flops, counters, registers, and also more complex standard building blocks such as microprocessors, I/O ports, etc. The system that we build from these standard components should behave in a predefined way and exhibit this predefined behaviour. In practice this is not as simple as described here.

## COMPLICATIONS

- Objective of design is unclear

- No unique behavioural description / specification

- Missing:

- Overall picture of the total system

- Relation between the different parts of the system

-2.11-

#### REMEDY

- Specify WHAT to make

The wanted behaviour must be precisely described

- Make a STRUCTURED design and make use of a HIERARCHICAL system setup

A system should be constructed using a <u>limited number</u> (a maximum of 7) subsystems which again should be constructed using a <u>limited number</u> of subsystems which again should be constructed .....

using a handful of building blocks

-2.12-

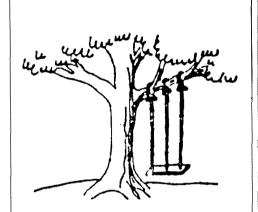

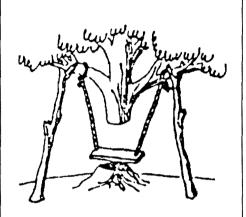

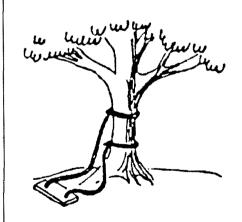

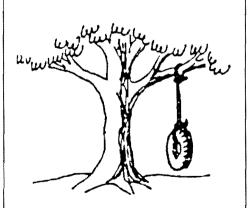

Two frequently occurring complications are (see figure 2.11): the absence of a (good) behavioral description. That is, what the system must do is not (clearly) specified. This results in a situation where the realized system does not always do what the client had in mind. The swing example on page 2.9 illustrates this problem. Secondly, when dealing with very complex systems one tends easily to lose the overview of the total system. One has frequently no insight in the relation between different system subcomponents. This results in situation where suboptimal solutions are frequently obtained, sometimes causing sub-components not to work optimally together. When the underlying relation is not clear anymore, one often attempts to solve a problem in one part which actually occurs in other parts.

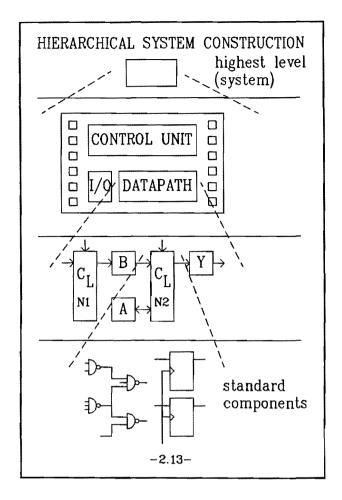

The remedy of these design complications is twofold (see figure 2.12). First we have to decide WHAT we shall make. That is, the desired system behaviour must be carefully described. Secondly, we must manage the complexity by designing in a structured way. Therefore we must use a hierarchical system structure. This means that we shall try to build a system from a limited number of subsystems (a maximum of 7). We shall try to construct each of these subsystems from a limited number of smaller subsystems. We continue this process until the subsystems can be realized by means of a handful of building blocks.

How it was designed

What the drawing looked like

How it was ordered

How it was mounted

How it was modified

What the client really wanted

#### DESIGN METHOD

- WHAT should the (sub)system do?

- HOW should the (sub)system be built using a number of simpler subsystems?

- If these subsystems are NO standard building blocks, repeat from WHAT

# HOW TO BUILD A (SUB)SYSTEM

- Make choices from alternatives

- Make use of knowledge and experience

experienced designer, system expert

-2.14-

Figure 2.13 shows this hierarchical system decomposition schematically. In this case we see that the highest system level is divided into three subsystems. Each of these subsystems is internally divided into a number of smaller building blocks. Finally, we realize these building blocks with standard components. It is important to apply this structured hierarchical design methodology at all levels. That is to say, that on each level we must first describe WHAT the subsystem must do, and then, only after the system is completely specified, we should consider how to build the system from a number of limited and well-defined subsystems.

We have already divided the design process into a number of repeated applications of the following two steps (see figure 2.14):

- 1. What must the system do?

- 2. How do I build the subsystem from a number of simple blocks?

If these blocks are not standard, we should first describe what these block do, and then afterwards define how they could be realized. When building a system from a number of simple blocks we must sometimes make well balanced choices. Some alternatives may be less suitable because they lead to a less optimal realization using standard build blocks. Hence to make the choice it is necessary to have some knowledge of the set of available standard building blocks and their use in more complex modules. This is called *experience* and a person with this knowledge is an experienced designer.

Ultimately, in the future, a designer would be assisted by an expert system.

#### THIS COURSE

- Behavioural description of digital systems

- Functional behaviour of combinational circuits

- Boolean algebra and switching algebra

- Combinational systems and standard building blocks

- Behavioural description of sequential systems

- ASM-charts and state diagrams

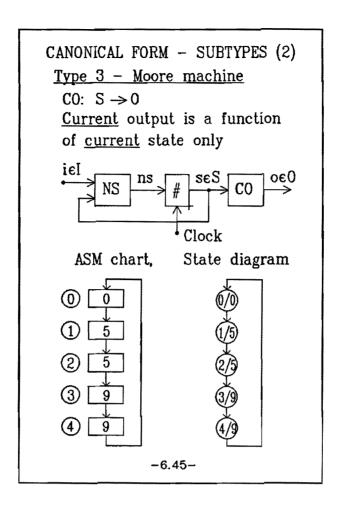

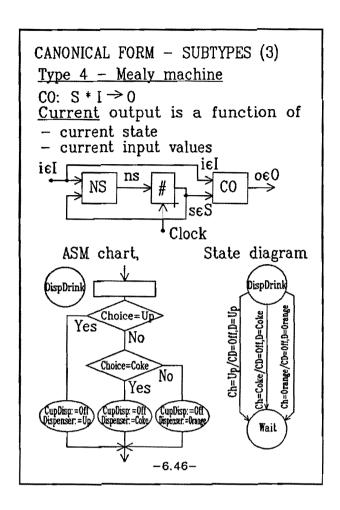

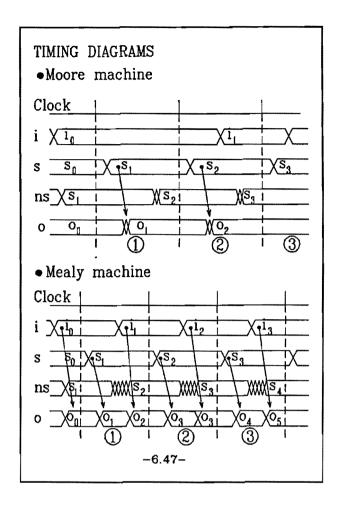

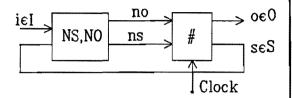

- Memory-combinational model

Moore model, Mealy model

- Realization of flip-flops and memories

- Realization of state machines

counters, registers, pattern generators

- Elements of system design

- processes and data flows

- control unit and data path

- selection and adressing

-2.15-

We can observe two things about the above discussion:

- The definition of what is an optimal realization depends on many factors, such as the price, the number of components, the size of the system, the reliability, the speed, or the desired degree of security.

- The definition of what are the standard building blocks, and consequently where the design cycle stops, depends on the state of the art. It changes towards more and more complex building blocks, and even to software automatically generating circuits (silicon compilation).

2We have now seen what digital systems are and we have discussed a method for designing them, namely the structured hierarchical design methodology. With some more knowledge about the basic building blocks, we could view this course as basically finished.

As one could expect this is not our endpoint, however. We shall consider, apart from the necessary basic knowledge and basic building blocks, the use of a design methodology.

It the remainder of this course we shall first discuss (see figure 2.15) the description of digital system behaviour. Subsequently we shall study the functional behaviour of combinational systems, Boolean algebra, switching algebra, and standard building blocks related to combinational functions. Furthermore, we shall discuss the behavioral description of sequential systems, being systems with memory. Here so-called ASM charts and state diagrams play a role. A sequential system could be realized using memory and combinational functions. We shall discuss the realization of this memory using flip-flops. We shall also discuss state machines, counters, registers, pattern generators etc. And last but not least we are going to consider elements of system design such as processing and data flow, control and data path, selection and addressing.

# DIGITAL SYSTEMS

- Combinational systems

- Sequential systems

- Binary systems

-2.16-

#### SYSTEM

$$-\frac{\mathbf{u}}{\mathbf{w}} \longrightarrow \mathbf{I}_{\mathbf{u}} * \mathbf{I}_{\mathbf{w}} \longrightarrow \mathbf{0}_{\mathbf{x}} * \mathbf{0}_{\mathbf{z}} \longrightarrow \mathbf{z}$$

· inputs

u...w with value set I....I.

• outputs

$x_{1}...z$  with value set  $0_{x_{1}}...0_{z_{n}}$

· behaviour

-for every  $u \in I_u$ ,... $w \in I_w$  there is defined a  $x \in O_x$ ,... $z \in O_z$

$$\forall u \in I_{u}... \forall w \in I_{w} \exists x(u,..w) \in O_{x}$$

$$\forall u \in I_{u}... \forall w \in I_{w} \exists z(u,..w) \in O_{z}$$

-if input/output relation = function:

Function

$$F: I_{\mathbf{u}}^*, ... I_{\mathbf{w}} \rightarrow 0_{\mathbf{x}}^*, ... 0_{\mathbf{z}}$$

$(X,..Z) = F(U,..W)$  with  $u \in I_{\mathbf{u}}, ... w \in I_{\mathbf{w}}$

$\times \in O_{\mathbf{x}}, ... \times \in O_{\mathbf{z}}$

u,..w: <u>independent</u> variables x,..z: <u>dependent</u> variables -2.17-

# 2.3 Combinational, sequential and binary systems

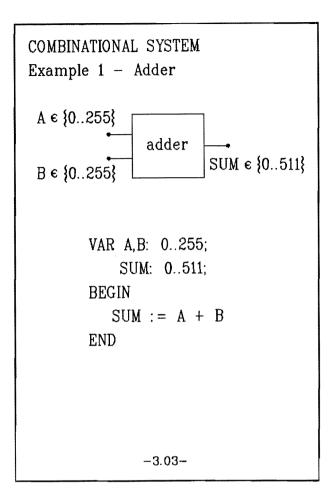

In the previous subsection we discussed the WHAT and HOW of digital system design, and we classified its internals as combinational, sequential and binary. Figure 2.17 shows what we mean by a system in this course. A system has inputs, u up to and including w, belonging to the value sets  $I_u$  up to and including  $I_w$ . Furthermore, it has outputs, x up to and including z, belonging to the value sets  $O_x$  up to and including  $O_z$ . The behaviour of such a system can be specified (defined) by a relation R. This relation R describes the relation between the input values and the output response. More formally, for all allowed input values there is at least one output value that is defined by the relation.

In this relation we consider all outputs at the same time. We can also look at every output separately. Hence, for each output, we get a relation that describes the connection between the input values and the values of the considered output. The system is described by a number of relations equal to the number of outputs. Both approaches are equally valid for our purposes. When the relation is a function (later we shall discuss what this means) we can write it in another style. We emphasize that the values of the inputs, u up to and including w, and the values of the output, x up to and including z, are defined by the system. There is a functional relation between the input and output values. We call the input and outputs of the system the variables of the system, u up to and including w are called the independent variables, and x up to and including z the dependent system variables.

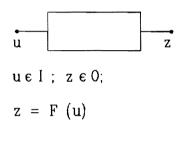

#### COMBINATIONAL SYSTEM

- No memory operation

- $F: I \rightarrow 0$  is a function

This means that the response of the system to the input values are only depending on the input values at that particular moment and <u>not</u> on earlier input values

-2.18-

As previously mentioned, there are digital systems with and without memory. We shall call a system without memory a combinational system. Figure 2.18 shows the attributes of a combinational system. A characteristic of such a system is that the input/output relation is time invariant. The response of the system to input values depends only to the current inputs and not to the previous inputs. That is to say, the system has no memory, i.e. it cannot remember. The functional description maps the input domain uniquely to the output value domain, i.e. each input value has one specific output value. Furthermore, the function is time invariant, i.e. the mapping does not change in time. and the system always exhibits the same behaviour.

Figure 2.19 shows two examples of combinational systems. In the first example, the input set is the set of days of the week and the output set is the set of "yes"/"no". the input/output relation is given by: "is x a weekday?". It is clear that the answer to this question depends on the current input value and does not depend on previous ones. Besides the answer tomorrow will be the same as today. In the second example the variable x may take the integer values from 0 to 15. The value of the output z is given by the "floor" of x/4. The floor function has a value equal to the greatest integer being smaller or equal to its argument. Thus, the floor of 3.14 is 3 and the floor of 6.73 is 6. The value domain of z is the subset of the integer numbers from 0 to 3. This is also a system without memory.

# SEQUENTIAL SYSTEM

- Memory operation

The system remembers the input values of the past

- There is no function F: I→0

Because the response is not only depending on the current input values but also on earlier input values

$$u \in I$$

$z \in 0$

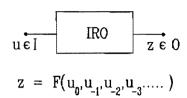

$z = F(u_0, u_{-1}, u_{-2}, u_{-3}, ... u_{-\infty})$

-2.20-

EXAMPLE - COMPUTATION OF AVERAGE

$$I = \{ 0 ... 15 \}$$

$$0 = \{ 0 ... 15 \}$$

$$F : z_0 = \lfloor (x_0 + x_{-1} + x_{-2} + ... + x_{-9})/10 \rfloor$$

$$z_0 \in 0 , x_i \in I$$

•  $x_{-1}$  ....  $x_{-9}$  are the nine previous input values

-2.21-

We shall call a system that has memory a sequential system. Figure 2.20 summarizes the characteristics of sequential systems. A sequential systems has a memory function, i.e. the system keeps track of previous input values. As a result, the input/output relation is not defined by a function. That is to say, the response not only depends on the current input values, but also on previous ones. A certain input value could lead to several different output values. Repeated dialling of a certain digit in a telephone number leads to changing responses from the telephone exchange. The telephone exchange remembers the previously dialled digits. In the case of sequential systems, there is a functional relation between the output z, and the current input value and all previous input values.

Figure 2.21 shows an example of a sequential system. This sequential system computes the running average of ten input values. The inputs may take integer values from 0 up to and including 15; the same holds for the outputs. The value of the output is equal to the average of the current input value and the previous nine input values. The average is rounded downwards using the floor function.

# BINARY SYSTEM

- Is a digital system

- Each input and output can have two values {0,1} or {False,True} or {No,Yes}

$$I = \{0,1\}^n$$

- is the input set or domain

- is a set of binary n-tuples

$$0 = \{0, 1\}^{m}$$

- is the output set or range

- is a set of binary m-tuples

-2.22-

## A BINARY SYSTEM

is simpler to realize than

a general digital system

# A DIGITAL SYSTEM

any <u>digital system</u> can be replaced

by an equivalent <u>binary system</u>

-2.23-

The binary system is a special and technically important digital system. Figure 2.22 shows some of its characteristics. A binary system is a digital system with the special characteristic that all input and output values may take only two different values. Thus every input and output is bivalent. This value set is generally given the symbols 0 and 1, false and true, real and unreal etc. In a binary system we limit the value domain of inputs and outputs. If the system has n inputs and m outputs we can say that (see figure 2.22) I is the input set of the function domain. I is formed by the set of all binary n-tuples. A binary n-tuple is a row of elements, where each element may take the values 0 or 1. Furthermore, we can define O as the output domain of the function. O is formed by the set of all binary m-tuples.

A number of advantages of binary systems are:

The input values are bivalent. For example, this can be realized by a high and low voltage, the absence or existence of current, a high or low resistance etc. We need only to distinguish between two levels.

- Because of that a binary system is easy to realize with electronic devices (building blocks). In the realization of such a system a large inaccuracy margin may be built in.

- A realization of a binary system has a high reliability.

- A realization of binary system has generally a good resistance against possible disturbances and other external influences.

Notice that all these advantages have an influence on the realized system. Binary systems are simpler to realize than general digital systems (see figure 2.23). The specification, however - the description of the desired behaviour of a digital system - is simpler for the more general digital systems. The reason is that such systems relate better to human reasoning.

For that reason an important assertion is (see figure 2.23): every digital system can be replaced by an equivalent binary system.

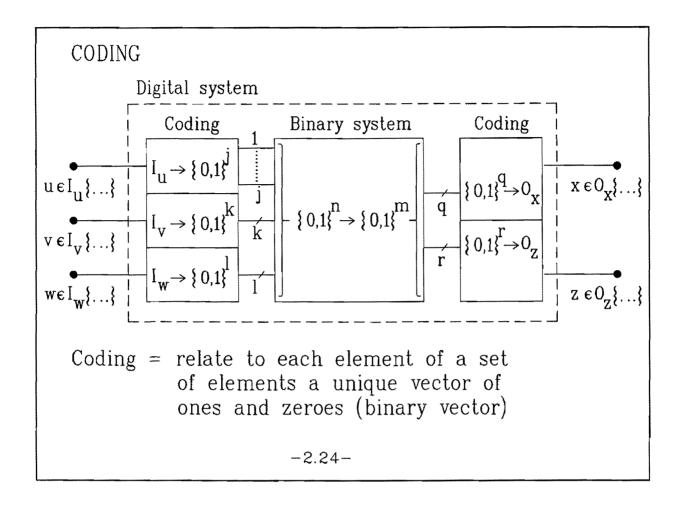

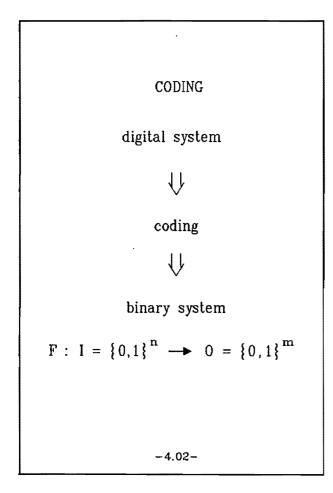

The process of translating a digital system into a binary one is called *coding*. Figure 2.24 shows a schematic of the coding process. Coding means that every element in a set of elements is mapped to a unique vector of zeroes and ones (a binary vector). In figure 2.24 we see that every input value is translated into a binary tuple by a coding step. All these tuples together provide the binary n-tuple input to the binary system; based on this input n-tuple the system determines the m-tuple output value.

This binary value is mapped by a second coding step to elements of the digital system's output set. This second coding step is also-called the decoding step. Actually coding is something that can be done by a digital system, more specifically a combinational system. Usually such a coding system is not explicitly realized.

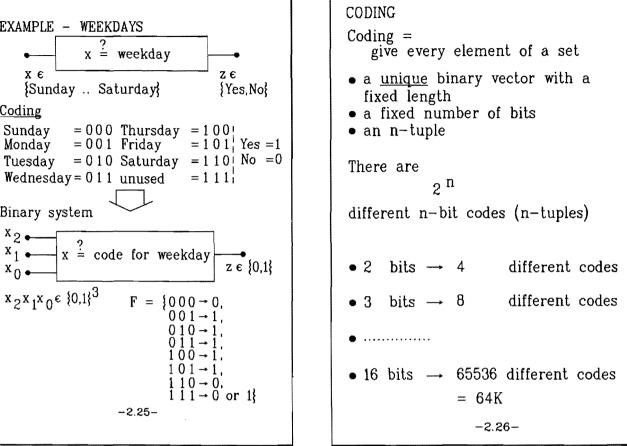

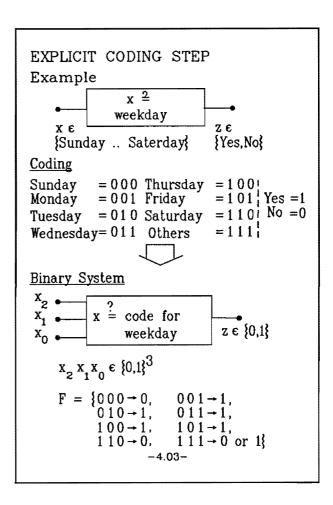

Figure 2.25 shows the first step in the process of realizing our combinational function: "Is x a weekday?". A coding step is necessary for the realization of a binary system. Figure 2.25 shows a possible coding scheme. The days of the week are coded as triples, i.e. binary vectors with three elements. Since we have three element that may take the values 0 or 1, we have eight different combinations, of which there is an unused code. In this case we use the 111 code for the element "others". Coding of the output values is simple: "yes" = 1, and "no" = 0. The equivalent binary system is given by a functional relation between the binary value on the output z and the binary values on the inputs  $x_0$  up to and including  $x_2$ . The function can be specified to give an output value for each corresponding combination of input values. This is shown in figure 2.25. Note that for the input combination 111 the output cannot be specified; indeed 111 does not correspond to a code for a day of the week, and thus there is no answer to the question: "Is this a code for a weekday?". Later we shall return to the issue of undefined output values.

Thus coding is: giving each element of a set a unique binary vector with a fixed length, i.e. a fixed number of elements. Each element of a binary vector is also-called a binary digit or "bit". Hence an n-tuple is called an n-bit vector. A bit (a binary digit) can have two values, 0 or 1. Thus, with n bits (binary n-tuple) we can make 2<sup>n</sup> different codes. There are four different code for two bits, and 65.536 codes for 16 bits. We also denote 65.536 by 64k, where k stands for  $2^{10} = 1024$ .

#### CODING

If a set S has #S elements:

- it can be coded using  $n = \lceil \log_2 \# s \rceil \text{ bits}$

- there are #S = 2<sup>n</sup> code words with in total

$$\Rightarrow \frac{(2^n)!}{(2^n - \#S)!}$$

different assignments

#### **EXAMPLE**

- 7 weekdays

- n =  $\lceil \log_2 7 \rceil = \lceil 2.8 ... \rceil = 3$  bits

- Number of different code assignments:

$$\frac{(2^3)!}{(2^3-7)!} = \frac{8!}{1!} = 40320$$

Given a value set that we want to code this question arises: how many bits do we need for this coding and in how many different ways can codes be assigned. Figure 2.27 answers this question. We want to code the value set S. The number of elements in the set is given by #S. In order to code with n bits, 2<sup>n</sup> must be at least equal to the number of elements. For that reason n must at least be equal to the "ceiling" of log<sub>2</sub>(#S). The ceiling function is the smallest integer grater than or equal to its arguments. With n bits we can make 2<sup>n</sup> different code words. There are #S code words necessary for the coding. Thus 2<sup>n</sup>-#S code words remain unused. Figure 2.27 shows how many different ways we can deduce #S code words from 2<sup>n</sup> code words. These are the different possible code assignments.

#### Problem 2.1 (2.6)

Consider coding the set of integer numbers {0..99}

- a. How many bits are needed for coding this set?

- b. How many code words are unused for this coding scheme?

- c. How many different coding schemes can be employed?

- d. How many elements can a set have at a maximum to enable coding with the indicated number of bits?

- e. How many coding schemes can be employed for (d)?

From the numeric example in figure 2.27 we see that the number of possible codes increases rapidly with n. Our seven days of the week can be coded in more than 40,000 different ways. Now the question is: are these codes equally optimal, equally good? The answer to this question is certainly *no!*. The definition of what is a good code depends on a number of factors:

- The used code must lead to a simple realization. The code must be optimal with relation to costs, reliability and availability for realization purposes.

- The used code is depending on the operation (transformation) carried out on the binary data and is depending on the way these operations are realized.

- Sometimes the use of the code is defined by an agreement, convention, or some used standard. So any two related subsystems must use the same code.

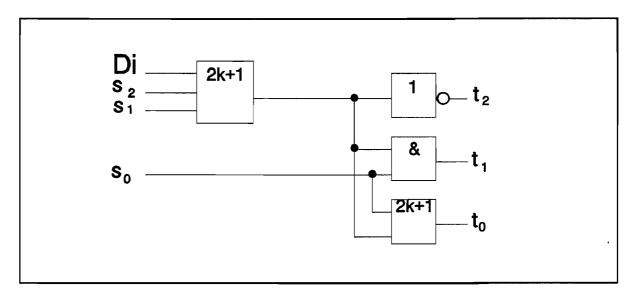

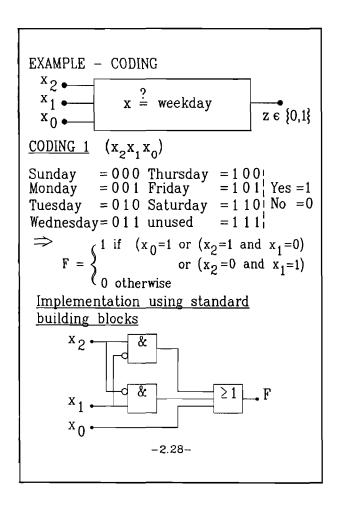

Figure 2.28 shows another possible coding scheme for our weekday function. We have previously specified the related binary function (see figure 2.25). We see that the output F=1 if  $x_0=1$  (Monday, Wednesday, and Friday) or  $x_2=1$  and  $x_1=0$  (Thursday, and Friday) or  $x_2=0$  and  $x_1=1$  (Thursday and Wednesday). Otherwise the function value equals 0. Later we shall see that this function can be realized with three standard building blocks, as shown in figure 2.28. Here we use two building blocks to realize the "and" functions. These are indicated with the & sign. A second building block is used for the realization of the "or" function. This is indicated by the  $\ge 1$  sign.

#### Problem 2.2 (2.7)

Consider the set {Spades, Hearts, Diamonds, Clubs}.

- a. How many bits are needed for coding this set?

- b. How many different coding schemes are possible?

- c. Specify all possible coding schemes.

- Are all of them really different?

- Is there an essential difference between codes 01 and 10? (Remark: no weights are assigned to the individual bits).

- If there is no difference: specify the number of different coding schemes.

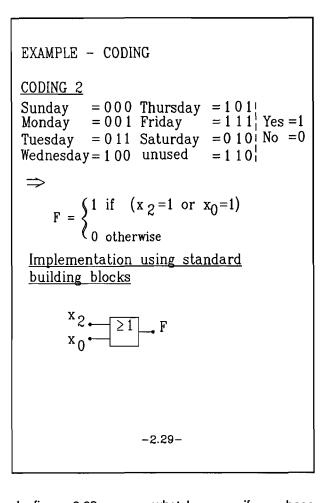

In figure 2.29 we see what happens if we chose another code for our function. The codes for the days of the week are chosen on purpose so that the function could be realized simply, i.e. with a minimal number of building blocks. We see that we have to deal with the code of a weekday if  $x_2 = 1$  or  $x_0 = 1$ . This function could be realized with only one standard building block: the "or" function. We conclude that the choice of a code may have a clear influence on the complexity of the realization.

How do we chose a good code? In general this is a very difficult question; there are many possible different codes. Next it is always not clear what a good code is. In this course we shall not pay any further attention to the choice of optimal codes. However, we shall notice that a (defacto) standard code is frequently prescribed. Often the standardized ISO or ASCII codes (ASCII = American Standard Code for Information Interchange) are applied when coding the set of alphanumeric characters (letters, digits, dialectical signs etc).

|                                                                                                                      | ISO<br>obb<br>'65                                                                                               | 7 -                | ASC                | II co             | ode                             | table            | <del>)</del>                                    | • • • • • • • • • • • • • • • • • • • • |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------|--------------------|-------------------|---------------------------------|------------------|-------------------------------------------------|-----------------------------------------|--|--|--|

| hhhh□                                                                                                                | 000 001                                                                                                         | 010                | 011                | 100               | 101                             | 110              | 111                                             |                                         |  |  |  |

| 0000 N<br>0001 S<br>0010 S<br>0011 E<br>0100 E<br>0110 A<br>0111 B<br>1000 I<br>1010 I<br>1011 S<br>1100 I<br>1101 S | UL DLE OH DC1 STX DC3 CTX DC3 COT DC4 CNQ NAK CK SYN BEL ETB BS CAN HT EM LF SUB VT ESC FF FS CR GS SO RS SI US | SP:" #\$%&, ()* +/ | 0123456789 <   > ? | @ ABCDEFGHIJKLMNO | P Q R S T U V W X Y Z [ \ ] \ - | abcdef ghijklmno | pqrstuvwxyz~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |                                         |  |  |  |

| -2.30-                                                                                                               |                                                                                                                 |                    |                    |                   |                                 |                  |                                                 |                                         |  |  |  |

Figure 2.30 gives an overview of this code. We see that it contains 128 different characters. The first 31 characters are the so-called control characters. They do not belong to the set of printable characters, but are used to control printers and similar devices.

There we also find codes for moving to the following line, and to place the print-head at the beginning of the line. Furthermore, we find a large number of printable characters, e.g. the digits 0 to 9 and all 26 letters of the alphabet in upper and lower case.

BCD - CODE

- BCD = Binary Coded Decimal

- BCD code is a weighted code

BCD coded numbers:

- Simple conversion from/to decimal digit symbols

- · Many bits needed

- 4-digit BCD number:

- 0000-9999 - range

- bits used 4\*4 = 16

- $2^{16} = 65536$  combinations - 16 bits

- 8-digit BCD number:

- range  $0 10^8$  bits used 8\*4 = 32

- 32 bits

range 0 - 4\*10<sup>9</sup> binary

• Operations on BCD numbers (+,-,\*./) are not trivial for binary systems

-2.32-

Another frequently used standard code is the BCD code. BCD stands for Binary Coded Decimal. These codes can be used to code decimal digits into numbers. Figure 2.31 gives an overview. The BCD code is a weighted code. That is, each individual bit position is associated with a weight factor. In the BCD code these weights are, from right to left,  $2^0 = 1$ ,  $2^1 = 2$ ,  $2^2 = 4$ , and  $2^3 = 8$ . Using these weight factors we can calculate the decimal equivalent of a BCD coded digit. This is done by multiplying each bit value (0 or 1) by the corresponding weight factor, and then summing up all the results. Numbers can be coded into BCD by translating each individual digit into its equivalent BCD code.

Figure 2.32 shows how to code the number 1994. We see how individual digits are translated into a 4bit BCD code.

The conversion between BCD coded numbers and decimal numbers is simple. In reality BCD code has some disadvantages. First we name the small domain. We need 4x4 = 16 bits to code a number with four decimal digits, i.e. 0..9999. But as earlier 16 bits provide 65,536 mentioned possibilities. Thus the numbers 0 to about 65,000 can be coded in 16 bits. When considering eight digits the difference between BCD coding and the number of different codes becomes much larger. A second disadvantage of BCD codes is that the standard operations on numbers such as addition, subtraction, multiplication and division of BCD coded numbers are not easy to realize in a binary system. Consequently binary numbers often constitute a better choice.

Numbers

and

Number Systems

-2.33-

#### NUMBER SYSTEMS

#### A number

- has a value

- uses a notation

- uses a number system

# Examples - notation

• decimal

1994

Roman

MCMXCIV

• floating point

1.994 \* 10

binary

111111001010

# Number system

- base (radix) R

- R digit symbols having values 0, 1, 2, .... R-1

-2.34-

#### 2.4 Numbers and number systems

Now, we shall briefly overview numbers and how they can be represented. We shall consider number systems. We must remember that a number has a value, and besides that, has a notational form or way of representation. The value of a number is fixed; the method of writing it mostly depends on the number system in which this value is given. Figure 2.34 demonstrates this by displaying a specific number, 1994, in four different ways. First we see the familiar decimal representation.

Next, the same number is shown as the Romans would write it using the Roman digit symbols. The next representation is given in the so-called floating point notation. And finally we have the binary representation of the number. Each notation has a set of conventions, or rules that are used to calculate the value of the number. Such a set of conventions or rules is called a number system. A number system is formed by a base or radix with a value R, and in total R digit symbols with values 0, 1, 2, .. R-1, respectively.

# Number systems

Decimal number system

$\bullet R = 10$

$\bullet d_i \in \{0, 1, 2, 3, 4, 5, 6, 7, 8, 9\}$

• notation : 1994• value =  $1*10^3 + 9*10^2 + 9*10^1 + 4*10^0$

Binary number system

$\bullet R = 2_{10}$

$\bullet$  d;  $\varepsilon$  {0,1}

notation:

• notation: 10011• value =  $1*2^4 + 0*2^3 + 0*2^2 + 1*2^1 + 1*2^0$

Hexadecimal number system

$\bullet R = 16_{10}$

• d<sub>i</sub> ∈ {0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F}

• notation:

• notation: 9EA3• value =  $9*16^3 + E*16^2 + A*16^1 + 3*16^0$

-2.35-

Figure 2.35 shows some examples of number systems. The first example is the decimal system. In this system the base value (radix) is 10. The digit symbols are formed by the digits 0 to 9. Also we see how the value 1994 is denoted in the decimal system. The value can be computed by considering each digit position as coupled to a weight factor. The rightmost digit has the weight 10°, the next digit has a weight factor 101, then 102, and finally the weight factor 103. The weight factor is thus a power of the base.

In the binary number system the base is equal to 2. The digits are formed by the symbols 0 and 1. A binary number is formed by a row (n-tuple) of binary digits, or bits. Figure 2.35 shows an example of a binary number. The value of a binary number can be defined by multiplying the individual binary digits by the corresponding weight factors, and then summing up the results. The weight factors are, once more, powers of the base, i.e. powers of 2. Figure 2.35 shows this value computation, expressed in the decimal system. A third important number system is the hexadecimal system or the 16-digit system. In this system the base value is 16. The digit symbols are now formed by the digits from 0 to 9 and, because we need 16 symbols, the letters from A to F. The symbols A to F have the values 10 to 15, respectively. Figure 2.35 shows an

# NOTATION AND VALUE

Number notation

n-tuple of digit symbols  $d_{n-1} d_{n-2} \dots d_2 d_1 d_0$

d, ∈ {digit symbols}

Number value

value =

$$\sum_{i=0}^{n-1} d_i * R^i$$

$$= d_{n-1}R^{n-1} + d_{n-2}R^{n-2} + ... + d_2R^2 + d_1R^1 + d_0R^0$$

-2.36-

example of the notational form and the value computations expressed in the decimal system.

Figure 2.36 shows that the notational form of a number is an n-tuple of digit symbols, each of these digit symbols being selected from the set of R (Radix) digit symbols. The value of a number is defined by the weighted sum of all digit symbols, the weight factor being a power of the base. We notice that the determination of this value (the calculation of the weighted sum) can be performed in different number systems. Because we humans find it easier to calculate in the decimal system, we determine its value generally computations in decimal. In a computer it is easier to use a binary system.

Hence the use of different systems gives different notational forms for the same number. We are interested in methods to convert a number from one notational form to another, preserving its value. There are two available methods. The methods we use depend on:

- the number system in which the calculation will be executed;

- the original number system in which the number is represented;

- the target number system in which we want to represent the number.

#### NUMBER SYSTEM CONVERSION

Base x → base 10

• Computation in decimal

• Method: repeated multiplication

Number value =

$$(...(d_{n-1}*R+d_{n-2})*R+...+d_2)*R+d_1)*R+d_0$$

Example - binary to decimal

$$1010_2 = ((1*2+0)*2+1)*2+0 = 10_{10}$$

$$110110_2 = ((((1*2+1)*2+0)*2+1)*2+1)*2+0 = 54_{10}$$

Alternative method:

$$110110 = 1 * 2^{5} + 1 * 2^{4} + 0 * 2^{3} + 1 * 2^{2} + 1 * 2^{1} + 0 * 2^{0}

= 32 + 16 + 4 + 2 = 54_{10}$$

Example - hexadecimal to decimal

$$9EA3 = ((9*16+14)*16+10)*16+3 = 40611_{10}$$

$$7CA = (7*16+12)*16+10 = 1994_{10}$$

Alternative method:

$$7CA = 7 * 16^{2} + 12 * 16^{1} + 10 * 16^{0} = 1792 + 192 + 10 = 1994_{10}$$

$$-2.37 -$$

#### Problem 2.3 (2.4)

Consider the binary number system using n bits for the representation of numbers.

- Show that the greatest value that can be represented is:

2<sup>n</sup> 1

- b. What is the greatest value for n=8?

- c. What is the greatest value for n = 16?

We apply repeated multiplications if the system we shall use for calculations and the target system are equal. Figure 2.37 shows an example of a conversion to the decimal system with the calculations also carried out in the decimal system. We begin by noting the value of the most significant digit symbol, i.e. the leftmost one. When there are more digits in the number, we multiply this decimal value with the base where this number is coded. This multiplication is carried out in the decimal system. Subsequently we add the result to the value of the following digit symbol. If there are more digits we repeat the whole procedure. The final result of this calculation is the value of the number in decimal. Figure 2.37 shows a number of conversion examples from the binary and hexadecimal systems.

NUMBER SYSTEM CONVERSION

Base 10  $\longrightarrow$  base x

• Computation in decimal

• Method: repeated <u>division</u>

• Determination of digits:

Digit 0 (rightmost digit):  $\left(\sum_{i=0}^{n-1} d_i \cdot R^i\right) \stackrel{\cdot}{\rightarrow} R = \sum_{i=1}^{n-1} d_i \cdot R^{i-1} \text{ remainder } d_0$ Digit k:  $\left(\sum_{i=k}^{n-1} d_i \cdot R^{i-k}\right) \stackrel{\cdot}{\rightarrow} R = \sum_{i=k+1}^{n-1} d_i \cdot R^{i-k-1} \text{ remainder } d_k$ Example - decimal to binary  $83 \stackrel{\cdot}{\rightarrow} 2 = 41 \text{ rem 1 least sign. bit}$   $41 \stackrel{\cdot}{\rightarrow} 2 = 20 \text{ rem 1}$   $20 \stackrel{\cdot}{\rightarrow} 2 = 10 \text{ rem 0}$   $10 \stackrel{\cdot}{\rightarrow} 2 = 5 \text{ rem 0}$   $5 \stackrel{\cdot}{\rightarrow} 2 = 2 \text{ rem 1}$   $2 \stackrel{\cdot}{\rightarrow} 2 = 2 \text{ rem 1}$   $2 \stackrel{\cdot}{\rightarrow} 2 = 1 \text{ rem 0}$   $1 \stackrel{\cdot}{\rightarrow} 2 = 0 \text{ rem 1 most sign. bit}$   $83_{10} = 1010011_{2}$ Example - decimal to hexadecimal  $2783_{10} \stackrel{\cdot}{\rightarrow} 16 = 173 \text{ remainder 15}$

remainder 13

remainder 10

#### Problem 2.4 (2.3)

10

Show that:

$173^{10} \div 16 = 10$

$2783_{10} = ADF_{16}$

$\div 16 = 0$

-2.38-

b.

$$01101100_2 = 108_{10}$$

The second method is applied if the number system used for the calculation is equal to the number system used to code the number. We make use of the method of repeated division. Figure 2.38 shows how to convert a number from the decimal system by means of calculations also executed in the decimal system. In this method of repeated division we divide the number by the base of the target number system. In figure 2.36 we see that if we perform such a division we keep a remainder that is equal to the value of the least significant, i.e. the rightmost, digit. If we divide the result again by the base of the target system then we get a remainder equal to the next digit. By repeating this division we translate all the digits of the number into the target system, starting with the least significant digit and ending with the most significant one. Figure 2.38 shows two examples: in the first example a number is converted into binary and in the second one into hexadecimal.

#

# Problem 2.5 (2.2)

Show that:

b.

$$99_{10} = 1203_4$$

c.

$$A7_{16} = 2213_4$$

$$d. 83_{16} = 2003_4$$

Binary systems will generally use numbers denoted in the binary system. A disadvantage of using binary numbers is that the number of digit symbols (bits) is large, even for relatively small numbers. We need ten digit symbols to represent the decimal number 1000. The advantage of the hexadecimal system is that it provides a very compact way of writing numbers, and at the same time, it is simple to convert hexadecimal numbers to and from the binary system. Hence hexadecimal numbers are frequently used as a short way of writing binary numbers.

#### Problem 2.6 (2.5)

- a. Write 10985<sub>10</sub> in the binary system.

- b. Write 278<sub>10</sub> in the base 5 number system.

Figure 2.39 discusses the conversion between binary and hexadecimal numbers, being a very simple one: a four bit binary number can be coded into a single hexadecimal digit. Indeed, with four bits we can have 16 different quadruples which can clearly be represented by the 16 digits of the hexadecimal system. If you wish you can verify this representation by converting the binary and hexadecimal numbers to the decimal system. The opposite way is also possible. A hexadecimal digit can always be written as a 4-digit binary number. And an n-bit binary number can be converted to (n/4)-digit hexadecimal number, beginning with the least significant bit, forming groups of four bits, and replacing these groups by the corresponding hexadecimal digit. Figure 2.39 shows a number of examples.

## BINARY ADDITION

Adding 2 bits:

$$0 + 0 = 0$$

$0 + 1 = 1$

$1 + 0 = 1$

$1 + 1 = 10$  (result=1; carry=1)

Adding with carry:

$$\begin{array}{rcl}

5_{10} & = & 101_{2} \\

3_{10} & = & 011_{2} \\

& & & & 111 \\

8_{10} & = & 1000_{2}

\end{array} + \begin{array}{c}

\text{(carry=1)}

\end{array}$$

-2.40-

## BINARY ADDITION

$$27_{10} = 011011_{2}$$

$$35_{10} = 100011_{2}$$

$$\frac{11}{62_{10}} + \frac{(carry)}{}$$

$$93_{10} = 01011101_{2}$$

$$47_{10} = 00101111_{2}$$

$$\frac{1111111}{140_{10}} + \frac{(carry)}{2}$$

-2.41-

We have now seen how to denote numbers in the binary system. The following step is to be able to calculate with binary numbers. In this course we shall limit ourselves to addition and multiplication of two positive binary numbers. When we learn to add in the decimal system we could start by adding two digits. Applying this to the binary system means adding two binary digits, i.e. two bits. Figure 2.40 shows the rules for adding two bits.

Regarding calculations in the decimal system, when adding two digits the result is sometimes too large to be represented in one digit. For example 9+7 gives 16. We say then 9+7=6 with a "carry" of 1. Something similar is valid for the binary system. We see that if we calculate 1+1 the result is 0 with a carry of 1. This carry is used when adding the next two digits in the number as shown in figure 2.40. There the carry from the last (right) two digits is explicitly shown.

Figure 2.41 shows another two examples. We recommend that you carefully study these two examples and that you practice with the addition of other binary numbers.

# Problem 2.7 (2.1)

Determine the sum of the binary numbers 011011 and 110110. What do you notice concerning the number of bits in the result?

## BINARY MULTIPLICATION

$$\begin{array}{c}

18_{10} \\

103_{10} \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

0 * 18 = 00000 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10010 \\

1 * 18 = 10$$

Multiplication by a power of 2

•  $*2_{10}$  = shift left 1 position:

$$d_{n-1} d_{n-2} \cdots d_{2} d_{1} d_{0} * 10_{2} = d_{n-1} d_{n-2} \cdots d_{2} d_{1} d_{0} 0$$

$$10110_{2} * 10_{2} = 101100_{2}$$

•  $*2^{n}_{10}$  = shift left n positions:  $1000_{2} * 1000_{2} = 1000000_{2}$

-2.42-

# NOT COVERED IN THIS COURSE

- Negative numbers

- Fractional numbers

- Floating point numbers

- Subtraction and division

- Finite register length

- Error detecting and error correcting codes

-2.43-

When considering multiplication in the binary system we could also look at related examples in the decimal system. Also in multiplication the multiplicand is successively multiplied by all digits in the multiplier starting with the least significant (i.e. the rightmost) digit. Now the digits of the multiplier have the value 1 or 0. The result of the multiplication is consequently the multiplicand itself or 0. As usual, the intermediate result is shifted one place to the left and then we add all these intermediate results. This gives the result of the multiplication. Figure 2.42 shows a worked out example.

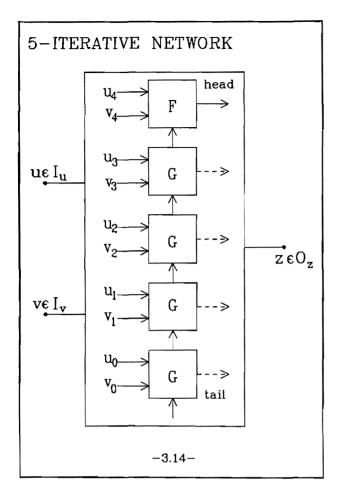

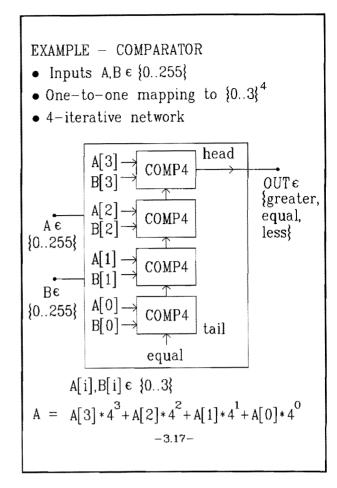

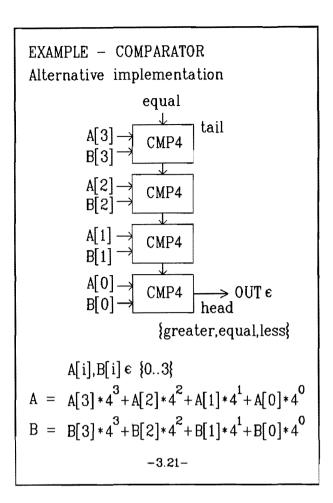

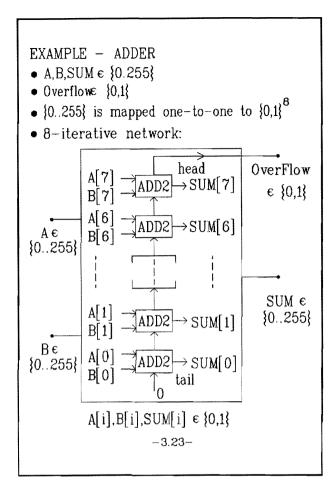

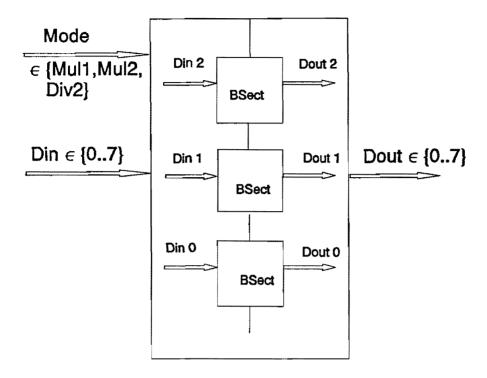

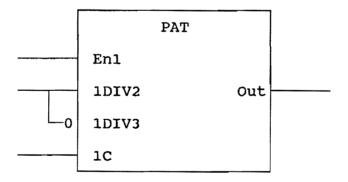

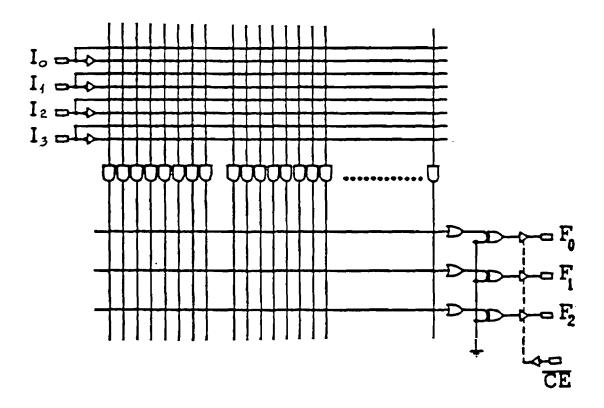

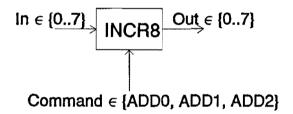

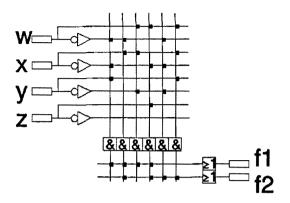

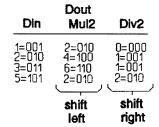

Furthermore we shall pay attention to a special attribute of binary multiplication. It appears that binary multiplication of a number by 2 is equivalent to shifting the binary number one position to the left and adding a least significant 0 to the right of the number. Figure 2.42 shows an example. We also observe that a multiplication by 2<sup>n</sup> (2, 4, 8, 16 etc.) means that the binary number is shifted to the left by n positions and the free positions are filled with zeros. These characteristics are frequently utilized in digital systems.