## Proceedings of the third workshop on computersystems

*Citation for published version (APA):* Withagen, W. J. (Ed.) (1991). Proceedings of the third workshop on computersystems: research forum on design, realization and the use of computersystems. Eindhoven University of Technology.

Document status and date: Published: 01/01/1991

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# Proceedings of the Third Workshop Computersystems Research forum on design, realization and use of computersystems

Edited by: W. J. Withagen Faculty of Electrical Engineering Eindhoven University of Technology Eindhoven, The Netherlands May 15 1991

#### CIP-GEGEVENS KONINKLIJKE BIBLIOTHEEK, DEN HAAG

#### Proceedings

Proceedings of the third workshop computersystems: research forum on design, realistation and use of computersystems. Eindhoven, 15 may 1991/ ed. by Willem Jan Withagen. -Eindhoven: University of Techonology, Faculty of Electrical Engineering. - Fig., tab. -Met lit. opg., reg. ISBN 90-6144-995-2 NUGI 832 Trew.: computersystemen. This workshop was the third in a serie of workshops organised by the research forum on design, realization, and application of **computersystems**. Currently the forum consists of researchers of four Dutch universities:

Delft University of Technology

Eindhoven University of Technology

University of Amsterdam

University of Twente

The forum also maintains a mailinglist to aid communication between the researchers. Submission of messages must be directed to:

#### system-network@duteca.et.tudelft.nl,

requests for inclusion or removal of this list should be directed to:

#### system-request@duteca.et.tudelft.nl.

Information about the forum can be requested from the university representatives:

Amsterdam Delft Eindhoven Twente Pieter Hartel<sup>a</sup> Hans Mulder Willem Jan Withagen Corrie Huijs

phh@ecs.soton.ac.uk hansm@duteca.et.tudelft.nl wjw@eb.ele.tue.nl chuijs@cs.utwente.nl

<sup>a</sup>Until 8/91 acting representative is Henk Muller, henkm@fwi.uva.nl

The copyrights of the papers included in these proceedings remain with the individual authors. The authors are encouraged to submit the papers to other (international) conferences or to journals.

Proceedings and conference information:

Program chairWillem Jan WithagenProceedings EditorWillem Jan Withagen

## Table of Contents

| Dalia: A Language for the description and Analysis of Digital Systems 1   |

|---------------------------------------------------------------------------|

| Henk van der Weij, Eindhoven University of Technology                     |

| Parallel Computers for Advanced Information Processing                    |

| E. Odijk, Philips Resach laboratories                                     |

| Parallel Discrete-Event Simulation                                        |

| Benno Overeinder, University of Amsterdam                                 |

| A Partitoning and Redundancy Model for Wafer-Scale Integrated Circuits 31 |

| Martin F. Beusekamp, University of Twente                                 |

| Efficient Implementation of High-Level Parallel Symbolic Languages        |

Mark Korsloot, Delft University of Technology

Henk van der Weij Eindhoven University of Technology Faculty of Electrical Engineering Digital Systems Section P.O. box 513, 5600 MB Eindhoven, The Netherlands

## Abstract

DALIA is a formal language for the description and analysis of digital systems at a behavioural as well as a structural level of abstraction. It is based on a functional style of programming, extended with annotations for indicating system structure, accessability, and signal flow direction. Program transformation rules are defined for rewriting DALIA descriptions to behaviourally equivalent alternatives. Since the same language is used for behavioural and structural descriptions, a smooth conversion between them can be made. The language is developed to be used as a formal basis for automated system design, adopting the following philosophy: First the (informal) requirements for the system to be designed are formalised in the DALIA notation. Next, the formal specification is stepwise transformed to a structural description of the system realisation (typically register transfer or gate level). The latter phase deals with formal descriptions and transformations, allowing a correctness by construction methodology.

## 1 Introduction

Nowadays, the technology to physically implement VLSI (Very Large Scale Integration) circuits has taken a lead on methods to correctly design them. This causes a need for formal design methods that can be automated and are able to manage the increasing complexity.

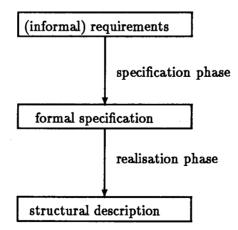

In this article, I will concentrate on a design method, and more specifically, a description language for digital systems. The design method adopted here consists of two main parts: a *specification phase* and a *realisation phase* (figure 1).

Figure 1: Design phases

#### Specification phase

In the *specification phase*, the informal requirements for a system to be designed are translated to a formal specification. This formal specification completely defines the system to be designed<sup>1</sup>. It is important to note that the specification phase can not (and will never be) fully automated. It can be computer-supported though, but the starting point will always be an informal idea.

#### **Realisation phase**

Once a formal description of the system to be designed has been obtained, its realisation can commence. The essence of the design methodology proposed here is, that this phase will be *completely formal*, and thus provable correct. The being formal of this phase does not induce that no human input is required; it only states that the actual transformation of the formal specification to a realisation is performed mechanically. The designer can 'guide' the process, and this will even be a necessity in the case of complex designs (which are the ones we want to deal with).

This translation of a 'high-level' description to a hardware structure is called *high-level* synthesis [5, 12].

#### 1.1 Digital system description

When adopting a *correctness by construction* design methodology, a well defined description language has to be chosen for the representation of digital systems. System descriptions in this language must be suited for algorithmic manipulation to enable automation of the design path, especially the realisation phase.

In this article, a language will be introduced for the representation of digital systems under design. For this language, a number of general requirements can be stated: it must be

- Implementation independent

- Hierarchical

- General

- Formal

- Automatically processable

Currently used languages do not fulfil all of these requirements. The hardware description standard VHDL [2] for example, which is directed towards practical system design, is really useful for describing and simulating digital systems, but hardly analysable in a formal way. This is due to the large number of constructs, and the fact that it is an imperative language. Apparently, a more formal basis is needed to fulfil the requirements stated above.

A more formal approach to the modelling of digital systems is the use of formalisms for the description of communicating processes like CCS [13] and CSP [8]. These languages however are not really suited for description of data processing at a logic level. Extensions have been made to make these formalisms more practical, like LOTOS [1, 9] which is an extension of CCS. The basic language however remains *action oriented*, which makes it difficult to integrate data structures, while maintaining analysability.

<sup>&</sup>lt;sup>1</sup>Theoretically, this means that the initial informal requirements can be forgotten. They do however provide non-functional, but useable information like design history and documentation

Higher-order logic is another approach to digital system description [7]. In higher-order logic, behaviour of a digital system is defined by predicates on its external lines. A circuit structure can be represented by the conjunction of predicates of the sub-circuits. Abstraction of the internal structure is accomplished by existential quantification over the internal lines [14]. Though the principle is very simple, a large class of systems can be described. A disadvantage is, that expressions tend to expand to large proportions when dealing with complex designs. Furthermore, it makes use of a discrete time model, whereas it would be desirable to abstract from time intervals (delay insensitive specification).

Another direction of research is toward description of digital systems using functional languages. The DALIA language also belongs to this class. Functional languages are easy to analyse, but not directly suited for structural description (like description of hardware architectures). In the next section, a closer look will be taken on the application of functional languages in hardware description.

### 2 Functional languages and hardware description

In a *functional language*, programs are described by means of functions. This essentially differs from the more common *imperative* approach, as used in languages like PASCAL and C. The imperative way of programming is induced by the one-word-at-a-time von Neumann concept, rather than by programmer demands [3]. In software development, the use of an imperative language can be somehow justified because of its easy implementation on conventional architectures. For the description of hardware however, imperative programming unacceptably limits the flexibility of the language.

Functional languages offer some advantages with respect to imperative languages. They are better analisable, and inherently capable of describing concurrency (arguments of a function can be evaluated in parallel). These are very desirable properties for a hardware description language.

As mentioned before, functional languages do not express structure which is a problem in case of translating a specification to a hardware architecture. This problem can be solved by changing the interpretation of function applications. For example, in [10, 15], tail recursion is interpreted as iteration, and infinite lists as signals. This solution however does not deal with another problem: the modelling of *bidirectional information flow*, a common concept in hardware designs. If this is to be handled in a formal way, other bases than pure functions have to be used like [4].

Another, more pragmatic approach is to add constructs for indicating structure like in SBL [6]. This is also the approach adopted for the design of DALIA, since it offers a basis for practical integration of the language in a hardware environment.

## 3 An informal introduction to DALIA

DALIA was designed by considering the most elementary characteristics of digital systems in general. The constructs of the language have been kept simple, in order to ease application of formal operations on system descriptions.

DALIA is able to describe system behaviour (formal specification) as well as system structure (architecture description). This makes it possible to use a single language as a description framework during the system design, avoiding conversion between different languages.

<sup>3&</sup>lt;sup>rd</sup> Computersystems Workshop, may 15 1991, Eindhoven.

In DALIA, digital systems are represented by interacting concurrent *processes*. A process is an abstract information processing entity that performs part of the function of the total system. Processes may contain subprocesses, so a hierarchical system structure can be used. Furthermore, operations called *dependencies* have been defined for modelling logic operations.

#### 3.1 Processes

Basically, a DALIA system description consists of a set of rules, defining the allowable transformations of the system. As a simple example, consider the following set of rules:

```

def (a OR 0) \rightarrow a

def (0 OR b) \rightarrow b

def (1 OR 1) \rightarrow 1

def (NOT 0) \rightarrow 1

def (NOT 1) \rightarrow 0

def (a NOR b) \rightarrow (NOT (a OR b))

```

These rules define the operations (functions) OR, NOT, and NOR. Expressions are evaluated by transforming them according to the given rules. An example of an evaluation is

$(1 \text{ NOR } 0) \rightarrow (\text{NOT } (1 \text{ OR } 0)) \rightarrow (\text{NOT } 1) \rightarrow 0$

By adopting appropriate evaluation conventions, it is also possible to describe hardware-like structures. For example, an OR gate can be described as

def (OR\_GATE a b x)  $\rightarrow$  (OR\_GATE a b (a NOR b))

Here a system is defined by a recursive definition. The system itself (NOR\_GATE) is just a parameter, with the property that it 'remains unchanged at the same position' when applying any of the rules. This is exactly the property of a hardware resource: it is an unchangeable part of the system.

To explicitly state that parts of the system are unchangeable, the *process concept* is introduced. A process also permits local variables and data transformation rules, thus hiding irrelevant information from the outside world. A system description in DALIA consists of a set of *process definitions*

system ::=

{ proc\_def }

In DALIA, processes are the means of structuring system descriptions. A process consists of three main parts:

- Interface

- Internal variables

- Behaviour description

Communication with a process takes place via the *interface*. The other parts of the process are invisible from the outside, hiding irrelevant details.

The *internal variables* determine the state of the process. The values of these variables can be changed by interaction of the process with its environment.

The description of the process' function is contained in the *behaviour definition*. Behaviour is defined by *data dependencies* between the variables of the process (interface and internal variables).

A variable will retain its value until it is overwritten, and reading variables is non-destructive. This provides a memory function, which reflects the register concept as known from hardware implementations.

As an example, the OR\_GATE is described by the following process:

```

def (OR_GATE a b x) =

[ { a ∈ ?bit, b ∈ ?bit, x ∈ !bit }

x = (a OR b)

]

```

or in expanded form:

```

def (OR_GATE a b x) =

[ { a \in ?bit, b \in ?bit, x \in !bit }

case (a b)

\in (bit 0) \rightarrow x=a

\in (0 bit) \rightarrow x=b

\in (1 1) \rightarrow x=1

endcase

]

```

Some additional notations have been introduced here, like assertions (enclosed by curly brackets), indicating type and direction of the interface variables, and a case construct. These will be discussed later.

Another important concept is the *subprocess*. The use of subprocesses is illustrated by the following process description of a NOR gate:

```

def (NOR_GATE a b x) =

[ var or_g = (OR_GATE bit bit bit);

{ a ∈ ?bit, b ∈ ?bit, x ∈ !bit }

or_g.a=a | or_g.b=b | x=(NOT or_g.x)

]

```

or using an additional subcomponent NOT\_GATE with its obvious meaning:

```

def (NOR_GATE a b x) =

[ var i,

or_g = (OR_GATE bit bit bit),

not_g = (NOT_GATE bit bit);

{ a ∈ ?bit, b ∈ ?bit, x ∈ !bit }

or_g.a=a | or_g.b=b | i=or_g.x |

not_g.a=i | x=not_g.x ]

```

Here subcomponents are referred to by variables, and the connection of components is defined by a list of assignments. The vertical bars stand for asynchronous composition (see section 3.3.3).

#### 3.2 Values

The values used in the language are symbolic. All values are either symbols or symbol trees. A symbol is denoted by an identifier, which will by convention consist of only upper-case characters or non-letter symbols. A symbol tree is a structure that contains a number of branches, that are in turn symbolic values. A tree is denoted by indicating its structure using round brackets. Some examples of symbolic values are

| SYM         | (symbol) |

|-------------|----------|

| 1           | (symbol) |

| (A (B C) D) | (tree)   |

Symbols do not have a predefined 'meaning'. For example symbol 1 is just another identifier for a symbol. An interpretation can be attached to a symbol only when operations on it are defined.

In DALIA, sets of symbolic values play an important role. They are used for specifying guards in conditional dependencies and for putting constraints on variables (typing). Sets will be denoted using normal set operators like  $\cup$ ,  $\cap$ , and  $\setminus$ . In the notation adopted here, no distinction will be made between symbols and sets containing only one symbol, to ease notation. For example,  $A \cup B \cup C$  denotes the set containing symbols A, B, and C.

#### 3.3 Data dependencies

The behaviour of a process is defined by its *dependencies*. Dependencies define how variables are related to each other. A process can be 'executed' by concurrent evaluation of its data dependencies.

Basically, there are two kinds of dependencies: assignment and conditional dependency, which can be combined using the asynchronous and synchronous composition operators.

#### 3.3.1 Assignment

The assignment attaches the value of an expression to a variable. It acts much like the normal assignment in imperative languages, but its interpretation differs because dependencies operate concurrently; it denotes how the current value of a variable is related to the current value of other variables in the system. The interpretation will become more clear in sections 3.3.3 and 3.3.4, where composition of dependencies is explained. An example of an assignment is

$\mathbf{x} = (\mathbf{a} \mathbf{b})$

which defines variable x to be equal to the combination of variables a and b.

#### 3.3.2 Conditional dependency

Conditional dependencies can be used for the definition of logic operations on symbolic data. In a conditional dependency, (part of) the state of a process and its interface is compared to a set of symbolic values, describing a set of states. Only those subdependencies in the conditional statement that are attached to a set containing the current value of the selector expression will be activated. For example,

```

case (a b)

\in (0 \ 0) \rightarrow x=1

\in (1 \ 1) \rightarrow x=0

endcase

```

denotes that the value of x will be 1 if both a and b are zero, and 0 if a and b are both equal to 1. Otherwise, this dependency does not affect x. Variables unaffected by dependencies will retain their current value.

#### 3.3.3 Asynchronous composition

With asynchronous composition, dependencies can be combined without specifying synchronisation between them. Evaluation of asynchronously combined dependencies is assumed to be 'fair': no statement is made about evaluation order of the dependencies or the time it takes to evaluate them, but eventually all dependencies will be evaluated. This assumption excludes the occurrence of *livelock*.

Though asynchronously combined dependencies are not time-related, they are allowed to share variables through which communication can take place. It is even possible to synchronise dependencies by using shared variables, but this is often circumstantial.

An example of asynchronous composition is the following:

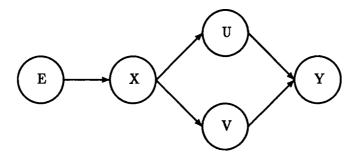

y=(u v) | u=x | v=x | x=E

Here u, v, x, and y denote variables, and E denotes a symbol. The corresponding dependency graph is shown in figure 2. Independently of which evaluation order is applied, the result of the evaluation will be the same: x, u, v, and y will be equal to E, E, E, and (E E) respectively.

Figure 2: Dependency graph

#### 3.3.4 Synchronous composition

For the synchronisation of dependencies, synchronous composition should be used. In an operational terminology: when evaluating two synchronously combined dependencies, first the result of evaluating both sides will be calculated, the combined result will be instantaneously applied on the state space. A synchronous combination can be compared to a *transition* in Petri nets [16]. It is used for introducing synchronisation points in the data-flow graph.

An example of synchronous composition is

x=y , y=x

Evaluation of this dependency will cause x and y to be 'swapped'. A dependency like this is only useful when placed within a conditional dependency, since otherwise x and y would be swapped infinitely which is unlikely to be desired. An example of such an embedded dependency is

```

case (x y)

\in (0 \ 1) \rightarrow x=y, y=x

endcase

```

#### **3.4** Assertions

For analysing descriptions, assertions can be inserted at various places in the process definitions. An assertion contains predicates on variables. By checking their consistency, processes can be searched for errors. Also, assertions provide information that can be used to transform processes (see section 4).

An example of an asserted dependency is

```

\{ x \in A \cup B \}

case x

\in B \cup C \rightarrow y=x

endcase

```

#### 4 **Process transformations**

A process transformation is a function that transforms a process description to a semantically equal alternative description [11]. To give an indication of the principle, consider the asserted conditional dependency of section 3.4. The assertion states that x is a member of set  $A \cup B$ . The condition within the case dependency specifies the case that x is a member of set  $B \cup C$ . From this, it can be derived that in this specific case x can never be equal to A nor to C. This means that C can be removed from the set specified in the case dependency.

```

\{ x \in A \cup B \}

case x

\in B \rightarrow \{ x \in B \} y=x

endcase

```

which in turn is semantically equal to

```

\{ x \in A \cup B \}

case x

\in B \rightarrow y=B

endcase

```

The result of these process transformations is a 'more simple' process, performing exactly the same function as the original one. This example illustrates just one of the applications of process transformations.

The aim is to formalise transformations like these, in order to automate the manipulation of process descriptions. For this, a formal definition of process transformations will be given:

**Definition 1** A process transformation is a function  $t: L \to L$  with  $\forall_{l \in L}(C(t(l)) = C(l))$ . Here L denotes the set of all possible process descriptions and  $C: L \to S$  a function that maps process descriptions on their semantics. S denotes the semantic domain of the description language.

In the definition above, S is not defined formally since this is out of the scope of this article.

From the definition, it follows that process transformations map descriptions in the language on other descriptions under invariance of behaviour. They can be used to manipulate descriptions in a provably correct way. Process manipulations can be used to correctly optimise systems, transform specifications to architecture descriptions, or prove equivalence between systems. When automating transformations, the risk of introducing errors will be decreased, since all formal steps are correct by construction.

#### 4.1 Primitive transformations

For transforming processes, definition 1 can be applied. It states that a process may be transformed to another process if their semantics are the same. This is however not a suitable approach for automating process manipulations. The problem is, that first a transformation has to be proposed, and only afterwards it can be proven correct. Clearly, such a trial-and-error approach is very inefficient.

So, in attempt to give 'direction' to process transformations, a set of *primitive process trans*formations will be derived from definition 1 and the semantics definition of the language. Complex transformations can be performed by repeatedly applying primitive transformations.

A primitive process transformation rule will be denoted in terms of an *attribute grammar* for the language. An attribute grammar [18] is a grammar definition, with attributes attached to its elements (terminals or non-terminals). Attributes describe properties of these elements that can not (or not easily) be described in terms of syntax. For example, a variable identifier may have an attribute attached to it, denoting its type. The value of the attributes can be derived from other attributes in the parse-tree of a program. Relations between attributes are defined by *attribution rules* attached to the syntax-definition rules.

A complete attribute grammar of the language will not be given here. Only attributes occurring in transformation rules will be explained. Transformation rules will be denoted as follows:

$struct_1 \leftrightarrow struct_2$ { condition }

Here  $struct_1$  and  $struct_2$  denote syntax expressions, and *condition* denotes a statement about the syntax elements and their attributes that has to hold for the equality to be true.

To achieve full processability of descriptions, the primitive rules must enable the conversion of any description to any of its semantic equivalents. This property is called *completeness* [17].

**Definition 2** A set of process transformations T is complete if and only if  $\forall_{l,m\in L}((C(l)=C(m))\Rightarrow \exists_{t\in T^*}(t(l)=m))$

Here  $T^*$  denotes the collection of functions that can be constructed by composing primitive transformations (i.e. any sequence  $t_0 \circ t_1 \circ \cdots \circ t_n$  with  $t_i$  a primitive transformation).

It is not self evident that such a set of primitive transformations exists, but an attempt has been made to construct a powerful set, able to accomplish many process transformations. Transformations that can not be performed will have to take place using definition 1: by proposing a new process and proving it equivalent using the formal semantics definition of the language.

#### 4.2 A set of primitive transformations

In the scope of this article, it is not possible to show all primitive transformations defined yet. Some important ones will be highlighted next.

#### 4.2.1 Commutativity

These rather obvious transformations can be described as follows:

$dep_1 \mid dep_2 \leftrightarrow dep_2 \mid dep_1$  $dep_1 , dep_2 \leftrightarrow dep_2 , dep_1$

That these transformations are valid is clear, since the compositions are in parallel, so no evaluation sequence is specified.

#### 4.2.2 Synchronisation

This transformation can be used to introduce or remove synchronisation between dependencies:

$\begin{array}{l} dep_1 \mid dep_2 \leftrightarrow dep_1 \ , dep_2 \\ \{ \ dep_1.uses \cap dep_2.affects = \emptyset \\ \land \ dep_2.uses \cap dep_1.affects = \emptyset \\ \} \end{array}$

This definition states that synchronisation may be removed or inserted if the dependencies involved do not make use of variables the other one may change. Here attribute *uses* contains the variable identifiers referred to in the dependency, and *affects* contains the identifiers of variables that are affected by evaluating the dependency.

An example of a derivation using this transformation is the following:

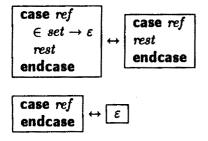

#### 4.2.3 Condition calculus

Several rules are defined that deal with conditional dependencies. Some important ones will be shown here.

One of the most important rules deals with the propagation of conditions from the context into conditional dependencies:

| $\{ ref \in S \}$ | ↔ | $\{ ref \in S \}$ |

|-------------------|---|-------------------|

| case ref          |   | case ref          |

| $\in set$         |   | $\in set \cap S$  |

| $\rightarrow dep$ |   | $\rightarrow dep$ |

| rest              |   | rest              |

| endcase           |   | endcase           |

The next rule states that dependencies can be removed if they will never be active ( $\varepsilon$  denotes the empty dependency):

$$\begin{cases} state \in \emptyset \\ dep \end{cases} \leftrightarrow \begin{cases} state \in \emptyset \\ \varepsilon \end{cases}$$

Here state denotes the collection of all variables within the scope of the process.  $\varepsilon$  denotes the empty dependency.

These two rules can also be denoted using an attribute *cond* attached to each dependency. This attribute specifies the states in which the dependency may be activated. The notation using the assertion has been used since it is better readable.

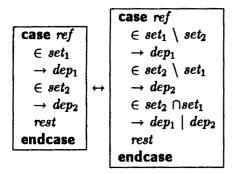

The next rules deal with the removal of parts of the case dependency:

A rule for creating mutually exclusive cases is the following:

#### 4.2.4 Other transformations

It is not possible to present all rules defined yet. Other rules take care of operations like

- Removing assignments to unused variables

- Removing declarations of unused variables

- Substitution of defines

- Expansion of subprocesses

- Substitution of variables

In the next section, a sample system description will be transformed, illustrating the use of process transformation.

#### 4.3 An example

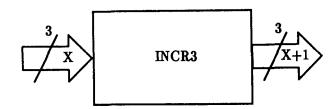

As a simple example to illustrate the use of process transformation, the design of a 3-bit wide incrementor will be shown (figure 3).

First, the top level of the system will be defined:

**Figure 3: Incrementor**

The function of the incrementor has been specified by using a universal increment function defined on integer values. The data types (actually sets) used here and in the rest of this example are defined as

def int = ZERO  $\cup$  (int bit) def ZERO = (ZERO 0) def bit = 0  $\cup$  1 def int3 = (((ZERO bit) bit) bit)

The values modelled by elements of these sets are defined as follows:

```

val((r b)) = 2val(r) + bitval(b)

val(ZERO) = 0

bitval(0) = 0

bitval(1) = 1

```

The definition of ZERO is unusual, since it can be rewritten only by using ZERO again. This is however no problem, because its value is well determined (0). When evaluating dependencies that make use of ZERO, it will be evaluated only if required.

Function INC can be defined as follows:

```

def (INC x) =

[ { x \in int }

case x

\in (t:int 0) \rightarrow (t 1)

\in (t:int 1) \rightarrow ((INC t) 0)

endcase

]

```

With this last definition, the system has been completed. Expansion can now start by substituting the INC function in INC3. By evaluating the initial assertions (in  $\in$  int3, out  $\in$  int3), consistency of the system can be checked. After some transformations, the result is

```

def (INC3 in out) =

[ { in \in int3, out \in int3 }

case in

\in (t:int 0) \rightarrow out = (t 1)

\in (t:int 1) \rightarrow { t \in ((ZERO bit) bit) }

out = ((INC t) 0)

endcase

]

```

By successively substituting INC and expanding the case statements, eventually the following dependency (in some form) can be derived:

```

case in

∈ (((ZERO 1) 1) 1) →

out=((((ZERO 1) 0) 0) 0)

endcase

```

This causes an inconsistency in the assertions since it was stated that out  $\in$  int3, and

```

\begin{array}{ll} ((((ZERO 1) 0) 0) \cap int3 & = \\ ((((ZERO 1) 0) 0) \cap (((ZERO bit) bit) bit) & = \\ ((((ZERO 1) \cap ZERO] 0) 0) 0) & = \\ (((((ZERO 1) \cap (ZERO 0)] 0) 0) 0) & = \\ ((((ZERO [1 \cap 0]) 0) 0) 0) & = \\ ((((ZERO \emptyset 0) 0) 0) 0) & = \\ \emptyset \end{array}

```

This result indicates that an error has been made in the specification. This is indeed the fact, since the increment of 7 is 8, requiring 4 bits in binary representation. By reconsidering the initial requirements, it can be decided to 'throw away' the most significant bit or define a four bit wide output in the system specification.

#### 5 Architecture mapping

The eventual purpose of the description and analysis language is the actual realisation of digital systems. A realisation may be a software program, but the accent of the description language is on hardware synthesis.

For translating a system description to a hardware architecture, the processes in the description have to be mapped on *resources*. These resources may be gate-level components or more complex building blocks like ALU's, memories, or even microprocessors. Within the language, it is possible to create a model of an architecture, by modelling each resource as a process and specify the connections between these resource processes by assignments.

The processes occurring in a hardware description are bound to some restrictions that are inherent to hardware implementation. For example, data types must be finite and no recursion or process creation is allowed. If the original description does contain these 'unimplementable' constructs, they have to be converted. This can be done by evaluating the constraints, that give a definition of what the process is to expect as its input. By eliminating redundant parts of constrained processes (like non-occurring data values or recursion), a finite structure may be obtained. If not, the system is either unimplementable, or the wrong decisions have been made

during its analysis, leading the transformation to a dead point. This points out the necessity of human intervention during the design.

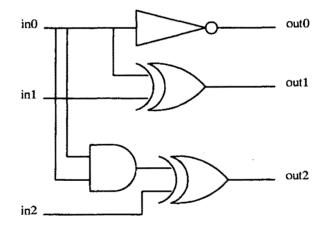

An architecture description of the incrementor example of section 4 is

```

def (INC_REAL in2 in1 in0 out2 out1 out0) =

[ { in2 ∈ ?bit, in1 ∈ ?bit, in0 ∈ ?bit,

out2 ∈ !bit, out1 ∈ !bit, out0 ∈ !bit }

var i=(NOT_GATE bit bit),

a=(AND_GATE bit bit bit),

x1,x2=(XOR_GATE bit bit bit);

var n;

i.in=in0 | out0=i.out |

a.in1=in0 | a.in2=in1 | n=a.out |

x1.in1=in0 | x1.in2=in1 | out1=x1.out |

x2.in1=n | x2.in2=in2 | out2=x2.out

]

```

The interface has been slightly changed for reasons of readability. Figure 4 depicts the described architecture.

Figure 4: Increment realisation

## 6 Conclusions and further research

The language proposed here seems suited for the formal processing of digital system descriptions, which makes it possible to use it as a basic representation method for an automated design system. Though for complex systems it is difficult, if not impossible, to fully automate hardware synthesis from a given specification, the language may prove to be useful in offering a formal design framework. This framework is capable of guaranteeing correctness of all design steps, whether taken autonomously by the system or by the designer.

Further research will concentrate on automatic decision making. An 'expert system' layer controlling the language framework will store information from previous designs and apply heuristic searching techniques to take standard design steps or generate design proposals for

the designer. It is not likely that fully automatic system design is possible in the near future, but new methods will certainly ease the designers' task.

#### References

- [1] LOTOS: Language for the temporal ordening specification of observational behaviour, international standard ISO/IS 9074, 1987.

- [2] IEEE standard VHDL language reference manual, 1988.

- [3] John Backus. Can programming be liberated from the von neumann style? a functional style and its algebra of programs. In *Communications of the ACM*, pages 613-641, August 1978.

- [4] Raymond T. Boute. The beta calculus: Scoping and substitution in formal descriptions of systems with bidirectional information flow. Technical Report 92, University of Nijmegen, 1986.

- [5] Raul Camposano and Wolfgang Rosenstiel. Synthesising circuits from behavioral descriptions. In Transactions on Computer Aided Design, pages 171–180. IEEE, February 1989.

- [6] Ganesh C. Gopalakrishnan, David R. Smith, and Mandayam K. Srivas. An algebraic approach to the specification and realisation of VLSI designs. In Computer Hardware Description Languages and their Applications, pages 16-38. IFIP, August 1985.

- [7] Mike Gordon. Why higher-order logic is a good formalism for specifying and verifying hardware. In Formal Aspects of VLSI Design, pages 153-177, 1986.

- [8] C.A.R. Hoare. Communicating Sequential Processes. Prentice-Hall International Series in Computer Science. Prentice-Hall, 1985.

- [9] Dieter Hogrefe. Estelle, LOTOS und SDL: Standard-Specifikationssprachen für Verteilte Systeme. Springer-Verlag, 1989.

- [10] Steven D. Johnson. Synthesis of Digital Designs from Recursion Equations. ACM Distinguished Dissertations. MIT Press, 1984.

- [11] Carlos Delgrado Kloos and Walter Dosch. Transformational development of digital circuit descriptions: a case study. In Compeuro Conference on VLSI and Computers, pages 319– 322. IEEE, May 1987.

- [12] Michael C. McFarland, Alice C. Parker, and Raul Camposano. Tutorial on high level synthesis. In Design Automation Conference, pages 330-336. ACM/IEEE, June 1988.

- [13] R. Milner. A Calculus of Communicating Systems. Lecture Notes in Computer Science. Springer-Verlag, 1980.

- [14] Ben Moszkowski. Executing Temporal Logic Programs. Cambridge University Press, 1986.

- [15] John T. O'Donnell. Hardware description with recursion equations. In Computer Hardware Description Languages and their Applications, pages 363-382. IFIP, April 1987.

- [16] James L. Peterson. Petri net theory and the modeling of systems. Prentice-Hall, 1981.

- [17] Ranga Vemuri. How to prove the correctness of a set of register level design transformations. In Design Automation Conference, pages 207-212. ACM/IEEE, June 1990.

- [18] William M. Waite and Gerhard Goos. Compiler Construction. Text and Monographs in Computer Science. Springer-Verlag, 1984.

## Parallel Computers for Advanced Information Processing

ir E. Odijk Philips Natuurkundig laboratorium P.O. box 80.000, 5600 JA Eindhoven, The Netherlands e-mail: odijk@prl.philips.nl

### Abstract

Within the Computer Architecture Department of Philips Research Laboratories Eindhoven, a five years research effort has resulted in the design and implementation of a parallel objectoriented computer system, POOMA, and a parallel object-oriented language to express programs for execution on this system.

Conceptually, POOMA is a distributed-memory, scalable, computer that consists of selfcontained computers, each with their own cpu, main memory and a communication unit. These computers communicate via a sparsely connected, packet-switching, topology of bidirectional communication links that are serviced by the communication unit.

The architecture (which is understood to denote the functionality as implemented by both the hardware and systems software) has been designed to meet the requirements of the parallel object-oriented language, and the match of the conceptual and operational models can be well demonstrated.

The presentation will include a survey of the systems concepts, the rationale of a number of the design choices and an informal presentation of the lessons that have been learnt during the design.

#### Contents

The contents of the article is printed in a separate handout. It is a copy of the publication in IEEE micro of december.

## Parallel Discrete Event Simulation

Benno Overeinder

Bob Hertzberger

Peter Sloot

Department of Computer Systems University of Amsterdam Kruislaan 403, 1098 SJ Amsterdam, The Netherlands e-mail: overeind@fwi.uva.nl

## Abstract

In simulating applications for execution on specific computing systems, the simulation performance figures must be known in a short period of time. One basic approach to the problem of reducing the required simulation time is the exploitation of parallelism. However, in parallelizing the simulation new problems arise. Due to the distributed generation of events causality errors can occur, as a result the sequence in which to process the events is essentially indeterminated.

In this paper we present a model to analyse the inherent parallelism of a simulation, together with a survey of existing strategies to perform the simulation in parallel. Some extensions to this model are discussed, resulting in reliable evaluation of the effectiveness of these strategies.

#### **1** Introduction

In the Parallel Scientific Computing Working-group at the University of Amsterdam, we are interested in the execution performance of classes of applications on classes of computing systems. We distinguish the following levels that are involved in performance prediction: application, general abstract machine, simulation language, and discrete event simulator. Each level is supported by the level underneath. In this way the efficiency of a level is partially determined by the supporting level, thus imposing severe constraints to the simulator. Especially if the performance figures are iteratively used to optimize the application, the effectiveness of the simulator is of vital importance.

Large discrete event simulations are known to consume enormous amounts of time on sequential machines. One basic approach to reduce the required simulation time is the exploitation of parallelism. A major drawback however, is the inherent complexity of this type of simulation since the notion of global time does not easily map on a parallel computer. Sophisticated clock synchronization algorithms are required to ensure that cause-and-effect relationships are correct reproduced by the simulator.

The idea of parallel simulation—in literature also indicated by distributed simulation—was first proposed by K.M. Chandy and independently by R.E. Bryant. Papers by Chandy and Misra [Cha79], and Bryant [Bry77] contain basic ideas of parallel simulation, the problem of deadlock and schemes for deadlock resolution, detection and recovery [Cha81]. Alternative schemes proposed by D.R. Jefferson are based on the concepts of Virtual Time [Jef85].

This paper is structured in the following way. Section 2 gives an introduction to discrete event simulation. In section 3 a parallel view to the sequential simulation is proposed, and various methods for parallel simulation are described together with a discussion on their effectiveness. Finally, in section 4 an evaluation of these methods and some suggestions for further research are presented.

B. Overeinder: Parallel Discrete Event Simulation.

## 2 Concepts of Discrete Event Simulation

Modelling and simulation can be characterized as the complex of activities associated with constructing models of real world systems and simulating them on a computer.

Essential to every model is the time base on which events occur. Accordingly, models can be classified depending on their temporal behaviour [Zei76]. A model is a *continuous time* model when time flows smoothly and continuously. A model is a *discrete time* model if time flows in jumps of some specified time unit.

A second classification can be based on the range sets of a model's descriptive variables. The model is a *continuous state* model if the range of the descriptive variables can be represented by the real numbers. The model is a *discrete state* model if its variables only assume discrete values.

Continuous time models can be further divided into *differential equation* and *discrete event* classes. A differential equation model is a continuous time-continuous state model where changes in state occur smoothly and continuously in time. In a discrete event model, even though time flows continuously, state changes can occur only at countable points in time—i.e., time jumps from one event to the next, and these events can occur arbitrarily separated from each other.

#### 2.1 Discrete Event Simulation

The concept of a system and a model of a system were already used in the definition of the classes of simulation. These concepts need to be specified in order to develop a framework for the design of a discrete event model of a system. The major concepts are:

- System A collection of entities that interact together over time to accomplish one or more goals.

- Model An abstract representation of the system under consideration, usually containing logical and/or mathematical relationships that describe the behaviour of the system.

- System state A collection of variables that contain all the information necessary to describe the system at any time.

- Entity Any object or component in the system that requires explicit representation in the model.

Attributes The properties of a given entity.

- Event An instantaneous occurrence that may change the state of the system.

- Activity A duration of time of specified length during which entities engage some operation.

- **Process** A sequence of events ordered in time. These events must be logically connected, involving the same entity.

To illustrate these concepts, we consider a bank. In the dynamics of a bank, customers might be one of the entities, the balance in their accounts might be an attribute, and making deposits might be an activity. Possible state variables are the number of busy tellers, the number of customers waiting in line or being served, and the arrival time of the next customer. The arrival of a customer as well as the completion of service of a customer are possible events.

Every discrete event simulation contains a state variable called the *simulation clock* to model the flow of time. Simulated time is advanced from the time of the current event to the time of the next scheduled event; thus skipping periods of inactivity. Future events are stored in a calendar that contains the time and the type of all scheduled events, usually in chronological order. The nature of the routine depends on the world view used in the model. Let us therefore consider some different world views relevant to discrete event simulation.

#### 2.2 World Views

All simulations contain an executive routine for the management of the calendar and clock, i.e., the sequencing of events and driving of the simulation. This executive routine fetches the next scheduled event, advances the simulation clock and transfers control to the appropriate routine. The operation routines depend on the world view, and may be events, activities, or processes.

A world view is the point of view from which the modeller sees the world or the system to be modelled. Most of the discrete event simulations use one of the three following perspectives [Hoo86]: event scheduling, activity scanning, or process interaction.

In event scheduling each type of event has a corresponding event routine. The executive routine processes a time ordered calendar of event notices to select an event for execution. Event notices consist of a time stamp and a reference to an event routine. Event execution can schedule new events by creating an event notice and place it at the appropriate position in the calendar. The clock is always updated to the time of the next event, the one at the top of the calendar.

In the *activity scanning* approach a simulation contains a list of activities, each of which is defined by two events: the start event and the completion event. Each activity contains test conditions and actions. The executive routine scans the activities for satisfied time and test conditions and executes the actions of the first selectable activity. When execution of an activity completes, the scan begins again.

The process interaction world view focuses on the flow of entities through a model. This strategy views systems as sets of concurrent, interacting processes. The behaviour of each class of entities during its lifetime is described by a process class. Process classes can have multiple entries and exits at which a process interacts with its environment. The executive routine uses a calendar to keep track of forthcoming tasks. However, apart from recording activation time and process identity, the executive routine must also remember the state in which the process was last suspended.

Evidently, large discrete event simulations, using one of these three world view strategies, put extreme computational demands on sequential computers. Intuitively, the process interaction world view seems to be attractive as a starting point in our effort to the parallelization of the simulation. The modeller perceives the simulation already as a set of concurrent objects interacting with each other by well-defined communication. Besides, parallel simulation is interesting because it represents a problem domain that often contains substantial amounts of inherent parallelism (e.g., see [Liv85]).

In the following section a parallel view to a sequential execution will be presented in order to analyse the inherent parallelism of the simulation. Next the problems involved in parallel execution and the methodologies to circumvent these problems are described.

#### **3** From Sequential to Parallel Discrete Event Simulation

#### 3.1 The Average Parallelism Measure

If we have made the decision to do the simulation in parallel, there are some fundamental questions to be answered. What is the parallelism inherent to the simulation? How much benefit do we expect from doing things in parallel? And, once the job is done, how well did we perform this?

One very interesting characterization of the simulation that can be used to answer these questions is the *average parallelism*. Average parallelism can be defined in two equivalent ways:

- 1. The ratio of the total service time required to process events, to the length of the critical path through the execution of the simulation.

- 2. The speedup figures, if a hypothetical machine contains an unbounded number of available processors and zero synchronization overhead.

As a consequence of the second definition, the average parallelism figure should be regarded as an upper bound to the speedup that can be achieved.

To reveal the average parallelism inherent to a simulation, we have implemented a tool to analyse a sequential simulation run and extract the average parallelism [Ove91]. A system model is defined to express the parallelism explicitly and consists of a software component and a hardware component. The software component is a graph representing the execution of a sequential simulation. The hardware component of our system model reflects our focus on the parallelism inherent to a simulation, and makes assumptions of ideal hardware.

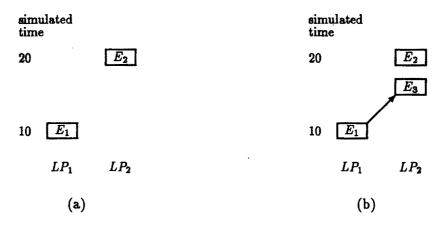

Figure 5: A program activity graph.

The execution of a simulation is represented by an acyclic directed graph (see Fig. 5). Each vertex of the graph corresponds to an event occurring in the simulation. Precedence constraints exist among the events, modelling the chronological order of events. These precedence constraints are modelled by the arcs of the graph: an arc from vertex  $E_A$  to vertex  $E_C$  means that event  $E_C$  cannot occur (or be executed) before event  $E_A$  is processed. Two types of arcs are distinguished: *intra-process arcs* and *inter-process arcs*. Intra-process arcs are precedence

constraints between events that occur within the same process (e.g., arc between vertex  $E_A$  and  $E_C$  in Fig. 5). The intra-process arc denotes an independent unit of sequential work inside a process. We can consider inter-process arcs as precedence constraints between events that occur in different processes (e.g., arc between vertex  $E_B$  and  $E_C$ ). These inter-process arcs represent synchronization requirements achieved by some communication primitive.

The hardware component of the system is modelled as an infinite number of identical processors, each of unit speed. The synchronization between processors has zero overhead and the entire computer is devoted to one single task.

A sequential run of the simulation generates an acyclic directed graph of events with their precedence constraints. When every process in the simulation is assigned to a different processor (i.e., one process to one exclusive processor), all *intra*-process dependent events occur at the same exclusive processor and all *inter*-process dependent events occur at different processors. As a consequence, the *intra*-process arc denotes an independent unit of sequential work on a processor, whereas the *inter*-process arc represents synchronization requirements between processors. Furthermore, the execution times of the independent units of work, measured during the sequential run, are assigned to the *intra*-process arcs and the zero synchronization costs to the *inter*-process arcs. In this way the graph is reduced to a representation of the execution of the simulation on a hypothetical machine. The total amount of time required to process the events is equal to the sum of all the costs in the graph and the critical path through the execution of the simulation is now represented by the longest path in the graph.

Eager et al. [Eag89] use the average parallelism measure to express lower bounds on speedup and efficiency, and on the incremental benefit and cost of allocating additional processors. It is our opinion that average parallelism can be applied as a measure in the evaluation of effectiveness of various methods in parallel simulation. In other words, how much of the parallelism that is inherent to the simulation is actually exploited?

#### 3.2 The Fundamental Problem in Parallel Discrete Event Simulation

We are especially interested in parallelization of asynchronous system simulation, where events are not synchronized by a global clock, but rather occur at irregular time intervals. In these simulations few events occur at any single point in simulated time and therefore parallelization techniques based on synchronous execution using a global simulation clock performs poorly. Concurrent execution of events at different points in simulated time is required, but this introduces interesting synchronization problems.

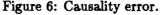

These problems become clear if one examines the operation of a sequential discrete event simulator. The sequential simulator typically uses three data structures: the state variables, an event list (the calendar), and a global simulation clock. For the execution routine (see section 2.2) it is crucial that the smallest time stamped event  $(E_{min})$  from the event list is selected as the one to be processed next. If it would depart from this rule and select an other event with a larger time stamp  $(E_x)$ , it would be possible for  $E_x$  to change the state variables used by  $E_{min}$ . This implies that one is simulating a system where the future could affect the past. We call errors of this kind causality errors.

Let us next consider the parallelization of a simulation based on the above paradigm. Most parallel discrete event simulation (PDES) strategies adhere to a process interaction world view that strictly forbids processes to have direct access to shared state variables. To this methodology some extensions have been made to support the parallel execution of the simulation [Cha79]. The system being modelled is viewed as being composed of some number of *physical processes* that interact at various points in simulated time. The simulation is constructed as a set of *logical*

B. Overeinder: Parallel Discrete Event Simulation.

processes  $LP_0$ ,  $LP_1$ ,..., one per physical process. All interactions between physical processes are modelled by time stamped event messages sent between the corresponding logical processes. Each logical process contains a portion of the state corresponding to the physical process it models, as well as a local clock that denotes the progress of the process.

One can assure that no causality error occurs if one adheres to the local causality constraint:

Local Causality Constraint: A discrete event simulation, consisting of logical processes that interact exclusively by exchanging time stamped messages, obeys the local causality constraint *if and only if* each logical process executes events in non decreasing time stamp order.

Consider two events.  $E_1$  at logical process  $LP_1$  with time stamp 10, and  $E_2$  at  $LP_2$  with time stamp 20 (see Fig. 6). If  $E_1$  schedules a new event  $E_3$  for  $LP_2$  containing a time stamp less than 20, then  $E_3$  could affect  $E_2$ , necessitating sequential execution of all three events. If one had no information what events could be scheduled by other events, one would be enforced to process the only save event, the one containing the smallest time stamp, resulting in a sequential execution.

During the simulation we must therefore decide whether  $E_1$  can be executed concurrently with  $E_2$ . But how do we know whether or not  $E_1$  affects  $E_2$  without actually performing the simulation for  $E_1$ ? It is this question the parallel discrete event simulation strategies must address.

In this paper we classify parallel discrete event simulation strategies by two categories: conservative and optimistic. Conservative approaches strictly avoid the possibility of any causality error ever occurring. These approaches rely on some strategy to determine when it is safe to process an event. The optimistic approaches use a detection and recovery approach: whenever causality errors are detected a rollback mechanism is invoked to recover. We will describe some of the concepts behind conservative and optimistic simulation mechanisms.

#### **3.3** Conservative Methods

The conservative approaches are the first distributed simulation mechanisms. The basic problem conservative mechanisms must address is to determine which event is save to process. If a process contains an event  $E_1$  with time stamp  $T_1$  and the process can determine that it is impossible to receive another event with time stamp smaller than  $T_1$ , then the process can safely process

event  $E_1$  without a future violation of the local causality constraint. Processes containing no safe events must block; this can lead to deadlock situations if no appropriate precautions are taken.

Independently, Chandy and Misra [Cha79], and Bryant [Bry77] developed the parallel discrete event simulation algorithms, where one statically specifies the links that indicate which process may communicate with which other processes. In order to determine when it is safe to process a message, it is required that messages from any process to any other process are transmitted in chronological order according their time stamps. Each link has a clock associated with it that is equal to either the time stamp of the message at the front of that link's queue or, if the queue is empty, the time of the last received message. The process repeatedly selects the link with the smallest clock and, if there is a message in that link's queue, updates its local clock to the link's clock and process the message. The order of event processing will be correct because all future messages received will have later time stamps than the local clock, since they will arrive in chronological order along each link. If the selected queue is empty, the process blocks. This is because the process may receive a message over this link with a time that is less than all the other input time stamps. Thus to insure correct chronology, the process is forced to wait for a message to update the clock on the link before the process can update its local clock. This protocol guarantees that each process will only process events in nondecreasing time stamp order, and thereby ensuring chronological integrity.

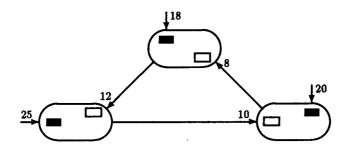

Figure 7: An example of deadlock. (The numbers indicate time stamps.)

Deadlock occurs when there is a cycle of blocked processes and each process is blocked due to another process in the cycle. For example consider the network of Fig. 7. Each process is waiting on the incoming link containing the smallest clock value because the corresponding queue is empty. All three processes are blocked, even though there are event messages in other queues that are waiting to be processed.

Null messages are used to avoid deadlock. This scheme requires that there is a strictly positive lower bound on the *lookahead* for at least one process in each cycle. Lookahead is defined to be the amount of time that a process can look into the future. In other words, if the local clock of the process is any time T and the process can predict all messages it will send with time stamps less than T + L, where L is the lookahead. Thus, for a queueing network model, a strictly positive lower bound for the service time for some stations would be required. Intuitively, processes keep the clocks of their output links ahead of their local clocks by sending null messages. A null message with time stamp  $T_{null}$  from process  $LP_A$  to  $LP_B$ , tells  $LP_B$  that there will be no more messages from process  $LP_A$  with time stamp less than  $T_{null}$ . Whenever a process finishes processing an event, it sends a null message on each of its output ports

#### B. Overeinder: Parallel Discrete Event Simulation.

indicating the lower bound on the time stamp of the next outgoing message. The receiver of the null message can then compute new bounds on its outgoing links, send this information to its neighbours, and so on.

Chandy and Misra [Cha81] also presented a two-phase scheme where the simulation proceeds until deadlocked, then the deadlock is detected and resolved. The mechanism is similar to that described above, except no null messages are created. Instead the computation is allowed to deadlock. The scheme involves a controller process to monitor for deadlock and control deadlock recovery. Deadlock detection mechanisms are described in [Gro89, Mis86]. The deadlock can be broken by the observation that the message with the smallest time stamp is always save to process; or, with use of a distributed computation, obtain a lower bound to enlarge the set of safe messages.

The mechanisms described above only attempt to detect and recover from global deadlocks. Prakash and Ramamoorthy [Pra88] suggested a hierarchical decentralized algorithm that takes advantage of the locality of these deadlocks. Another approach to detect and recover from local deadlocks can be found in [Mis86].

The performance of conservative mechanisms is critically determined by the degree to which processes can look ahead and predict future events; or more importantly, what will not happen in the simulated future. A process with lookahead L can guarantee that no events, other than the ones that it can predict, will be generated up to time Clock + L. This may enable processes to safely process forthcoming messages that they have already received. Fujimoto describes lookahead quantitatively using a parameter called the lookahead ratio and presents empirical data to demonstrate the importance of exploiting lookahead to achieve good performance [Fuj89]. Other studies of the performance as a function of lookahead can be found in [Lin89, Lou90, Su89].

#### **3.4 Optimistic Methods**

In optimistic approaches a process's clock may run ahead of the clocks of its incoming links and if errors are made in the chronology a procedure to recover is invoked. In contrast to conservative approaches, optimistic strategies need not determine when it is safe to proceed. Advantages of this approach are that it has a potentially larger speedup than conservative approaches and that the topology of possible interactions between processes need not be known.

An optimistic approach to distributed simulation called Time Warp, based on the Virtual Time paradigm, was proposed by Jefferson and Sowizral [Jef82, Jef85]. Here virtual time is the same as the simulated time. The local clock, called the Local Virtual Time (LVT) of a process, is set to the minimum receive time of all unprocessed messages. Processes can execute events and proceed in local simulated time as long as they have any input at all. As a consequence, the local clock or LVT of a process may get ahead of its predecessors' LVTs, and it may receive an event message from a predecessor with time stamp smaller than its LVT, i.e., in the past of the process. If this happens the process rolls back in simulated time. The event causing the roll back is called a *straggler*. Recovery is accomplished by undoing the effects of all events that have been processed prematurely by the process receiving the straggler.

The premature execution of an event results in two things that have to be rolled back: the state of the logical process and the event messages to other processes. Rolling back the state is accomplished by periodically saving the process state and restoring an old state vector on roll back. Unsending a previously sent message is accomplished by sending a *anti-message* that annihilates the original when it reaches its destination. Messages that are sent while the process is propagating forward in simulated time are called *positive messages*. If a process receives an anti-message that corresponds to a positive message that is still in the input queue, then the

two will annihilate each other and the process will proceed. If an anti-message arrives that correspond to a positive message that is already processed, then the process has made an error and must also roll back. It sets its current state to the last state vector saved with simulated time earlier than the time stamp of the message. A direct consequence of the roll back mechanism is that more anti-messages may be sent to other processes recursively.

The Global Virtual Time (GVT) is the minimum of the LVTs for all the processes and the time stamps of all messages sent but unprocessed. No event with time stamp smaller than GVT will ever be rolled back, so storage used by such event (i.e., saved states) can be discarded.

The procedure just described is referred to as Time Warp with aggressive cancellation. An alternative is lazy cancellation, where anti-messages are not sent immediately after roll back. Here, the process resumes executing forward in simulated time from its new LVT, and when it procedures a message it compares it with the messages in its output queue. If the same message is recreated, then there is no need to cancel the message. An anti-message created at simulated time T is only sent after the process's clock sweeps past time T without regenerating the same message. Thus, under lazy cancellation a roll back at the successor process may be avoided. On the other hand, if messages are not reproduced, then roll backs at the successor processes will be required under both mechanisms, and they will occur sooner with aggressive cancellation.

Depending on the application, lazy cancellation may either improve or degrade performance. States may be saved less frequently at the expense of greater overhead for roll back. As a consequence, lazy cancellation requires more memory than aggressive cancellation. Studies of the performance of optimistic approaches can be found in [Lin90, Mad90].

#### 4 Conclusion and Discussion

Performance evaluation is critical for the design, implementation, and improvement of complex applications executing on parallel computers. Analytical approaches to performance evaluation are usually inadequate because they are based on unrealistic assumptions and require many approximations. Therefore, simulation is a good alternative for obtaining accurate measures of performance. Currently, however, detailed simulations are extremely slow. Parallel simulation seems to be a promising approach for speeding up the simulations, although much more work needs to be done to increase the effectiveness of the existing methods.

Conservative methods offer good potential for certain classes of problems. A major drawback, however, is that they cannot fully exploit the parallelism available in the simulation application. If it is possible that event  $E_A$  might affect  $E_B$  either directly or indirectly, conservative approaches must execute  $E_A$  and  $E_B$  sequentially. If the simulation is such that  $E_A$  seldom affect  $E_B$  these events could have been processed concurrently most of the time. As a consequence, conservative algorithms heavily rely on lookahead to achieve good performance.

Optimistic methods offer the greatest potential as a general purpose simulation mechanism. A critical question faced by optimistic approaches is whether the system will spent most of its time on executing incorrect computations and rolling them back, at the expense of correct computations. An intuitive explanation why the behaviour tends to be stable is that incorrect computations can only be initiated by a premature execution of a correct event. This premature execution, and subsequent incorrect computations, are by definition in the simulated time future of the correct, straggler computation. Also, the further the incorrect computation spreads the further it moves into the simulated time future, thus lowering its priority for execution. Preference is always given to computations containing smaller time stamps. The incorrect computation will be slowed down, allowing the error detection and correction mechanism to correct before too much damage has been done.

#### B. Overeinder: Parallel Discrete Event Simulation.

A more serious problem with the optimistic mechanisms is the need to periodically save the state of each logical process. This limits the effectiveness of the optimistic mechanisms to applications where the amount of computation, required to process an event, is significantly larger than the cost of saving the state vector.

The type of application, or classes of applications, is important when determining an appropriate approach to distributed simulation. For dynamic topology systems and systems with irregular interactions, Time Warp methods are preferred over conservative methods, especially if state-saving overheads do not dominate. On the other hand, if the application has good lookahead properties, conservative algorithms can exploit the special structure within a fixed topology system. If the application has both poor lookahead and large state-saving overheads all existing parallel discrete event simulation approaches will have trouble obtaining good performance, even if the application has a considerable amount of parallelism.

A challenging, yet not fully exploited, problem is the use of hierarchical methods in parallel discrete event simulation (PDES). It is our contention that, if processes are forced to remember the values of all private variables, an object-oriented methodology can be employed. Here a class must encapsulate all relevant aspects of an entity: its attributes, actions, and life cycle. Communication between objects is allowed only through well-defined interfaces, described by the types of messages an object is willing to respond to. With the use of such object-oriented methodologies, the hierarchical decomposition of the problem under investigation can also be made available in the simulation. In conservative approaches there is some modest effort to use this hierarchical knowledge in the detection of local deadlock and recovery [Pra88]. In optimistic approaches, hierarchical knowledge could be used by the error detection and correction mechanism to quickly stop the spread of the erroneous computations. Furthermore, the proposed model in section 3.1 has to be extended for the evaluation of the various PDES strategies. Many performance evaluations of PDES strategies, found in the literature, compare the parallelism available in the application with the measured speedup of the application on a specific parallel computer. In consequence, there is interference with load balance and scheduling strategies that obscure the effectiveness of the PDES strategy. The extended model should eliminate this interference, and measure the exploited parallelism by a PDES strategy. In this way, the exploited parallelism can be compared to the average parallelism to obtain the effectiveness of the strategy.

#### Acknowledgements

I would like to thank Sjaak Koot from our working-group for some valuable discussions.

#### References

- [Bry77] Bryant, R.E., "Simulation of Packet Communications Architecture Computer Systems," MIT-LCS-TR-188, Massachusetts Institute of Technology, 1977.

- [Cha79] Chandy, K.M., and J. Misra, "Distributed Simulation: A Case Study in Design and Verification of Distributed Programs," *IEEE Transactions on Software Engineering*, vol. SE-5, no. 5, pp. 440-452, September 1979.

- [Cha81] Chandy, K.M., and J. Misra, "Asynchronous Distributed Simulation via a Sequence of Parallel Computations," Communications of the ACM, vol. 24, no. 11, pp. 198-205, November 1981.

- [Eag89] Eager, D.L., J. Zahorjan, and E.D. Lazowska, "Speedup Versus Efficiency in Parallel Systems," *IEEE Transactions on Computers*, vol. 38, no. 3, pp. 408-423, March 1989.

- [Fuj89] Fujimoto, R.M., "Performance Measurements of Distributed Simulation Strategies," Transactions of the Society for Computer Simulation, vol. 6, no. 2, pp. 89–132, April 1989.

- [Gro89] Groselj, B., and C. Tropper, "A Deadlock Resolution Scheme for Distributed Simulation," Proceedings of the SCS Multiconference on Distributed Simulation, pp. 108-112, March 1989.

- [Hoo86] Hooper, J.W., "Strategy Related Characteristics of Discrete Event Languages and Models," Simulation, vol. 46, no. 4, pp. 153-159, April 1986.

- [Jef82] Jefferson, D.R., and H. Sowizral, "Fast Concurrent Simulation using the Time Warp Mechanism, Part I: Local Control," Technical Report N-1906-AF, RAND Corporation, December 1982.

- [Jef85] Jefferson, D.R., "Virtual Time," ACM Transactions on Programming Languages and Systems, vol. 7, no. 3, pp. 404-425, July 1985.

- [Lin 89] Lin, Y-B., and E. Lazowska, "Exploiting Lookahead in Parallel Simulation," Technical Report 89-10-06, Department of Computer Science, University of Washington, Seattle (WA), 1989.

- [Lin90] Lin, Y-B., and E. Lazowska, "Reducing the State Saving Overhead for Time Warp Parallel Simulation," Technical Report 90-02-03, Department of Computer Science, University of Washington, Seattle (WA), 1990.

- [Liv85] Livny, M., "A Study of Parallelism in Distributed Simulation," Proceedings of the SCS Multiconference on Distributed Simulation, pp. 94–98, San Diego (CA), January 1985.

- [Lou90] Loucks, W.M., and B.R. Preiss, "The Role of Knowledge in Distributed Simulation," Proceedings of the SCS Multiconference on Distributed Simulation, pp. 9–16, San Diego (CA), January 1990.

- [Mad90] Madisetti, V., J. Walrand, and D. Messerschmitt, "Synchronization in Message-Passing Computers-Models, Algorithms, and Analysis," Proceedings of the SCS Multiconference on Distributed Simulation, pp. 35-48, San Diego (CA), January 1990.

- [Mis86] Misra, J., "Distributed Discrete Event Simulation," ACM Computing Surveys, vol. 18, no. 1, pp. 39-65, March 1986.

- [Ove91] Overeinder, B.J., and P.M.A. Sloot, "Parallelism in Architecture Simulation," Technical Report, Department of Computer Systems, University of Amsterdam, Amsterdam, The Netherlands, under preparation.

- [Pra88] Prakash, A., and C.V. Ramamoorthy, "Hierarchical Distributed Simulations," Proceedings of the 8th International Conference on Distributed Computing Systems, pp. 341-347, San Jose (CA), June 1988.

- [Su89] Su, W.K., and C.L. Seitz, "Variants of the Chandy-Misra-Bryant Distributed Discrete-Event Simulation Algorithm," *Proceedings of the SCS Multiconference on Distributed* Simulation, pp. 38-43, March 1989.

- B. Overeinder: Parallel Discrete Event Simulation.

- [Zei76] Zeigler, B.P., Theory of Modelling and Simulation, John Wiley & Sons, New York, 1976.

## A Partitioning and Redundancy Model for Wafer-Scale Integrated Circuits.

Dr.ir. Martin F. Beusekamp University of Twente Department of Computer Science P.O. Box 217 7500 AE Enschede Telefoon: 053 - 893796 Telefax: 053 - 356531

#### <u>Abstract</u>