# Proceedings of the first international workshop on Investigating dataflow in embedded computing architectures (IDEA 2015), January 21, 2015, Amsterdam, The Netherlands

Citation for published version (APA):

Ahmad, W., Groote, de, R., Lele, A., & Moreira, O. (Eds.) (2015). Proceedings of the first international workshop on Investigating dataflow in embedded computing architectures (IDEA 2015), January 21, 2015, Amsterdam, The Netherlands. (Computer science reports; Vol. 1502). Technische Universiteit Eindhoven.

#### Document status and date:

Published: 01/01/2015

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

If you believe that this document breaches copyright please contact us at:

providing details and we will investigate your claim.

Download date: 04 Oct 2023

### Technische Universiteit Eindhoven Department of Mathematics and Computer Science

Proceedings of the First International Workshop on Investigating Dataflow in Embedded computing Architectures (IDEA 2015)

15/02

ISSN 0926-4515

All rights reserved

editors: prof.dr. P.M.E. De Bra

prof.dr.ir. J.J. van Wijk

#### Reports are available at:

$http://library.tue.nl/catalog/TUEPublication.csp? Language=dut\&Type=ComputerScienceReports\&Sort=Author\&level=1\ and$

http://library.tue.nl/catalog/TUEPublication.csp?Language=dut&Type=ComputerScienceReports&Sort=Year&Level=1

### Proceedings of the

### First International Workshop on Investigating Dataflow in Embedded computing Architectures (IDEA 2015)

January 21, 2015, Amsterdam, The Netherlands

Held in Conjuction with the

10th HiPEAC Conference, January 19 - 21, 2015

UNIVERSITY OF TWENTE.

### **Preface**

IDEA '15 held at HiPEAC 2015, Amsterdam, The Netherlands on January 21st, 2015 is the first workshop on Investigating Dataflow in Embedded computing Architectures. This technical report comprises of the proceedings of IDEA '15.

Over the years, dataflow has been gaining popularity among Embedded Systems researchers around Europe and the world. However, research on dataflow is limited to small pockets in different communities without a common forum for discussion. The goal of the workshop was to provide a platform to researchers and practitioners to present work on modelling and analysis of present and future high performance embedded computing architectures using dataflow.

Despite being the first edition of the workshop, it was very pleasant to see a total of 14 submissions, out of which 6 papers were selected following a thorough reviewing process. All the papers were reviewed by at least 5 reviewers.

This workshop could not have become a reality without the help of a Technical Program Committee (TPC). The TPC members not only did the hard work to give helpful reviews in time, but also participated in extensive discussion following the reviewing process, leading to an excellent workshop program and very valuable feedback to authors. Likewise, the Organisation Committee also deserves acknowledgment to make this workshop a successful event. We take this opportunity to thank everyone who contributed in making this workshop a success.

Waheed Ahmad Robert de Groote Alok Lele Orlando Moreira

# Organisation

### Technical Program Committee

- Benny Åkesson (Czech Technical University, Prague)

- Marco Bekooij (NXP Research, Eindhoven)

- Shuvra S. Bhattacharyya (University of Maryland, College Park)

- Pieter J. L. Cuijpers (Eindhoven University of Technology, Eindhoven)

- Michael Glaß, (Friedrich-Alexander-Universität, Erlangen-Nürnberg)

- Kim Grüttner (OFFIS Institute for Information Technology, Oldenburg)

- Alix Munier Kordon (INRIA / LIP6, Paris)

- Orlando Moreira (Ericsson, Eindhoven)

- Luis Miguel Pinho (CISTER, Porto)

- Petro Poplavko (VERIMAG, Grenoble)

- Gerard Smit (University of Twente, Enschede)

- Sander Stuijk (Eindhoven University of Technology, Eindhoven)

- Jean-Pierre Talpin (INRIA, Rennes)

- Xue-Yang ZHU (SKLCS, Beijing)

### Organising Committee

- Waheed Ahmad (University of Twente, Enschede)

- Robert de Groote (University of Twente, Enschede)

- Alok Lele (Eindhoven University of Technology, Eindhoven)

# Contents

| 1        | Energy-Aware Mapping and Scheduling of Large-Scale Macro Data-Flow Applications | 5  |

|----------|---------------------------------------------------------------------------------|----|

| <b>2</b> | Pipelined Scheduling of Acyclic SDF Graphs using SMT Solvers                    |    |

| 3        | Compile-Time Mapping of Dataflow Applications with Buffer Minimization          | 13 |

| 4        | Towards Translating FSM-SADF to Timed Automata                                  | 17 |

| 5        | Towards Generally-Timed Energy SADF                                             | 21 |

|          | State-Based Real-Time Analysis of SDF Applications on Multi-<br>Cores           | 25 |

# Energy-Aware Mapping and Scheduling of Large-Scale Macro Data-Flow Applications

Jörg Walter

OFFIS – Institute for Information Technology,

Oldenburg, Germany

joerg.walter@offis.de

Wolfgang Nebel University of Oldenburg Oldenburg, Germany wolfgang.nebel@uni-oldenburg.de

Abstract—Predicting the performance of parallel programs for large-scale parallel platforms is difficult due to the disparity between development system and target platform. Additionally, energy efficiency is becoming a universal concern, and platforms move towards highly heterogeneous systems containing GPUs, FPGAs, and other unconventional processing elements.

In this paper we propose a static macro data-flow mapping and scheduling tool that is able to handle large parallel applications targeting heterogeneous platforms. It optimizes overall run time and energy consumption at the same time with a userconfigurable cost function, allowing a selectable trade-off between both properties.

#### I. Introduction

Energy efficiency is a universal concern by now: the world's fastest supercomputers exhibit a de facto 20 MW power limit, in mobile computing it affects battery life time; even high-end workstations are constrained due to size and noise requirements.

An equally universal concern is parallel application design. Well-established in the high-performance computing (HPC) world as in embedded system level design, general-purpose computing has embraced heterogeneous parallelism as well.

Experience shows that embedded systems can be expected to reach the computational power of today's supercomputers within ten years. Consequently, they will face the same challenges as supercomputers: a developer workstation will struggle to model, map, and simulate an application running on hundreds of processing elements at today's level of detail.

Our current research includes a design and optimisation flow for large parallel applications on heterogeneous platforms. It works on task precedence graphs, or macro data-flow graphs, and treats tasks in an abstract way so that it can handle larger applications than usually addressed in embedded system design.

In this paper we present our tool to solve the mapping problem, i. e. how to assign tasks to processing elements (PEs) and how to schedule tasks on a given PE. While our mapper is based on well-known algorithms, it has two main advantages over existing tools:

Instead of just minimizing overall run time time, it optimizes energy efficiency by minimizing the energy delay product or any other function of these two values.

The research leading to these results has received funding from the European Union Seventh Framework Programme (FP7/2007-2013) under grant agreement N $^{\circ}$  609757 (FiPS - Developing Hardware and Design Methodologies for Heterogeneous Low Power <u>Fi</u>eld <u>Programmable Servers</u>).

It handles real-world applications consisting of thousands of tasks mapped to hundreds of heterogeneous processing elements with much better results than simulatedannealing-based tools.

This paper has the following structure: The next section lists research related to our methodology. Section III shows the context for which we designed the mapper. Section IV defines input data that it operates on. We explain the actual algorithm in Section V, followed by Section VI, where we highlight open issues and possible solutions. Finally, Section VII summarizes our findings and gives an outlook to ongoing research.

#### II. RELATED WORK

Mapping and scheduling of task graphs is a well-researched topic. Many algorithms exist, and [8], [9] give a comprehensive overview; the latter also evaluates some of them. Most algorithms use very simple assumptions about computation and communication behaviour. We base our tool on a combination of such well-understood algorithms, but since we map to real-world heterogeneous cluster architectures, our performance and power models are more detailed.

Few schedulers are energy aware in any case, and they usually minimize energy under fixed deadlines, like [5], [6] or reduce PE idle consumption by stretching tasks via voltage/frequency scaling [2], but the actual scheduling still optimizes for time only. Our mapper minimizes a configurable cost function, by default energy times delay, and thus is able to perform an arbitrary trade-off between time and energy.

#### III. A DESIGN AND OPTIMISATION FLOW

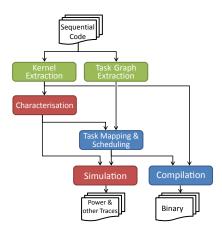

Fig. 1 shows the application design and optimization flow for which we designed the mapper.

Designers have a golden application model, i.e. sequential program code. They separate the code into several compute-intensive kernels and extract them. With these stand-alone kernels, they perform a one-time characterisation process; later stages of the flow use its results.

Designers then build a task graph so that each task executes exactly one kernel; one kernel usually corresponds to multiple task instances. Task graph plus kernel code should be functionally equivalent to the source application.

Our mapping and scheduling algorithm uses task graph, platform description, and characterisation results to map each

Figure 1. Overview of our design flow.

task of the task graph to a processing element (PE) on the target platform and generates a queue of tasks for each PE.

Simulation then uses this mapping in conjunction with characterisation results to predict makespan (i. e. overall run time) and energy consumption, as well as other metrics provided by simulation models.

With these predictions, designers can optimize the application in various ways: they can restructure the task graph, e. g. by changing the amount of parallelism, they can change the application's separation into kernels, and they can even start over and rewrite the application using different algorithms. This effectively constitutes a design space exploration loop. When satisfied, designers can create an executable version of the parallelised application from the mapped task graph in conjunction with the extracted kernels.

#### IV. MAPPING INPUTS

Our mapper works on an application model and a platform model, much like embedded design space exploration tools. We specifically target large parallel applications on loosely coupled (cluster-like) architectures.

#### A. Application Model

Applications are represented as task precedence graphs as commonly used in HPC research, e.g. in [1]. This application model is also known as macro data-flow, with slightly different terminology as main difference. Recent research has shown practical usefulness of this representation [4].

We add annotations in order to express computation and communication complexity with higher detail than simple edge/node weights could express: a task graph  $TG = (T, D, K, \kappa, \delta)$  is an annotated directed acyclic graph, where T is the set of tasks (graph nodes), D is the set of precedence constraints (edges) between tasks, K is the set of known kernels (see Section III), function  $\kappa$  maps tasks to kernels, and function  $\delta$  specifies communication volume for each edge.

A task can execute as soon as all predecessor tasks have completed execution, and all data objects associated with incoming dependencies have been received. Task execution is atomic (at least conceptually) and has no hidden side-effects, just communication as expressed by  $\delta$ . Communication happens after the originating task has completed execution and before the destination task starts execution.

Our mapper expects that the task graph has exactly one start node, i.e. exactly one node with in-degree zero.

#### B. Platform Model

The mapper uses an abstract model for the target platform that provides a list of processing elements, their hardware architecture, and a graph of communication resources.

The platform communication graph  $PCG = (C, L, M_C, \lambda)$  is an annotated directed graph, where C is the set of communication elements (CEs). Subset  $P \subseteq C$  is the set of processing elements (PEs). Set L represents links between CEs. Function  $\lambda$  maps CEs to behavioural parameters contained in set  $M_C$ , most importantly start-up delay and usable bandwidth.

#### C. Characterisation Database

In addition to the task graph, the mapper relies on kernel execution times collected in a characterisation database. For each kernel k that is in the set K of all characterised kernels, it contains the average execution time for k running on each PE architecture, and the corresponding average power consumption. The database could hold synthetic numbers derived from power/performance simulation models, but it is intended to store actual measurements done on real hardware.

By splitting applications into kernels and characterising those independently of application and platform models, we get the flexibility to explore hypothetical (i. e. unfinished, non-existing) applications and platforms. A single processing element of each architecture is sufficient for characterisation.

#### V. ENERGY-AWARE MAPPING AND SCHEDULING

Our mapping tool uses a constructive hybrid heuristic: An earliest-finishing-time-first list scheduler works on a linear task queue, while a modified version of simulated annealing (SA) explores random permutations of tasks in that queue by repeating the scheduling process for each permutation.

The mapper/scheduler only maps computation, not communication. We assume the platform has a shortest-path routing policy as is common with Ethernet interconnects. Furthermore, in its current state it does not model communication contention in any way (see Section VI).

#### A. Data Structures

In addition to the input models as explained in Section IV, our mapper uses the following important data structures:

1) Task Queue: The task queue is the central data structure. Initially, it contains a breadth-first traversal of the task graph, starting at the single start node. It must always contain a topological ordering of the task graph: for every task in the queue, all of its predecessors occur in front of it, and all of its successors appear after it. The optimizing heuristic always preserves this property.

- 2) Communication Matrix: The mapper assumes static shortest-path routing. From the platform communication graph it constructs a square matrix with one row and column per processing element (PE). It contains the cumulative start-up delay per transmission, and the maximum achievable bandwidth between each pair of PEs, which is the bandwidth of the slowest link on the route between them.

- 3) PE Schedule: The main output of the mapping process is a queue of tasks to be executed for each PE. A PE strictly adheres to this order of tasks, but it dynamically determines when the current task can start, i.e. when all inputs for a task are available. This is because the lack of communication congestion may lead to considerable timing inaccuracy.

#### B. Constructive Scheduler

The list-based mapper/scheduler traverses the task queue in order and maps each task to the PE that yields the earliest task finish time. It uses task execution times from the characterisation database and models communication delays via data taken from the communication matrix in conjunction with data size as recorded in the application model.

Even though this only considers time, there is a strong correlation between time and energy. As a consequence, we have achieved good results with this scheduler in conjunction with the actual optimizing heuristic (see Table I).

#### C. Optimizing Heuristic

The simulated-annealing (SA) part explores permutations of the task queue in order to minimize the user-configurable cost function, which can be any function of the two parameters total time and total energy. As its only move, the heuristic swaps the position of two adjacent tasks in the task queue. If that would violate the ordering restriction noted in Section V-A1, it chooses another pair until it finds a valid move.

It then lets the scheduler determine timing of the new task queue. After that, the mapper uses a two-state power model (active and idle) for processing elements to calculate total energy usage. Finally, it calculates the score using the user-configured cost function. It then decides whether to accept the solution with a typical SA probability function. Then it repeats the whole process; currently, it uses one million iterations.

1) Windowing: The mapper is intended for task graphs of a few hundred nodes as well as for ones with tens to hundreds of thousands of tasks. Therefore, it is difficult to set a fixed iteration count for simulated annealing. Instead, we subdivide the task queue into equal-sized windows. Each window overlaps with half of the preceding window and half of the following window. SA then works on a single window at a time, in increasing order, spending one million iterations each time.

In our experiments, a window size of about  $3 \cdot |P|$  tasks has given best results; we observed a significant improvement in result quality over the all-at-once variant (given similar total mapping time).

2) Optimizations: We employed several optimisations in order to reduce mapping time. Most importantly, we do not reschedule the whole task graph on each iteration. We store

Figure 2. Mapping speed for various task graph and target platform sizes.

intermediate scheduling results for every task in the task queue (using  $O(|T|\cdot|P|)$  memory) and start rescheduling only the swapped tasks and the following ones. In average, this halves mapping time.

The list-based scheduler itself contains another useful optimisation: when searching for the best PE, it first checks if a given PE would be a viable candidate if it did not experience communication delays. If not, the scheduler skips calculation of communication delays entirely, which yields another significant speed-up (depending on target platform size).

#### D. Evaluation

1) Mapping Speed: With a fixed iteration count, our mapper has an asymptotic run time of  $O(|T|\cdot|P|)$ , because the list scheduler iterates exactly once over the task queue on each annealing iteration, and it has to check all possible PEs for each task. This relies on the assumption that the average indegree of all nodes is constant regardless of task graph size. It is easy to create task graphs that break this assumption, but for real-world parallel application patterns this holds, since kernels usually have a fixed, small number of inputs. With windowing this stays the same, because no matter how many windows there are, the amount of work per window decreases by that factor.

Fig. 2 shows the mapping time of some sample runs, each a mapping of Cholesky matrix decomposition in various degrees of parallelisation to various heterogeneous target platforms built from of three different types of processing elements. The mapper executed on a single core of an AMD Opteron processor running at 2.6 GHz. The figure shows that actual mapping times indeed scale linearly with number of PEs and tasks

2) Mapping Quality: We compared our mapper to a plain SA implementation as it is often found in literature, e.g. in [9], and to the plain list-based scheduler without annealing. Table I lists the results of mapping 1543 tasks to 90 PEs using the energy delay product as cost function, as suggested in [3]. As expected, the list-based scheduler is several orders of magnitude faster than the others. We selected SA parameters so it would run roughly the same time as our hybrid mapper.

Table I COMPARISON TO OTHER MAPPING HEURISTICS.

| Туре                | Predicted Time (s) Energy (kJ) |     | Cost<br>(MJs) | Mapping<br>Time (s) |

|---------------------|--------------------------------|-----|---------------|---------------------|

| Simulated Annealing | 162                            | 164 | 26.5          | 2260                |

| List Scheduler      | 160                            | 199 | 31.8          | 0.003               |

| Hybrid              | 132                            | 177 | 23.4          | 2385                |

Our hybrid mapper produces mappings that are 26% better than the plain list-based scheduler (measured by the cost function). It is 12% better than plain simulated annealing running for a similar amount of time. With an 8% increase in energy usage over SA, it produced a solution that has 18% less makespan. That solution is even faster than the time-only optimizing list scheduler.

#### VI. FUTURE IMPROVEMENTS

There are some open issues we want to solve in order to make our tool more suitable for its intended purpose. Unfortunately, it is already quite slow, so any improvement in accuracy must be essentially free, or we need to find further optimization opportunities in the algorithm.

#### A. Performance

One way to speed up the mapper is to use variable SA iteration counts. That way, users are able to make a speed/optimality trade-off.

Another common technique is parallelisation. There are existing implementations that promise easy parallelisation of SA-based heuristics [7]. We have not yet tried this, but will probably do so.

#### B. Data-Dependent Behaviour

In order to account for data-dependent behaviour that can be expressed statically, kernels can actually be parametrised, e.g. by the size of the inputs they process. In that case, tasks in the task graph also specify kernel parameter values.

We do not yet handle data-dependent behaviour that cannot be determined statically. Regarding execution time, histograms instead of constant task execution times are a possible solution. Since simulated annealing already encompasses repeatedly retrieving execution times, a simple random sample from these histograms on each iteration might be enough to get a realistic task execution time distribution. If this expectation turns out to be true, this means that essentially, we get stochastic modelling for free.

#### C. Communication Congestion

The worst accuracy problem we face is the lack of communication congestion modelling. As far as we are aware, there is no cheap solution. Since the scheduler iterates over the task queue once, we cannot (cheaply) readjust already-mapped tasks. This means that earlier tasks in the queue cannot account for communication of later tasks even though they might be contending for the same communication links.

The problem actually consists of two parts: how to get congestion data, and how to incorporate it.

1) Collecting Congestion Information: So far, we have had two ideas for gathering congestion data: As our mapper is part of an iterative design space exploration flow, congestion data generated by earlier iterations could influence future mappings.

Our windowing technique could also provide abstract link utilisation figures. A window could record how much data went over each link. The following (overlapping) window could use this for congestion modelling.

2) Accounting for Congestion: In order to account for such congestion, link bandwidth could simply be reduced. Alternatively, link bandwidth could be modelled stochastically, just like we intend to do for task execution times. The latter solution might work well with iterative feedback, and it might even be fed from each iteration of the annealing heuristic.

#### VII. CONCLUSION

In this paper, we have presented a mapping tool intended for mapping large task graphs onto highly heterogeneous parallel platforms. It uses a combination of two well-known heuristics to create better mappings than each one on its own. Furthermore, it scales linearly with the number of tasks and the number of processing elements. Its main drawback is a speed that is only suitable for static ahead-of-time mappings.

We are still investigating ways to improve the computation and communication model employed in the mapper. The most important missing element is communication congestion, as this is a major source of mismatch to real-world execution behaviour. Since the mapper is part of a full design space exploration flow, we expect that other parts of the flow can supply useful data to address this issue.

#### REFERENCES

- [1] Vikram Adve and Rizos Sakellariou. Application representations for multiparadigm performance modeling of large-scale parallel scientific codes. *International Journal of High Performance Computing Applications*, 14(4):304–316, 2000.

- [2] Sanjeev Baskiyar and Rabab Abdel-Kader. Energy aware DAG scheduling on heterogeneous systems. *Cluster Computing*, 13(4):373–383, 2010.

- [3] Luca Benini and Giovanni de Micheli. System-level Power Optimization: Techniques and Tools. ACM Trans. Des. Autom. Electron. Syst., 5(2):115–192, April 2000.

- [4] George Bosilca, Aurelien Bouteiller, Anthony Danalis, Mathieu Faverge, Thomas Herault, and Jack J Dongarra. PaRSEC: Exploiting Heterogeneity to Enhance Scalability. Computing in Science & Engineering, 15(6):36–45, 2013

- [5] Po-Chun Chang, I-Wei Wu, Jyh-Jiun Shann, and Chung-Ping Chung. ETAHM: An energy-aware task allocation algorithm for heterogeneous multiprocessor. In *Design Automation Conference*, 2008. DAC 2008. 45th ACM/IEEE, pages 776–779. IEEE, 2008.

- [6] Jia Huang, Christian Buckl, Andreas Raabe, and Alois Knoll. Energy-aware task allocation for Network-on-Chip based heterogeneous multiprocessor systems. In Parallel, Distributed and Network-Based Processing (PDP), 2011 19th Euromicro International Conference on, pages 447–454. IEEE, 2011.

- [7] Georg Kliewer. A general software library for parallel simulated annealing. EURO Winter Institute on Metaheuristics in Combinatorial Optimisation, Lac Noir, Switzerland, 2000.

- [8] Yu-Kwong Kwok and Ishfaq Ahmad. Static Scheduling Algorithms for Allocating Directed Task Graphs to Multiprocessors. ACM Comput. Surv., 31(4):406–471, December 1999.

- [9] Kaushik Ravindran. Task allocation and scheduling of concurrent applications to multiprocessor systems. ProQuest, 2008.

# Pipelined Scheduling of Acyclic SDF Graphs using SMT Solvers

Pranav Tendulkar, Peter Poplavko, Oded Maler VERIMAG Lab (CNRS, University of Grenoble), France

Abstract—We consider compile-time multi-core mapping and scheduling problem for synchronous dataflow (SDF) graphs, proved an important model of computation for streaming applications, such as signal/image processing and video/image coding. In general the real-time constraints for these applications include both the task periods / throughput and the deadlines / latency. The deadlines are typically larger than the periods, which enables pipelined scheduling, allowing concurrent execution of different iterations of an application. A majority of algorithms for scheduling SDF graphs on a limited number of processors do not consider both latency and period real-time constraints at the same time. For this problem, we propose an efficient method based on SMT (satisfiability modulo theory) solvers. We restrict ourselves to periodic scheduling and acyclic graphs, giving up some efficiency for the sake of simplicity. We present an approach to encode the pipelined scheduling problem and demonstrate its practicality on Kalray MPPA-256 multi-core platform by executing various benchmarks according to the optimal schedules.

#### I. INTRODUCTION

Streaming applications process streams of data of indefinite length, where output stream(s) are function(s) of input streams. Typical examples are digital signal processing (DSP) applications, video/audio (de-)coding, digital radio and television applications [11]. Such applications have high computational demands and hence they are often implemented in dedicated hardware. However, the semiconductor technology advances make it worthwhile to port many such applications to programmable parallel architectures, such as multi-cores. To meet the performance targets on programmable hardware, it is crucial to make use of task parallelism through optimizing compiler tools. To this end, the designers represent their application by a model of computation that exposes the parallelism. The streaming applications can be conveniently expressed using dataflow models, such as synchronous dataflow graph (SDF) [4]. Several multi-core compilers for SDF and other dataflow models have been proposed, e.g., StreamIt [11]. This paper contributes to SDF compiler optimization to satisfy realtime constraints on M identical shared-memory processors. For simplicity, we restrict ourselves to acyclic graphs (i.e., all feedback loops are hidden inside the graph nodes).

In real-time systems, for given limited set of processors the tasks should satisfy constraints on both throughput (*i.e.*, period) and latency (*i.e.*, response time, deadline). What makes the problem harder is the typical lack of support of task preemption in DSP multi-cores, which invalidates many real-time scheduling policies, such as EDF, making it computationally hard

Research supported by the European ICT Collaborative Project no. 288175 (CERTAINTY).

to analyze the schedulability. Moreover, even if preemptions were allowed, another problem is that DSP applications are *task graphs* and not independent tasks, which makes it hard to compute the response times. Therefore, many scheduling algorithms for DSP multi-cores are non-preemptive and they ignore latency and focus on throughput *e.g.*, [3]. Satisfying throughput, latency and processor count constraints at the same time is a hard combinatorial problem rarely addressed in the literature, especially if one tries to obtain or approximate the exact solution. For example, [6] approximates a similar problem using classical preemptive scheduling techniques.

Due to hardness of this problem, generic constraint solving techniques are typically applied for it, such as, SMT (Satisfiability Modulo Theory), ILP (integer linear programming), ASP (Answer Set Programming), and CP (constraint programming). For example [5] use SMT solvers and propose unfolding method for a problem similar to ours, but not considering specific constraints for SDF graphs. In our previous work [9], we apply SMT solvers for mapping and scheduling a (subclass of) acyclic SDF graphs, but we still focused on latency constraint and ignored the throughput constraint. Though we convert SDF graphs into task graphs (also known as homogeneous (HSDF) graphs), we propose task symmetry breaking constraints that use the information of the original (multi-rate) SDF graph actors to speed up the search for solutions. In this paper, we propose extensions of that work for period/throughput, assuming pipelined scheduling, i.e., the period can be smaller than the latency. For simplicity, we restrict ourselves to *strictly* periodic schedules, i.e., schedules where task graph iterations are spawned at equal time intervals. However, we believe that we do not loose much efficiency with this assumption because even self-timed solutions are eventually periodic, though not necessarily strictly periodic, but in general, multi-periodic, *i.e.*, imposing a period every K iterations for some  $K \in \mathbb{N}$ .

We propose a new technique called 'period locality' for pipelined scheduling of SDF graphs. The proposed method represents the pipelined scheduling by a significantly simpler set of SMT constraints than the comparable encoding of unfolding [5] or modulo scheduling [10]. It also offers solutions that are sustainable to period variations for the fixed latency, in exchange of possible loss of optimality.

This technique was implemented in our tool StreamExplorer [7] and we perform experiments on the benchmarks from StreamIt and we validate our results by deploying them on a Kalray MPPA-256 multi-core processor architecture [1]. We observe that the error in prediction of period using a single cluster inside the platform is less than 15%.

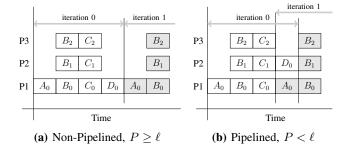

Fig. 1: Periodic Schedule Examples for an SDF Graph

#### II. SYNCHRONOUS DATAFLOW GRAPHS

**Definition II.1** (Acyclic SDF Graph). An acyclic SDF graph is a tuple S=(V,E,d,r) where (V,E) is a connected finite direct acyclic graph (DAG) whose nodes are repeatedly executed processes (actors) and edges are FIFO (first-in-first-out) channels,  $d:V\to\mathbb{R}_+$  is a function assigning an execution time to each node,  $r:E\to\mathbb{N}_+\times\mathbb{N}_+$  assigns pairs of token production/consumption rates to channels. We use the notation  $r(u,v)=(\alpha(u,v),\beta(u,v))$ . The meaning of  $\alpha$  is the number of data tokens produced to the channel at the end of each execution of actor u, and  $\beta$  is the number of data tokens consumed at the start of each execution of actor v. An SDF graph with r(e)=(1,1) for every e is called a task-graph and is denoted by  $T=(U,\mathcal{E},\delta)$ , renaming the first three tuple components and skipping the implicit component r.

We deviate from the common definition of SDF graph by forbidding cyclic paths and initial tokens. This is not due to any fundamental restrictions, but certain parts of the theory, mentioned later, need to be extended to support these features in future work.

A practical SDF graph should satisfy the *consistency* property [4], namely, it should be possible to execute the actors such that the total amount of data produced on each channel is equal to the total amount of data consumed. Let c(v) denote the number of times actor v is executed. The balance equation for an SDF channel (v,v') is written as:

$$c(v) \cdot \alpha(v, v') = c(v') \cdot \beta \ (v, v') \tag{1}$$

A graph is consistent if the balance equations have solutions c(v), and only the smallest positive integer solutions are considered. Executing every actor c(v) number of times is called *graph iteration*. The dependencies between actor executions in a graph iteration is modeled by equivalent task graph  $(U, \mathcal{E}, \delta)$ , where the nodes – called *tasks* – represent actor executions and edges represent precedence constraints. A consistent SDF graph can be expanded to a task graph, by well-known algorithm of deriving homogeneous SDF graph, see *e.g.*, [10]. In the derived task graph, every actor v is expanded into c(v) tasks:  $U_v = \{v_1, v_2, \ldots\}$ .

#### III. SMT ENCODING OF THE SCHEDULING PROBLEM

A problem instance of the scheduling problem consists of an acyclic SDF graph S and the costs. Though for scheduling

not the SDF graph itself, but the derived task graph is used, still we exploit the relation between these graphs for symmetry breaking in the solution space. The costs are the number of processors M, the latency  $\ell$ , and, period P. The primary decision variables for the scheduling problem are the task start times, s(u), and task mapping to processors,  $\mu(u)$ , assuming real  $s(u) \in \mathbb{R}_{\geq 0}$  and integer  $\mu(u) \in \mathbb{N}_+$ . A scheduling interval for task u is interval [s(u), e(u)), where  $e(u) = s(u) + \delta(u)$ . We assume non-preemptive scheduling, and hence the task executes entirely inside this interval. Note that the scheduling is assumed periodic, so a task scheduled at s(u) is also scheduled at s(u) + P, s(u) + 2P, etc., where P is period.

A schedule is *realizable*, if the tasks mapped to the same processor do not overlap in time. In addition, to be *feasible* it should respect tasks dependencies and the cost constraints. We define a realizable and feasible schedule in terms of constraints presented to the SMT solver tools. To express the scheduling constraints, it is convenient to define the following predicate:

$$\psi_{u,u'}: e(u) \le s(u')$$

This predicate states that the scheduling interval of task u' follows after the interval of task u.

The following constraint is necessary to ensure that the schedule is realizable [5]:

$$\varphi_{\mu}: \bigwedge_{u \neq u' \in U} (\mu(u) = \mu(u')) \Rightarrow \psi_{u,u'} \lor \psi_{u',u}$$

$\varphi_{\mu}$  is called *mutual exclusion constraint*. It asserts that the scheduling intervals of two tasks running on the same processor are mutually exclusive.

The task graph dependencies are specified by precedence constraints:

$$\varphi_{\epsilon}: \bigwedge_{(u,u')\in\mathcal{E}} \psi_{u,u'} \tag{2}$$

We define two cost constraints: one for the *latency* (termination of the last task), denoted  $\ell$ , and the other one for the number of *processors* used, denoted M:

$$\zeta_{\ell}: \bigwedge_{u \in U} e(u) \le \ell \land \zeta_{M}: \bigwedge_{u \in U} \mu(u) \le M$$

Putting all constraints together, we have the following encoding for the scheduling problem:

$$\Phi_{\mu\epsilon\ell M}: \varphi_{\epsilon} \wedge \varphi_{\mu} \wedge \zeta_{\ell} \wedge \zeta_{M} \tag{3}$$

In addition, we assert the processor and task symmetry breaking constraints in order to accelerate the search for solutions [9]. In particular, the task symmetry breaking constraints sort the schedule in the order compatible with the task index:

$$\bigwedge_{v \in V} \bigwedge_{v_h, v_{h+1} \in U_v} s(v_h) \le s(v_{h+1})$$

where h is the index of task appearance in the 'classical' SDF graph sequential schedule with FIFO communication on the channels [10]. We prove a theorem that these constraints do not eliminate any feasible costs [9], [10]. Note that it is here where we exploit the connection of the derived task graph to its SDF origin. Note also that the task symmetry theorem would

<sup>&</sup>lt;sup>1</sup>mostly referred to as homogeneous SDF graph

need to be revisited and generalized if we considered pipelined scheduling of SDF graphs that contain initial tokens. In fact, that is the reason why we do not yet support SDF graphs with feedback loops.

The encoding presented in this section is sufficient for non-pipelined scheduling, illustrated in Fig. 1a. However for pipelined scheduling, these constraints are not sufficient.

#### IV. PIPELINED SCHEDULING

In pipelined scheduling the graph iterations follow with a period that is smaller than the latency, so they can overlap in time, Fig 1b. The constraints  $\varphi_{\mu}$  presented in the previous section ensure mutual exclusion inside every iteration but not between the iterations.

We introduce a novel approach of encoding mutual exclusion in order to produce a pipeline schedule. We call this method  $period\ locality$ . The idea is to use the same mutual exclusion constraints as the non-pipelined scheduling, but to restrict the schedule such that different iterations cannot compete for processors. For this we require that all task scheduling intervals assigned to the same processor fit within a timing interval of length P.

$$\varphi_{\lambda}: \bigwedge_{u,u' \in U} (\mu(u) = \mu(u')) \Rightarrow e(u) - s(u') \le P$$

In a strictly periodic schedule with period P this condition eliminates the inter-iteration processor conflicts. Hence, we have the following encoding of the period locality method (if we ignore symmetry breaking):

$$\Phi_{\lambda\mu\epsilon\ell M}:\varphi_{\lambda}\wedge\varphi_{\epsilon}\wedge\varphi_{\mu}\wedge\zeta_{\ell}\wedge\zeta_{M}$$

The period locality is a heuristic, as it restricts the periodic schedule such that the iterations do not overtake each other on a processor. One can construct manual examples that show that this restriction may eliminate optimal periodic scheduling solutions. Nevertheless, for practical benchmarks, exact encoding methods such as unfolding and modulo scheduling do not show any advantage in quality of solutions, but require a much more complex encoding. Apparently, the higher complexity of the exact methods does not typically lead to significantly worse solver computation times in practice, though it may lead to higher solver memory demands [10]. The main advantage of period locality is, however, that it possesses period monotonicity property<sup>2</sup>, meaning that if a given period is feasible then larger periods are feasible as well while reusing the same problem solution and thus keeping intact the other costs such as latency and processor count. Monotonicity is important for efficient design space exploration for cost trade-offs, because (in)feasibility of some points implies (in)feasibility for the dominated (or dominating) cost points [9].

For the cost trade-off exploration, in this paper we consider two costs: the number of processors M and the period P, fixing the latency to an upper bound  $\ell_{\rm max}$ , computed by [10]:  $2(\Omega+1)P$ , where  $\Omega$  is a maximal number of edges in an SDF graph path. The scheduling problem gets significantly

<sup>2</sup>probably related to so-called schedule sustainability

more difficult if the latency constraint  $\ell$  is below this value:  $\ell < \ell_{\rm max}$ , whereas when  $\ell \geq \ell_{\rm max}$ , one can decouple mapping and processor scheduling without compromising the latency constraint. The mapping would be done by load balancing, ensuring the sum of task execution times per processor does not exceed P [3]. The scheduling would be done after mapping by maximal re-timing, *i.e.*, splitting the time axis into equal intervals of length P and assigning every task to the interval that follows immediately after the interval of its latest predecessor [10]. Comparing the SMT solver efficiency between this approach and period locality at  $\ell_{\rm max}$  is future work. Note that for generalizing this method to cyclic SDF graphs one would have to reconsider the definition of  $\ell_{\rm max}$ .

#### V. EXPERIMENTS

For pipelined scheduling problem, using our tool [7], we investigate the performance of SMT solver when applied for multi-criteria cost optimisation problems. We validate the computed solutions by deploying the application benchmarks on a single shared-memory cluster of the Kalray MPPA-256 platform [1]. Extending the pipelined scheduling to multiple clusters is a non-trivial task, requiring co-scheduling of tasks and communication transfers [8], which is currently limited to non-pipelined scheduling. From the solution obtained from the SMT solver, our framework uses the task-to-processor mapping and ordering and lets the tasks synchronize their communication at run-time. In a single cluster, we execute the application for a configured number of iterations in a self-timed way and measure the period in which every task executes. The maximum value over all tasks is taken into account.

Maximal actor execution times obtained from measurements are used in the scheduling constraints. The costs to minimize are the period and the number of allocated processors at  $\ell_{\rm max}$  latency<sup>4</sup>. Within a certain predefined timeout a query to the SMT solver should provide a **sat** or **unsat** answer, *i.e.*, satisfiable (feasible) and non-satisfiable (unfeasible). The solver may also give a **timeout** answer when it cannot conclude on the feasibility within the given time. Our goal is to find the closest approximation of the Pareto front possible, for which we used a *grid based exploration strategy* [9]. Our benchmarks consist of JPEG decoder and number of benchmarks from StreamIt [11], [8].

All the experiments were performed using the Z3 Solver [2] version 4.1 running on a Linux machine with *Intel Core i7* processor at 1.73 GHz with 4 GB of memory. The time out per query is 3 minutes while we keep the global exploration timeout to be 10 minutes.

1) Radix Sort: We explain the experiments with the running example of Radix Sort benchmark, an application that sorts integers. It consists of chain of 11 radix actors connected between the source and sink actors.

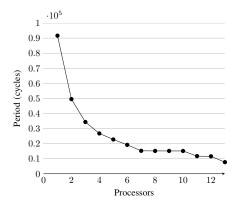

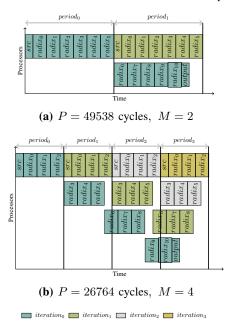

Figure 2 shows the results obtained for the two-dimensional cost space exploration of the period and the processors used. We can observe the trade-off between the two. We show an example schedule in Figure 3 for two and four processors. We can see how the solver is able to pack multiple iterations

<sup>&</sup>lt;sup>3</sup>positioning inside the interval is not important

<sup>&</sup>lt;sup>4</sup>see [10] for experiments at  $\ell < \ell_{\rm max}$

Fig. 2: Radix Sort: Processors used vs Period exploration

Fig. 3: Radix Sort : schedule for 2 and 4 processors

together. The amount of overlap between different iterations has increased when more processors are used. This also implies that the four-processor schedule requires larger communication buffers than the two-processor one, as more iterations run concurrently. However taking into account the communication buffer size together with the three other costs in pipelined scheduling is future work.

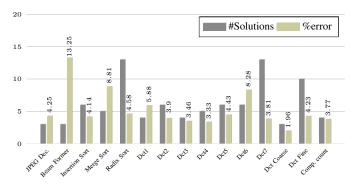

2) Other benchmarks: For the other benchmarks we perform the same experiment, i.e., approximating the Pareto front and deploying the optimized solutions on the MPPA-256 cluster. Figure 4 shows the results for different benchmarks. We plot the number of solutions obtained for every benchmark and the maximum error as mismatch between the solverpredicted and measured period on the Kalray platform. The maximum error observed is 13.25% in case of BeamFormer application. There are two sources of error in our experiments. One is that we don't model the conflicts due to concurrent memory accesses by the processors. Secondly, Beamformer application has 53 tasks, which is relatively large. The cost space exploration experiences multiple solver timeouts, which leads to very loose predictions of feasible schedule periods. Since we execute them in a self-timed way the measured period is often much less than the predicted one in this benchmark.

Fig. 4: Application benchmarks: maximum error for predicted vs. measured period

#### VI. CONCLUSIONS

In this paper we applied SMT solvers to address the pipelined scheduling problem for acyclic SDF graphs on shared-memory multi-cores with identical processors. We also evaluated our approach for a multi-core platform, showing good accuracy. Hereby, we considered *throughput* (*i.e.*, period), *latency* and *processor count* costs simultaneously, a problem that is rarely addressed in the literature.

We proposed the *period locality* heuristic, whose main advantage compared to exact methods is monotonicity, required for efficient design space exploration. We implemented this technique in our tool StreamExplorer [7] and evaluated it on a multi-core platform.

#### REFERENCES

- B. de Dinechin et al. A clustered manycore processor architecture for embedded and accelerated applications. In *High Performance Extreme* Computing Conference (HPEC), 2013 IEEE, pages 1–6, 2013.

- [2] L. de Moura and N. Bjorner. Z3: An efficient SMT solver. In TACAS, 2008.

- [3] M. V. Kudlur. Streamroller: A Unified Compilation and Synthesis System for Streaming Applications. PhD thesis, The University of Michigan, 2008.

- [4] E. Lee and D. Messerschmitt. Synchronous data flow. Proceedings of the IEEE, 75, 1987.

- [5] J. Legriel and O. Maler. Meeting deadlines cheaply. In ECRTS, 2011.

- [6] D. Liu, J. Spasic, J. T. Zhai, T. Stefanov, and G. Chen. Resource optimization for csdf-modeled streaming applications with latency constraints. In *Proceedings of the Conference on Design, Automation & Test in Europe*, DATE '14, pages 188:1–188:6, 3001 Leuven, Belgium, Belgium, 2014. European Design and Automation Association.

- [7] P. Tendular. Streamexplorer tool, http://www-verimag.imag.fr/ poplavko/streamexplorer.html.

- [8] P. Tendulkar, P. Poplavko, I. Galanommatis, and O. Maler. Many-core scheduling of data parallel applications using SMT solvers. In Conf. on Digital System Design, DSD 14, Proc. IEEE, 2014.

- [9] P. Tendulkar, P. Poplavko, and O. Maler. Symmetry breaking for multicriteria mapping and scheduling on multicores. In Formal Modeling and Analysis of Timed Systems (FORMATS'13), 2013.

- [10] P. Tendulkar, P. Poplavko, and O. Maler. Strictly periodic scheduling of acyclic synchronous dataflow graphs using SMT solvers. Technical Report TR-2014-5, Verimag, 2014.

- [11] W. Thies and S. Amarasinghe. An empirical characterization of stream programs and its implications for language and compiler design. In PACT, 2010.

# Compile-Time Mapping of Dataflow Applications with Buffer Minimization

Youen LESPARRE and Alix MUNIER-KORDON

Sorbonne Universités UPMC Univ Paris 06 UMR 7606, LIP6, F-75005, Paris, France

Email: name.lastname@alsoc.lip6.fr

Jean-Marc DELOSME **IBISC** Université d'Évry-Val-d'Essonne 91025 Évry, France Email: delosme@ibisc.univ-evry.fr

Abstract—The problem of mapping dataflow applications on multi-core chips is notoriously difficult. This difficulty is compounded with the fact that the graphs describing the applications of interest are becoming very large. This paper proposes an approach which ensures that the size of the description of the mapping problem grows only polynomially with respect to the sizes of the graphs describing the application and the architecture. The application graphs considered in this paper are synchronous data flow graphs (SDFG) and the architectures are multi-cluster arrays of identical processors. The key idea is to apply a previously obtained polynomial condition of liveness to the SDFG describing the mapped application. This permits a formulation of the mapping problem as an Integer Linear Program whose objective is the minimization of buffer memory and whose size is polynomial in the sizes of the application and architecture graphs.

#### I. Introduction

Keeping pace with the evolution of multi-core chips and the advent of many-core architectures [4], dataflow applications are broken down into numerous computation tasks, or actors, to be assigned to multiple on-chip processors. Finding an efficient algorithm to map these applications on clustered architectures, scalable for many cores, such as Kalray MPPA-256, STHORM or CoMPSoC, is difficult as this task encompasses the assignment of many actors to the processing resources and their scheduling under multiple resource constraints.

Synchronous Dataflow Graphs (SDFG), introduced in [9], are commonly used to model dataflow applications. They express an application with actors (nodes) and communications of data items between pairs of actors (arcs). Whenever an SDFG is consistent [9], it is possible to find an initial distribution of data items over the arcs, or initial marking, that ensures liveness and, hence, the existence of solutions to the scheduling problem [2]. In order to obtain good quality solutions, several methods have been recently proposed that jointly resolve the actor-to-resource assignment and the scheduling problem. Some authors [5], [8], [12] consider only homogeneous SDFGs (HSDFG), whose actors produce for (consume from) other actors a single data item at a time. By applying a simple transformation to a given consistent SDFG, an equivalent homogeneous SDFG may be obtained whose size is, however, exponential with respect to the SDFG's. This limits the scalability of HSDFG-based mapping methods, such as [3], where nodes and arcs are added to the HSDFG equivalent of the application's SDFG in order to model each candidate mapping and compute the associated throughput.

An alternative is to bound the throughput from below by computing a schedule, see [14], and [6] for acyclic SDFGs.

To overcome the scalability problem associated to the use of the HSDFG model, a simplified model is used in [13] to evaluate the volume of the communications between two adjacent actors. Actors are assigned to processors under resource constraints in order to minimize the bandwidth between the processors. This technique gives coarser solutions with a better scalability (although the underlying problem remains NP-complete). Our model is similar but with a finer evaluation of the memory requirements.

We present in this paper a new analysis of the mapping problem on a clustered multi-core architecture using the SDFG model with bounded buffers. Instead of being transformed into an HSDFG, the SDFG is just "normalized" [11], [10]. Normalization, a simple scaling transformation applicable to any consistent SDFG, makes the weights on the arcs adjacent to an actor—the numbers of data items produced or consumed on each arc—all equal. It can be performed in polynomial time and does not increase the size of the model. Its main practical interest is that it simplifies live initial marking and throughput computation. Since it is reversible, all the mapping computations may be performed on normalized SDFGs, thus we shall assume in the paper that the SDFGs are normalized.

The architecture is a distributed memory architecture consisting of n equal tiles, the clusters, with limited memory (and limited processor count). They communicate by a NoC and each one contains an amount of memory equal to  $\Delta^{max}$  to handle communications. Our goal is to minimize the overall memory required for communication between processor clusters while ensuring that the mapped application be live.

The application graph is supposed to fulfill the sufficient condition of liveness from [10]. Whenever a buffer is needed between two clusters, lower bounds on the amount of memory reserved in each cluster to implement the buffer are computed which guarantee that liveness is preserved. A simplified model issued from graph theory is then considered using these bounds to solve the global optimization problem.

The paper is organized as follows. The Synchronous Dataflow Graph model is introduced in Section II. In Section III, after a study of the memory needed when there is a single buffer between two clusters, a set of conditions on the memory required in order to fulfill the sufficient condition of liveness for the whole SDFG is derived, and a simple solution is proposed. Section IV presents two equivalent models for the global optimization problem. The first proceeds from graph

theory while the second formalizes the first using Integer Linear Programming. Section V is our conclusion.

#### II. DATAFLOW MODELS

#### A. Synchronous Dataflow Graph model

In a Synchronous Dataflow Graph, nodes represent actors, which are programs that are executed repeatedly, and arcs represent data communications. Data are stored in a first-in first-out (FIFO) memory during communication. The SDFG is normalized as shown in [11]: as a result, an integer value Z>0 is associated to each actor t so that, each time actor t is executed, Z data items are consumed (resp. produced) on each of its input (resp. output) buffers. The initial marking  $M_0(a)$  of an arc a represents the normalized number of data items initially present in the associated buffer.

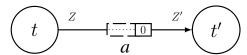

Fig. 1. A buffer a with initial marking  $M_0(a) = 0$  between two actors of an SDFG, t, with production weight Z, and t', with consumption weight Z'.

#### B. Liveness

A dataflow graph is said to be live if all actors can be executed infinitely often. The liveness of a graph depends on its initial marking.

The most common ways to check the liveness of an SDFG are to compute a self-timed schedule or to expand the SDFG into its HSDFG equivalent [7]. However these methods have an exponential complexity, and their scalability is limited.

Another way is to evaluate the sufficient condition of liveness obtained in [10], which can be computed in polynomial time and, while not being necessary, is tight in practice. It has been implemented in the graph generator Turbine and used to generate live initial markings of SDFGs of up to 10,000 nodes [2]. In this paper this sufficient condition is supposed to be satisfied by the SDFG models of applications considered.

### III. EVALUATION OF THE OVERALL MEMORY FOR COMMUNICATIONS BETWEEN CLUSTERS

This section presents a simple solution to the problem of evaluating the memory needed for buffers between two different clusters. Subsection III-A presents the problem and some notations. Subsection III-B expresses a condition when there is a unique buffer between two clusters. Subsection III-C extends the condition to several buffers between two clusters. Subsection III-D presents a feasible solution that will be used to express the subsequent global optimization problem.

#### A. Problem and notations

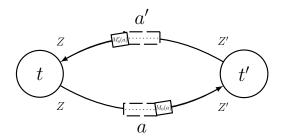

The application graph is an SDFG,  $\mathcal{G}=(\mathcal{T},\mathcal{B},M_0)$ , with  $\mathcal{T}$  the set of actors,  $\mathcal{B}$  the set of buffers and marking function  $M_0$  giving the initial amount of data in the buffers. Any bounded buffer  $a=(t,t')\in\mathcal{B}$ , such that the number of data items it can contain is bounded by a fixed value B(a), can be modeled by a backward arc a'=(t',t) with  $M_0(a')=B(a)-M_0(a)$ , as shown in Fig. 2.

Fig. 2. A bounded buffer, with a the original arc and a' the backward arc.

Two assumptions are made on the buffer-aware SDFG  $\overline{\mathcal{G}} = (\mathcal{T}, \overline{\mathcal{B}}, M_0)$  obtained when adding all the backward arcs:

- 1) The initial marking  $M_0(a)$  of any buffer a=(t,t') is divisible by  $gcd_a=gcd(Z,Z')$ , the greatest common divisor of the weights of the actors. Indeed, replacing  $M_0(a)$  by  $\lfloor M_0(a)/gcd_a \rfloor \cdot gcd_a$  does not change the behavior of the SDFG [10].

- 2)  $\overline{\mathcal{G}}$  satisfies the sufficient condition of liveness found in [10]. Defining the height of an arc a=(t,t') as  $H(a)=M_0(a)+gcd_a-Z'$  and the height of a cycle  $\mu$  as  $H(\mu)=\sum_{a\in\mu}H(a)$ , this condition states that the height of any cycle  $\mu$  of  $\overline{\mathcal{G}}$  satisfies  $H(\mu)>0$ .

The set of clusters of the many-core architecture is denoted by  $\mathcal{C}$ , with  $|\mathcal{C}| > 1$ , and the overall memory available in each cluster is bounded by a fixed value  $\Delta^{max}$ . The size of the data items stored in buffer  $a \in \mathcal{B}$  is denoted by  $\theta(a)$ . If the two adjacent actors t and t' of a = (t, t') are in a same cluster, the resource requirement for a is just  $\theta(a) \cdot (M_0(a) + M_0(a'))$ . Otherwise, the amount of memory needed in each cluster to ensure liveness is evaluated as shown in the rest of the section.

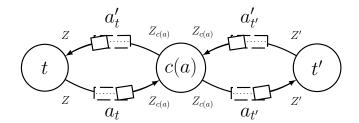

#### B. Case of a single bounded inter-cluster buffer

Consider now a bounded buffer a=(t,t') with t and t' assigned to different clusters, c and c'. An actor c(a) is inserted to perform the communication of data from c to c' via two bounded buffers,  $a_t$  and  $a_{t'}$ , as depicted in Fig. 3.

The weight  $Z_{c(a)}$  of c(a) and the initial markings of  $a_t$  and  $a_{t'}$  are determined by minimizing the buffer sizes  $B(a_t) = M_0(a_t) + M_0(a_t')$  and  $B(a_{t'}) = M_0(a_{t'}) + M_0(a_{t'}')$  while satisfying the sufficient condition of liveness. We shall see that if we set  $Z_{c(a)} = gcd_a$  the equations will be greatly simplified.

Fig. 3. A bounded inter-cluster buffer. The buffer a=(t,t') is split between the two clusters. The part belonging to the cluster where actor t resides is represented by arc  $a_t$  (and backward arc  $a_t'$ ) while the part belonging to the cluster where t' resides is represented by  $a_{t'}$  (and  $a_{t'}'$ ).

A sufficient condition of liveness for a single inter-cluster buffer is given in the following theorem. **Theorem** 1: A single inter-cluster buffer a=(t,t') with  $Z_{c(a)}=gcd_a$  is live if  $M_0(a_t)+M_0(a_t')\geq Z$  and  $M_0(a_{t'})+M_0(a_{t'}')\geq Z'$ .

*Proof:* Let  $\mu_1=(t,a_t,c(a),a_t',t)$  and  $\mu_2=(t',a_{t'}',c(a),a_{t'},t')$  be the two elementary cycles of the inter-cluster buffer. The sufficient condition of liveness of the buffer is that  $H(\mu_1)>0$  and  $H(\mu_2)>0$ . Now,  $H(\mu_1)=H(a_t)+H(a_t')>0$  is strictly equivalent to

$$M_0(a_t) + gcd(Z, Z_{c(a)}) - Z_{c(a)} + M_0(a'_t) + gcd(Z_{c(a)}, Z) - Z > 0.$$

Since  $Z_{c(a)}=\gcd_a=\gcd(Z,Z'),\ \gcd(Z,Z_{c(a)})=\gcd_a$  and the inequality simplifies to

$$M_0(a_t) + M_0(a'_t) + gcd_a - Z > 0.$$

Since, by our first assumption on  $\overline{\mathcal{G}}$ ,  $M_0(a_t) + M_0(a_t') - Z$  is divisible by  $gcd_a$ , this inequality is equivalent to

$$M_0(a_t) + M_0(a_t') - Z \ge 0.$$

The other inequality results similarly from  $H(\mu_2) > 0$ .

#### C. General case

Define a communication-aware graph  $\overline{\mathcal{G}}_c = (\mathcal{T}_c, \overline{\mathcal{B}}_c, M_0)$  as an SDFG obtained from the buffer-aware graph  $\overline{\mathcal{G}}$  by splitting every bounded inter-cluster buffer a=(t,t') as done in the previous subsection. The next theorem gives conditions on  $\overline{\mathcal{G}}_c$ 's initial marking  $M_0$  ensuring that  $\overline{\mathcal{G}}_c$  satisfies the sufficient condition of liveness from [10].

**Theorem** 2: Consider a communication-aware graph  $\overline{\mathcal{G}}_c = (\mathcal{T}_c, \overline{\mathcal{B}}_c, M_0)$  associated to a live buffer-aware graph  $\overline{\mathcal{G}} = (\mathcal{T}, \overline{\mathcal{B}}, M_0)$ . The graph  $\overline{\mathcal{G}}_c$  is live if, for every bounded inter-cluster buffer  $a = (t, t') \in \mathcal{B}$ , in addition to having  $Z_{c(a)} = gcd_a$  and the two inequalities of Theorem 1 satisfied, the inequalities  $M_0(a_t) + M_0(a_{t'}) \geq M_0(a)$  and  $M_0(a'_{t'}) + M_0(a'_t) \geq M_0(a')$  are satisfied.

*Proof:* With the assumption  $Z_{c(a)} = gcd_a$ , the two inequalities of Theorem 1 ensure that the liveness condition is satisfied for the two elementary cycles associated to each bounded inter-cluster buffer  $a=(t,t')\in\mathcal{B}$ . Consider now all the other elementary cycles introduced when there is more than one inter-cluster buffer between two clusters. Under the assumption that  $\overline{\mathcal{G}}$  satisfies the sufficient condition of liveness from [10], a sufficient condition of liveness for  $\overline{\mathcal{G}}_c$  can be expressed as  $H(a_t) + H(a_{t'}) \geq H(a)$  and  $H(a_t') + H(a_{t'}') \geq H(a')$  for every bounded inter-cluster buffer  $a=(t,t')\in\mathcal{B}$ . The first inequality is equivalent to

$$M_0(a_t) + gcd(Z, Z_{c(a)}) - Z_{c(a)} + M_0(a_{t'}) + gcd(Z_{c(a)}, Z') - Z' \ge M_0(a) + gcd(Z, Z') - Z'.$$

Since  $Z_{c(a)} = gcd(Z, Z') = gcd(Z, Z_{c(a)}) = gcd(Z_{c(a)}, Z')$ , this inequality simplifies to  $M_0(a_t) + M_0(a_{t'}) \ge M_0(a)$ . The second inequality is obtained in a similar manner.

#### D. A live initial marking for a bounded inter-cluster buffer

The following corollary exhibits a simple solution to the inequalities of Theorem 2.

**Corollary** 1: Consider a live buffer-aware graph  $\overline{\mathcal{G}} = (\mathcal{T}, \overline{\mathcal{B}}, M_0)$  and the associated communication-aware graph  $\overline{\mathcal{G}}_c = (\mathcal{T}_c, \overline{\mathcal{B}}_c, M_0)$  with the initial marking  $M_0(a_t) = M_0(a)$ ,  $M_0(a_t') = Z$ ,  $M_0(a_{t'}') = M_0(a')$  and  $M_0(a_{t'}) = Z'$  for every

inter-cluster buffer  $a=(t,t')\in\mathcal{B}$ . The graph  $\overline{\mathcal{G}}_c$  is live. Moreover, the buffer sizes  $B(a_t)=M_0(a_t)+M_0(a_t')$  and  $B(a_{t'})=M_0(a_{t'})+M_0(a_{t'}')$  verify

$$B(a_t) + B(a_{t'}) \le 2(M_0(a) + M_0(a')) + gcd(Z, Z').$$

*Proof:* One can easily check that the initial marking considered verifies the inequalities of Theorem 1 and 2. Let  $m = B(a_t) + B(a_{t'}) = M_0(a) + M_0(a') + Z + Z'$ . Since the buffer-aware graph  $\overline{\mathcal{G}} = (\mathcal{T}, \overline{\mathcal{B}}, M_0)$  verifies the sufficient condition of liveness, for the cycle of Fig. 2

$$M_0(a)+M_0(a')\geq Z+Z'-gcd(Z,Z'),$$

implying that  $m\leq 2(M_0(a)+M_0(a'))+gcd(Z,Z').$

The initial marking from Corollary 1 will be used in the next section to formalize the mapping problem.

#### IV. FORMULATION OF THE MAPPING PROBLEM

The mapping problem is formalized is this section. Subsection IV-A describes the problem, while Subsection IV-B models it using an Integer Linear Program of polynomial size.

#### A. Problem definition

The application is modeled by a live SDFG  $\mathcal{G} = (\mathcal{T}, \mathcal{B}, M_0)$ . The buffer-aware SDFG  $\overline{\mathcal{G}} = (\mathcal{T}, \overline{\mathcal{B}}, M_0)$  is derived from  $\mathcal{G}$  by adding reverse arcs and associated initial markings so that the sufficient condition of liveness of [10] be satisfied.

The buffer memory requirements for the application can be modeled using an undirected multigraph  $H=(\mathcal{T},\mathcal{E})$  whose nodes are the actors. To each arc  $a=(t,t')\in\mathcal{B}$  corresponds an edge  $e=\{t,t'\}\in\mathcal{E}$  with three associated values:

- S(e), the memory size required for arc a if t and t' are in the same cluster.  $S(e) = \theta(a) \cdot (M_0(a) + M_0(a'))$ , where a' = (t', t) is the reverse of arc a in  $\overline{\mathcal{G}}$ .

- $S_t(e)$ , and  $S_{t'}(e)$ , the memory sizes required for arc a in the cluster of t, and of t', if t and t' are not in the same cluster.  $S_t(e) = \theta(a) \cdot B(a_t)$  and  $S_{t'}(e) = \theta(a) \cdot B(a_{t'})$ , where, from Corollary 1, these values are set to  $B(a_t) = M_0(a) + Z$  and  $B(a_{t'}) = M_0(a') + Z'$ .

Note that  $\mathcal{E}$  is a multiset; thus, when both arcs (t,t') and (t',t) belong to  $\mathcal{B}$ , there are two instances of  $e=\{t,t'\}$  in  $\mathcal{E}$ . Sizes S(e),  $S_t(e)$  and  $S_{t'}(e)$ , are sums over all the instances of e.

A mapping consists in assigning the actors to the clusters. To each couple  $(t,c)\in\mathcal{T}\times\mathcal{C}$  is associated a binary variable  $x_{t,c}$  defined by

$$x_{t,c} = \begin{cases} 1 \text{ if actor } t \text{ is in cluster } c \\ 0 \text{ otherwise} \end{cases}$$

The mapping problem is to find the values  $x_{t,c} \in \{0,1\}$  for all the couples  $(t,c) \in \mathcal{T} \times \mathcal{C}$  such that the total additional memory (due to buffers split into two different clusters) is minimized under the constraints that each actor is assigned to one and only one cluster, and the total memory assigned in each cluster is bounded by  $\Delta^{max}$  (capacity constraint).

#### B. Integer Linear Programming Formulation

To each couple  $(e,c) \in \mathcal{E} \times \mathcal{C}$  are associated two binary variables  $s_{t,c}^e$ , where  $t \in e$ , defined as:

$$s_{t,c}^e \! = \! \begin{cases} 1 \text{ if } x_{t,c} = 1 \text{ and } x_{t',c} = 0, \text{ where } t' \in e \text{ and } t' \neq t, \\ 0 \text{ otherwise} \end{cases}$$

Lemma 1 expresses the relationship between  $s_{t,c}^e$  and  $x_{t,c}$ . It allows to compute  $s_{t,c}^e$  using Integer Linear Programming:

**Lemma** 1: For any edge  $e = \{t, t'\} \in \mathcal{E}$  and any cluster  $c \in C, s_{t,c}^e \ge x_{t,c} - x_{t',c}.$

*Proof:* If  $x_{t,c} = x_{t',c}$  then  $s_{t,c}^e = 0$  and the inequality is  $s_{t,c}^e \geq 0$ . Now, if  $x_{t,c} = 1$  and  $x_{t',c} = 0$ ,  $s_{t,c}^e = 1$  and the inequality becomes  $s_{t,c}^e \geq 1$ . Lastly, if  $x_{t,c} = 0$  and  $x_{t',c} = 1$ ,  $s_{t,c}^e = 0$  and the inequality becomes  $s_{t,c}^e \geq -1$ . The inequality  $s_{t,c}^e \geq x_{t,c} - x_{t',c}$  is thus verified in all cases.

Lemma 2 allows to express the capacity constraint:

**Lemma** 2: For any couple  $(c,e) \in \mathcal{C} \times \mathcal{E}$ , the size of the memory allocated to edge e in cluster c is:

$$f(c,e) = \sum_{t \in e} s_{t,c}^e \cdot S_t(e) + \sum_{t \in e} (x_{t,c} - s_{t,c}^e) \frac{S(e)}{2}.$$

Proof: Three cases have to be considered:

- If  $x_{t,c} = x_{t',c} = 0$ , neither t nor t' is assigned to

- cluster c. Then  $s_{t,c}^e = s_{t',c}^e = 0$  and f(c,e) = 0. If  $x_{t,c} = x_{t',c} = 1$ , both t and t' are in c and so is the buffer associated to e. Then  $s_{t,c}^e = s_{t',c}^e = 0$  and f(c,e) = S(e)/2 + S(e)/2 = S(e).

- If  $x_{t,c} \neq x_{t',c}$ , suppose that  $x_{t,c} = 1$  and  $x_{t',c} = 0$  thus t is assigned to c but not t'. Then  $s_{t,c}^e = 1$  and  $s_{t',c}^e = 0$  hence  $f(c,e) = S_t(e)$ .

The lemma is thus verified.

The mapping problem may now be expressed as an Integer Linear Program as follows:

$$\text{minimize } \sum_{c \in \mathcal{C}} \sum_{e \in \mathcal{E}} \sum_{t \in e} s^e_{t,c} \cdot S_t(e)$$

under the constraints

$$\sum_{c \in \mathcal{C}} x_{t,c} = 1, \ \forall t \in \mathcal{T}, \tag{1}$$

$$s_{t,c}^e \ge x_{t,c} - x_{t',c}, \ \forall t \in e, \ \forall e = \{t, t'\} \in \mathcal{E}, \ \forall c \in \mathcal{C},$$

(2)

$$\sum_{e \in \mathcal{E}} f(c, e) \le \Delta^{max}, \ \forall c \in C,$$

$$(3)$$

$$x_{t,c} \in \{0,1\}, \forall c \in \mathcal{C}, \ \forall t \in \mathcal{T}$$

(4)

$$s_{t,c}^e \in \{0,1\}, \forall e \in \mathcal{E}, \ \forall c \in \mathcal{C}, \forall t \in \mathcal{T}.$$

(5)

The objective is the minimization of the memory used for the communications between clusters. Constraints (1) ensure that each actor is assigned to exactly one cluster. Constraints (2) express the relationships between the binary variables. Constraints (3) ensure that the limit  $\Delta^{max}$  of total memory in each cluster is not exceeded. Further constraints, such as  $\sum_{t \in \mathcal{T}} x_{t,c} \ge \sum_{t \in \mathcal{T}} x_{t,c'}$  where c immediately precedes c' in a total order on the clusters, could be added to reduce the number of equivalent solutions.

A key feature of our formulation is that the size of the program is polynomial. Indeed, the number of variables is  $|\mathcal{T}|$ .  $|\mathcal{C}| + |\mathcal{T}| \cdot |\mathcal{C}| \cdot |\mathcal{E}|$  while the number of equations is  $|\mathcal{T}| + |\mathcal{T}|$  $|\mathcal{C}| \cdot |\mathcal{E}| + |\mathcal{C}|$ .

#### V. CONCLUSION AND PERSPECTIVES

The problem of finding a mapping of an SDFG on a clustered architecture that minimizes the overall memory has been formulated as an Integer Linear Program of polynomial size in terms of the SDFG and architecture model sizes. The first perspective is to test the scalability of this method using a solver and develop efficient heuristics to solve the program on large instances. The evaluation of the memory size presented in Corollary 1 should also be improved. Two other interesting issues are the extension of this method to more widely applicable models such as the Cyclo-Static DataFlow Graphs [1] and the incorporation of a minimum throughput guarantee.

#### REFERENCES

- Greet Bilsen, Marc Engels, Rudy Lauwereins, and Jean A. Peperstraete. Cyclo-static data flow. IEEE Transactions on Signal Processing, pages 3255-3258, 1995.

- Bruno Bodin, Youen Lesparre, Jean-Marc Delosme, and Alix Munier-Kordon. Fast and efficient dataflow graph generation. In Proceedings of the 17th International Workshop on Software and Compilers for Embedded Systems, pages 40-49. ACM, 2014.

- Alessio Bonfietti, Luca Benini, Michele Lombardi, and Michela Milano. An efficient and complete approach for throughput-maximal SDF allocation and scheduling on multi-core platforms. In 13th Design, Automation & Test in Europe Conference (DATE), pages 897-902, 2010.

- Shekhar Borkar. Thousand core chips: a technology perspective. In Proceedings of the 44th annual Design Automation Conference, pages 746-749. ACM, 2007.

- Thomas Carle, Manel Djemal, Dumitru Potop-Butucaru, Robert De Simone, Zhen Zhang, et al. Off-line mapping of real-time applications onto massively parallel processor arrays. Research Report INRIA RR-8429, December 2013,

- Yuankai Chen and Hai Zhou. Buffer minimization in pipelined sdf scheduling on multi-core platforms. In 17th Asia and South Pacific Design Automation Conference, pages 127-132. IEEE, 2012.

- Amir Hossein Ghamarian, MCW Geilen, Twan Basten, Bart D Theelen, Mohammad Reza Mousavi, and Sander Stuijk. Liveness and boundedness of synchronous data flow graphs. In Formal Methods in Computer Aided Design, 2006. FMCAD'06, pages 68-75. IEEE, 2006.

- Tae ho Shin, Hyunok Oh, and Soonhoi Ha. Buffer optimal static scheduling with a throughput constraint for synchronous dataflow applications on multiprocessors. In 2010 International SoC Design Conference (ISOCC), pages 298-301, Nov 2010.

- Edward A. Lee and David G. Messerschmitt. Synchronous dataflow. Proceedings of the IEEE, 75(9):1235-1245, 1987.

- Olivier Marchetti and Alix Munier-Kordon. A sufficient condition for the liveness of weighted event graphs. European Journal of Operational Research, 197(2):532-540, September 2009.

- Olivier Marchetti and Alix Munier-Kordon. Cyclic scheduling for the synthesis of embedded systems. In Yves Robert and Frédéric Vivien, editors, Introduction to scheduling, pages 135-164. CRC Press, 2010.

- Orlando Moreira, J-D Mol, Marco Bekooij, and Jef Van Meerbergen. Multiprocessor resource allocation for hard-real-time streaming with a dynamic job-mix. In 11th Real Time and Embedded Technology and Applications Symposium, RTAS 2005., pages 332-341. IEEE, 2005.

- Oana Stan, Renaud Sirdey, Jacques Carlier, and Dritan Nace. A GRASP for placement and routing of dataflow process networks on many-core architectures. In 8th International Conference on P2P, Parallel, Grid, Cloud and Internet Computing (3PGCIC), pages 219-226. IEEE, 2013.

- Zheng Zhou, K. Desnos, M. Pelcat, J.-F. Nezan, W. Plishker, and S.S. Bhattacharyya. Scheduling of parallelized synchronous dataflow actors. In 2013 International Symposium on System on Chip (SoC), pages 1-10. IEEE, Oct 2013.

## Towards Translating FSM-SADF to Timed Automata

Mladen Skelin

Department of Engineering Cybernetics,

Norwegian University of Science and Technology

mladen.skelin@itk.ntnu.no

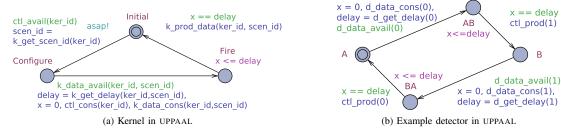

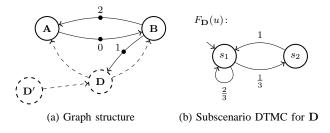

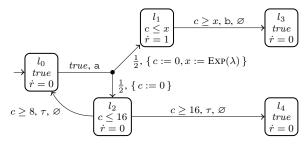

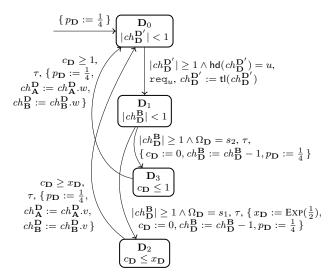

Abstract-Dataflow formalisms play a significant role in the areas of design and analysis of embedded streaming applications. These formalisms can roughly be split into static and dynamic ones. Static dataflow formalisms are highly analyzable, but due to their static nature are not able to capture the dynamism inherent to modern embedded streaming applications. Dynamic dataflow formalisms on the other hand provide a sufficient level of expressiveness to capture the application dynamism at the cost of reduced analyzability. The recently introduced finite state machine-based scenario aware dataflow (FSM-SADF) formalism provides a good trade-off between expressiveness and analyzability. This paper reports on the translation of the FSM-SADF formalism to timed automata (TA). In short, we propose a compositional translation from FSM-SADF to TA that enables computation of some quantitative and qualitative properties of the model not supported by the existing tools, in the UPPAAL model checker. We demonstrate our approach on an MPEG-4 case study which is a typical example of a streaming application from the multi-media domain.

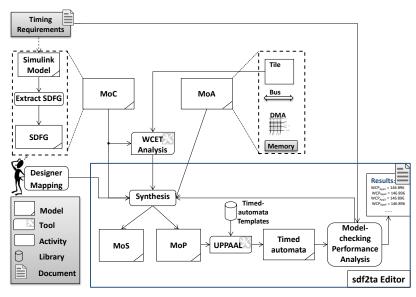

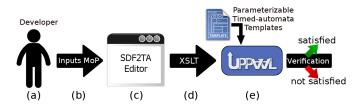

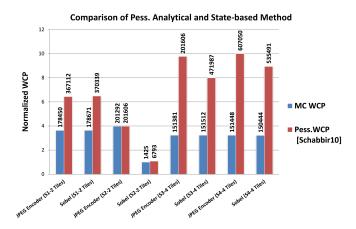

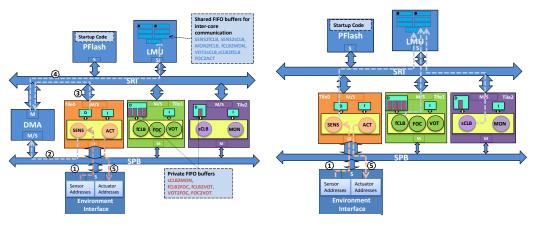

#### I. INTRODUCTION

Dataflow formalisms are widely used to design and analyze embedded streaming applications running on distributed platforms such as MPSoCs (Multi-Processor System on Chips). In general, dataflow formalisms take the form of a directed graph which consists of actors as vertices and channels as edges. Actors are computational entities that usually represent application sub-tasks, while channels are communicational entities used to communicate application, control and synchronisation data between actors. In dataflow, an actor firing is an indivisible quantum of computation during which an actor consumes a certain number of data values from its input channels and produces a certain number of data values on its output channels. These data values are abstracted into tokens and the consumption and production numbers are called *rates*. In timed dataflow formalisms, it takes some time for the actor firing to complete and this time duration is called the actor firing duration.