# CMOS Low-Noise Amplifier Design for Reconfigurable Mobile Terminals

vorgelegt von Diplom-Ingenieur Dariusz Pieńkowski

Von der Fakultät IV Elektrotechnik und Informatik der Technishen Universität Berlin zur Verleihung des akademischen Grades

Doktor der Ingenieurwissenschaften — Dr-Ing. —

genehmigte Dissertation

#### Promotionsausschuss:

Vorsitzender: Prof. Dr. Ing. H. Klar Gutachter: Prof. Dr. Ing. G. Böck Gutachter: Prof. Dr. Ing. P. Weger

Tag der wissenschaftlichen Aussprache: 03. Dez. 2004

Copyright © 2004 by Dariusz Pieńkowski All rights reserved

## Abstract

ommunication standards developed in Europe, Japan and USA are not compatible with each other. This is a profound drawback particularly in the digital cellular telephony, where there is no common standard up to now.

The variety of wireless standards leads to some disadvantages, therefore the need for reconfigurability seems to be evident. A reconfigurable terminal should be able to support different standards.

Reasonable integration of different standards may include standards, which belong to the same family (e.g., GSM), but are developed in different continents. Such terminals have been already produced and a broad offer exists on the market.

A rather new approach of the standard integration is the combination of different families of standards, for example between wireless data and digital cellular telephony like UMTS with WLAN or HIPERLAN. In this case, nearly all parameters defining a standard are different.

In the scope of this work the multistandard, reconfigurable terminal is considered that supports the OFDM based WLAN standards (IEEE802.11 and Hiperlan/2) and the CDMA based UMTS FDD standard. Special consideration has been made for the receiver of this terminal.

A reconfigurable hybrid architecture has been developed, rather than an architecture using many parallel switchable transceivers. Additionally to the hybrid architecture, a study on RF impairments is given.

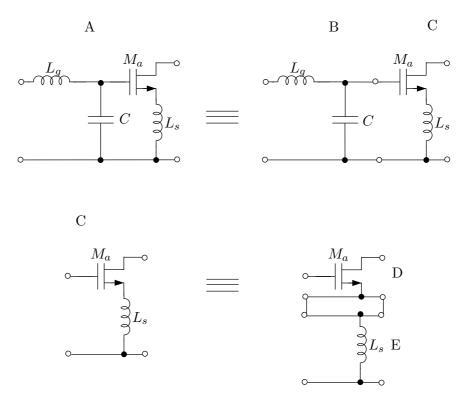

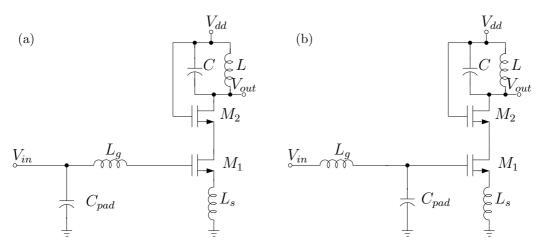

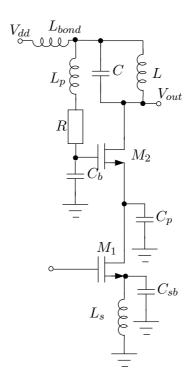

The second part of this work handles with transistor physics and low noise amplifier design for a reconfigurable receiver, defined earlier. Since the small FET sizes of state of the art sub-micron RF-MOS-technologies have low capacitance values, thus large inductors are needed for matching. Because of theirs large dimensions they are placed off-chip. For this reason, the pad capacitance can not be longer neglected in the design process. It is shown II Abstract

that the noise figure of low-noise amplifiers can be improved considerably by a proper choice of passive components. A design methodology is introduced, which reduces the equivalent noise resistance, and thus very good noise performance can be achieved in spite of rather poor noise matching.

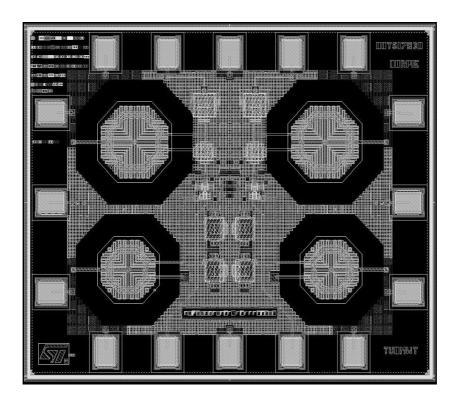

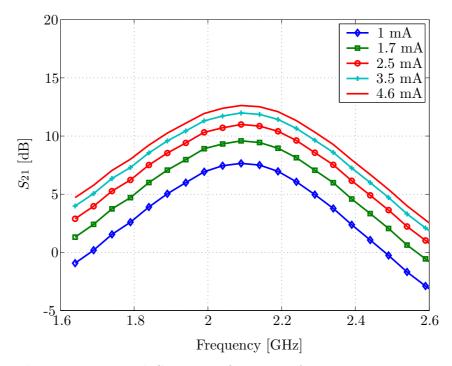

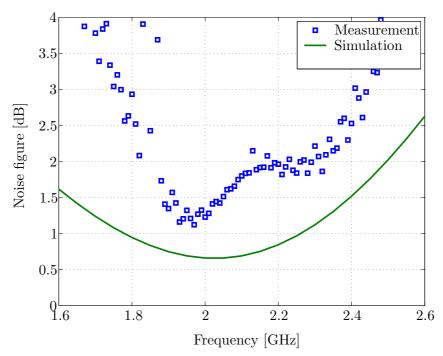

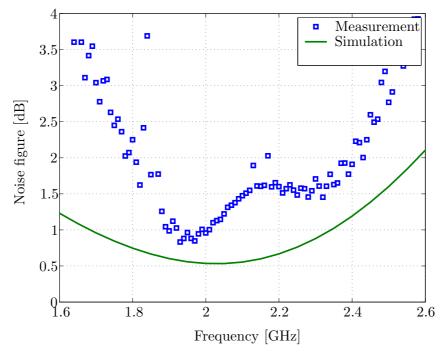

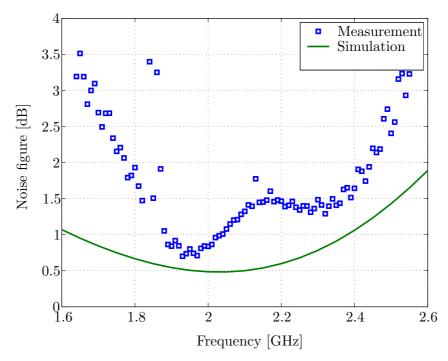

The measurements of the amplifier, in respect to the noise performance and power consumption, show very good results, one of the best ever reported. 0.76 dB noise figure and 12 dB gain were achieved at 2.14 GHz, 3.5 mA supply current and 1.2 V supply voltage.

# Acknowledgments

would like to thank my doctoral thesis supervisor Professor Georg Böck for his continuously support and many ideas that help me with work on this thesis.

I wish to acknowledge also Nokia Research Center Bochum, Germany. For the last three years, I have worked together with the Nokia Research Center, within the German funded BMBF-project "Software Defined Radio Based Architecture Studies for Reconfigurable Mobile Communication Systems" (RMS), No. 01 BU171. This thesis is partially based on the research carried out during this cooperation.

I also would like to thank my parents. Without their support in all aspect of my life, this thesis would never come true. I owe many very important things in my life to my parents, therefore I regret that my father had died before I have finished this thesis.

Finally I would like to thank my wife, Joanna for invaluable help and support. She has cheered me up during work on this thesis and during the long time of our separation, when every two weeks I travelled between Berlin and Warsaw back and forth. Actually, she has made almost all graphics in this thesis.

I can not forgot also my little daughter, Agata. Although unconscious of all the matter, she has also participated in writing this thesis. With his calmness, she let his father to go to sleep in the night. Therefore, I could finish faster this work. It is time now, to repay her for that.

This work is dedicated to her.

# Contents

| Abstr | act     |                                      | I   |

|-------|---------|--------------------------------------|-----|

| Ackno | wledgi  | ments                                | III |

| Chapt | er 1. I | Introduction                         | 1   |

| 1.1.  | Scope   | of This Work                         | 2   |

| Chapt | er 2. I | Reconfigurable Systems               | 5   |

| 2.1.  | Genera  | al Concepts in Multi-standard Radios | 6   |

|       | 2.1.1.  | One-Bit Reconfiguration              | 6   |

|       | 2.1.2.  | Software Defined Radio               | 8   |

|       | 2.1.3.  | Software Reconfigurable Radio        | 8   |

| 2.2.  | RF Re   | eceiver Requirements                 | 8   |

|       | 2.2.1.  | UMTS FDD                             | 8   |

|       | 2.2.2.  | WLAN                                 | 13  |

| 2.3.  | Recon   | figurable RF Receiver Architecture   | 16  |

| 2.4.  | LNA I   | Requirements                         | 21  |

| 2.5.  | RF Re   | elated Impairments                   | 22  |

|       | 2.5.1.  | Frequency Offset                     | 24  |

|       | 2.5.2.  | Phase Noise                          | 25  |

|       | 2.5.3.  | Direct Current Offset                | 26  |

|       | 2.5.4.  | I/Q Imbalance                        | 28  |

|       | 2.5.5.  | Nonlinearities                       | 29  |

| Chapt | er 3. I | Passive Devices                      | 33  |

| 3.1.  | Induct  | tors                                 | 33  |

|       | 3.1.1.  | Spiral Inductors                     | 33  |

|       | 3.1.2.  | Bond-wire Inductors                  | 36  |

| 3.2.  | MIM (   | Capacitors                           | 36  |

| 3.3.  |         | ors                                  | 38  |

| 2.4   | Doda    |                                      | 30  |

VI

| Chapt | er 4. RF MOSFET Devices                                        | 41  |

|-------|----------------------------------------------------------------|-----|

| 4.1.  | Long-channel Regime                                            | 41  |

| 4.2.  | Short-channel Regime                                           | 43  |

|       | 4.2.1. Velocity Saturation                                     | 43  |

|       | 4.2.2. Threshold Reduction                                     | 44  |

|       | 4.2.3. Hot Carriers                                            | 44  |

| 4.3.  | Radio Frequency Operation                                      | 45  |

|       | 4.3.1. MOSFET Capacitances                                     | 45  |

|       | 4.3.2. Distributed Gate Resistance                             | 46  |

|       | 4.3.3. Channel Resistance and Transit Time Effects             | 48  |

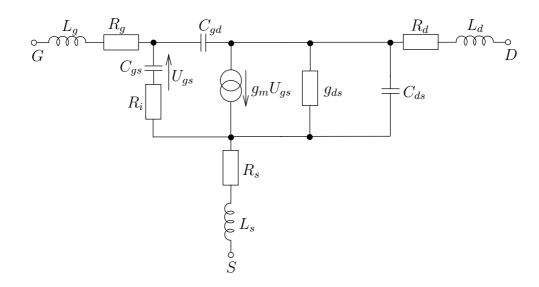

|       | 4.3.4. Small-signal RF-model                                   | 50  |

|       | 4.3.5. Noise Model of a MOSFET                                 | 50  |

|       | 4.3.6. Noise Matching                                          | 53  |

| Chapt | er 5. Noisy two-ports                                          | 57  |

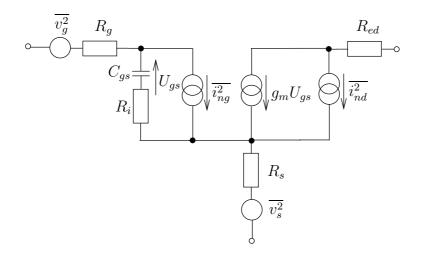

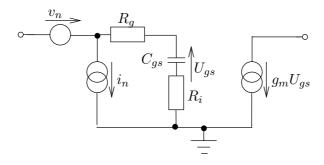

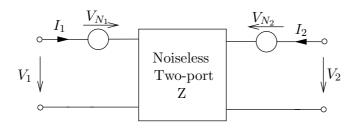

| 5.1.  | Noise Representation of Noisy Circuits                         | 57  |

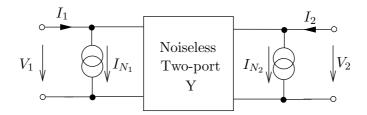

| 5.2.  | Correlation Matrices of Noisy Two-ports                        | 60  |

| 5.3.  | Relations Between Different Noise Correlation Matrices         | 62  |

| 5.4.  | Relations Between Different Electrical Matrices                | 63  |

| 5.5.  | Interconnections of Noisy Two-ports                            | 63  |

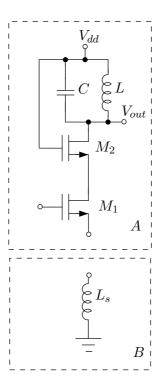

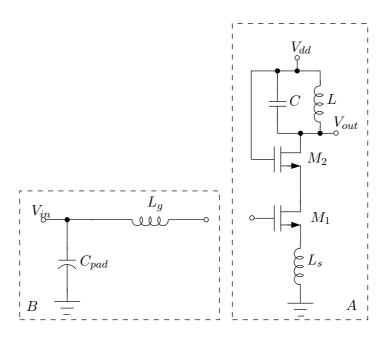

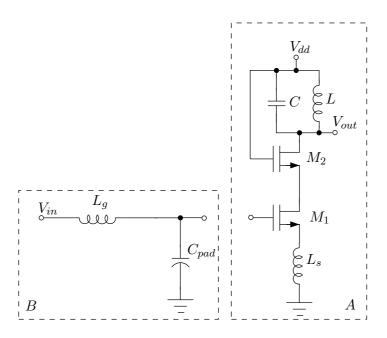

| Chapt | er 6. Low Noise Amplifier Design                               | 67  |

| 6.1.  | Impact of Channel and Gate Resistance on LNA Performance $$    | 72  |

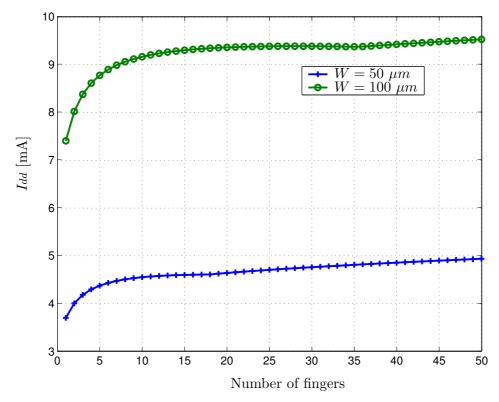

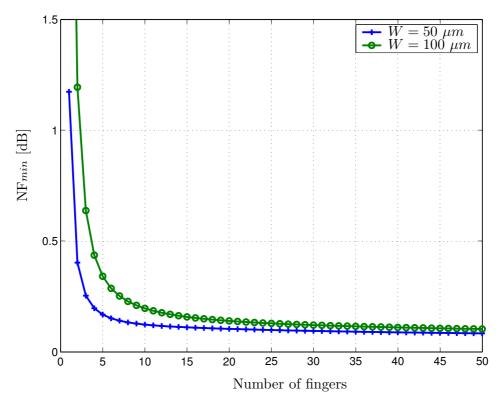

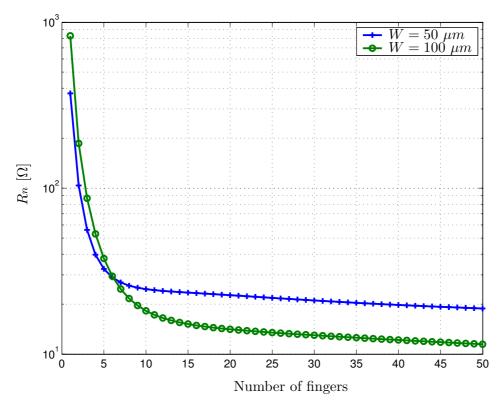

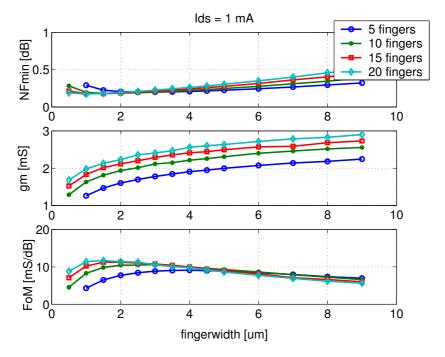

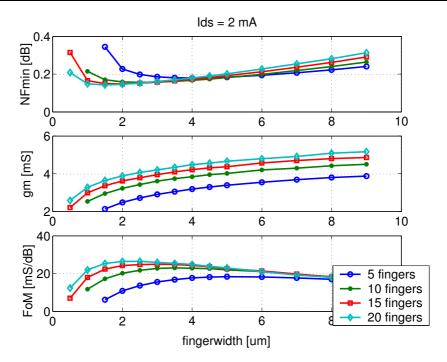

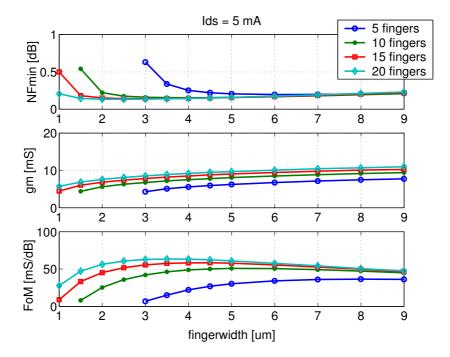

| 6.2.  | Choosing Transistor Width and Bias Conditions                  | 72  |

| 6.3.  | Two-port Noise Theory in LNA Design                            | 81  |

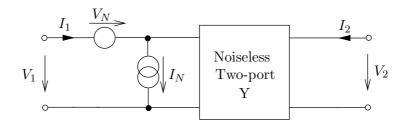

|       | 6.3.1. Influence of source degeneration                        | 81  |

|       | 6.3.2. Influence of Pad Capacitance with On-chip Inductance    | 83  |

|       | 6.3.3. Influence of Pad Capacitance and Off-chip Inductance $$ | 85  |

|       | 6.3.4. Comparison of two input matching principle              | 87  |

|       | 6.3.5. Influence of On-chip Enhanced Inductance                | 88  |

| 6.4.  | Design Flow                                                    | 90  |

| Chapt | er 7. LNA Measurements                                         | 93  |

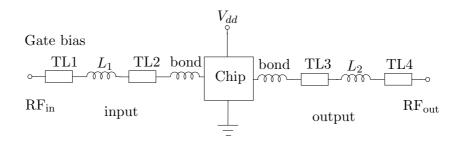

| 7.1.  | Measurement Test Bench                                         | 93  |

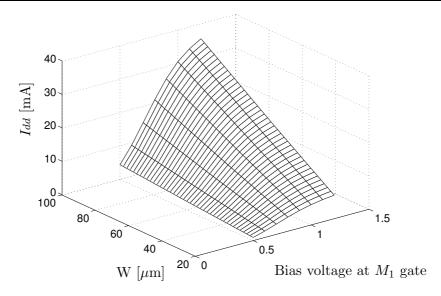

| 7.2.  | DC Measurements                                                | 95  |

| 7.3.  | S-parameter Measurements                                       | 96  |

| 7.4.  | Noise Figure Measurements                                      | 99  |

| 7.5.  | Compression Measurements                                       | 103 |

| 7.6.  | Comparison with State-of-the-art Amplifiers                    | 103 |

| Chapt | er 8. Conclusion                                               | 105 |

| Contents | VII |

|----------|-----|

|----------|-----|

| Appendix A. Cascode Amplifier                              | 107 |

|------------------------------------------------------------|-----|

| Appendix B. Electrical Chain Matrix of Cascode Amplifier   | 109 |

| Appendix C. Simultaneously Power and Noise Matching in LNA | 111 |

| Bibliography                                               | 113 |

| Nomenclature                                               | 123 |

| List of Figures                                            | 125 |

| List of Tables                                             | 127 |

## Chapter 1

# Introduction

Decades of continuous development of wireless communication has brought many standards. This is an ongoing process focusing on 3G-and 4G- systems at the moment.

Although all existing wireless standards have their own particularities, they belong to one of the four following groups: digital cordless telephony, wireless data, analog cellular telephony and digital cellular telephony. They cover the frequency range from 800 to 5800 MHz.

Unfortunately, standards developed in Europe, Japan and USA are not compatible with each other. This is a profound drawback particularly in the digital cellular telephony, where there is no common standard up to now.

This problem exists also for new WCDMA systems, where the standards defined in Europe (e.g., UMTS) differ from the ones in USA and Japan. Reasons for this incompatibility are: different needs of mobile users, different frequency allocations for preceding standards, different interests of companies and political constraints.

The variety of wireless standards leads to some disadvantages: manufacturers have a high effort with respect to development of many different devices and systems for base stations and terminals. Providers and users have additional costs because of higher base station complexity and the need of more than one terminal (e.g., mobile phone) if international availability is needed. The well-known dual or tri-band GSM mobile phones are not really reconfigurable systems within meaning of this work, because they just support very similar standards in different or even adjacent frequency bands.

Therefore the need for reconfigurability seems to be evident. A reconfigurable terminal should be able to support different standards. The principle of reconfigurability presumes that only one standard will be used at a time, but does not exclude the advanced idea of multi-usability, where the terminal supports different standards in different networks at the same time. Reasonable integration of different standards may also include standards, which belong to the same family (e.g., GSM) but are developed in different continents. Such terminals have been already produced and a broad offer exists on the market. These terminals support also a few frequency bands but use very similar procedures for signal and channel coding.

A rather new approach of the standard integration is the combination of different families of standards, for example between wireless data and digital cellular telephony like UMTS with WLAN or HIPERLAN. In this case, nearly all parameters defining a standard are different.

The development of such really reconfigurable systems is a challenging matter because very innovative ideas, concepts and technologies are needed to overcome the integration problems. Standardization-, system-, RF- and baseband engineers have to work very close together, to find the optimal system architecture. The optimization of the system performance can be no longer performed on the base of the single function blocks optimization, but a system simulation is needed. Only based on system simulations, the system optimizations with respect to technical performance, power consumption, dimensions, weight and cost will be possible.

This work copes with such demanding task, not only in high level system concept but also in LNA design.

## 1.1. Scope of This Work

The following chapters provide extensive information about reconfigurable systems and LNA design guidelines. To achieve these goals, this dissertation takes into consideration areas such as reconfigurability, transceiver system simulation, device physics, noise optimization and finally LNA design.

Chapter 2 shows the demand of reconfigurability for near future systems. For such reconfigurable systems the software defined radio and signal path optimization techniques shall be used. Therefore, the digital and analog part of the transceiver has to be optimized through system simulation. This chapter shows also the reconfigurable receiver radio frequency architecture that supports two standards. An impairments analysis based on system simulations is also given, for this architecture.

Chapter 3 discusses passive devices realized on chip, and Chapter 4 the submicron MOS transistor. In the latter chapter the short channel devices are emphasized since they play a major role for current circuit designs. Besides

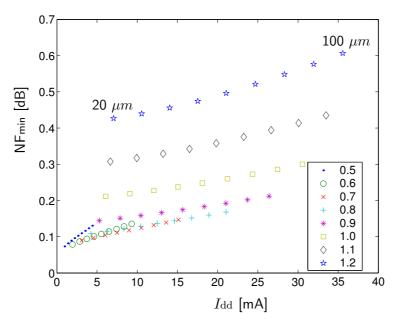

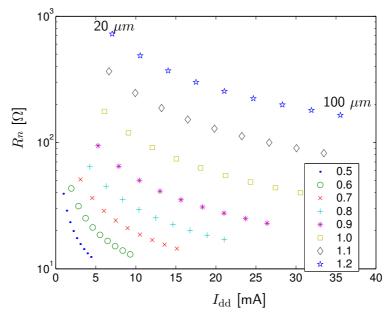

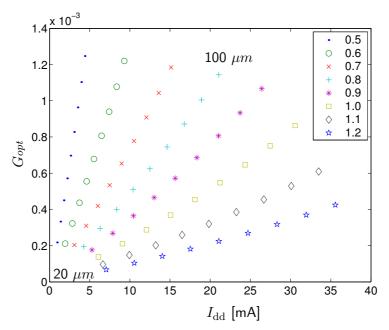

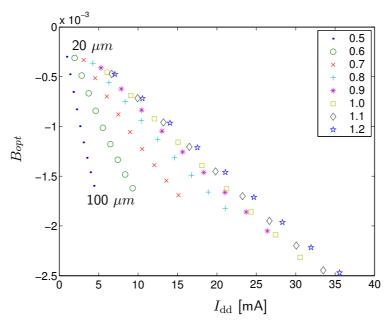

of direct current (DC) characteristics, high frequency transistor behavior is shown, together with noise models. This chapter shows also the four noise parameters of the transistor as a function of its size. These results are extensively needed in subsequent chapters of this thesis.

Chapter 5 gives a background for two-port noise theory. Various two-port noise representations and their relationships are shown. The way of deriving the four noise parameters from noise correlation matrix is shown. Moreover, guidance for noise analysis of the circuit that consists of basic two-ports connected together is given.

Chapter 6 shows design guidelines for LNAs in which the pad capacitance is treated as a part of the amplifier. To the knowledge of the author, the extensive study presented in this chapter is novel. Based on the approach on two-port noise theory, It shows that pad capacitance have positive influence on the amplifier noise characteristic. The LNA using the described design methodology is designed, and the measured results are given in Chapter 7. Although some problems has been reported, measured and simulated noise performance is in good agreement. Finally, Chapter 8 concludes with a summary and suggestions for further improvements.

Several appendices provide more detailed explanation of certain subjects. Appendix A introduces some issues with layout and on-chip implementation of cascode amplifier. Appendix B gives an electrical chain matrix of a cascode amplifier. Finally, Appendix C shows the case when the power and noise matching in cascode amplifier leads to the same input matching network.

## Chapter 2

# Reconfigurable Systems

In the near future, communication systems will be required to perform an increasing number of functions within reduced size, power, and weight requirements and tight costs constraints. In a reconfigurable, software defined radio (SDR) system it is even more the case due to the necessity to support all the functionalities of two or more different systems within one hardware architecture [1].

Because of these requirements dynamic signal path optimization (SPO) becomes more and more important. SPO incorporates a variety of correction methods for radio frequency (RF)-related disturbances and mismatches, which should maintain a good system performance despite of nonlinearities and non-idealities of analog hardware elements. SPO is being carried out in the digital baseband (BB) but under conditions defined by the analog frontend (FE) configuration. By this way a higher precision is guaranteed than in case of a control loop in the FE.

Due to the existence of a great number of standards covering a variety of communication scenarios, reconfigurable multi-mode implementations for mobile terminals gain on popularity. The SDR approach [2] emerges as a potential answer to the trade-off between dynamic adaptation, reconfigurability and technical feasibility. Unlike many standard dependent operations (i.e. transmission techniques, modulation, coding), compensation of RF-related effects is primarily determined by the physical nature of the phenomena, and therefore predestinated for a joint implementation. In case of a transceiver supporting WLAN and UMTS, several SPO methods have been studied in order to achieve best possible performance of the complete system.

Orthogonal frequency division multiplex (OFDM) based IEEE 802.11a and code division multiply access (CDMA) based UTRA frequency division duplex (FDD) represent two different wireless systems using entirely different air interface technologies. Despite of the differences, it is highly desirable to

have an intelligent transceiver that can work seamlessly on both systems. It is also feasible to involve particularly IEEE 802.11a and UMTS because of their complementary character: wireless local area network (WLAN) can provide high data rate in a stationary hot-spot situation and UMTS will take over if high mobility is in demand.

Since the feasibility of an SDR supporting UMTS and WLAN is beyond controversy as far as market relevance and application areas of both systems are concerned, particular architectures and implementation solutions for the target system must be studied (compare [3]).

## 2.1. General Concepts in Multi-standard Radios

The variety of communication systems existing today, with their different applications, coverage areas, data rates, etc, raise the question about the possibility of having multi-standard transceivers that are capable to operate in any communication system, at any time. These super-transceivers would definitely give the users another reality of mobility and flexibility. In addition, from the network point of view, the operators would also win another perspective in the management of their links and services. However, the provisioning of such a multi-standard scenario is not a trivial task and is currently a diffused topic of research. It comprehends work on the necessary network procedures (inter-system handover, inter-connection between systems, etc) and the development of multi-standard transceivers.

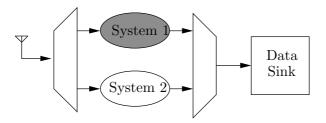

In the present chapter the multi-standard transceiver architectures are going to be discussed. The key-word when talking about multi-standard architectures is reconfigurability. The multistandard terminal must be able to be (re)configured according to the current application scenario. It should not be forgotten that to keep the implementation convenient the existing hardware resources must be as fast as possible [4]. In addition, the reconfiguration procedure (intersystem-handover) have to be as fast as possible. Basically, there are three types of reconfiguration architectures shown in Fig. 2.1.

#### 2.1.1. One-Bit Reconfiguration

This reconfiguration scheme requires an independent baseband implementation for each standard. The incoming data stream is multiplexed to the dedicated baseband processing chain and the processed data is given back to the data sink. In this case, the amount of information needed for recon-

(a) One-Bit Reconfiguration

(b) Software Defined Radio

(c) Software Reconfigurable Radio

Fig. 2.1. Reconfigurable architectures

figuration is at the minimum of one single bit. However, this approach fails in sharing the existing hardware resources and for this reason is inadequate for mobile devices where the power consumption and area play an important role.

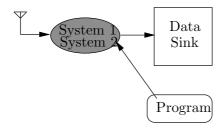

#### 2.1.2. Software Defined Radio

This is the most flexible way to provide reconfigurability to the multi-standard transceiver. Here, (re)configuring the device has the meaning of (re)programming the device to the various standards. The target of this design-philosophy is to develop the transceiver architecture in such a way that its operations and functions can be represented by programs that run in a hardware platform [5]. This hardware platform must be able to cope with the different transmit and receive algorithms and thus has to provide sufficient processing power and communication bandwidth. Therefore, high-bandwidth communication systems such as 54 Mbit/s WLAN would require a massively parallel implementation of the up-to-date microprocessor and DSP resources in order to fulfill the performance requirements. This would lead to high power supply consumption and area overhead, making this approach uninteresting for mobile terminals. However, this is a long term tendency in wireless world.

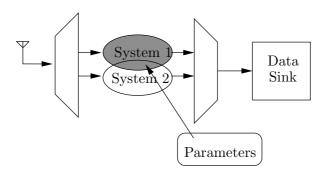

#### 2.1.3. Software Reconfigurable Radio

In this approach [6], the similarities and differences between the standards will be firstly identified and parameterized. Then, the basic algorithms underlying the systems are divided in classes according to their properties. Dedicated hardware will be now developed for the required classes of algorithms and the differences between the systems can be accommodated by reconfiguration based on the defined parameters.

The last two architectures are somewhat similar. The software reconfigurable radio is a simplified version of a software defined radio architecture. However, in recent publications the term software defined radio is used for both architectures.

## 2.2. RF Receiver Requirements

#### 2.2.1. UMTS FDD

In this section four third generation partnership project (3GPP) front-end test cases are discussed briefly [7]. Based of these examples, it is demonstrated how RF key parameters can be derived from the 3GPP specification. The complete set of RF specific test cases for the 3GPP FDD mode can be found in [8], [9], [10] and is further discussed in [11].

In Tab. 2.1, common terms from the 3GPP specification used in the following section are described. Unless otherwise stated, all parameters are specified at the antenna connector of the receiver. They are defined using the 12.2-kb/s down link (DL) reference measurement channel [8]. The total received powe spectrum density (PSD)  $\hat{I}_{or}$  for all test cases described in the following is composed of the actual data carrying signal (DPCH) to be detected and the so-called common downlink channels (pilot channel, synchronization channel, etc.), necessary for establishing and maintaining a link between the base station and terminal. Therefore, DPCH\_E<sub>c</sub> is usually several decibels below  $\hat{I}_{or}$ .

$DPCH_E_c$ Average energy per chip of a dedicated physical channel (DPCH)  $I_{or}$ Received (DL) power spectral density measured at the UE antenna connector  $I_{or}$ Total DL transmit power spectral density at the base station antenna connector  $I_{oac}$ Power spectral density of the adjacent channel measured at the EU antenna connector  $I_{ouw}$ Unwanted signal power level **OCNS** Orthogonal Channel Noise Simulator, a mechanism used to simulate users or control signals on the other orthogonal channels of a DL

Tab. 2.1. Common 3GPP Parameters

#### Reference sensitivity level test case

In 3GPP, the reference sensitivity is the minimum receiver input power measured at the antenna port at which the bit error rate (BER) does not exceed a value of  $10^{-3}$ . This test case determines the tolerable noise figure (NF) of the receiver front-end.  $\hat{I}_{or}$  and DPCH\_E<sub>c</sub> are -106.7 dBm/3.84 MHz and -117 dBm/3.84 MHz, respectively. The 12.2-kb/s reference measurement channel used for this test case has a symbol rate of 30 ks/s and an spread factor (SF) of 128, i.e., a spreading gain (SG) of approximately 21 dB. Let us assume that the required bit energy to interference PSD ratio  $E_{b,req}/I$  is 5 dB [12], then the insertion loss (IL) for the baseband implementation is 2 dB, and that the coding gain (CG) is 4 dB (CG estimation is difficult for

the used convolutional coder; 4 dB seems to be rather conservative). The acceptable interference signal level after despreading  $(P_I)$  then results in

$$P_I = DPCH - E_c + SG + CG - \frac{E_{b,req}}{I} - IL.$$

(2.1)

Inserting the above given values, we have  $P_I$ =-99 dBm. This leaves a margin for the front-end NF of

$$NF = P_I - 10\log(kTB) = -99 \text{ dBm} + 108 \text{ dBm} = 9 \text{ dB}$$

(2.2)

with the Boltzmann constant k, the ambient temperature T=300 K, and the bandwidth B=3.84 MHz.

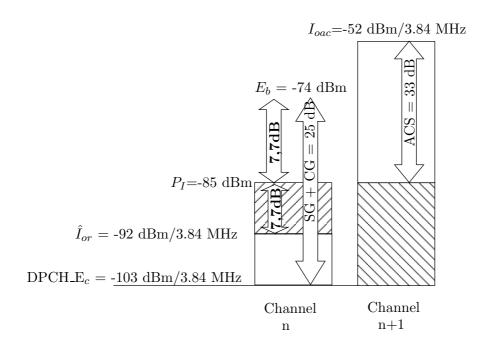

#### Adjacent channel selectivity test case

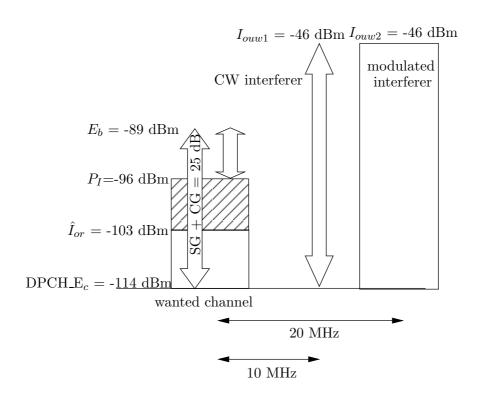

Adjacent channel selectivity (ACS) is a measure of a receiver's ability to receive a W-CDMA signal at its assigned channel frequency in the presence of an adjacent channel signal at a given frequency offset from the center frequency of the assigned channel. ACS is the ratio of the receive filter attenuation at the assigned channel frequency to the receive filter attenuation at the adjacent channel frequencies. The ACS has to be better than 33 dB. Simultaneously, the BER schould not exceed  $10^{-3}$  for the following test parameters (see also Fig. 2.2):  $\hat{I}_{or}$  and DPCH\_E<sub>c</sub> are -92.7 dBm/3.84 MHz and -103 dBm/3.84 MHz, respectively. The same reference measurement channel with a symbol rate of 30ks/s and SG of 21 dB is used as in the reference sensitivity level test case. The PSD of the adjacent channel signal  $\pm 5$  MHz away from the wanted channel is  $I_{oac}$ =-52 dBm/3.84 MHz. The signal levels for the ACS test case are summarized in Fig. 2.2.

$$P_I = DPCH L_c + SG + CG - \frac{E_{b,req}}{I} - IL = -85 \text{ dBm.}$$

(2.3)

If the adjacent channel interference signal is treated as Gaussian noise-like interference, the required ACS can be derived to be

$$ACS = I_{oac} - P_I = -52 \text{ dBm} + 85 \text{ dBm} = 33 \text{ dB}.$$

(2.4)

#### Intermodulation test case

For the intermodulation test case, two types of interferers are specified: a continuous wave (CW) interferer ( $I_{ouw1}$ ) and a W-CDMA interference signal ( $I_{ouw2}$ ). Both interferers have a power of 46 dBm, with the CW signal ( $I_{ouw2}$ ).

Fig. 2.2. Signal levels for the ACS test case

nal spaced 10 MHz away from the wanted signal and the modulated interferer having a spacing of 20 MHz. The power of the wanted channel is DPCH\_E<sub>c</sub> =-114 dBm/3.84 MHz and  $\hat{I}_{or}$  =-103.7 dBm/3.84 MHz. The modulated interference signal consists of the necessary common channels for any connection and 16 dedicated data channels with uncorrelated user data and the channelization codes for data channels are chosen to optimally reduce the peak-to-average ratio. These test-case conditions are illustrated in Fig. 2.3.

The sum of both interfering signals is transferred by means of a third-order nonlinearity into the desired channel. Therefore, this test case defines the required input intercept point of third order (IIP3) of the receiver. The acceptable noise-plus-interference level  $P_{N,I}$  in the desired channel must not exceed -96 dBm/3.84 MHz if we assume a combined spreading gain of 25 dB. Before determining the required IIP3, we have to assign the total noise-plus-interference power  $P_{N,I}$  to their sources. According to [13], we assume the following: 50% noise power (-3 dB), 15% intermodulation power (-8 dB), 15% blocking from CW interferer (-8 dB), 15% blocking from modulated interferer (-8 dB), and 5% power from oscillator noise (-13 dB). Furthermore, we neglect second-order products. From these assumptions, we derive a tolerable level for the third-order intermodulation power of

Fig. 2.3. Signal levels for the intermodulation test case

$P_{I,3} = -104.2 \text{ dBm/}3.84 \text{ MHz}$ . The required IIP3 can be derived as

IIP3 =

$$\frac{2I_{ouw1} + I_{ouw2} - P_{I,3}}{2} = -16.9 \text{ dBm.}$$

(2.5)

The equations presented above exemplify how the signal levels are influenced by the despreading operation and by interference sources. Further estimations like the above-mentioned ones can be found in [13], [9]. However, one should keep in mind that these results can only serve as coarse estimates. What has been neglected in, e.g., the IIP3 calculation, is the fact that (2.5) is based on pure sinusoidal signals. However, the IIP3 of a nonlinear building block with respect to a W-CDMA signal is different from the IIP3 for sinusoidal signals [14]. A second point neglected in the above estimation is the fact that the modulated interference signal is a W-CDMA signal spread with other orthogonal variable spreading factor (OVSF) codes than the wanted signal. Depending on the preserved orthogonality between signals that are spread with different codes, this type of interference can behave strongly different to the Gaussian noise model, which is often used for CDMA signals. These simplifications make the above computation of the required IIP3 only to an estimation. Furthermore, the actual CG has to be

simulated to achieve realistic values. Altogether, this leads for certain test cases to the necessity of an accurate computer-aided system design using an appropriate combination of commercial baseband and microwave simulation tools like COSSAP, SystemC and ADS. These tools, in some cases, have to be backed up with self-written user-defined codes. The maximum input level test case is such an example.

#### Maximum input level test case

The maximum input level test case defines the maximum input power at the antenna port of the mobile station at which a coded BER of at least  $10^{-3}$  must be achieved. According to the 3GPP specifications [8], the majority of the interference consists of a signal derived from a so-called orthogonal channel noise simulator (OCNS). This signal is used to simulate other user and control signals on the orthogonal channels in the downlink.  $\hat{I}_{or}$  is specified to be -25 dBm/3.84 MHz with the wanted user signal level being 19 dB below. If we assume the interference coming only from the common channels and the OCNS and perform the same simplified estimations, as in the above-described test cases, we would require a combined spreading and CG of 26 dB to achieve the necessary  $E_b/I$  of 7 dB for a BER of  $10^{-3}$ . However, the system simulations show different results [15].

It proves a fact that only with system simulation full and adequate receiver requirements can be obtained. In this case the 1-dB compression point  $(P_{1dB})$  of the receiver has to be better than -20 dBm.

#### Other front-end specification

The font-end receiver specifications do not fully describe fully the receiver, because signal impairments play an important role, too. Impairments have their origin in hardware components. However, only system simulations that connect the hardware and software processing chain can define the maximum level of allowed signal impairments. Signal impairments are discussed later in this work. They are noticed here, to emphasize the need of system simulation in receiver design.

#### 2.2.2. WLAN

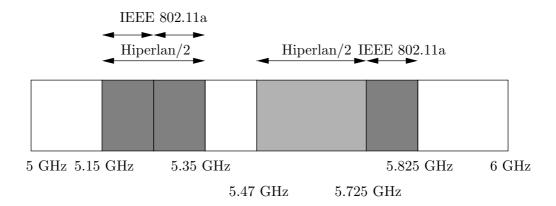

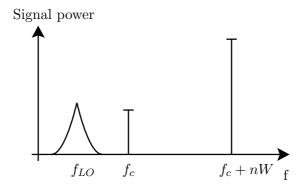

The IEEE 802.11a standard [16] and Hiperlan/2 standard use the frequency bands shown in Fig. 2.4.

Fig. 2.4. Signal bandwidth for WLAN standards

Although the medium access control (MAC) layers for HiperLAN2 and 802.11a differ significantly, performance requirements for the RF signal processing blocks are quite similar [17], [18]. This commonality concerns similar frequency bands, data rates, and intended deployment scenarios. Consequently, it is possible for a single receiver design to comply with both sets of specifications. To determine the precise target values, we first compute the specifications for both HiperLAN and 802.11a separately, and select the more stringent of the two in every case. Here we reduce the specification set to frequency range, noise figure, maximum input signal level (or input-referred  $P_{1dB}$ ), and limits of spurious emissions.

Wireless LAN systems require receiver architectures with wide dynamic range[19], [20], [21], [22]. When a transmitter and receiver are close to each other, the received signal strength can be as high as 20 dBm. A highly linear receiver is needed to accommodate such strong signals. On the other hand, the received signal can be quite weak due to fading. The receiver must be sensitive enough to detect signals as small as -148 dBm/Hz. (i.e., -74 dBm for a 24 MHz bandwidth signal [7]). To have a predetection signal-to-noise ratio (SNR) of at least 12 dB, the overall noise figure of the receiver must be better than

$$NF = -148 \text{ dBm/Hz} - 12 \text{ dB} - (-174 \text{ dBm/Hz}) = 14 \text{ dB}$$

(2.6)

where 174 dBm/Hz is the available noise power of the source. This noise

figure is readily achievable in CMOS with a reasonably low power consumption

Since the noise figure of the receiver is defined, other parameters can be derived. The  $P_{1dB}$  can be derived as maximum input power at the receiver antenna. This power is -20 dBm and -30 dBm for HIPERLAN/2 and IEEE802.11a, respectively. The receiver that can support both standards should have  $P_{1dB} > -15$  dBm, with a small 5 dB margin.

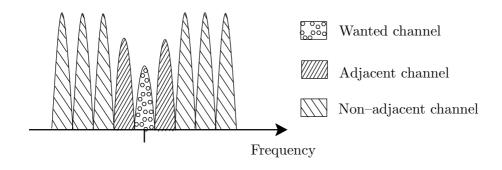

Input intercept point of second order (IIP2) and third IIP3 can be derived from adjacent and non adjacent channel rejection specifications and blocking characteristics. The adjacent and non adjacent channels are shown in Fig. 2.5.

Fig. 2.5. Adjacent and non-adjacent channels

Since for both standards different blocking levels (BL) are defined as well as different channel rejection specification they have different requirements for the IIP2 and IIP3. It these parameters are defined as

$$IIP2 = P_{in} + SNR + 2BL \tag{2.7}$$

and

$$IIP3 = \frac{2P_{in} + SNR + 3BL}{2} \tag{2.8}$$

where  $P_{in}$  is the input power, 3 dB above sensitivity level, by definition. Taking the most restrictive values the receiver that supports both standards should have at least 6 dBm of the IIP2 and at least -7 dBm of the IIP3.

In both WLAN systems the phase noise of the oscillator is important, since the systems are wide band. This is because the phase noise of the receiver oscillator(s) is translated into the IF passband of the receiver by a strong accompanying signal. This phenomenon is called reciprocal mixing,

and is also described later in this work as an important source of signal impairment.

Typically, phase noise performances of the oscillators used in low cost WLAN equipments are in the order of -120 dBc/Hz at 1 MHz offset, with noise floors of around -140 to -150 dBc/Hz. In any system consideration, transmitter and receiver phase noise must be take into account, although for convenience in calculation, it is easier to assume a clean transmitter and degrade the receiver performance by 3 dB: this assumes equal phase noise performance between transmitter and receiver. However, the flexibility of WLAN systems means that precise calculations are impossible, but first order approximations are nevertheless useful in determining the magnitude of the effects of particular parameters.

From the view of a multiple signal environment, the dominant limiting parameter of receiver performance seems to be phase noise, rather than gain compression or intermodulation. Even where the phase noise performance of the receiver is adequate, the assumption that transmitters will be of equal performance is not necessarily valid when considering the multiplicity of offerings from various vendors.

The effects of phase noise in WLAN standards are devastating, insofar as these effects are bandwidth related. Considered WLAN systems will typically have a noise bandwidth in the order of 25 MHz, so that even a -140 dBc/Hz noise floor will produce noise at -66 dBc. Thus, a -20 dBm signal will lead to a noise floor some 12 to 15 dB above kTB level.

# 2.3. Reconfigurable RF Receiver Architecture

A high diversity of solutions regarding the analog processing of the RF signal is available on the market. The obvious trend is towards the reduction of the number of functional blocks needed and total integration of the analog part together with the baseband components on a single chip. This is the idea of the so-called system on a chip (SoC) approach.

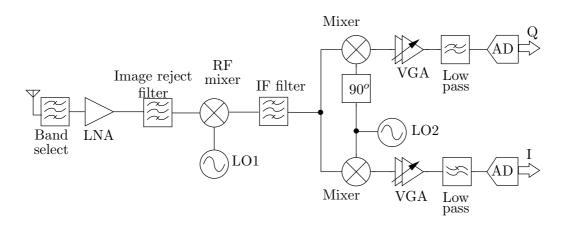

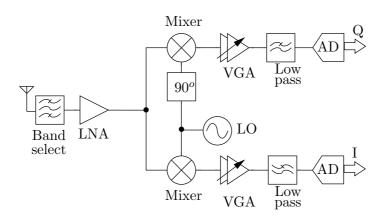

The classical architecture used since decades is the heterodyne type presented in Fig. 2.6. The RF signal band is first down-converted to an intermediate frequency (IF) and in a second step down-converted to the baseband by the I/Q demodulator. On the one hand, due to the high requirements regarding particular components, especially an image reject filter, some components can hardly be integrated and have to be placed off chip. On the

other hand, heterodyne receivers offer advantages with respect to sensitivity, selectivity and intermodulation behavior over other solutions.

It is important, too, that such architectures can easily be implemented at very high RF frequencies. Therefore, the heterodyne architecture is often used for standards which work at relatively high frequencies like IEEE802.11a or HIPERLAN/2 ([23], [24]). Heterodyne architecture has also some limitations. However, they can be overcome. This architecture is not a good solution as far as reconfigurability is concerned, because external filters cannot be combined as bandwidth varies for the various modes. Fortunately, a lot of drawbacks can be limited, when the improved architecture [25] is used.

Fig. 2.6. Heterodyne receiver architecture

The homodyne receiver shown in Fig. 2.7 has gained in popularity in the recent years due to the overcoming of its principal challenges like the DC offset problem or the LO leakage [26], [27], [28]. In this receiver type, the RF signal channel is mixed with an LO frequency that is equal to the carrier frequency and thus, IF is equal to zero. For this reason this architecture is also called zero-IF (ZIF) or direct conversion receiver (DCR) [26]. The direct conversion architecture offers a number of advantages due to its simplicity, the possibility of a monolithic integration as well as the lack of image related problems [29]. Superior integration is given by the fact that no external IF filters are needed. It is also characterized by a smaller number of functional

blocks than the heterodyne receiver. Other resulting qualities are low power consumption, lower chip area and also lower production costs.

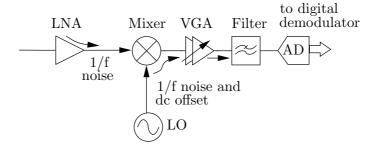

Fig. 2.7. Homodyne receiver architecture

Apart from the already mentioned advantages, the ZIF architecture has also some drawbacks. First of all, because of direct-conversion, the second order intermodulation (IP2) requirements for the receiver are high. Second, analog modules running at high frequencies suffer from I/Q imbalance. Moreover, low insertion loss passive filters are not available at baseband, and therefore active filters have to be used [30]. This leads to the fact that receiver noise can become a problem. These problems are rather uncritical for broadband baseband signals, so zero-IF is a very good candidate for UMTS or WLAN receivers (2 or 10 MHz bandwidth). All problems enumerated above are easier to overcome for lower RF frequencies, but the world tendency is to use DCR receivers even for high frequency [31], [32].

It is worth to mention that another receiver type, the low-IF architecture, gains more and more on significance. Although this architecture could also be regarded as a potential candidate for a multi-mode receiver, low-IF structures work well for rather narrowband baseband signals. As mentioned before, in our case, wide band signals are used in both standards.

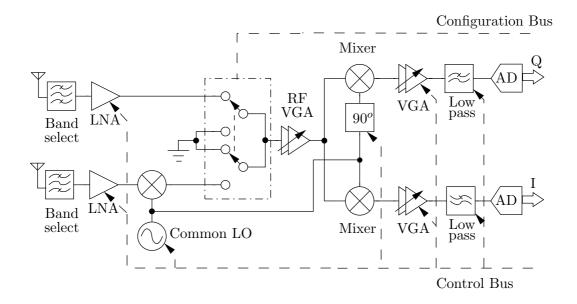

Neither the homodyne nor the heterodyne architecture leads to the required reconfigurability with respect to integration level, power consumption, components design, etc., Therefore, after extensive studies of both architectures [33], we propose a reconfigurable solution shown in Fig. 2.8. A few months ago, similar solution has been published [24]. Although our solution was suggested almost three years ago, it shows advantages with respect to

component reuse. The objective drawback of our architecture is, that it has not been fully integrated, yet.

Fig. 2.8. Reconfigurable receiver architecture

The hybrid architectures combines both heterodyne and homodyne architectures [34]. The homodyne receiver is chosen for the UMTS and the heterodyne receiver for the WLAN standard. Such a hybrid solution does not support both standards at the same time, leading to a reconfiguration with downtime scenario. It means that to change the standard, power-off power-on sequence is needed.

In the above mentioned architecture, advantages of homodyne and heterodyne architectures are combined. Direct conversion receiver is used by the low frequency standard UMTS (2 GHz), therefore its well known drawback, I/Q imbalance, is decreased. On the other hand, high frequency standard WLAN (5 GHz) uses the heterodyne architecture, which gives good leakage rejection between RF and local oscillator (LO) port, and good selectivity.

This hybrid architecture provides the maximum number of reusable functional blocks by setting the IF band of the WLAN receiver very close to the RF band of the UMTS receiver. This way, the receiver chain behind the first WLAN mixer uses the same functional blocks for both standards. The active standard is chosen by the user through control and configuration buses. The configuration bus determines which signal path will be processed, whereas the control bus sets the functionality parameters for the implied functional blocks. The unused functional blocks, like the UMTS low noise amplifier

(LNA) in WLAN mode, are idled to save battery power. Both buses actually represent digital signals coming from higher layers of the BB part of the system.

Another advantage of this solution is the rational application of the LO frequencies. The heterodyne receiver uses the same LO frequency for both down-conversion stages, thus producing an IF at half of the RF input frequency [25]. That means a LO frequency in the range 2.5-2.9 GHz for WLAN. Moreover, in this solution the image band is centered around the zero frequency and is highly suppressed by the antenna, channel filter and LNA, therefore eliminating the need for external image reject filters. For the UMTS homodyne architecture, the LO frequency is, on the other side, in the range 2.1-2.2 GHz. This arrangement of LO frequencies offers the possibility of using a common reconfigurable LO, with a relatively narrow tuning range. To cover both standards, the voltage controlled oscillator (VCO) should work in the range from 2.1 GHz up to 2.91 GHz, giving a differential quadrature signal ( $90^{\circ}$  phase shift).

There are two commonly used ways for generating the quadrature signal. In the first method, the VCO is used, which works nominally at a frequency two times higher than needed [35], [36]. Then, the VCO output signal [37] is divided by two in a frequency divider which also introduces 90° of the phase shift in the output signals. In our case, this method leads to the VCO operating in the frequency range from 4.2 GHz up to 5.82 GHz. Despite the two gaps in this range, the design of the such VCO can be challenging.

Therefore, a quadrature VCO (QVCO) is used [38]. This oscillator consists of two identical oscillators connected together in such way, that it generates the quadrature output signal. It is possible to cover the whole tuning range using only one reconfigurable QVCO [39].

The feasibility of a reconfigurable VCO is not the only argument for the half IF heterodyne receiver. Another advantage is given by the fact that the image band is centered around the zero frequency. This frequency band is highly suppressed by the antenna, channel filter and LNA, therefore eliminating the need for external image reject filters.

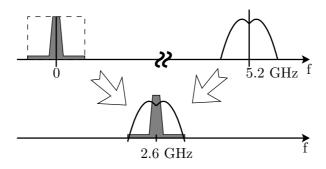

An advantage of the heterodyne WLAN receiver over the direct conversion solution is the fact that the LO – RF leakage can be rejected better by the LNA and antenna selectivity, avoiding the re-radiation problem that may occur in this way. There are, however, some problems that one must deal with in the heterodyne receiver. First, the flicker noise of the WLAN LNA is,

Fig. 2.9. Image band up-conversion for WLAN receiver

as depicted in Fig. 2.9, up-converted into the IF band and corrupts the signal. Depending on the transistor size, the flicker noise of the LNA may have a corner-frequency of several megahertz, so that the signal-to-noise (SNR) ratio of the WLAN signal despite its 20 MHz band may degrade considerably. In case of an active mixer topology, the mixer input stage will contribute along with the LNA to the flicker noise level. Therefore a resistive mixer should be the best solution in order to minimize the flicker noise level [40]. In this case a capacitive coupling between the LNA and the first WLAN mixer will solve the image problem. Another problem may appear in case of poor isolation between the LO and IF ports of the first WLAN mixer. In this case, the LO carrier may fall into the center of the IF band. As an effect, sensitivity problems may arise, making a double balanced mixer topology necessary to assure the best isolation values. Another problem which also concerns the I/Q demodulator mixer is the high linearity required for the mixer in absence of the channel select filter in the IF band. All these problems have to solved.

## 2.4. LNA Requirements

Having finished the studies on system simulations and system requirements, the system requirements have to be translated into specifications for each particular component [41]. It means, that all functional blocks shown in Fig. 2.8 has to be fully specified in respect to small signal, large signal and noise performance. Proposed reconfigurable architecture has two separate LNAs for UMTS and WLAN standards. The set of requirements for the UMTS LNA are collected in Tab. 2.2.

| Parameter              | Value       | Unit |

|------------------------|-------------|------|

| Frequency              | 2110 - 2170 | MHz  |

| Input power level      | -11028      | dBm  |

| Input impedance        | 50          | Ω    |

| $S_{11}$               | < -10       | dB   |

| Gain                   | 13          | dB   |

| Noise Figure           | < 3         | dB   |

| Input P <sub>1dB</sub> | -17         | dBm  |

| IIP3                   | -7          | dBm  |

| Power dissipation      | 7           | mW   |

**Tab.** 2.2. Specification for UMTS low noise amplifier

## 2.5. RF Related Impairments

Despite of advanced sub-micron technologies and several particular solutions (c.f. [42]), the designer still has to struggle through trade-offs, technology constrains and increasing requirements. As an effect, the receiver components, even the best available, still show non-ideal behavior.

Since the receiver FE contains non-ideal components, the overall FE performance is affected [43]. Impairments appear at the receiver output signal, and handicap its decoding [44], [45].

This problem is ubiquitous and standard independent. However, the maximum level of impairments differs for various standards. In case of a reconfigurable receiver, the impairments should not exceed the limits defined for the more restrictive standard.

For further impairments analysis, it can be assumed that the hybrid receiver is a homodyne receiver, which receives a high frequency modulated signal r(t). In this case, when the impairments of heterodyne architecture should be taken into account, the r(t) signal has to be improved. Due to this assumption, impairments stem mainly from the common part of the hybrid receiver.

Once again, this part is followed by an appropriate down-converting stage in a heterodyne receiver, whereas it constitutes the only down-converting stage in a homodyne receiver. Since it can be found also in a Low-IF receiver architecture, this circuit depicts the common stage of every receiver used nowadays. Thus, next considerations are applicable to almost all receivers. The common part of the receiver depicted in Fig. 2.8 consists of the I/Q

demodulator (mixers, LO, phase shifter) and amplifiers with filters for each baseband analog branch. The LO produces a reference signal for the receiver and provides the channel select function. The phase shifter connected to the LO splits the LO signal into two signals with 90° phase shift between them. The LO consist of a voltage controlled oscillator, which defines its frequency together with reference oscillator and a phase locked loop (PLL).

Since the power of the RF signal may vary in time, the gain of the variable gain amplifiers (VGA) depend on the RF input signal level. Therefore, the VGA delivers a constant power level at its output. Both filters restrict the frequency range of the baseband signal and filter adjacent, unwanted frequency bands and the interferers produced by nonlinearities in the receiver. These filters can also remove the DC component from the baseband signal.

Due to the non-deal components, the following impairments may occur: frequency offset, phase noise, direct current (DC) offset, I/Q imbalance and other imperfections.

Generally, the high frequency carrier modulated signal at receiver input can be expressed as [29]

$$r(t) = m_a(t)\cos[2\pi f_c + m_p(t)]$$

(2.9)

where  $f_c$  is the carrier frequency,  $m_a(t)$  is the amplitude modulation and  $m_p(t)$  is the phase modulation of the signal.

The signal

$$z(t) = m_a(t)e^{jm_p(t)} = z_I(t) + jz_Q(t)$$

(2.10)

contains all the information and it is called the complex envelope of the signal.

Due to quadrature demodulation, the received signal r(t) is down-converted and divided into real and imaginary parts. The local LO signal  $x_{LO}(t)$  can be simplified to:

$$x_{LO}(t) = \cos(\omega_{LO}t) - jq\sin(\omega_{LO}t + \phi), \tag{2.11}$$

where  $\phi$  is the phase mismatch between I and Q signal and g the amplitude mismatch factor.  $f_{LO} = \frac{\omega_{Lo}}{2\pi}$  denotes the LO frequency. Generally, the phase mismatch may have a considerable value, and g is bound to be very close to one.

In the following subsections, we focus on these impairments, show their sources and possible ways of avoiding them. We also search for implementation solutions which minimize these impairments. Unfortunately, not all of them can be removed in the FE, thus the cooperation with the baseband (BB) in impairments cancellation is inevitable and necessary. This can be done if signal path optimization approach [46] is used.

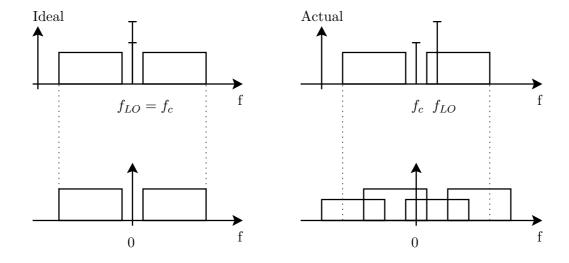

#### 2.5.1. Frequency Offset

In the UMTS and WLAN systems the information is transmitted using frequency channels. Each frequency channel is centered at a particular frequency (called carrier frequency) and occupies a predefined bandwidth. To retrieve the information placed in the channel, one has to shift down the carrier frequency to zero (2.9).

In order to receive information which is being transmitted through a channel with carrier frequency  $f_c$  at the antenna, the receive frequency has to be equal to  $f_c$ . Due to the non-ideal oscillators, obtaining these frequencies to be equal to each other is not a trivial task, and a sort of impairments called frequency offset occurs.

Fig. 2.10. Frequency offset phenomenon

According to that and (2.10), the BB equivalent signal at the FE output (BB input) can be expressed as

$$z_f(t) = z(t)e^{j(2\pi f_o t + \Theta)} + n(t)e^{j(2\pi f_o t + \Theta)}$$

(2.12)

where  $f_o = |f_{LO} - f_c|$  for the homodyne case and  $|2f_{LO} - f_c|$  for the heterodyne case. The n(t) term denotes additive white Gaussian noise, and  $\Theta$  stems from the phase difference between transmitted and received signal

and is responsible for twist of the constellation diagram. In other words, the constellation diagram rotates with angle velocity depending on the difference between the transmit and receive frequency.

In case of a WLAN system, the frequency offset disturbs the orthogonality between the subcarriers causing intercarier interference (ICI). The characteristics of the ICI are similar to white Gaussian noise and lead to degradation of the SNR.

Two frequency offset situations are depicted in Fig. 2.10. The first one shows an ideal case of  $f_{LO} = f_c$ , The other one shows he consequences of frequency offset in a pictographic, a bit exaggerated way.

The frequency offset is responsible for the rotation of the constellation diagram. When the frequency offset is constant, speed of rotation is also constant. This phenomenon can be also interpreted as an additional phase shift, which is added to the signal at each sampling time.

#### 2.5.2. Phase Noise

In contrast to the frequency offset, which fluctuates rather slowly, quick changes of the LO frequency may also appear (variable  $f_o$  in (2.12)). Since the changes are random and result in unpredictable phase shifts, they are called phase noise. The LO generates also amplitude fluctuations, but the amplitude noise can be suppressed effectively by mixers as described before, so that in the end only the phase noise has a considerable influence on the quality of the FE signal path.

Two problems concerning LO phase noise should be taken into account. First, if any large blocking signal close to the wanted signal appears at the antenna receiver input, LO phase noise will appear at the IF due to a reciprocal mixing phenomenon. The signal to noise ratio will be automatically decreased by this way. Second, random changes of the LO frequency, even without the blocking signal, decrease the SNR, too. This case is also discussed in section 2.2.2

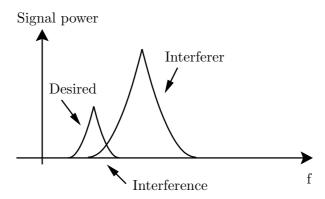

Phase noise induces reciprocal mixing at the receiver [47]. The receiver LO down-converts the RF carrier of the desired signal as well as the interferer, to a lower frequency. Ideally, the down-conversion should not spread the interference to the desired signal frequency. However, in the mixing process, phase noise in the LO modulates the interfering signal and can generate significant interference in the desired signal as shown in Fig. 2.11.

**Fig.** 2.11. Reciprocal mixing; the wanted signal suffers from significant noise due to the tail of the interference.

Deployment of a more precise LO is the only feasible way to limit phase noise in the FE. Actually, poor phase noise performance affects the FE functionality and triggers further problems.

#### 2.5.3. Direct Current Offset

The DC offset is an immediate consequence of the direct conversion process in zero-IF and near-zero-IF receivers [48]. It can be expressed mathematically, by adding a constant value to BB signal components (2.10). Basically, the DC offset can be classified into two types [49]:

— Static type, caused by the LO leakage back into the antenna port of the transmitter or by circuit imbalances. This type is most common and varies only slowly. It is often considered fixed over a packet duration. Therefore, this type can be compensated simply by passing the signal through a running mean operation.

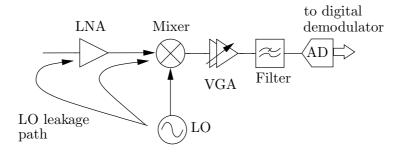

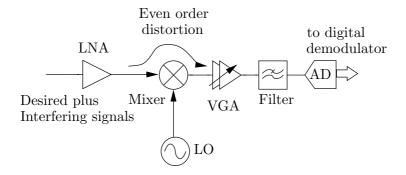

## (a) LO leakage

#### (b) even order harmonic distortion

(c) 1/f noise leakage

Fig. 2.12. Sources of DC errors in homodyne receivers

— Dynamic type, resulting from the signal leakage from the RF input to the LO. Combined with the circuit imbalances and nonlinearity within the mixer, this type of DC offset causes second order intermodulation distortion within the mixer

Due to the substantial influence of the I/Q imbalance and the DC offset on the data transmission performance it is an important task to find an adequate solution to compensate the described mismatch. Fortunately that can be done in BB part of the receiver.

#### 2.5.4. I/Q Imbalance

The main source of I/Q imbalance is the final stage of the receiver's analog part. Mixers, filters and amplifiers contribute to the I and Q mismatch, because of their non equal gains and group delays. Significant contributors may also be found in the digital part of the receiver. The main reason of phase imbalance is the phase shifter. Main amplitude imbalance contributor is a non equal gain in the I and Q signal paths. However, these impairments can also originate from the transmitter site, either a base-station or an access point in case of UMTS or WLAN, respectively.

An analytical description of the I/Q imbalance phenomenon may be obtained by processing (2.11) in a way described in [50]. It leads to the following form of the BB signal delivered by the receiver:

$$x(t) = z_I(t) + j \left( g \cos(\phi) z_Q(t) - g \sin(\phi) z_I(t) \right), \tag{2.13}$$

where  $z(t) = z_I(t) + jz_Q(t)$  is the BB equivalent of the signal r(t) received at the antenna.

Equation (2.13) describes I/Q impairments in a system with solely time domain signal processing. OFDM based systems must be considered separately.

Let Z(f) and X(f) denote the frequency domain representations of the original and filtered signal, respectively. The output signal  $X(nf_s)$  may be expressed as a function of  $Z(nf_s)$ , where  $f_s = \frac{1}{\Delta t_s}$  stands for the sampling frequency. After expressing  $z(k\Delta t)$  as inverse fast fourier transformation (IFFT) of  $Z(nf_s)$ , inserting the result into (2.13) and computing fast fourier transformation (FFT), then splitting the exponential terms in their real and imaginary parts and taking advantage of the sum orthogonality, the following

equation appears:

$$X_{n} = Z_{n} + \frac{1}{2} \left[ (1 - g \cdot \cos\phi) \left( Z_{n} - Z_{L-n+1}^{*} \right) - jg \cdot \sin\phi \left( Z_{n} + Z_{L-n+1}^{*} \right) \right], \qquad (2.14)$$

where L - n + 1 denotes a position symmetrical to n within the discrete fourier transformation (DFT) (or FFT) frame characterized by the length L. To simplify the equation,  $X(nf_s)$  and  $Z(nf_s)$  were referred to as  $X_n$  and  $Z_n$ , respectively.

Phase and amplitude impairments of an I/Q architecture are standard independent. However, OFDM based systems suffer more from imbalances than other communication systems due to a particular form of the distorted signal [51].

The differences between I/Q imbalance impact on a single carrier time division multiply access (TDMA)/frequency division multiply access (FDMA) or CDMA system compared with an OFDM based one can be found in [51].

Equation (2.14) describes the influence of I/Q imbalance on multi carrier OFDM systems for L > 1 and single carrier systems for L = 1. Further observations may be derived from the analytical model for OFDM based systems:

- The FFT length has no relevance for I/Q imbalance,

- for each modulation symbol, the resulting constellation consists of the same number of points as the order of the modulation scheme because that is exactly the number of different  $Z_{L-n+1}^*$  signals that may exist,

- I/Q architecture is very sensitive to amplitude imbalance due to the  $g \cdot cos\phi$  term,

- regular "chessboard-like" patterns appear for quadrature amplitude modulation (QAM) schemes due to their symmetry.

According to (2.14) the ranges of amplitude and phase imbalance values can be derived that do not lead to bit errors when no other influences are present. It can be seen that an error free range of phase imbalance values is larger than error free range of amplitude imbalance values. This important conclusion can be exploited by the SPO approach.

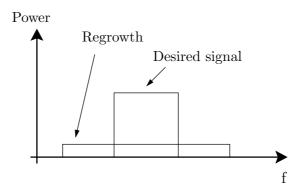

#### 2.5.5. Nonlinearities

Nonlinearities are a general term for a whole class of impairments that affect the functionality of a receiver due to nonlinear characteristics of its components. The input power varies in time and in addition to the wanted signal, unwanted signals like adjacent channels and sometimes also interferers appear at the antenna, too - producing a power level, which can cause nonlinear operation of the receiver. To avoid it, a high  $P_{1dB}$  of the receiver is needed, because small signal linearity measures (like IIP3) of the function block are in the linear relation. The IIP3 is around 10 dB and IIP2 is around 20 dB higher than  $P_{1dB}$ , without any linearization techniques. To define this receiver requirements some knowledge of the signal properties is necessary. Generally, each standard specifies maximum values of the signal at the receiver antenna, which shall be accepted without significant losses of the transmitted data. Additionally, the so-called back-off level defined as a minimum difference between maximum input power and  $P_{1dB}$ , has to be considered. Quite obviously, the larger the back-off, the more linear the receiver. In reality its value is limited, because high  $P_{1dB}$  requires more power and more chip area. Therefore, the back-off about 6-7 dB is very often used.

Another problem, which has to be considered, are third order nonlinearities. Since large adjacent channels accompany the received signal, nonlinearities of particular receiver stages (LNA, Mixers) become important. When large adjacent channels in the vicinity of the wanted signal appear at the antenna, the output signal, passing through the nonlinear functional block, contains also copies of the adjacent channels.

This phenomenon can negatively influence multiuser detection performed in the BB. Additionally, even without any strong interferer, when the input signal is larger than spurious free dynamic range (SFDR) of the receiver, the nonlinearity products will have values larger than the noise floor. It can be visible as the spectrum re-grow as depicted in Fig. 2.13. It can be seen that

Fig. 2.13. Spectrum regrowth due to the third order nonlinearities

the original signal, which occupies only its own frequency band, regrows to adjacent frequency channels after passing through the nonlinear component. The same phenomenon occurs for the two adjacent channels. Therefore, if at least one of the adjacent channels is characterized by sufficient power, its copy will appear in the desired channel.

## Chapter 3

# Passive Devices

The performance of the RF integrated circuits is strongly connected with the quality of passive elements [52]. Good passive components are still a limitation of modern CMOS technologies. For example inductors of large values consume significant die area and have relatively poor quality factor Q.

Capacitors with high Q and low temperature coefficient are available, but their parasitics can not be neglected. Resistors with low parasitic capacitance and temperature coefficient are hard to come by. So design of RF integrated circuits is highly influenced by the passive devices.

In this section pads are also discussed. Obviously they are not basic devices, but they are passive and introduce significant contribution to the circuit.

#### 3.1. Inductors

From the point of view of RF circuits the lack of good inductors is the shortcoming of the standard IC processes. Although active integrated circuits can sometimes synthesize the equivalent of an inductor, they always have higher noise, power consumption and distortion than real passive planar inductors.

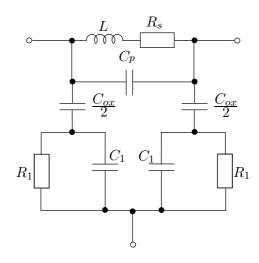

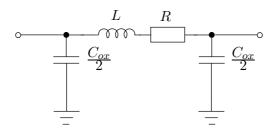

### 3.1.1. Spiral Inductors

The widely used on-chip inductor is the planar spiral, which can be of different shapes, square, hexagonal, octagonal etc. The wiring of the spiral is implemented in the topmost available metal, sometimes are two or more metal layers strapped together and the connection to the center of the spiral is made with a cross-under of some lower level of metal. The inductance of such a spiral is a complicated function of geometry and accurate anylysis requires 3D-EM field solvers. However, using the libraries given in a Design

Kit from foundry, the designer has only to make choice of an appropriate kind of the inductor, and some parameters and the whole inductor parameters are self-calculated by the design environment using the information provided by the model.

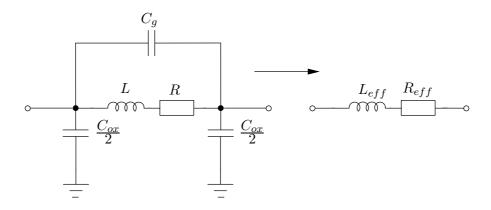

Fig. 3.1. Model for on-chip spiral inductor

To examine some important characteristic of the spiral on chip inductors simulation used an inductor taken from design kit has been performed. Simulation results are shown in Tab. 3.1. In the used design kit only the value of inductance L and number of turns n cab be specified by the designer. All other parameter are self-calculated by the model.

**Tab.** 3.1. Simulated maximum Q and self resonant frequency  $f_{res}$  values for various inductors

| Induc  | tor  | $\max Q$      | $f_{res}$ |

|--------|------|---------------|-----------|

| L [nH] | n    |               | [GHz]     |

| 12     | 6.5  | 8.3 @ 1.5 GHz | 2.6       |

| 10     | 6.5  | 8.7 @ 1.7 GHz | 3.0       |

| 8      | 6.5  | 9.3 @ 2.0 GHz | 4.0       |

| 6      | 6.5  | 10 @ 4.7 GHz  | 4.5       |

| 4      | 5.0  | 13 @ 3.3 GHz  | 6.2       |

| 2      | 4.25 | 15 @ 5.3 GHz  | 10.7      |

| 1      | 3.25 | 17 @ 8.5 GHz  | 18        |

In respect to the resonant frequency and maximum Q factor the best results shows the smallest inductor. Increasing the inductance leads to decreas-

3.1. Inductors 35

ing the maximum Q, and resonant frequency, as well. For 2 GHz operation, maximum value of inductance used in the matching circuits is approximately equal 8 nH, and for 6 GHz 4 nH for this kind of inductor. For other purposes, like e.g., RF blocking larger values can be used.

The same value of inductance can be achieved by not only one combination of spiral diameter and number of turns. Tab. 3.2 shows maximum value of factor Q and resonant frequency  $f_{res}$  for an inductor with L=5 nH. Two values of n are extreme; smallest and largest realizable.

**Tab.** 3.2. Spiral inductors parameters with L=5 nH for different number of turns n

| n    | $\max Q$   | $f_{res}$ [GHz] |

|------|------------|-----------------|

| 3.25 | 14 @ 4 GHz | 7.9             |

| 4.25 | 13 @ 4 GHz | 7.8             |

From this investigation can be found, that increasing n lowers factor Q, but does not change the frequency at which maximum Q appears. Additionally, increasing n lowers the self resonant frequency of the inductor. Therefore, the conclusion is clear, one has to use inductors with as small number of turns as possible.

These on-chip spirals consume much area. Aside from large area another serious problem with the spiral inductors is their relatively large loss. The DC resistive losses together with the skin effect cause a nonuniform current distribution in a conductor at RF. The consequence is the reduction of the effective conductor cross-section, increasing the series resistance.

In addition to the series resistive loss, capacitance to the substrate is another problem of on-chip spirals. In silicon technology, there is a substrate near to the spiral and is fairly conductive, creating a parallel plate capacitor that resonates with the inductor. The resonance frequency of the LC combination represents the upper useful frequency of the inductor. The proximity of the substrate also degrades Q because of the energy coupled into the lossy substrate.

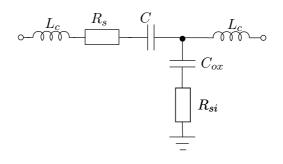

An additional parasitic capacitance is in shunt to the inductor that arises from the overlap of the cross-under from rest of the spiral. The model for on-chip spiral inductor is shown in Fig. 3.1. This model is symmetrical, even though actual spiral are not. The error introduced is in most instances negligible.

The series resistance  $R_s$  is proportional to the total length of winding and inverse proportional to the width of the interconnect and skin depth. The shunt capacitance  $C_p$  is proportional to number of turns, to the square of width of the interconnect and to the oxide capacitance. The capacitance  $C_{ox}$  is a parallel plate capacitor, with its capacitance between substrate and interconnection. The last element,  $C_1$  denotes the substrate capacitance as well as other reactive effects associated with the inductor.

Q of the inductor can be optimized by removing the turns in the middle of the spiral as they contribute negligible to the total flux but contribute to the total loss. Furthermore, a pattern ground-shield [53] also helps to improve the Q of the inductor. A patterned ground shield prevents capacitive coupling to the lossy substrate while avoiding short-circuiting of the magnetic flux. Another advantage is that the shielding greatly reduces coupling of noise from the substrate to the inductor. The penalty is the reduction of the self resonant frequency of the inductor. In the layout of the final low noise amplifier shielded inductors are used.

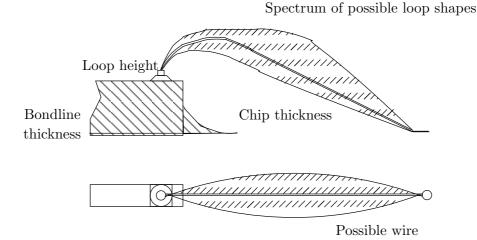

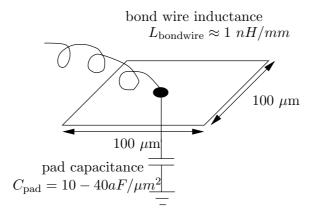

#### 3.1.2. Bond-wire Inductors

In addition to spirals, bond wires are frequently used to make inductors. Because standard bond wires are about 20  $\mu$ m in diameter, they have much more surface area per length than the planar spirals and hence less resistive loss, and therefore higher Q values. The inductance of bond-wire can be approximately given by 1 nH/mm and resistance 0.1  $\Omega$ /mm.

The cross section of a hypothetical bond wire between a chip and a test board shows Fig. 3.2. The length of the bond wire varies, thus the inductance varies also. It is the main problem of bond wires, lack of repeatability. Another problem associated with varying shape of the bond wire are additional parasitics. And last but not least, high values of inductance are rather not feasible, since the bond wire can act as an antenna.

# 3.2. MIM Capacitors

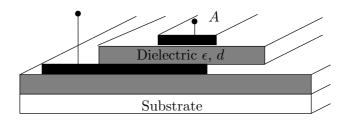

Metal insulator metal (MIM) type capacitors are illustrated in Fig. 3.3. They have lower parasitics than MOS capacitors. In the used technology,

Fig. 3.2. Bonding wire

they are built using the additional dedicated metal layers. The capacitance is given by

$$C = \frac{\epsilon_0 \epsilon_r A}{d} \tag{3.1}$$

where A is the plate area,  $\epsilon_0$  is the dielectric constant in the vacuum,  $\epsilon_r$  is the relative dielectric material constant and d the distance between the metal plates. The capacitance per area is approximately 2 fF/ $\mu$ m<sup>2</sup>.

Good capacitors for RF application should have low voltage coefficients, good capacitor matching, precision control of capacitor values and small parasitic elements.

Traditionally parallel plate capacitance suffers from many such problems. One is the parasitic bottom plate capacitance which is frequently as large as 10--30~% or more of the main capacitance and often degrades the circuit performance.

Metal-insulator-metal (MIM) capacitors are very valuable in RF circuits. MIM capacitors can be used for coupling capacitances and bypass capacitances in RF circuits. They have good linearity and high dynamic range. In general, when MIM capacitors are used in RF circuits the dielectric loss must be extremely small and the series resistance of the wiring should be minimized.

(a) cross section

(b) electrical model

Fig. 3.3. MIM capacitor made on-chip

#### 3.3. Resistors

There are relatively good resistor options in the standard CMOS (complementary metal-oxide silicon) processes. One possibility is to use polysilicon ("poly") interconnect material, since it is more resistive than metal. However, most poly these days have small resistivity. It stems form the fact, that poly material are used as a gate connection of the transistor, and decreasing its resistivity improves the noise performance of the transistor 4.3.2. The tolerance of the resistors is often poor and temperature coefficient depends on doping composition and is typically in order of 1000 ppm/°C. Unsilicided poly has higher resistivity, but higher tolerance, too. Poly resistors have a reasonably low parasitic capacitance per unit area and the lowest voltage coefficient of all the resistor material available in a standard CMOS technology. Resistors made from source-drain diffusion is also an option. The resistivities

3.4. Pads 39

and temperature coefficient are generally similar to those of silicided polysilicon with lower temperature coefficient associated with higher doping. There is also a significant parasitic capacitance and noticeably voltage coefficient. The former limits the useable frequency range of resistors while the latter limits the dynamic range of voltages that can be applied without introducing significant distortion.

## 3.4. Pads

In this work, grounded shielded (GS) pads shown in Fig. 3.4 are used for all signals, since only GS pads are available in used technology (HCMOS9, STM). The first metal acts as a shield connected to ground, and a top level metal layer acts as a pad connection [54]. For the GS structure, a grounded highly conducting plate is inserted underneath the pad metal plates to shield the upper bonding pad from the substrate. This technique has the advantages of excellent isolation [55] and lowered noise figure [55], [56], [57]. However, the insertion of the GS plate increases the pad capacitance. It results in a lower resonant frequency of the bond-wire-pad connection for a given inductance of the interface connection, especially for some technologies with a small number of metallization levels.

Fig. 3.4. Bonding pad together with connection

Typically, a GS bonding pad can have a pad capacitance as high as 0.35 pF for a typical pad size of 100  $\mu$ m x 100  $\mu$ m. Assuming a 2 mm long bond wire connected to the GS bonding pad, the inductance ( $\approx$ 2 nH) of the bond wire will resonate with the pad capacitance at about 6 GHz as

$$f = \frac{1}{2\pi LC}. (3.2)$$

The low resonant frequency can kill the high frequency connection of the bonding pad and the overall performance of the circuit. Hence, using these pads, the pad capacitance and bond wire inductance shall be kept low. However, as it is shown later in this work there are still more factors that should be taken into account especially in LNA design.

To overcome the mentioned issues with GS pads, depletion-insulation (DI) bonding pad structure can be used as shown in [58]. This kind of pads can be used for high frequencies [59].

## Chapter 4

# RF MOSFET Devices

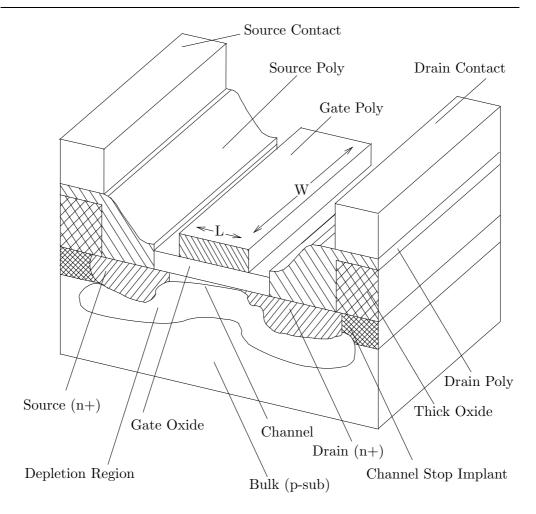

## 4.1. Long-channel Regime

The physical structure of a MOSFET transistor is shown in Fig. 4.1. Electrically, the MOSFET has four contacts: a bulk, source, drain and gate contact [60], [61]. When the drain to source voltage  $V_{ds}$  is larger than zero, then the gate source voltage  $V_{gs}$  larger than the threshold voltage  $V_T$  forms a conducting channel between drain and source. Between the drain and source flows the current  $I_{ds}$ , which is dependent on the gate source voltage and the gate poly area (W, L).

MOSFETs exhibit three distinct regions of operation depending upon their bias condition. They are subthreshold, triode and saturation. In the first region, in simple MOSFET models, no current flows, and for RF design purposes it is not interesting.

The second mentioned region is triode or linear. A MOSFET operates in its triode when  $V_{gs}$  is large enough to guarantee the formation of an inversion layer the whole distance from source to drain [52]. It means that  $V_{gs} \ge V_T$  and  $V_{ds} \le V_{gs} - V_T$ , where  $V_{gs}$  is a threshold voltage. In this case the drain source current can be written as

$$I_D = \mu_n C_{ox} \frac{W}{L} \left[ (V_{gs} - V_T) V_{ds} - \frac{V_{ds}^2}{2} \right]$$

(4.1)

where W, L are device dimensions,  $C_{ox}$  is oxide capacitance and  $\mu_n$  electron mobility.

Equation (4.1) shows, that in triode region drain source current is linear for small drain-to-source voltages. Thus, a MOSFET in this region behaves as a voltage controlled resistor.

In radio frequency applications, the MOSFET operates normally in its saturation region. In this case  $V_{ds}$  is high enough  $(V_{ds} \ge V_{ds,sat} = V_{gs} - V_T)$  so

Fig. 4.1. Physical structure of a MOSFET

that the inversion layer does not extend the whole source to drain distance, the channel is said to be "pinched off", and any increase in  $V_{ds}$  increases the drain current only slightly. The reason that the drain current increases for increasing  $V_{ds}$  is because the depletion layer width increases for increasing  $V_{ds}$ .

This effect is called channel length modulation and is accounted for  $\lambda$ , the channel length modulation parameter.  $\lambda$  is in range from approximately 0.1 for short channel devices to 0.01 for long channel devices. Since MOSFETs designed for radio frequency operation normally use minimum channel lengths, channel length modulation is an important concern for radio frequency implementations in CMOS, especially for short channel devices commonly used in nowadays RF designs. When a MOSFET operates with a pinched off channel the drain source current can be written as

$$I_D = \frac{1}{2}\mu_n C_{ox} \frac{W}{L} \left( V_{gs} - V_T \right)^2 \left( 1 + \lambda \left( V_{ds} - V_{ds,sat} \right) \right) \tag{4.2}$$

Hence, in saturation, the drain current has a square-law dependence on the gate-source voltage and is independent of drain voltage if the channel length modulation is neglected.

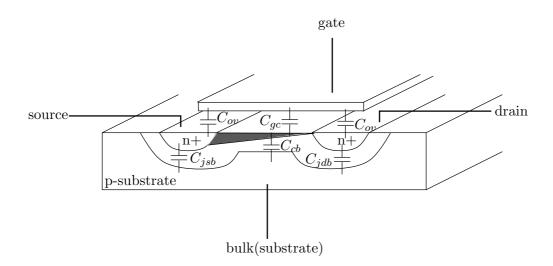

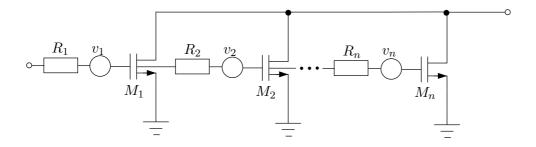

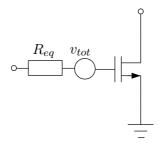

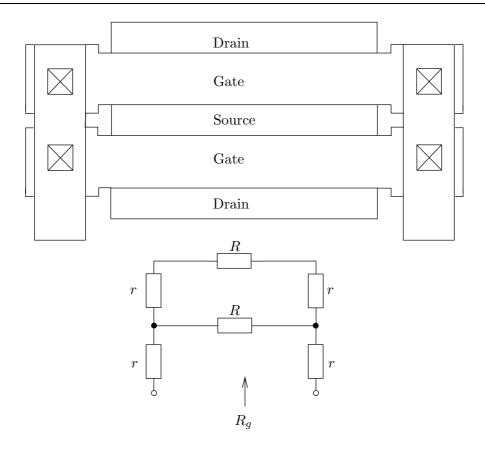

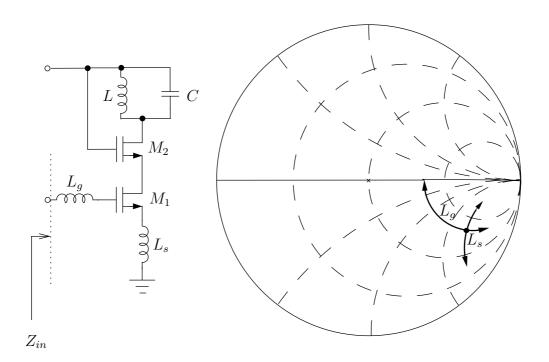

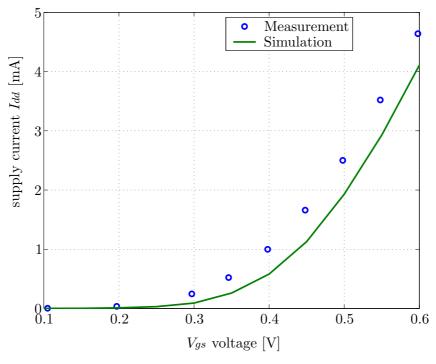

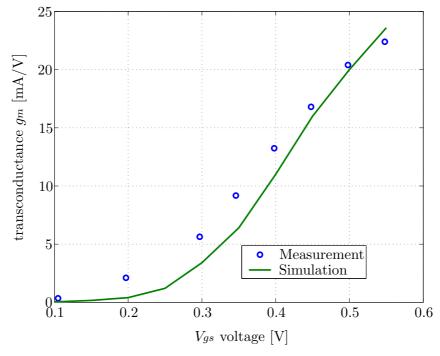

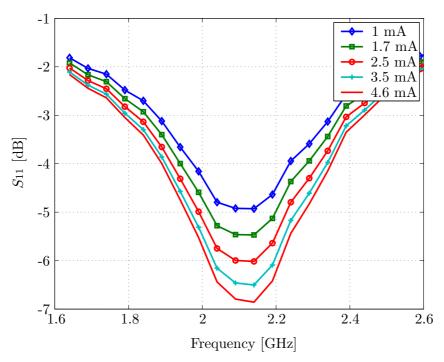

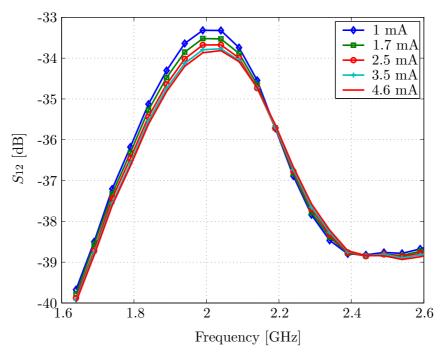

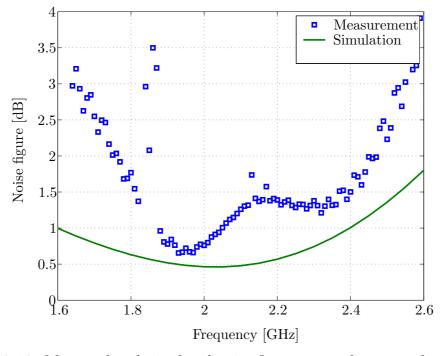

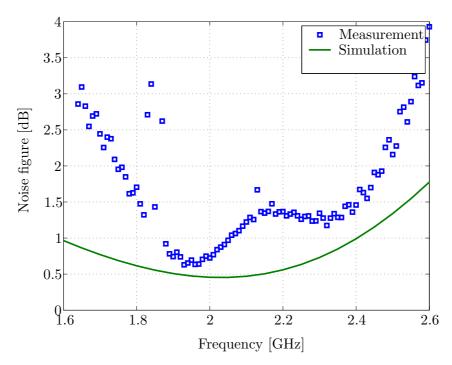

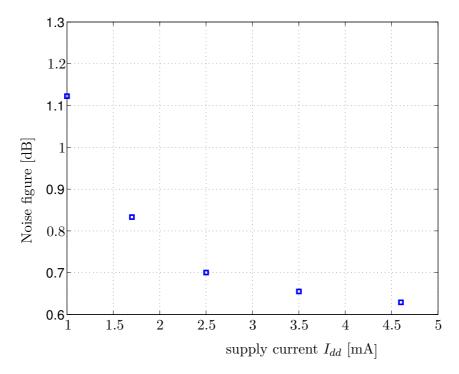

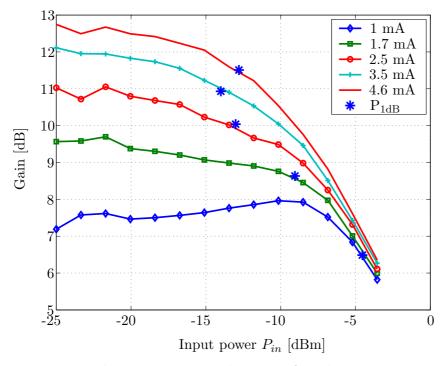

The transconductance of such a device in saturation is easily found from differentiating the expression for the drain current with respect to  $V_{gs}$  (with neglecting the channel length modulation):