# ULTRA WIDEBAND 5 W HYBRID POWER AMPLIFIER DESIGN USING SILICON CARBIDE MESFETs

von

Master of Engineering

Ahmed Sedek Mahmoud Sayed

von der Fakultät IV – Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades Doktor der Ingenieurwissenschaften – Dr.-Ing. –

genehmigte Dissertation

#### Promotionsausschuss:

Vorsitzender: Prof. Dr.-Ing. H. Klar Gutachter: Prof. Dr.-Ing. G. Böck Gutachter: Prof. Dr. G. Tränkle Dr. -Ing. W. Heinrich

Tag der wissenschaftlichen Aussprache: 31. Mai 2005

Berlin 2005

# ULTRA WIDEBAND 5 W HYBRID POWER AMPLIFIER DESIGN USING SILICON CARBIDE MESFETs

von

Master of Engineering

Ahmed Sedek Mahmoud Sayed

von der Fakultät IV – Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades Doktor der Ingenieurwissenschaften – Dr.-Ing. –

genehmigte Dissertation

#### Promotionsausschuss:

Vorsitzender: Prof. Dr.-Ing. H. Klar Gutachter: Prof. Dr.-Ing. G. Böck Gutachter: Prof. Dr. G. Tränkle Dr. -Ing. W. Heinrich

Tag der wissenschaftlichen Aussprache: 31. Mai 2005

Berlin 2005

@ Copyright by

AHMED SEDEK MAHMOUD SAYED

2005

All Rights Reserved

# **ACKNOWLEDGMENTS**

All praise is due to our God (ALLAH) who has been bestowing me with his great bounties and enabled me to complete my dissertation.

I'm deeply indebted to my graduate advisor, Professor Georg Boeck, who is extremely hard working and dedicated to his work, for his guidance and encouragement during the past four years. His work ethics, pragmatic methodology have greatly influenced my approach to the professional world and surely will be with me for the years to come.

I am also thankful to both Dr.-Ing. Wolfgang Heinrich and Prof. Dr.-Ing. Günther Tränkle for useful recommendations.

Of course I cannot forget the colleges at my microwave group here in Berlin and also my microstrip department in Cairo. I was lucky to meet like people, who advice and assistance me during my work.

My deep gratitude is due to my parents for their continuous guidance, encouragement, support, and prayers during my life. Thanks are due to my wife for her patience, help, and being away from her family for several years during my study.

Finally, to my Sons Alaa and Mohamed, when you smile, I see my live with colors. Thanks for Allah to be in my life.

# ZUSAMMENFASSUNG

Aufgrund des hohen Bandabstandes von SiC besitzen SiC-MESFETs ein hohe Duruchbruchspannung und können folglich bei hohen Versorgungsspannungen betrieben werden. Darüber hinaus besitzen sie eine hohe Elektronensättigungsgeschwindigkeit und Wärmeleitfähigkeit. Aufgrund dieser Eigenschaften eignen sich diese Bauelemente hervorragend für die Entwiklung von breitbandigen Leistungsverstärkern bis in den unteren GHz-Bereich. In dieser Arbeit wird ein neues empirisches Modell für SiC MESFET vorgeschlagen. Ein kommerziell erhältlicher, gehäuster MESFET Typ (CREE CRF24010) wird für die Entwicklung des Modelles verwendet. Messungen wurden sowohl in Arbeitspunkten mit als auch ohne Vorspannung durchgeführt um die Gleichungen und Parameter abzuleiten. Die "Cold FET" Technik wurde verwendet um die parasitären extrinsischen Elemente zu bestimmen, während die arbeitspunktabhängigen Elemente des Modelles analytisch bei mehreren Arbeitspunkten bestimmt wurden. Nichtlineare Gleichungen für die arbeitspunktabhängigen Elemente wurden ebenfalls abgeleitet. Das so entwickelte Modell für den SiC MESFET wurde sowohl hinsichtlich des Kleinsignal als auch des Großsignalverhaltens überprüft. Fünf verschiedene Generationen von Breitband-Leistungsverstärkern wurden auf Grundlage des entwickelten Modelles implementiert. Dabei wurde keinerlei Impedanztransformator eingesetzt. Eine neuartige breitbandige Biasstruktur wurde entwickelt, um gute Isolation und geringe Verluste über die angestrebte Bandbreite zu erreichen. Die Anpassungsnetzwerke an Eingang, Ausgang und zwischen den Stufen sowie die Parallel-Rückkopplung wurden mit Hilfe von Mikrostreifenleitungstechnik realisiert um die Bandbreite zu erhöhen und die Stabilität zu verbessern. Als erste Generation wird ein einstufiger 5 Watt Leistungsverstärker mit einem SiC MESFET entworfen und aufgebaut, der den Frequenzbereich von 10 MHz bis 2,4 GHz abdeckt. Eine Leistungsverstärkung von 6 dB, 37 dBm Ausgangsleistung, 33% PAE und 52 dBm OIP3 wurden erreicht. Ein zweistufiger Leistungsverstärker mit hoher Verstärkung für die selbe Bandbreite, der einen GaAs und einen SiC MESFET in Kaskade verwendet, wurde ebenfalls aufgebaut. 23 dB Leistungsverstärkung, 37 dBm Typische Werte von

Ausgangsleistung, 28 % PAE und 47 dBm OIP3 wurden erreicht. Der Einfluss der Treiberstufe auf die Leistungs- und Linearitätseigenschaften der zweiten Generation wurde untersucht. Basierend auf SiC Chips wurden die dritte und vierte Generation in Form von einstufigen und zweistufigen ultra-breitband Leistungsverstärkern implementiert, die das Frequenzband von 1 MHz bis 5 GHz abdecken. Der Einfluss des GaAs FET Treibers in der vierten Kategorie auf die Gesamteigenschaften wurde ebenfalls diskutiert. Unter Einsatz der Rückkopplungs-Kompensationstechnik wurde ein schmalbandiger 10 W Leistungsverstärkerentwurf mit hoher Verstärkung, basierend auf einem SiC Chip, als fünftes Beispiel vorgestellt. Alle Leistungs- und Linearitäts-Ergebnisse wurden über das gesamte Frequenzband ermittelt. Die Entwurfsprozedur wird detailliert beschrieben und die Ergebnisse werden diskutiert und ausführlich mit den Simulationen verglichen.

# **ABSTRACT**

SiC MESFETs have an enormous potential for realizing high-power amplifiers at microwave frequencies due to their wide band-gap features of high breakdown field, high electron saturation velocity and high operating temperature. In this thesis, a new empirical model for SiC MESFET is proposed. A commercially packaged high power MESFET device (CREE CRF24010) is adopted for the model development. Both hot and cold bias condition measurements are performed to derive equations and parameters. Cold FET technique is used to extract the parasitic extrinsic elements whereas the bias-dependent model elements are extracted analytically from multiple bias points. Nonlinear equations for the bias dependent elements are derived, too. The derived model for the SiC MESFET has been verified in small signal as well as large signal performances. Five different generations of broadband power amplifiers based on the developed model have been implemented. No impedance transformer was used at all. A novel broadband choke structure has been developed to obtain good isolation and low loss over the desired bandwidth. Input, interstage and output matching networks and shunt feedback topology have been designed based on microstip technique to increase the bandwidth and improve the stability. In the first generation, a single stage 5-watt power amplifier using a SiC MESFET covering the frequency range from 10 MHz to 2.4 GHz is designed and fabricated. A power gain of 6 dB, 37 dBm output power, 33 % PAE and 52 dBm OIP3 have been achieved. A high gain two stage power amplifier covering the same bandwidth using a GaAs- and a SiC-MESFET in cascade also has been fabricated. Typical values of 23 dB power gain, 37 dBm output power, 28 % PAE and 47 dBm OIP3 have been obtained. The impact of the driver stage on power and linearity performances of the second generation has been discussed. Based on SiC Chip, the third and the fourth generation represent ultra wideband single stage and two stage power amplifiers, covering the frequency band from 1 MHz to 5 GHz have been simulated. Small signal and harmonic balance simulations based on ADS have been introduced. The impact of the GaAs FET driver in the fourth category on the overall performances also has been discussed. Using feedback compensation technique, a 10-W narrow band high gain power amplifier ABSTRACT Ahmed Sayed

design based on SiC Chip has been presented as a fifth example. All power and linearity results were obtained over the whole frequency band. The design procedure is given in detail and the results are being discussed and compared with simulations extensively.

# TABLE OF CONTENTS

| ACKNO          | WLEDGEMENT                                                      | I        |

|----------------|-----------------------------------------------------------------|----------|

| ZUSSAN         | MENFASSUNG                                                      | III      |

| ABSTR <i>A</i> | ACT                                                             | V        |

| TABLE (        | OF CONTENTS                                                     | VII      |

| LIST OF        | TABLES                                                          | XI       |

| LIST OF        | FIGURES                                                         | XIII     |

| СНАРТЕ         | ER ONE INTRODUCTION                                             | 1        |

| СНАРТЕ         | ER TWO POWER AMPLIFIER FUNDAMENTALS                             | 5        |

| 2.1            |                                                                 |          |

| 2.1            | Power Amplifier Design Considerations                           | د        |

|                | 2.1.2 Power Gain and Stability                                  | 7        |

|                | 2.1.3 Efficiency                                                | 7        |

|                | 2.1.4 Linearity                                                 | 8        |

| 2.2            | Distortion in Power Amplifiers                                  | 8        |

|                | 2.2.1 Harmonic distortion                                       | 8        |

|                | 2.2.2 Intermodulation Distortion                                | 10       |

|                | 2.2.3 Phase Distortion                                          |          |

|                | 2.2.4 Spurious Distortion                                       |          |

| 2.3            | Measures of Distortion                                          |          |

|                | 2.3.1 1 dB Compression Point                                    | 12       |

| 2.4            | 2.3.2 Intercept Point                                           | 13       |

| 2.4            | Power Amplifier Classes                                         | 13       |

|                | 2.4.1 Class A                                                   | 14       |

|                | 2.4.2 Class B                                                   | 14<br>15 |

|                | 2.4.3 Class AB                                                  | 13       |

|                | 2.4.4 Class D                                                   | 17       |

|                | 2.4.5 Class E                                                   | 17       |

|                | 2.4.6 Class F                                                   | 19       |

| CII A DET      | ED TUDEE CMALL CICNAL MODELDIC OF                               |          |

| CHAPTE         | ER THREE SMALL SIGNAL MODELING OF SILICON-CARBIDE MESFETS       | 21       |

| 2.1            |                                                                 |          |

| 3.1<br>3.2     | Why SiC MESFETs                                                 | 21       |

| 3.2            | Principles of the MESFET Operation  3.2.1 Parasitic Inductances | 25<br>26 |

|                | 3.2.2 Parasitic Resistances                                     |          |

|                | 3.2.2 Pad Capacitances                                          |          |

|                | 3.2.4 Intrinsic Capacitances                                    | 2.7      |

|                | 3.2.5 Charging Resistance R <sub>gs</sub>                       | 29       |

|                | 3.2.6 Transconductance                                          | 29       |

|                | 3 2 7 Transit Time                                              | 30       |

|        | 3.2.8 Output Resistance                                       | 30       |

|--------|---------------------------------------------------------------|----------|

| 3.3    | Small Signal Modeling and Parameter Extraction                | 31       |

|        | 3.3.1 Determination of the Intrinsic Y-Parameters             |          |

| 2.4    | 3.3.2 Intrinsic Parameters in Terms of Intrinsic Y-Parameters | 34       |

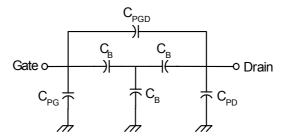

| 3.4    | A Simplified Model of the MESFET at Pinch-off Mode            | 34       |

|        | 3.4.1 Determination of Pad Capacitances                       | 33       |

|        | 3.4.2.1 Determination of Parasitic Inductances                |          |

|        | 3.4.2.1 Determination of Parasitic Resistances                |          |

| 3.5    | SiC MESFET Intrinsic Parameters Extraction                    | 37<br>42 |

| 5.5    | SIC WILST LT manister arameters Extraction                    | т∠       |

| CHAPT] | ER FOUR LARGE SIGNAL MODELING OF SIC MESFETS                  | 47       |

| 4.1    | Classification of device models                               | 47       |

| 7.1    | 4.1.1 Physical models                                         |          |

|        | 4.1.2 Empirical models                                        | 50       |

| 4.2    | Model Description.                                            |          |

|        | 4.2.1 DC Characterization                                     |          |

|        | 4.2.1.1 Curtice Cubic Model                                   |          |

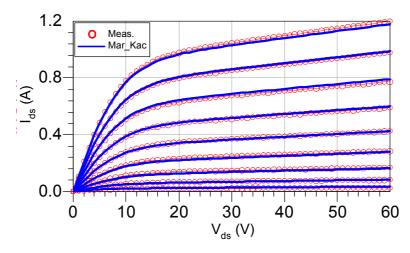

|        | 4.2.1.2 Materka-Kacprzak Model                                | 53       |

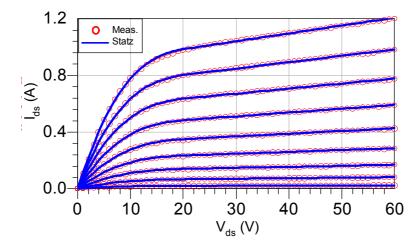

|        | 4.2.1.3 Statz Model                                           |          |

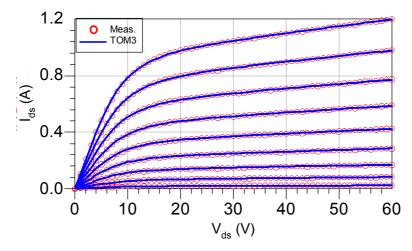

|        | 4.2.1.4 TOM3 Model                                            | 55       |

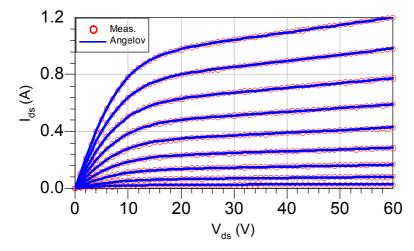

|        | 4.2.1.5 Chalmers (Angelov) Model                              | 57       |

|        | 4.2.2 Capacitive Modeling.                                    | 58       |

| 1.2    | 4.2.3 Frequency Dispersion                                    | 63       |

| 4.3    | Model Verification                                            |          |

|        | 4.3.1 Power Performance                                       |          |

| CHAPT  | ER FIVE WIDEBAND POWER AMPLIFIER                              |          |

|        | DESIGN                                                        | 69       |

| 5.1    | Power Amplifier structure                                     | 69       |

| 5.2    | Broadband matching                                            | 70       |

|        | 5.2.1 Bandwidth limitation                                    | 70       |

|        | 5.2.2 Bandwidth extending methods                             | 72       |

|        | 5.2.2.1 Feedback                                              | 72       |

|        | 5.2.2.2 Lossy Match                                           | 73       |

| 5.2    | 5.2.2.3 Broadband LC lowpass matching networks                |          |

| 5.3    | Design Procedure                                              | 7/       |

|        | 5.3.1 PA Specifications and Transistor Choice                 | /8<br>79 |

|        | 5.3.2 Stability                                               |          |

|        | 5.3.4 Broadband DC Biasing Network                            |          |

|        | 5.3.4.1 DC-DC Converter                                       | 85<br>85 |

|        | 5.3.5 Output matching for maximum output power                |          |

|        | 5.3.5.1 Power matching techniques                             | 86       |

|        | 5.3.5.1 Power matching techniques                             | 88       |

|        | 5.3.6 Input Matching for maximum gain                         | 90       |

|        | 5.3.6 Interstage Matching Network Design                      | 91       |

| 5.4    | Design examples                                               | 92       |

|        | 5.4.1 5 W wideband single stage PA                            | 93       |

|        | 5.4.2 5 W wideband two stage PA                               | 94       |

|        | 5.4.3 5 W ultra wideband single stage PA using SiC Die        | 96       |

|        | 5.4.4 5 W ultra wideband two stage PA using SiC Die           | 97/      |

|        | 5.4.5 10 W high gain single stage PA using SiC Die            | 98       |

| CHAPTER   | SIX POWER AMPLIFIER PERFORMANCE                                       | 101 |

|-----------|-----------------------------------------------------------------------|-----|

| 6.1 Sr    | mall Signal Performance                                               | 101 |

|           | 1.1 5 W Wideband Single Stage PA                                      |     |

| 6.        | 1.2 5 W Wideband Two Stage PA                                         | 103 |

| 6.2 Pc    | ower Performance                                                      | 104 |

|           | 2.1 5 W Wideband Single Stage PA                                      | 105 |

| 6.        | 2.2 5 W Wideband Two Stage PA                                         | 106 |

| 6.        | 2.3 5 W Ultra Wideband Single Stage PA Using SiC Chips                | 107 |

|           | 2.4 5 W Ultra Wideband Two Stage PA Using SiC Chips                   | 109 |

| 6.        | 2.4 5 W Ultra Wideband Two Stage PA Using SiC Chips                   | 110 |

| 6.3 Li    | nearity Performance                                                   | 111 |

| 6.        | 3.1 5 W Wideband Single Stage PA                                      | 112 |

|           | 3.2 5 W Wideband Two Stage PA                                         | 115 |

|           | 5 W Ultra Wideband Single Stage PA Using SiC Chips                    | 117 |

|           | 3.4 5 W Ultra Wideband Two Stage PA Using SiC Chips                   | 119 |

| 6.        | 3.5 10 W high gain Single Stage PA Using SiC Chips                    | 120 |

| CHAPTER   | SEVEN CONCLUSION                                                      | 123 |

| APPENDIX  | A INTERMODULATION DISTORTION ANALYSIS                                 | 127 |

| APPENDIX  | T B EXTRACTION OF INTRINSIC SMALL SIGNAL MODEL PARAMETERS             | 131 |

|           | erivation of Intrinsic Y-Parameters erivation of Intrinsic Parameters |     |

| APPENDIX  | C DETERMINATION OF BROADBAND GAIN BASED ON RESISTIVE FEEDBACK         | 135 |

| DECEDENIA |                                                                       | 120 |

# LIST OF TABLES

| Table     |                                                                        | Page |

|-----------|------------------------------------------------------------------------|------|

| Table 3.1 | Inherent material superiorities of SiC over silicon and GaAs           | 22   |

| Table 3.2 | Extracted extrinsic SiC MESFET equivalent circuit elements             | 42   |

| Table 4.1 | Extracted DC parameters of Curtice cubic model.                        | 53   |

| Table 4.2 | Extracted DC parameters of Materka-Kacprzak model                      | 54   |

| Table 4.3 | Extracted DC parameters of Statz model.                                | 56   |

| Table 4.4 | Extracted DC parameters of TOM3 model.                                 | 57   |

| Table 4.5 | Extracted DC parameters of the modified Angelov model.                 | 58   |

| Table 4.6 | Comparison of the error function values of the most used models in ADS | 58   |

| Table 5.1 | Specifications of EXCELICS GaAs FET from datasheet.                    | 97   |

| Table 6.1 | Specifications of the driver amplifier.                                | 105  |

# LIST OF FIGURES

| Figure      | 1                                                                                                                                                                                                 | Page |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2.1  | Frequency response of an ideal amplifier: a) at the input, b) at the output                                                                                                                       | 9    |

| Figure 2.2  | A frequency spectrum for the input and output of a nonideal amplifier.                                                                                                                            | 9    |

| Figure 2.3  | Graphical concept of intermodulation distortion.                                                                                                                                                  | 10   |

| Figure 2.4  | (a) AM-AM conversion, (b) AM-PM conversion, (c) combination of AM-AM and AM-PM conversion.                                                                                                        | 11   |

| Figure 2.5  | 1 dB compression point.                                                                                                                                                                           | 12   |

| Figure 2.6  | Graphical intercept point concept.                                                                                                                                                                | 13   |

| Figure 2.7  | Class A PA: (a) input waveform, (b) bias point                                                                                                                                                    | 14   |

| Figure 2.8  | Class B PA: (a) input waveform, (b) bias point.                                                                                                                                                   | 15   |

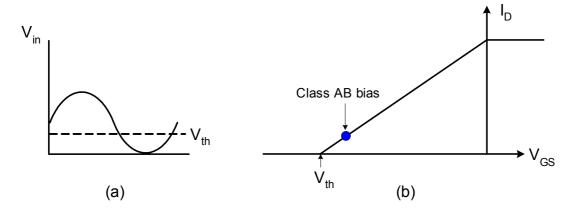

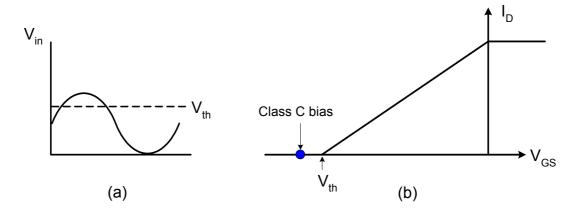

| Figure 2.9  | Class AB PA: (a) input waveform, (b) bias point.                                                                                                                                                  | 16   |

| Figure 2.10 | Class C PA: (a) input waveform, (b) bias point.                                                                                                                                                   | 17   |

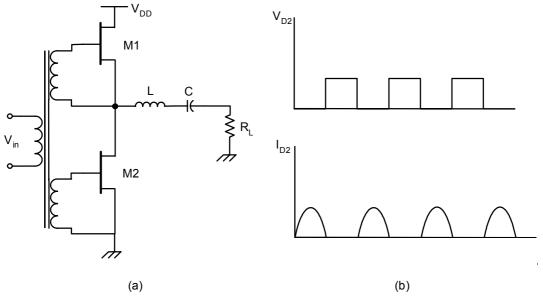

| Figure 2.11 | Class D PA: (a) circuit implementation, (b) ideal drain voltage and current waveforms.                                                                                                            | 18   |

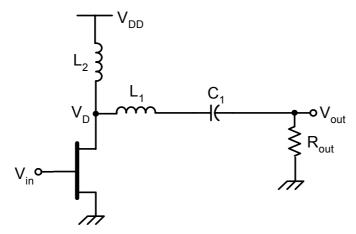

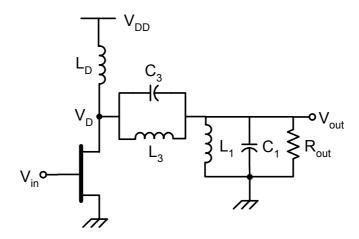

| Figure 2.12 | Class E PA implementation.                                                                                                                                                                        | 18   |

| Figure 2.13 | Class E PA waveforms                                                                                                                                                                              | 18   |

| Figure 2.14 | Class F PA implementation.                                                                                                                                                                        | 19   |

| Figure 2.15 | Class F waveforms.                                                                                                                                                                                | 19   |

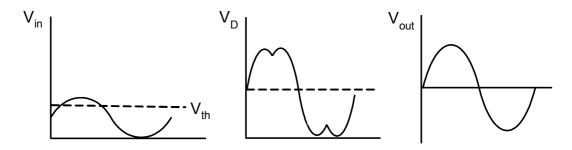

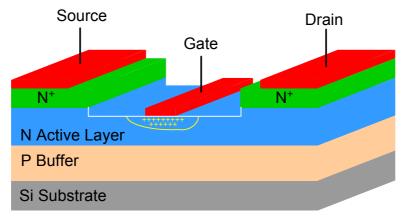

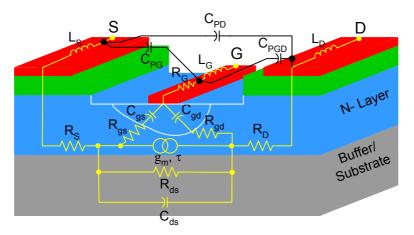

| Figure 3.1  | Perspective of SiC MESFET Structure.                                                                                                                                                              | 22   |

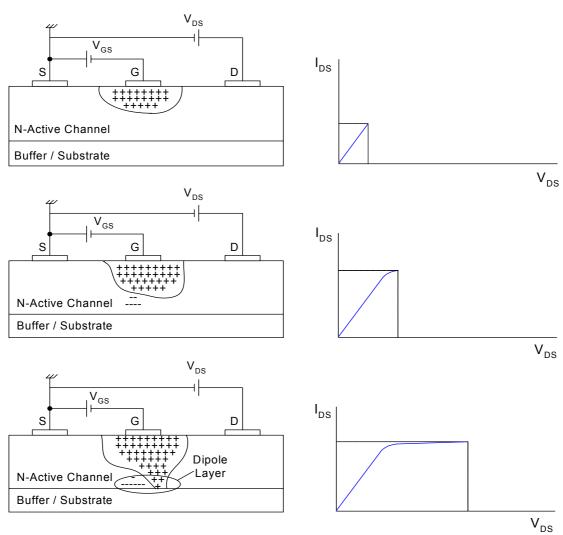

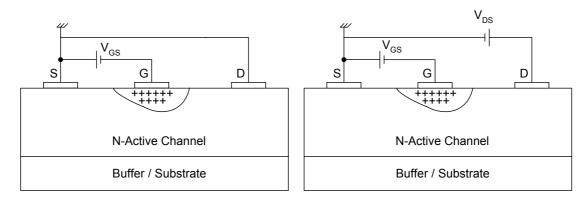

| Figure 3.2  | SiC MESFET operation under different $V_{ds}$ biasing with $V_{GS} < 0$ : (a) Linear region ( $V_{DS}$ is very low), (b) $V_{DS}$ at the onset of saturation, (c) $V_{DS}$ is high.               | 24   |

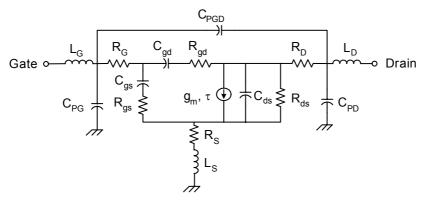

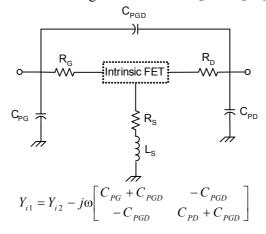

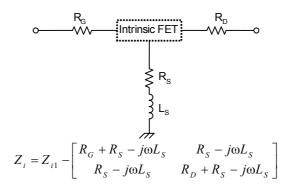

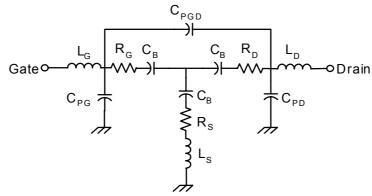

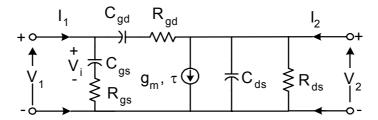

| Figure 3.3  | MESFET models showing physical origin of elementsand the corresponding small-signal model.                                                                                                        | 25   |

| Figure 3.4  | depletion region shapes for different applied bias voltages: (a) gate-<br>source voltage is equal to gate-drain voltage, (b) gate-drain reverse<br>bias is greater than gate-source reverse bias. | 29   |

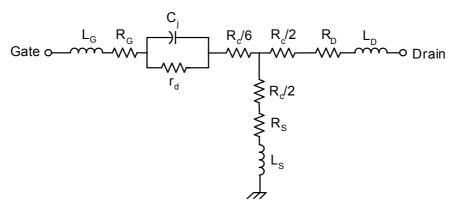

| Figure 3.5  | Small signal equivalent circuit of SiC MESFET.                                                                                                                                                                    | 32 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.6  | De-embedding of Inductances $L_G$ and $L_S$ : $S_{meas} \Longrightarrow Z_{i3}$                                                                                                                                   | 32 |

| Figure 3.7  | De-embedding of the parasitic capacitances $C_{PG}$ , $C_{PGD}$ and $C_{PD}$ : $Z_{i2} \Longrightarrow Y_{i2}$                                                                                                    | 32 |

| Figure 3.8  | De-embedding of the resistances $R_G$ , $R_D$ and $R_S$ : $Y_{i1} \Longrightarrow Z_{i1}$                                                                                                                         | 33 |

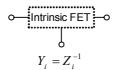

| Figure 3.9  | Converting of the intrinsic MESFET Z-parameters into Y-parameters: $Z_i \Longrightarrow Y_i$                                                                                                                      | 33 |

| Figure 3.10 | Simplified equivalent circuit at pinch-off mode.                                                                                                                                                                  | 35 |

| Figure 3.11 | Simplified equivalent circuit in the pinch-off mode at low frequencies.                                                                                                                                           | 35 |

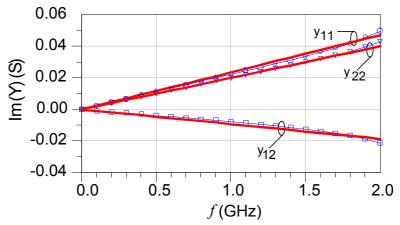

| Figure 3.12 | Simulated (solid lines) and measured imaginary part of Y-parameters after optimization process.                                                                                                                   | 37 |

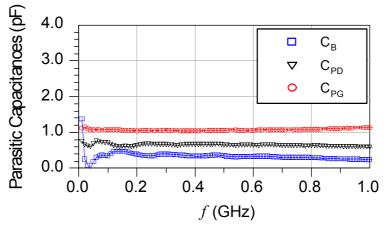

| Figure 3.13 | Extracted parasitic capacitances versus frequency                                                                                                                                                                 | 37 |

| Figure 3.14 | Simplified equivalent circuit at forward bias.                                                                                                                                                                    | 38 |

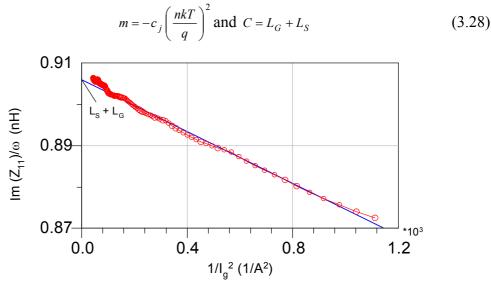

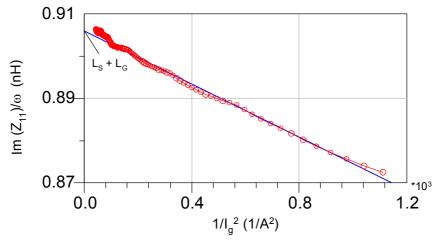

| Figure 3.15 | Dependency of $Im(Z_{11})$ on gate current $(1/I_g^2)$                                                                                                                                                            | 39 |

| Figure 3.16 | Dependency of Re $(Z_{11})$ on gate current $(1/I_g)$ .                                                                                                                                                           | 40 |

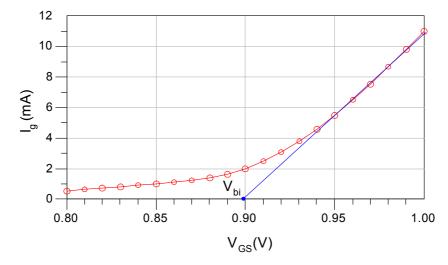

| Figure 3.17 | Extraction of diode built-in voltage from forward-bias diode characteristic s at $V_{\rm DS} = 0$                                                                                                                 | 41 |

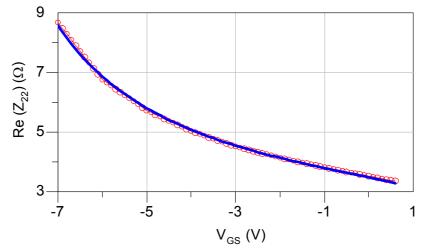

| Figure 3.18 | Extracted values of Re $(Z_{22})$ as a function of $V_{GS}$ between $V_p$ and $V_{bi}$ ; Measurements (circles), curve fitting function (solid line)                                                              | 41 |

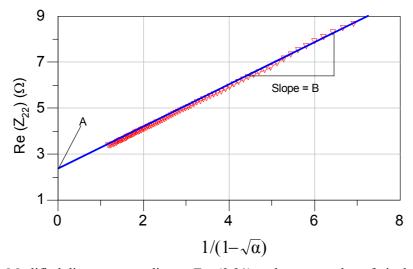

| Figure 3.19 | Modified diagram according to Eq. (3.31) at the exact value of pinch-off voltage; LRT in solid line resulting in $(R_S + R_D)$ extraction                                                                         | 42 |

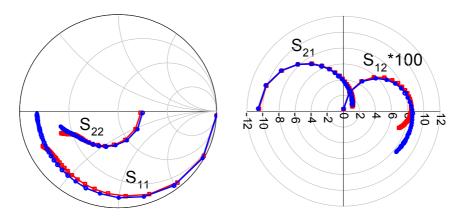

| Figure 3.20 | Measured (squares) and simulated (circles) S-parameters of SiC MESFET: Frequency range from 20 kHz to 4 GHz, $V_{ds}$ = 30 V and $V_{gs}$ = -7 V                                                                  |    |

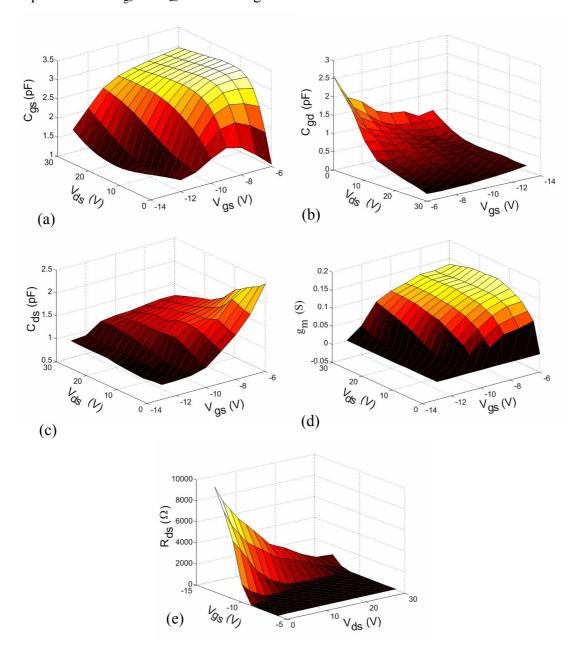

| Figure 3.21 | Extracted nonlinear parameters as a function of internal control voltages: a) gate-source capacitance, b) gate-drain capacitance, c) drain-source capacitance, d) transconductance and e) drain-source resistance | 44 |

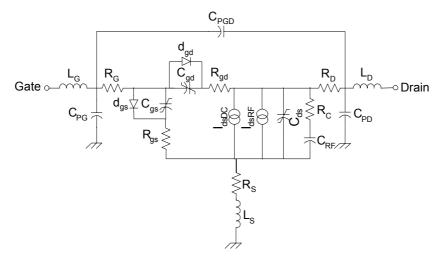

| Figure 4.1  | Large signal model of SiC MESFET                                                                                                                                                                                  | 52 |

| Figure 4.2  | Measured (symbols) and calculated (solid lines) DC characteristics of the CRF24010 based on Curtice cubic model, $V_{gs}$ = - 13 V to -5 V, step 1 V.                                                             | 53 |

| Figure 4.3  | Measured (symbols) and calculated (solid lines) DC characteristics of the CRF24010 based on Materka-Kacprzak model, $V_{\rm gs}$ = -13 V to -5 V, step 1 V.                                                       | 54 |

| Figure 4.4  | Measured (symbols) and calculated (solid lines) DC characteristics of the CRF24010 based on Statz model, $V_{gs} = -13 \text{ V}$ to $-5 \text{ V}$ , step 1 V                       | 56 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.5  | Measured (symbols) and calculated (solid lines) DC characteristics of the CRF24010 based on TOM3 model, $V_{\rm gs}$ = -13 V to -5 V, step 1 V.                                      | 56 |

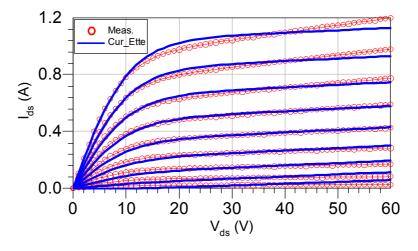

| Figure 4.6  | Measured (symbols) and calculated (solid lines) DC characteristics of the CRF24010 based on Angelov model, $V_{gs} = -13 \text{ V}$ to $-5 \text{ V}$ , step 1 V                     | 58 |

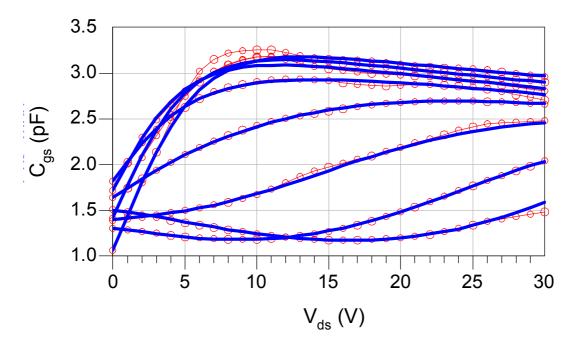

| Figure 4.7  | Measured (symbols) and modeled (solid lines) gate-source capacitance $C_{gs}$ versus $V_{ds}$ ; $V_{gs}$ varies from $-$ 13 V (bottom) to - 6 V (top), step 1 V                      | 60 |

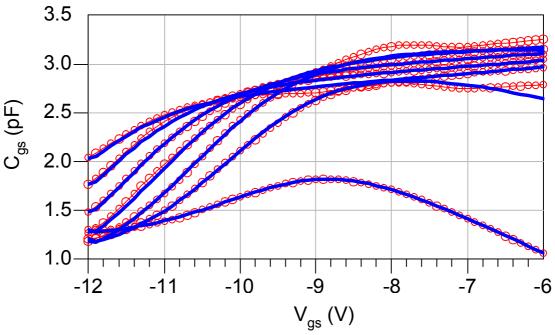

| Figure 4.8  | Measured (symbols) and modeled (solid lines) gate-source capacitance $C_{gs}$ versus $V_{gs}$ ; $V_{ds}$ varies from 0 V (bottom) to 30 V (top), step 5 V.                           | 61 |

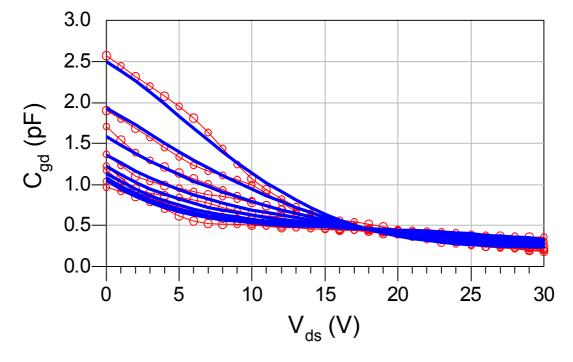

| Figure 4.9  | Measured (symbols) and modeled (solid lines) gate-drain capacitance $C_{gd}$ versus $V_{ds}$ ; $V_{gs}$ varies from $-13~V$ (bottom) to $-6~V$ (top), step 1 $V$                     | 61 |

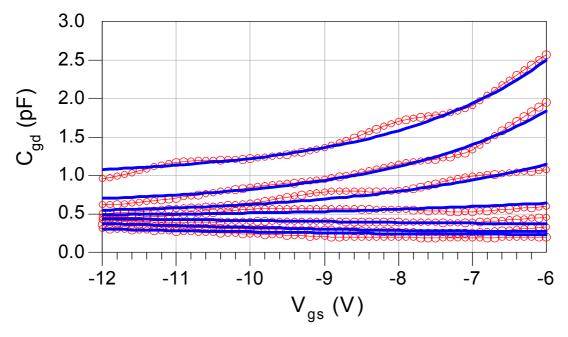

| Figure 4.10 | Measured (symbols) and modeled (solid lines) gate-drain capacitance $C_{gd}$ versus $V_{gs}$ ; $V_{ds}$ varies from 0 V (bottom) to 30 V (top), step 5 V.                            | 62 |

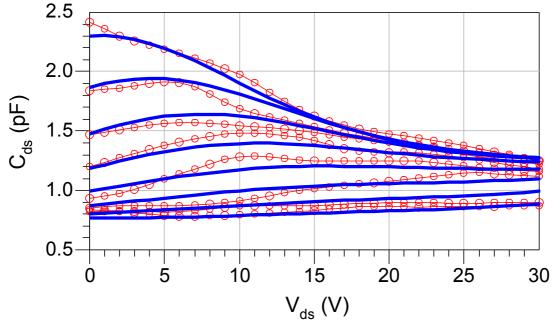

| Figure 4.11 | Measured (symbols) and modeled (solid lines) drain-source capacitance $C_{ds}$ versus $V_{ds}$ ; $V_{gs}$ varies from $-$ 13 V (bottom) to $-$ 6 V (top), step 1 V.                  | 62 |

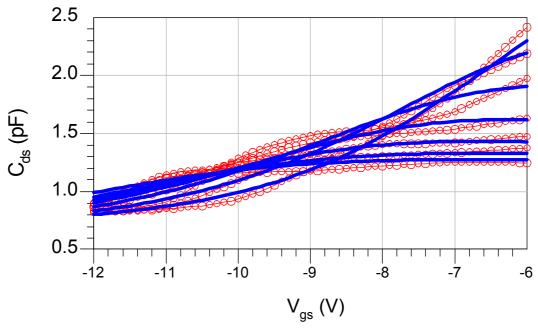

| Figure 4.12 | Measured (symbols) and modeled (solid lines) drain-source capacitance $C_{ds}$ versus $V_{gs}$ ; $V_{ds}$ varies from 0 V (bottom) to 30 V (top), step 5 V.                          | 63 |

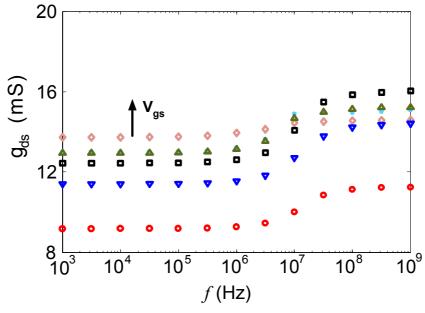

| Figure 4.13 | Dispersion of the output conductance at $V_{ds}$ = 30 V. $V_{gs}$ = -11 V to - 6 V, step 1 V.                                                                                        | 64 |

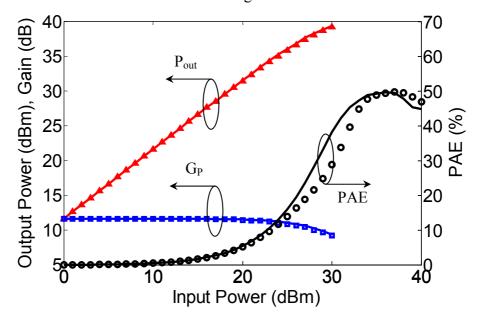

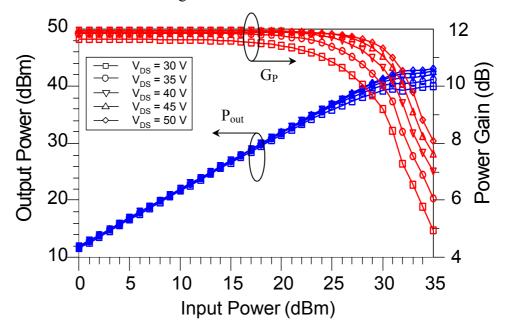

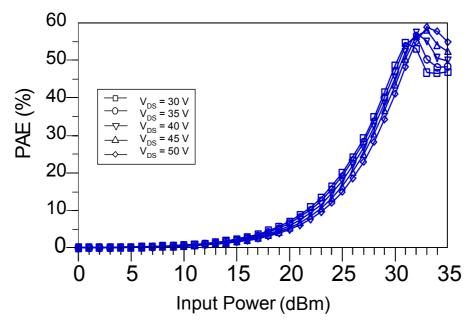

| Figure 4.14 | Power performance verification of the derived model (solid lines) compared with the Cree model (symbols). $f = 1 \text{ GHz}$ , $V_{DS} = 30 \text{ V}$ and $I_D = 500 \text{ mA}$ . | 65 |

| Figure 4.15 | Power performance verification of the derived model at different drain source voltages, $f = 1$ GHz.                                                                                 | 65 |

| Figure 4.16 | Power added efficiency of the derived model at different drain-<br>source voltages, $f = 1$ GHz.                                                                                     | 66 |

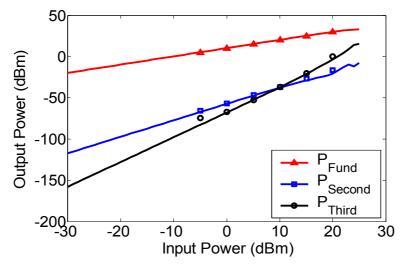

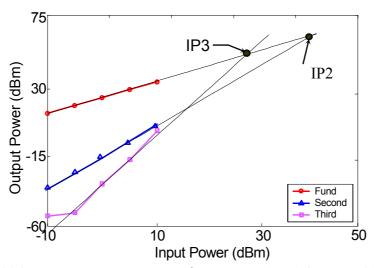

| Figure 4.17 | Two-tone test_ Comparison of the derived model (solid lines) and Cree's model performance (symbols) @ $f$ = 1 GHz, $V_{DS}$ = 30 V and $I_D$ = 500 mA.                               | 67 |

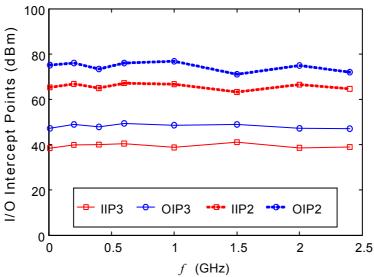

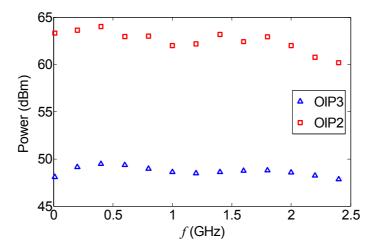

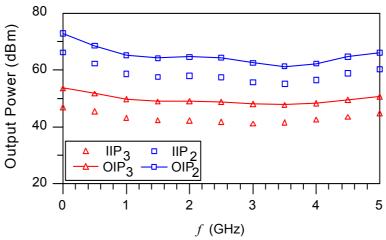

| Figure 4.18 | Sweep of output intercept points with frequency at $V_{DS} = 30 \text{ V}$ and $I_{DS} = 500 \text{ mA}$ : solid lines $\implies$ derived model, symbols $\implies$ Cree model.      | 67 |

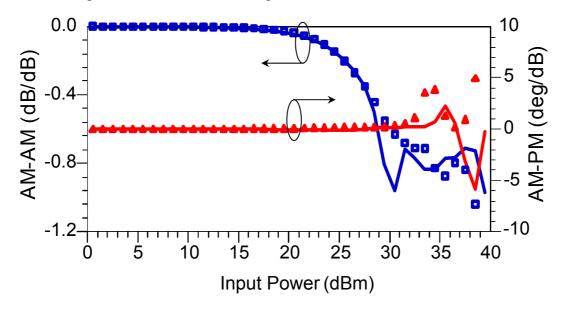

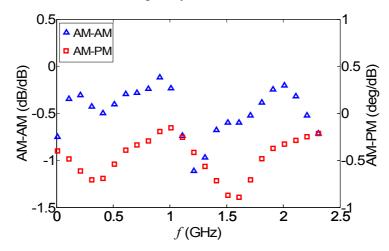

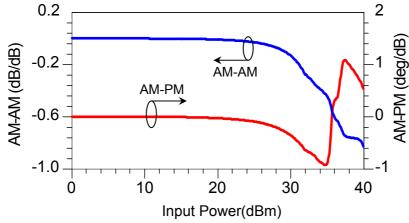

| Figure 4.19                                                     | AM-AM and AM-PM conversions: Comparison of the derived model (solid lines) and Cree's model performance (symbols) $@f = 1 \text{ GHz}, V_{DS} = 30 \text{ V} \text{ and } I_D = 500 \text{ mA}.$ | 68 |  |  |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

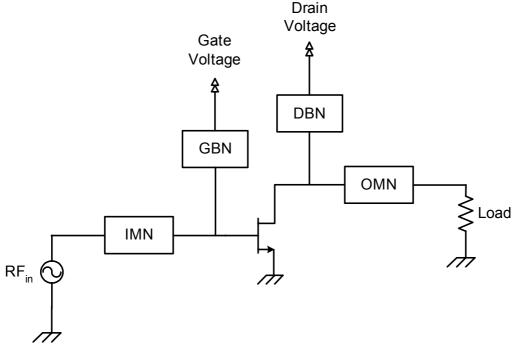

| Figure 5.1                                                      | Basic structure of single stage amplifier.                                                                                                                                                       | 70 |  |  |

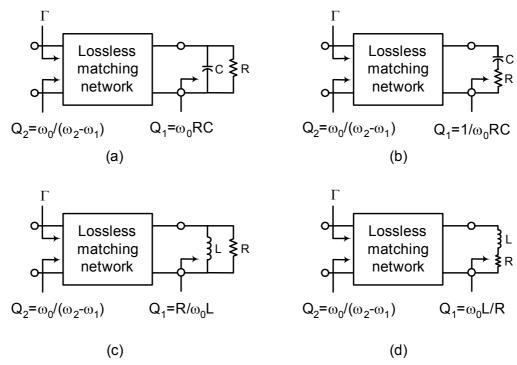

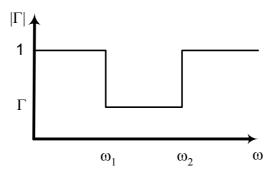

| Figure 5.2                                                      | Network topologies used in the calculation of the gain-bandwidth limitations.                                                                                                                    |    |  |  |

| Figure 5.3                                                      | Optimum values of $ \Gamma $                                                                                                                                                                     | 71 |  |  |

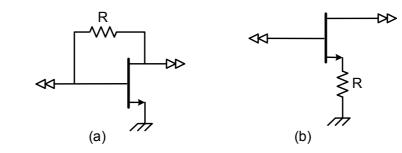

| Figure 5.4                                                      | Feedback configurations: (a) Shunt-shunt, (b) Series-series                                                                                                                                      |    |  |  |

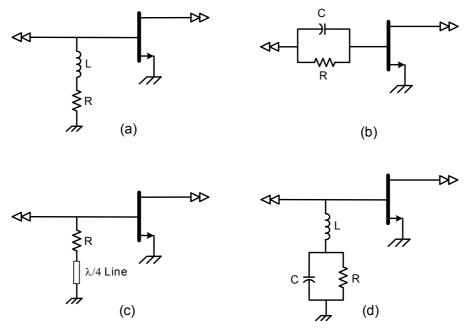

| Figure 5.5                                                      | lossy match networks at the input of the device (a) R-L shunt network, (b) R-C series network, (c) $R-\lambda/4$ line network, (d) R-L-C shunt network.                                          | 73 |  |  |

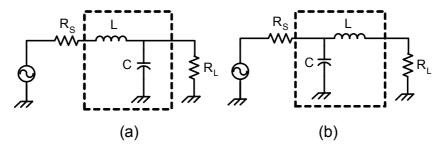

| Figure 5.6                                                      | Lowpass LC matching networks for (a) $R_L > R_S$ , (b) $R_L < R_S$                                                                                                                               | 75 |  |  |

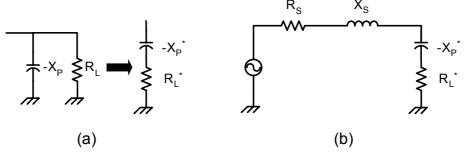

| Figure 5.7                                                      | are 5.7 (a) Transform from parallel to series network $(X_P = 1/\omega C)$ , (b) T equivalent circuit of figure 5.6 $(X_S = \omega L)$                                                           |    |  |  |

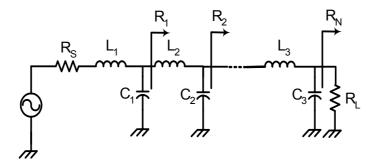

| Figure 5.8 Multi-stage low Q LC matching networks $(R_L > R_S)$ |                                                                                                                                                                                                  |    |  |  |

| Figure 5.9                                                      | Substitution of a lumped inductance by a transmission line.                                                                                                                                      | 77 |  |  |

| Figure 5.10                                                     | Substitution of a lumped inductance by a transmission line.                                                                                                                                      | 77 |  |  |

| Figure 5.11                                                     | Substitution of a lumped capacitor by an open circuit transmission line                                                                                                                          | 77 |  |  |

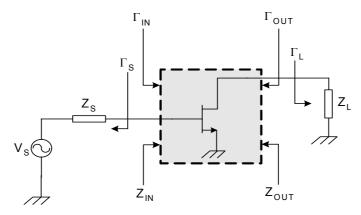

| Figure 5.12                                                     | Block diagram of a RF amplifier.                                                                                                                                                                 | 79 |  |  |

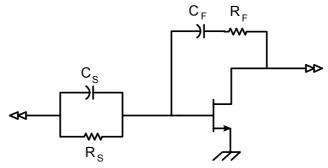

| Figure 5.13                                                     | Passive-network stabilization.                                                                                                                                                                   | 81 |  |  |

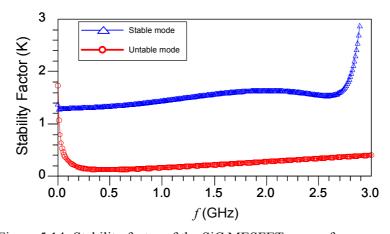

| Figure 5.14                                                     | Stability factor of the SiC MESFET versus frequency.                                                                                                                                             | 81 |  |  |

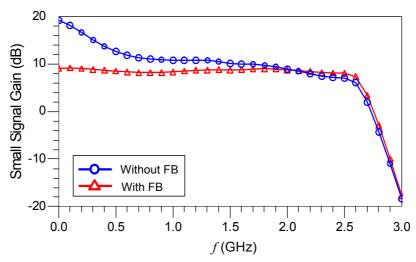

| Figure 5.15                                                     | Small signal gain of the SiC MESFET with and without feedback network.                                                                                                                           | 83 |  |  |

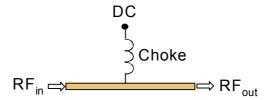

| Figure 5.16                                                     | Schematic of the board for the choke under test                                                                                                                                                  | 84 |  |  |

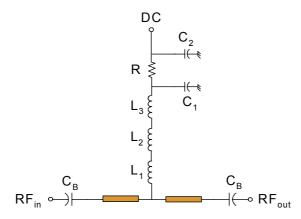

| Figure 5.17                                                     | DC biasing network                                                                                                                                                                               | 84 |  |  |

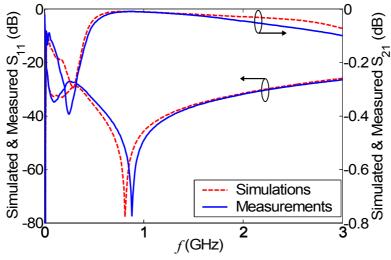

| Figure 5.18                                                     | Simulated and measured S-parameters of broadband choke                                                                                                                                           | 84 |  |  |

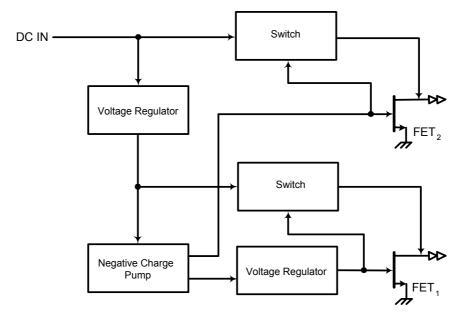

| Figure 5.19                                                     | Block diagram of the DC-DC converter for the two stage power amplifier.                                                                                                                          |    |  |  |

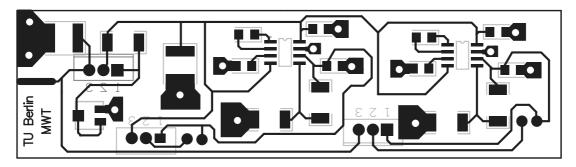

| Figure 5.20                                                     | PCB layout of DC biasing network for the two stage power amplifier.                                                                                                                              | 86 |  |  |

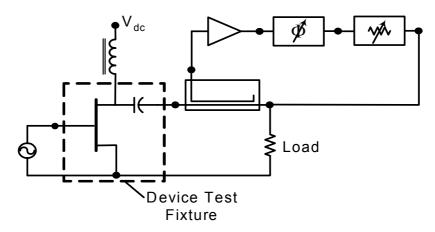

| Figure 5.21                                                     | Active load pull measurement system                                                                                                                                                              | 87 |  |  |

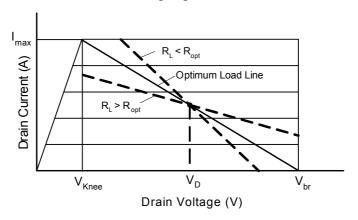

| Figure 5.22                                                     | Load-line method.                                                                                                                                                                                | 87 |  |  |

|                                                                 |                                                                                                                                                                                                  |    |  |  |

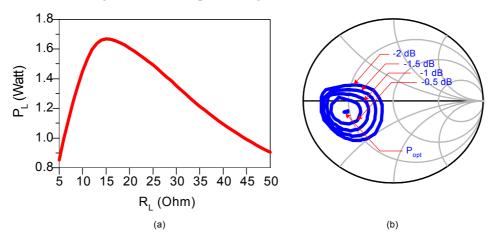

| Figure 5.23 | Load pull tuning based on the developed model                                                                               | 89   |

|-------------|-----------------------------------------------------------------------------------------------------------------------------|------|

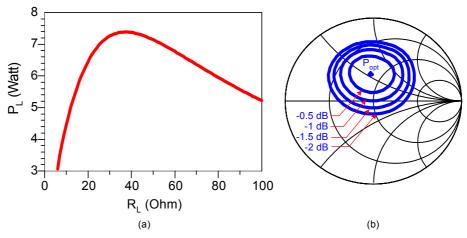

| Figure 5.24 | (a) Ouptut power of the power stage transistor (CRF24010) versus load, (b) Simulated load pull contours at $f = 2.4$ GHz    | 89   |

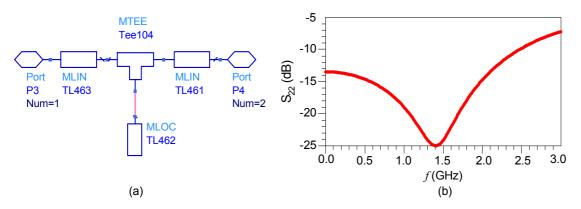

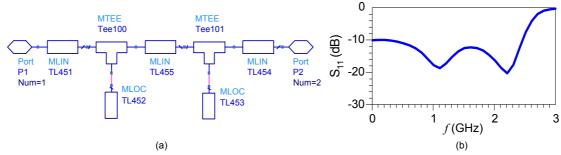

| Figure 5.25 | (a) Ouptut matching network topology, (b) Simulated output return loss of the power stage amplifier                         | 90   |

| Figure 5.26 | Load pull tuning of the driver GaAs FET.                                                                                    | 91   |

| Figure 5.27 | (a) Ouptut power of the driver stage transistor (FLL177ME) versus load, (b) Simulated load pull contours at $f = 2.4$ GHz   | 91   |

| Figure 5.28 | (a) Input matching network of the driver stage, (b) Simulated input return loss                                             | 91   |

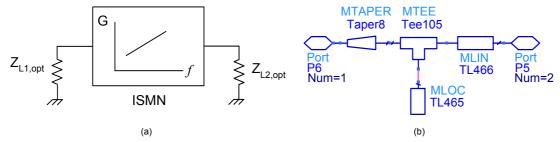

| Figure 5.29 | (a) Interstage matching network topology, (b) ISMN network                                                                  | 92   |

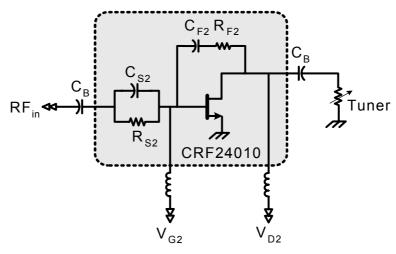

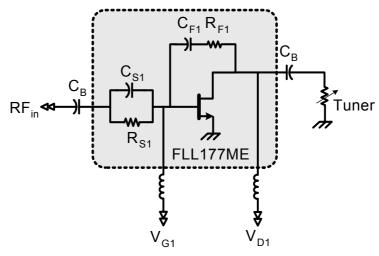

| Figure 5.30 | Schematic diagram of the power stage.                                                                                       | 94   |

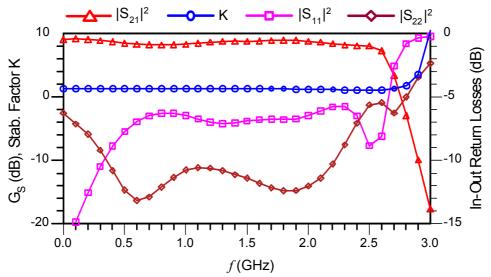

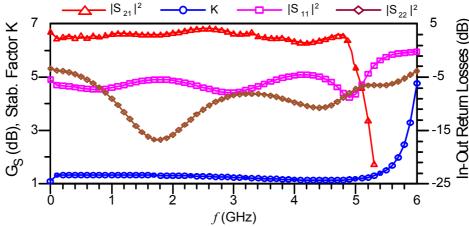

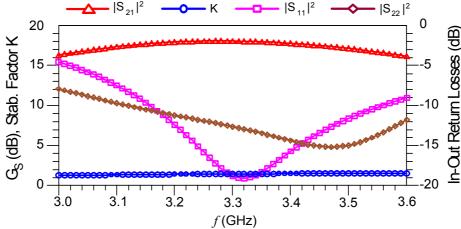

| Figure 5.31 | Small signal performance of the power stage.                                                                                | 94   |

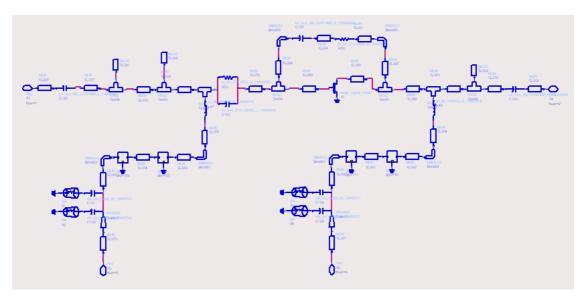

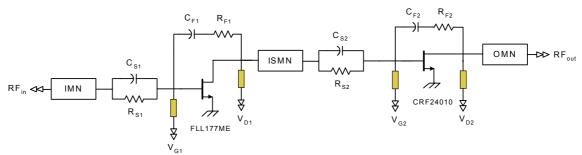

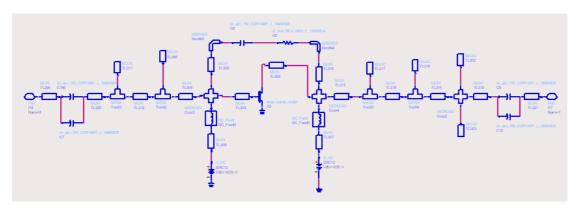

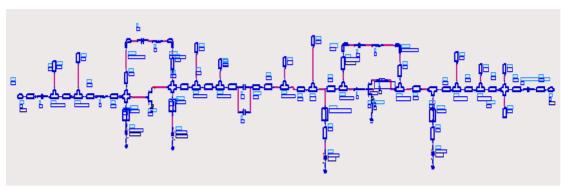

| Figure 5.32 | Schematic diagram of two stage power amplifier                                                                              | 95   |

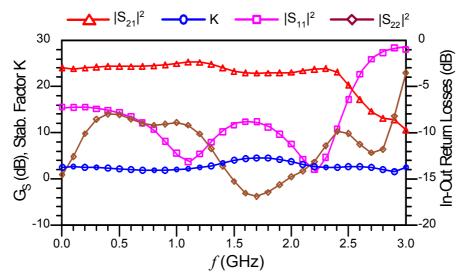

| Figure 5.33 | Small signal performance of the two stage power amplifier                                                                   | 96   |

| Figure 5.34 | Schematic diagram of the power stage amplifier using a SiC Die                                                              | 96   |

| Figure 5.35 | Small signal performance of the 5 W ultra broadband single stage PA using a SiC Die                                         | 97   |

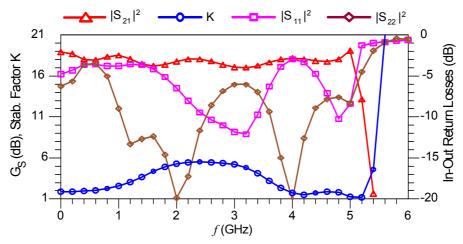

| Figure 5.36 | Schematic diagram of the ultra broadband two stage PA using a SiC Die.                                                      | 97   |

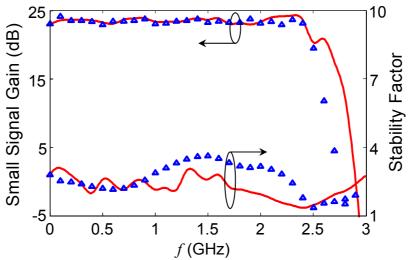

| Figure 5.37 | Small signal performance of 5 W ultra broadband two stage PA using SiC Die.                                                 | 98   |

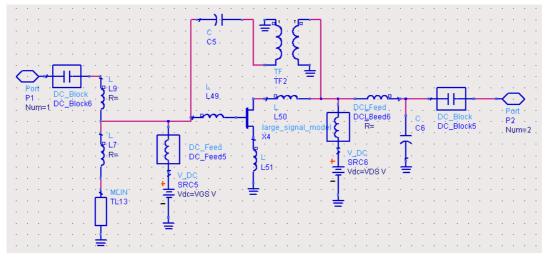

| Figure 5.38 | Schematic diagram of the high gain 10 W power amplifier.                                                                    | 98   |

| Figure 5.39 | Small signal performance of the 10 W high gain single stage PA                                                              | 99   |

| Figure 6.1  | Measurement setup of small signal performance.                                                                              | .102 |

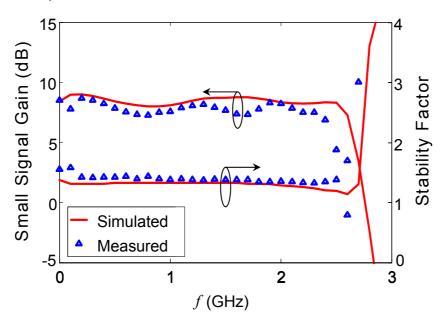

| Figure 6.2  | Simulated and measured gain and stability factor of the single stage PA.                                                    | .102 |

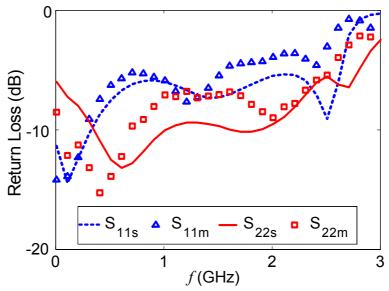

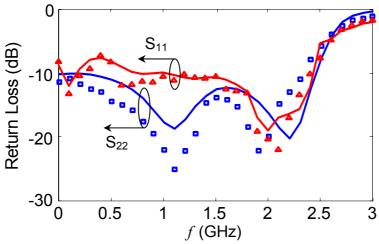

| Figure 6.3  | Simulated and measured return loss of the single stage PA                                                                   | .103 |

| Figure 6.4  | Simulated and measured gain and stability factor of two stage PA                                                            | .103 |

| Figure 6.5  | Simulated and measured return loss of the two stage PA: Input return loss (solid lines), output return loss (dashed lines). | .104 |

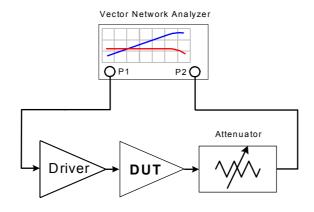

| Figure 6.6  | Power performance measurement setup.                                                                                        | .104 |

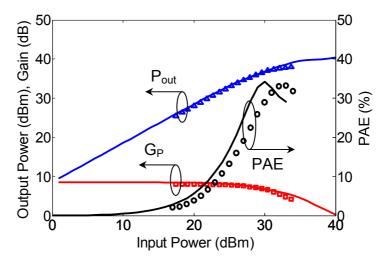

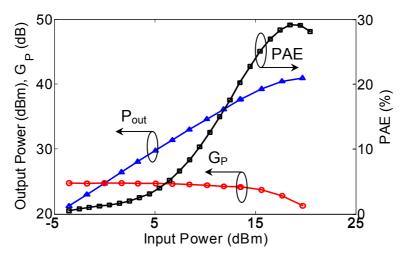

| Figure 6.7  | Measured (symbols) and simulated (solid lines) power performance of a single stage PA based on the derived model: $f = 1 \text{ GHz}$ , $V_{DS} = 30 \text{ V}$ , $I_D = 500 \text{ mA}$ . | 105 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

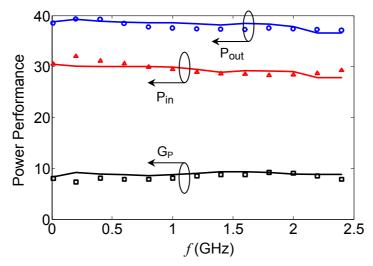

| Figure 6.8  | Simulated (solid lines) and measured power performances of the single stage PA over the operating frequency range: $V_{DS}$ = 30 V and $I_D$ = 500 mA.                                     | 106 |

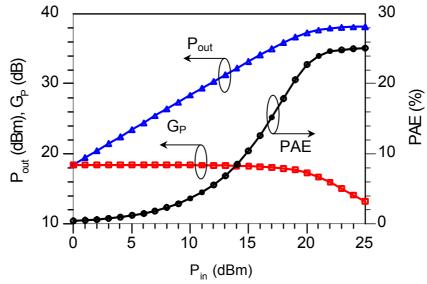

| Figure 6.9  | Measured power performance of the two stage PA at 1 GHz                                                                                                                                    | 106 |

| Figure 6.10 | Measured power performance of the two stage PA over the operating frequency range: $V_{D1}$ = 10 V, $I_{D1}$ = 350 mA, $V_{D2}$ = 30 V and $I_{D2}$ = 500 mA.                              | 107 |

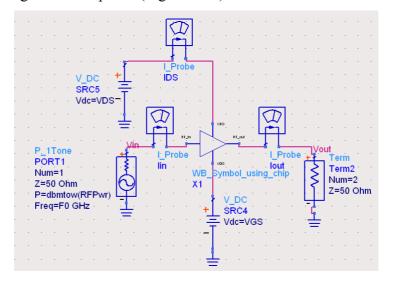

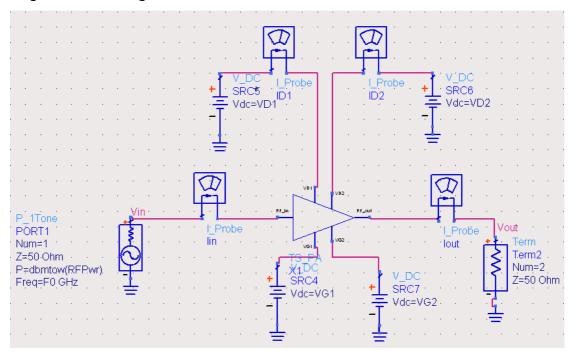

| Figure 6.11 | Schematic diagram of the single-tone HB simulation.                                                                                                                                        | 107 |

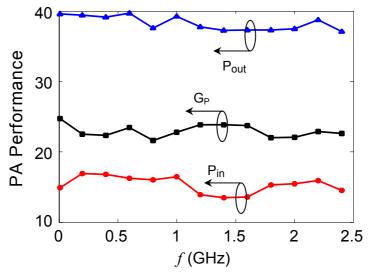

| Figure 6.12 | Simulated power performance of the ultra wideband single stage PA at 1 GHz.                                                                                                                | 108 |

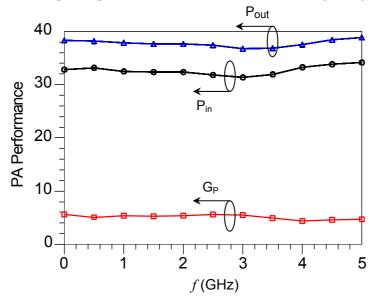

| Figure 6.13 | Simulated power performance of the ultra wideband single stage PA over the operating frequency range: $V_{DS} = 30 \text{ V}$ and $I_D = 500 \text{ mA}$                                   | 108 |

| Figure 6.14 | Schematic diagram of single-tone HB simulation for the ultra WB-two stage PA                                                                                                               | 109 |

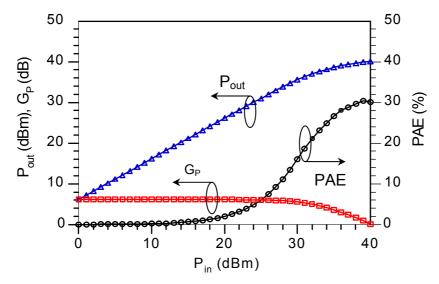

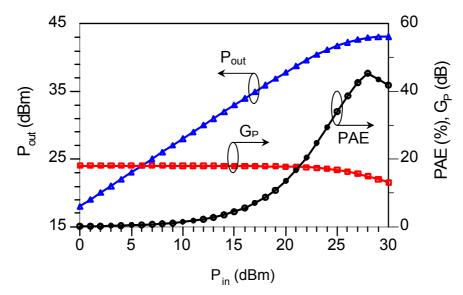

| Figure 6.15 | Simulated power performance of the ultra WB two stage PA at 1 GHz.                                                                                                                         | 110 |

| Figure 6.16 | Simulated power performance of the 10 W high gain single stage PA at 3.3 GHz.                                                                                                              | 110 |

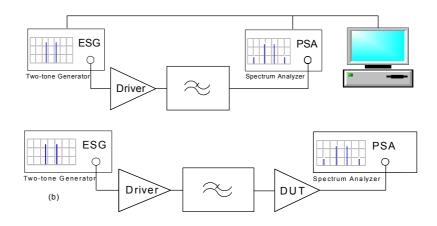

| Figure 6.17 | Two-tone measurement setup based on the Agilent Mulitone Studio: a) IMD cancellation b) IMD measurements of DUT.                                                                           | 111 |

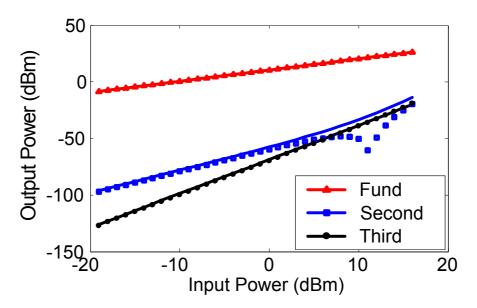

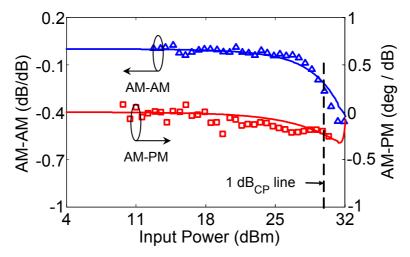

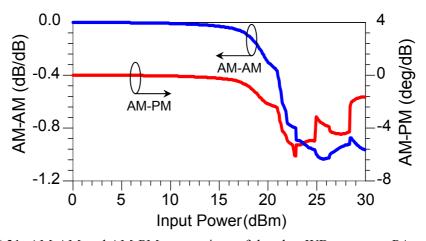

| Figure 6.18 | AM-AM and AM-PM response of single-stage PAs at $f= 2$ GHz: measurements $\implies$ (symbols) and simulations $\implies$ (solid lines)                                                     | 112 |

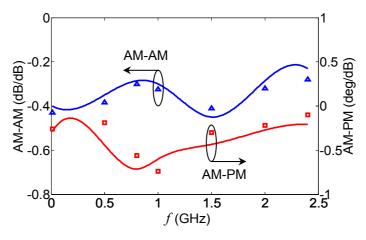

| Figure 6.19 | Measured (symbols) and modeled (solid lines) AM-AM and AM-PM response of the SiC power stage versus frequency: $V_{DS} = 30 \text{ V}$ , $I_D = 500 \text{ mA}$ .                          | 113 |

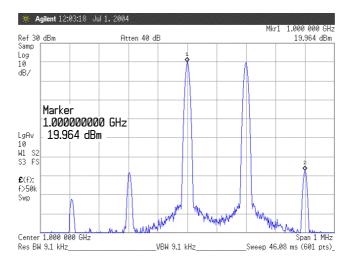

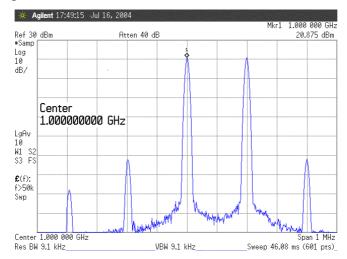

| Figure 6.20 | Two-tone measurement of the wideband single stage PA at $Pin = 0$ dBm, $f = 1$ GHz and $\Delta = 200$ kHz.                                                                                 | 113 |

| Figure 6.21 | Two-tone measurements (symbols) and simulations (solid lines) of the single stage PA at 1 GHz, $\Delta$ = 200 kHz                                                                          | 114 |

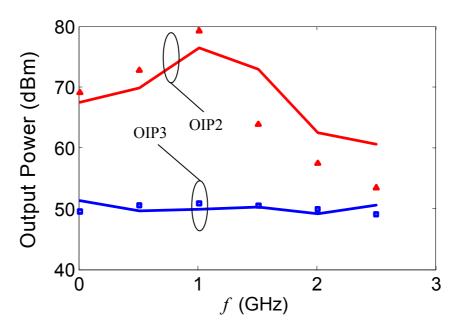

| Figure 6.22 | Extrapolated input and output intercept points of the wideband single stage PA at $V_{DS}$ = 30 V and $I_D$ = 500 mA.                                                                      | 114 |

| Figure 6.23 | AM-AM (squares) and AM-PM (triangles) response of two-stage PA at $f = 2$ GHz.                                                                                                             | 115 |

| Figure 6.24 | Measured AM-AM (triangles) and AM-PM (squares) conversions of the two stage PA versus frequency                                                                                            | 115 |

| Figure 6.25 | Two-tone measurement of the two stage PA at $P_{in} = 0$ dBm, $f = 1$ GHz and $\Delta = 200$ kHz.                                                                         | 116 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 6.26 | Two-tone measurements of the two stage PA at 1 GHz, $\Delta$ = 200 kHz.                                                                                                   | 116 |

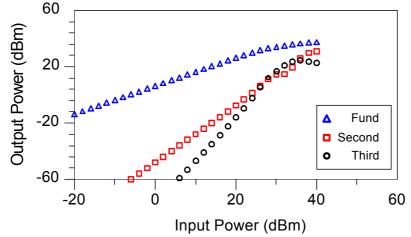

| Figure 6.27 | Extracted output intercept points of the wideband two stage PA: $V_{D1} = 10 \text{ V}$ , $I_{D1} = 350 \text{ mA}$ $V_{D2} = 30 \text{ V}$ and $I_{D2} = 500 \text{ mA}$ | 117 |

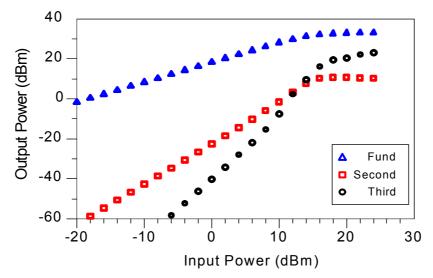

| Figure 6.28 | Amplitude and phase convesions of the ultra WB single stage PA at $f=1$ GHz.                                                                                              | 118 |

| Figure 6.29 | Simulated two-tone performance of the ultra WB single stage PA at $f=1$ GHz and $\Delta=200$ kHz.                                                                         | 118 |

| Figure 6.30 | Extracted input and output intercept points of the ultra WB single stage PA: $V_{DS} = 30 \text{ V}$ and $I_D = 500 \text{ mA}$ .                                         | 119 |

| Figure 6.31 | AM-AM and AM-PM conversions of the ultra WB two stage PA at 1 GHz.                                                                                                        | 119 |

| Figure 6.32 | Two-tone performance of the ultra WB two stage PA: $f = 1$ GHz and $\Delta = 200$ kHz.                                                                                    | 120 |

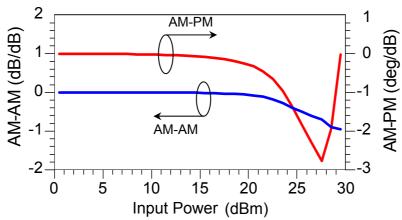

| Figure 6.33 | AM-AM and AM-PM conversions of the 10 W high gain single stage PA at 1 GHz.                                                                                               | 120 |

| Figure 6.34 | Two-tone performance of the 10 W high gain single stage PA at $f = 3.3$ GHz and $\Delta = 200$ kHz                                                                        | 121 |

| Figure A.1  | Frequency spectrum of intermodulation distortion                                                                                                                          | 129 |

| Figure B.1  | Intrinsic model for MESFET                                                                                                                                                | 131 |

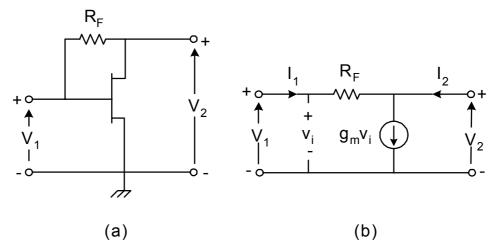

| Figure C.1  | (a) MESFET with shunt feedback (b) Feedback equivalent circuit                                                                                                            | 135 |

# **CHAPTER ONE**

# INTRODUCTION

The demand for power amplifiers has been continually increasing over the last decade. The requirements include aspects of high power level, high efficiency, high linearity and high operating frequency and the relative importance of each of these features is application specific [1 - 3]. One major trend is the continuous demand for more power over a very wide bandwidth. Unfortunately, the existing technologies have struggled to satisfy the higher demand. GaAs-based power devices have been very reliable workhorses at high frequencies especially in the microwave spectrum. However, their power performances have already been pushed close to the theoretical limit [4].

Under such circumstance, wide band-gap semiconductors with an order of magnitude or so higher breakdown voltage along with excellent thermal properties began to emerge. High breakdown voltage makes low operating current and high internal impedance possible. High internal impedance in turn can simplify impedance matching and result in efficient power coupling and broad bandwidth. Further, the performance of these transistors does not degrade drastically under elevated temperatures (unlike conventional GaAs and silicon devices). Therefore, we expect RF power amplifiers made of these transistors to have uniform performance characteristics over both a wide bandwidth and a wide temperature range. Such amplifiers are very desirable for applications in measurement equipment, aerospace and military systems that involve frequency hopping or spread spectrum operation under a fluctuating ambient temperature [5 - 7].

The interest in power amplifier design based on SiC MESFETs necessitates the development of accurate large signal models that can predict the maximum output power level, achievable power added efficiency (PAE) and other nonlinear phenomena over the whole operating frequency range, using harmonic balance (HB) simulation. Empirical table-based models of MESFET are the most widely used models in nonlinear circuit simulators today which have the important advantage of

Ahmed Sayed Introduction

flexibility and high computation efficiency. A lot of empirical models suitable for the simulation of MESFET in nonlinear circuits have been developed. In this approach, the tabulated data that represent the extracted nonlinear elements of the small signal model are mathematically transformed into spline functions which should be differentiable to a high order of derivatives in order to ensure a correct description of harmonics and convergence with harmonic balance simulations.

In order to achieve a higher output power level, a large periphery device would be required. The lowered impedance levels of the devices would represent more difficulty in the design of the matching networks. Generally speaking, the ratio for each matching circuit should be less than 1.5 in order to achieve larger than 3:1 bandwidth. Multisection matching networks would be necessary to achieve the desired bandwidth, resulting in more complex and lossy matching networks [8], [9]. In this work, impedance transformation is demonstrated based on multisections of microstrip elements. The output matching network is implemented based on the simulated load pull data for maximum output power. Input, and interstage matching networks are designed for maximum gain. Feedback technique is used to flatten the gain ripple and improve the stability of the device. A novel DC biasing network is developed with very low loss to meet the wide frequency band. [11], [70].

With the power density advantage of the SiC MESFETs technology and the novel approaches to the challenges of the broadband power amplifier design, we have successfully designed five categories of SiC power amplifiers; two of them have been fabricated and measured. All simulations in this work have been accomplished based on ADS2003A from Agilent while the design fabrication has been done based on microstrip materials R4003 from Rogers.

This thesis includes seven chapters. First chapter is the introduction of the thesis; it describes the background of the research and defines the objective of the thesis. Chapter 2 reviews the fundamentals of the power amplifier, design considerations, distortion in amplifiers and how to measure it and some of power amplifier classes have been also described.

Chapter 3 introduces an accurate small signal parameter extraction procedure. Extrinsic parameters in both pinch-off and forward bias modes are extracted using cold FET technique whereas the intrinsic parameters are being extracted analytically at various bias points.

Introduction Ahmed Sayed

Chapter 4 presents the model incorporating empirical expressions for DC, capacitance and frequency dispersion modeling. Accuracy of the new model will also be verified. A model developed by Cree for the packaged transistor CRF24010 is compared in its performance to the proposed model.

Chapter 5 introduces the design procedure in 3 steps. First, the selection process leading to the power transistor, which fulfils the design requirements, is described. The development of the DC biasing networks that meet the desired bandwidth is considered in the next step while the third one deals with input, output and interstage matching networks as well as shunt feedback circuit design resulting in the required broadband characteristic.

In chapter 6, simulations and measurements of the implemented amplifiers are given and discussed. Small-signal gain, stability factor and matching over the frequency band are introduced, and power performances (PAE, output power and power gain) are presented. Two-tone measurements at frequency spacing of 200 kHz have been performed, too. AM-AM and AM-PM conversion data are introduced and discussed at the end of the chapter.

Chapter 7 concludes the thesis with the achievements summary and suggestions for the future work.

Appendix A introduces a brief analysis for intermodulation distortion in power amplifiers. Appendix B presents the two-port intrinsic Y-parameters extraction in terms of the measured S-parameters. Small signal gain determination based on the value of the feedback resistance is presented in appendix C.

# **CHAPTER TWO**

# POWER AMPLIFIER FUNDAMNENTALS

The RF power amplifier (PA), a critical element in transmitter units of communication systems, is expected to provide a suitable output power at a very good gain with high efficiency and linearity. The output power from a PA must be sufficient for reliable transmission. High gain reduces the number of amplifier stages required to deliver the desired output power and hence reduces the size and manufacturing cost. High efficiency improves thermal management, battery lifetime and operational costs. Good linearity is necessary for bandwidth efficient modulation. However, these are contradicting requirements and a typical power amplifier design will require a certain level of compromise. There are several types of power amplifiers, which differ from each other in terms of linearity, output power or efficiency. In this chapter, we present an overview on power amplifiers; design considerations, distortions in power amplifiers and how to measure them. The last section introduces a number of PA classes that meet either high efficiency or linearity.

### 2.1 Power Amplifier Design Considerations

The beneficial method is to characterize the properties of MESFETs through its two-port scattering parameters matrix (S-parameters), which is widely used in RF/microwave theory. This approach works very well under steady state and small-signal approximation. As it is known when dealing with power amplifiers this approximation is not valid because the amplifier operates over a nonlinear region. Therefore, some other techniques have to be presented to conduct the appropriate design. Harmonic balance (HB) analysis is utilized as a method to characterize PA. Anyhow, small signal S-parameters may still be used when designing a class A amplifier with sufficient precision. Here the signal amplification is largely restricted

to the linear region of the transistor. However, the small-signal S-parameters become progressively unsuitable for class AB, B, or C amplifiers, due to changes in the transfer characteristic of the device (it is not possible to assume anymore that transconductance is constant) [12]. In other words, when the power of the input signal reaches a certain level, the amplifier saturates and starts clipping the output signal. The consequence is the generation of spurious frequencies that invokes distortion of the fundamental signal and power losses. As a result, the specific properties for evaluation of PAs as well as typical properties must be considered.

#### 2.1.1 Output Power

There are two concepts of power for RF/microwave circuits: available and dissipated power. Available or transferable is the maximum power, which is accessible from a source. The maximum available power is obtained from the source if the input impedance of the device equals the conjugate of the source impedance  $(Z_{in} = Z_s^*)$  [13]. Therefore, the maximum available power as a function of frequency can be expressed as:

$$P_{av}(\omega) = \frac{1}{8} \frac{\left| V_S(\omega) \right|^2}{\text{Re}\{Z_S(\omega)\}},$$

(2.1)

where  $V_S(\omega)$  is the peak value of a sinusoidal voltage applied to the input. Re $\{Z_S(\omega)\}$  is the real part of the source impedance. The dissipated or transferred power is the power dissipated in a load [14]. It can be expressed as:

$$P_d(\omega) = \frac{1}{2} \frac{\left| V_L(\omega) \right|^2}{\text{Re}\left\{ Z_L(\omega) \right\}},\tag{2.2}$$

where  $V_L(\omega)$  is the peak value of the sinusoidal output voltage. Re $\{Z_L(\omega)\}$  is the real part of the load impedance. The more practical representation for output power in terms of class A PA is;

$$P_{out} = \frac{1}{2} V_D I_D = \frac{1}{8} V_{\text{max}} I_{\text{max}},$$

(2.3)

where  $I_{max} = 2 I_D$ ,  $V_{max} = 2 V_{DS}$  are maximum drain current and voltage.

#### 2.1.2 Power Gain and Stability

Power gain is the ratio of the power delivered to an arbitrary load  $(P_L)$  to the power delivered to the network by the source  $(P_S)$ . It is a function of the load

reflection coefficient ( $\Gamma_L$ ) and the S-parameters of the network and it is independent of source reflection coefficient. This can be expressed as shown in the following formula:

$$G_P = \frac{P_L}{P_S} \tag{2.4}$$

The stability of a small-signal RF amplifier is ensured by deriving a set of S-parameters from measured data or a linear model, and then establishing the value of the K factor stability parameter. If the K factor is greater than unity, at the frequency and bias level in question, then expressions for matching impedances at input and output can be evaluated to give a perfect conjugate match for the device. Amplifier design in this context is mainly a matter of designing matching networks, which present the prescribed impedances over the necessary specified bandwidth. If the K factor is less than unity, negative feedback or lossy matching must be employed in order to maintain an unconditionally stable design (as will be discussed later in chapter 5).

There are cases where a device has a very high K factor value, but very low gain in conjugate matched condition. The physical cause of this can be traced to a device, which has gain roll-off due to carrier-mobility effects, rather than parasitics. In such cases, introduction of some positive feedback reduces the K factor and increases the gain in conjugately matched conditions, while maintaining unconditional stability.

### 2.1.3 Efficiency

Efficiency is a critical factor in PA design. Three definitions of efficiency are commonly used. Drain efficiency is defined as the ratio of RF output power to DC input power:

$$\eta = \frac{P_{out}}{P_{dc}} \tag{2.5}$$

Power-added efficiency (PAE) incorporates the RF drive power by subtracting it from the output power, i.e.

$$PAE = \frac{P_{out} - P_{in}}{P_{dc}} \tag{2.6}$$

PAE gives a reasonable indication of PA performance when gain is high. An overall efficiency such as  $P_{out}/(P_{dc} + P_{in})$  is useable in all situations. This definition can be varied to include driver DC input power, the power consumed by supporting circuits, and anything else of interest.

#### 2.1.4 Linearity

The need for linearity is one of the principal drivers in the design of modern power amplifiers. Nonlinearities cause imperfect reproduction of the amplified signal, resulting in distortion and splatter. In the next section, a variety of distortion in PAs will be discussed. Measures of distortion include 1 dB compression point representing the amplitude distortion, intercept point representing the intermodulation distortion, and amplitude to phase (AM–PM) conversion representing the phase distortion will also be presented.

#### 2.2 Distortion in Power Amplifiers

This section presents the various forms of RF amplifier distortion: single-tone (harmonic distortion), two-tone (intermodulation distortion), phase distortion and other spurious distortions.

#### 2.2.1 Harmonic distortion

An ideal amplifier will have a linear transfer characteristic, where the output voltage would be a scalar multiple of the input voltage, that is,

$$V_{out}(t) = K_1 V_{in}(t) \tag{2.7}$$

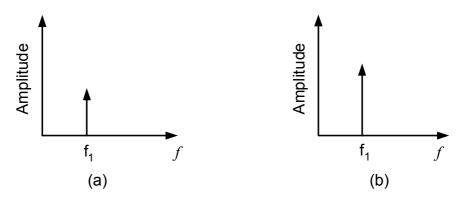

where  $K_1$  is the voltage gain of the amplifier. The output spectrum from such an amplifier will be identical to that of the input and no new (extra) frequency components will be introduced neither within nor outside the amplifier bandwidth as shown in figure 2.1.

However, practical amplifiers are nonlinear devices. A simple form of amplifier nonlinearity may be illustrated (for example) by the addition of a second order term to the transfer characteristic given by (2.7) as

$$V_{out} = K_1 V_{in}(t) + K_2 V_{in}^2(t)$$

(2.8)

Figure 2.1. Frequency response of an ideal amplifier: a) at the input, b) at the output.

Figure 2.2. A frequency spectrum for the input and output of a nonideal amplifier.

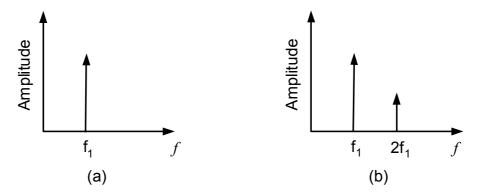

This nonlinear amplifier will introduce extra frequency components, which will appear at two times the original frequency. This gives rise to the term second harmonic distortion used to describe the form of nonlinear distortion introduced by the second-order term in the transfer characteristic, as shown in figure 2.2. Examination of the amplitude of the second harmonic component indicates that it will increase in proportion to the square of the input signal (and also in proportion to the constant, K<sub>2</sub>). The amplitude of the fundamental frequency component, however, will only increase in proportion to the voltage gain, K<sub>1</sub>. As a result, the amplitude of the second harmonic will increase at a greater rate than that of the fundamental component with increasing input level and at some input level both the fundamental and the second order harmonic will have the same output level, which is referred to as second harmonic intercept point. Note that a second order characteristic produces harmonic distortion but it does not produce in-band intermodulation distortion (see below). This is an important difference between even-order and odd-order nonlinearities, even-order nonlinearities do not generate in-band intermodulation distortion.

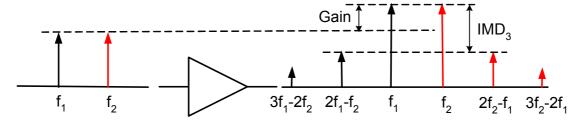

#### 2.2.2 Intermodulation Distortion

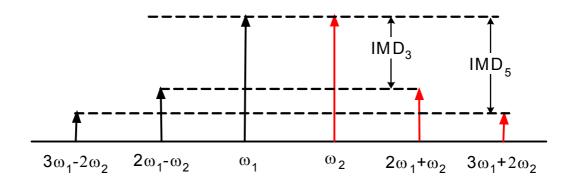

Intermodulation distortion is a nonlinear distortion characterized by the appearance in the output of a device, of frequencies that are linear combinations of the fundamental frequencies and all harmonics present in the input signals (see appendix A for details) [15]. A very common procedure to measure the intermodulation distortion is by means of a two-tone test. In a two-tone test a nonlinear circuit is excited by two closely spaced input sinusoids. This would result in an output spectrum consisting of various intermodulation products in addition to the amplified version of the two fundamental tones and their harmonics as shown in figure 2.3. If  $f_1$  and  $f_2$  are the fundamental frequencies then the intermodulation products are seen at frequencies given by

$$f_{IMD} = \pm m f_1 \pm n f_2 \tag{2.9}$$

The ratio of power in the intermodulation product to the power in one of the fundamental tones is used to quantify intermodulation. Of all the possible intermodulation products usually the third order intermodulation products (at frequencies  $2f_1-f_2$  and  $2f_2-f_1$ ) are typically the most critical as they have the greatest power. Furthermore they often fall into the receiver pass band making it difficult to filter them out.

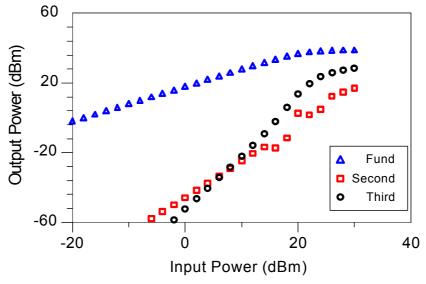

Figure 2.3. Graphical concept of intermodulation distortion.

#### 2.2.3 Phase Distortion

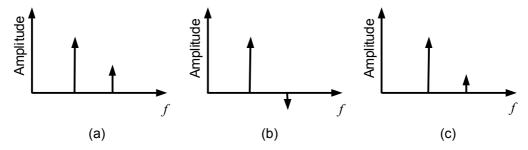

Most practical amplifier circuits exhibit memory effects because of storage elements such as capacitors and inductors. In this case, phase distortion can arise from capacitive or inductive nonlinearities. This is commonly referred to as amplitude-modulation-to-phase modulation (AM-PM) conversion. By applying a single-tone signal at the input of a nonlinear amplifier, the fundamental component at the output can be given by the form [16]:

$$(A + Be^{j\theta})\cos(\omega t) \tag{2.10}$$

The amplitude of equation (2.10) consists of a first order component, A, and a third order component,  $Be^{i\theta}$ , where  $\theta$  is the phase difference (due to nonlinear capacitances) between the two components.

Addition of the two phasors, linear and third order, leads to a phasor with a new angle. This new angle is dependent on variations of the input signal amplitude. As a result, changes in input amplitude give rise to changes in angle of the linear component of the output signal. This mechanism is called AM–PM conversion. Since the third order component rises three times faster than the first order output component on a logarithmic scale, AM–PM conversion will be most serious as the circuit is driven into saturation. Figure 2.4 illustrates AM–AM and AM–PM conversions on a sinusoidal signal in three cases: only amplitude conversion (Figure 2.4 (a)), only phase conversion as in case (b), and the superposition of two conversions as in figure 2.4(c).

Figure 2.4. (a) AM-AM conversion, (b) AM-PM conversion, (c) combination of AM-AM and AM-PM conversion.

# 2.2.4 Spurious Distortion

Some signals appear at the output of an amplifier and they have no obvious relationship to the input signals being amplified. They may appear and disappear randomly and may change frequency and level. Such signals are referred to as spurious products and consist of parasitic and sub-harmonic oscillations together with unwanted external interference.

#### 2.3 Measures of Distortion

In order to get a better understanding of the level of nonlinear distortion of a circuit, measures are defined which characterize nonlinear behaviour of the circuits.

Two commonly used measures to describe nonlinearities of a circuit are 1 dB compression point and third order intercept point (IP3). Simple test signals such as those described in the previous section are commonly used to test the device for linearity and find these measures. First, the 1 dB compression point as a measure for gain (output power) compression will be discussed.

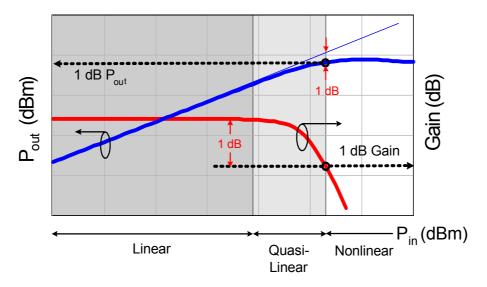

## 2.3.1 1 dB Compression Point

The 1 dB compression point is defined as the power gain where the saturation of the device (caused by nonlinearities) reduces the power gain by 1 dB over the small signal linear power gain [17]. This is the point where the gain is no longer in the linear area, and the component/system is starting to compress. It is useful to know the 1 dB compression point of any component or system, since this parameter determines the maximum input power which can be supplied to the amplifier and still have a gain that can be considered constant with respect to power level. As discussed in section 2.2, harmonic and intermodulation distortion (when multiple input frequencies are present) occur when the DUT starts to saturate. Figure 2.5 shows two different ways of displaying the same compression behaviour. Referring to the plot of Pout versus Pin, the compression can be seen to begin at the point where the data deviates from a linear 1:1 slope line. The second display method is to plot the gain versus input power. Compression can be seen to begin where the data drops below a constant valued gain, and the 1 dB compression point can be deduced as the point where the gain has dropped 1 dB, compared to the reference level.

Figure 2.5. 1 dB compression point.

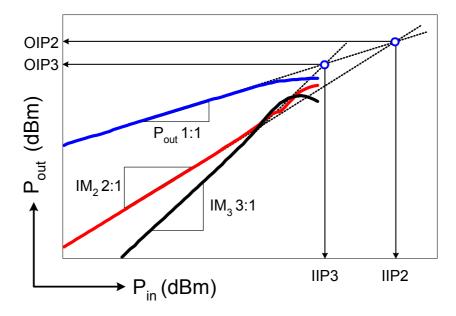

## 2.3.2 Intercept Point

The intercept point is the point where the slope of the fundamental linear component meets the slope of the intermodulation products on a logarithmic chart of output power versus input power. The intercept point can be input or output referred. Input intercept point represents the input power level for which the fundamental and the intermodulation products have equal amplitude at the output of a nonlinear circuit. In most practical circuits, intermodulation (IM) products will never be equal to the fundamental linear term because both amplitudes will compress before reaching this point. In those cases intercept point is measured by a linear extrapolation of the output characteristics for small input amplitudes. Since the third order intermodulation products, among the IM products, are of greatest concern in power amplifier design, the corresponding intercept point called the third order intercept point (IP3) is an important tool to analyze the effects of third order nonlinearities. In fact, intercept point serves as a better measure of linearity in comparison to intermodulation products as it can be specified independent of the input power level [18].

Figure 2.6. Graphical intercept point concept.

# 2.4 Power Amplifier Classes

RF power amplifiers are commonly designated as classes A, B, C, D, E, and F [19]. All but class A employ various nonlinear, switching, and wave-shaping

techniques. Classes of operation differ not only in the method of operation and efficiency, but also in their power-output capability.

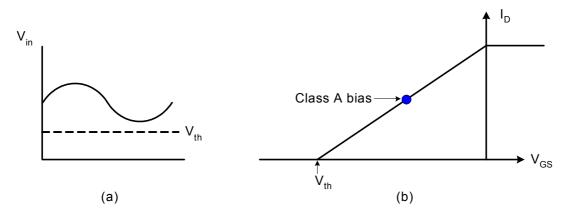

#### 2.4.1 Class A

Class A is the simplest power amplifier type in terms of design and construction. The Class A amplifier has a conduction angle of  $2\pi$  radians or  $360^{\circ}$ . Conduction angle refers to the time period for which a device is conducting. Thus a conduction angle of  $360^{\circ}$  tells us that in Class A operation the device conducts current for the entire input cycle. Class A amplifiers are considered to be the most linear since the transistor is biased in the center of the load line to allow for maximum voltage and current swings without cut-off or saturation (Figure 2.7). However the problem with Class A amplifiers is their poor efficiency. This is because the device is draining current at all times which translates to higher power loss. In fact it can be shown that the maximum efficiency achievable from a Class A power amplifier is only 50% [19]. However, this is a theoretical number and the actual efficiency is typically much less. In fact commercial Class A amplifiers have efficiencies as low as (20 - 30%). Hence Class A amplifiers are usually only used in places where linearity is a stringent requirement and where efficiency can be compromised as in the initial stages of a multi-stage power amplifier.

Figure 2.7. Class A PA: (a) input waveform, (b) bias point.

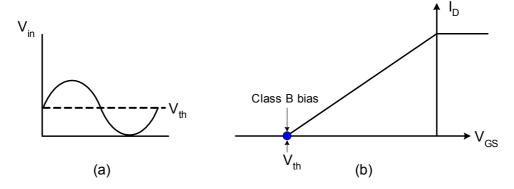

## 2.4.2 Class B

The transistor is biased at the threshold voltage point of the transistor for Class B operation (Figure 2.8). Hence there is a current flowing at the output of the device only when there is a signal at the input. Moreover the device would conduct current

only when the input signal level is greater than the threshold voltage. This occurs for the positive half cycle of the input signal and during the negative half cycle the device remains turned off. Hence the conduction angle for Class B operation is  $180^{\circ}$  or  $\pi$ radians. Due to this behaviour, there is a large saving in the power loss. It can be shown that the maximum theoretical efficiency achievable with Class B operation is about 78.5% [19]. Commercial Class B amplifiers typically have an efficiency of 50-60%. However, the increased efficiency comes at the cost of reduced linearity. The reduction in the output power occurs because the output current flows for only one half cycle of the input signal. The poor linearity is primarily attributed to an effect called the crossover distortion [19]. Whenever the transistor is turned on (at the start of positive half cycle) and turned off (at the start of negative half cycle) the transistor does not change abruptly from one state to the other. Instead the transition is gradual and nonlinear, and results in an offset voltage. This voltage alters the output waveform (crossover distortion) thereby reducing the linearity. Sometimes a class B amplifier is realized in "push-pull" configuration. In this configuration the two transistors are driven 180° out-of-phase so that each transistor is conducting for one half cycle of the input signal and turned off for the other half cycle.

Figure 2.8. Class B PA: (a) input waveform, (b) bias point.

#### 2.4.3 Class AB

The crossover distortion effect in Class B amplifiers can be minimized by biasing the gate in a way to produce a small quiescent drain current. This leads to the type of amplifiers called Class AB, where the transistor is biased above the threshold voltage but below the center of the load line (Figure 2.9). Class AB amplifier operation, as the name suggests, can be considered to be a compromise between Class A and Class B

operation. The conduction angle of a Class AB amplifier lies between 180° and 360°. By varying the conduction angle the amplifier can be made to behave more like a Class A or Class B amplifier. Hence the theoretical maximum efficiency of a Class AB amplifier is between 50% and 78.5%. Commercial Class AB amplifiers typically have much lower efficiencies in the order of 40-55%. A trade-off between linearity and efficiency can be achieved by simply changing the gate bias. Class AB amplifiers can also be realized in push-pull configurations even though single transistor configuration is preferred for high frequency linear operation.

Figure 2.9. Class AB PA: (a) input waveform, (b) bias point.

#### 2.4.4 Class C

A Class C power amplifier is a nonlinear power amplifier used in places where linearity is not a requirement and high efficiency is highly desired. Class C amplifiers are widely used in constant envelope modulation systems where linearity is not required. The transistor is biased below threshold for Class C operation and hence the device conduction angle varies from 0° to 180° (see figure 2.10). When a voltage signal is applied to the input, the transistor conducts only for the period of time when the input signal is greater than the threshold voltage. The transistor remains switched off at all other times. Since only a portion of the positive input voltage swing takes the device into the amplifying region the output current is a pulsed representation of the input. Due to this pulsed output current the input and output voltages are not linearly related. Thus the amplitude of the power amplifier output is highly distorted. The efficiency of a Class C amplifier depends on the conduction angle. The efficiency of a Class C power amplifier is 100%. However this is obtainable only for a conduction

angle of 0°, which means that no signal is applied and this condition is of no interest. Commercially Class C amplifiers typically show an efficiency of 60% or more.

Figure 2.10. Class C PA: (a) input waveform, (b) bias point.

#### 2.4.5 Class D