## Circuit design in complementary organic technologies

Citation for published version (APA):

Abdinia, S. (2014). Circuit design in complementary organic technologies. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR781486

DOI:

10.6100/IR781486

Document status and date:

Published: 01/01/2014

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 04. Oct. 2023

# CIRCUIT DESIGN IN COMPLEMENTARY ORGANIC TECHNOLOGIES

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus prof.dr.ir. C.J. van Duijn, voor een commissie aangewezen door het College voor Promoties, in het openbaar te verdedigen op dinsdag 25 november 2014 om 16:00 uur

door

Sahel Abdinia

geboren te Rasht, Iran

Dit proefschrift is goedgekeurd door de promotoren en de samenstelling van de promotiecommissie is als volgt:

voorzitter: prof.dr.ir. A.C.P.M. Backx

1<sup>e</sup> promotor: prof.dr.ir. A.H.M. van Roermund

copromotor: dr.ir. E. Cantatore

leden: prof.dr J. Schmitz (U Twente)

prof.dr.ir. J. Genoe (KU Leuven)

Prof.Dr.-Ing. K. Bock (TU Berlin)

dr. E.A.J.M. Bente

adviseur: dr. R. Gwoziecki (CEA-Liten)

Circuit Design in Complementary Organic Technologies Sahel Abdinia Eindhoven University of Technology

Cover photo by: Bart van Overbeeke

A catalogue record is available from the Eindhoven University of Technology Library.

ISBN: 978-90-386-3725-9

This work was funded in the frame of the European FP7 project COSMIC (grant agreement  $n^{\circ}$  247681).

#### **Table of Contents**

| LIST O            | DF FIGURES                                          | VII      |

|-------------------|-----------------------------------------------------|----------|

| LIST O            | DF TABLES                                           | XI       |

| LIST O            | OF ABBREVIATIONS                                    | XII      |

| LIST O            | OF SYMBOLS                                          | xv       |

| <u>1   </u>       | NTRODUCTION_                                        | <u>1</u> |

|                   |                                                     |          |

| 1.1               | ORGANIC CIRCUITS: STATE OF THE ART                  | 3        |

| 1.1.1             | IMPLEMENTED APPLICATIONS                            | 3        |

| 1.1.2             | CHALLENGES AND PROGRESS                             | 5        |

| 1.2               | ROLE OF COMPLEMENTARY TECHNOLOGIES                  | 8        |

| 1.3               | PROBLEM STATEMENT                                   | 10       |

| 1.4               | AIM OF THE THESIS                                   | 10       |

| 1.5               | SCOPE OF THE THESIS                                 | 11       |

| 1.6               | ORIGINAL CONTRIBUTIONS                              | 12       |

| 1.7               | OUTLINE OF THE THESIS                               | 13       |

|                   | TI COMPLEMENTARY OTFT TECHNOLOGY, MODELLING, AND BI | 17       |

| 2.1               | Introduction                                        | 18       |

| 2.2               | SHEET-TO-SHEET (S2S) FABRICATION PROCESS            | 18       |

| 2.2.1             |                                                     | 19       |

| 2.2.2             |                                                     | 21       |

| 2.2.3             | TYPICAL LAYOUT RULES                                | 22       |

| 2.3               | WAFER-TO-WAFER (W2W) FABRICATION PROCESS            | 24       |

| 2.3.1             |                                                     | 24       |

| 2.3.2             | TYPICAL LAYOUT RULES                                | 27       |

| 2.4               | HIGHLIGHTS OF THE S2S AND W2W TECHNOLOGIES          | 28       |

| <u>3</u> <u>C</u> | OTFT MODELLING AND CHARACTERISTICS                  | 31       |

| 3.1               | Introduction                                        | 32       |

| 3.2               | OTFT OPERATION AND PERFORMANCE                     | 33  |

|-------------------|----------------------------------------------------|-----|

| 3.3               | MODELLING OF S2S OTFTS                             | 36  |

| 3.3.1             | OTFT MODEL FOR GEN.1                               | 37  |

| 3.3.2             | OTFT MODEL FOR GEN.2                               | 44  |

| 3.4               | MODELLING OF W2W OTFTS                             | 46  |

| 3.5               | HIGHLIGHTS OF THE S2S AND W2W OTFT CHARACTERISTICS | 50  |

| <u>4</u> <u>D</u> | OIGITAL CIRCUIT DESIGN                             | 53  |

| 4.1               | Introduction                                       | 54  |

| 4.2               | DIGITAL DESIGN IN S2S TECHNOLOGY                   | 55  |

| 4.2.1             | FULLY-STATIC BLOCKS                                | 57  |

| 4.2.2             | Transmission-gate (TG) blocks                      | 63  |

| 4.2.3             | DYNAMIC BLOCKS                                     | 66  |

| 4.2.4             | LOGIC STYLE SELECTION                              | 68  |

| 4.3               | DIGITAL DESIGN IN W2W TECHNOLOGY                   | 69  |

| 4.3.1             | FULLY-STATIC BLOCKS                                | 70  |

| 4.3.2             | Transmission-gate blocks                           | 73  |

| 4.3.3             | LOGIC STYLE SELECTION                              | 73  |

| 4.4               | DIGITAL DESIGN HIGHLIGHTS                          | 75  |

| <u>5 A</u>        | NALOGUE AND MIXED-SIGNAL CIRCUIT DESIGN            | 77  |

| 5.1               | Introduction                                       | 78  |

| 5.2               | Analogue design in S2S technology                  | 79  |

| 5.2.1             | OTAs                                               | 80  |

| 5.2.2             | Comparators                                        | 82  |

| 5.2.3             | DAC                                                | 90  |

| 5.2.4             | RECTIFIERS                                         | 92  |

| 5.2.5             | AM DEMODULATOR                                     | 100 |

| 5.3               | W2W OTA                                            | 102 |

| 5.4               | ANALOGUE DESIGN HIGHLIGHTS                         | 103 |

| PART              | II IMPLEMENTED SYSTEMS-ON-FOIL                     | 105 |

| 6 D               | DISPLAY DRIVER                                     | 107 |

| 6.1               | INTRODUCTION            | 108 |

|-------------------|-------------------------|-----|

| 6.2               | LINE DRIVER CIRCUIT     | 108 |

| 6.3               | SYSTEM TEST             | 110 |

| 6.4               | HIGHLIGHTS              | 111 |

| <u>7</u> 1        | TEMPERATURE MONITOR     | 113 |

| 7.1               | Introduction            | 114 |

| 7.2               | ADC                     | 115 |

| 7.3               | SENSOR                  | 120 |

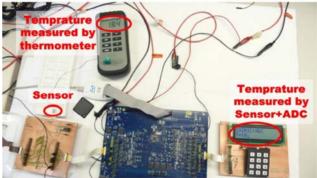

| 7.4               | SYSTEM TEST             | 123 |

| 7.5               | Ніднііднтѕ              | 124 |

| <u>8</u> <u>I</u> | RFID TAG                | 127 |

| 8.1               | Introduction            | 128 |

| 8.2               | RFID CIRCUITS           | 129 |

| 8.2.1             | 1 FRONT-END             | 129 |

| 8.2.2             | 2 CODE-RECOGNITION UNIT | 132 |

| 8.3               | TEST SYSTEM SCHEMES     | 136 |

| 8.4               | Нідниіднтѕ              | 137 |

| <u>9</u>          | CONCLUSIONS             | 139 |

| Refei             | RENCES                  | 145 |

| LIST C            | OF PUBLICATIONS         | 152 |

| Sumi              | SUMMARY                 |     |

| Ackn              | Acknowledgement         |     |

| BIOGRAPHY         |                         | 159 |

# **List of Figures**

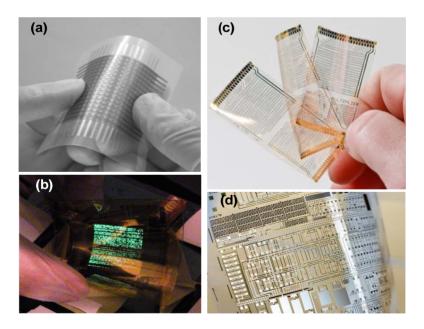

| Figure 1. Some applications implemented using organic technologies: (a) artificial skin based on a matri of organic sensors [34], (b) all-organic integrated flexible display [22], (c) microprocessor on foil [48], (d) ADC and other ICs on foil. |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

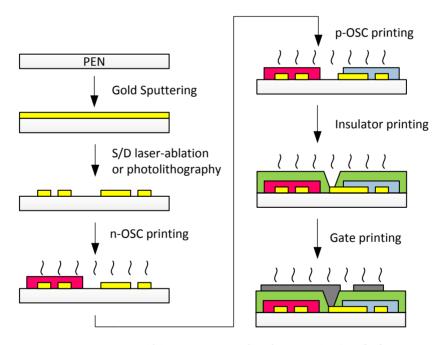

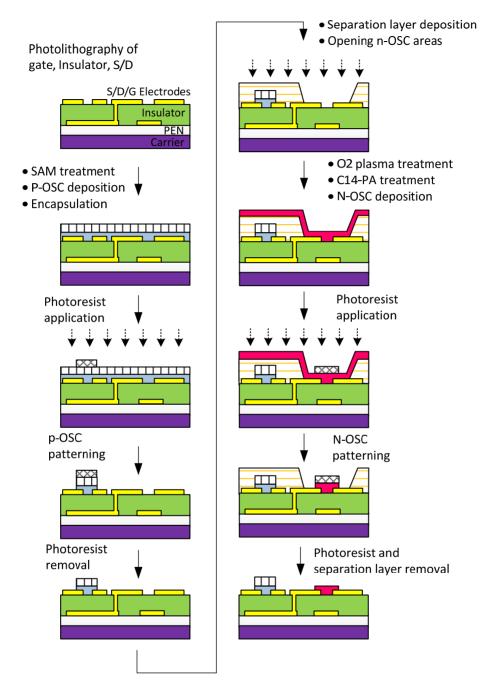

| Figure 2. General fabrication process flow for S2S technology [68]20                                                                                                                                                                                |

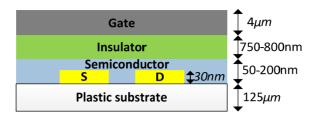

| Figure 3. Cross section of the top-gate bottom-contact OTFT in S2S technology2                                                                                                                                                                      |

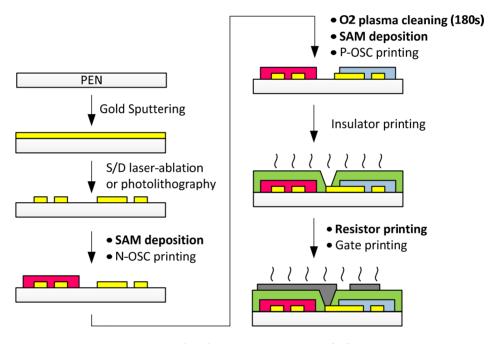

| Figure 4. Fabrication process flow for Gen.2 S2S technology [66], the operations which are added to each step compared to the general process flow are bolded2.                                                                                     |

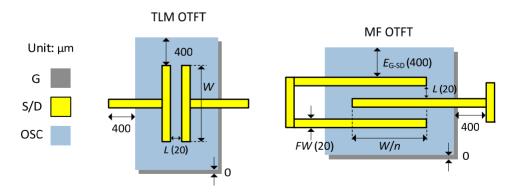

| Figure 5. Layout of TLM and MF OTFTs in S2S2                                                                                                                                                                                                        |

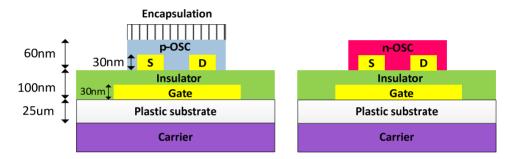

| Figure 6. Process flow for W2W technology [67]2!                                                                                                                                                                                                    |

| Figure 7. Cross-section of bottom-gate bottom-contact OTFTs in W2W2                                                                                                                                                                                 |

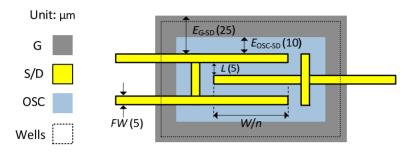

| Figure 8. Layout of OTFTs in W2W technology28                                                                                                                                                                                                       |

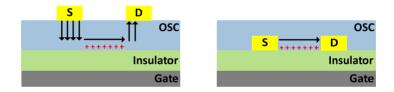

| Figure 9: Channel formed in bottom-gate staggered (left) and coplanar (right) TFTs3                                                                                                                                                                 |

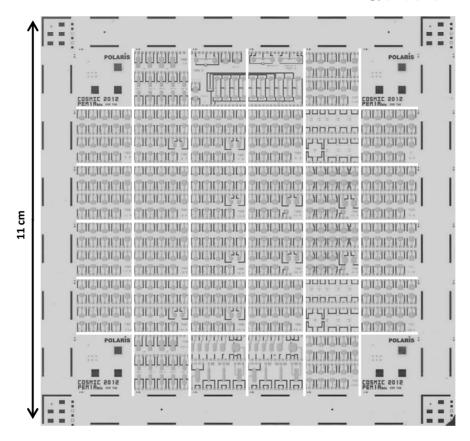

| Figure 10. Picture of S2S device characterization foil (PEM1a). The white grid shows the division of dies 3                                                                                                                                         |

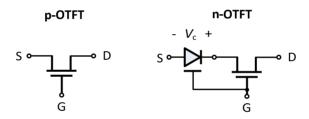

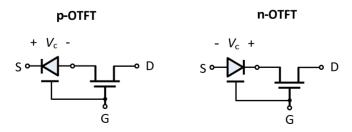

| Figure 11. The schematic model for p-type (left) and n-type (right) OTFTs in Gen.140                                                                                                                                                                |

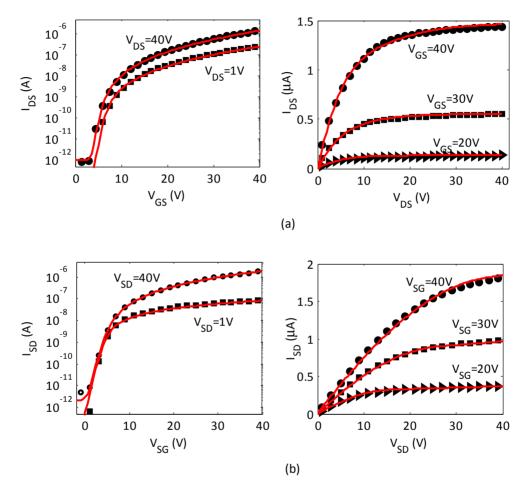

| Figure 12. Measured (symbols) and modelled (line) transfer and output characteristics of (a) n-type and (b) p-type transistors with $W/L=1000\mu m/20\mu m$                                                                                         |

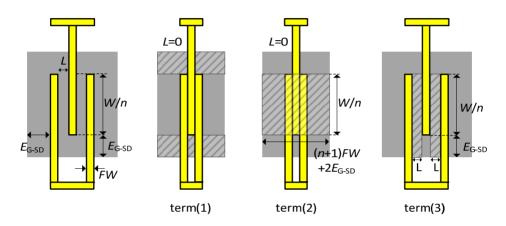

| Figure 13. The layout of a S2S OTFT (left) and the area (hashed) attributed to each term of C <sub>tot</sub> in Equation (9)                                                                                                                        |

| Figure 14. The schematic model for p-type (left) and n-type (right) OTFTs in Gen.1                                                                                                                                                                  |

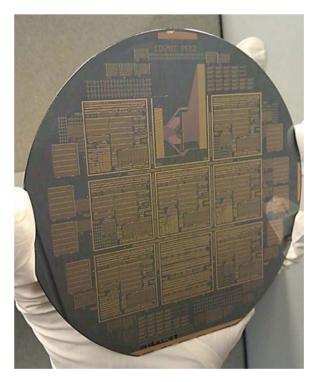

| Figure 15. Picture of W2W characterization foil (PEM2)4                                                                                                                                                                                             |

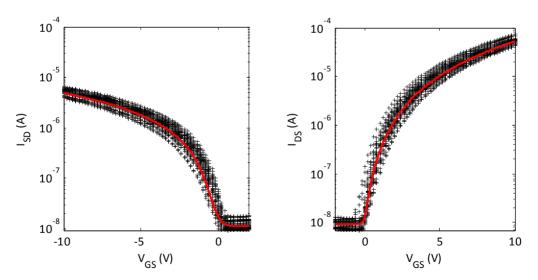

| Figure 16. Measured transfer characteristics of twenty-four p-type (left) and n-type (right) transistors wit $W/L=140\mu m/5\mu m$ (symbols) and the equivalent model (solid line) at $V_{DS}=10$ V (absolute value)4                               |

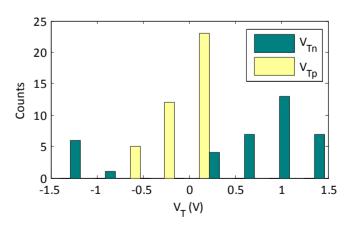

| Figure 17. Number of occurrences for threshold voltage of forty p-type ( $V_{Tp}$ ) and n-type ( $V_{Tn}$ ) transistor on a W2W die                                                                                                                 |

| Figure 18. Number of occurrences for mobility of forty p-type ( $\mu_p$ ) and n-type ( $\mu_n$ ) transistors on a die. 50                                                                                                                           |

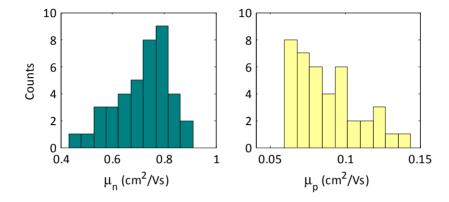

| Figure 19. Picture of the foil containing several building blocks (PEM1b). Digital blocks are individuall shown: 1. JK-FF, 2. Dynamic NAND, 3.Inverters, 4. Ring oscillator, 5. TSPC (dynamic) FF, 6. MS (fully-static FF, NAND/NOR gates.          |

| Figure 20. Measurement of S2S foils using a probe station56                                                                                                                                                                                         |

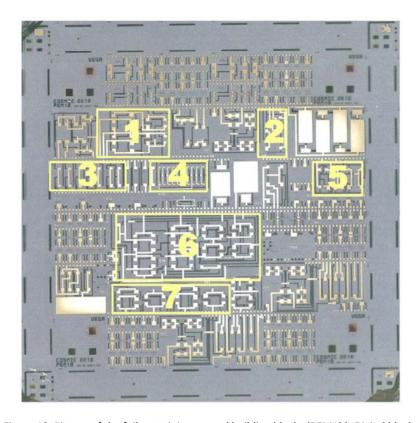

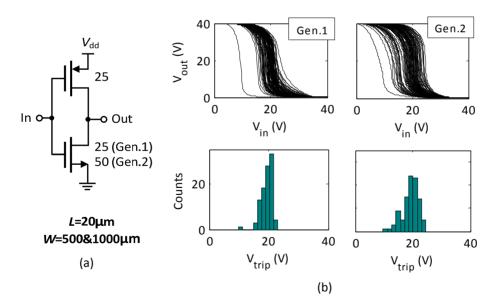

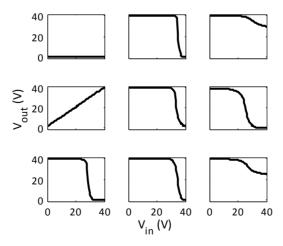

| Figure 21. (a) Schematic of the complementary inverter (b) 100 iterations of an MC simulation for a inverter in Gen.1 (left panels) and Gen.2 (right panels). The (W/L) ratio is given in the schematic58                                           |

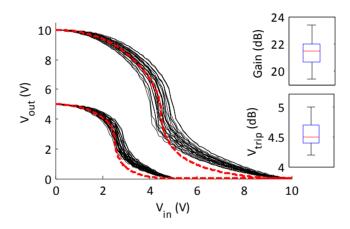

| Figure 22. Measurement of nine inverters on one of the first samples manufactured in Gen.2 proces (April 2011)                                                                                                                                      |

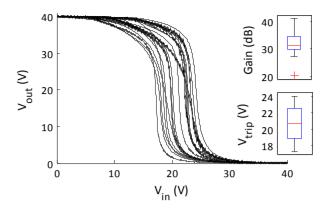

| Figure 23. Measurements of inverters representing 10 different foils manufactured in Gen.2 (the inset show the boxplot of gains and trip points)                                                                                                    |

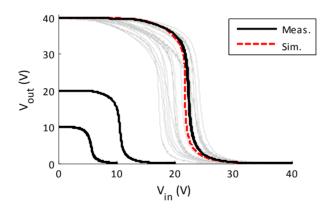

| Figure 24. Measurements (black solid line) an simulation (red dashed line) of one of the inverters among many manufactured in Gen.2 (light gray lines). The measurements are shown $V_{dd}$ equal to 10, 20, and 40 V                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

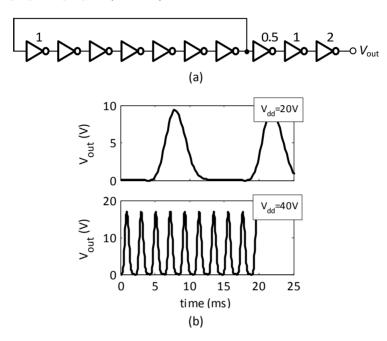

| Figure 25. (a) Schematic of a 7-stage ring oscillator and (b) its measurements at 20 V and 40 V 61                                                                                                                                                                                                                   |

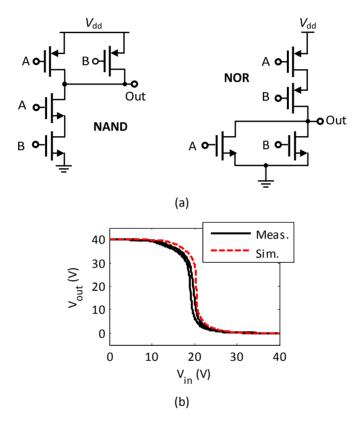

| Figure 26. (a) Schematic of NAND and NOR gates, (b) Measurements of a NAND gate for one input set at $V_{\rm dd}$ (40 V) and the other swept from 0 to $V_{\rm dd}$ and vice versa                                                                                                                                   |

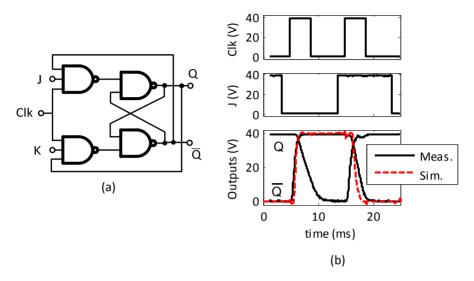

| Figure 27. (a) Schematic of JK-FF, (b) measurements and simulation of the JK-FF at $f_{\rm clk}$ of 100 Hz 63                                                                                                                                                                                                        |

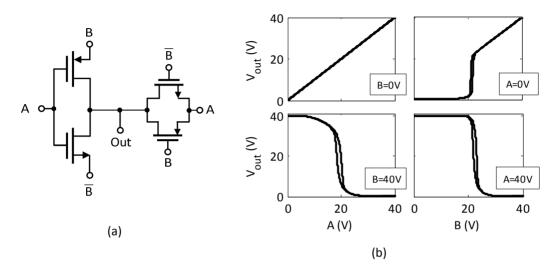

| Figure 28. (a) The schematic of a TG-based XOR gate and (b) measurements at different input states 64                                                                                                                                                                                                                |

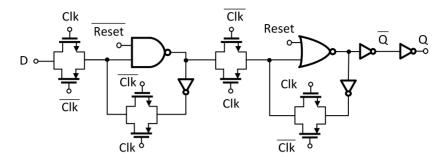

| Figure 29. (a) Schematic of a master/slave TG D-FF with asynchronous reset 65                                                                                                                                                                                                                                        |

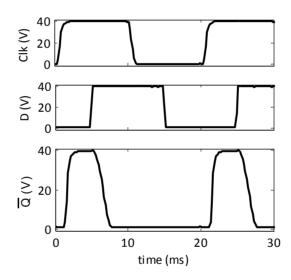

| Figure 30. Measurements of a D-latch at $f_{\rm clk}$ of 50 Hz. The latch is transparent when the Clk is high (Q is shown).                                                                                                                                                                                          |

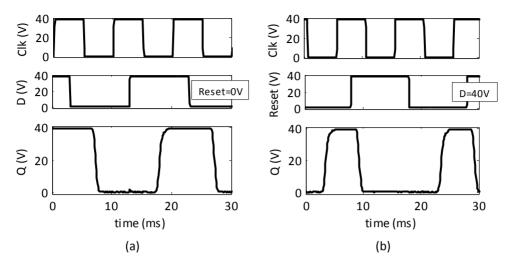

| Figure 31. (a) D-FF measurement while reset is inactive. Q follows D at each falling edge of Clk, (b) D-FF measurement while D is 40 V, Q remains low when Reset is high. In both measurements $f_{\rm clk}$ is 100 Hz 66                                                                                            |

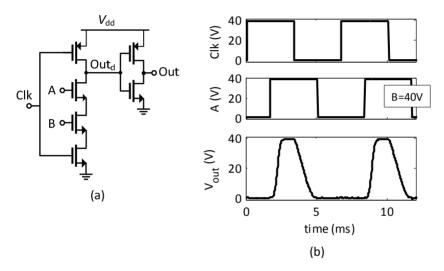

| Figure 32. (a) Schematic of a dynamic NAND gate with an static inverter at the output, (b) experimental characterization of the gate for two states (AB=01 and AB=11) at $f_{clk}$ of 150 Hz                                                                                                                         |

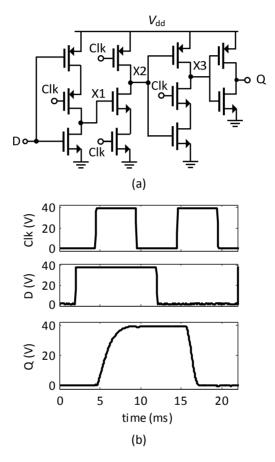

| Figure 33. (a) Schematic of the dynamic flip-flop, (b) experimental characterization of the flip-flop at $f_{\rm clk}$ of 100 Hz68                                                                                                                                                                                   |

| Figure 34. Measurements of eleven complementary inverters (solid lines) and nominal simulation of inverters (dashed lines). The insets show the boxplot of gains and trip points                                                                                                                                     |

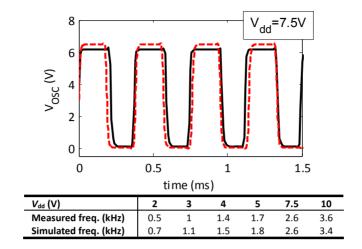

| Figure 35. Measured (solid line) and simulated (dashed line) output of a 19-stage ring-oscillator at $V_{\rm dd}$ of 7.5 V. The table shows the measured and simulated frequency of the ring oscillator at different supply voltages                                                                                 |

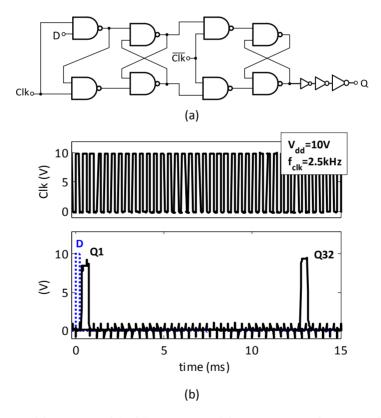

| Figure 36. (a) Schematic of the fully-static MSFF, (b) measurements of a 32-stage fully-static shift register at $V_{\rm dd}$ =10 V and $f_{\rm clk}$ =2.5 kHz. Q1 and Q32 are shown                                                                                                                                 |

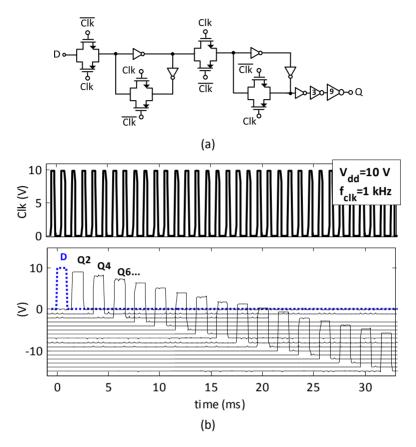

| Figure 37. (a) Schematic of TG-based FF, (b) measurements of a 32-stage TG-based shift register at $V_{\rm dd}$ =10 V and $f_{\rm clk}$ =1 kHz. Q2, Q4, Q6, to Q32 are shown with an added vertical offset for clarity                                                                                               |

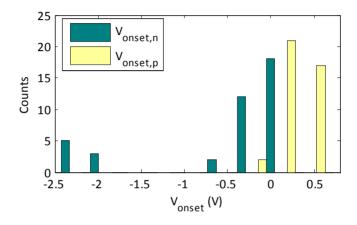

| Figure 38. Number of occurrences for onset voltage (V <sub>onset</sub> ) of forty p-type and n-type transistors on a W2W die75                                                                                                                                                                                       |

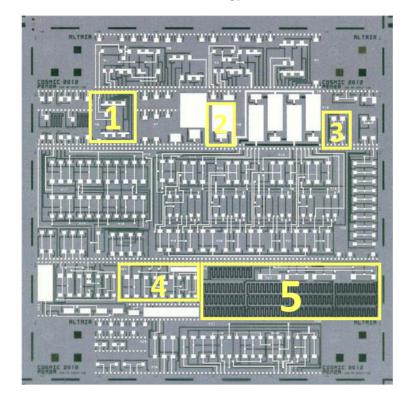

| Figure 39. Picture of the foil containing several building blocks (PEM2a). Some analogue blocks are individually shown: 1. Two-stage OTA/Comparator (Figure 43), 2. Envelope detector, 3. Single-stage OTA/4. Two-stage inverter-based comparator (Figure 45), and 5.R-2R DAC. Most of the other blocks are digital. |

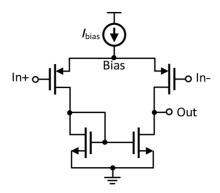

| Figure 40. Schematic of the OTA81                                                                                                                                                                                                                                                                                    |

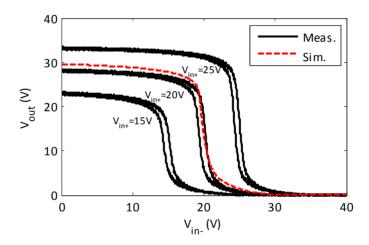

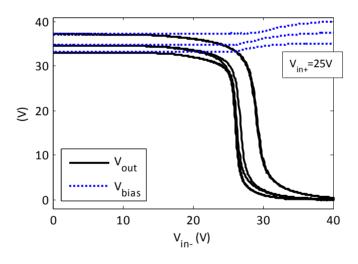

| Figure 41. Gen.1 OTA simulation and measurements: output voltage vs. input voltage ( $V_{in}$ .) measured at different $V_{in+}$ values are shown. The simulation shows the case when $V_{in+}$ is equal to 20 V. $I_{bias}$ is 0.3 $\mu$ A.81                                                                       |

| Figure 42. Measurements of two samples of Gen.2 OTAs on two different foils: the voltages at the bias and output nodes are measured when In+ is set at 25 V and In- is swept. I $_{\text{bias}}$ is 2 $\mu$ A                                                                                                        |

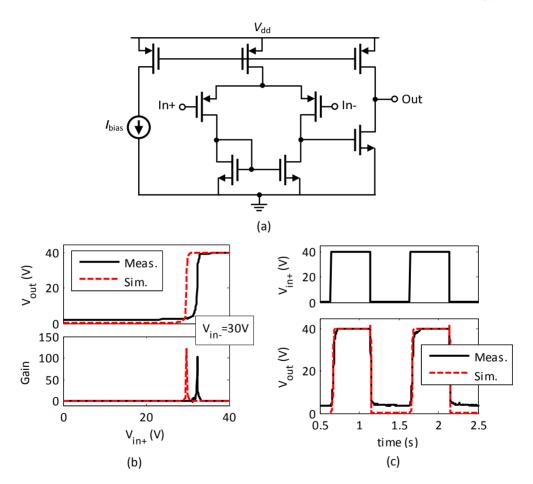

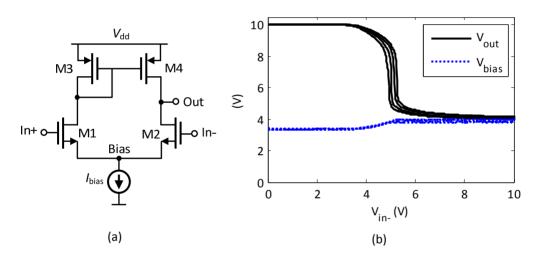

| Figure 43. (a) Schematic of the comparator manufactured in Gen.1, (b) quasi-static measurement at $V_{\text{in}}$ = 30 V and $I_{\text{bias}}$ = 0.15 $\mu$ A, (c) Dynamic measurements at $f_{\text{clk}}$ of 1 Hz                                                                                                  |

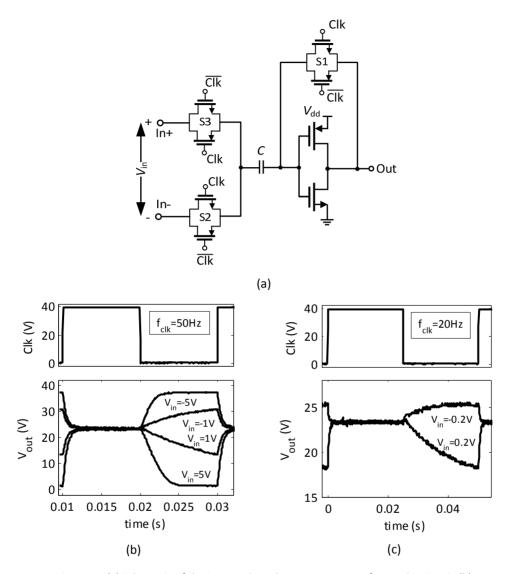

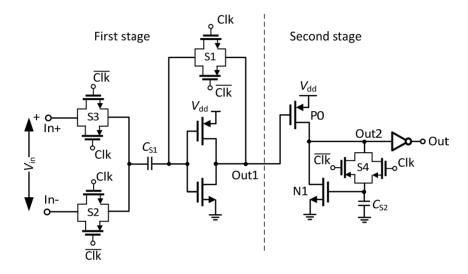

| Figure 44. (a) Schematic of the inverter-based comparator manufactured in Gen.2, (b) comparator measurement results @ $f_{\rm clk}$ =50 Hz and $V_{\rm in}$ =±5, ±1 V, (c) comparator measurement results @ $f_{\rm clk}$ =20 Hz and $V_{\rm in}$ =±0.2 V                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

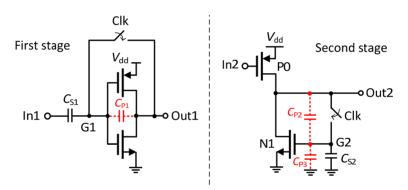

| Figure 45. Schematic of the two-stage dynamic comparator manufactured in Gen.286                                                                                                                                                                                                                        |

| Figure 46. Simplified schematic of the two stages of the comparator in Figure 45 including parasitic capacitances                                                                                                                                                                                       |

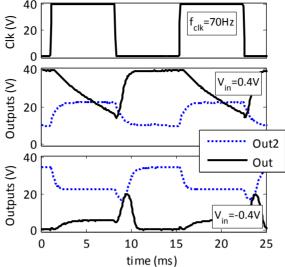

| Figure 47. Measurement of the Gen.2 two-stage comparator (Figure 45) at $f_{\rm clk}$ =70 Hz and $V_{\rm in}$ =±0.4 V 89                                                                                                                                                                                |

| Figure 48. Measurement of the Gen.2 two-stage comparator (Figure 45) at $f_{\rm clk}$ =20 Hz and $V_{\rm in}$ =±50 mV. Only $V_{\rm out}$ (the voltage at node Output) is shown                                                                                                                         |

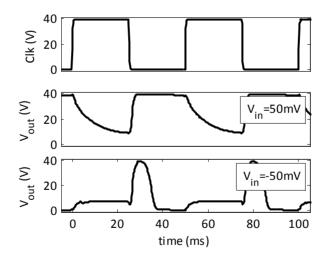

| Figure 49. (a) Schematic of 4-bit R-2R DAC, (b) The measured DNL and INL of one of the ADC samples (figure), and the absolute value of the measured maximum DNL and INL of three samples (table) 91                                                                                                     |

| Figure 50. The measurement setup of rectifier/envelope detectors93                                                                                                                                                                                                                                      |

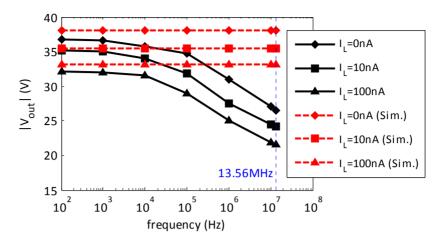

| Figure 51. Gen.1 Rectifier output voltage (absolute value) as a function of input frequency at different load currents. Solid lines show measurement results and dashed lines show simulations. The input $V_{\rm M}$ and $V_{\rm pp}$ (Figure 50) are -25 and 30 V, respectively94                     |

| Figure 52. Gen.1 Rectifier output voltage as a function of input signal amplitudes for different input frequencies ( $I_L = 0 \text{ A}$ )95                                                                                                                                                            |

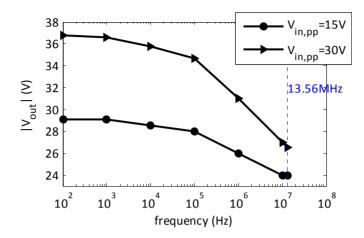

| Figure 53. Gen.2 Rectifier output voltage (absolute value) as a function of input frequency at different load currents for (a) a p-OTFT and (b) an n-OTFT. $V_{\rm M}$ and $V_{\rm pp}$ (Figure 50) are -25 and 30 V, respectively 96                                                                   |

| Figure 54. Gen.2 Rectifier output voltage as a function of input signal amplitudes for different input frequencies in (a) a p-OTFT and (b) an n-OTFT ( $I_L = 0 \text{ A}$ )97                                                                                                                          |

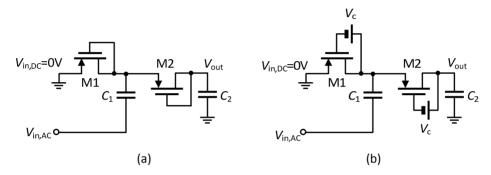

| Figure 55. (a) A 2-stage charge pump (voltage doubler), and (b) a simplified schematic for the charge pump incorporating threshold-cancellation techniques98                                                                                                                                            |

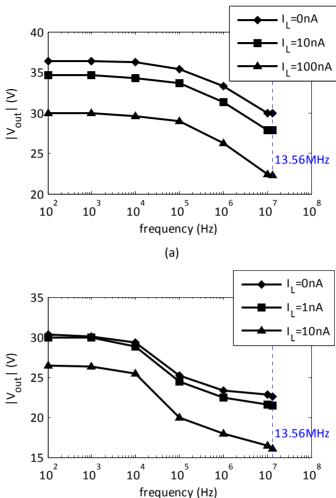

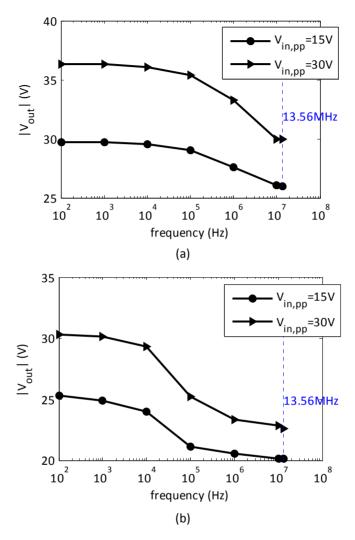

| Figure 56. (a) Schematic of a 4-stage charge pump incorporating threshold voltage cancellation (b) the measured rectifier output $(V_{out})$ under different load and input conditions99                                                                                                                |

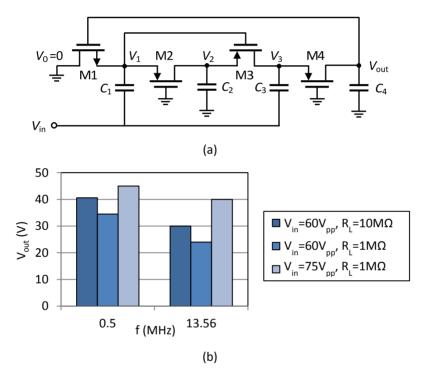

| Figure 57. (a) Structure of a demodulator for recovering an AM-modulated data, (b) AM-demodulator simulation. The extracted data is shown for a single-stage OTA (Figure 40(a)) or a two-stage OTA (Figure 43(a)) are employed as a comparator101                                                       |

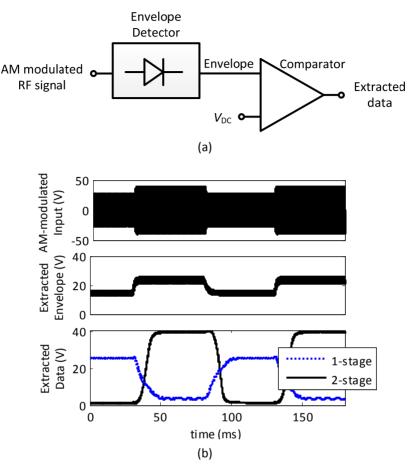

| Figure 58. (a) Schematic of the OTA implemented in W2W technology, (b) Measurements of two samples of OTA: the voltages at the bias and output nodes are measured when In+ is set to 5 V and In- is swept. $I_{\text{bias}}$ is 1 $\mu$ A102                                                            |

| Figure 59. (a) The schematic of a 32-stage line driver, (b) measurements of the driver: Q1, Q16 and Q32 are shown109                                                                                                                                                                                    |

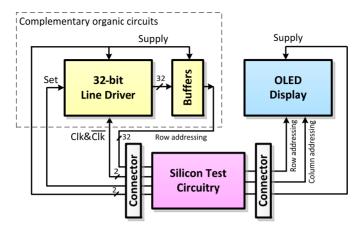

| Figure 60. Block diagram of the display driver testing system111                                                                                                                                                                                                                                        |

| Figure 61. Photographs of a die containing two 32-stage line drivers (and other building characterization circuits) and the image generated on the display using the driver. One line driver is connected to the display through a mechanical YOKOWO connector (which can be seen in the top figure)112 |

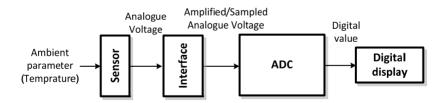

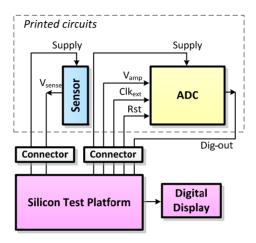

| Figure 62. Simplified block diagram of a temperature monitor114                                                                                                                                                                                                                                         |

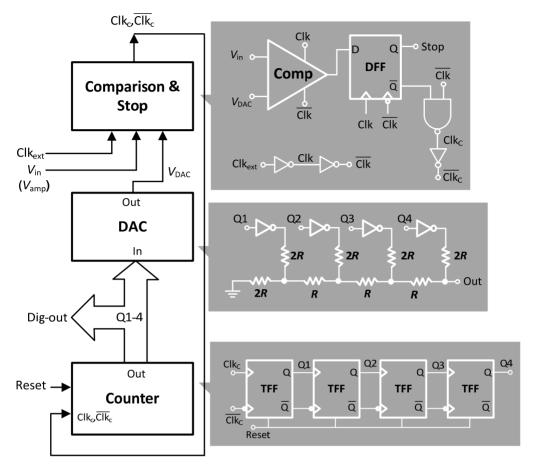

| Figure 63. Structure of the 4-bit counting ADC (left) and the schematic of its building blocks (right)116                                                                                                                                                                                               |

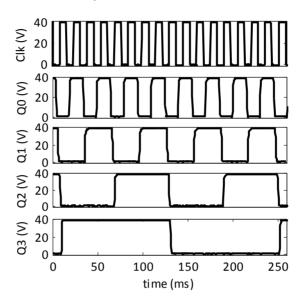

| Figure 64. Counter outputs (Q1-Q4) measured at $f_{clk}$ of 67 Hz117                                                                                                                                                                                                                                    |

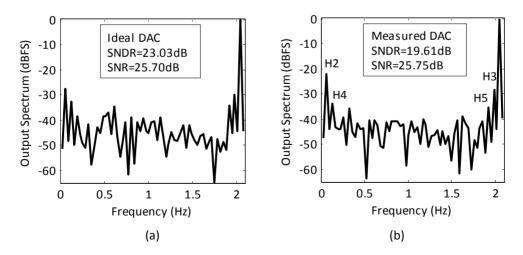

| Figure 65. Measured output spectrum of the ADC (a) based on an ideal DAC (generated using generator) and (b) based on a measured DAC (H2-H5 show the first harmonics) |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

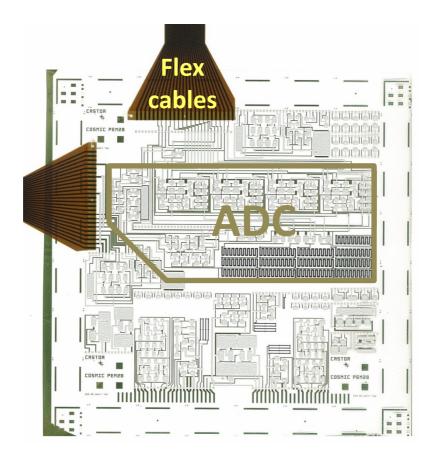

| Figure 66. The foil containing the fully-integrated 4-bit counting ADC (PEM2b-top1)                                                                                   | 118 |

| Figure 67. The schematic of the temperature sensor and the foil containing implemented sen                                                                            |     |

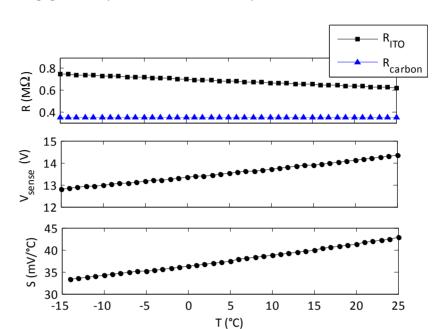

| Figure 68. Calculated resistance values (R), output voltage (V <sub>sense</sub> ) and sensitivity (S) of the sensor                                                   |     |

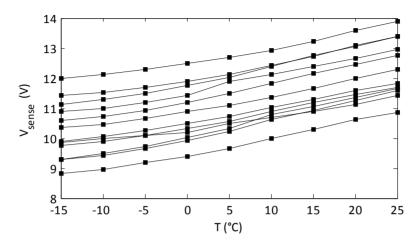

| Figure 69. Measured output voltage versus temperature of twelve samples of the sensor                                                                                 | 123 |

| Figure 70. Block diagram of the temperature-monitor testing system                                                                                                    | 124 |

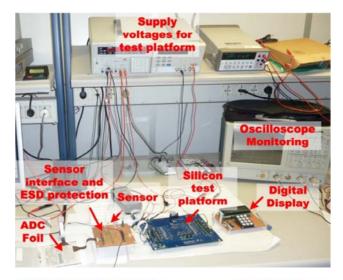

| Figure 71. Photo of the temperature-monitor measurement setup                                                                                                         | 125 |

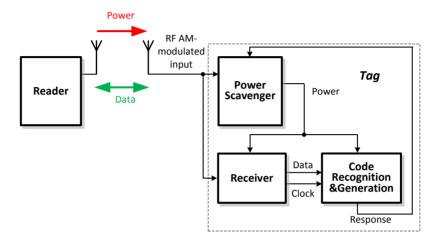

| Figure 72. Simplified block diagram of a reader-talks-first RFID tag based on the silent tag con protocol                                                             |     |

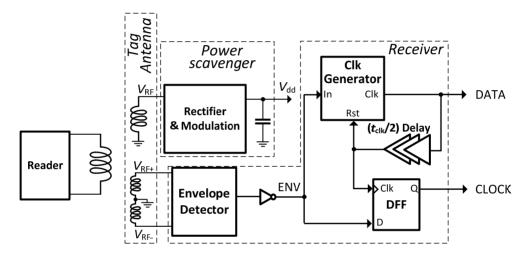

| Figure 73. RFID tag front-end                                                                                                                                         | 130 |

| Figure 74. Input code PWM scheme                                                                                                                                      | 130 |

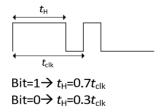

| Figure 75. Rectifier used in the final version of RFID tag                                                                                                            | 131 |

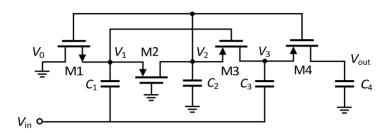

| Figure 76. (a) Block diagram of the code recognition unit (CRU) including reset module (RM) verification module (IVM), (b) more detailed schematic of the CRU blocks  |     |

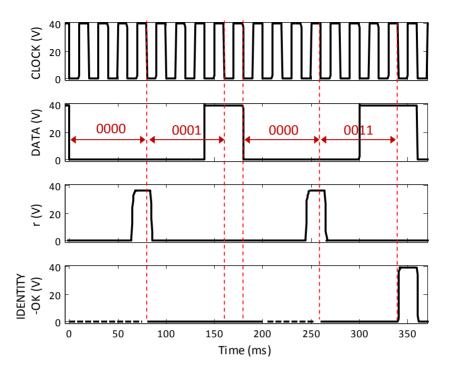

| Figure 77. Measurements of the code recognition unit for a tag with identity of 0011 [99]                                                                             | 135 |

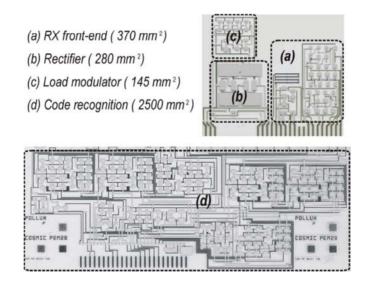

| Figure 78. Photo of the first implementation of RFID blocks (in PEM2b-Top1 and -Top2)                                                                                 | 135 |

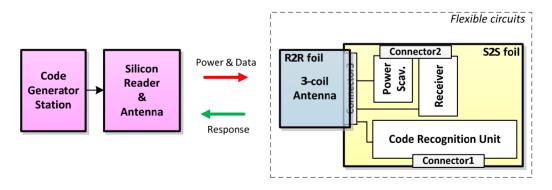

| Figure 79. Block diagram of the RFID testing system                                                                                                                   | 136 |

#### **List of Tables**

| Table 1. List of applications implemented based on organic circuit                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2. Highlights of S2S and W2W technologies28                                                                                                                   |

| Table 3. Typical electrical characteristics of OTFTs in Gen.1 S2S technology [10]42                                                                                 |

| Table 4. The nominal value and standard deviation ( $\sigma$ ) of Gen.1 OTFT parameters44                                                                           |

| Table 5. Typical electrical characteristics of OTFTs in Gen.2 S2S technology [66]46                                                                                 |

| Table 6. The mean value (M) and standard deviation ( $\sigma$ ) of Gen.2 OTFT parameters46                                                                          |

| Table 7. Typical electrical characteristics of OTFTs in W2W technology [96]49                                                                                       |

| Table 8. The mean value (M) and standard deviation ( $\sigma$ ) of $V_{Tp}$ and $V_{Tn}$ on the whole die as well as in each block of sixteen transistors (B1-B5)50 |

| Table 9. The mean value (M) and standard deviation ( $\sigma$ ) of $\mu_p$ and $\mu_n$ over the whole die as well as in each block of sixteen transistors (B1-B5)50 |

| Table 10. Comparison of our line driver with other organic line drivers previously reported in literature110                                                        |

| Table 11. Comparison of our printed DAC with state-of-the-art organic DACs119                                                                                       |

| Table 12. Comparison of our printed ADC with state-of-the-art organic ADCs119                                                                                       |

### List of abbreviations

| Abbreviation | Description                                                   |

|--------------|---------------------------------------------------------------|

| AC           | Alternating Current                                           |

| ADC          | Analogue to Digital Convertor                                 |

| $Al_2O_3$    | Aluminium Oxide                                               |

| AM           | Amplitude Modulation                                          |

| AMOLED       | Active-Matrix Light-Emitting Diode                            |

| AND          | AND Logic Gate                                                |

| ASK          | Amplitude-Shift Keying                                        |

| BCD          | Binary Coded Decimal                                          |

| BW           | Band Width                                                    |

| C14-PA       | a N-tetradecylphosphonic Acid                                 |

| C-2C         | Capacitor-double-Capacitor                                    |

| CAD          | Computer Aided Design                                         |

| CDR          | Clock and Data Recovery                                       |

| CMOS         | Complementary Metal Oxide Semiconductor                       |

| COSMIC       | Complementary Organic Semiconductor Metal Integrated Circuits |

| CRU          | Code Recognition Unit                                         |

| CYTOP        | a Fluoropolymer Dielectric                                    |

| DAC          | Digital to Analogue Converter                                 |

| DC           | Direct Current                                                |

| D-FF         | Data Flip Flop                                                |

| D-latch      | Data latch                                                    |

| DNL          | Differential Nonlinearity                                     |

| DNLmax       | Maximum DNL                                                   |

| ED           | Envelope Detector                                             |

| ELR          | Extrapolation of the Linear Region                            |

| ENOB         | Effective Number Of Bits                                      |

| ESD          | Electro-Static Discharge                                      |

| FF           | Flip Flop                                                     |

| FOC          | Foil On Carrier                                               |

| FPD          | Flat Panel Display                                            |

| FW           | Finger Width                                                  |

| Gen.1 and 2  | Generation one and two of S2S technology                      |

| GND          | Ground                                                        |

| HF           | High Frequency                                                |

| IC           | Integrated Circuit                                            |

|              |                                                               |

Abbreviation Description INL **INtegral Nonlinearity INLmax** Maximum INL ITO Indium Tin Oxide IVM **Identity Verification Module** LSB Least Siginificant Bit LUMO Lowest Unoccupied Molecular Orbital MC Monte Carlo MF Multi-Finger MIM Metal-Insulator-Metal Metal-Oxide-Semiconductor Field-Effect Transistor **MOSFET** MS Master-Slave **MSFF** Master-Slave Flip-Flop MTR Multiple Trapping and Release N3004 N-type Active Material NAND Not-AND logic gate NOR Not-OR logic gate n-OSC n-type OSC n-OTFT n-type OTFT n-TFT n-type TFT 0, Oxygen OLED Organic Light Emitting Diode OR logic gate OR OSC Organic Semiconductor OTA **Operational Transconductance Amplifiers OTFT** Organic Thin-Film Transistor PCE Power Conversion Efficiency PDN Pull-Down Network Name of the designed mask-sets (e.g. PEM1a, PEM1b, PEM2a, etc) PEM PEN Polyethylene naphthalate **PFBT** pentafluorobenzenethiol Ph-PXX 3,9-diphenyl-peri-xanthenoxanthene p-OSC p-type OSC p-OTFT p-type OTFT

PUN Pull-Up Network

PWM Pulse-Width Modulation

PαMS poly(α-methylstyrene)

p-type TFT

polytriarylamine

PTAA

p-TFT

| Abbreviation | Description                           |

|--------------|---------------------------------------|

| QQVGA        | Quarter-Quarter Video Graphics Array  |

| R2R          | Roll-to-Roll                          |

| R-2R         | Resistance-double-Resistance          |

| RF           | Radio Frequency                       |

| RFID         | Radio Frequency Identificagtion       |

| RM           | Reset Module                          |

| S/D          | Source/Drain terminals                |

| S2S          | Sheet-to-Sheet                        |

| SAM          | Self-Assembled Monolayer              |

| SAR          | Successive-Approximation-Register     |

| SC           | Switched-Capacitor                    |

| SNDR         | Signal-to-Noise-and-Distortion-Ratio  |

| SNR          | Signal-to-Noise-Ratio                 |

| SR-FF        | Set-Reset Flip Flop                   |

| TCR          | Temperature Coefficient of Resistance |

| T-FF         | Toggle Flip Flop                      |

| TFT          | Thin-Film Transistor                  |

| TG           | Transmission Gate                     |

| Ti-Au        | Titanium-Gold                         |

| TLM          | Transmission Line Model               |

| TSPC-FF      | True Single Phase Clock Flip Flop     |

| VRH          | Variable Range Hopping                |

| W2W          | Wafer-to-Wafer                        |

| XOR          | Exclusive-OR logic gate               |

|              |                                       |

# List of symbols

| Symbol             | Description                                               |

|--------------------|-----------------------------------------------------------|

| μ                  | Mobility                                                  |

| $\mu_{n}$          | n-type mobility                                           |

| $\mu_{p}$          | p-type mobility                                           |

| $C_{GD}$           | Gate-drain capacitance                                    |

| $C_{ins}$          | Insulator capacitance                                     |

| $C_{L}$            | Load capacitance                                          |

| $C_{P}$            | Parasitic capacitance                                     |

| $C_{S}$            | Sampling capacitance                                      |

| $C_{tot	ext{-}0}$  | OTFT parasitic capacitance for $L$ and $W$ equal to zero  |

| $dL/dV_{DS}$       | OTFT channel parameter                                    |

| $E_{G-SD}$         | Gate layer enclosure on S/D contacts                      |

| $E_{OSC-SD}$       | OSC layer enclosure on S/D contacts                       |

| $E_{p}$            | OTFT channel parameter                                    |

| $f_{clk}$          | Clock frequency                                           |

| FW                 | Finger-width                                              |

| $G_{i}$            | Gain of i <sup>th</sup> stage                             |

| $g_{m}$            | OTFT transconductance                                     |

| $g_{m,n}$          | n-OTFT transconductance                                   |

| $g_{m,p}$          | p-OTFT transconductance                                   |

| $G_{max}$          | Maximum gain                                              |

| $G_{t}$            | OTFT channel parameter                                    |

| $H_i$              | <i>i</i> <sup>th</sup> harmonic                           |

| I <sub>00</sub>    | OTFT contact parameter                                    |

| I <sub>c</sub>     | Contact current                                           |

| $I_{D}$            | Drain current                                             |

| $I_{L}$            | Load current                                              |

| $I_{\mathrm{off}}$ | OTFT off-current                                          |

| I <sub>on</sub>    | OTFT on-current                                           |

| $I_{rev}$          | Contact current (I <sub>c</sub> ) coefficient             |

| $K_{\rm B}T/q$     | Thermal voltage                                           |

| L                  | Nominal channel length                                    |

| $L_{early}$        | OTFT channel parameter                                    |

| М                  | Mean value                                                |

| $N_{t}$            | density of trap states at the channel-insulator interface |

| n                  | Number of OTFT channels                                   |

|                    |                                                           |

| Symbol                 | Description                                                                   |

|------------------------|-------------------------------------------------------------------------------|

| q                      | Injected charge                                                               |

| $R_i$                  | Resistance of i <sup>th</sup> resistor                                        |

| $R_{c}$                | Contact resistance                                                            |

| $R_{L}$                | Load resistance                                                               |

| R <sub>off</sub>       | <ol> <li>OTFT channel parameter</li> <li>Transistor off-resistance</li> </ol> |

| $R_{on}$               | OTFT on-resistance                                                            |

| S                      | Sub-threshold swing, sensor sensitivity                                       |

| Τ                      | Temperature                                                                   |

| $t_{ m clk}$           | Clock period                                                                  |

| $V_0$                  | OTFT contact parameter                                                        |

| $V_{b}$                | OTFT channel parameter                                                        |

| $V_{\rm c}$            | OTFT contact voltage                                                          |

| $V_{\sf dd}$           | Supply voltage                                                                |

| $V_{\rm diode}$        | OTFT contact parameter                                                        |

| $V_{DS}$               | Drain-source voltage                                                          |

| $V_{\rm g,min}/V_{00}$ | OTFT contact parameter                                                        |

| $V_{GS}$               | Gate-source voltage                                                           |

| $V_{high}$             | Inverter high output voltage level                                            |

| $V_{low}$              | Inverter low output voltage level                                             |

| $V_{M}$                | Average voltage                                                               |

| $V_{PP}$               | Peak-to-peak voltage                                                          |

| $V_{RF}$               | RF voltage                                                                    |

| $V_{SS}$               | OTFT channel parameter                                                        |

| $V_{T}$                | Threshold voltage                                                             |

| $V_{Tn}$               | n-type threshold voltage                                                      |

| $V_{Tp}$               | p-type threshold voltage                                                      |

| $V_{trip}$             | Inverter trip point                                                           |

| W                      | Nominal channel width                                                         |

| $W_{\rm eff}$          | Effective channel width                                                       |

| $W_{\rm p}/W_{\rm n}$  | Ratio of the width of p-type to n-type OTFTs in an inverter                   |

| $\gamma_c$             | OTFT contact parameter                                                        |

| $\gamma_t$             | OTFT channel parameter                                                        |

| η                      | OTFT contact parameter                                                        |

| σ                      | Standard deviation                                                            |

| τ                      | Time constant                                                                 |

|                        |                                                                               |

# 1 Introduction

The concept of "ambient electronics", referring to electronics embedded extensively in common environments, has emerged in recent years. Embedding intelligence in surfaces such as walls, ceilings, clothes, and packages will improve safety, security, and convenience in everyday life [1]. We will refer to these novel applications as "smart systems-on-foil". Such systems require characteristics that are not met by silicon-based technologies, for example mechanical flexibility and large-area integration at a low cost. The standard crystalline and amorphous silicon technologies require high processing temperatures which are incompatible with flexible surfaces [2]. The possible alternative solutions, such as the thin chip technology [3] and substrate transfer from silicon-on-insulator wafers<sup>1</sup> [4], currently require a fabrication procedure that is not suitable to large-area applications, is complex and, hence, costly. Therefore, there is a growing need for technologies to build electronics with different characteristics from what mainstream silicon technology provides.

Since organic semiconductors allow for low-temperature processing, organic-based devices can be implemented on substrates such as plastic sheets, papers, and cloth [1]-[2]. In addition, some organic materials in solution can be deposited and patterned with conventional graphic art printing processes, promising a simple, fast, and low-cost fabrication flow [5]-[11]. Being flexible and able to cover large areas, organic electronic circuits could be unobtrusively integrated on ambient surfaces and consumer goods.

Though mature organic technologies usually comprise only p-type transistors, in recent years complementary organic transistors have also been developed [12]-[18]. This advancement makes organic technologies more suited for implementing complex circuits, due to the intrinsic lower operating voltage, higher speed, and higher robustness provided. The availability of both p-type and n-type transistors with relatively high performance and stability is an important advantage of organic technologies compared to the low-temperature oxide-based technologies such as [19]

<sup>-</sup>

<sup>&</sup>lt;sup>1</sup> A thin film of Silicon is built on an layer of oxide lying on a thick silicon substrate, later removed by subtracting methods

and [20] which lack p-type transistors.

All the above-mentioned features make complementary organic technology an appealing platform to attain the aims of ambient electronics through smart systems realized on plastic foils, or systems-on-foil. The ability to integrate on the same substrate all the functionalities to realize a complete system is the differentiating advantage of complementary organic electronics.

#### 1.1 Organic circuits: state of the art

Organic smart systems-on-foil need to acquire data from the environment or from digital sources, perform the required data conversion and analysis, and store, display, or transmit the collected data. Some of these functions have been already achieved in several implemented applications, while others are more challenging for organic electronics to accomplish. The implemented applications and the challenges and progress are discussed in the following sections.

#### 1.1.1 Implemented applications

Basic functions based on organic electronics have been shown in several research works, including e.g. backplane matrices for displays [21]-[25], light emission and detection [26]-[29], mechanical and thermal sensors [30]-[34], and actuators [35]-[36]. In addition to these functions, several digital and analogue circuits need to be realized in organic technologies in order to minimize the need for hybrid integrations with silicon chips and keep cost low. These circuits, for instance, should provide analogue signal conditioning interfaces, perform data conversion, control the data flow, and restore synchronization. To give a more specific example, radio-frequency identification (RFID) tags which can interface sensors and actuators are the focus of a considerable part of organic electronics research. After first demonstration of a capacitively-coupled organic RFID tag working at 13.56 MHz [37], more complex versions have been shown. For instance, in [38] an inductively-coupled 64-b RFID tag was presented, and in [39], a 128-b tag has been discussed, which incorporates Manchester encoding and an anti-collision protocol.

First organic analogue to digital converters (ADCs) and digital to analogue

converters (DACs) were shown in [40]-[42] and [43]-[44], respectively. These data converters implemented in different technologies employ various architectures to tackle the resolution and linearity challenge. For example, [40] adopts a delta-sigma structure and reaches a signal to noise and distortion ratio (SNDR) of 24.5dB. The 6-bit ADC in [41] has a successive-approximation-register (SAR) architecture with a maximum integral nonlinearly (INL) of 0.6 LSB and 3 LSB with and without calibration (off-chip SAR logic). In [42], a simple VCO-based structure is used to achieve an INL of 1LSB at the same resolution (6 bit), without using any calibration. In all cases, the circuits are very slow and only suitable for quasi-static signals. A DAC is discussed in [43] with a C-2C architecture comprising only twenty organic thin-film transistors (OTFTs) and seventeen capacitors. In [44], 129 OTFTs are used to realize a current-steering DAC. Due to the use of OTFTs instead of capacitors, the current-steering DAC is more than 50-times smaller and three orders of magnitude faster than the C-2C DAC. At 6-bit resolution, the maximum INL is 1.16 LSB for the former and 0.8 LSB for the latter.

In the digital domain, different line-select drivers for displays based on OTFTs were realised in [45]-[47]. Specifically, the 240-stage shift register in [47] achieves a complexity level of more than thirteen-thousand transistors. In addition, an 8-bit microprocessor was implemented in [48]. The microprocessor can execute user-defined programs at an operation speed of 40 instruction-per-seconds. Recently, Inkjet printing techniques were used in [49] to implement a 8-bit RFID transponder comprising p-only inverters and NANDs with almost 300 OTFTs.

Most of the state of the art presented above is related to p-type only technologies. In recent years, several methods have been exploited to integrate complementary transistors after first demonstrations of stable n-type organic. In [7], solution-based techniques such as spin coating are used together with photolithography to realize a CMOS RFID transponder chip mostly composed of digital circuits. The 48-stage shift register in [14] is implemented by evaporating p- and n-type organic semiconductors with a coarse shadow mask. The SAR ADC in [41] is based on transmission-gates (TGs) which are manufactured using a similar approach. Ultra-fine shadow masks are employed in [15] and [16] to fabricate complementary logic circuits with a few

hundreds of transistors. Circuits with lower number of transistors are also implemented using direct inkjet printing<sup>2</sup> [17]. In [10], a complementary organic technology based on screen-printing<sup>3</sup> techniques is shown, with typical mobility of around 0.02 cm<sup>2</sup>/Vs for both p- and n-type OTFTs. Ultra-low-voltage logic gates [12] and high-speed ring oscillators [13] have also been realized using complementary organic technologies.

Hybrid complementary TFT-based technologies have also been developed in recent years [50] incorporating p-type OTFTs and n-type solution-processed metal-oxide TFTs. This technology has been used to implement circuits on flexible substrates, such as a bidirectional RFID tag [51] and a microprocessor [52] with an architecture similar to [48], but much faster thanks to the complementary technology with a good balance in the mobilities of p-type and n-type TFTs.

Table I summarizes the characteristics of a representative set of implemented organic circuits. It is worth noting that many of the circuits are implemented in p-only technologies due to the scarcity of a stable and robust complementary process. In addition, in the implementation of all these circuits lithographic-based techniques were used. A few of these circuits are shown in Figure 1.

#### 1.1.2 Challenges and progress

Despite all the advancements described, various intrinsic and extrinsic characteristics of organic technologies limit the level of complexity and performance in the circuits. Organic electronic generally aims at applications that do not require high performance, e.g. ambient temperature monitoring and display drivers. Nevertheless, to be able to play a substantial role in future electronics, organic circuits need to communicate with silicon-based circuits based on certain standards. Therefore, specific requirements such as high-frequency (HF) rectification or low-voltage functionality are inevitable at times [53]-[54].

<sup>&</sup>lt;sup>2</sup> The material in solution is used as "ink" in an inkjet printer to form droplets using techniques such as thermal or piezoelectric drop-on-demand (DOD) [130].

<sup>&</sup>lt;sup>3</sup> The ink is pushed through a screen comprising a fine mesh. The pattern is defined by filling certain openings of the mesh with a stencil material [129].

| Table 1  | List of   | annlications | implemented      | hased on  | organic circuit  |

|----------|-----------|--------------|------------------|-----------|------------------|

| Iable 1. | . LIST OI | abblications | IIIIDIEIIIEIILEU | Dascu OII | Organiic Circuit |

| Ref. | Circuit                           | Technology                       | #Tran. | Year |

|------|-----------------------------------|----------------------------------|--------|------|

| [14] | Shift register                    | Complementary                    | 864    | 2000 |

| [45] | Shift register                    | p-only                           | 1888   | 2004 |

| [46] | Display driver                    | p-only                           | ≈4000  | 2005 |

| [37] | Capacitive-coupled RFID tag       | p-only                           | 1938   | 2007 |

| [38] | Inductive-coupled RFID tag        | p-only                           | ≈420   | 2008 |

| [7]  | Transponder chip                  | Complementary                    | 168    | 2009 |

| [39] | RFID tag including anti-collision | p-only                           | 1286   | 2009 |

| [43] | C-2C DAC                          | Complementary                    | 22     | 2009 |

| [15] | Decoder                           | Complementary                    | ≈200   | 2009 |

| [40] | Delta-sigma ADC                   | Dual-gate p-only                 | ≈70    | 2010 |

| [41] | SAR ADC (the logic is off-chip)   | Complementary                    | 53     | 2010 |

| [16] | AC power-meter                    | Complementary with floating gate | 609    | 2011 |

| [44] | Current-steering DAC              | p-only                           | 129    | 2012 |

| [48] | Microprocessor                    | Dual-gate p-only                 | 3381   | 2012 |

| [42] | VCO-based ADC                     | Dual-gate p-only                 | N.A.   | 2013 |

| [48] | Shift register                    | Dual-gate p-only                 | 13440  | 2014 |

Figure 1. Some applications implemented using organic technologies: (a) artificial skin based on a matrix of organic sensors [34], (b) all-organic integrated flexible display [22], (c) microprocessor on foil [48], (d) ADC and other ICs on foil.

Typically the mobility ( $\mu$ ) of OTFTs is in the order of 0.1 cm<sup>2</sup>/Vs and does not surpass 0.5-1 cm<sup>2</sup>/Vs. This characteristic, along with a typical minimum feature size of several microns and large overlap parasitic capacitances, limit the speed of organic circuits. For instance, the microprocessor in [48] works at a clock frequency of 40 Hz, and the sampling frequency of the delta-sigma ADC in [40] is 500Hz. There have been many efforts to achieve OTFTs with high field-effect mobility, reaching around 10 cm<sup>2</sup>/Vs for p-type [55] and 1 cm<sup>2</sup>/Vs for n-type [56]. In addition, submicron OTFTs with minimum channel length of 0.8 µm have been implemented using high-resolution silicon masks [57]. Some techniques to reduce the parasitic overlap capacitances in printed OTFTs have also been investigated. For example in [58], thanks to the selfalignment of layers in inkjet-printed OTFTs, the registration errors and, thus, the parasitic capacitances are substantially reduced. However, the use of high-precision or un-conventional techniques for organic technologies can weaken or eliminate some attractive features such as low-cost and simplicity. The same holds when very high mobility materials are used, as these semiconductors are usually very crystalline small molecules which are hard to process.

In addition to low mobility, OTFTs may suffer from high threshold voltages ( $V_T$ ), as in [10]. As a result, circuits based on these OTFTs function only at high supply voltages, making the realization of portable and battery-powered applications very cumbersome. This situation is exacerbated for circuits in unipolar<sup>4</sup> technologies which have intrinsically higher power consumption. In recent years several approaches have been developed to realize high-capacitance dielectrics at low temperatures, reducing the supply voltage of organic circuits considerably, especially in the case of digital circuits [53], [59]. In [43] and [44], the DACs are functional at voltages as low as 3 V, and the organic decoder in [15] works at 2 V. However, most applications realized in organic technologies till now use power supplies in the range of a few tens of volts [7], [14], [16], [38]-[42], [46], [48].

Another key factor limiting the complexity of organic circuits is the relatively high

<sup>&</sup>lt;sup>4</sup> In this dissertation, the term "unipolar" is used for technologies incorporating only one type of transistor (p- or n-type)

variability in the characteristics of OTFTs [60], [61]. These variations result from the use of low-temperature and low-cost techniques which allow only limited control on the process. The global (large-area) and local (small-area) variations in the characteristics of the process lead to considerable deviations from the target device performance and thus in soft faults at the circuit level. In addition, the occurrence of defects during the process causes functional failures or hard faults. Environmental and bias instabilities also add to the parameter variations in some technologies. Such shortcomings are seriously limiting the complexity and performance of organic circuits, especially in case of unipolar technologies where the lack of n-type transistors further exacerbates the sensitivity to device variations. This problem becomes even more prominent in technologies employing printing techniques, due to the low degree of spatial correlation typical of printing processes, which translates in even worse matching and larger variability in the transistors. That is why circuits implemented based on printed OTFTs [5]-[10] are mainly limited to digital electronics or large-area switch matrices.

#### 1.2 Role of complementary technologies

Currently, organic p-only technologies are the most reliable in terms of hard faults. Indeed, state-of-the-art p-only circuits have reached the complexity level of thirteen-thousand OTFTs [47], compared to a few hundreds OTFTs in complementary circuits. However, when complementary technologies become reliable enough to offer a comparable hard yield, the maximum circuit complexity will be limited by soft faults to which complementary circuits are far less vulnerable.

Due to the lack of n-type OTFTs, p-only logic gates mostly employ zero- $V_{\rm GS}^{5}$  or diode-connected transistors as load [62]. The load transistor is thus permanently conducting, and the gates sustain very low switching speeds and/or high static power consumption. In addition, when load and drive p-OTFTs have the same  $V_{\rm T}$ , the output pull-up and pull-down are unbalanced, leading to an asymmetric transfer curve and a very low noise margin. Therefore, digital circuits in single- $V_{\rm T}$  unipolar technologies are

<sup>&</sup>lt;sup>5</sup> Zero-Gate-Source voltage. This kind of load is used only for technologies which provide normally-on (or depletion) transistors.

very sensitive to variability and suffer seriously from poor robustness. The circuit robustness can be increased by addition of an extra gate to each OTFT [63], [47]. The dual gate technology allows for tuning the  $V_T$  of transistors in order to have a more balanced pull-up and pull-down and, thus, an improved noise margin. In this case, an external biasing is needed to set the back-gate voltage.

In the analogue circuit domain, almost no well-known architecture in CMOS technology can be exploited in unipolar technologies. Unipolar OTFTs are typically normally-on, and being such, sink diode-connected transistors do not work in saturation [64]. Consequently, current mirrors can be used neither as an active load nor to provide reference bias currents [65], also meaning that auto-biasing cannot be realized. In addition, not only are transmission-gates (TGs) unavailable, but, due to the depletion characteristics of most p-only OTFT technologies, switches cannot be turned off without the use of charge pumps or external biasing. Therefore, switched-capacitor (SC) architectures are typically very cumbersome, or unpractical. Another disadvantage of unipolar technologies is the very limited input common-mode range of p-only amplifiers. Indeed, due to the different DC levels of the input and output voltages, cascading gain-stages does not lead to a large gain improvement [65], or necessitates large AC coupling capacitors, which have poor yield.

In summary, unipolar technologies impose many restrictions on circuit design, which can strongly limit the performance, robustness and practical applicability of organic electronics. This clarifies the role that complementary technology could play in facilitating the design and improving the robustness and performance of OTFT-based circuits. Indeed, complementary circuits provide a better power-delay product, intrinsically-lower supply voltage for a given threshold voltage level, higher noise margin, larger resilience to variability, and more design options (especially in case of analogue and mixed-signal design). Although dual-gate transistors can also improve circuit robustness, the development of crystalline-silicon CMOS technology teaches us that the use of a complementary technology is the most promising route to further improve the complexity of analogue and digital organic circuits.

The realization of a reliable and stable organic complementary technology, however, is hampered by technical challenges at the process level. For instance, air-

stable and high-mobility n-type organic semiconductors are not widespread. In addition, the organic material deposited first can easily degrade when it is exposed to the processing steps related to the second material [7]. In general, the added complexity of the complementary process increases the probability of hard faults. That is why a mature complementary organic technology is not yet available and, as depicted in Table I, the most complex applications based on organic circuits thus far have been realized in p-only technologies.

#### 1.3 Problem statement

From the prior art discussed in Section 1.1, it is clear that, despite the potentials of organic technologies and their recent advancements, many challenges hinder the design and implementation of circuits based on OTFTs. OTFTs suffer from low mobility, large feature size, high threshold voltage, high variability, and environmental and bias instability. These characteristics unfavourably affect speed, gain, power, and yield of organic circuits as well as their level of integration and complexity. Therefore, the main challenge is to improve performance and robustness of organic circuits in order to enable implementation of the target applications.

#### 1.4 Aim of the thesis

The aim of this thesis is to explore circuit and system design in complementary organic technologies. We focus on using the characteristics of complementary technologies to improve circuit performance and robustness, taking into account current-state drawbacks of these technologies such as immaturity and relatively large amount of defects. To achieve this goal, we study the characteristics of state-of-the-art manufacturing processes for complementary OTFTs and the modelling of these OTFTs. This knowledge allows us to carry out a technology-aware design procedure starting from devices and building blocks and reaching complete systems-on-foil. For doing so, we investigate the design at different abstraction levels including architecture, circuit, and layout. In addition, we do a study on the device-level parametric variability and its effect on circuit design. From a practical point of view, considering the challenges we are confronting to realize circuits in organic electronics, we specifically focus on the following aspects:

- Complementary digital circuit design to achieve high noise-margin and lowvoltage logic

- Complementary analogue and RF circuit design to achieve performant and reliable circuits

- Design of mixed-signal systems-on-foil combining logic, energy scavengers, and reliable analogue circuits for sensing and actuating applications

#### 1.5 Scope of the thesis

In this work, we focus on the design of three systems-on-foil in complementary organic technologies:

- A display driver

- An ADC for ambient temperature monitoring

- An RFID tag based on the so-called "silent tag" communication protocol<sup>6</sup>

These applications have been selected based on their industrial impact and are the lead applications of the Framework 7 European project "Complementary Organic Semiconductor Metal Integrated Circuits" (COSMIC).

Two technologies are used to implement the above applications, namely:

- A wafer-to-wafer technology (W2W)

- A sheet-to-sheet technology (S2S)

These technologies have characteristics that make them suitable for different types of applications and are discussed later in the thesis. The display driver is designed in W2W technology which is compatible with the current flat panel display (FPD) industry. On the other hand, the ADC and RFID tag are designed for the printing-based S2S technology. The designs are, thus, technology-aware, meaning that they take into account the specific characteristics of each technology. We discuss several digital and analogue building blocks tailored to the specific applications for each technology. Finally, we integrate the different building blocks in complex systems.

11

<sup>&</sup>lt;sup>6</sup> A type of reader-talks-first protocol in which the RFID tag only sends a reply to the reader when it receives its unique identity code

#### 1.6 Original contributions

This work advances in multiple ways the state-of-the-art of OTFT-based circuits and systems using two novel complementary technologies:

Wafer-to-Wafer (Lithographic technology)

- First-level statistical characterization of OTFT parametric variations

- Logic-style selection based on the specific characteristics of W2W technology

- Design and characterization of a display driver. The circuit works at the lowest supply voltage achieved by an organic line driver and it exploits the largest number of OTFTs in a complementary organic technology to-date

Sheet-to-sheet (Printing technology)

- First-level statistical characterization of Gen.1 and Gen.2<sup>7</sup> OTFT parametric variations

- Logic-style selection based on specific characteristics of the S2S technology

- Design and characterization of:

- A dynamic flip-flop to reduce the area of printed logic (first experiment of printed dynamic logic)

- A comparator exploiting input offset cancellation and achieving high accuracy (input accuracy ±50mV at 40V supply)

- o A resistor-based DAC (first printed DAC) achieving 7-bit linearity

- HF rectifiers in Gen.1 and Gen.2 technology

- o The first ADC printed on foil

- A temperature monitor system incorporating an ADC and a sensor on foil

- Building blocks of an RFID tag on foil, including silent tag logic and power scavenging

The above achievements lead to:

<sup>&</sup>lt;sup>7</sup> Two generations of S2S technology have been studied (See Section 2.2)

- A step-by-step advancement in the level of complexity of complementary organic circuits towards the implementation of systems-on-foil

- A platform to factually compare different state-of-the-art complementary technologies and explore what they can offer in comparison with unipolar technologies

#### 1.7 Outline of the thesis

This thesis is divided in two main parts. Part I concerns the OTFT technology, modelling, and building block design addressed in chapters 2 to 5. Part II, including chapters 6 to 8, focuses on the implementation of three systems-on-foil.

Chapter 2 introduces the various fabrication methods, TFT architectures, and typical layout rules adopted by the two main technologies used in this work, namely S2S and W2W. The main differences between the two versions of S2S technology, designated Gen.1 and Gen.2, are also pointed out. The electrical characterizations and models of the S2S and W2W complementary OTFTs are described in chapter 3, after a qualitative description of the operation and performance of OTFTs. In addition, the parametric variations which were extracted and used for circuit design are presented in this chapter.

The design and experimental characterization of a large set of digital blocks in the S2S and W2W technologies are illustrated in Chapter 4. Chapter 4 also includes a comparison of different implementation styles (e.g. fully-static and dynamic) to help choose the architecture that fits better to the specific characteristics of each technology. In Chapter 5, we show the design and characterization of several analogue and mixed signal blocks tailored for applications targeted by the S2S technology. These circuits include operational transconductance amplifiers (OTAs), comparators, DACs, and rectifiers. Single-stage OTAs in the W2W technology are also presented in this chapter.

The illustration of systems-on-foil starts with chapter 6 which presents a line driver on foil and its tests with a flexible display in the W2W technology. Chapter 7 shows the design and characterization of an ADC and a sensor on foil, and the implementation and test of a temperature monitor based on the aforesaid circuits. A

printed passive reader-talks-first RFID tag based on the silent tag communication protocol is presented in chapter 8. Finally, conclusions are drawn in Chapter 9.

#### PART I

# COMPLEMENTARY OTFT TECHNOLOGY, MODELLING, AND BUILDING-BLOCK DESIGN

# 2 Complementary OTFT Technology

In this chapter, we introduce the characteristics of the S2S and W2W technologies used in this work to implement different circuits and systems-on-foil. For each technology, we explain the process flow, the device configuration, and the typical layout rules. The knowledge of these characteristics is paramount to carry out a technology-aware circuit design.

#### 2.1 Introduction

An OTFT consists of a stack of different thin layers deposited on a flexible substrate, such as plastic foil or paper. These layers form the source/drain (S/D) contacts, gate electrode, gate dielectric, and active layer (channel) of the TFT. Depending on the position of the S/D contacts and gate electrode with respect to the organic semiconductor (OSC), various TFT structures with some differences in their electrical performance can be realised.

As explained in the introduction, a variety of methods have been used to deposit and pattern the individual layers of complementary OTFTs. Examples include evaporation of organic semiconductors through coarse [14] or ultra-fine [15] shadow masks, and ink-jet printing [17]. In this work, two complementary organic technologies have been exploited, namely sheet-to-sheet (S2S) [66] and wafer-to-wafer (W2W) [67]. The S2S and W2W technological platforms concern different manufacturing modes in terms of toolset and materials, technology specifications, and foil size. The process in S2S technology is performed directly on 11×11 cm² sheets of plastic and is based on semiconductors in solution. The OTFTs are manufactured using screen-printing techniques. In W2W technology, the manufacturing process is based on evaporated semiconductors and is performed on plastic foils laminated on 6-inch wafer carriers. The employed photolithography techniques help to achieve highly integrated OTFTs with small footprints.

In Section 2.2 and 2.3, the various fabrication methods and TFT architectures adopted by S2S and W2W are illustrated, respectively. In addition, the typical layout rules for each technology are discussed. Section 2.4 summarises the highlights of S2S and W2W technologies.

#### 2.2 Sheet-to-sheet (S2S) fabrication process

Some potentially attractive features of organic electronics, e.g. the high-throughput fabrication, are associated with the possibility to manufacture electronics using processes that are compatible with conventional graphic arts printing processes,

such as Gravure-printing<sup>8</sup> and screen-printing [5]-[11]. The interest in printed electronics is nurtured by the possibility to formulate organic functional materials like insulators, conductors and semiconductors in ink-like fluids that can actually be printed: printing organic technology could foster the widespread use of organic electronics applications for a substantial improvement in the quality of every-day life [8]. In the S2S technology, OTFTs and other components such as capacitors and resistors are implemented using screen-printing techniques. The manufacturing process is carried out in CEA-Liten, Grenoble, France.