# Wireless wire - ultra-low-power and high-data-rate wireless communication systems

Citation for published version (APA):

Li, X. (2011). Wireless wire - ultra-low-power and high-data-rate wireless communication systems. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR716273

DOI:

10.6100/IR716273

Document status and date:

Published: 01/01/2011

Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 04. Oct. 2023

# Wireless Wire — Ultra-Low-Power and High-Data-Rate Wireless Communication Systems

Xia Li

Front and back covers:

"The persistence of injection locking", oil painting by Xia Li

The invitation bookmark:

"Burn the witch", oil painting by Xia Li

# Wireless Wire — Ultra-Low-Power and High-Data-Rate Wireless Communication Systems

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus, prof.dr.ir. C.J. van Duijn, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op donderdag 29 september 2011 om 14.00 uur

door

Xia Li

geboren te Xi'an, China

Dit proefschrift is goedgekeurd door de promotoren:

prof.dr.ir. P.G.M. Baltus en prof.dr.ir. A.H.M. van Roermund

Copromotor:

dr. D. Milosevic

A catalogue record is available from the Eindhoven University of Technology Library.

CIP-DATA LIBRARY TECHNISCHE UNIVERSITEIT EINDHOVEN

Xia Li

Wireless Wire — Ultra-Low-Power and High-Data-Rate Wireless Communication

Systems / by Xia Li. – Eindhoven: Technische Universiteit Eindhoven, 2011.

Proefschrift. – ISBN: 978-90-386-2548-5

**NUR 959**

Key words: Low power / high data rate / CMOS integrated circuit design / millimeter wave / injection locking / wake-up receiver / wireless phased array receiver frontends

Copyright © 2011 by Xia Li, Eindhoven

All rights reserved. No part of this publication may be reproduced or transmitted in any form or by any means, electronic, mechanical, including photocopy, recording, or any information storage and retrieval system without the prior written permission of the copyright owner.

#### Lisa · Maverick

Everybody has a witch in one's soul

She entices you to be a maverick

and keeps your secret wounds being healed

You love yourself as she has told

You become beloved by the rest once she would go

I used to love my witch

But now I have no choice but to burn her into ashes

Life is a live show

No rehearsal and the audience is low

Staying with her, I am a weirdo but full with hope

Without her, I become somebody but smile like a joke

My dream is sealed

My witch is killed

I want to grow

I want to glow

-By Xia Li

# Samenstelling Promotiecommissie:

prof.dr.ir. P. van den Bosch prof.dr.ir. P.G.M. Baltus

prof.dr.ir. A.H.M. van Roermund

dr.ir. D. Milosevic prof.dr.ir. J.R. Long prof.dr.ir. B. Nauta prof.dr.ir. J.P. Linnartz

dr.ir. G. Dolmans

TU Eindhoven (voorzitter)

TU Eindhoven (promotor)

TU Eindhoven (2<sup>nd</sup> promotor)

TU Eindhoven (co-promotor)

TU Delft

TU Twente

TU Eindhoven / Philips Research

Holst Center /IMEC-NL

# **TABLE OF CONTENTS**

| TABLE OF CONTENTS                                         | I    |

|-----------------------------------------------------------|------|

| LIST OF FIGURES                                           | V    |

| LIST OF TABLES                                            | X    |

| LIST OF ABBREVIATIONS                                     | XI   |

| LIST OF SYMBOLS                                           | XIII |

| CHAPTER 1 INTRODUCTION                                    | 1    |

| 1.1 Background                                            | 1    |

| 1.2 RESEARCH OBJECTIVES                                   | 3    |

| 1.3 CHALLENGES AND RESEARCH METHOD                        | 4    |

| 1.4 Scope of the thesis                                   | 8    |

| 1.5 Original contributions                                | 9    |

| 1.6 OUTLINE OF THESIS                                     | 10   |

| CHAPTER 2 STATE OF THE ART                                | 13   |

| 2.1 STATUS AND TRENDS OF WIRELESS SYSTEMS                 | 13   |

| 2.2 Low power techniques                                  | 14   |

| 2.2.1 IMPULSE RADIO UWB                                   | 14   |

| 2.2.2 Super-regenerative receiver                         |      |

| 2.2.3 BACK-SCATTERING ARCHITECTURE FOR ASYMMETRICAL LINKS | 16   |

| 2.3 MILLIMETRE-WAVE COMMUNICATIONS                        | 17   |

| 2.4 WAKE-UP RECEIVER                                      | 18   |

| CHAPTER 3 CROSS-LAYER POWER OPTIMIZATION                  | 21   |

| 3.1 Figure-of-merit                                       | 22   |

| 3.2 PHY-LAYER POWER OPTIMIZATION                          | 24   |

| 3.2.1 Optimum frequency for minimum $E_{\it bit}$         | 24   |

| 3 2 2 OPTIMUM DATA RATE FOR MINIMUM $P_{AVE}$             | 29   |

| 3.2.3 OPTIMUM MODULATION SCHEME                                       | 34 |

|-----------------------------------------------------------------------|----|

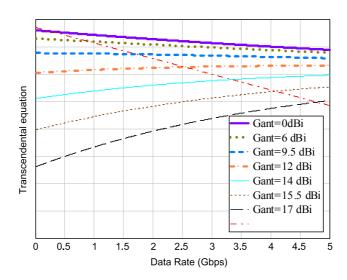

| 3.2.4 Antenna gain                                                    | 36 |

| 3.3 PHY-MAC CO-DESIGN TOWARDS MINIMUM AVERAGE POWER                   | 37 |

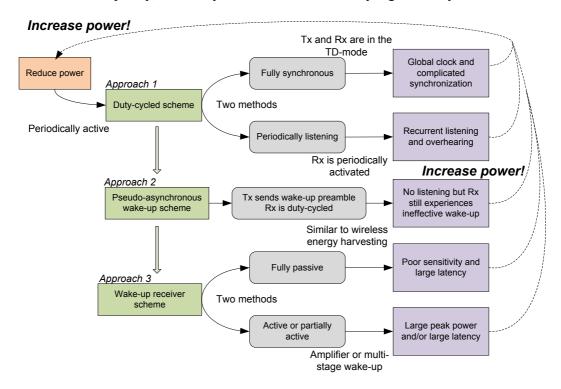

| 3.3.1 Generic solutions for power management                          | 37 |

| 3.3.2 ASYNCHRONOUS DUTY-CYCLED WAKE-UP SCHEME                         | 38 |

| 3.3.3 COMPARISON OF POWER MANAGEMENT SCHEMES                          | 40 |

| 3.3.4 DUTY-CYCLED WAKE-UP WITH CSMA/CA MEDIUM ACCESS                  | 42 |

| 3.4 MAC-NETWORK CO-DESIGN: DIRECTIONAL COMMUNICATION IN THE MULTI-HOL |    |

| AD HOC NETWORKS                                                       | 43 |

| 3.4.1 THE AD HOC NETWORK: IMPACT OF INTERFERENCE ON CAPACITY          | 43 |

| 3.4.2 MULTI-HOP ROUTING TOWARDS MAXIMUM NETWORK LIFETIME              | 48 |

| 3.5 COMPARISON BY FOM                                                 | 51 |

| CHAPTER 4 SYSTEM DESIGN AND OPTIMIZATION                              | 55 |

| 4.1 SYSTEM ARCHITECTURE AND POWER OPTIMIZATION.                       | 55 |

| 4.1.1 Wireless wire system structure                                  | 55 |

| 4.1.2 AVERAGE POWER CONSUMPTION OPTIMIZATION                          | 57 |

| 4.1.3 Energy sources: harvesting, battery and combined                | 59 |

| 4.2 PRACTICAL ISSUES IN THE LINK BUDGET MODEL                         | 63 |

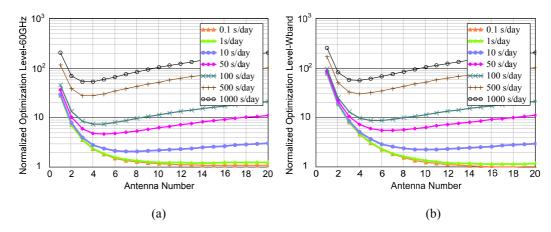

| 4.2.1 Antenna gain vs. power consumption of multi-path transceiver    | 64 |

| 4.2.2 System bandwidth discussion                                     | 68 |

| 4.3 IJLO BASED ASYNCHRONOUS DUTY-CYCLED WURX                          | 70 |

| 4.3.1 Basic theory of the IJLO                                        | 71 |

| 4.3.2 WuRx with frequency-sweeping injection locking mechanism        | 75 |

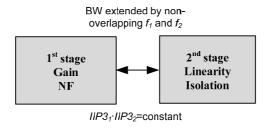

| 4.3.3 BANDWIDTH EXTENSION AND SENSITIVITY ENHANCEMENT OF THE WURX     | 79 |

| 4.3.4 SUMMARIZED DESIGN CONSIDERATIONS AND METHODS                    | 80 |

| 4.3.5 Interference tolerance: pseudo capture effect                   | 81 |

| 4.3 MAIN RADIO POWER OPTIMIZATION                                     | 83 |

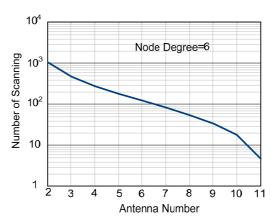

| 4.4.1 OPTIMIZED ANTENNA NUMBER—BEAM SCANNING RELATED                  | 85 |

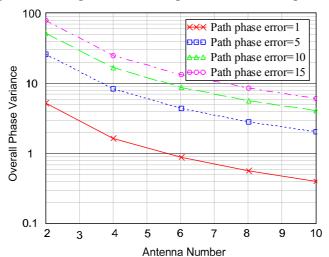

| 4.4.2 Antenna number discussion considering phase errors              | 88 |

| 4.5 CONCLUSIONS                                                       | 89 |

| CHAPTER 5 MMW LOW-POWER WAKE-UP RECEIVER                              | 91 |

| 5.1 GENERAL INTRODUCTION OF WAKE-UP RECEIVERS                | 92  |

|--------------------------------------------------------------|-----|

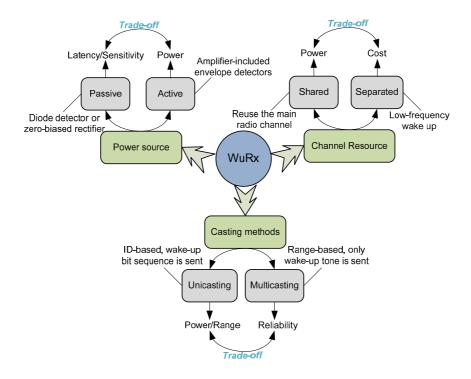

| 5.1.1 CLASSIFICATIONS AND TRADE-OFFS                         | 92  |

| 5.1.2 SOLUTIONS FOR THE MMW WAKE-UP RECEIVERS                |     |

| 5.2 TECHNOLOGY FOR MMW LOW-POWER APPLICATIONS                | 95  |

| 5.3 WAKE-UP RECEIVER CIRCUIT DESIGN                          | 97  |

| 5.3.1 LINK BUDGET AND SYSTEM SPECIFICATIONS                  | 97  |

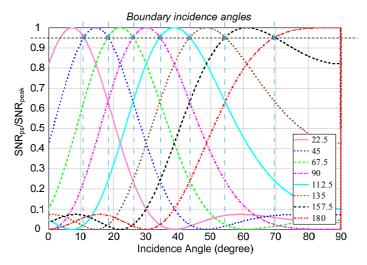

| 5.3.2 WuRx architecture and brief system design review       | 100 |

| 5.3.3 DESIGN OF THE INJECTION-LOCKED OSCILLATOR              | 102 |

| 5.3.4 DESIGN OF THE PASSIVE MIXER AND THE BUFFER AMPLIFIER   | 117 |

| 5.3.5 DESIGN OF THE WAKE-UP RECEIVER                         | 121 |

| 5.4 IMPLEMENTATION AND EXPERIMENTAL RESULTS                  | 128 |

| 5.5 CONCLUSIONS AND FOLLOW-UP                                | 136 |

| CHAPTER 6 PHASED ARRAY RECEIVER DESIGN                       | 141 |

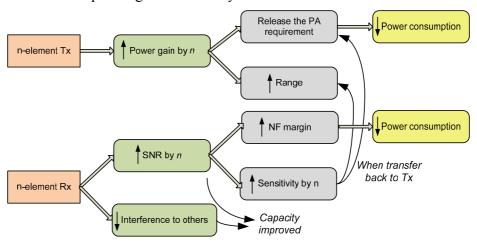

| 6.1 DISCUSSIONS ON BEAMFORMING                               | 141 |

| 6.1.1 Benefits and potential problems of beamforming arrays  | 143 |

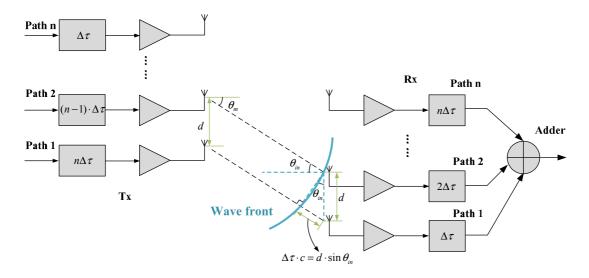

| 6.1.2 True time delay array and phased array                 | 146 |

| 6.1.3 IMPACT OF DISCRETE PHASE SHIFTING                      | 149 |

| 6.1.4 Position of phase shifting                             | 151 |

| 6.2 Main receiver architecture of the wireless wire system   | 152 |

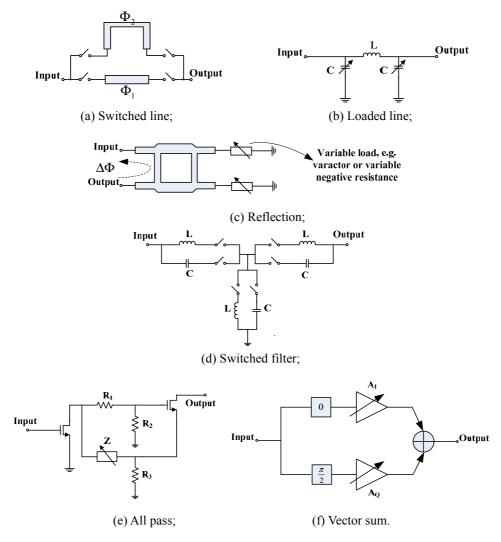

| 6.3 DESIGN OF 60-GHZ LOW-NOISE AMPLIFIER                     | 154 |

| 6.3.1 LNA DESIGN METHODOLOGY                                 | 154 |

| 6.3.2 DESIGN EXAMPLES OF THE 60-GHZ LOW-POWER LNA            | 157 |

| 6.4 Design of 60-GHz phase shifters                          | 160 |

| 6.4.1 Phase shifters comparison                              | 161 |

| 6.4.2 DESIGN OF A 60-GHZ REFLECTION-TYPE PHASE SHIFTER       | 163 |

| 6.4.3 Design of a 60-GHz 4-bit vector-sum type phase shifter | 166 |

| 6.5 DESIGN EXAMPLE OF A 4-ELEMENTS PHASED ARRAY RECEIVER     | 170 |

| 6.6 CONCLUSIONS                                              | 173 |

| CHAPTER 7 CONCLUSIONS AND RECOMMENDATIONS                    | 175 |

| APPENDIX A NOISE MODEL                                       | 179 |

| APPENDIX B. RF HARVESTING | 181 |

|---------------------------|-----|

| SUMMARY                   | 183 |

| ACKNOWLEDGEMENT           | 185 |

| BIOGRAPHY                 | 187 |

| LIST OF PUBLICATIONS      | 189 |

# LIST OF FIGURES

| Fig. 1.1 Wireless P2P commutations.                                                | 2     |

|------------------------------------------------------------------------------------|-------|

| Fig. 1.2 Research objectives and potential applications                            |       |

| Fig. 1.3 Aspects related to average power consumption reduction of a system        | 6     |

| Fig. 2.1 Status and trends of wireless systems on personal communications          | 13    |

| Fig. 2.2 Block diagram of a non-coherent IR-UWB Rx with energy detection           | ction |

| approach                                                                           | 15    |

| Fig. 2.3 Block diagram of a conventional super-regenerative Rx                     | 15    |

| Fig. 2.4 (a) Block diagram of a conventional back-scattering transceiver and       | (b) a |

| transceiver consisting of a polar Tx and a self-correlation Rx for F               | RFID  |

| application.                                                                       | 16    |

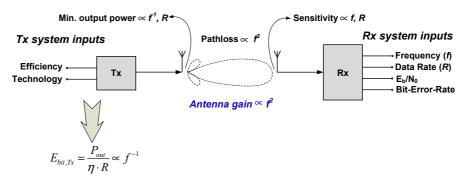

| Fig. 3.1 Parameters in different layers of a wireless system.                      | 21    |

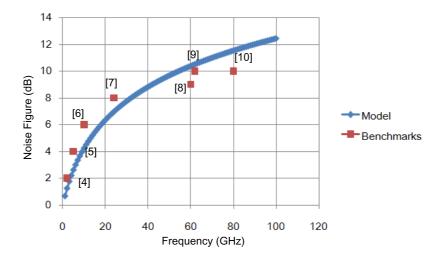

| Fig. 3.2 Noise factor as a function of frequency.                                  | 25    |

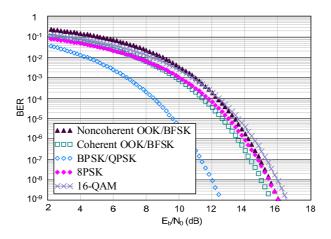

| Fig. 3.3 BER as a function of $E_b/N_0$ in the AWGN channel                        | 25    |

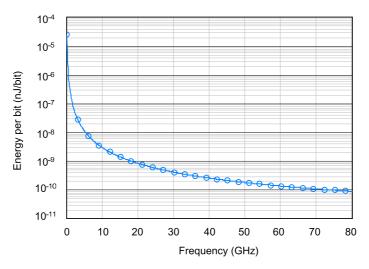

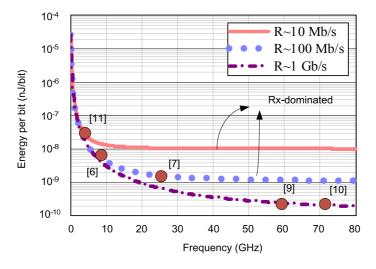

| Fig. 3.4 The minimum $E_{bit}$ of the Tx as a function of frequency.               | 28    |

| Fig. 3.5 Trend of the $E_{bit}$ scaling with frequency for entire transceivers     | 28    |

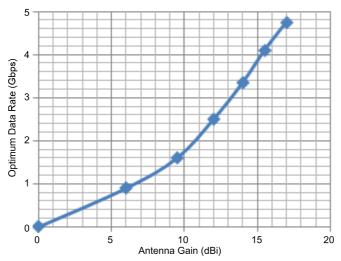

| Fig. 3.6 The optimum data rate as a function of antenna gain for the wireless      | wire  |

| system.                                                                            | 31    |

| Fig. 3.7 Peak data rate vs. antenna gain.                                          | 32    |

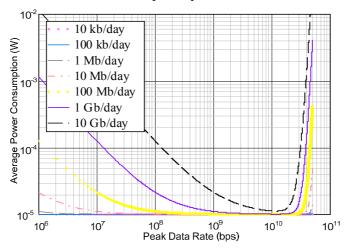

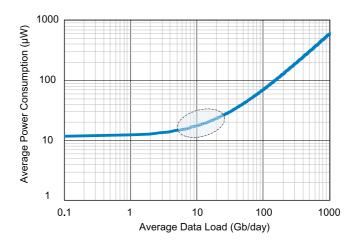

| Fig. 3.8 Average power consumption as a function of data rate ( $G_{ant}$ =10 dBi) | 32    |

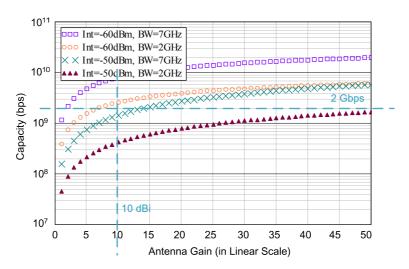

| Fig. 3.9 Antenna gain vs. channel capacity under interference                      | 33    |

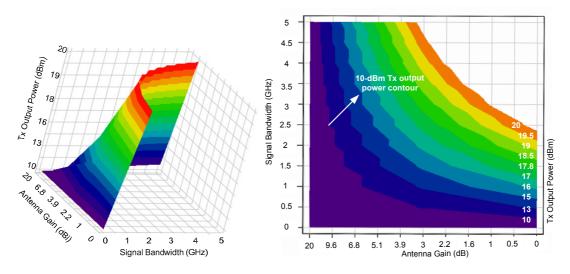

| Fig. 3.10 (a) Tx Output as a function of the antenna gain and signal BW; (b)       | ) top |

| view.                                                                              | 34    |

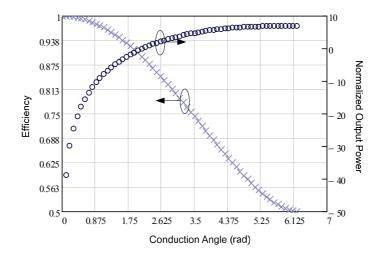

| Fig. 3.11 The PA efficiency and output power                                       | 35    |

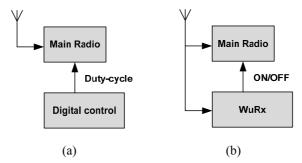

| Fig. 3.12 Architectures of (a) duty-cycled radio and (b) the wake-up radio         | 37    |

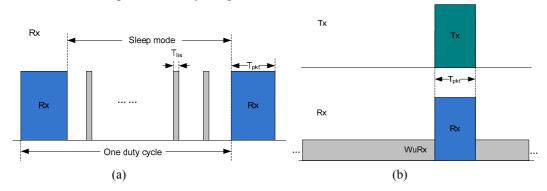

| Fig. 3.13 Operation activity diagrams of (a) the duty-cycled Rx and (b) the wak    | e-up  |

| radio                                                                              | 38    |

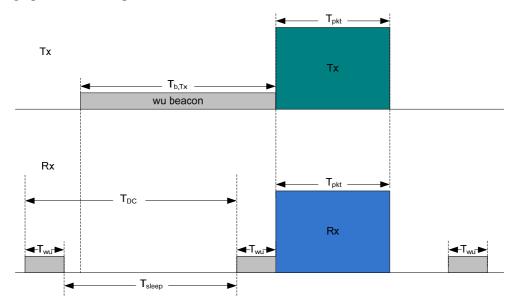

| Fig. 3.14 The asynchronous duty-cycled wake-up scheme.                             | 39    |

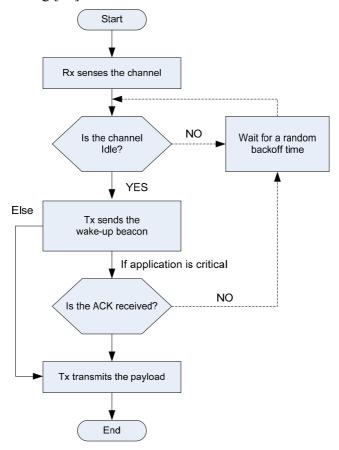

| Fig. 3.15 CSMA/CA based asynchronous wake-up flow.                                 |       |

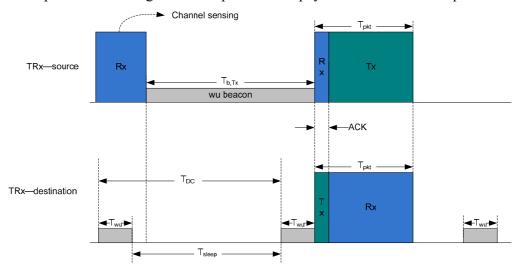

| Fig. 3.16 Asynchronous duty-cycled wake-up with CSMA with ACK.                     | 43    |

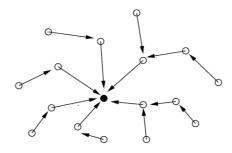

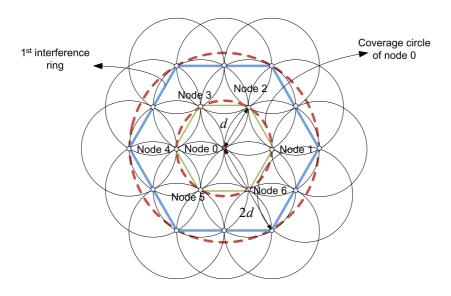

| Fig. 3.17 A simple ad hoc network with multi-hop routing.                          | 44    |

| Fig. 3.18 Interferers prediction with CSMA/CA in a multi-hop network               | 44    |

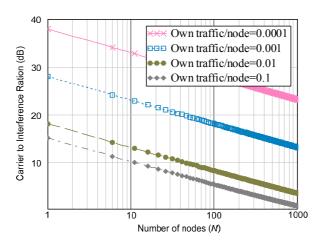

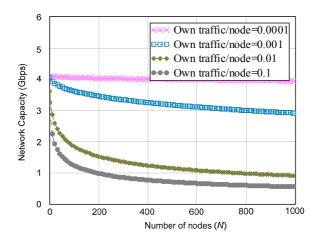

| Fig. 3.19 Impact of the traffic on CIR in an ad hoc and multi-hop network          | 46    |

| Fig. 3.20 The capacity of a 60-GHz system in the ad-hoc and multi-hop network      |       |

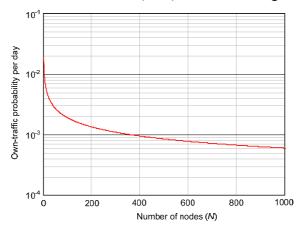

| Fig. 3.21 Own-traffic probability of a node when total traffic is 0.0116           |       |

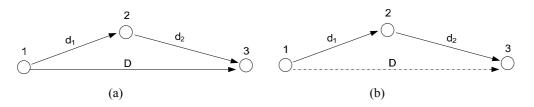

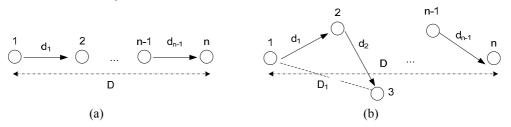

| Fig. 3.22 (a) direct communication and (b) multi-hop routing.                      |       |

| Fig. 3.23 (a) Linearly hopping array and (b) randomly hopping array                | 49    |

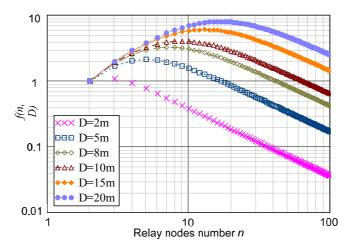

| Fig    | 3.24 Optimum relay nodes number in the linear array                             | 50  |

|--------|---------------------------------------------------------------------------------|-----|

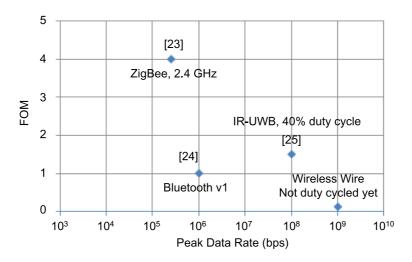

| Fig. 3 | 3.25 Comparison of ULP systems by FOM or $E_{ave,corr}$                         | 52  |

| Fig. 4 | 4.1 The wireless wire front end                                                 | 56  |

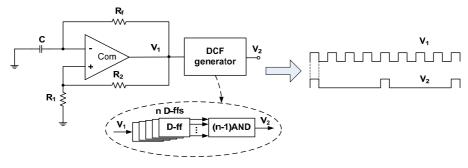

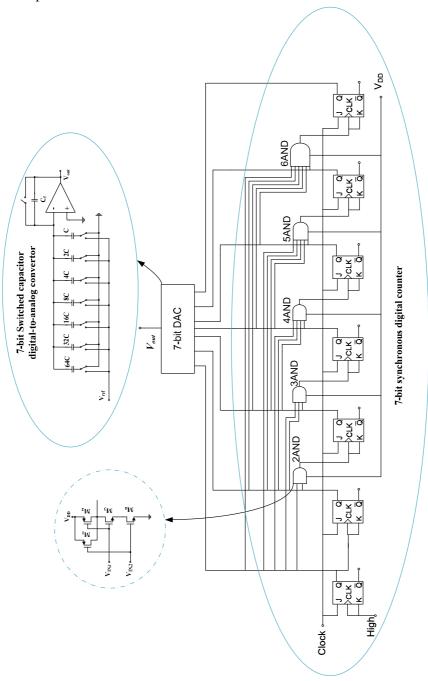

| Fig. 4 | 4.2 Duty cycle control voltage generator                                        | 56  |

|        | 4.3 The minimum average power consumption                                       |     |

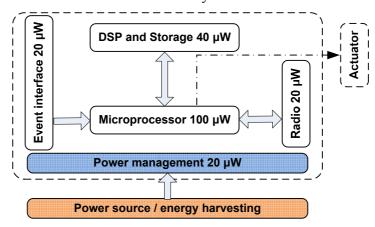

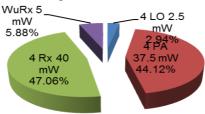

| Fig. 4 | 4.4 The power budget of the entire node                                         | 59  |

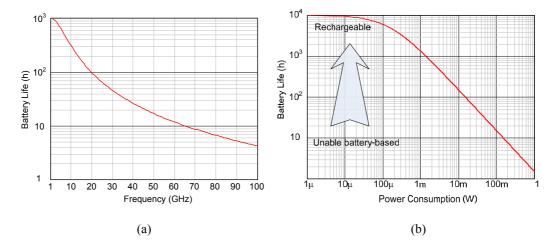

| Fig. 4 | 4.5 Battery life of (a) an always-on system and (b) as a function of the power. | 61  |

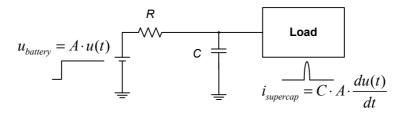

| Fig. 4 | 4.6 Work principle of a supercapacitor                                          | 62  |

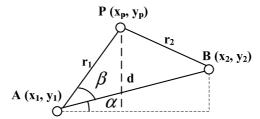

| Fig. 4 | 4.7 The link model of the directional communication system                      | 63  |

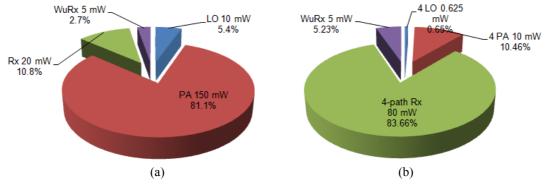

| Fig. 4 | 4.8 The power distribution of (a) an omni-directional and (b) a phased-array    | 64  |

| Fig. 4 | 4.9 Total power vs. antenna number when scaling the Rx circuit parameters       | 68  |

| Fig.   | 4.10 Power budget of the 4-path transceiver array when scaling the              | Rx  |

|        | parameters.                                                                     | 68  |

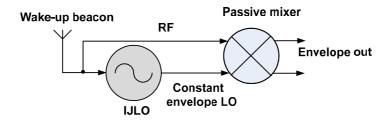

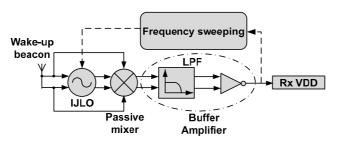

| Fig. 4 | 4.11 An IJLO based WuRx                                                         | 71  |

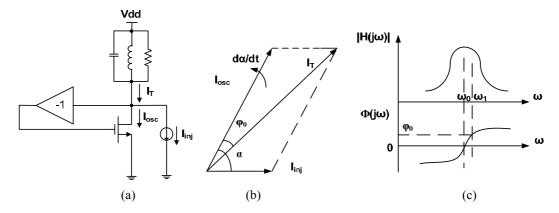

| Fig.   | 4.12 (a) The conceptual IJLO model, (b) the phasor diagram at a given insta     | ant |

|        | and (c) the open-loop characteristics of the resonator                          | .72 |

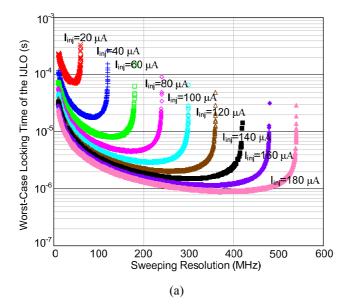

| Fig.   | 4.13 The worst-case settling times of (a) a 60-GHz IJLO with a 7-GHz to         | tal |

|        | bandwidth and (b) a 70-GHz IJLO with a 10-GHz total bandwidth                   | .77 |

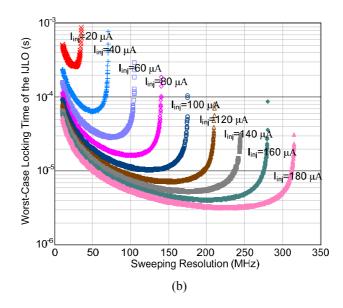

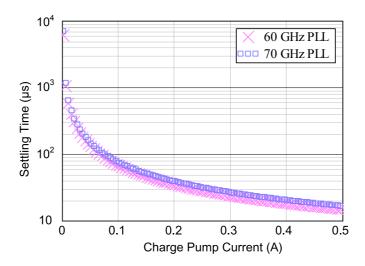

| _      | 4.14 Settling times of 60-GHz and 70-GHz PLLs as a function of bias curre       |     |

|        | of charge pumps.                                                                |     |

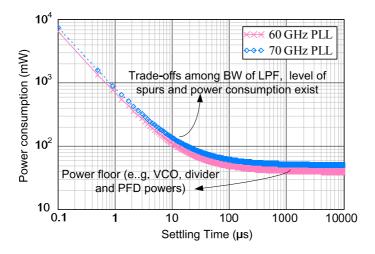

| Fig. 4 | 4.15 Power consumption of 60-GHz and 70-GHz PLLs                                | .78 |

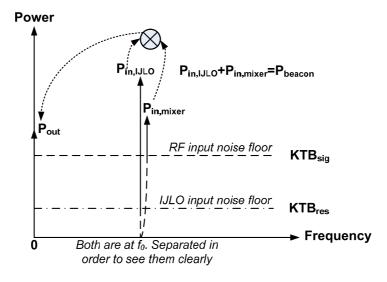

| _      | 4.16 Illustration of the sensitivity of the WuRx.                               |     |

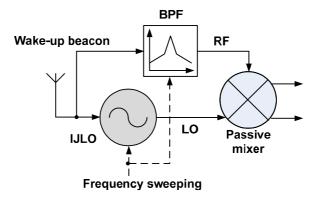

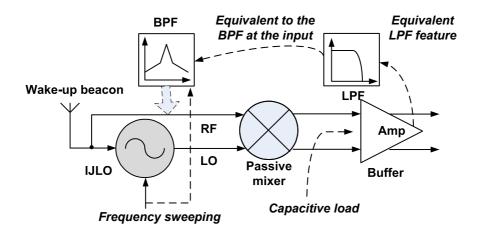

| Fig. 4 | 4.17 A tunable BPF-first WuRx                                                   | .79 |

| Fig. 4 | 4.18 The WuRx with an LPF at its output.                                        | 80  |

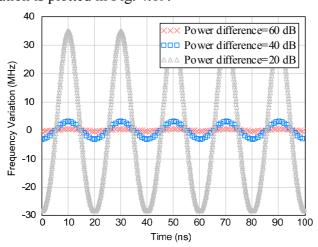

| _      | 4.19 The IJLO frequency variation under the influence of the interferer         |     |

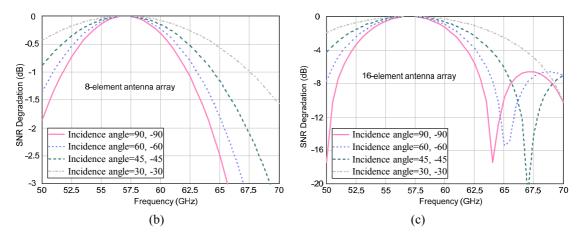

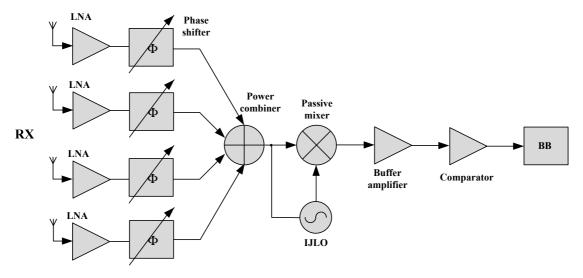

| _      | 4.20 AoA algorithm.                                                             |     |

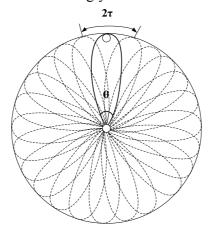

| _      | 4.21 Beam scanning process.                                                     |     |

| _      | 4.22 The number of scanning as a function of the antenna number                 |     |

| _      | 4.23 The normalized optimized average power level as a function of the anter    |     |

|        | number and the average event frequency of (a) the 60-GHz system and (b)         |     |

|        | W-Band system.                                                                  |     |

|        | 4.24 Overall phase error when errors are present in each path                   |     |

| _      | 5.1 Rendezvous schemes.                                                         |     |

| _      | 5.2 Classifications and trade-offs of WuRxs.                                    |     |

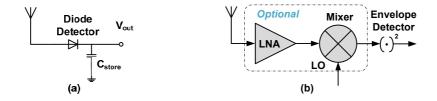

| _      | 5.3 Conceptual models of (a) a passive diode detector and (b) an act            |     |

|        | envelope detector.                                                              |     |

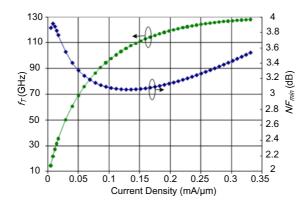

| _      | 5.4 The simulated $f_T$ and $NF_{min}$ curves of the TSMC 65-nm LVT NMOS        |     |

|        | transistor                                                                      |     |

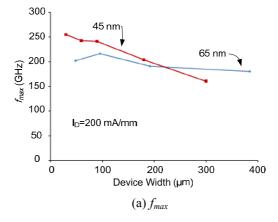

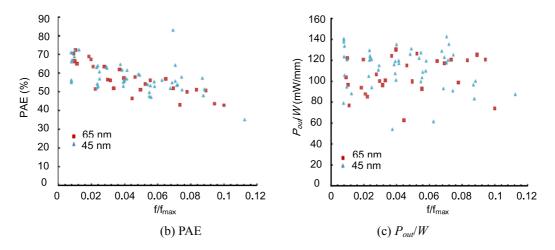

| Fig. : | 5.5 The performance comparison of 45-nm and 65-nm technologies                  | 97  |

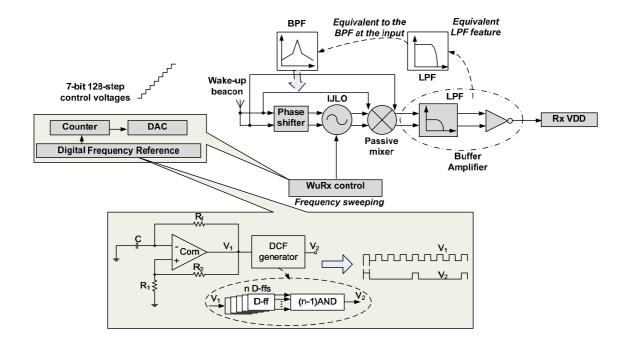

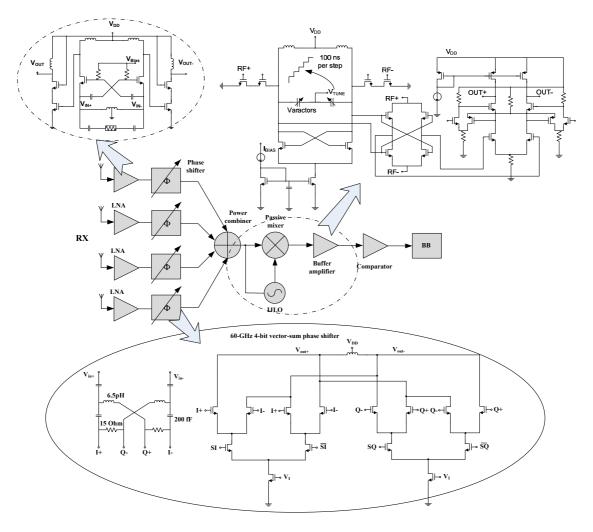

| Fig. | 5.6 The IJLO-based WuRx. 100                                                                                                                                       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. | 5.7 Conceptual models of (a) the conventional envelope detector and (b) the                                                                                        |

|      | IJLO-based linear self-mixing detector. 101                                                                                                                        |

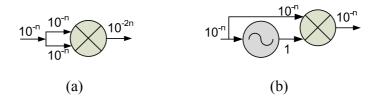

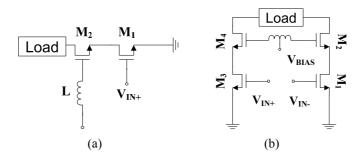

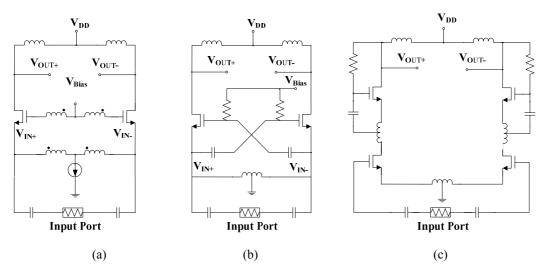

| Fig. | 5.8 Conceptual models of (a) a common-gate Colpitts oscillator, (b) a                                                                                              |

|      | common-source Colpitts oscillator and (c) a cross-coupled LC oscillator 103                                                                                        |

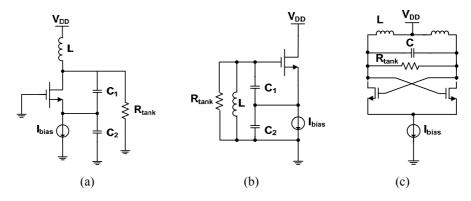

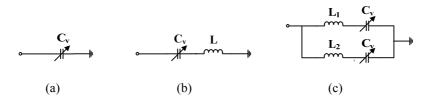

| Fig. | 5.9 (a) The active inductor tuning, (b) variable capacitor tuning and (c) Clapp                                                                                    |

|      | oscillator scheme. 104                                                                                                                                             |

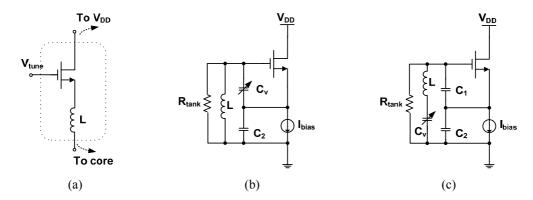

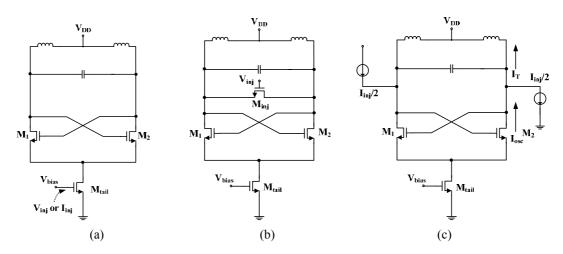

| Fig. | 5.10 (a) Tail injection in voltage or current mode; (b) direct voltage mode injection and (c) direct current mode injection                                        |

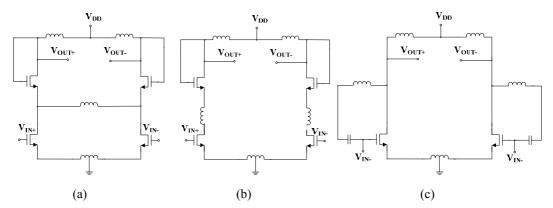

| Fig  | 5.11 (a) The current-reuse cascode input buffer and (b) its differential version                                                                                   |

| rig. | • • • • • • • • • • • • • • • • • • • •                                                                                                                            |

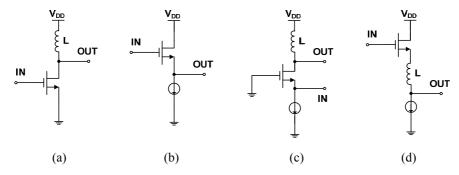

| Eic  | 5.12 (a) The common-source buffer, (b) the common-drain buffer, (c) the                                                                                            |

| rig. | common-gate buffer and (d) the inductor-enhanced common-drain buffer 108                                                                                           |

| Fig  | 5.13 The inductive behavior of a common drain buffer when driven by a                                                                                              |

| rig. | •                                                                                                                                                                  |

| Eic  | relatively large impedance. 109                                                                                                                                    |

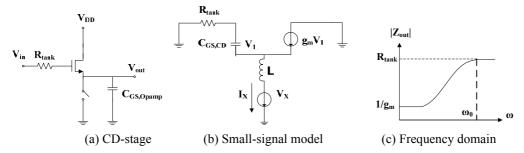

| гıg. | 5.14 (a) The quality factor of the varactor and (b) the overall quality factor with all parasitic capacitances, buffer influence and interconnection imperfections |

|      |                                                                                                                                                                    |

| Ei~  | included                                                                                                                                                           |

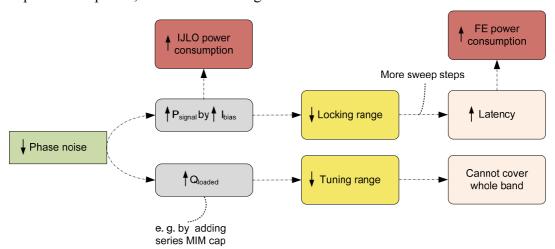

| _    | 5.15 The trade-offs involved in the design of the IJLO.                                                                                                            |

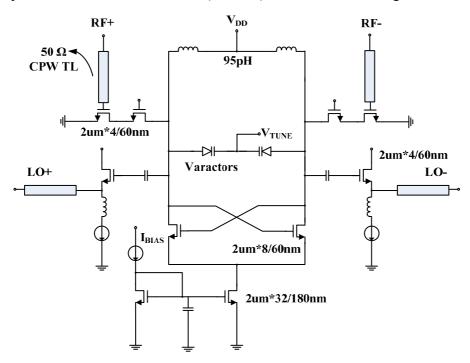

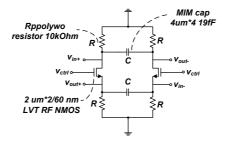

| _    | 5.16 The 73 to 83 GHz IJLO in TSMC 65-nm CMOS technology                                                                                                           |

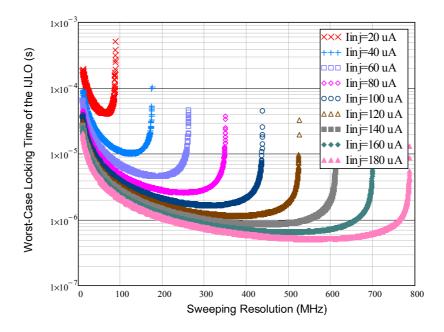

| Fig. | 5.17 The worst-case locking time as a function of the sweep resolution and the                                                                                     |

|      | injection current strength. It should be noted that $\omega_{res}$ is divided by $2\pi$ and                                                                        |

| Ei.  | transferred into $f_{res}$ as the X-axis.                                                                                                                          |

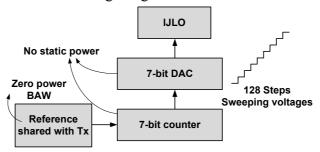

| _    | 5.18 Diagram of the 7-bit low-power sweep voltage generator                                                                                                        |

| _    | 5.19 The schematic of the 128-step low-power sweep-voltage generator 116                                                                                           |

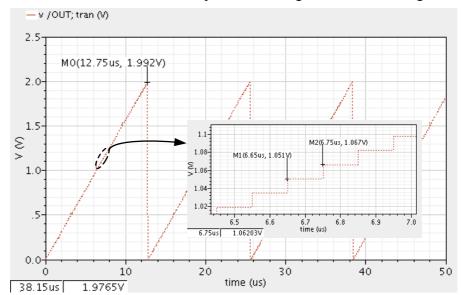

| _    | 5.20 The 7-bit digital control voltages. 117                                                                                                                       |

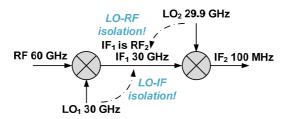

| _    | 5.21 The LO-IF and LO-RF isolations in a superheterodyne system                                                                                                    |

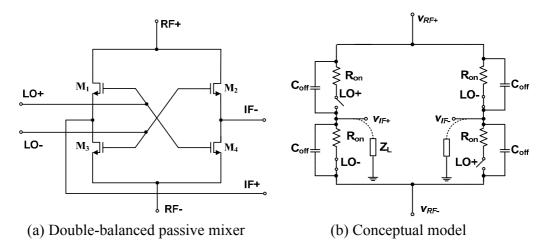

| Fig. | 5.22 The schematic and conceptual model of a double-balanced passive mixer.                                                                                        |

| Eic  | 5.22 The gain heasted buffer amplifier 120                                                                                                                         |

| _    | 5.23 The gain-boosted buffer amplifier                                                                                                                             |

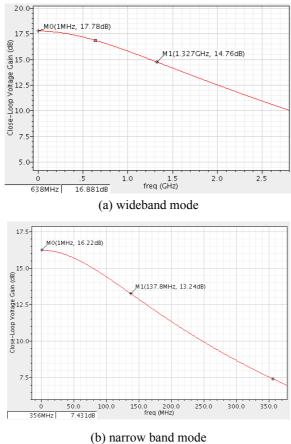

|      | 5.24 The AC-responses of the output buffer. 121                                                                                                                    |

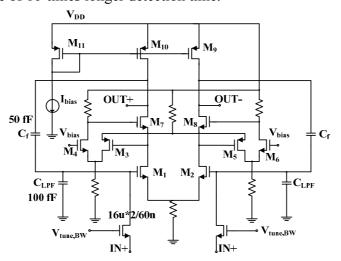

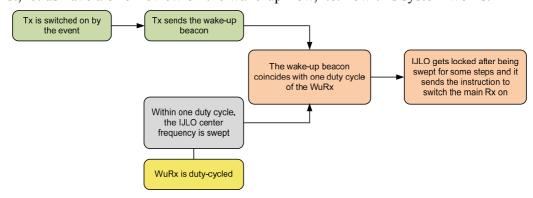

| •    | 5.25 The wake-up process                                                                                                                                           |

| _    | 5.26 The W-band WuRx circuit.                                                                                                                                      |

| _    | 5.27 The RC zero-biased all-pass phase shifter. 126                                                                                                                |

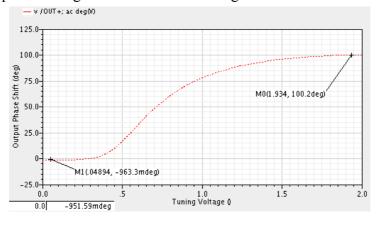

| _    | 5.28 The phase shift range of the RC phase shifter                                                                                                                 |

| _    | 5.29 The updated system diagram.                                                                                                                                   |

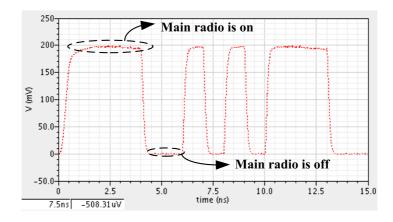

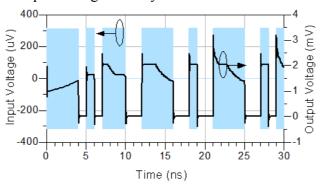

| Fig. | 5.30 The output signals of the WuRx (open load): random RF amplitudes are                                                                                          |

|      | used to test the speed of the wake up process. The output signal of the IJLO and                                                                                   |

|      | the RF signal are tuned in phase in this simulation                                                                                                                |

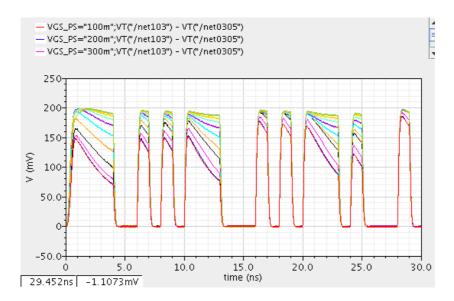

| Fig 5.31 The influence of the phase shift.                                                | .128  |

|-------------------------------------------------------------------------------------------|-------|

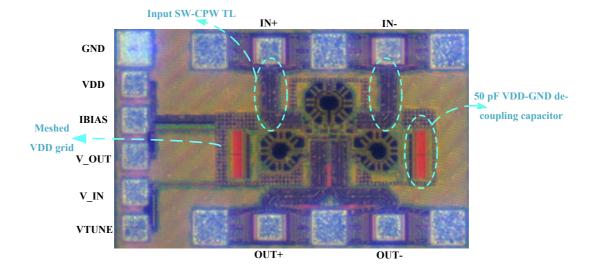

| Fig. 5.32 Chip photo of the IJLO.                                                         | .129  |

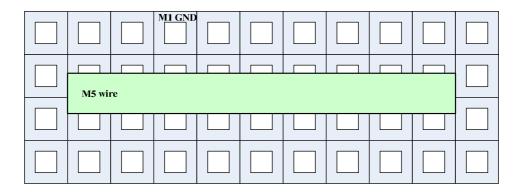

| Fig. 5.33 The meshed ground plane                                                         | .129  |

| Fig. 5.34 The 70 to 80 GHz signal generation mechanism.                                   | .130  |

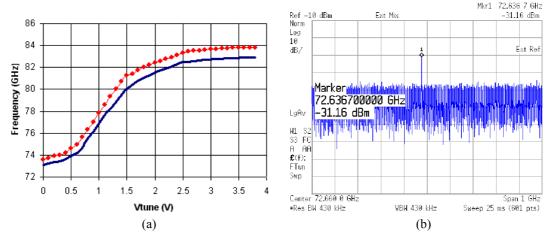

| Fig. 5.35 (a) the tuning range of the IJLO and (b) output spectrum (not de-embed          | dded) |

|                                                                                           | .130  |

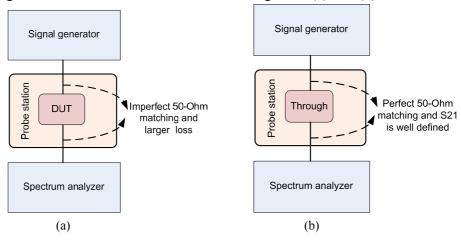

| Fig. 5.36 The comparison between (a) losses in the real DUT measurer                      | nent  |

| peripherals and (b) actually measured using a "through" structure                         | .131  |

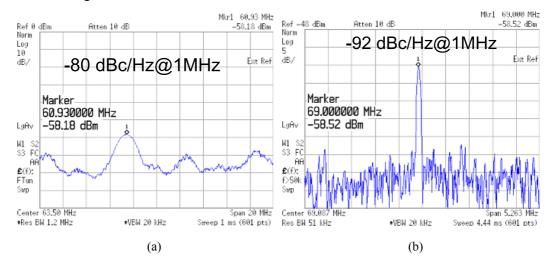

| Fig. 5.37 The measurement results of the standalone IJLO: (a) free-running and            | d (b) |

| locked at the edge of one single-step locking range.                                      | .132  |

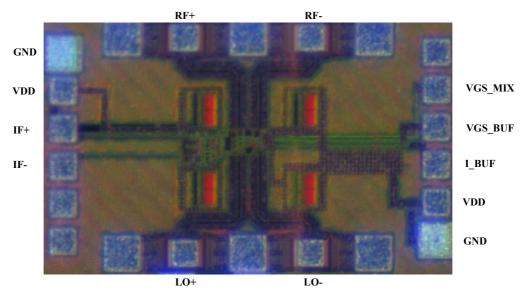

| Fig. 5.38 The chip photo of the passive mixer.                                            | .133  |

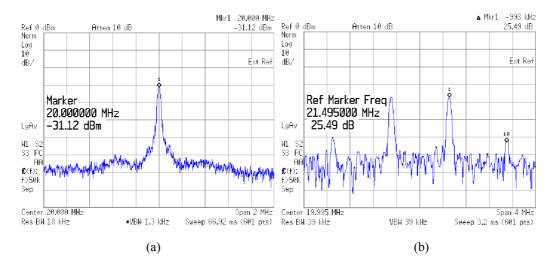

| Fig. 5.39 (a) The output spectrum of the mixer and (b) the two-tone test spectrum         |       |

|                                                                                           | .134  |

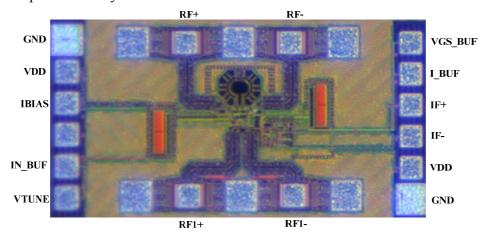

| Fig. 5.40 The chip photo of the W-Band WuRx.                                              | .134  |

| Fig. 5.41 The output spectra of the WuRx (a) free-running and (b) locked                  | .135  |

| Fig. 5.42 The complete W-band low-power WuRx system.                                      | .137  |

| Fig. 6.1 Basic architecture of a beamforming transceiver array.                           | .142  |

| Fig. 6.2 Benefits of beamforming array.                                                   | .143  |

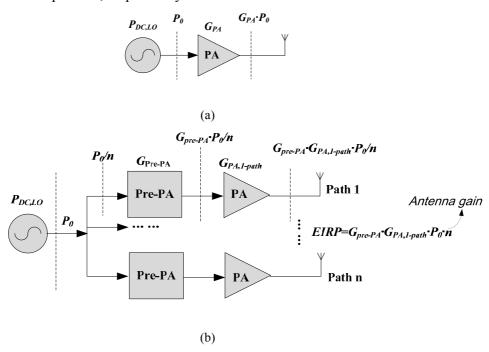

| Fig. 6.3 The power budget illustrations of (a) a single-path Tx and (b) an <i>n</i> -path | ı Tx. |

| The pre-PA stage refers to the overall effect of other blocks like the d                  | lelay |

| element or PA drivers that are exclusively required in the <i>n</i> -path Tx array        | .144  |

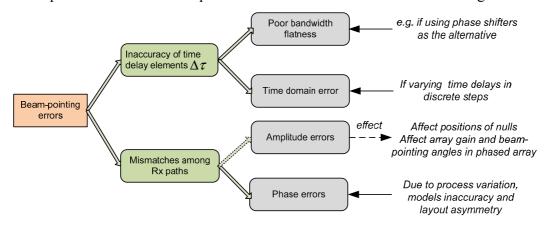

| Fig. 6.4 Potential causes of beam-pointing errors.                                        | .146  |

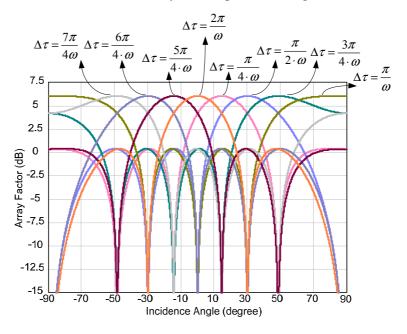

| Fig. 6.5 Array factor of a 4-element antenna array at 57 GHz. Similar figure ca           | n be  |

| obtained at all frequency points in the 60 GHz band                                       | .147  |

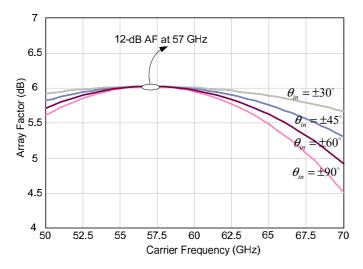

| Fig. 6.6 Frequency behavior of AF of a 4-path phased array with unit phase                | shift |

| target at 57 GHz                                                                          | .148  |

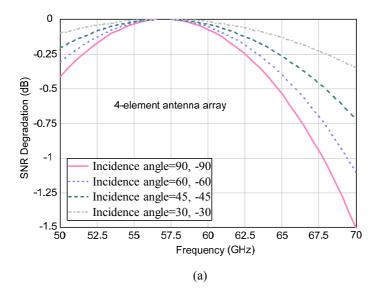

| Fig. 6.7 SNR degradation of a (a) 4-element array, (b) 8-element array and                | (c)   |

| 16-element array due to using of phase shifters.                                          |       |

| Fig. 6.8 SNR degradation due to discrete phase shifting in a 4-element phased a           | rray. |

|                                                                                           | .150  |

| Fig. 6.9 A 4-element phased array self-demodulating Rx.                                   |       |

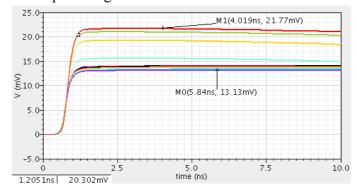

| Fig. 6.10 Input and output signal amplitudes simulated in ADS.                            | .153  |

| Fig. 6.11 Black-box optimization model.                                                   | .157  |

| Fig. 6.12 LNA input stage: (a) (b) gm-boosted; (c) current-reused                         | .158  |

| Fig. 6.13 LNA second stage: (a) middle inductor shunt peaking; (b) artif                  | icial |

| transmission line based inter-stage matching; (c) shunt inductor b                        |       |

| neutralization on miller effect.                                                          |       |

| Fig. 6.14 Typical phase shifters.                                                         |       |

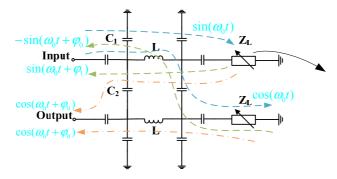

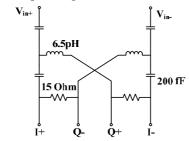

| Fig. 6.15 The reflection type phase shifter using lumped elements.                        | .163  |

| Fig. 6.16 Typical refection load configurations: (a) Capacitive load (CL); (b)     |

|------------------------------------------------------------------------------------|

| resonating load (RL) and (c) dual resonating load (DRL)                            |

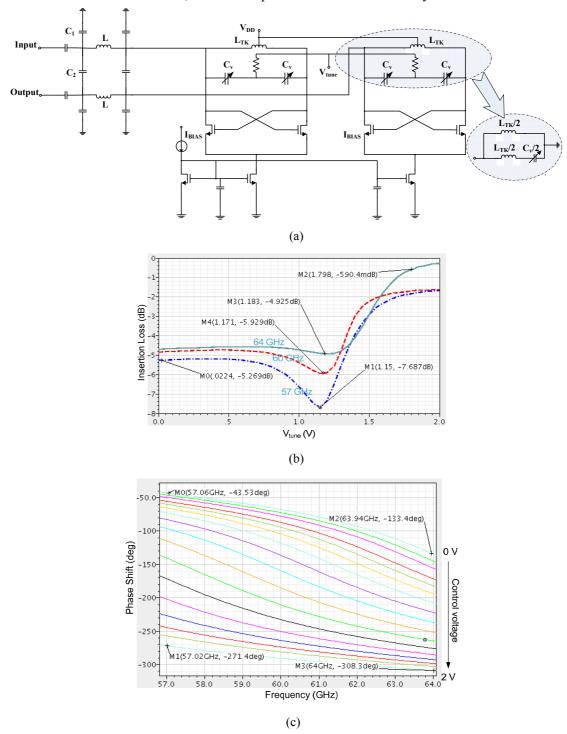

| Fig. 6.17 (a) RTPS with negative resistance loss compensation loads, and RTPS      |

| performance of (b) Insertion loss at 57 GHz, 60 GHz and 64 GHz and (c) Phase       |

| shift for different control voltages (calibration is not done)                     |

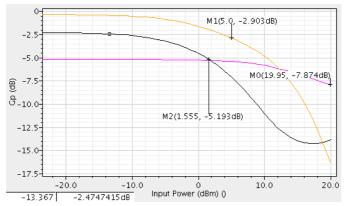

| Fig. 6.18 $P_{-1dB,in}$ of the RTPS with different control voltages (at 60 GHz)    |

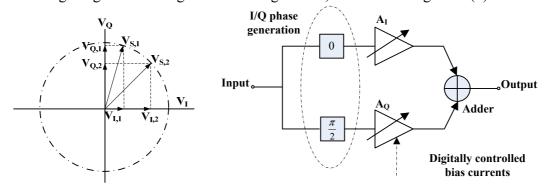

| Fig. 6.19 (a) Concept and (b) architecture of a vector-sum type phase shifter 166  |

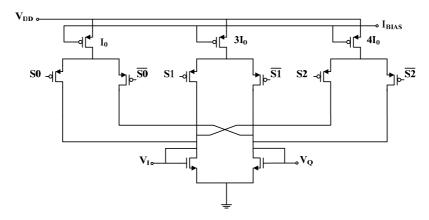

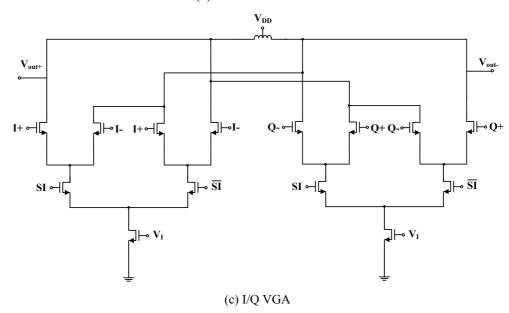

| Fig. 6.20 Schematic of a 4-bit 60-GHz vector-sum type phase shifter                |

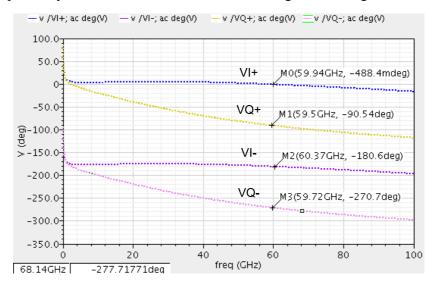

| Fig. 6.21 I/Q phases                                                               |

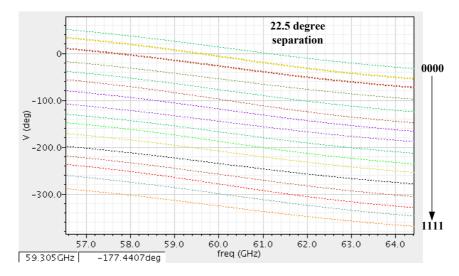

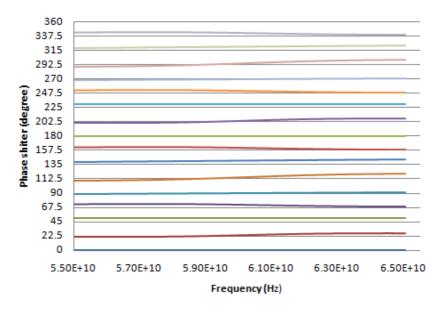

| Fig. 6.22 Insertion phases (deg)                                                   |

| Fig. 6.23 Relative phase shifts of different settings                              |

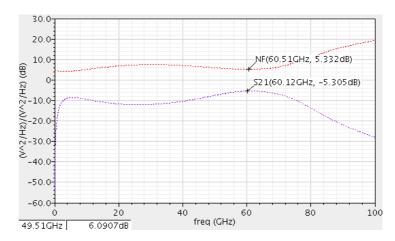

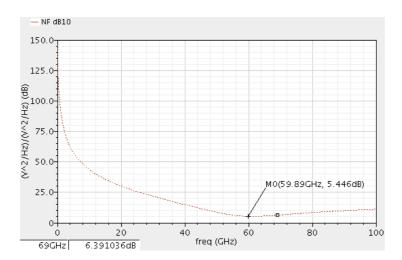

| Fig. 6.24 $S_{21}$ and NF of the stand-alone I/Q generation network                |

| Fig. 6.25 S-parameters of the stand-alone adder                                    |

| Fig. 6.26 NF of the stand-alone adder                                              |

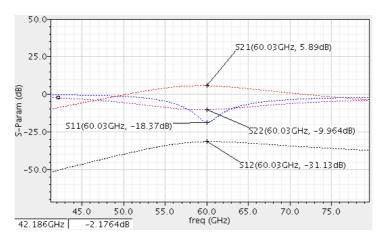

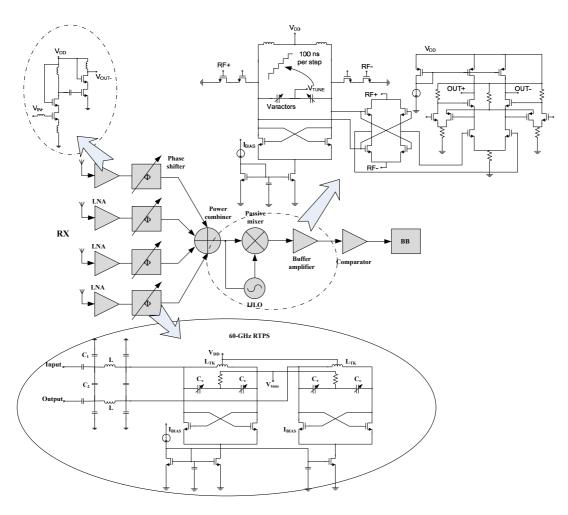

| Fig. 6.27 Schematic of a 4-element phased array Rx based on the reflection-type    |

| phase shifters                                                                     |

| Fig. 6.28 Output signal amplitude variations under different phase settings (input |

| power is -60 dBm and its output terminals are connected to 50-Ohm loads by         |

| adding source follower output buffers)                                             |

| Fig. 6.29 Schematic of a 4-element phased array Rx based on vector-sum-type phase  |

| shifters. 172                                                                      |

# LIST OF TABLES

| Table 1.1 Regional Spectrum allocations and EIRP constrain of 60 GHz bar | 1ds8 |

|--------------------------------------------------------------------------|------|

| Table 2.1 Review of State-of-the-Art WuRxs                               | 18   |

| Table 3.1 The optimum relay nodes number                                 | 50   |

| Table 4.1 Power densities of the energy harvesting methods               | 60   |

| Table 4.2 The performance of 60-GHz front ends and RF blocks             | 64   |

| Table 4.3 Summary of the WuRx performance enhancement methods            | 81   |

| Table 5.1 Challenges and possible solutions of mmW WuRxs                 | 95   |

| Table 5.2 Link budget parameters of the 60-GHz and 70-GHz channels       | 98   |

| Table 5.3 Specifications for mmW WuRxs                                   | 99   |

| Table 5.4 Performance comparison of three types of oscillators           | 105  |

| Table 5.5 The comparison of output buffers for the 70-GHz IJLO           | 108  |

| Table 5.6 Simulated capacitance distribution in the 70-GHz IJLO          | 110  |

| Table 5.7 Three methods for phase compensation                           | 125  |

| Table 5.8 The performance comparison of IJLOs                            | 132  |

| Table 5.9 Measurement results of the WuRx                                | 136  |

| Table 6.1 Comparison of different phase shifting positions               | 151  |

| Table 6.2 LNA performance comparison                                     | 160  |

| Table 6.3 Comparisons of several well-known RF phase shifters            | 161  |

#### LIST OF ABBREVIATIONS

ACK Acknowledgement

ADC Analog-to-digital convertors

AF Array factor

AoA Angle-of-arrival

BAN Body-area network

BER Bit-error-rate

BPF Band-pass filter

BW Bandwidth

CA Collision avoidance

CIR Carrier-to-interference ratio

CSMA/CA Carrier sense multiple access with collision avoidance

DAC Digital-to-analog convertor

DCF Duty cycle factor

DO Directional to omni-directional

DRL Dual resonated load

EIRP Equivalent isotropic radiation power

EVM Error vector magnitude

FCC Federal Communications Commission

FOM Figure-of-merit

GaAs Gallium Arsenide

IC Integrated circuit

IIP3 Input-referred third-order intercept point

IJLO Injection-locked oscillator

IMEC Inter-Universitair Micro-Electronica Centrum

InP Indium Phospide

IR-UWB Impulse-radio ultra-wideband ISI Inter-symbol interference

ISM Industrial, scientific and medical

LNA Low-noise amplifier

LO Local oscillator

LoS Line-of-sight

LR-WPAN Low-rate wireless personal-area network

MAC Media access control

MB-OFDM Multiband orthogonal frequency-division multiplexing

mmW Millimeter-wave NF Noise figure

OOK On-off-keying

P2P Point-to-point

PA Power amplifier

PAE Power-added efficiency

PEIF Power efficiency improvement factor

PL Pathloss

PLL Phase-locked-loop

PSK Phase-shift-keying

QoE Quality-of-experience

QoS Quality of service

RFID Radio-frequency identification RTPS Reflection type phase shifter

Rx Receiver

SiGe Silicon Germanium SNR Signal-to-noise ratio

SR Short-range

SW-CPW Slow-wave coplanar waveguide

TL Transmission lines

Tx Transmitter

VCO Voltage-controlled oscillator

VGA Viable-gain amplifier

Wi-Fi Wireless fidelity

WiGig Wireless gigabit

WLAN Wireless local-area network

WuRx Wake-up receiver

#### LIST OF SYMBOLS

В Bandwidth

Instantaneous bandwidth  $B_{inst}$ Effective bandwidth  $B_{eff}$ CChannel capacity Antenna directivity  $D_{ant}$

$E_{ave,corr}$ Average energy per bit of correctly received bits

$E_b$ Energy transmission per bit Energy consumption per bit  $E_{bit}$

FNoise factor f Frequency  $G_{ant}$ Antenna gain Transconductance  $g_m$ Antenna gain of the Tx  $G_{Tx}$  $G_{Rx}$ Antenna gain of the Rx  $G_{TRx}$ Total antenna gain Injection current  $I_{ini}$ Oscillation current  $I_{osc}$  $L_{pkt}$ Packet length Electronics factor  $k_e$ Technology factor  $k_{Tech}$ Event frequency

$P_{b,Tx,DC}$ Power consumption of the wake-up beacon generation

$P_{DC.tot}$ Total power consumption of the entire front end

PLPath loss

nevent

$P_{LO,DC}$ Power consumption of an LO

Output power of a Tx  $P_{out}$  $P_{pr,DC}$ Pre-receiving power

$P_{Rx,DC}$ Power consumption of a Rx

$P_{Rx,DC,n-path}$ Power consumption of an *n*-element phased array Rx front end

$P_{Tx,DC}$ Power consumption of a Tx

Power consumption of an *n*-element phased array Tx front end  $P_{Tx,DC,n-path}$ Total Power consumption of an *n*-element phased array front end  $P_{TRx,DC,n-path}$

Power consumption of a wake-up receiver  $P_{WuRx,DC}$

Quality factor Q R Data rate

$R_{effect}$ Effective data rate

#### XIV

$R_{raw}$  Raw data rate

S Receiver sensitivity

$S_{WuRx}$  Wake-up receiver sensitivity  $SNR_{in}$  Input signal to noise ratio  $SNR_{out}$  Output signal to noise ratio

$T_{DC}$  Active time of one cycle of a wake-up receiver

$t_{Rx,overhead}$  Packet overhead  $t_{settling}$  Total settling time  $T_{tot}$  Total observe time

$T_{wu}$  Active time of one cycle of a duty-cycled wake-up receiver

$\alpha$  Conduction angle of a PA  $\theta_m$  Beam-pointing angle

$\theta_{ss}$  Steady-state phase difference

$\kappa$  Power-linearity factor

$\lambda$  Wave length

$\eta_{PA}$  Efficiency of a PA

$\eta_{Tx}$  Efficiency of a transmitter  $\omega_{inj}$  Injection signal frequency  $\omega_0$  Free oscillation frequency

$\omega_L$  Locking range of an injection locked oscillator

$\omega_{res}$  Frequency sweep resolution (sweep step)

#### CHAPTER 1 INTRODUCTION

## 1.1 Background

Thanks to Moore's law, capabilities of integrated circuits (IC) have been improving exponentially in the past decades. The size of transistors has consistently shrunk, and the speed, which is normally described by the cut-off frequency  $f_T$ , is doubled about every two years [1]. Along with technology progress and rapid development of wireless technologies, the wireless communication market has been growing explosively and various consumer electronics products have been developed accordingly<sup>1</sup>, such as Bluetooth earphone and wireless gaming consoles. In today's market of interest, two types of prevalent applications can be distinguished: low-power and high-speed wireless communications. In the first category, most of the systems are relatively low frequency, low rate and low cost. For example, as regulated in the IEEE 802.15.4 low-rate wireless personal-area network (LR-WPAN) standard, Zigbee systems can provide low-cost and low-power wireless connections for equipment that requires battery life as long as several months to several years. Its maximum raw data rate is only 250 kbps at 2.4 GHz [2]. Quite on the contrary, the second category targets at high-speed communications for massive data transferring. This type of communication systems tends to offer wireless connections for short-range (SR) personal data transfer, which is also known as the last-meter problem. The IEEE 802.15.3c task group has worked on a 60-GHz WPAN standard that is able to provide a data rate as high as at least 1 Gbps for short-range video streaming and high-speed downloading [3]. Unsurprisingly, the power dissipation of such systems would easily reach a level of tens to hundreds of milliwatts [4].

There are also some wireless systems that are in between of those two categories, e.g. Bluetooth systems (IEEE 802.15.1), and wireless local-area networks (WLAN, IEEE 802.11 standards family)<sup>2</sup>. However, a trend of data rate increase has been observed in these standards. For instance, the maximum data rate is extended from 11 Mbps of IEEE 802.11.b to 150 Mbps of IEEE 802.11.n [5]. In 2010, wireless gigabit (WiGig) alliance has published a tri-band (2.4 GHz, 5 GHz and 60 GHz) system that commercializes the

<sup>&</sup>lt;sup>1</sup> Although the performance improvement of wireless radios lags behind the digital basebands that are predicted by Moore's law, rapid progress can be observed in improvement of the entire system.

<sup>&</sup>lt;sup>2</sup> In fact, it is not very reasonable to compare WPAN and WLAN systems due to their different applications and requirements like range and mobility. However, there is a very interesting phenomenon that along with increasing of data rate and particularly emerging of WiGig, their definitions seem to be blurred and thus can be compared to some extent.

60 GHz band for indoor personal communications and wireless fidelity (Wi-Fi) applications. It is able to provide up to 7 Gbps data rate and is backward compatible to 802.11 standards. Its applications include wireless synchronization, wireless display, cordless computing and internet access. New scheduled access mode to reduce power consumption is also included in WiGig systems [6].

Some IC designers believe that for given applications and physical constraints (e.g. certain communication quality of service (QoS), range, and IC technology level, etc.), high data rate always results in high power dissipation. However, the application-driven market apparently does not agree with that. There is an increasing demand for a solution to achieve high speed and low power of communications simultaneously, so that people can transmit large files with very low power dissipation<sup>3</sup> and in a short time (e.g. several seconds). One of the most important applications is point-to-point (P2P) data links, as shown in Fig. 1.1.

Fig. 1.1 Wireless P2P commutation.

According to Shannon's theory, some efforts have been made by investigating broadband solutions, such as the impulse-radio ultra-wideband (IR-UWB) system. In principle, if the bandwidth is sufficiently wide, it can support high data rate communication with very low RF power density. This field has gained momentum since Federal Communications Commission (FCC) regulations allowing unlicensed communication using the 3.1 to 10.6 GHz frequency band in 2002 [7]. However, due to the inherent low immunity to noise and interference, difficulties to capture multi-path energy, high power dissipation of high-speed analog-to-digital converters (ADC), coexistence problems, and difficulties in

-

<sup>&</sup>lt;sup>3</sup> It usually refers to the average power dissipation level which determines battery life or suitability of energy scavenging technologies.

receiver design (particularly, synchronization issues), this type of systems still cannot fulfill the job as a low power and high speed solution at this moment. For instance, multiband orthogonal frequency-division multiplexing (MB-OFDM) UWB systems are announced by WiMedia Alliance, which are able to provide 480 Mbps maximum data rate [8]. However, it still has co-existence problems with wireless systems below 10 GHz. Besides that, the transmit power density is stringently limited below -41.3 dBm/Hz, which limits the signal-to-noise ratio (SNR) level and therefore degrades the design flexibility of such systems.

## 1.2 Research objectives

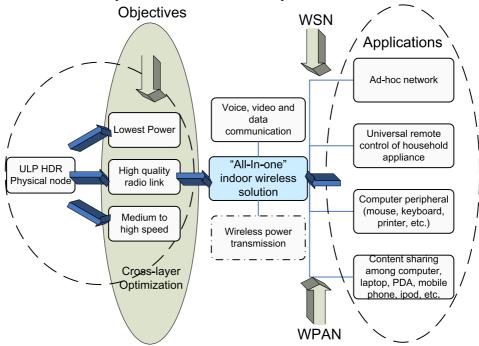

The primary goals of this work are to investigate and propose a new type of wireless system solution which is able to support high data rate communication with low power consumption (as illustrated in Fig. 1.2), and to provide circuit-level designs and implementations to verify the effectiveness of the system.

Fig. 1.2 Research objectives and potential applications.

Efforts will be made but not be limited to:

- Investigating trade-offs among PHY-layer parameters and identifying optimum frequency bands and key techniques that fundamentally enable high energy efficiency communication.

- ➤ Identifying the suitability of high data rate communication in a rendezvous system

- and finding out the optimum data rate level with respect to different application requirements.

- > Cross-layer analyses and optimizations towards low average power consumption. Some potential medium access control (MAC) and network methods are discussed in order to achieve overall power optimization.

- ➤ Proposing a suitable power management scheme that is compatible with highdata-rate systems based on above results. The overall goal is to minimize average power consumption on system level.

- ➤ Design and optimization of system architectures based on link budget model, application requirements as well as the system-level optimization results.

- Circuit designs of key blocks of the proposed system.

- ➤ Implementation and characterization of key blocks to verify the new concepts and system design.

# 1.3 Challenges and research method

This thesis aims at providing generic system solutions for ultra-low power and high-speed personal communications. Besides, key blocks will be designed, implemented and characterized in order to verify new concepts, system architectures and circuit theories. Compared with those design-oriented projects that mainly focus on limited aspects or sub-blocks of a large system, this work is arranged in a top-down manner: i.e. starting from very broad high-level practical issues, going down to realization of a feasible physical system, and then down to the detailed designs and implementations. Innovations are made on aspects where problems are encountered and identified. Results will be cross-checked iteratively in order to maintain the overall targets of design and optimization. Potential research challenges can be classified as flows:

#### A. Challenges during cross-layer optimization

According to the wooden barrel theory<sup>4</sup>, the overall performance of a complicated system is usually determined or limited by its weakest chain. As a result, a cross-layer research scope becomes important. The main necessities include:

➤ Design of a communication system is actually a practice-oriented work. Before solving a specific physical problem, one should make it clear why this problem must be solved and to what extent it should or can be improved. That kind of information

<sup>&</sup>lt;sup>4</sup> A barrel composed of many pieces of wood. If the composition of these pieces vary in length, the maximum capacity of the wooden barrel does not depend on the longest piece of wood, but on the shortest one [8].

- is normally given by higher levels of a communication system instead of merely PHY-layer parameters.

- Some detailed problems like power consumption reduction or interference alleviation of a communication system can only be optimally solved through cross-layer cooperation. It does not mean that one cannot "solve" a problem by only looking into one specific layer of the communication model, but if doing so, a global optimization will not be guaranteed. Cross-layer trade-offs have to be concerned during the process of solving a practical problem.

- In principle, by knowing relevant figure-of-merits (FOMs) and state-of-the-art benchmarks of certain IC technologies, the boundary conditions (or some values close to these) of a circuit block can be obtained. Trade-offs and transforms can then be made accordingly in order to optimize this block with regard to certain aspects such as power consumption, linearity and noise. However, considering the entire communication system, FOMs or proper benchmarks are hard to obtain due to disparate applications. Approaching physical boundary conditions (e.g. minimum noise figure or power) of each block does not necessarily lead to the overall optimum of the entire system. As a result, a cross-layer view is also required to guide or check the physical systems and circuits design.

When realizing a cross-layer optimization, however, it turns out to be quite a challenging work, because:

- The degree of optimization is determined not only by the complexity of the system, or the degree of difficulty of research questions, but it is limited by the knowledge of designers as well, because a designer is normally specialized in limited fields. As a result, in practice, the cross-layer optimization process has different weights for each layer depending on the designer's own preference. In this thesis, the PHY-layer systems and circuit realization and optimization are our focused aspects. Some higher-layer parameters are not involved in the optimization process but just assumed within a reasonable range.

- It is usually difficult and nontrivial to achieve an ultimate optimization. In order to reduce complexity while keeping in-depth analyses over certain essential aspects, the scope of the research work should be limited to a reasonable and controllable range. Therefore, only the most direct cross-layer parameters will be considered during the optimization flow and others will be assigned as assumptions or prerequisites. This activity will reduce the design complexity and number of iterations significantly at the expense of optimization degree. For instance, in our 60-GHz phased array system, line-of-sight (LoS) communication is assumed at the first place, because: (i) in the network layer, a short-range (less than 1-meter relay distance) ad hoc topology and a multi-hop routing method are assumed; (ii) in the chosen MAC power management

scheme, the radio operates in a high-speed burst-mode rendezvous manner, and it will be shut off immediately when communication is done; (iii) with a narrow beamwidth of the array and a directional communication method, diffraction, refraction and reflection phenomena are less serious. As a result, in the link budget calculation, the path loss index is taken as 2, i.e. as the free-space case.

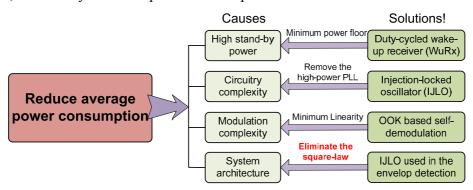

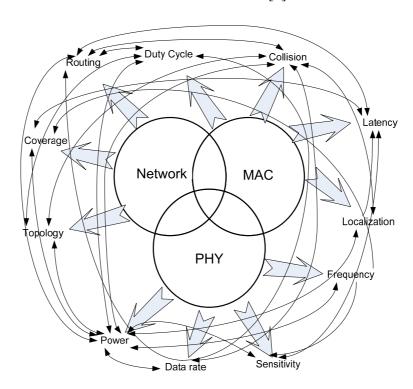

#### B. Challenges due to lack of methodology

Design and optimization within one specific layer of the communication model is complicated and iterative, too. For instance, as shown in Fig. 1.3, in order to minimize the overall average power consumption of a system, different aspects have to be considered, and innovations may be required in each aspect (details will be specified later in following chapters), but sometimes they may conflict with each other. For example, compared to digital binary amplitude modulation schemes like on-off-keying (OOK), phase-shift-keying (PSK) scheme requires a lower signal-to-noise ratio per bit ( $E_b/N_0$ ) for a given bit-error-rate (BER). Consequently, with the same data rate and receiver (Rx) noise figure (NF), the PSK system requires less output power of the transmitter (Tx) in order to maintain the same communication range. Therefore, the Tx power consumption can be reduced. However, the Tx for a PSK system requires a higher level of linearity. As a result, a higher-efficiency non-linear power amplifier (PA) is not allowed to be used in this case, which may cause Tx power consumption increase in the end.

Fig. 1.3 Aspects related to average power consumption reduction of a system.

Situations would get worse when the systems are working at very high frequency, with very high speed or when they must achieve ultra-low power consumption, because in such cases, limits of technology such as the limited cut-off frequency ( $f_T$ ), high noise and high parasitics levels, will be critical and even decisive. A structuralized design and optimization methodology would therefore be very useful to solve this kind of problem. In [9], a minimum-power design methodology is proposed that provides solutions to optimize gain, linearity and noise of a system, and also offers a detailed front-end design procedure. This method will be used during the system architecture design process in this thesis. More details and relevant parameters will be added with regards to real design

problems. Considering system architecture innovations, a new design method (not that generic as [9], but more specific for our designed architecture) will be proposed as well.

#### C. Challenges related to some practical issues

Besides fundamental limitation factors like propagation pathloss at a certain frequency, some practical limitations also hamper performance optimization of a communication system. These practical issues include:

- > Implementation technology. Firstly, it is known that technologies that use III-V compounds, such as Gallium Arsenide (GaAs) and Indium Phospide (InP), normally offer high  $f_T$ , low noise and high speed compared to Silicon based technologies like CMOS. However, due to its high integration level and low cost (per unit), CMOS technology would normally be preferred for mass production and therefore becomes an interesting potential technology for research work as well. Consequently, it is inevitable that the circuits will suffer from poor noise, worse linearity and lower gain (at the same bias level) compared to these III-V technologies [10]. Secondly, trade-offs have to be made when choosing a certain version among different silicon based technologies. For instance, Silicon Germanium (SiGe) technologies would be relatively cheaper than the most advanced CMOS technologies and it is able to offer even better performance. However, it is reported in [11] that the technology development of BiCMOS technology lags about three to four generations behind compared to CMOS technology because of the lack of product drivers in the market. Consequently, it is worth to keep on with the most leading technology, i.e. CMOS for our research at the expense of some performance degradation. Thirdly, in order to achieve high data rate communication, systems normally choose to work at higher frequency bands like the millimeter-wave (mmW) bands due to their wider bandwidth. This would cause potential problem in CMOS technology due to their limited  $f_T$  and maximum available gain of transistors. Along with the downscaling process of CMOS technology, the cut-off frequency continues to increase. For example, the maximum oscillation frequency increased from 200 GHz in 65-nm to 250 GHz in 45-nm CMOS technologies [12]. However, the parasitics level and leakage problems, on the other hand, become more severe. All these imperfections of the implementation technology will degrade the performance of a communication system, especially in high-frequency systems.

- Regulation and standardization

The realization and optimization of a communication system should abide by specific regulations (e.g. regulations of FCC) and be compatible with certain communication protocols as well. For instance, the most achievable system bandwidth and maximum allowed output power of the 60 GHz band is limited as shown in Table 1.1.

| Regions              | Frequency bands (GHz) | Maximum EIRP <sup>5</sup> (dBm) |

|----------------------|-----------------------|---------------------------------|

| US, Canada and Korea | 57-64                 | 43                              |

| Europe and Japan     | 59-66                 | 57                              |

| Australia            | 59.4-62.9             | 51.8                            |

Table 1.1 Regional spectrum allocations and EIRP constraints of 60 GHz bands [11]

Moreover, diverse communication protocols exist. If a certain frequency band is chosen, normally the related standard should be stringently adhered. Otherwise there would be co-existence problems, causing communication failures. For instance, the power spectral density of UWB systems is stringently limited to -41.3 dBm/Hz, and there is no design freedom with this parameter during the system optimization process. For IR-UWB systems, the PHY-layer parameters are well described in IEEE 802.15.4a standard [7]. As a result, the design freedom is relatively reduced.

# 1.4 Scope of the thesis

As discussed in Section 1.3 A, the degree of system optimization will be determined by the author's scope and knowledge, or deliberatively limited for complexity reduction. The main limitations on the scope of this thesis are:

- Cross-layer optimization with emphasis on the PHY-layer. The possibilities and potential solutions of higher layers will be discussed in order to show the feasibility of the proposed physical system. However, the discussions are not in-depth for all aspects, except the closely related ones. A new power management method is provided that suits the most to our physical system. However, the detailed algorithm is not given.

- Generic solution. As a first attempt, this thesis focuses mainly on proving new communication methods and system architectures and focuses on the design of key blocks which are compatible with the proposed communication method and system. As a result, the proposed system is not made to adhere to any communication standard. However, as a short-range, burst-mode, high-speed and directional communication system, it will cause less problems compared to those long-range, always-on, low-rate and omni-directional communication systems in the PHY-layer as long as it does not conflict with existing protocols. On the other hand, for a suitable MAC protocol, more design work will be needed in a next step.

- ➤ Choice of some PHY parameters. In Chapter 3, it is shown that the energy efficiency can be optimized at higher frequency bands with high data rate and directional communication methods. The available candidates include: 60 GHz band, 71 to 76

<sup>&</sup>lt;sup>5</sup> It refers to equivalent isotropic radiated power, i.e. the output power plus antenna gain.

- GHz bands, 81 to 86 GHz, 92 to 95 GHz and even higher industrial, scientific and medical (ISM) bands. However, due to the limitations of the chosen technology, only one or two bands can be chosen for the design of the system and the implementation in circuit level.

- Design methodology. A new method is proposed in this thesis to design a communication system that is able to achieve high speed and low power communication simultaneously. In Chapter 5, a design example is given and the design methodology is summarized. However, due to the complexity of the system, there are too many inputs and optimization factors among all communication layers. As a result, some parameters are fixed as assumptions in our proposed design methodology, which would make it less generic but more specific, e.g. towards particular modulation schemes or specific circuitry. Nevertheless, it can still offer an overall solution with regards to our research question.

- ➤ Limited design cycle. It may also happen that the specific circuits are not fully optimized, because the initial target of designing these circuits like phase shifters and low-noise amplifiers (LNA) is to verify the system design and innovation, but not to push circuits themselves to the level with the most aggressive FOMs. In fact, however, the optimum gain, NF and linearity distribution of each block in a system should follow a way which leads to overall optimization (for example, following the model described in [9]) instead of separate optimization.

- Chosen technology. In this work, the TSMC 65-nm CMOS technology is chosen to implement our proposed system and blocks due to its high integration level, low cost (per unit) and acceptable leakage,  $f_{max}$  and noise level at our system frequencies. However, the systems and designs are not constrained by any particular technology. When shifting to other technologies like III-V ones, no fundamental difficulties or limitations are expected.

# 1.5 Original contributions

The main contributions of the work presented in this thesis include:

A cross-layer power optimization. A new FOM is derived to evaluate the power and communication efficiency of a wireless system. In the PHY-layer, optimum frequency bands for high efficiency communication are identified by analyzing the fundamental relationships among noise, pathloss, antenna gain and frequency. It is shown that by adopting directional antennas, the frequency-induced loss (e.g. pathloss, higher noise, etc.) can be compensated by the frequency induced gain (i.e. higher antenna gain due to better directivity at higher frequency). The optimum peak data rate is identified for the rendezvous and directional communication system. A new MAC power management, i.e. asynchronous duty-cycled wake up scheme is

- proposed especially for our high-speed system in order to minimize its average power consumption. Some network layer issues are discussed as well.

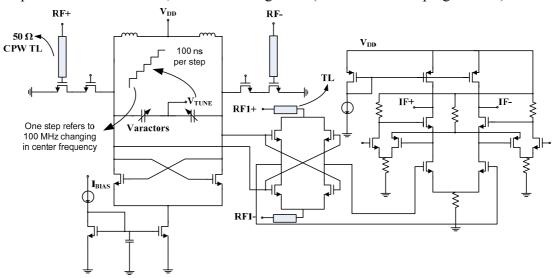

- The complete "wireless wire" system (as discussed in Chapter 4). It is designed and optimized in a hierarchical manner. Key blocks (e.g. the injection-locking oscillator (IJLO)) are identified and discussed by using mathematical models. System level trade-offs are discussed and optimized. The critical trade-off between sensitivity and locking range of an IJLO is solved by using our proposed frequency-sweeping locking method. Its effectiveness is discussed as well.

- ➤ Complete 70-GHz wake-up receiver (WuRx). It is designed and implemented in TSMC 65-nm CMOS technology. Measurement results are provided as well. By adopting our proposed self-mixing demodulation structure, typical high-power blocks like a phase-locked-loop (PLL) and local oscillator (LO) generation module are avoided while the frequency accuracy is not impaired. In such a WuRx, key blocks as IJLO, passive mixer and output buffer amplifier are designed, implemented and tested. The digital control blocks are simulated by using TSMC 65-nm CMOS models.

- Design and simulation of 60-GHz 4-element phased array Rx. A design methodology for a high-frequency power-constrained LNA is provided followed by several design examples of 60-GHz low-power LNAs. Two types of 60-GHz RF phase shifters are designed and simulated, which are able to reach the same performance level (e.g. power consumption, insertion gain and NF) compared to state-of-the-art results in similar technologies. Simulations are done on two versions of the complete Rx chain by adding the self-mixing demodulation module to the phased array Rx.

#### 1.6 Outline of thesis

The state-of-the-art results about low-power Rx architectures, low-power WuRx architectures, and mmW phased array techniques are stated in Chapter 2.

In Chapter 3, the cross-layer power optimization is carried out. Some key PHY parameters are identified towards the maximum power efficiency and minimum average power consumption. The asynchronous duty-cycled wake-up scheme MAC power management method is proposed and compared with other widely used power-efficiency MAC methods. Possible network configurations, routing methods and interference issues are reviewed and discussed.

The complete system architecture is given in Chapter 4. Afterwards, several energy scavenging technologies are discussed and compared. The power optimization models of a multi-element directional communication system are provided. Several system level trade-offs and system mathematical models are analyzed and optimized.

A 70-GHz IJLO-based self-mixing WuRx is shown in Chapter 5. By using the frequency-sweeping locking method, the trade-off between sensitivity and locking range (bandwidth) is converted into the trade-off between sensitivity and circuit sweeping time. Besides, the WuRx sensitivity is also in trade-off with the WuRx detection time. As a result, the WuRx is designed with wideband and narrowband modes. The former is used in situations that require fast response of the WuRx, and the latter is used when the sensitivity is the ultimate important factor, e.g. when the communication range is large.

Two versions of 60-GHz phased array Rxs are designed and simulated in Chapter 6. The main work includes: design and simulations of the 60-GHz LNAs, the 60-GHz low-loss reflection-type RF phase shifter, the 60-GHz 4-bit vector-sum type phase shifter and the complete Rx chains.

Last but not least, conclusions and recommendations are given in Chapter 7.

#### References

- [1] Moore's Law, www.wikipedia.org, 2011.

- [2] IEEE 802.15 WPAN Task Group 4 (TG4), Low Rate Alternative PHY, 2011.

- [3] IEEE 802.15 WPAN Task Group 3c (TG3c), Millimeter Wave Alternative PHY, 2009.

- [4] Yikun Yu, Design Methods for 60GHz Beamformers in CMOS, PhD dissertations, Eindhoven University of technology, 2010.

- [5] IEEE 802.11, www.wikipedia.com.

- [6] Wireless Gigabit Alliance, WiGig White Paper defining the future of Multi-gigabit Wireless Communications, www.wigig.org, 2010.

- [7] IEEE 802.15.4a WPAN Task Group 4a (TG4a), Low Rate Alternative PHY for WPANs, 2011.

- [8] Liu Huabo et al., "The Barrel Theory Based Decision-making Algorithm and Its Application," in 2009 International Conference on Computational Intelligence and Natural Computing, China, 2009.

- [9] Peter Baltus, *Minimum Power Design of RF Front Ends*, PhD dissertations, Eindhoven University of technology, 2004.

- [10] Hammad Mehmood Cheema, Flexible Phase-Locked Loops and Millimeter Wave PLL Components for 60-GHz Wireless Networks in CMOS, PhD dissertations, Eindhoven University of technology, 2010.

- [11] Radio Frequency and Analog/Mixed-Signal Technologies for Wireless Communications, *International Technology Roadmap for Semiconductors*, 2009 edition.

- [12] Usha Gogineni et al., "Power Potential of 45 nm CMOS Technology," in *Proceedings of IEEE 10th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF2010)*, US, 2010.

### **CHAPTER 2 STATE OF THE ART**

In this chapter, a short summary of the current state and the trends of wireless systems (particularly about personal communications) is given. State-of-the-art design examples and development trends of low power, mmW and WuRx systems are discussed as well.

## 2.1 Status and trends of wireless systems

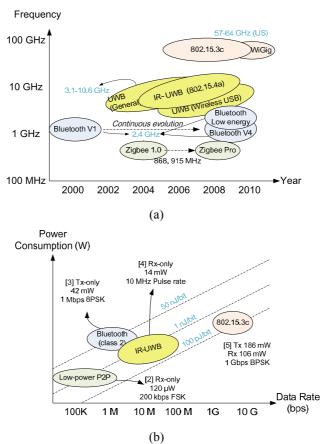

Communication data rates have been increasing during the last decade, as can be observed in Fig. 2.1 (a). Although some (relatively) low frequency systems like Bluetooth also grow horizontally, emerging high frequency technologies like the mmW communications (57-64 GHz, 71-76 GHz and 81-86 GHz, etc.) become increasingly important. One of the reasons is shown in Fig. 2.1 (b): with higher data rates, it is possible for these mmW systems to achieve better energy efficiency.

Fig. 2.1 Status and trends of wireless systems on personal communications.

Besides the high speed and the possibility to achieve low energy per bit  $(E_{bit})^6$ , high frequency (e.g. mmW) communications also provide advantages like smaller electronics feature sizes, smaller directional antennas, better security and higher frequency reuse factor [6]. In addition, compared to the crowded spectrum at lower frequency bands like 2.4 GHz, mmW communication spectrum is relatively empty. As a result, more versatile applications and design freedoms become feasible. For instance, an 87 GHz transceiver front-end is reported in [7] that utilizes unconventional baseband-less carrier and data recovery circuitry and it is able to achieve up to 3.5 Gbps data rate with less than  $10^{-11}$  BER. In 2010, 60 GHz indoor personal communications was standardized by WiGig as part of a tri-band communication system. By adopting beamforming techniques, the 60 GHz system is able to provide up to 7 Gbps data rates that can be used for wireless P2P, wireless display, cordless computing and also Wi-Fi over 60 GHz [8].

## 2.2 Low power techniques

In this section, some widely used low-power architectures and techniques are discussed followed with state-of-the-art design approaches and examples.

## 2.2.1 Impulse radio UWB

IR-UWB is a well-known low power and low cost wireless technology for short range personal communication [9]. According to the Shannon theorem, for a constant channel capacity, the required SNR at the demodulator of an IR-UWB system can be very small due to its wide bandwidth. As a result, a low power Tx can be realized. Early in 2005 to 2007, Inter-Universitair Micro-Electronica Centrum (IMEC) designed the first fully digital IR-UWB Tx that is compatible to the IEEE 802.15.4a standard. Its peak power consumption is 0.65 mW with 1 Mbps data rate and  $E_{bit}$  is 0.65 nJ/bit [10]. However, some drawbacks make the development of IR-UWB system slacken afterwards. Firstly, conventional IR-UWB systems have low immunity to interference. Also, it is difficult for them to capture multi-path energy. Secondly, the requirement of high speed (e.g. Gsamples per second) and wide dynamic range ADC increases Rx power consumption significantly [11]. Thirdly, when adopting coherent detection methods in the Rx front-end, large amounts of power would be consumed in the synchronization process, which results in  $E_{bit}$  value of the Rx ten times larger than that of the Tx [9].

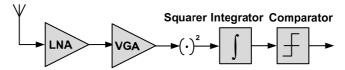

In order to reduce the Rx power consumption, several methods are adopted in IR-UWB systems such as simple modulation schemes (e.g. OOK), duty cycling and non-coherent

<sup>&</sup>lt;sup>6</sup> It should be emphasized that in this thesis,  $E_{bit}$  refers to energy consumption per bit while  $E_b$  (normally used in  $E_b/N_0$ , i.e. the SNR per bit) refers to the energy transmitted per bit.

energy detection approaches. The basic principle of energy-detection non-coherent IR-UWB Receivers is illustrated in Fig. 2.2 [12], while various design details and techniques can be found in the literature. In [12], the proposed energy detector (i.e. the combination of squarer and integrator in Fig. 2.2) is able to achieve a sensitivity of -89 dBm and an  $E_{bit}$  of 0.2 nJ/bit with 100 kbps data rate. With a similar non-coherent detection approach, the OOK IR-UWB Rx front end and baseband in [9] consume 1.64 mW to 2.18 mW (with 40% duty cycle) with 1 Mbps data rate, which corresponds to  $E_{bit}$  values from 1.64 nJ/bit to 2.18 nJ/bit.

Fig. 2.2 Block diagram of a non-coherent IR-UWB Rx with energy detection approach.

#### 2.2.2 Super-regenerative receiver

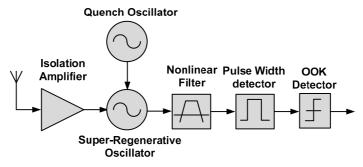

The conventional super-regenerative receiver uses a second low frequency oscillator<sup>7</sup> to periodically quench the main RF oscillation in order to provide high but non-linear gain. The basic topology is shown in Fig. 2.3. Although it is disputed due to drawbacks like poor selectivity, susceptibility to front end overload, lack of stability and restriction to certain types of modulation schemes like OOK modulation, it is, in principle, able to achieve very high RF gain with very low power consumption [11]. For that reason, it is included in this overview of low-power techniques.

Fig. 2.3 Block diagram of a conventional super-regenerative Rx.

<sup>7</sup> In fact, the super-regenerative Rx can operate in linear or logarithmic modes. In the linear mode, the amplitude of the core oscillator is measured before it goes into saturation and then the core oscillator is disabled immediately. In the logarithmic mode, however, two different implementation approaches can be used: full quenching by the second low frequency oscillator or self-sequencing. In the sequencing super-regenerative Rx, no quenching oscillator is required [13].

A 402-to-405MHz super-regenerative receiver is presented in [14]. It is implemented in 0.18-µm CMOS technology. It consumes 0.5mW power at a data rate of 120 kbps and achieves a sensitivity of -95dBm, which corresponds to 4.17 nJ/bit.

In [15], an ultra-low power super-regenerative RF front end is reported for medical body-area network (BAN) applications. It is implemented in 90-nm CMOS technology. The proposed Rx operates at the 2.36-2.4 GHz and 2.4-2.485 GHz ISM bands, and it consumes 500  $\mu$ W power with 1 to 5 Mbps data rate (i.e. 0.5 to 0.1 nJ/bit). In addition, it is able to achieve a sensitivity of -67 dBm at a BER of  $10^{-3}$ .

Although these state-of-the-art super-regenerative Rxs are able to achieve sub-mW power consumption, one significant problem is that they have speed limitation besides other common disadvantages listed at the beginning of this section.

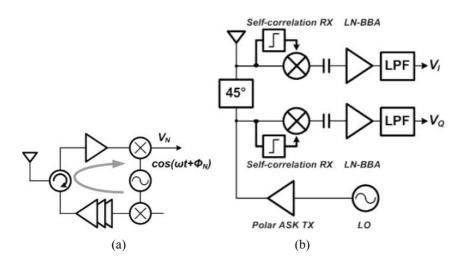

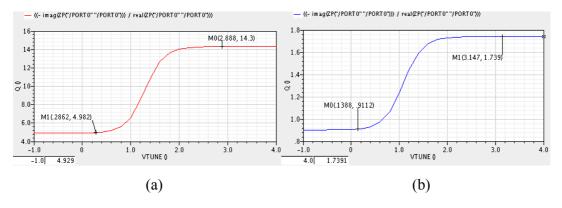

#### 2.2.3 Back-scattering architecture for asymmetrical links

The back scattering technique is widely used in asymmetric wireless applications like radio-frequency identification (RFID) that uses radio waves to exchange data between a reader and a transponder or a tag [16]. Its basic architecture is illustrated in Fig. 2.4 (a).

Fig. 2.4 (a) Block diagram of a conventional back-scattering transceiver and (b) a transceiver consisting of a polar Tx and a self-correlation Rx for RFID application [17].

By adopting the self-correlation structure in the Rx, as shown in Fig. 2.4 (b) [17], the requirement of a Tx-Rx isolator is eliminated, and the proposed Rx is able to achieve -75 dBm sensitivity with 10 mA current consumption from a 3.3-V supply. An obvious disadvantage of backscattering technique is that this approach is only suitable for asymmetric wireless systems instead of a generic solution for low power radios.

#### 2.3 Millimetre-wave communications

Three major topics are observed for mmW wireless communications:

## ➤ Low power and low cost

Compared to lower frequency communication systems, low power and low cost mmW transceivers tend to adopt simpler transceiver architectures, such as direct conversion, sliding/zero IF and non-coherent envelope detection (for Rx) [18]. In [18], a 60-GHz direct conversion Rx is realized in 65-nm CMOS technology, which is able to achieve 30-dB front-end gain, 9.2 dB NF and -36 dBm input-referred third-order intercept point (IIP3) with 43 mW power consumption. A digitally controlled 60-GHz Rx is reported by IMEC in 2009. Its noise figure is about 6 dB and power consumption is only 21 mW<sup>8</sup>. Furthermore, fully digital control makes it can be readily integrated in a multi-element phased array [19].

## ➤ High performance

In order to achieve high performance like high data rate and low BER, usually much more complicated transceiver architectures and/or modulation schemes are required. Consequently, it is not surprising that system power consumption of such high performance systems is also higher. In 2011, a fully integrated sliding IF 60GHz transceiver in a 65nm CMOS technology for wireless high-definition video streaming has been presented in [20]. The CMOS chip is compatible with the WirelessHD<sup>TM</sup> standard and is able to cover four channels. The 16-QAM OFDM modulation scheme is adopted. The proposed transceiver front end consumes 454mW in receiver mode and 1.357W in the transmit mode (357mW for the transmitter and 1W for the PA). The Rx is able to achieve 3.8 Gbps data rate with 11% error vector magnitude (EVM) over 1 meter communication distance. In [21], a 60-GHz direct conversion transceiver in 65 nm CMOS technology is reported, which is compatible with the IEEE 802.15.3c standard. The proposed transceiver front end consumes 186 mW, 106 mW and 66 mW for Tx, Rx and PLL, respectively. The maximum data rates with an antenna built-in the package are 8Gbps in QPSK mode and 11Gbps in 16QAM mode within a BER less than  $10^{-3}$ .

#### > Multi-element phased array front end

Besides advantages like spatial filtering, high security and additional antenna gain, the directional communication system can be optimized to achieve either low power or high performance. Among several directional communication methods, the multi-element phased array beamforming technique provides benefits like high integration level, potential for low cost and low power, and suitability for digital

<sup>&</sup>lt;sup>8</sup> Additional power consumed in the phase-locked-loop (PLL) is 78 mA from a 1.1 V supply.

control<sup>9</sup> and decent beam pointing resolution. As a result, it is widely used. In [22], a low power 60GHz 4-element 65nm CMOS phased array transceiver is presented. The total measured power consumption is 137mW in both Rx and Tx mode, including 29mW for the synthesizer. With 3-bit digitally controlled phase shifters (plus an extra polarity bit for controlling the sign of the phase), the Rx is able to achieve a worst-case phase resolution of 11°. In the high performance direction, a 60-GHz multi-Gbps phased array transceiver is shown in [23]. The proposed Rx is able to support 4-Gbps data rate with a 10 meters communication distance and a BER less than 10<sup>-11</sup>. Its total power consumption is up to 2 W. As a result, the potential applications as well as device mobility are limited.

# 2.4 Wake-up receiver

Power management is one of the most important topics in wireless communication, especially for low power applications. Among all the different methods, wake-up receivers (WuRx) form a very interesting category, because, in principle, it can reduce the standby power of the main radio very efficiently. If the power consumption of the WuRx itself can be minimized, the mobility of the entire communication system can be increased significantly. The state-of-the-art low-power WuRxs are listed in Table 2.1.

| Types                     | Performance |             |             |           |                           |