# Contributions to switched capacitor filter synthesis

Citation for published version (APA): Hegt, J. A. (1988). Contributions to switched capacitor filter synthesis. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR288540

DOI: 10.6100/IR288540

# Document status and date:

Published: 01/01/1988

# Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

# Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# CONTRIBUTIONS TO SWITCHED CAPACITOR FILTER SYNTHESIS

J.A. HEGT

# CONTRIBUTIONS TO SWITCHED CAPACITOR FILTER SYNTHESIS

# PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof. dr. F.N. Hooge, voor een commissie aangewezen door het College van Dekanen in het openbaar te verdedigen op dinsdag 28 juni 1988 te 14.00 uur

duor

JOHANNES ALBERTUS HEGT geboren te Amsterdam

druk wibro dissertatiedrukkenij, helmond

DIT PROEFSCHRIFT IS GOEDGEKEURD DOOR DE PROMOTOREN

Prof.Dr.Ir.W.M.G. van Bokhoven en Prof.Dr.Ing.J.A.G. Jess

Aan Marti, Stan en Ledje

# CONTENTS

| 1 | INTRODUCTION AND SUMMARY                                        | Ŧ, |

|---|-----------------------------------------------------------------|----|

| 2 | SOME BASIC PRINCIPLES FOR THE ANALYSIS AND SYNTHESIS OF SWITCHE | D  |

|   | CAPACITOR FILTERS                                               | 5  |

|   | 2.1 Transformation methods                                      | 5  |

|   | 2.2 Realization of capacitors in MOS technology                 | 10 |

| 3 | ANALYSIS OF SWITCHED CAPACITOR FILTERS                          | 13 |

|   | 3.1 Analysis based on charge conservation                       | 14 |

|   | 3.2 Analysis based on the application of z-domain equivalent    |    |

|   | circuits                                                        | 15 |

|   | 3.3 Analysis based on the application of signal flow graphs     | 22 |

| 4 | SYNTHESIS METHODS FOR BIPHASE STRAYS-INSENSITIVE SWITCHED       |    |

|   | CAPACITOR FILTERS                                               | 32 |

|   | 4,1 Basic concepts for strays-insensitive synthesis             | 33 |

|   | 4.2 An exhaustive synthesis approach                            | 42 |

|   | 4.3 Synthesis by addition of nodes                              | 43 |

| 5 | SC SYNTHESIS BASED ON A 'STRAYS-INSENSITIVE DESIGN GRAPH'       | 51 |

|   | 5.1 Strays-insensitive design graphs                            | 52 |

|   | 5.2 Design examples                                             | 59 |

|   | 5.3 Measurement of a realized SC filter design                  | 72 |

|   | 5.4 Sensitivity properties of SDG based synthesis               | 73 |

|   | 5.4.1 Sensitivity to capacitance deviations                     | 73 |

|   | 5.4.2 Sensitivity to amplifier gain                             | 75 |

|   | 5.4.3 Sensitivity to amplifier bandwidth                        | 75 |

|   | 5.5 SC filter synthesis with finite-gain amplifiers             | 78 |

|   | 5.5.1 Compensation networks for finite-gain amplifiers          | 78 |

|   | 5.5.2 A pre-distortion method for finite-gain amplifiers        | 84 |

|   |                                                                 |    |

| 6            | COMPARISON WITH OTHER EXISTING SC FILTER SYNTHESIS METHODS     | 91  |  |

|--------------|----------------------------------------------------------------|-----|--|

|              | 6.1 SC filter synthesis based on leapfrog LC ladder simulation | 91  |  |

|              | 6.2 SC filter synthesis based on a biquadratic building-block  |     |  |

|              | approach                                                       | 102 |  |

|              | 6.3 Other existing signal flow graph based SC synthesis        |     |  |

|              | methods                                                        | 108 |  |

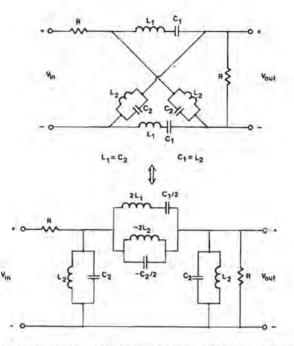

| 7            | A SWITCHED CAPACITOR EQUIVALENT IMMITTANCE CONVERTER           | 111 |  |

|              | 7.1 Immittance converters                                      | 111 |  |

|              | 7.2 Application of GIC's and EIC's in filter synthesis         | 116 |  |

|              | 7.3 NMOS realization of an EIC-based filter                    | 119 |  |

|              | 7.4 Compensation of parasitic capacitances                     | 124 |  |

|              | 7.5 Finite gain effects of the amplifiers                      | 127 |  |

| 8            | CONCLUSIONS                                                    | 130 |  |

| AP           | APPENDIX A                                                     |     |  |

| APPENDIX B   |                                                                | 139 |  |

| REFERENCES   |                                                                | 142 |  |

| SAMENVATTING |                                                                | 149 |  |

| CU           | RRICULUM VITAE                                                 |     |  |

CURRICULUM VITAE

# 1. INTRODUCTION AND SUMMARY.

After A.Fettweis published his theory of resonant-transfer circuits [1] in 1968<sup>1</sup>, the appearance of the famous Fried paper [2] in 1972 and a next few years of relative silence, the development of switched capacitor (SC) filters from a basic concept into a manifold applied commercial product is one of unusual speed.

A number of reasons can be given for their popularity. SC filters

- are low cost,

- need a small chip area,

- are low power,

- are accurate, don't need tuning after production,

- on the other hand, the filter transfer can be transformed to another frequency range by simply changing the clock frequency; this can be attractive for adaptive filter applications.

- are fully implementable in standard MOS processes,

- can be combined with digital circuits on one chip.

As a starting point for many SC filter synthesis methods, other important categories of filters, such as LC, active RC and digital are used.

The main reason for this is a historical one. In the early days of the application of switched capacitors, designers and network theorists had already gathered a huge amount of knowledge and experience, especially in the field of continuous-time filters. It were these designers and theorists who were the first to approach this new offspring and put their stamp on it.

One of the reasons for the unusual speed of the development of switched capacitor filter theory was the available knowledge and experience they brought along.

Though much of the existing theories could be transformed in a more or

<sup>1</sup>In fact J.C. Maxwell mentioned the principle of switched capacitors already in 1873 in his book "A treatise on electricity and magnetism". less straight forward way to make them suitable for SC filters, the similarity between SC filters and other filter categories is only on the surface.

One of the most typical SC aspects and also the most pressing problem is the existence of stray-capacitances on the final integrated chip. These parasitics are not even an order of magnitude smaller than the desired capacitors. The effects of this dominant error source have to be minimized in advance, by a strays-insensitive design.

The synthesis methods that will be proposed in this thesis do not rely on a continuous-time or digital prototype filter as a starting point, but on the properties of switched capacitors <u>themselves</u> and the requirement of strays-insensitivity with the implications of this demand.

In order to reduce the complexity of this approach and not get lost in too many degrees of freedom, these synthesis methods are restricted to circuits with a biphase clock. This restriction is not in conflict with industrial interest: a great majority of the industrial produced SC filters belong to this above-mentioned class.

As a follow-up of this work the possibilities of an extension of this approach to circuits with a multiphase clock could be investigated.

Before we will focus on these synthesis methods, first some basic principles that are implicitly used in this thesis will be cleared up in chapter 2.

In chapter 3, some analysis methods for SC filters are considered. This is done fore two reasons. In the first place these methods will give the reader a way to verify the transfer of the circuits that will be presented in the next chapters. In the second place one of these methods will be an important tool for the synthesis methods that are proposed in this thesis. The first considered method is straight-forward and powerful, but on the other hand also very cumbersome. After being confronted with an example of this method in appendix A, the reader will appreciate the fact that often in practical situations many non-idealities of the circuit may be neglected. In these cases, the second presented method, which is

derived from the first one, may be used. This method is already less cumbersome, but the third and final approach, which is based on Signal Flow Graphs (SFG's), is the most convenient. Moreover, the restrictions for its application will turn out to correspond nicely with the constraints for SC circuits to be strays-insensitive. As an extension of this method a representation for finite gain effects of the amplifiers will be proposed.

In chapter 4 the basic concepts for strays-insensitive synthesis are considered. As a starting point the known Hasler constraints will be used, but in an extended form. In parallel the SFG based analysis will be simplified further. The obtained analysis method is extremely simple and very well suited for a reversed application as a synthesis tool. At this stage, the problem of strays-insensitive synthesis of biphase clocked circuits has been reduced to the composition of an appropriate SFG from branches of a very small set. Three synthesis methods, based on this approach will be proposed in this thesis. The first two of them are briefly considered in chapter 4.

In chapter 5 the third, and most important synthesis method of this thesis, based on the application of 'Strays-insensitive Design Graphs' (SDG's) is explained. Examples are given, one of which is actually built as a bread-board circuit and used as a verification. Furthermore attention is payed to sensitivity properties and possible solutions are given for synthesis with finite gain amplifiers.

As a validation, the SDG method is compared with several other existing methodologies in chapter 6.

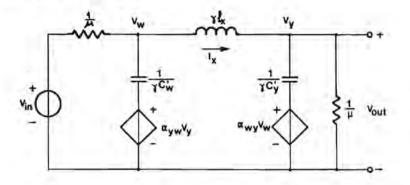

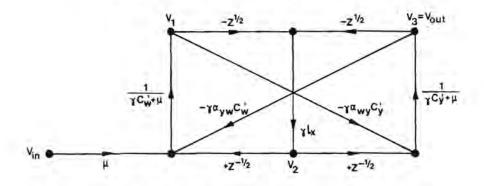

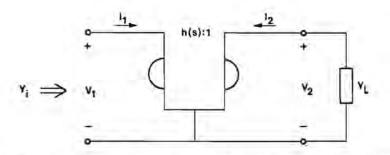

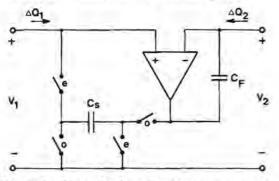

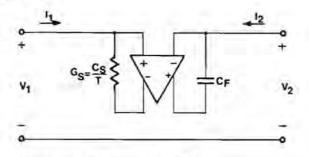

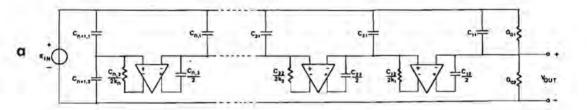

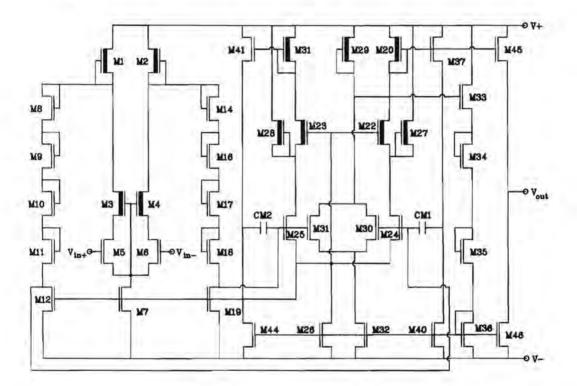

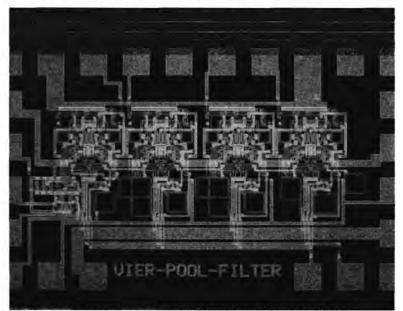

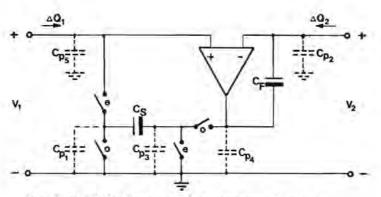

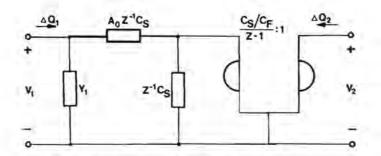

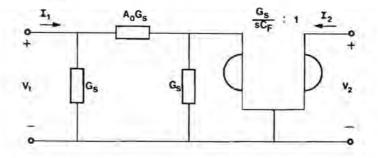

Chapter 7 can be seen as a separate part of this thesis, describing an 'Equivalent Immittance Converter' (EIC). This building block for SC circuits is comparable with a Generalized Immittance Converter in active-RC synthesis and may result in filters with very few circuit elements. A fourth order Butterworth filter using this concept was realized as an NMOS integrated circuit, measurement results of which are also given in this chapter. Although the EIC building block is insensitive to the most important bottom-plate strays of the desired capacitors, it is sensitive to other strays. However, as will be shown, these other strays can be compensated for. An interesting property of this EIC is the fact that its finite amplifier-gain effects can be represented by loading equivalent admittances.

Finally, in chapter 8, some conclusions will be made and suggestions are given for a follow-up.

# 2. SOME BASIC PRINCIPLES FOR THE ANALYSIS AND SYNTHESIS OF SWITCHED CAPACITOR FILTERS.

In this chapter we will briefly discuss some basic principles that are used in this thesis. For a more extensive description the reader is referred to one of the many books [3-6] about these subjects.

SC filters belong to the class of time-variable analog sampled-data systems which are commonly described in the z-domain. Therefore in section 2.1 we will discuss the z-transformation and furthermore a number of transformations from the continuous-time to the discrete-time domain and vice versa.

In section 2.2 the realization of capacitors in MOS technology is considered.

# 2.1 TRANSFORMATION METHODS.

A sample-sequence x(n), obtained by a periodic sampling of a signal x(t) at moments t = nT, such that

$$x(n) = x(nT) = x(t) \Big|_{t=nT}$$

(2.1)

can be represented by its z-transform, defined as:

$$X(z) = Z(x(n)) = \sum_{n=0}^{\infty} x(n) z^{n}$$

(2.2)

for all z where X(z) converges.

In fact this z-transform plays a comparable role in the description of discrete-time signals as the Laplace s-transform does for continuous-time signals.

Here z can be considered as a shift-operator: a multiplication of X(z) with z corresponds with a shift of the sequence x(n) over one sample, or equivalently a time-shift of the signal x(t) over an interval T. Noting that this time-shift can be represented in the Laplace s-domain by a multiplication of the s-transform X(s) of the

signal x(t) with  $e^{sT}$ , the validity of the following relation can be shown:

$$z = e^{sT}$$

(2.3)

This relation gives us the exact swz transform. This can for example be used for the transformation of the transfer function of a continuous-time filter, expressed in s, into a corresponding transfer function for a discrete-time filter, expressed in z. However, the problem arises that a realizable s-domain transfer function, being a rational function in s, will be transformed into an unrealizable equivalent z-domain transfer function, being a rational function in  $\frac{\ln(z)}{T}$  and not in z. The same problem arises when trying to transform a realizable z-domain transfer function into an s-domain equivalent transfer function, which results in a rational function in  $e^{sT}$  instead of in s. For that purpose other transformations than the exact relation (2.3) are used, five of which will be used in this thesis.

# A. Matched-z transform.

Application of this transformation method means, that each transmission zero (pole) of a rational transfer function in s is transformed to a transmission zero (pole) of a corresponding transfer function in the z-domain or vice versa, using the exact relation (2.3). As it only concerns the transmission poles and zeros, this transformation does not result in an exact transformed transfer function. Nevertheless, for frequencies that are low with respect to the sample frequency  $f_s = 1/T$ , the transformed transfer function will be a good approximation for the exact transform, and has the advantage of being a realizable rational function. Because poles are transformed exactly with this method, poles in the left s-half-plane will be mapped on poles within the unit-circle in the z-plane and vice versa. This guarantees conservation of the stability of a filter after transformation.

B. Forward-Euler transform.

Using this method, the operator s in a continuous-time transferfunction is replaced by

$$s \rightarrow \frac{z-1}{T}$$

(2.4a)

or inversely, z in a discrete-time transfer-function is replaced by

$$z + 1+sT$$

(2.4b)

Again a rational function in s is transformed into a rational function in z using this method. However, part of the left s-half-plane is mapped outside the unit-circle in the z-plane. This means that stable continuous-time filters, which have their poles in the left s-half-plane, may be transformed into instable discrete-time filters, having their poles outside the unit circle in the z-plane. However, apart from this potential instability, this transformation is a reasonable approximation for the exact transform for low frequencies with respect to the sample frequency  $f_s$ . Note that eq.(2.4b) can be considered to represent the first two terms of the Laurent polynomial expansion of the exact transform:

$$z = e^{sT} = 1 + sT + \frac{(sT)^2}{2!} + \frac{(sT)^3}{3!} + \dots$$

(2.5)

C. Backward-Euler transform.

Here, the operator s of a continuous-time transfer function is replaced by

$$s \rightarrow \frac{1-z^{-1}}{T}$$

(2.6a)

or conversely z is replaced by

$$z \neq \frac{1}{1-sT}$$

(2.6b)

In this case the left s-half plane is mapped within the unit-circle of the z-plane, so conservation of stability is guaranteed when this method is used for the transformation of a continuous-time transfer function into a discrete-time transfer function. However, also the jw-axis of the s-plane and part of the right s-half-plane is mapped within this unit circle. This means that using this method much of the selectivity of continuous-time filters is lost. Also for this method the resulting transfer function will be a reasonable approximation for frequencies that are low enough with respect to the sample-frequency  $f_g$ .

When eq.(2.6b) is rewritten as

this can be considered as representing the first two terms of the Laurent polynomial expansion of

$$z^{-1} = e^{-sT} = 1 - sT + \frac{(sT)^2}{2!} - \frac{(sT)^3}{3!} + \dots$$

(2.7)

D. Bilinear transform.

Using this transform, s is replaced by

$$s \rightarrow \frac{2}{T} \frac{z-1}{z+1}$$

(2.8a)

or conversely, z is replaced by

$$z \to \frac{1+sT/2}{1-sT/2}$$

(2.8b)

Now the left s-half-plane is mapped within the unit-circle in the z-plane and the j $\omega$ -axis is mapped onto this unit circle. Stability is preserved and also filter selectivity. When a bilinear transformed transfer function is transformed back to the s-domain using the exact substitution (2.3), it can be shown to be identical to the original transfer, except for a frequency warping with respect to the original transfer function. By means of 'pre-warping' one can in advance correct for this effect. The bilinear transform is probably the most popular in filter design.

When the division of (2.8b) is carried out, this results in an expansion:

$$z + 1 + sT + \frac{(sT)^2}{2} + \frac{(sT)^3}{4} + \dots$$

(2.9a)

the three first terms being equal to the expansion of the exact transform:

$$z = 1 + sT + \frac{(sT)^2}{2!} + \frac{(sT)^3}{3!} + \dots$$

(2.9b)

For frequencies that are low with respect to the sample frequency, this transform results in a good approximation for the exactly transformed transfer function, even without prewarping.

# E. Lossless Discrete Integration (LDI) transform.

In this case s is replaced by

$$s \rightarrow \frac{z^{1/2} - z^{-1/2}}{T}$$

(2.10a)

or conversely z is replaced by

$$z \to 1 + \frac{(sT)^2}{2} + sT \sqrt{1 + \frac{(sT)^2}{2}}$$

(2.10b)

Here, with  $z^{1/2}$  we mean the principle value of the root of z.

Also for this case the left s-half plane is mapped within the unit-circle in the z-plane and the j $\omega$ -axis onto this unit circle. Again when an LDI transformed transfer function is transformed back to the s-domain using the exact substitution (2.3), it can be shown to be identical to the original transfer, except for a frequency warping with respect to the original transfer function. This frequency warping can be corrected for in advance again by the application of pre-warping.

The first three terms of the polynomial expansion for eq.(2.10b)

$$z \rightarrow 1 + sT + \frac{(sT)^2}{2} + \frac{(sT)^3}{8} + \dots$$

(2.11)

are again equal to that of the expansion of the exact transform of eq.(2.9b).

For frequencies that are low with respect to the sample frequency, this transform also results in a good approximation for the exactly transformed transfer function, even without pre-warping. As the realization of an LDI transformed integrator results in very simple SC structures, which are used as building blocks in many filters, this LDI transform is often used in SC filter synthesis.

# 2.2 REALIZATION OF CAPACITORS IN MOS TECHNOLOGY.

The ability of MOS circuits to store signal carrying charge packets for relative long time intervals is one of the main principles that gives us the opportunity to realize SC filters. In fact this is the same principle that made the realization of dynamic logic circuits and dynamic random-access memories possible. In this latter application charges are stored on relative inaccurate parasitic capacitances. In digital techniques one can afford these inaccuracies because of the noise margins that are usually assigned to the quantizing operation. In straight-forward analog applications these inaccuracies would automatically lead to inaccurate circuits. Therefore in this latter case we need precision capacitors. It is a remarkable fact that capacitors, realized in normal MOS processes, although they are stable in terms of temperature and voltage coefficients, show random processing variations on the order of 10 to 20%. Nevertheless SC filters, that are realized with these imperfect MOS capacitors are well-known for their accuracy. This is possible, because the properties of SC filters depend on the ratio of capacitances. Because of the good 'tracking' of capacitances on one chip, this ratio is reproducible with an accuracy within some tenths of percents. In contrast to SC filters, the properties of integrated active-RC filters depend on products of resistances and capacitances, which are badly reproducible.

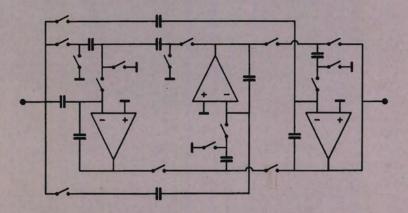

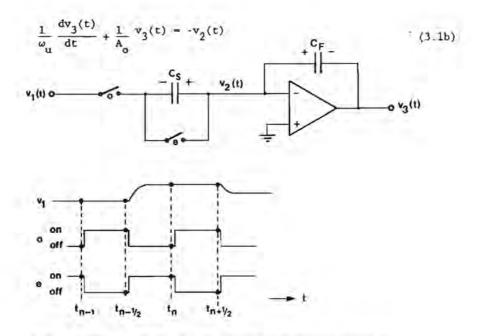

Several types of MOS monolithic capacitors are known. The type that was especially added to the standard N500 NMOS process of the 'Eindhovense Fabricage Faciliteit voor IC's' (EFFIC) was the 'double-poly' capacitor, as depicted in fig.2.1.

fig.2.1: Profile and top-view of a 'double-poly' MOS capacitor.

This capacitor is composed of a bottom-plate being the poly-I layer, a silicon dioxide dielectric layer, which is as thin as about 600Å (resulting in a capacitance of approx.  $60\mu$ F/m<sup>2</sup>) and a poly-II layer as the capacitor top-plate.

Ideally the value of this MOS capacitor is given by

$$C = \frac{\sum_{\substack{0 \\ 0 \\ 0 \\ 0 \\ 0 \\ x}} E_{0}}{E_{0}}$$

(2.12)

Therefore deviations in  $\epsilon_{ox}$ ,  $t_{ox}$ , W and L have a direct impact on the accuracy of the realized capacitance.

The area of the bottom-plate is larger than that of the top-plate, as shown in fig.2.1. This makes this configuration relative insensitive for mask-alignment tolerances. However, effects like undercutting still cause errors due to deviations of W and L. In order to minimize the effects due to these deviations, capacitances are composed of unit capacitors, which all have the same geometry and are expected to have about the same edge effects. Because SC filter characteristics depend on capacitance ratios, the resulting errors are greatly reduced.

Deviations of  $\epsilon_{\rm or}$  are relatively small with respect to the other error sources.

The most important error source in practice are variations in the oxide thickness t  $_{\rm ox}$ . In a standard MOS process these variations are

in the order of magnitude of 10%. Again due to the fact that SC filters are only dependant on capacitance ratios, the common errors due to these thickness deviations will cancel. The dependency of these deviations of the position on the chip are small: typical 1 to 10 ppm/ $\mu$ m. Long range gradients can be compensated for by common-centroid capacitor layouts, but this is not often done in practical SC filter realizations. Approximate temperature coefficients for these capacitors are 10 to 50 ppm/K, voltage coefficients are about 20 to 200 ppm/V.

As can be seen from fig.2.1 the oxide layer between the bottom-plate of the desired capacitor and substrate is only in the order of magnitude of 7.5 times as thick as the thin oxide between the the bottom and top-plates. This results in a parasitic capacitance between this bottom-plate and substrate of approx. 13% of the desired capacitance. With other parasitics connected to this bottom-plate taken into account the total parasitic may be as high as 15 to 20%. Because the thickness of the oxide layer between substrate and bottom-plate depends on a number of MOS process parameters, compensation methods for these bottom-plate parasitics are not very reliable.

The parasitics of the top-plate to ground (substrate) are an order of magnitude smaller than the bottom-plate strays. The most important top-plate parasitics are that of the interconnections which highly depend on the carefulness of the layout designer. However, due to the switches, amplifier in- and outputs etc., with their stray-capacitances the total parasitic from the circuit-node, to which this top-plate is connected, to ground will never be zero, and potentially influence the filter behavior.

For these reasons sensitivity to bottom-plate strays should by all means be avoided and sensitivity to other parasitics is undesirable.

# 3. ANALYSIS OF SWITCHED CAPACITOR FILTERS

Real-life switched capacitor filters suffer from all kinds of non-idealities such as

- parasitic capacitances

- finite open-loop DC gain and bandwidth of the amplifiers

- finite on-conductance of the switches

- finite on-conductance of the amplifier outputs

- non-linearity of the (parasitic) capacitors, switches and amplifiers

- clock feedthrough

- thermal noise and flicker noise in the MOS-fets of the amplifiers and switches

- etc.

that make the analysis of switched capacitor filters a tedious and complicated task.

For a more or less exact analysis of SCF's one is almost forced to make use of one of the numerous SC analysis computer programs [7-16] such as BSCAP, DIANA, DOSCA, DONES, PRSC, SCAPN, SCANAL, SCNAP, SCNET, SCYMBAL, SCOP, SWAP, SWICAP, SWINET, SWITCAP, WASCAP or WATSCAD, that can handle all or a number of the above-mentioned non-idealities. Fortunately however, in many applications most or all of these non-idealities have only a very small effect on the behavior of the filter. In these cases the analysis of a more or less idealized model of the real circuit may lead to results that approximate the actual behavior of the circuit close enough. In many cases the analysis 'by hand' of such a simplified circuit may be practicable feasible.

Many methods are known for such an analysis by hand [17-22], three of which are briefly examined here.

First we will consider a powerful but cumbersome analysis method based on charge conservation [19] (chapter 3.1).

From this first method a more restricted, but practical analysis procedure that applies 'z-domain equivalent circuits' [20] will be derived (chapter 3.2).

Finally a Signal Flow Graph (SFG) based analysis method [21] is examined (chapter 3.3). These SFG's will play an important role in this thesis, beacause they form a tool for the synthesis method, presented in chapter 4 and 5. As an extension of this analysis method, a representation for the finite gain of the operational amplifiers in the circuit will be proposed.

3.1 ANALYSIS BASED ON CHARGE CONSERVATION.

The first method that is considered here is based on charge conservation [19].

It is assumed that the leak of the capacitors, the input currents of the amplifiers and the conductances of the switches in the off-state are negligible. For not too low clock-frequencies and implementation in MOS-technology these assumptions seem reasonable. Furthermore the clock-phases are assumed to be non-overlapping.

For every clock-phase, contours are assigned, for which charge conservation is applicable.

Next the charge conservation is expressed in terms of voltages, using the charge to voltage relations of the capacitors and the (voltage to) voltage relations of the (voltage controlled) voltage sources.

Then the voltages at the sampling instants may be transformed to the z-domain and expressed in each other resulting in the input to output voltage relations of the circuit.

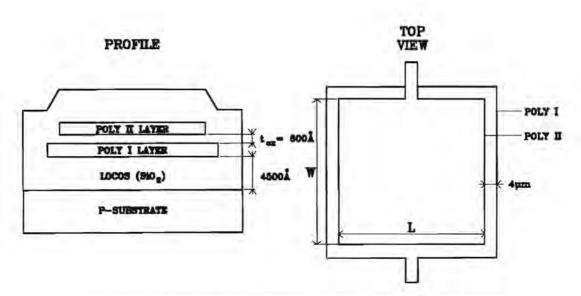

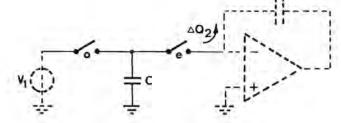

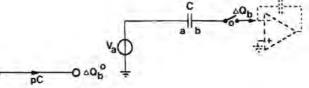

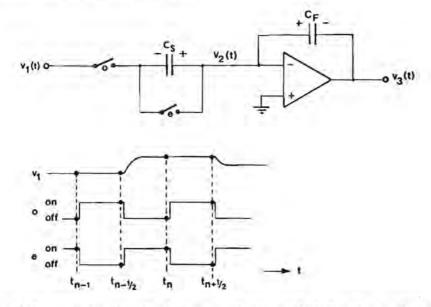

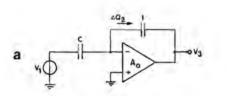

As an example of such an analysis the simple circuit of fig 3.1 is considered.

All elements in this circuit are considered ideal, except for the gain of the amplifier which has a single-pole roll-off:

$$V_{3}(s) = - \frac{A_{0}}{1 + \frac{sA_{0}}{\omega_{u}}} V_{2}(s)$$

(3.1a)

or expressed in the time-domain:

fig.3.1: Example circuit for an analysis method based on charge conservation.

Usually 'e' and 'o' are used to label switches, to indicate their control voltages as well as the time intervals (clock-phases) for which they are in the on-state.

The complete derivation of the transfer function of this circuit is given in appendix A. It should be mentioned that though the circuit taken into consideration is very simple and the only non-ideality taken into account is the frequency dependency of the amplifier gain, the analysis is rather tedious.

This example shows that though this method is powerful and nicely applicable, it is unpractical for analysis by hand of high order filters with a number of non-idealities.

3.2 ANALYSIS BASED ON THE APPLICATION OF Z-DOMAIN EQUIVALENT CIRCUITS.

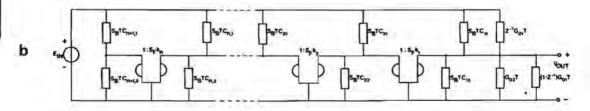

A second method can be derived from the first one and is based on the

application of z-domain equivalent circuits [20]. The method can be explained as follows.

- First the circuit that has to be analyzed is split up into elementary SC building blocks.

- Then for these elementary building blocks z-domain equivalent circuits are derived which have the same port relations for the voltages and charge-increments in the z-domain for every clock-phase as the original circuit. These equivalent circuits are composed of z-domain equivalent admittances. These z-domain equivalent admittances represent the relations between the voltages and charge-increments in the z-domain in a similar way as 'normal' admittances describe the relations between voltages and currents in the Laplace s-domain.

- Next these z-domain equivalent building blocks are interconnected according to the topology of the original circuit.

- Finally this compound z-domain equivalent circuit, which reflects the relations between voltages and charge-increments of the original SC circuit is analyzed, using 'normal' KVL for the (z-transformed) voltages and KCL for the (z-transformed) chargeincrements.

This method is less universal than the first one, because it is based on the assumption that momentary relations exist between the port voltages and charge increments at the sampling instants for every elementary SC building block separately. This assumption is not valid when non-idealities like finite on-conductances of the switches and amplifier output conductances or finite bandwidth of the amplifiers are taken into account.

Though this method is limited in its application it can handle some non-idealities like finite amplifier gain (without frequency dependency) and parasitic capacitances and has the advantage of being very well applicable for analysis by hand, even for higher order filters. Furthermore, for moderate switching frequencies the effects due to the finite amplifier bandwidth and output-conductance as well as the on-conductance of the switches are negligible. In the original paper [20] an extensive library of SC 'elementary' building blocks using non-overlapping biphase switches and their z-domain equivalent circuits are given. It is however sufficient to know the z-domain equivalent circuits of the building blocks that are really elementary: switch, capacitor and voltage-controlled voltage source, to be able to analyze the same collection of SC circuits as with this extensive library.

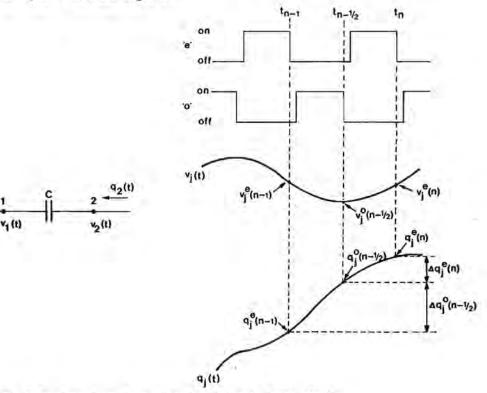

Consider a capacitor C (fig.3.2), which is assumed to be an element in a SC circuit with a biphase non-overlapping clock. (Note that this analysis method is not by principle restricted to biphase-clock circuits only; extension to multiphase-clock circuits is easy and left to the reader).

The two clock-phases are again indicated by indices 'e' (for 'even') and 'o' (for odd), see fig.3.2.

fig.3.2: Capacitor in a circuit with a biphase clock.

91(t)

Using charge conservation, the following relations can be obtained:

$$\Delta q_1^{e} = q_1^{e}(n) - q_1^{o}(n-1/2) = C \left[ v_1^{e}(n) - v_2^{e}(n) - v_1^{o}(n-1/2) + v_2^{o}(n-1/2) \right]$$

(3.2a)

$$\Delta q_1^{\circ}(n-1/2) = q_1^{\circ}(n-1/2) - q_1^{\circ}(n-1) = C \left[ v_1^{\circ}(n-1/2) - v_2^{\circ}(n-1/2) - v_1^{\circ}(n-1) + v_2^{\circ}(n-1) \right]$$

(3.2b)

$$\Delta q_2^{\bullet}(n) = -\Delta q_2^{\bullet}(n) \tag{3.2c}$$

$$\Delta q_{0}^{\circ}(n-1/2) = -\Delta q_{1}^{\circ}(n-1/2)$$

(3.2d)

$(\Delta q_1^e(n)$  being the charge flown into pole 1 during the interval  $t_{n^{-1/2}} < t \le t_n$ , etc.).

Or, after transformation to the z-domain:

$$\Delta Q_1^{\circ} = C V_1^{\circ} - C V_2^{\circ} - z^{-1/2} C V_2^{\circ} + z^{-1/2} C V_2^{\circ}$$

(3.3a)

$$\Delta Q_1^o = CV_1^o - CV_2^o - z^{-1/2} CV_1^o + z^{-1/2} CV_2^o$$

(3.3b)

$$\Delta Q_{a}^{e} = -\Delta Q_{a}^{e} \qquad (3.3c)$$

$$\Delta Q_2^o = -\Delta Q_1^o \tag{3.3d}$$

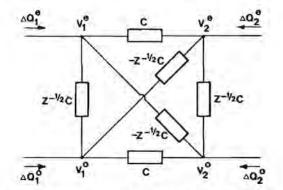

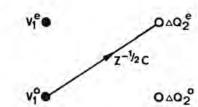

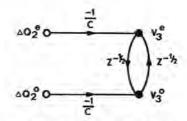

These relations (3.3 a-d) between charge-increments  $\Delta Q_i^j$  and voltages  $V_k^1$  can be represented by the z-domain equivalent circuit of fig.3.3.

Fig. 3.3: Z-domain equivalent circuit for the capacitor of fig. 3.2.

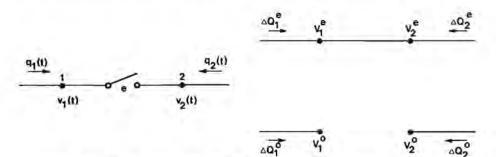

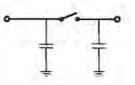

The z-domain equivalent circuit for a switch which is in the on-state during clock-phase 'e' will be a short circuit in phase 'e' and an open circuit in phase 'o' (fig.3.4).

Of course clock-phase 'e' and 'o' may be mutually interchanged.

fig.3.4: Switch with its z-domain equivalent circuit.

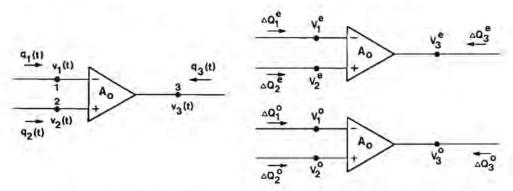

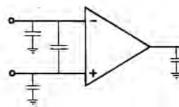

The z-domain equivalent circuit for a voltage-controlled voltage source (or amplifier) with (frequency independent) gain A will consist of two VCVS'es, one for each clock-phase (fig.4.5).

fig.3.5: Amplifier with its z-domain equivalent circuit

Now with the z-domain equivalent circuits for capacitors, switches and VCVS'es derived, the z-domain equivalents of more extensive circuits can be obtained.

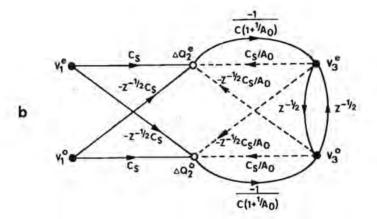

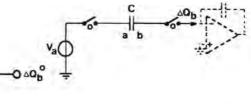

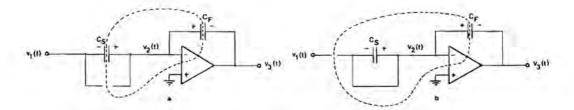

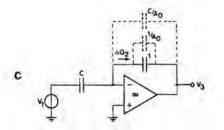

As an example the circuit of fig.3.1 is analyzed using this method, where the gain A of the amplifier is taken  $A_{i}$ .

This equivalent circuit can further be simplified by removing the redundant admittances (drawn with a dashed line in fig.3.6). Straight-forward analysis of this circuit yields

$$H^{oo}(z) = \frac{V_3^{o}(z)}{V_1^{o}(z)} = \frac{-C_s}{(1-z^{-1})(1+1/A_o)C_F + C_s/A_o}$$

(3.4a)

$$H^{oe}(z) = \frac{V_3^{e}(z)}{V_1^{o}(z)} = \frac{-z^{-1/2} C_s}{(1-z^{-1}) (1+1/A_s)C_p + C_s/A_s}$$

(3.4b)

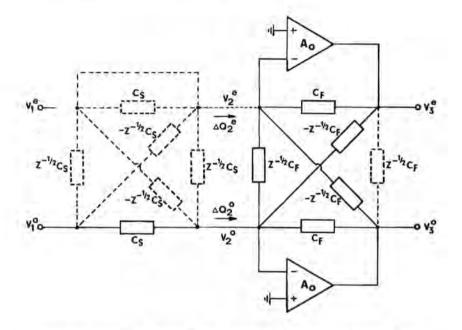

fig.3.6: Z-domain equivalent circuit for fig.3.1 with A=A.

representing a damped inverting Backward Euler integrator and a damped inverting LDI integrator respectively, in accordance with the results of the analysis in appendix A (with  $\omega_n \rightarrow \infty$ ).

When all elements would be considered ideal, so for the circuit of fig.3.1 A  $\rightarrow \infty$ , the z-domain circuit of fig.3.6 could be simplified further. In that case admittance  $z^{-1/2}C_{\rm F}$  would be connected between two virtual ground nodes and thus be redundant (fig.3.7).

fig.3,7: Z-domain equivalent circuit for fig.3,1 with A  $\rightarrow \infty$ .

Now the analysis is even more simple and yields

$$H^{oo}(z) = \frac{V_3^o(z)}{V_1^o(z)} = \frac{-C_s}{(1-z^{-1})C_p}$$

(3.5a)

$$H^{oo}(z) = \frac{V_3^o(z)}{V_1^o(z)} = \frac{-z^{-1/2}C_s}{(1-z^{-1})C_p}$$

(3.5b)

So in the ideal case these BE and LDI integrators are undamped.

Note that in this ideal case, where  $V_2^e - V_2^o = 0$  (virtual ground) the charge-increment  $\Delta Q_2^o$  is completely specified by the voltage  $V_1^o$  and the capacitance  $C_s$ :

$$\Delta Q_2^o = C_s V_1^o \tag{3.6}$$

Furthermore the voltages  $V_1^{\circ}$  and  $V_2^{\circ}$  can be expressed in the

charge-increments  $\Delta Q^{o}_{2}$  and  $\Delta Q^{o}_{2}$  and the capacitance  $C_{p}$  as:

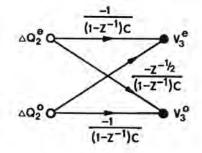

$$V_3^{e} = -\frac{1}{(1-z^{-1})C_p} \Delta Q_2^{e} - \frac{z^{-1/2}}{(1-z^{-1})C_p} \Delta Q_2^{e}$$

(3.7a)

and

$$V_{3}^{o} = -\frac{1}{(1-z^{-1})C_{u}} \Delta Q_{2}^{o} - \frac{z^{-1/2}}{(1-z^{-1})C_{u}} \Delta Q_{2}^{o}$$

(3.7b)

## 3.3 ANALYSIS BASED ON THE APPLICATION OF SIGNAL FLOW GRAPHS.

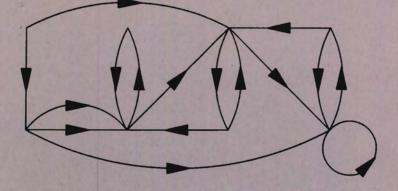

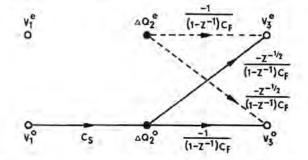

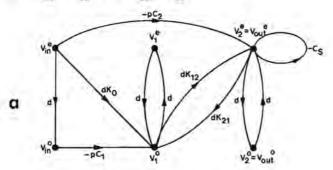

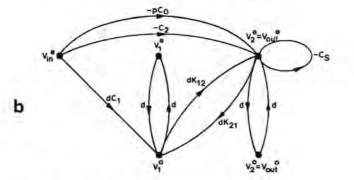

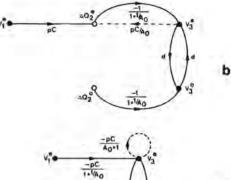

Relations (3.6), (3.7a) and (3.7b) can also be represented by a Signal Flow Graph [21], as depicted in fig.3.8.

Analysis of SC circuits based on SFG representation is the third and most convenient method considered here. It is also the most restricted method in its practical application. In order to be easily handled it

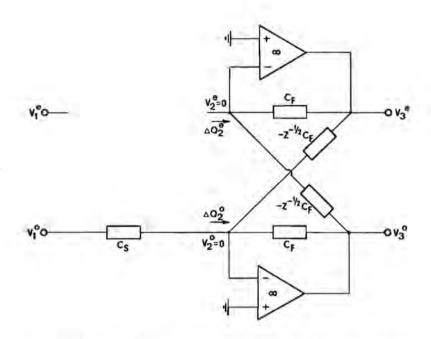

fig.3.8: Signal Flow Graph representation for the idealized circuit of fig.3.1.

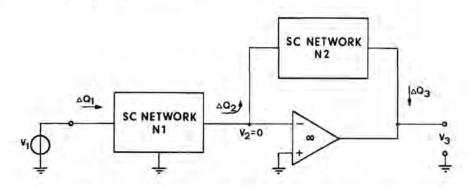

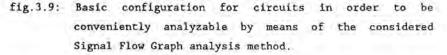

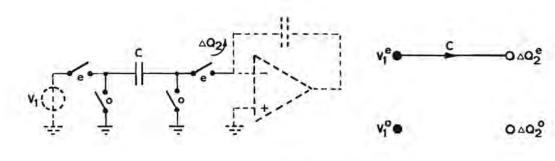

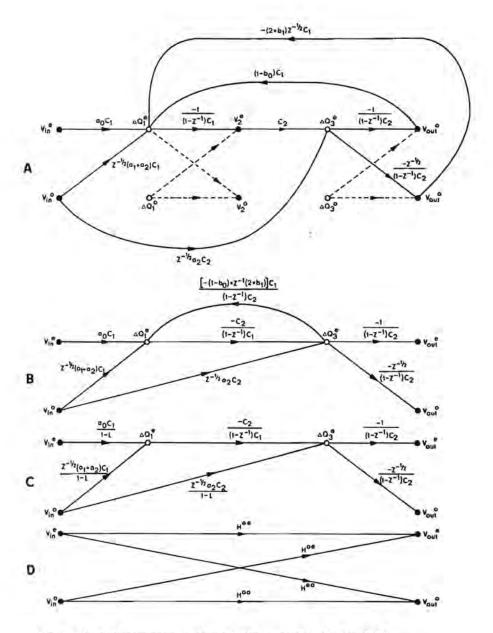

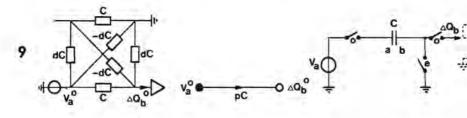

is assumed that the circuit consists of (a number of) basic configurations as depicted in fig.3.9.

This basic configuration consists of an ideal operational amplifier

(with infinite gain<sup>1</sup> and bandwidth) and a grounded non-inverting input, combined with a feedback SC network N2, such that  $V_2 = 0$  (virtual ground) and an input SC network N1 between an ideal voltage source  $V_1$  (for example the output of an ideal operational amplifier) and this virtual ground node.

Of the 4n port variables of network N1 with an n-phase clock  $(V_1^{\Phi}, \Delta Q_1^{\Phi}, V_2^{\Phi})$  and  $\Delta Q_2^{\Phi}$  per clock-phase  $\Phi$ ), interrelated by a 2n × 2n transmission matrix, 2n are redundant.  $\Delta Q_1^{\Phi}$  describes only the load of the ideal voltage source  $V_1$ , furthermore  $V_2^{\Phi} = 0$  (virtual ground). This reduces the size of the transmission matrix to n × n. For the same reasons also the size of the transmission matrix of network N2 can be reduced to n × n :  $V_2^{\Phi} = 0$  and  $\Delta Q_3^{\Phi}$  describes only the

The considered SFG analysis method is in fact based on a graph representation of the coupled transmission matrices of the 'input networks' (N1-type networks) with a signal flow from voltage nodes marked  $V_i^{\Phi}$  to charge-increment nodes marked  $\Delta Q_i^{\Phi}$  and of 'opamp networks'

load of an ideal voltage source  $V_{a}$ .

<sup>1</sup>At the end of this chapter an extension for this SFG analysis method will be presented that can also cope with finite gain amplifiers.

(combining the operational amplifiers with their N2-type network) with a signal flow from charge-increment nodes marked  $\Delta Q_k^{\Phi}$  to voltage nodes marked  $V_1^{\Phi}$ . (Here  $\Phi$  refers to clockphase 'e' or 'o', indices i, j, k and l are related to nodes in the considered SC circuit.) The composed SFG of the total circuit can then be analysed using for instance Mason's gain rule [26] or elimination of nodes, using

elementary graph transformations [25].

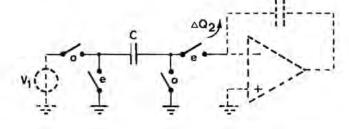

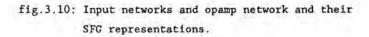

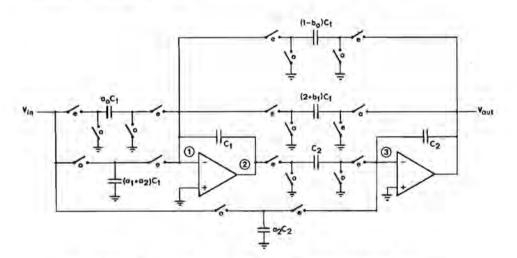

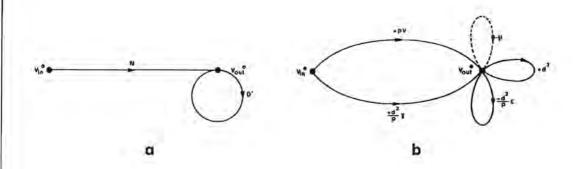

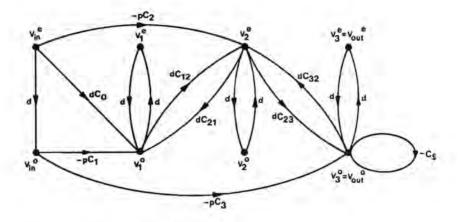

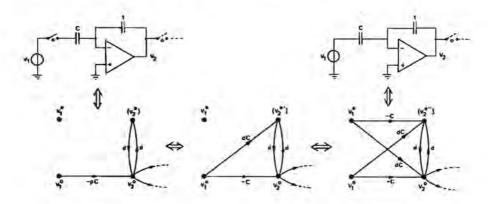

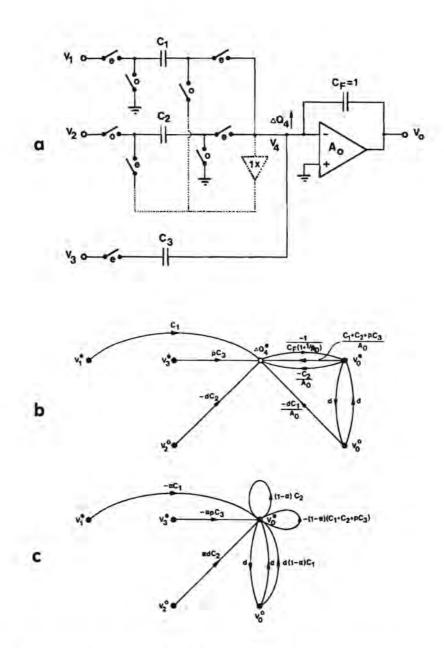

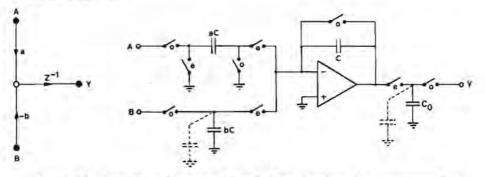

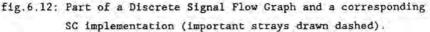

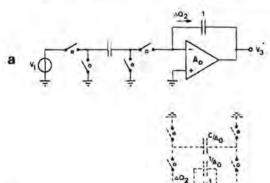

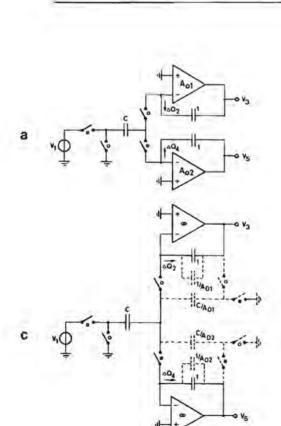

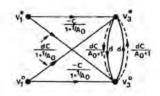

In [21] a small library of biphase clock input and opamp networks is given with their corresponding SFG representation, part of which is redrawn in fig.3.10.

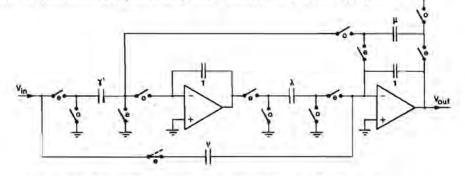

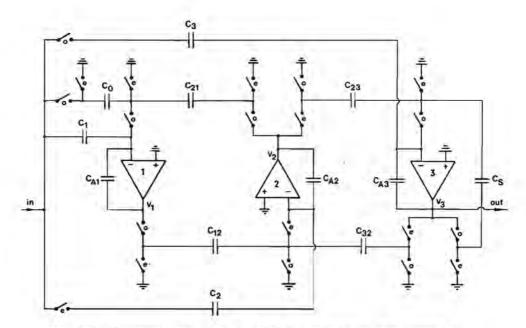

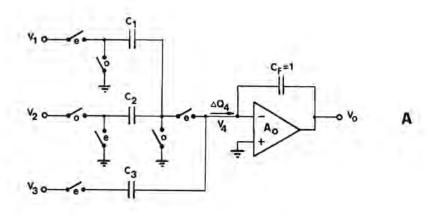

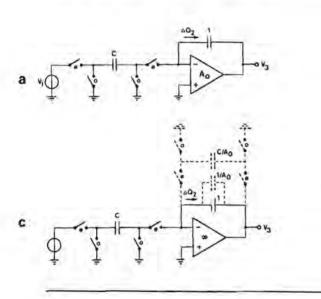

As an example using this method, the more complex circuit of fig.3.11 [23] will be analyzed.

This circuit consists of three different types of input networks and one type of opamp network, for which the corresponding SFG representation, given in fig.3.10, can easily be derived by the reader, or found in [21].

fig.3.11: Example circuit for the demonstration of SFG

analysis.

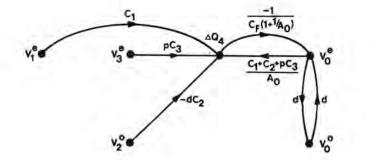

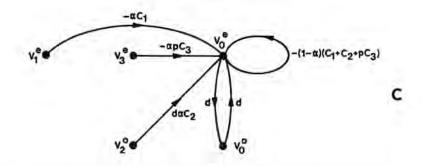

The SFG representations of the input networks and opamp networks are now interconnected, according to the topology of the SC network of

fig.3.12: SFG representation of the circuit of fig.3.10

- a: SFG as a composition of elementary graphs of fig.3.11

- b: simplified SFG with reduced number of nodes and branches

- c: SFG after elimination of the loop

- d: final SFG

fig.3.11, resulting in the SFG representation of the entire circuit as given in fig.3.12.

This SFG can be simplified by omitting the redundant branches of the opamp networks (dashed lines in fig.3.12a) and combining the two feedback branches, resulting in the SFG of fig.3.12b,

Then the loop with gain

$$L = \frac{(1-b_0) - z^{-1}(2+b_1)}{(1-z^{-1})^2}$$

can be eliminated (fig.3.12c), by dividing all branches ending on this loop by

$$1-L = \frac{b_0 + b_1 z^{-1} + z^{-2}}{(1 \cdot z^{-1})^2}$$

Finally elimination of the nodes marked  $\Delta Q_2^e$  and  $\Delta Q_3^e$  results in the SFG of fig.3.12d, with

$$H^{**} = \frac{V_{out}^{*}}{V_{in}^{*}} = \frac{a_{0}}{b_{0} + b_{1}z^{-1} + z^{-2}}$$

(3.8a)

$$H^{eo} = \frac{V_{out}^{e}}{V_{in}^{e}} = z^{-1/2} H^{ee}$$

(3.8b)

$$H^{oe} = \frac{V_{out}^{e}}{V_{o}^{o}} - z^{-1/2} \frac{a_{1}^{e} + a_{2}^{e} z^{-1}}{b_{a}^{e} + b_{1}^{e} z^{-1} + z^{-2}}$$

(3.8c)

$$H^{oo} = \frac{V_{out}^{o}}{V_{in}^{o}} = z^{-1/2} H^{oe}$$

(3.8d)

If the input signal is fixed for a full clock period, such that  $V_{in}^{o} = z^{-1/2} V_{in}^{o}$ , then

$$H^{ea} = z^{1/2} H^{eo} = z^{-1/2} \frac{a_0 + a_1 z^{-1} + a_2 z^{-2}}{b_0 + b_1 z^{-1} + z^{-2}}$$

(3.9)

Note that the locations of the realizable poles and zeros are restricted. In order to prevent the need for negative capacitances both  $a_2/a_0$  and  $(a_1+a_2)/a_0$  have to be non-negative. Furthermore  $b_0$  cannot exceed one,  $b_1$  cannot be smaller than -2.

This SFG analysis method plays an important role here, because it will be used as a tool for the SC synthesis methods, presented in chapter 4.

Two further remarks need to be made about this analysis method.

An equivalent SFG representation of the opamp network is proposed here, as given in fig.3.13. This reflects the physical mechanisms in this network in a better way and has the advantage of resulting in more simple expressions for the branch gains.

fig.3.13: Alternative SFG representation for an opamp network in a biphase clock circuit.

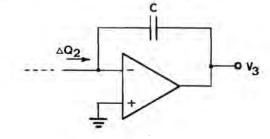

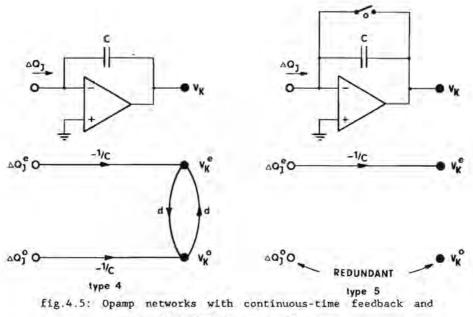

This analysis method can be extended, such that the finite gain effects of the amplifiers can be incorporated, as will be presented below.

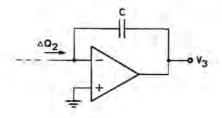

When the opamp network of fig.3.13 has an amplifier with finite gain  ${\rm A}_{\rm p}$  then

$$\Delta Q_2^e = C \left[ (V_3^e - V_2^e) - z^{-1/2} (V_3^e - V_2^e) \right]$$

(3.10a)

$$\Delta Q_2^o = C \left[ (V_3^o - V_2^o) - z^{-1/2} (V_3^o - V_2^o) \right]$$

(3.10b)

with  $V_2$  being the voltage at the inverting amplifier input, which is no longer zero, but  $V_2^o = -V_3^o/A_o$  and  $V_2^o = -V_3^o/A_o$ . Now

$$\Delta Q_2^e = -C \left(1 + \frac{1}{A_0}\right) \left(V_3^e - z^{-1/2} V_3^e\right)$$

(3.11a)

$$\Delta Q_2^o = -C \left(1 + \frac{1}{A_0}\right) \left(V_3^o - z^{-1/2} V_3^o\right)$$

(3.11b)

or conversely:

$$V_{3}^{e} = -\frac{\Delta Q_{2}^{e}}{(1-z^{-1}) C (1+\frac{1}{A}_{g})} - \frac{z^{-1/2} \Delta Q_{2}^{o}}{(1-z^{-1}) C (1+\frac{1}{A}_{g})}$$

(3.12a)

$$V_{3}^{o} = -\frac{\Delta Q_{2}^{o}}{(1-z^{-1}) C (1+\frac{1}{A}_{0})} - \frac{z^{-1/2} \Delta Q_{2}^{o}}{(1-z^{-1}) C (1+\frac{1}{A}_{0})}$$

(3.12b)

or with remark 1 above:

$$V_{3}^{o} = -\frac{\Delta Q_{2}^{o}}{C (1 + \frac{1}{A})} + z^{-1/2} V_{3}^{o}$$

(3.13a)

$$V_3^o = -\frac{\Delta Q_2^o}{C(1+\frac{1}{A_0})} + z^{-1/2} V_3^o$$

(3.13b)

The charge  $\Delta Q_2$  delivered by the input network will also be changed due to the finite amplifier gain.

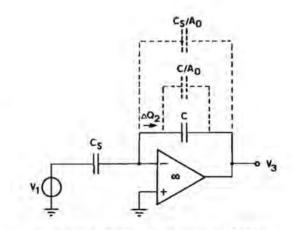

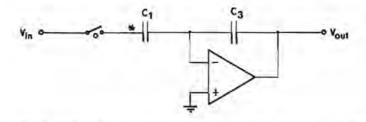

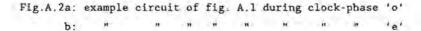

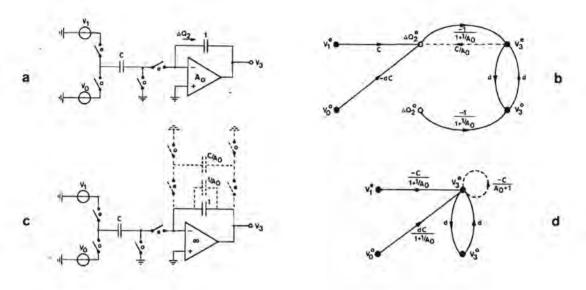

For an input network consisting of an unswitched capacitor  $C_{S}$  between a voltage source  $V_{i}$  and the inverting input of the amplifier (fig.3.14a)

$$\Delta Q_2^{\bullet} = C_g [(V_1^{\bullet} + V_3^{\bullet}/A_0) - z^{-1/2}(V_1^{\bullet} + V_3^{\bullet}/A_0)]$$

(3.14a)

$$\Delta Q_2^o = C_g [(V_1^o + V_3^o/A_0) - z^{-1/2}(V_1^e + V_3^e/A_0)]$$

(3.14b)

The resulting SFG is given in fig.3.14b.

α

fig.3.14 a: SC circuit with finite gain amplifier

b; corresponding SFG representation

c: SC circuit with infinite gain amplifier and virtual capacitors. The interesting observation can be made that the finite gain of the amplifier can be fully incorporated in virtual capacitors.

The four SFG branches representing the input capacitor  $C_s$  have four 'mirror-image' branches (dashed in fig.3.14b), that can be considered as branches representing a virtual capacitor  $C_s/A_0$  between the output and inverting input of the amplifier.

The altered branch gains of the opamp network can be considered as the result of an extra feedback capacitor  $C/A_{a}$  (fig.3.14c).

In appendix B a number of elementary SC circuits, that will play an important role in the next chapters, comprising finite gain amplifiers, with corresponding SFG's and virtual capacitor representation are tabulated.

# SYNTHESIS METHODS FOR BIPHASE STRAYS-INSENSITIVE SWITCHED CAPACITOR FILTERS.

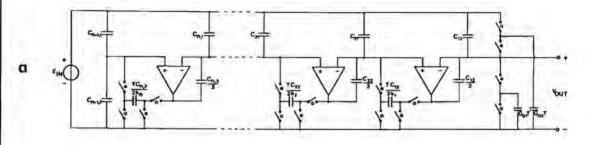

In chapter 4.1 we will first examine the consequences of strays-insensitivity, that we demand for our synthesis method. As a starting point, sufficient conditions known as the 'Hasler constraints' will be used. As it turns out, the blindfolded application of these constraints wrongly excludes a useful class of circuit nodes. Therefore we will permit this additional class, resulting in 'extended Hasler constraints', without releasing the strays-insensitivity demand. Combining these extended constraints with the exclusion of redundant circuit configurations results in a very limited set of possible SC structures.

As the extended Hasler constraints automatically result in circuits, for which the SFG analysis of chapter 3.3 is applicable, we will use this method as a tool for the synthesis. However, before this is done, the original SFG approach will be simplified further. As will be shown, the limited set of SC structures results in an even smaller set of allowable branches in the SFG description.

On the one hand we then have an extremely small set of allowable building blocks (branches), and on the other hand a very simple analysis method (SFG), that we will use in reverse as a synthesis tool.

Two synthesis methods, based on this concept, will be considered in this chapter. The first one is an exhaustive approach, briefly discussed in section 4.2. Next an SFG synthesis, based on node addition is considered in section 4.3.

Because of its importance for this thesis and the resulting extensiveness of its discussion, the treatment of a third method will be postponed to chapter 5.

32

4.1 BASIC CONCEPTS FOR STRAYS-INSENSITIVE SYNTHESIS.

In [24] Hasler formulates two topological constraints that guarantee insensitivity with respect to the following strays:

- of the desired capacitors from their bottom and top plates to ground,

- of the amplifier output and inverting and non-inverting amplifier inputs to ground as well as the parasitic capacitance between these two inputs,

- between the terminals of the switches and ground,

as depicted in fig.4.1.

fig.4.1: Stray capacitances referred to by Hasler's constraints.

The following classes of nodes are defined:

- V-nodes: (voltage source nodes), comprising the operational amplifier output nodes, as well as the input nodes of the circuit;

- I-nodes: (virtual ground nodes), the input of an operational amplifier with negative feedback, whose other input is connected to ground;

- 0-nodes: ground nodes.

With these definitions the Hasler constraints can be formulated as follows:

- In any clock-phase the circuit does not contain nodes other than V-nodes, I-nodes and O-nodes;

- A terminal of a capacitance is never switched from a V-node in one clock-phase to an I-node in the next phase.

This formulation is in fact an extension of the original Hasler constraints, which were stated for circuits with a biphase clock, to circuits with an n-phase clock.

The above mentioned constraints are sufficient conditions for strays insensitivity of SC filters.

In the original paper it is conjectured that this class contains essentially <u>all</u> stray capacitance insensitive filters. However, this conjecture will be contradicted here. The synthesis methods proposed in this thesis result in strays insensitive filters, but allow a class of nodes that is not mentioned in the first Hasler constraint. This class of nodes is what will be referred to as F-nodes: nodes that are floating.

As an example in fig.4.2 a circuit is given, that can easily be shown to be strays insensitive, although it contains an F-node in clock-phase 'e' (left plate of capacitor  $C_1$ ).

Examples can be given of circuits that comprise one or more F-nodes, and essentially are strays-sensitive. Nevertheless it will be shown that for circuits with a biphase clock all non-redundant switched capacitor configurations comprising F-nodes are strays-insensitive. For the time being, F-nodes are added and yield what will now be called the extended Hasler restrictions. Afterwards the switched capacitor configurations that contain F-nodes will be checked for strays insensitivity.

The first extended Hasler constraint makes the application of Signal Flow Graph analysis, as explained in chapter 3.3, convenient to apply.

Note that the first extended Hasler constraint actually assumes the operational amplifiers to be ideal.

However, as long as the gain of the amplifiers is sufficiently high (what in general already should be the case, in order to prevent the filter to have an unacceptable high sensitivity for this gain), the influence of stray capacitances is negligible.

In a strays insensitive SC circuit with a biphase clock (clock-phases 'e' and 'o') a capacitor with its 2 terminals (a and b) and 4 types of nodes (V, I, O and F) can be applied in 256 possible modes.

However, in order not to be redundant, at least one of its terminals should be connected to an I-node in at least one clock-phase. We will assume this to be the b-terminal in the 'o' clock-phase (of course the labels of the terminals (a/b) as well as of the clock-phases (e/o) can be mutually interchanged). This reduces the number of possible modes to 64.

Now, according with the second Hasler restriction, terminal b may not be a V-node in phase 'e'. This reduces the number of possible modes to 48.

There should at least be one terminal which is a V-node in one of the clock-phases, otherwise the capacitor is redundant. This reduces the number of possible modes further to 21.

According with the second Hasler constraint this V-node is not allowed to be an I-node in the other clock-phase. This reduces the number of possible modes further to 15.

These 15 possible modes are enumerated in table 4.1.

Of these 15 modes, mode 11 and 12 in table 4.1 are the same as mode 3 and 4 resp., because of clock-phase symmetry.

Mode 13 is a redundant mode, because the capacitor can't be charged nor discharged.

| clock-phase                | e | 0 | e | 0           |                         |

|----------------------------|---|---|---|-------------|-------------------------|

| mode terminal              | a | a | ъ | b           | 1                       |

| 1                          | 0 | v | 0 | I           |                         |

| 2                          | v | 0 | 0 | I           |                         |

| 1<br>2<br>3<br>4<br>5<br>6 | F | v | I | I           |                         |

| 4                          | 0 | v | I | I           |                         |

| 5                          | v | v | 0 | I           |                         |

| 6                          | V | v | I | I           |                         |

| (7)                        | v | v | F | I<br>I<br>I |                         |

| (8)                        | F | v | F | I           |                         |

| (9)                        | F | v | 0 | I           |                         |

| (10)                       | 0 | v | F | 1           | the second second       |

| (11)                       | v | F | I | I           | as mode 3 (clock symm.) |

| (12)                       | v | 0 | I | I           | as mode 4 (clock symm.) |

| (13)                       | v | F | F | I           | redundant               |

| (14)                       | v | F | 0 | I           | redundant               |

| (15)                       | v | 0 | F | I           | redundant               |

table 4.1: Modes for a (switched) capacitor configuration.

Mode 14 is a redundant mode, because though the capacitor can be charged it can't pass its charge to the I-node.

Mode 15 is a redundant mode, because though the capacitor can pass its charge to the I-node, it can't be charged.

It should be mentioned here, that mode 14 is sensitive for the stray capacitance connected to terminal a, and can serve as an example of stray sensitivity due to the application of an F-node. However, in consequence of the fact this mode is redundant, and therefore will not be used in the considered synthesis methods, this will be of no concern to us.

The remaining 10 modes are enumerated in table 4.2.

-> : virt. gnd. d=Z<sup>-1/2</sup> p=1-Z<sup>-1</sup>

Modes 3, 7, 8, 9 and 10 all realize the same transfer. Modes 8, 9 and 10 however apply one or more redundant switches and will not be used. When modes 3 and 7 are being compared, mode 3 has the slight advantage of having the switch stray capacitances at the voltage source side. In cases where the amplifier gain is rather low this is better than having them at the 'virtual ground' side of the desired capacitor.

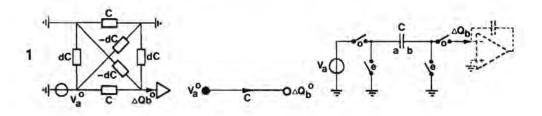

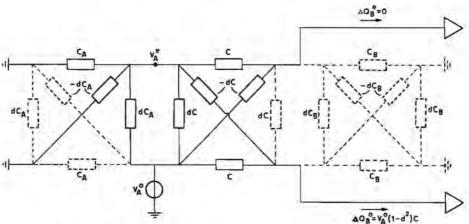

Now mode 3 has to be checked for strays-insensitivity, because it contains an F-node. When the z-domain equivalent circuit is extended with the admittances representing the parasitic capacitances  $C_A$  and  $C_B$  (fig.4.3),  $\Delta Q_B^{\theta}$  and  $\Delta Q_B^{\theta}$  indeed turn out to be independent of these strays.

fig.4.3: Mode 3 circuit with stray capacitances and z-domain equivalent circuit (redundant equivalent admittances drawn with a dashed line).

In a similar way modes 7, 8, 9 and 10 can also be checked and found to be strays-insensitive. This has been omitted here, because these modes will not be used. This leaves modes 1 to 6 as the elementary input networks for strays insensitive biphase clocked SC filter synthesis.

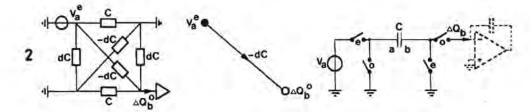

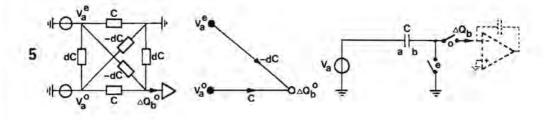

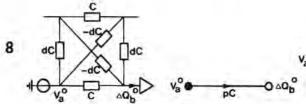

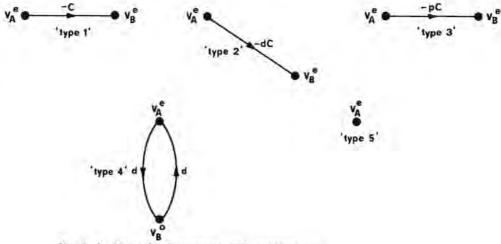

A closer look at table 4.2 shows that the SFG representations of all non-redundant strays-insensitive (switched) capacitor configurations are composed of only three types of branches (fig.4.4).

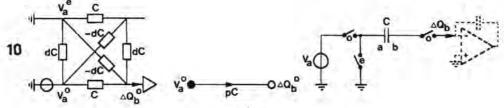

pC C DAOR VA 0 40 type 1 type 3 type 2 d=Z-1/2 O AO P p=1-Z-1

type 1: +C -branch (modes 1, 4, 5 and 6) type 2: -dC -branch (modes 2, 4, 5 and 6)  $(d = z^{-1/2})$ type 3: +pC -branch (modes 3, 7, 8, 9 and 10)  $(p = 1 - z^{-1})$

fig.4.4: elementary SFG branches for input networks clock-phases 'e' and 'o' may be mutually interchanged).

Now the opamp networks will be considered.

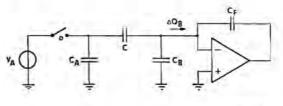

Since the clock-phases are nonoverlapping, we will demand a continuous-time feedback path around the operational amplifiers in order to guarantee stability. This results in 2 modes (fig.4.5), where again clock-phases 'e' and 'o' may be mutually interchanged. The corresponding SFG representations will be referred to as 'type 4' and 'type 5' respectively.

All other SC networks around an operational amplifier are considered as input networks.

Knowing the set of allowable elementary graphs (type 1 to 5), these could serve as a starting point for a synthesis method based on Signal Flow Graphs. However, before this is done a further simplification will be proposed.

Temporarily all continuous-time feedback capacitors of the opamp networks will be scaled to a value of 1. This is no restriction, because the voltage transfer of the filter is determined by the <u>ratios</u>

corresponding SFG representations.

of the capacitors of the input networks and the capacitors of the opamp networks. Later on we will rescale these capacitors in order to minimize the total capacitance of the filter.

As a next step all charge-increment nodes in the SFG are changed in sign. This corresponds to multiplication of all branches (except for the branches of the d\*d loop of the 'type 4' graph) with -1.

Every charge-increment node has only one branch leaving it. This is a branch with transfer 1, which ends on the voltage node of the same opamp network. Now all charge-increment nodes in the SFG are removed by means of contracting them in the voltage nodes of the corresponding opamp output.

The advantage of these steps is that the obtained SFG consists of voltage nodes only, and has a reduced number of branches.

The set of elementary SFG structures is given in fig.4.6.

Comparatively, the 'type 5' structure is of little value: it consists of an isolated node, at the price of an operational amplifier, a

switch and a capacitor (see fig.4.5),

Besides, because of the short circuit switch, the realization of this single node will have a deteriorated sensitivity for the finite bandwidth and slew-rate of the amplifier.

fig.4.6: Set of elementary SFG structures.

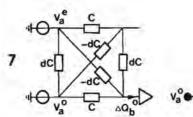

#### 4.2 AN EXHAUSTIVE SYNTHESIS APPROACH.

The synthesis of strays-insensitive SC filters with a biphase clock can be considered now as the following problem: given the opamp network branches ('type 4' and rarely 'type 5') place the input network branches 'type 1', 'type 2' and 'type 3' in such a way, that the transmission of the total SFG is in accordance with the desired transfer function.

The opamp network branches could be regarded as the 'skeleton' of the filter (fig.4.7), which is to be completed by the input network branches, giving it its 'personality'.

One approach could be to place <u>all</u> possible input network branches, from every node to every node, calculate the input to output transfer of the graph, and remove all superfluous branches again. There is a restriction: in order to avoid possible stability problems, delay free loops containing more than one amplifier will not be allowed. (This

fig 4.7: 'Skeleton' of a filter, made up of its opamp network branches.

will be worked out in more detail in chapter 6). In the simplified SFG representation, as was proposed in this chapter, these loops can easily be determined: they form loops in the graph that are totally in one clock-phase, with exception of self-loops.

Nevertheless the number of branches left is still  $4n^2+8n$ , when there are n amplifiers involved, which makes this method unpractical for synthesis of higher order filters. Furthermore this approach can hardly be called a synthesis method, since it is actually an exhaustive search based on analysis. On the other hand, it could be an interesting basic concept for a computer program generating a library of all (for the given restrictions) possible canonic or pseudo canonic SFG's for a certain limited number of amplifiers.

### 4.3 SYNTHESIS BY ADDITION OF NODES.

Another approach is one which is based on a method that has already been applied [25] for the synthesis of digital filters.

The synthesis method in question is based on the observation that the complexity of expressions for the gain of the branches in a SFG can often be reduced by introducing new nodes. (This is in fact the opposite of SFG analysis based on node elimination [26]). It should be mentioned that the synthesis of digital filters using this method, is far more straight-forward than that of SC filters, because in our case we have to deal with clock-phases and furthermore with fixed signs of the branches.

This approach leaves much freedom to the designer in the sense of how to construct the transfer function and how to manipulate the corresponding graph in order to end up with branches from the allowed set only. This method will not automatically lead to a fixed filter structure, like many other synthesis methods do. As will be shown in an example, this method can sometimes generate a circuit that has one or more advantages with respect to other designs.

On the other hand this freedom means that almost at every step in this approach the designer has to choose between a number of alternatives. It is often difficult to predict which one will lead to 'the best' final circuit for his application. Although counter examples can be given, in practice trying to minimize the total complexity of all branches at every step often results in a canonic or pseudo-canonic circuit.

As an example for the application of this method a 2nd order notch filter will be designed.

In order to obtain a filter with good sensitivity properties, the transfer function will first be written in a suitable way, using a form that is more or less comparable with the one used in [28]. The desired form of the transfer function is:

$$H(z^{-1}) = u \frac{z^{-2} - z^{-1}(2 - \sigma) + 1}{z^{-2} - z^{-1}(2 + \mu - \epsilon) + (1 + \mu)} = \frac{p^2 \upsilon + d^2 \gamma}{p^2 + d^2 \epsilon + p\mu}$$

(4.5)

with  $v, \gamma, \epsilon$  and  $\mu > 0, \gamma = \sigma \upsilon$   $d = z^{-1/2}, p = 1 - z^{-1}.$

It can be shown that eq.(4.5) has a much better sensitivity property for its parameters than

$$H'(z^{-1}) = v \frac{z^{-2} + z^{-1}b + 1}{z^{-2} + z^{-1}a_1 + a_0},$$

(4.6)

especially for designs with a high Q or a relative high clock frequency.

Using Mason's rule, a transfer function

$$H = \frac{V_{out}}{V_{in}} \Rightarrow \frac{N}{D} = \frac{N}{1 \cdot D'}$$

(4.7)

can be represented by a SFG as drawn in fig.4.8a.

Before this is done, the numerator and denominator of the considered transfer function are divided by p.

This is done for the following reason. The ('type 4')  $d^2$ -loops can be incorporated in the branches ('type 1, 2 and 3') ending on these loops, by dividing these latter branches by  $1 \cdot d^2 - p$  (Mason's rule). When we restrict ourselves to the application of 'type 1, 2, 3 and 4' branches, any node in the SFG that is not an input node is an amplifier output node, and thus connected to a 'type 4'  $d^2$ -loop. This means that all 'type 1, 2 and 3' branches will be divided by p, so one is in fact working with branches -C/p, dC/p and -C. However, in fig.4.8 the self-loop connected to the filter output node (containing its  $d^2$  loop) is explicitly drawn, so there may exist elements in the numerator or denominator with  $p^1$ . Powers of p higher than 1 are not possible: for instance  $p^2C$  could be written as a product (cascade) of branches  $-pC_1 * -pC_2$ , but the  $-pC_1$ branch, which is not ending on the the filter output node would be divided by p.

The transfer function is now written as:

$$H(z^{-1}) = \frac{pv + \frac{d}{p}^{2} \gamma}{1 - \left[ d^{2} - \frac{d}{p}^{2} \epsilon - \mu \right]}$$

(4.8)

thus in fig.4.8a

$$N = pv + \frac{d}{p}^2 \gamma$$

and  $D' = d^2 - \frac{d}{p}^2 \epsilon - \mu$  (4.9)

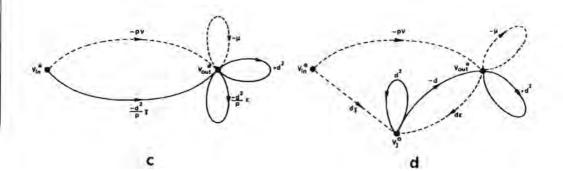

and the SFG can be redrawn as given in fig.4.8b. In the SFG only the  $-\mu$  branch is directly realizable ('type 1'). By means of changing the sign of the output, the pv branch is changed into -pv, which is also realizable ('type 3') (fig.4.8c.).

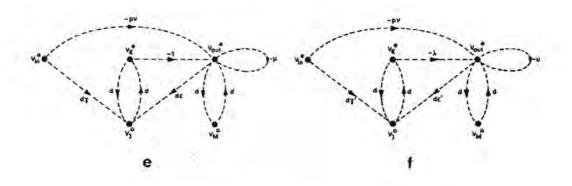

fig.4.8: Development of an elementary SFG (a) by way of a number of intermediate steps (b-e) into a directly realizable graph (f) (Directly realizable branches drawn with dashed lines).

There still are three branches left that are not directly realizable: the d<sup>2</sup> branch, the  $-\frac{d^2}{p}\gamma$  branch and the  $-\frac{d^2}{p}\epsilon$  branch. The latter two branches have the same kind of expression, which makes it obvious to try to combine their realizations. This has been done in fig.4.8d.

Of the three not directly realizable branches, two are d<sup>2</sup> loops, that can be realized introducing a node for each loop and the application of 'type 4' branches. The remaining -d branch can be realized as a cascade of an already existing d branch ('type 4') and a -l branch ('type 1'), as shown in fig.4.8e.

The -1 branch may be rescaled to a value of  $-\lambda$ , when the dy and de branches are rescaled accordingly to a value of  $d\gamma'=d\gamma/\lambda$  and  $d\epsilon'=d\epsilon/\lambda$ , resulting in the final SFG of fig.4.8f.

This rescaling has the advantage of resulting in more acceptable capacitor ratios, especially for relative high clock frequencies.

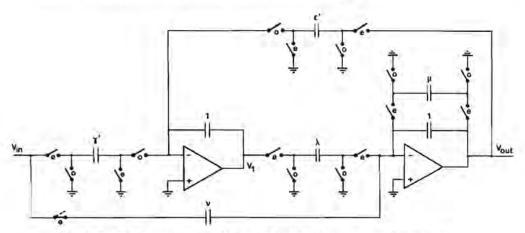

When we rename  $V_j^o$  to  $V_1^o$ ,  $V_k^a$  to  $V_1^o$  and  $V_m^o$  to  $V_{out}^o$ , this final SFG can now be translated into a SC circuit, using table 4.2.

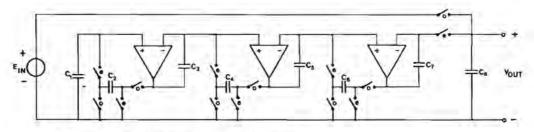

A direct translation results in the circuit of fig. 4.9.

fig.4.9: SC circuit as obtained by a direct translation of the SFG of fig.4.8f, using table 4.2.

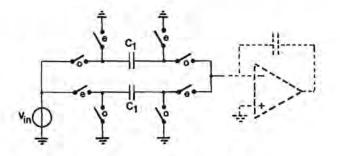

This circuit can be simplified, by means of the well-known 'switch-sharing' method: a closer look at the circuit reveals that there are many nodes that have the same voltage in both clock-phases and can thus be short-circuited. Then a great number of switches, being active in the same clock-phase can be seen to function in parallel, so there are many redundant switches in the circuit, that can be omitted (fig.4.10).

fig.4.10: Final circuit for a strays-insensitive notch filter, realizing the transfer function of eq.(4.5).

It is interesting to know, that exactly the same transfer function is realized by a different circuit, well-known as the 'Gregorian notch biquad' [29].

Since the formula for its transfer function equals that of eq.(4.8), it will have the same sensitivities for the capacitor values as for the circuit of fig.4.10.

However, a closer look at both circuits reveals a number of differences between them.

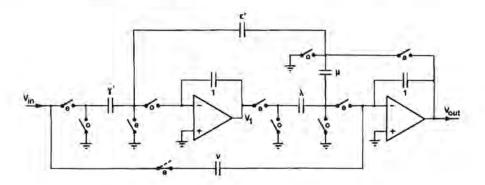

In the first place the lack of need for an input signal that is fixed over a full clock period (symbolized by the sample & hold circuit in fig.4.11) in the circuit of fig.4.10 can be mentioned. Furthermore, counting the switches in both circuits shows that there is one switch less in our circuit.

When the output voltage is only needed in clock-phase 'o', the switch drawn with a dashed line can be omitted, as will be shown in chapter 5, saving another switch.

In a design example, given by Gregorian in the same paper, the circuit is dimensioned for a notch frequency of 60 Hz, a 3-dB bandwidth of 58 Hz and a sampling frequency of 8 kHz. As it turns out there, the

fig.4.lla: Gregorian notch biquad, b; corresponding SFG representation.

values of capacitances  $\mu$  and  $\epsilon'$  are almost equal. This gives the possibility of saving additional components, by means of application of what will be called 'capacitor sharing'. This will be explained in more detail in chap.5. What it means here, is that capacitors  $\mu$  and  $\epsilon'$  can be realized using actually one 'shared' capacitor (fig.4.12).  $\mp$

fig.4.12: Simplified version of the circuit of fig.4.10, obtained by the 'shared' application of capacitance  $\mu_{-}$

With a very small correction on the capacitances  $\gamma^*$  and  $\lambda$ , this circuit realizes exactly the same transfer function as the circuits of figs.4.11 and 4.12.

This 'capacitor sharing' is not possible for the Gregorian motch biquad.

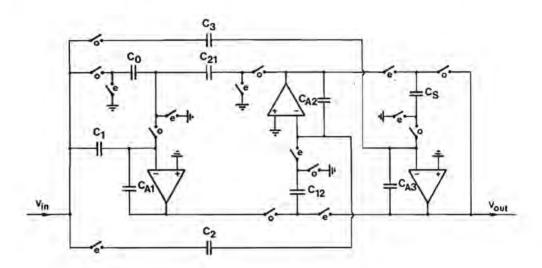

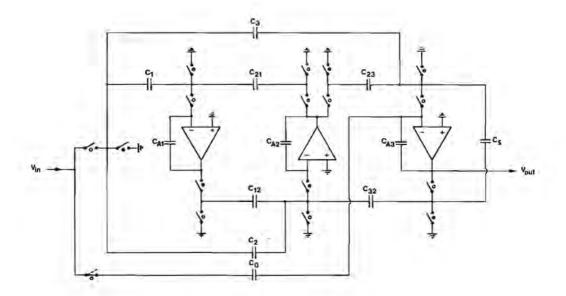

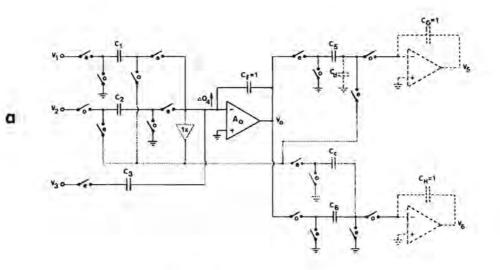

### 5. SC SYNTHESIS BASED ON A 'STRAYS-INSENSITIVE DESIGN GRAPH'.

In this chapter another synthesis method is presented, which is also based on the application of a SFG, composed of branches of the basic set only ('types 1 - 5').

This method does not give the designer the same amount of freedom as the previous approach, but depends on a SFG with a more or less fixed structure.

One of the main advantages of this method is, that it is far more an algorithmic procedure than the approaches that were presented in sections 4.2 and 4.3.

Other essentials of the considered synthesis method are as follows.

- As an 'input' for this method, a normal transfer function in the z-domain, that has not been specially shaped, will be used. There is no need of a continuous-time prototype filter.

- The 'output' of this method is a strays-insensitive biphase clocked SC circuit with exactly enough degrees of freedom to optimize the dynamic range and to minimize the total capacitance.

- With the exception of a small class of transfer functions, this method is canonic in the number of amplifiers that are applied for their realization.

- For a majority of transfer functions, this method can also handle input signals that are not fixed over a full clock-period.

- On the other hand, the produced output signal itself is fixed over a full clock-period, making it compatible with other filter inputs. This allows us easy cascading of filter networks.

- The filter has no delay free loops containing more than one amplifier.

- The resulting filter structures have good sensitivity properties for their capacitors and amplifier gains in comparison with a number of other designs. Moreover these structures inherently have advantages for the sensitivity to the bandwidth of the applied amplifiers.

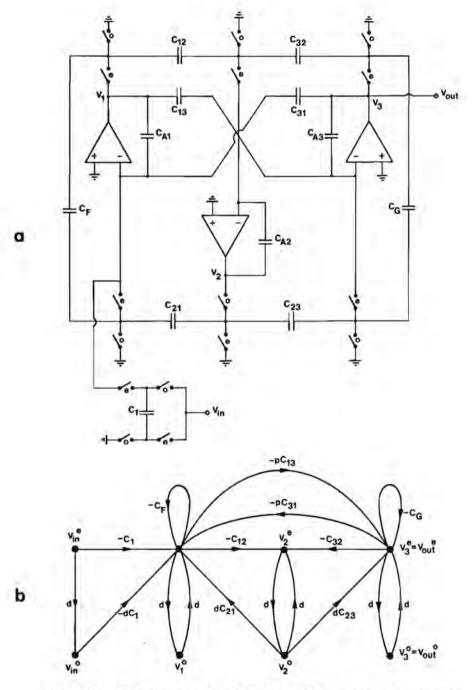

First, in section 5.1, two general Strays-insensitive Design Graphs (SDG's), with the above-mentioned properties, will be derived.

As an example, SC filters will be designed in section 5.2, using this SDG approach. Furthermore in this section possibilities for the reduction of circuit complexity and total capacitance, by the application of what will be called 'capacitor sharing' will be described.

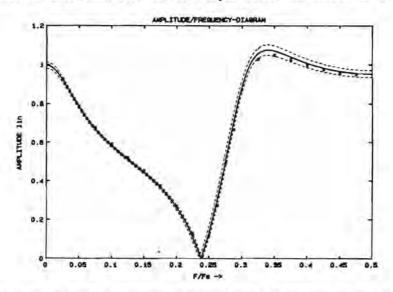

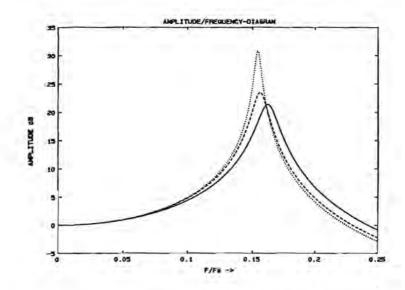

One of the designs of section 5.2 was actually built as a breadboard circuit. In section 5.3 the measured amplitude diagram of this circuit will be compared with theoretical curve.

In section 5.4 the sensitivity of the SDG filters to variations of the capacitances, finite amplifier gain and finite amplifier bandwidth will be discussed.

Finally in section 5.5 it will be considered how to deal with amplifiers that have such a low gain, that it significantly affects the filter behavior.

## 5.1 STRAYS-INSENSITIVE DESIGN GRAPHS.

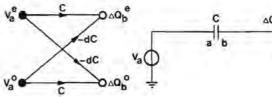

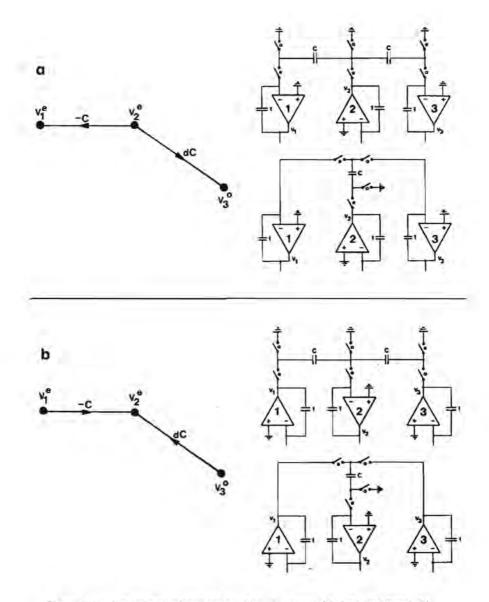

One of the problems that arise when constructing a maximally general SFG for the synthesis of an extensive class of transfer functions is the fact that the signs of the allowed branches (-C, +dC, -pC and d, with  $C \ge 0$ ) are fixed. However, one can circumvent this limitation and realize a transfer of -dC by means of combining a d branch ('type 4') with a -G branch ('type 1'), as depicted in fig.5.1.

fig.5.1:Creation of a -dC 'branch' as a combination of a d branch ('type 4') with a -C branch ('type 1').

This will only work if there are no other branches ending on the  $V_a^o$  node.

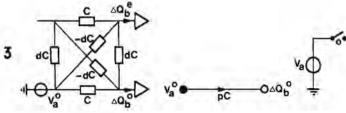

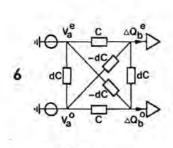

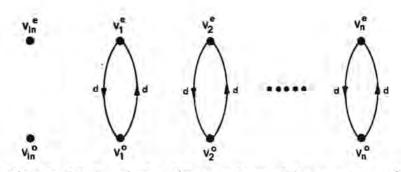

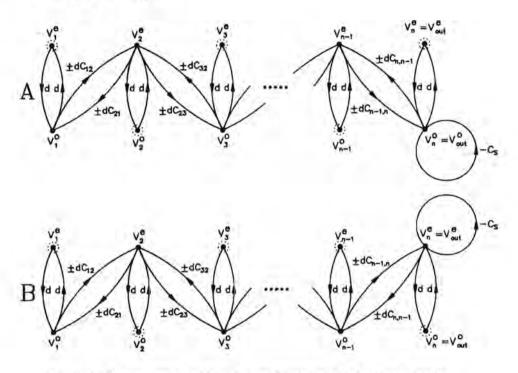

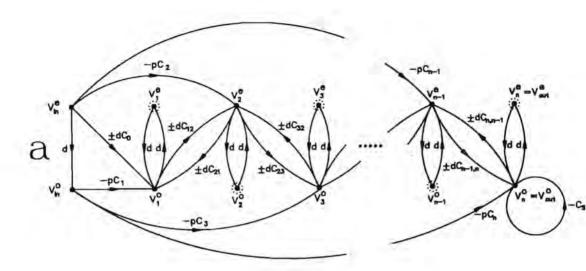

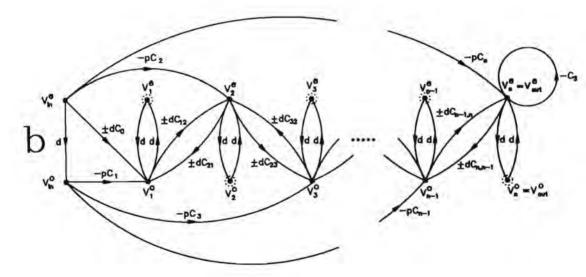

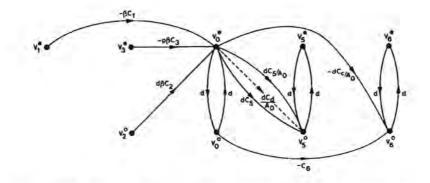

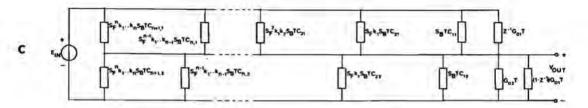

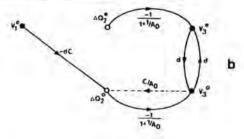

In the following synthesis, we first take only the denominator of the transfer function into consideration. For this purpose, an adequate SFG is given in fig.5.2.

fig.5.2: Loop-structure for the realization of the denominator of the transfer function, a: n odd,

b: n even.

Here the  $\pm dC$  branches are in fact  $\pm dC$  branches ('type 2') or -dC branches, realized with the method of fig.5.1 (combining 'type 1 & 4').

To be able to apply the method of fig.5.1 in all situations, no 'type 1, 2 or 3' branches may end on the nodes marked with a dashed circle in fig.5.2.

The only sign that is really fixed is the sign of the -C self-loop. Using Mason's rule it can be shown that the product of the realized poles is

$$\prod_{i=1}^{n} z_{\text{pole } i} = \frac{1}{1+C_{n}}$$

(5.1)

which thus yields the restriction:

$$0 < \prod_{i=1}^{n} z_{\text{pole } i} \le 1.$$

Of course the upper bound means no real restriction, because we are only interested in the realization of stable filters.

(5.2)

On the other hand the lower bound means that the class of transfer functions with an odd number of negative real poles in the z-domain can not be realized with the loop-structure of fig.5.2.

When needed, a negative real pole-zero 'doublet' (which we pay for in terms of circuit elements) could solve this problem. The exact position of this 'doublet' on the negative real z-axis can freely be chosen in the range -1 < z < 0, giving the designer a degree of freedom that can for instance be used for the minimization of the total capacitance of the filter. Note that this in fact increases the order of the filter by multiplying its transfer function with

(z + a)/(z + a), 0 < a < 1. Another and often better method is trying to find a transfer function of one order higher than the original. This new transfer function (that of course should not have an odd number of negative real poles) can in general approximate the ideal filter transfer more closely than the original one.

Let us assume that only one branch, with transfer G, would be added to the loop structure of fig.5.2, starting at the input node  $V_{in}^{e}$  and ending on the output node  $(V_{n}^{o}$  for n odd or  $V_{n}^{e}$  for n even). In that case, using Mason's rule, the transfer function could be written as a continued fraction expansion:

54

Again, in this expansion, the only restriction turns out to be the sign of  $+C_{-}$ .

Next the realization of the numerator of the transfer function will be included.

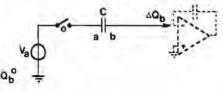

It is assumed here that the input voltage is fixed during the odd clock-phase, such that  $V_{in}^{o} = dV_{in}^{e}$ . (Of course the 'e' and 'o' clock-phase may again be mutually interchanged).

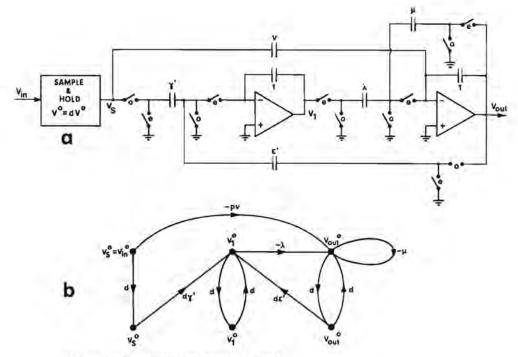

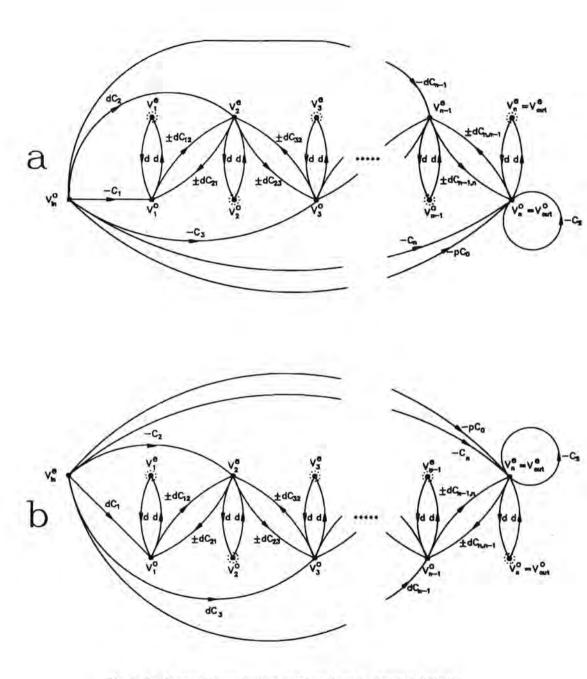

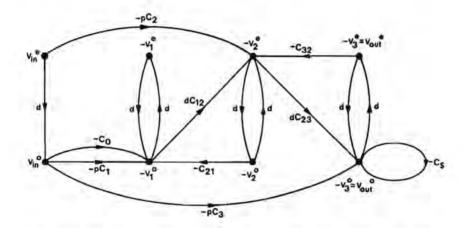

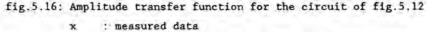

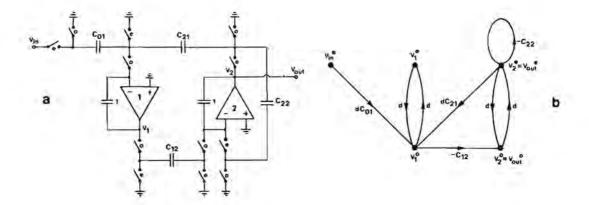

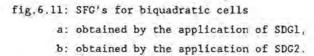

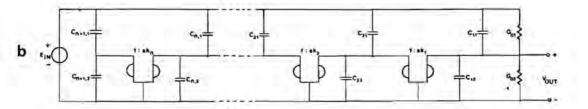

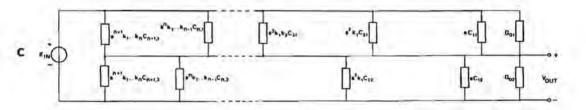

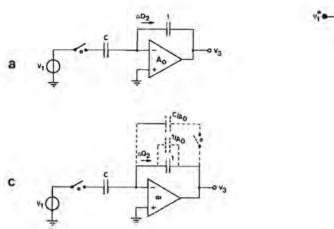

Now branches from the input nodes to several amplifier output nodes are added, such that the marked nodes are not touched. This results in, what will be called a 'Strays-insensitive Design Graph, form 1' (SDG1), as depicted in fig.5.3.

Note that the signs of the -pC branches ('type 3') are fixed.

However, this is not in fact a restriction. In case we should need a +pC branch we use a -pC branch and change the polarity of the node on which this branch ends. Of course we also have to change the signs of all the other branches ending or starting on this node (except for the self-loops), but that is no problem because these are only + or -dC branches, which we can realize both.

The required number of operational amplifiers (represented by the 'type 4' d\*d loops) equals the order n of the filter.

fig.5.3: Strays-insensitive Design Graph, form 1 (SDG1)

- a: n odd

- b: n even

The number of input network branches ('type 1, 2 and 3') equals 3n, which means that after having realized the 2n+1 filter coefficients we still have n-1 degrees of freedom left.

These can be used to optimize the voltage swings of all n-l internal amplifier outputs by means of scaling all capacitors connected to the outputs of these amplifiers.

Furthermore we have n continuous-time feedback capacitors of the opamp networks that we scaled to 1, which means that we have n degrees of freedom that can be used to scale all capacitors connected to the n amplifier inputs in order to minimize the total capacitance.

The only delay free loop is the self-loop  $-C_s$  containing only one amplifier, so no continuous-time loops of amplifiers are created here.

The SDG of fig.5.3 has the disadvantage to require a fixed input signal for a full clock-period.

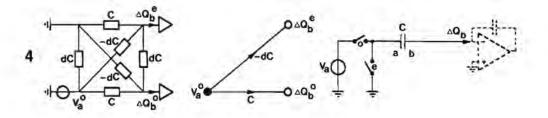

It is also possible to compose a SDG, based on the same loopstructure of fig.5.2 with only a single input node for one clock-phase. This results in the 'Strays-insensitive Design Graph, form 2' (SDG2), as shown in fig.5.4.

Because this SFG has the same loop-structure as the graph of fig.5.3, the same remarks about the denominator of the transfer function can be made here.

As a result from the fact that signs of both  $-pC_0$  and  $-C_n$  are fixed in this graph, there is a restriction for the numerator of the transfer function that can be realized with this SDG2. Using Mason's rule it can be shown that the product of the realized transmission zeros is

$$\prod_{i=1}^{n} z_{\text{zero } i} = \frac{C_0}{C_0 + C_n}$$

(5.4)

which yields:

$$0 \leq \prod_{i=1}^{n} z_{\text{zero } i} \leq 1 \tag{5.5}$$

The lower bound means that it is not possible to realize an odd number

fig.5.4: Strays-insensitive Design Graph, form 2 (SDG2)

- a: n odd

- b: n even

of negative real zeros with this graph, except for the case that there is at least one zero at z = 0 (which means that  $C_{p} = 0$ ).

It should be clear that for transfer functions having less transmission zeros than poles,  $C_0$  will automatically be zero and both of the above-mentioned limitations vanish.

In cases where the upper bound applies, the zeros outside the unit-circle can be transformed into the unit-circle by means of realizing their reciprocal values, provided that the phasecharacteristic is unimportant.

#### 5.2 DESIGN EXAMPLES.

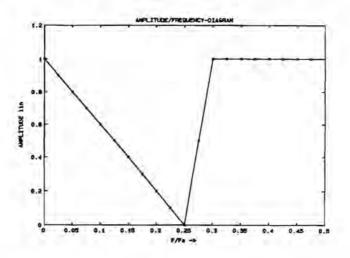

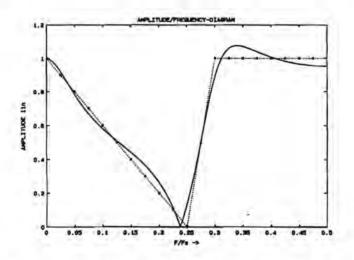

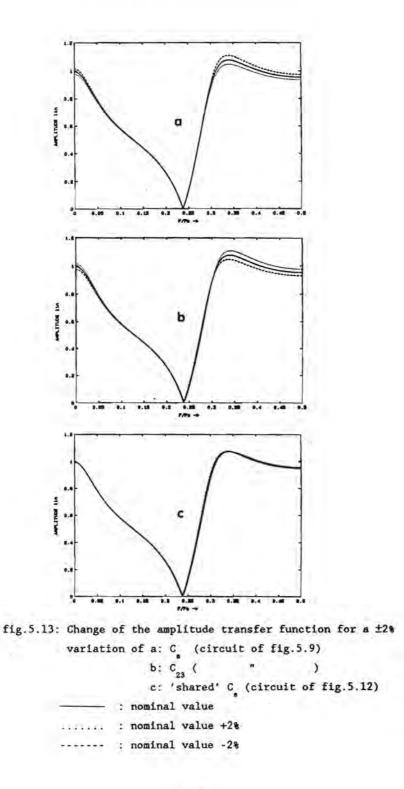

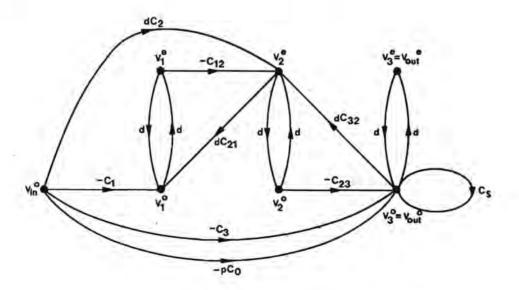

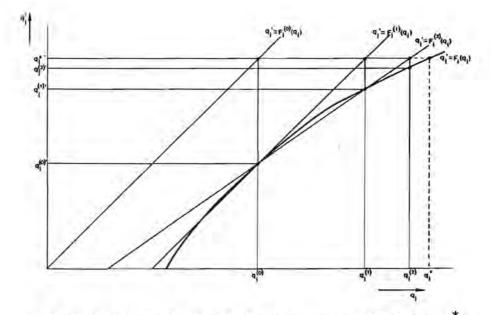

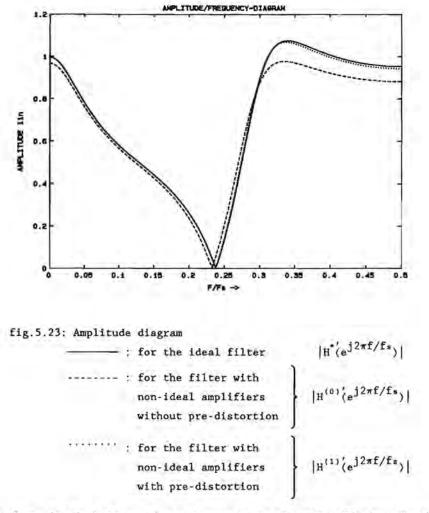

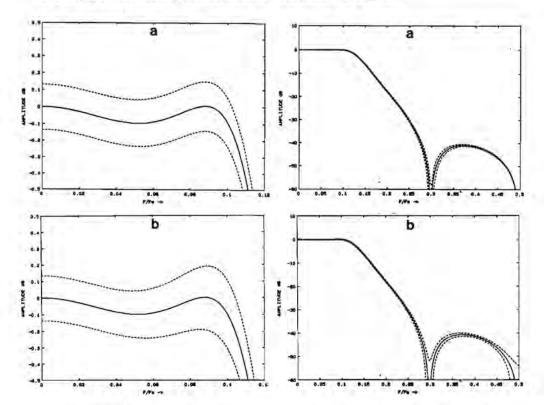

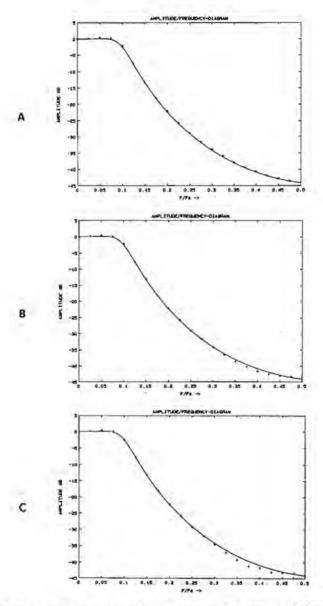

As an example of the synthesis method of section 5.1 a third order filter will be designed, which approximates the fancy amplitude transfer function of fig.5.5 'as good as possible'.

fig.5.5: Ideal amplitude transfer function.