## Formal development of control software in the medical systems domain

Citation for published version (APA):

Osaiweran, A. A. H. (2012). Formal development of control software in the medical systems domain. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Mathematics and Computer Science]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR739209

DOI:

10.6100/IR739209

Document status and date:

Published: 01/01/2012

Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 04. Oct. 2023

# Formal Development of Control Software in the Medical Systems Domain

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus, prof.dr.ir. C.J. van Duijn, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op maandag 17 december 2012 om 16.00 uur

door

Ammar Ahmed Hasan Osaiweran

geboren te Ta'izz, Jemen

Dit proefschrift is goedgekeurd door de promotoren:

prof.dr.ir. J.F. Groote en prof.dr. J.J.M. Hooman

**Formal Development of Control Software in the Medical Systems Domain** / By A.A.H. Osaiweran.

sense and simplicity

This work has been sponsored by Philips Healthcare, Best, The Netherlands. Thesis lay-out and page size of 160 x 450 mm are based on Philips style.

Cover design: Ammar Osaiweran

The work in this thesis has been carried out under the auspices of the research school IPA (Institute for Programming research and Algorithmics). IPA dissertation series 2012–15

A catalogue record is available from the Eindhoven University of Technology Library ISBN: 978-90-386-3276-6

Copyright © Ammar Osaiweran 2012.

## **Contents**

| Pı | eface | <del>)</del>                  |                                          | iii |  |  |

|----|-------|-------------------------------|------------------------------------------|-----|--|--|

| 1  | Intro | Introduction                  |                                          |     |  |  |

|    | 1.1   | The In                        | dustrial Context                         | 2   |  |  |

|    | 1.2   | The su                        | ibject matter                            | 4   |  |  |

|    | 1.3   | Overv                         | iew of the thesis                        | 5   |  |  |

| 2  | Met   | Methods, Tools and Techniques |                                          |     |  |  |

|    | 2.1   | Introd                        | uction                                   | 10  |  |  |

|    | 2.2   |                               | tical Software Design                    | 10  |  |  |

|    |       | 2.2.1                         | The specification of ASD models          | 11  |  |  |

|    |       | 2.2.2                         | The use of data parameters in ASD models | 14  |  |  |

|    | 2.3   | Relate                        | d work                                   | 15  |  |  |

|    | 2.4   | Incorp                        | orating ASD in industrial practices      | 15  |  |  |

|    |       | 2.4.1                         | Steps of developing ASD components       | 17  |  |  |

|    |       | 2.4.2                         | Roles of the interface models within iXR | 18  |  |  |

|    | 2.5   | A shor                        | rt introduction into mCRL2               | 19  |  |  |

| 3  | For   | mal Me                        | ethods in the BasiX Project              | 25  |  |  |

|    | 3.1   | Introd                        | uction                                   | 26  |  |  |

|    | 3.2   | The Po                        | ower Distribution Unit                   | 26  |  |  |

|    |       | 3.2.1                         | Introduction                             | 26  |  |  |

|    |       | 3.2.2                         | The design description                   | 27  |  |  |

|    |       | 3.2.3                         | Modeling and analyzing the PDU behavior  | 32  |  |  |

|    |       | 3.2.4                         | Modeling and verification efforts        | 42  |  |  |

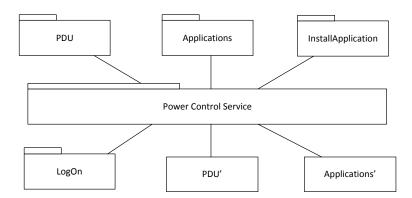

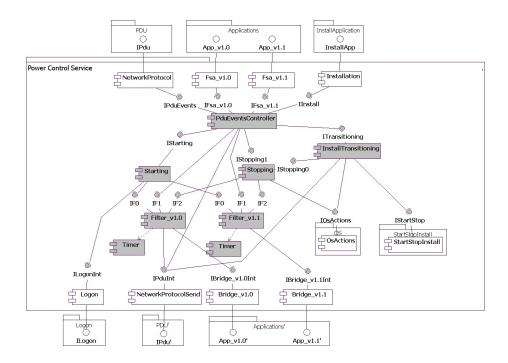

|    | 3.3   | The Po                        | ower Control Service                     | 44  |  |  |

|    |       | 3.3.1                         | Introduction                             | 44  |  |  |

|    |       | 3.3.2                         | Context of the Power Control Service     | 45  |  |  |

|    |       | 3.3.3                         | Steps of developing components of PCS    | 46  |  |  |

|    |       | 3.3.4                         | Results                                  | 50  |  |  |

|    |       | 3.3.5                         | Concluding Remarks                       | 51  |  |  |

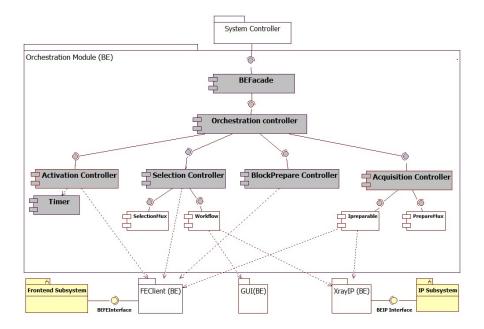

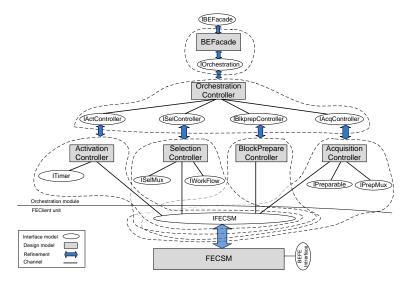

| 4 | Forr | mal Methods in the Backend Subsystem                               | 53  |

|---|------|--------------------------------------------------------------------|-----|

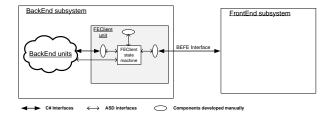

|   | 4.1  | Introduction                                                       | 54  |

|   | 4.2  | The Context of the BackEnd Subsystem                               | 54  |

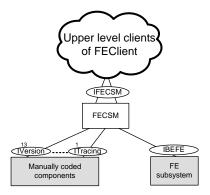

|   | 4.3  | The Frontend Client                                                | 56  |

|   |      | 4.3.1 Introduction                                                 | 56  |

|   |      | 4.3.2 Context of the FEClient unit                                 | 56  |

|   |      | 4.3.3 The application of ASD for developing the FEClient           | 57  |

|   |      | 4.3.4 Type of errors found during developing the FEClient          | 61  |

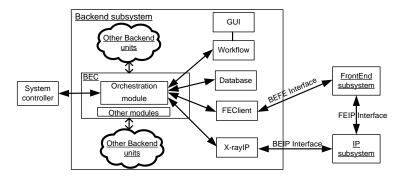

|   | 4.4  | The Orchestration Module                                           | 63  |

|   |      | 4.4.1 Introduction                                                 | 63  |

|   |      | 4.4.2 The context of the Orchestration module                      | 64  |

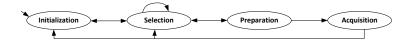

|   |      | 4.4.3 Developing and designing the Orchestration module            | 65  |

|   |      | 4.4.4 Type of errors found during developing the Orchestration     | 70  |

|   | 4.5  | Quality results of the FEClient and the Orchestration              | 71  |

| 5 | Eval | luating the Use of Formal Techniques                               | 75  |

|   | 5.1  | Introduction                                                       | 76  |

|   | 5.2  | Evaluating the Formal Techniques in the Frontend                   | 76  |

|   |      | 5.2.1 Introduction                                                 | 76  |

|   |      | 5.2.2 Description of the project                                   | 77  |

|   |      | 5.2.3 The development process of ASD components                    | 78  |

|   |      | 5.2.4 Data analysis                                                | 83  |

|   |      | 5.2.5 Analyzing the cause of ASD errors                            | 85  |

|   |      | 5.2.6 The quality and performance results                          | 87  |

|   |      | 5.2.7 Conclusions of applying ASD in the Frontend                  | 89  |

|   | 5.3  | Evaluating the Formal Techniques in the Backend                    | 91  |

|   | 5.4  | Other formal techniques used in other projects                     | 93  |

| 6 | Prop | posed Design Guidelines                                            | 97  |

|   | 6.1  | Introduction                                                       | 98  |

|   | 6.2  | Overview of design guidelines                                      | 99  |

|   | 6.3  | Guideline I: Information polling                                   | 101 |

|   | 6.4  | Guideline II: Use global synchronous communication                 | 103 |

|   | 6.5  | Guideline III: Avoid parallelism among components                  | 105 |

|   | 6.6  | Guideline IV: Confluence and determinacy                           | 107 |

|   | 6.7  | Guideline V: Restrict the use of data                              | 113 |

|   | 6.8  | Guideline VI: Compositional design and reduction                   | 119 |

|   | 6.9  | Guideline VII: Specify external behavior of sets of sub-components | 124 |

|   | 6.10 | Conclusion                                                         | 127 |

| 7 | App  | lying the Guidelines to the PDU Controller                         | 129 |

|   | 7.1  |                                                                    | 130 |

|   | 7.2  | The PDU controller                                                 | 130 |

|   | 73   | Strategy and tactics                                               | 134 |

|    | 7.4              | The external specification of the PDU controller        |    |  |  |  |

|----|------------------|---------------------------------------------------------|----|--|--|--|

|    | 7.5              | Implementing the PDU controller using the push strategy | 38 |  |  |  |

|    |                  | 7.5.1 The external behavior of the PCs                  | 38 |  |  |  |

|    |                  | 7.5.2 The design of the PDU controller                  | 40 |  |  |  |

|    | 7.6              | Implementing the PDU controller using the poll strategy | 43 |  |  |  |

|    |                  | 7.6.1 The external behavior of the PCs                  | 43 |  |  |  |

|    |                  | 7.6.2 The design of the PDU controller                  | 45 |  |  |  |

|    | 7.7              | Results of the experiments                              | 47 |  |  |  |

| 8  | Con              | conclusions 1                                           |    |  |  |  |

|    | 8.1              | Introduction                                            | 52 |  |  |  |

|    | 8.2              | Summary of achieved results and observations            | 52 |  |  |  |

|    | 8.3              | Future work                                             | 57 |  |  |  |

| Bi | Bibliography 161 |                                                         |    |  |  |  |

## **Preface**

After the completion of my Master study at the Eindhoven University of Technology and finishing my Master graduation project at Philips Healthcare, I was puzzled between working as a software engineer in industry or pursuing a PhD study in academia. The choice was initially very difficult as both trajectories are very attractive to me. Suddenly, I got an email from my supervisor Jan Friso Groote informing me that people at Philips Healthcare are willing to support my PhD study and whether I would be interested to continue my research on the running projects of Philips.

Without a doubt I was very happy and the offer attracted me since through this opportunity I felt that I could gain lots of experience from both industry and academia. Therefore, I decided to continue having fun biking every day all the way from Eindhoven to Best and accepted the PhD position.

During the last four years, I worked with many people at Philips Healthcare. First, I would like to thank Marcel Boosten, who was my first supervisor at Philips Healthcare, and Wim Pasman, both for arranging all required procedures towards sponsoring my PhD study by Philips. Especial thanks go to Marcel for adapting me to the Frontend team and for the technical and non-technical advices.

I would like to thank everybody I worked with in the Frontend team, especially during my first year. Although at the middle of that period there were many obstacles hindered the progress of this thesis due to changes in the organization, there were certainly many technical lessons and experiences gained when working with the team.

From the Frontend team I would like to thank everyone who had in some way or another contributed in the content of this thesis. I am thankful to Jan Borstrok, Hans van Wezep, Andre Postma, Johan Gielen and Ben Nijhuis, for sharing their expertise and domain knowledge, especially at the period of preparing the reference architecture of the Frontend controller. I am also thankful to Ad Jurriens and Mahmoud Elbanna for providing me the necessary information that helped constructing some of the work presented in this thesis.

At the beginning of my second year, I started a very productive period when joining the workflow team at the Backend. I can not express my deep thanks to my second supervisor at Philips Jacco Wesselius. I am thankful to him for adapting me to the Backend team and for his rigorous comments and valued feedbacks on most of the jointly published papers.

During the work with the workflow team I met many people who favorably contributed to this thesis. I am grateful to Paul Alexander and Bert Folmers for assigning me the development tasks that fit both my research interest and at the same time contribute to the end product. It was very pleasant sharing one office with Roel van Velzen. I am thankful to him for sharing his knowledge regarding the design of the Backend subsystem during the design phase.

I would like to express my thanks to the people I worked with, one by one, including Ron Swinkles, Amol Kakhandki, Amit Ray, Harry Kuipers, Tom Fransen, Paul Langemeijer, Marco van der Wijst and Astrid Morselt. Many thanks go to you all since you never hesitated to help or clarify any issue I faced despite the workload and the limited time you had. It was very pleasant working with you all. I am thankful for Bart van Rijnsover for being my Philips supervisor at the end of my study period and for his support.

From Verum, I would like to thank Leon Bouwmeester and Guy Broadfoot for their valued feedback on the joint work we did at early stage of my study regarding the suitability of ASD to model object-oriented designs.

From the BasiX project, I would like to thank Ivo Canjels, Marc Loos and Rob Kleihorst for explaining the architecture of the PDU and providing me the necessary documents and directions. Also many thanks go to them for their valued feedbacks.

I cannot express my deep thanks to Mathijs Schuts with whom I wrote some of the papers constitute this thesis. Many thanks for his kindness and sharing his knowledge and expertise. I enjoyed accompanying him in Tallinn when presenting one of our papers there.

Many thanks also go to my second promotor Jozef Hooman for assisting me making my work more mature. This thesis would not take its current shape without his directions and valued comments.

I would like to deeply thank my first promotor Jan Friso Groote. Without his advice and directions this thesis may never come to exist. Thank you Jan Friso for helping me to develop as a researcher during the entire 4 years.

Finally, but certainly not last, I thank my parents and wife for their endless support. Especial thanks go to my wife for her patience while preparing this thesis and for the limitless emotional support.

Thank you all!

Ammar Osaiweran, October 2012

# Chapter 1

# Introduction

#### 1.1 The Industrial Context

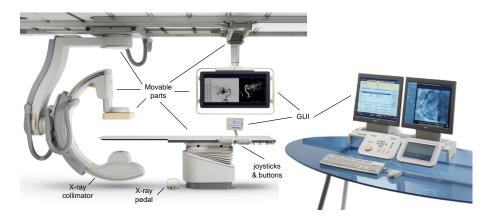

Philips Healthcare develops a number of highly sophisticated medical systems, used for various clinical applications. One of these systems is the interventional X-ray (iXR) system, which is used for minimally invasive surgeries. An example of this type of systems is depicted in Figure 1.1.

Figure 1.1 An interventional X-ray system

As can be seen in the figure, the system includes a number of graphical user interfaces, used for managing patients' personal data, exam, and X-ray details. It also comprises a number of motorized movable parts such as the table where patients can lay and the stand where the X-ray generator and the image detector are fixed. Furthermore, the system contains a number of PCs and devices that host the software that controls the entire system.

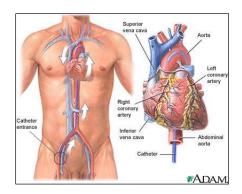

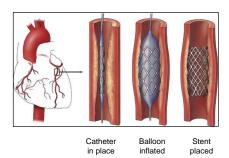

Using this type of systems various clinical procedures can be accomplished. As an example application, the system provides a practical means to avoid open-heart, invasive surgeries. For instance, if a heart artery of a patient is blocked or narrowed, the surgeon inserts a very thin flexible catheter (tube) to the artery of the patient and directs it to the blockage in the affected artery. When the catheter reaches the blockage, a small balloon and a stent are inflated to reopen the artery and flatten the blockage into the artery wall. Along the surgery, the physicians are guided by high quality X-ray images. Figure 1.2 illustrates this type of clinical procedure.

The main benefits of using these systems in hospitals are that they provide more effective and safe treatments, higher success rates, and shorter hospital stays. Therefore, many of these systems are widely used in hospitals, saving patients lives every day, and everywhere.

However, since the healthcare domain is quickly evolving, many challenges are imposed

**Figure 1.2** At the left, the insertion point of the catheter and its course to the heart, clinical users are guided by X-ray images. At the right, treatment of the blockage.

on such type of X-ray systems. This includes, for example, rapidly supporting the increasing amount of medical innovations, new complex and highly sophisticated clinical procedures and smooth integration with the increasing products of third party suppliers. Indeed, this requires a flexible software architecture that can be easily extended and maintained without the need of constructing the software from scratch.

For this reason, the software practitioners at Philips Healthcare are constantly seeking approaches, tools and techniques to advance current software development processes. The purpose is to improve the quality of developed code, enhance productivity, lower development costs, shorten the time to market, and increase end-user satisfaction.

To achieve a fast realization of the above goals, Philips Healthcare is gradually shifting to a component-based architecture with formally specified and verified interfaces. New components are developed according to this paradigm, and existing parts are gradually replaced by components with well-defined formal interfaces.

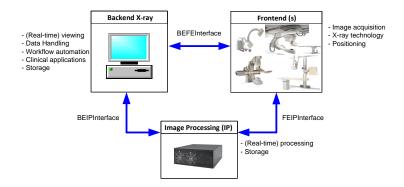

The software architecture divides the X-ray system into three main subsystems called, the Backend, the Frontend and the Image Processing subsystems. We detail their responsibilities in the subsequent chapters. In turn, the software of each subsystem is divided into a number of software units. Each unit comprises a number of modules that include software components with interfaces.

At Philips Healthcare, the component-based development approach is based on a formal approach called Analytical Software Design (ASD) [20, 21, 22]. This approach is supported by the commercial tool ASD:Suite of the company Verum [83]. ASD enables the application of formal methods into industrial practice by a combination of the Box Structure Development Method [65], CSP [79] and FDR2 [34, 79]. The tool ASD:Suite supports the automatic generation of code in high-level languages, such as C++ or C#, from formally verified models.

The aim of using the ASD approach at Philips Healthcare is to build high quality components that are mathematically verified at the design phase by eliminating defects as early as possible in the development life cycle, and thus reducing the effort and shortening the time devoted to integration and testing.

### 1.2 The subject matter

This thesis is concerned with evaluating the use of the ASD formal techniques in industry, and investigating whether the use of the techniques resulted in better quality software compared to traditional development. It details in depth the experiences and the challenges encountered during the application of the techniques to the development of the iXR system, providing practical solutions to the encountered shortcomings. In particular, it evaluates and details the formal development of various software components of the iXR system and investigates the added value of such techniques to the end quality and the productivity of the developed software.

The concept of quality in this thesis refers to the error density in terms of the number of reported defects per thousand lines of code while productivity denotes the number of lines of code produced per staff-hour.

The thesis also discusses a number of design steps and guidelines that facilitate the construction of formally verified software components, based on the experiences gained from designing various industrial cases. To detail these guidelines we employed another formal technology called mCRL2, which we used to formally specify and verify a number of design cases. For each guideline two designs that capture a same application intent are compared in terms of the number of states they produce, given that one design follows the guideline while the other does not. Moreover, we show that these guidelines can provide an effective framework to design verifiable components at Philips Healthcare by applying them to formally specify and verify an industrial case, developed at Philips Healthcare.

This work was established in an industrial context, dealing with real industrial projects and a real product. The results are very conclusive in the sense that, in the context of Philips Healthcare, the used formal techniques could deliver better quality code compared to the code developed in more traditional development methods. Also, the results show that the productivity of the formally developed code is better than the productivity of code developed by projects of Philips Healthcare. Our findings indicate the possibility of a 10 fold reduction in number of errors and a threefold increase in productivity, as a result of applying these techniques.

As observed in [86, 14], there are quite a number of reports detailing the application of formal methods to industrial case studies, but very few published reports of formal methods applications describe second or subsequent use. Similarly, the literature about the incorporation of formal methods in the standard industrial development process is very limited. Therefore, in this thesis, we discuss how the ASD formal techniques were tightly

5

incorporated in the development process of projects established at Philips Healthcare, and we introduce in the following chapters a series of industrial cases, demonstrating continues and subsequent usages of these formal techniques in industry.

This work concerns a PhD thesis funded by Philips Healthcare. The author of this thesis worked 4 days a week at Philips Healthcare as a member of various development teams, participating, monitoring and analyzing the progress of applying formal methods to the development of various components of the iXR product.

The effort was more concentrated on developing the control part of various components using ASD, and investigating the fundamental issues behind the technology and its applicability in industry. The work was accomplished in close contact with team members that include project and team leaders, lead architects, main responsible designers of the units, and the software and test engineers. Regarding the application of formal techniques in industry, the thesis provides answers to various research questions that were raised during the development process of the software. The research questions address various aspects encountered when integrating the formal techniques in industry.

With respect to the accomplished work, the thesis reports about the experiences gained from designing and developing real industrial products and not from designing case studies. The thesis evaluates the ASD technology not only in one project but in a series of projects. To answer some of the research questions raised for some of the projects where the author was partially involved, the author conducted plenty of meetings with the main responsible leaders, architects and designers and then evaluated the projects from the data available in many sources at Philips Healthcare such as version control and the defect management system. After a careful analysis of the data, the data and the results are communicated to the responsible teams for further feedback and comments. The author published the results externally [43, 70, 74, 69, 42, 75, 44] after they are being reviewed and confirmed by the responsible teams. The details are provided in the chapters of this thesis.

#### 1.3 Overview of the thesis

The thesis is divided into two parts and consists of seven chapters. Each chapter concentrates on different aspects of applying formal techniques in industry. The thesis is organized as follows.

The first part details the application of the ASD technology to develop various parts of the X-ray system. It includes four chapters in total.

Chapter 2 introduces the formal methods, tools and techniques that were used in this work. It provides the preliminary concepts needed for understanding the rest of the thesis. First, we start by detailing the fundamentals of the ASD approach, illustrating how the formal approach can be tightly integrated with the standard development processes in industry. Then, we briefly introduce relevant concepts of the mCRL2 language, which we

use to introduce the design guidelines to avoid the state space explosion problem of model checking in Chapter 6. Also we employe the language to formalize a number of industrial designs, specified using the design guidelines in Chapter 7, to show that the guidelines are effective in industrial settings.

Chapter 3 is mainly concerned with detailing experiences of incorporating the ASD technology in industrial practice during a project of the iXR, called the BasiX project. The chapter details two design cases. With the first case we show how the ASD technology was used to formalize and verify a controller of a power distribution unit (PDU) used to distribute electrical power and network signals to the PCs and the devices of the X-ray system. Using this design we elaborate more on how ASD models can be specified, the ASD notations used to model the components, and the formal checks established by FDR2. We discuss how the use of ASD formal techniques resulted in detecting some veiled errors and subsequently improved the quality of the controller.

The second design case is related to the development of a number of services deployed on the PCs of the X-ray system. The services communicate with the PDU across the network to facilitate the automatic start-up and shutdown of the system. Using this case we illustrate how the ASD technology was incorporated with the test-driven development method to develop the software of the service. Since any method or technology used in industry has to be compatible with other used methods, tools and techniques, we illustrate the main challenges and key issues encountered when integrating the ASD technology with available techniques and tools used at Philips, providing some practical solutions for the faced shortcomings. Furthermore, we detail the benefits of applying these formal techniques to the quality of the developed product. The details of this chapter is based on the following publications:

J.F Groote, A.A.H. Osaiweran and J.H. Wesselius. *Analyzing a controller of a power distribution unit using formal methods*. Proceedings of the Fifth International Conference on Software Testing, Verification and Validation (ICST 2012, Montreal, Canada, April 18-20, 2012), (pp. 420-428). IEEE.

A.A.H. Osaiweran, M.T.W. Schuts, J.J.M. Hooman and J.H. Wesselius. *Incorporating formal techniques into industrial practice: an experience report.* Proceedings of the 9th International Workshop on Formal Engineering Approaches to Software Components and Architectures (FESCA'12, Tallinn, Estonia, March 31, ), (Electronic Proceedings in Theoretical Computer Science, ..., pp. ...-...), submitted / in press.

Chapter 4 introduces experiences of developing sizable software units of the Backend subsystem. The first unit is the FEClient, using which we detail the effort spent to develop the control part using ASD and the percentage of time consumed for every development process: requirements, formal modeling and verification, for instance. The second unit is the Orchestration, by which we demonstrate the steps performed to obtain structured components and the peculiarities that made the components easily verified using model checking. For both cases, we discuss the typical errors found during the construction of the units and we show that the errors that could escape the formal verification were

7

easy to find and to fix, not very deep interface or design errors. Finally, compared to the industrial standard, we show that the end quality result of the two units was remarkable, and the units were robust against the frequent changes in the requirements. The details of this chapter is based on the following publications:

- J.F. Groote, A.A.H. Osaiweran and J.H. Wesselius. *Experience report on developing the Front-end Client unit under the control of formal methods*. Proceedings of the 27th ACM Symposium on Applied Computing, The Software Engineering Track (ACM SAC-SE 2012, Riva del Garda, Italy, March 25-29, 2012), (pp. 1183-1190).

- A.A.H. Osaiweran, T. Fransen, J.F. Groote and B.J. van Rijnsoever. *Experience report on designing and developing control components using formal methods*. Proceedings of the 18th international Symposium of formal methods. Cnam, Paris, France, 27-31 August, 2012. (pp. ...-...), submitted / in press

Chapter 5 evaluates the use of the ASD formal techniques in both the Frontend and the Backend subsystems. The chapter highlights the main obstacles encountered during the application of the ASD technology. Furthermore, we compare the end quality and productivity of the units that incorporate ASD with others that were developed in a more traditional development method. We demonstrate the steps followed to empirically evaluate the ASD developed units. The details of this chapter is based on the following publications:

- A.A.H. Osaiweran, M.T.W. Schuts, J.F. Groote, J.J.M. Hooman and B.J. van Rijnsoever. *Evaluating the effect of formal techniques in industry*. (Computer Science Report, No. 12-13). Eindhoven: Technische Universiteit Eindhoven, 21 pp.

- J.F. Groote, A.A.H. Osaiweran and J.H. Wesselius. *Analyzing the effects of formal methods on the development of industrial control software*. Proceedings of the 27th IEEE International Conference on Software Maintenance (ICSM 2011, Williamsburg VA, USA, September 25-30, 2011), (pp. 467-472). IEEE.

The second part is concerned with introducing a number of specification and design guidelines to circumvent the state space explosion problem and detailing their applicability to design real industrial cases. This part of the thesis consists of two chapters.

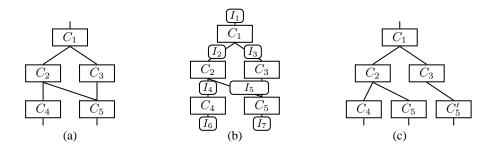

Chapter 6 introduces the guidelines. For each design guideline we introduce two different designs that both maintain the same application intent. The first design does not consider the guideline so it subsequently produces a large state space. The second design uses the guideline so the resulting state space is less compared to the first design. The details of this chapter is based on the following publication:

J.F. Groote, T.W.D.M. Kouters and A.A.H. Osaiweran. *Specification guidelines to avoid the state space explosion problem. Fundamentals of Software Engineering (4th IPM International Conference, FSEN 2011, Tehran, Iran, April 20-22, 2011. Revised Selected Papers)*, (Lecture Notes in Computer Science, 7141, pp. 112-126). Berlin: Springer.

Chapter 7 demonstrates the application of some of the proposed guidelines of Chapter 6 to the design and the verification of the PDU controller, addressed in Chapter 4. We show that the guidelines were effective for designing the controller, and hence could provide a suitable framework to design verifiable components of real industrial cases. The details of this chapter is based on the following publication:

J.F. Groote, A.A.H. Osaiweran, M.T.W. Schuts and J.H. Wesselius. *Investigating the effects of designing industrial control software using push and poll strategies*. (Computer Science Report, No. 11-16). Eindhoven: Technische Universiteit Eindhoven, 19+36 pp.

## Chapter 2

# Methods, Tools and Techniques

#### 2.1 Introduction

This chapter is concerned with a concise introduction to the formalisms, tools and techniques used for modeling, verifying and developing components of the industrial designs presented along the rest of this thesis. First, we introduce the ASD approach. We illustrate its main principles and how the formal techniques supplied by the approach were tightly integrated with the standard development processes of software in iXR projects. The ASD approach was used to develop software components of the industrial projects presented in Chapter 3,4, and 5.

Second, we introduce the mCRL2 language [63] in Section 2.5. We use the mCRL2 toolset to formally analyze a number of design cases. The purpose is to illustrate the effectiveness of various design guidelines and styles that we propose to circumvent the state explosion problem in Chapter 6 and 7.

The reason of choosing mCRL2 as an alternative technology of ASD is that we found that some of the guidelines may not be directly realized using the current version of the ASD:Suite. The mCRL2 toolset is used to merely specify and formally verify the behavior of a number of designs constructed following the proposed guidelines. Code generation of the specified formal models is not of importance here as the main goal is to illustrate how the guidelines may circumvent the state explosion of model checking and lead to construct verifiable components.

## 2.2 Analytical Software Design

Philips Healthcare introduced the ASD technology to its development context in 2006. The technology was initially used as a formal means to formally specify the interaction protocol between the subsystems of the X-ray machine. Then, in 2008 the technology was used as a formal approach to develop various software components of the system. Below we briefly discuss the fundamentals of the approach and how it is being exploited in Philips Healthcare.

ASD is a model-based technology that combines formal mathematical methods such as Sequence-based Specification (SBS) [52] technique, Communicating Sequential Processes (CSP) [79] and the model checker FDR2 (Failures-Divergence Refinement) [79, 34] with component-based software development [26].

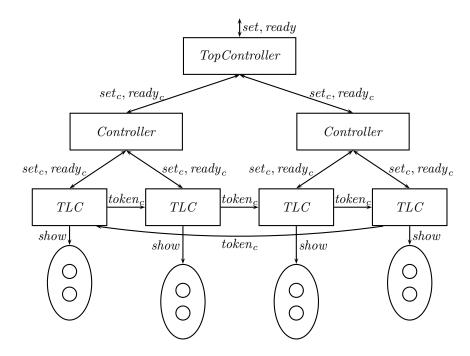

A key principle of ASD is to identify a design of software as interacting components, communicating with each other or their environment via channels (interfaces). A common ASD practice is to distribute system functionalities among components in levels (e.g., hierarchical structure), to allow a systematic construction and verification of each component separately. Each ASD component includes a state machine that comprises input stimuli and output responses.

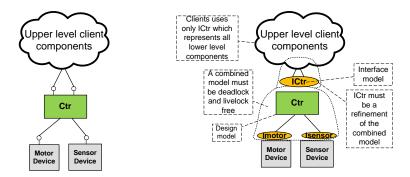

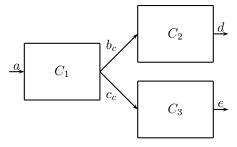

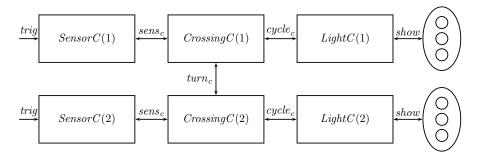

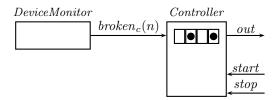

Figure 2.1 at the left depicts an example structure of components, which includes a con-

Figure 2.1 Example of structured components

troller (Ctr) that controls a motor and a sensor. We assume that the motor is responsible for moving the patient table to the left and to the right while the sensor is used to detect any object during the movement to prevent potential collisions. We use this example system along the rest of this chapter.

#### 2.2.1 The specification of ASD models

Any ASD component is realized by constructing two types of models specified in a similar tabular notation: an interface model and a design model. The two models are exploited as follows:

- The *interface* model is an initial abstract state machine of the component being developed. The model is used as a formal means to describe not only the methods to be invoked on the component but also the external behavior with respect to clients. Interactions with components located at a lower level of the component being developed are abstracted away from this interface specification.

- The *design* model of a component refines and extends the interface model with more internal details. From the behavioural perspective, the design model is not an abstract state machine but a concrete state machine in the sense that all detailed behavior is described. Usually, the design model uses the interface models of other ASD and non ASD components (i.e., the handwritten components). These interfaces, in turn, are independently refined by other design models (perhaps by other teams), facilitating multi-site, parallel development of components.

The state machine of the ASD interface model provides a technical description between client and server components, affording a shared understanding of the required behavior. The model represents the protocol of interactions similar to a protocol state machine of

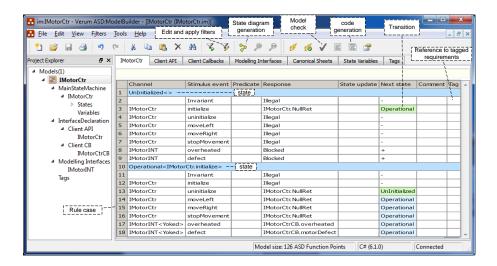

Figure 2.2 The ASD interface model of the Motor in the ASD:Suite

UML [16]. When a design is decomposed into a number of components in levels, a client component uses the interface model of the server component. So a server at one level becomes a client of another component located at a lower level, similar to the Design by Contract approach [64].

To ensure complete and consistent specifications, the models are described using the sequence-based specification technique [72]. That is, any ASD model includes a complete specification in the sense that responses to every possible input stimulus in every state must be described.

An example of the tabular specification related to the interface model of the motor component of Figure 2.1 is depicted in Figure 2.2. As can be seen from the specification, each table is a state, where all potential input stimuli are listed in rule cases (rows of the tables). A rule case comprises a number of items, each of which includes an interface (channel), a stimulus, predicate (conditions on the stimulus), responses, state (or predicate) updates, a next state, comments, and tags of informal requirements.

The set of stimuli of a component consists of events invoked by clients located at an upper level plus callback events sent by used components at a lower level. The set of responses includes events sent to used components plus callback events sent to upper client components. Calls from client to used components are always synchronous, whereas callback events sent by used components to the client components are asynchronous and stored locally in a FIFO queue of the target client component.

To ensure specification completeness, the set of user-defined responses is extended with special purpose responses: *Illegal*, *Blocked*, and *Null*. The *Illegal* response denotes that

invoking a stimulus is illegal. The *Blocked* response denotes that the corresponding stimulus cannot happen. The *Null* response denotes that no action is required when the stimulus event is invoked: consuming a call, for instance.

In all presented models throughout this thesis the *NullRet* response indicates the completion of the client request (i.e., the call is returned to the client). A channel postfixed by *INT* denotes an internal channel, not visible to the client. The corresponding stimulus event of an internal channel denotes a spontaneous event internally generated by the component, not synchronized with any component. A channel postfixed by *CB* indicates a callback stimulus/response event received/sent from/to a queue of the client.

To illustrate the above modeling conventions, consider Figure 2.2. The *NullRet* of rule case 3 indicates that the *initialize* event is successfully completed, and the motor transits to the *Operational* state. The spontaneous *defect* stimulus of the *IMotorINT* channel of rule case 18 denotes that the motor may fail internally for some internal reasons, and as a response the motor notifies the upper controller by sending the *IMotorCB.motorDefect* callback event to the queue of the controller.

The addition <yoked> of rule case 17 and 18 indicates that the number of allowed callbacks (listed in the corresponding response list of the rule case) in the queue is restricted. In our example specification, if the yoking threshold is set to 1 for each of the two callbacks then this means that the queue will include only 2 callbacks at maximum. This is one way to circumvent queue overflow cases in ASD, during formal verification using model checking, since the CSP processes will deadlock when the queue is full.

The specification of ASD design models is restricted to components with data-independent control decisions. This means that the correctness of parameter values of methods is not checked by the tool, and components responsible of data manipulations or algorithms should be implemented by other techniques. The technology is also restricted to the development of components with discrete behavior and does not support the development of timed systems.

To ensure consistency and correctness, mathematical CSP models [79] are automatically generated from the ASD model. To enable better industrial usage, all CSP models are hidden from end-users and the models are verified at a remote server located at Verum. The details of such translation is outside the scope of this thesis.

A vital and very attractive feature in the ASD:Suite is the support of a comprehensive code generation from formally verified design models to a number of programming languages (C, C++, C#, Java), following the state machine pattern of [35]. The details of such translations are irrelevant for this thesis. The translation details are part of the ASD patent described in [22].

#### 2.2.2 The use of data parameters in ASD models

The interface model is used to declare calls received from clients (the implemented interface of the component) and the callbacks sent to client components. Calls and callbacks might include data parameters that must be compatible with the target programming language of code generation.

In the design model these parameters are used as control independent parameters. That is, the parameters, for instance, can not be used in the model as state variables (in the predicates), i.e., they do not affect the behavior of the component as they are only used to pass the data across the component. The design model abstracts from the data details and how the data is processed. Processing the values of these parameters is done by other components written manually.

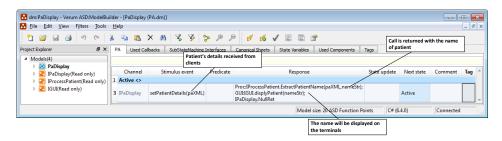

Figure 2.3 Use of data parameters in a design model

To illustrate the parameter usage in ASD consider the example specification of the design model depicted in Figure 2.3. It corresponds to an ASD component that is responsible of displaying a patient name on a screen. The design model uses two interface models representing the external behavior of two handwritten components: *IProcessPatient* and *IGUI* interface models, depicted at the left of the figure and used in the Responses column. The component is used by a client component and receives a stimulus event (*setPatientDetails*) that contains a parameter of an xml string which includes the details of a patient. We assume that the GUI accepts only a string representing the name of the patient to be displayed.

To obtain the name from the xml string the ASD component passes the received string to another handwritten component which extracts the name and returns it to the ASD component with the call. For instance, the parameter *paXML* (patient xml) may be passed to the handwritten code by value while *nameStr* is passed by reference so that *nameStr* will contain the name as soon as the call is returned to the ASD component. When the call is returned from the handwritten code, the ASD component passes the name to the component responsible of displaying the name on the terminal.

The values of parameters can be stored in the ASD components at some states and retrieved later at some other states, if needed. Currently, the parameters and their values

2.3 Related work 15

are not considered during the formal verification using model checking so correctness are checked by other means, for instance testing. Furthermore, checking refinement of the handwritten code against the interface model is not supported.

#### 2.3 Related work

The ASD approach has been inspired by the formal Cleanroom software engineering method [59, 71] which is based on systematic stepwise refinement from formal specification to implementation. As observed in [19], the method lacks tool support to perform the required verification of refinement steps. The tool ASD:Suite can be seen as a remedy to this shortcoming. The additional code generation features of the tool make the approach attractive for industry. Related to this combination of formal verification and code generation are, for instance, the formal language VDM++ [32] and the code generator of the industrial tool VDMTools [27]. Similarly, the B-method [3], which has been used to develop a number of safety-critical systems, is supported by the commercial Atelier B tool [24]. The tool ProB provides facilities to model-check and animate models specified in the B specification. ProB was used in a number of critical systems, most notably railway control. The SCADE Suite [30] provides a formal industry-proven method for designing critical applications with both code generation and verification. Compared to ASD, these methods are less restricted and, consequently, correctness usually requires interactive theorem proving. ASD is based on a careful restriction to data-independent control components to enable fully automated verification.

## 2.4 Incorporating ASD in industrial practices

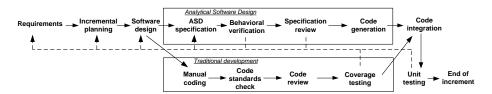

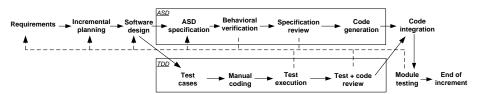

The development process of software used in projects within the context of iXR is an evolutionary iterative process. That is, the entire software product is developed through accumulative increments, each of which requires regular review and acceptance meetings by several stakeholders. Figure 2.4 outlines the flow of activities in a development increment, including the steps required to develop ASD components.

Figure 2.4 Steps performed in a development increment

Developers are divided into groups, each of which is responsible for developing a software unit. Each unit is developed by a team of 2-5 members. Each unit comprises modules which in turn consist of components with well-defined interfaces and responsibilities.

Each increment starts after lead architects and project leaders identify a list of features to be implemented by the development team. As soon as the features and the corresponding requirements are approved, the development team is required to provide work breakdown estimations that include, for instance, required functionalities to be implemented, necessary time, potential risks, and efforts.

Team and project leaders take these work breakdown estimations as an input for preparing an incremental plan, which includes the list of functions to be implemented in a chronological order, tightly scheduled with strict deadlines to realize each of them. The plan is used as a reference during a weekly progress meeting for monitoring the development progress.

The construction of software components starts with an accepted design, i.e., a decomposition into components with clear interfaces and well-defined responsibilities. Usually such a design is the result of iterative design sessions and approved by all team members.

The design clearly distinguishes between control (state machines) and non control components (e.g., data manipulation, computation and algorithms). Non control components are always developed using conventional development methods, while control component are usually constructed using ASD.

Given a software design, the manually written components and ASD components can be constructed in parallel, as depicted in Figure 2.4. For the manually coded components, checking coding standards is mandatory. Such a check is performed automatically using the TIOBE technology [81], and required by quality management. After that, the code is thoroughly reviewed by team members before it becomes a target of coverage testing.

Development teams are required to provide at least 80% statement coverage and 100% function coverage for the manually written code. Upon the completion of coverage testing, the code is integrated with the rest of product code, including the automatically generated code from ASD models. The steps performed to develop ASD components are introduced in the subsequent section.

After that, the entire unit becomes a target of unit test, usually accomplished as a black-box testing. Then, the entire code is delivered to the main code archive, managed by the IBM clearcase technology, where the code is integrated with the code delivered by other team members responsible for developing other units.

At the end of each increment, the units of the Frontend including the ASD components are thoroughly and extensively tested by specialized test teams, using various type of testing such as smoke test, regression test, performance test, statistical test etc, of which details are outside the scope of this thesis. Testing usually reveals some coding errors which are communicated to and resolved by the responsible team.

In the subsequent section, we describe the steps required to develop ASD components in

a given design.

#### 2.4.1 Steps of developing ASD components

When the aim is to use ASD, a common design practice is to organize components in a hierarchical control structure. Typically, there is a main component at the top which is responsible for high-level, abstract behavior, e.g., dealing with the main modes and the transitions between these modes. More detailed behavior is delegated to lower-level components which deal with a particular mode or part of the functionality.

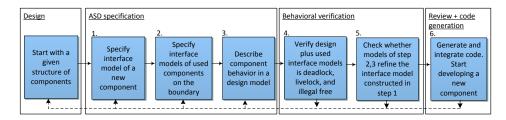

ASD components are created and verified in isolation. The compositional design and verification of isolated components in ASD is essential to circumvent the state space explosion problem. The typical steps required for developing an ASD component are summarized below, according to the steps 1 through 6 of Figure 2.5. We consider developing the *Ctr* component depicted in Figure 2.1 at the right as an example.

Figure 2.5 Steps to develop a component using the ASD approach

- 1. Specification of externally visible behavior. Initially, an ASD interface model of the component being developed is created. Note that this interface model might already exist if the component is used by a component that has been developed already, as explained in the next step.

- For instance *ICtr* in Figure 2.1 is the interface model of the *Ctr* component, where concrete interactions with the sensor and the motor interfaces are not included. *ICtr* specifies how the clients are expected to use *Ctr*.

- Specification of external behavior of used components. Similarly, ASD interface

models are constructed to formalize the external behavior of components that are

used by the component under development. These models describe also the external

behavior exposed to the component being developed.

- For example, the *Imotor* and *Isensor* interface models describe the external behavior related to the *Ctr* component. All other internal interactions not visible to *Ctr* are not present.

- 3. *Model component design*. On completion of the external behavior specification, an ASD design model of the component is created. It describes the complete behavior of the component, including calls to used interface models (as created in step 2) to realize proper responses to client calls.

- For instance the design model of *Ctr* includes method invocations from and to the lower level *Motor* and *Sensor* components.

- 4. Formal verification of the design model. Through this step CSP processes are generated automatically from the interface and design models created earlier by the ASD:Suite. These processes form a combined model that includes the parallel composition of the design model process plus the processes of the used interface models. The combined model is used to verify that the design model uses its used interfaces correctly. This is done by checking a fixed set of properties including searching for deadlocks, livelocks, and illegal invocations using FDR2. We detail these properties in Section 3.2. The ASD verification is compositional [49] in the sense that the design model is verified only with the used interfaces, which are refined by other design models.

- To clarify this step using the *Ctr* component example, a combined model that includes *Ctr* and *Imotor* and *Isensor* is constructed. The behavioral verification checks whether *Ctr* uses the motor and the sensor interfaces correctly, such that no deadlocks, livelocks, race conditions, etc. are present.

- 5. Formal refinement check. In this step the ASD:Suite is used to check whether the design model created in step 4 is a correct refinement of the interface model of step 1. As in the previous steps, errors are visualized and related to the models to allow easy debugging. When the check succeed, the interface model of step 1 replaces all lower level components. It can be used when constructing upper level components. The refinement check is formally established in ASD using the failure or failures-divergence refinement supplied by the FDR2 model checker, where the interface process is the specification and the combined model is the implementation. For instance, when the combined model constructed in step 4 is a valid refinement of the *ICtr* process, *ICtr* formally represents all lower level components during the verification with upper-level client components.

- 6. *Code generation and integration*. After all formal verification checks are successfully accomplished, source code can be generated from the model. The generated code can be integrated with the rest of the code in the target programming language. Furthermore, for every interface model constructed earlier, the previous steps can be repeated until all components are developed.

#### 2.4.2 Roles of the interface models within iXR

The ASD interface model plays important roles along the development of software in iXR projects. Below, some of these roles are summarized.

- 1. The interface model is used as a formal document that specifies the protocol of interaction between two or more components or subsystems (e.g., between the Backend and the Frontend subsystems). It provides a shared understanding and simplifies communication among independent software architects, designers and engineers, responsible of developing different parts of the system.

- 2. The interface model is used to formally represent all lower level components. Since all internal details are abstracted away, the interface behavior is often easy to understand. Furthermore, the formal description of the interface reduces the risk of misunderstanding of certain behavior or critical design decisions.

- 3. When the interface model is formally refined by other lower-level complex models, the model is used for verification with the design models of upper level clients. The interface behavior tends to be simpler than its corresponding composed model, so that verification of clients using model checking can be a straightforward activity. For verification substantially fewer states are generated compared to combining all design models at once.

- 4. When a formally refined interface model of a component is used correctly by ASD clients, the integration of clients' code with the ASD code of the component is typically done without errors (especially during the compilation and the building process of the code).

- 5. The interface model can represent foreign components (hardware devices, legacy code or handwritten code) developed outside ASD by describing the externally visible behavior. Doing this simplifies understanding and implementing the internal code, regardless of the programming language being used.

#### 2.5 A short introduction into mCRL2

We give a short exposition of the specification language mCRL2. We only restrict ourselves to the parts of the language that we need in this thesis. At www.mcrl2.org the toolset for mCRL2 is available, as well as lots of documentation and examples.

The abbreviation mCRL2 stands for micro Common Representation Language 2. It is a specification language that can be used to specify and analyse the behavior of distributed systems and protocols. mCRL2 is based on the Algebra of Communicating Processes (ACP, [8]), which is extended to include data and time.

We first describe the data types. Data types consist of sorts and functions working upon these sorts. There are standard data types such as the booleans  $(\mathbb{B})$ , the positive numbers  $(\mathbb{N}^+)$  and the natural numbers  $(\mathbb{N})$ . All sorts represent their mathematical counterpart. E.g. the number of natural numbers is unbounded.

All common operators on the standard data sorts are available. We use  $\approx$  for equality between elements of a data type in order to avoid confusion with = which we use as

equality between processes. We also use if(c, t, u) representing the term t if the condition c holds, and u if c is not valid.

For any sort D, the sorts List(D) and Set(D) contain the lists and sets over domain D. Prepending an element d to a list l is denoted by  $d\triangleright l$ . Getting the last element of a list is denoted as rhead(l). The remainder of the list after removing the last element is denoted as rtail(l). The length of a list is denoted by #(l). Testing whether an element is in a set s is denoted as  $d\in s$ . The set with only element d is denoted by  $\{d\}$ . Set union is written as  $s_1 \cup s_2$  and set difference as  $s_1 \setminus s_2$ .

Given two sorts  $D_1$  and  $D_2$ , the sort  $D_1 \rightarrow D_2$  contains all functions from the elements from  $D_1$  to elements of  $D_2$ . We use standard lambda notation to represent functions. E.g.  $\lambda x : \mathbb{N}.x+1$  is the function that adds 1 to its argument. For a function f we use the notation  $f(t \rightarrow u)$  to represent the function f, except that if  $f(t \rightarrow u)$  is applied to f, the value f is returned. We call  $f(t \rightarrow u)$  a function update.

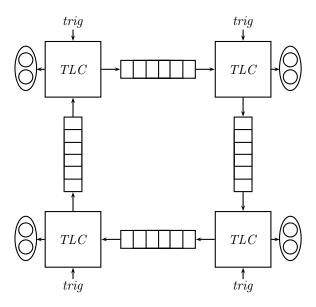

Besides using standard types and type constructors such as *List* and *Set*, users can define their own sorts. In this thesis we most often use user defined sorts with a finite number of elements. A typical example is the declaration of a sort containing the three aspects *green*, *yellow* and *red* of a traffic light.

```

sort Aspect = \mathbf{struct} \ green \mid yellow \mid red;

```

A more complex user defined sort that we use is a message containing a number that can either be active or passive. The number in each message can be obtained by applying the function  $get\_number$  to a message. The function  $is\_active$  is true when applied to a message of the form active(n) and false otherwise.

```

sort Message = \mathbf{struct} \ active(get\_number:\mathbb{N})?is\_active \mid passive(get\_number:\mathbb{N});

```

Using the **map** keyword elements of data domains can be declared. By introducing an equation the element can be declared equal to some expression. An example of its use is the following. The constant n is declared to be equal to 3 and f is equal to the function that returns false for any natural number.

```

\begin{array}{ll} \mathbf{map} & n: \mathbb{N}; \\ & f: \mathbb{N} \to \mathbb{B}; \\ \mathbf{eqn} & n=3; \\ & f=\lambda \, x {:} \mathbb{N}. \mathit{false}; \end{array}

```

This concise explanation of data types is enough to understand the specifications presented in this thesis.

The behavior of systems is characterised by atomic actions. Actions can represent any elementary activity. Here, they typically represent setting a traffic light to a particular colour, getting a signal from a sensor or communicating among components. Actions can carry data parameters. For example trig(id, false) could typically represent that the sensor with identifier id was not triggered (indicated by the boolean false).

In an mCRL2 specification, actions must be declared as indicated below, where the types indicate the sorts of the data parameters that they carry.

```

\begin{array}{ll} \textbf{act} & trig: \mathbb{N} \times \mathbb{B}; \\ & send: Message; \\ & my\_turn; \end{array}

```

In the examples in this thesis we have omitted such declarations as they are clear from the context.

If two actions a and b happen at the same time, then this is called a multi-action, which is denoted as a|b. The operator '|' is called the multi-action composition operator. Any number of actions can be combined into a multi-action. The order in which the actions occur has no significance. So, a|b|c is the same multi-action as c|a|b. The empty multi-action is written as  $\tau$ . It is an action that can happen, but which cannot directly be observed. It is also called the hidden or internal action. The use of multi-actions can be quite helpful in reducing the state space, as indicated in guideline II in section 6.4.

Actions and multi-actions can be composed to form processes. The choice operator, used as p+q for processes p and q, allows the process to choose between two processes. The first action that is done determines the choice. The sequential operator, denoted by a dot ('·'), puts two behaviors in sequence. So, the process  $a \cdot b + c \cdot d$  can either perform action a followed by b, or c followed by d.

The *if-then-else* operator,  $c \to p \diamond q$ , allows the condition c to determine whether the process p or q is selected. The else part can always be omitted. We then get the conditional operator of the form  $c \to p$ . If c is not valid, this process cannot perform an action. It deadlocks. This does not need to be a problem because using the + operator alternative behavior may be possible.

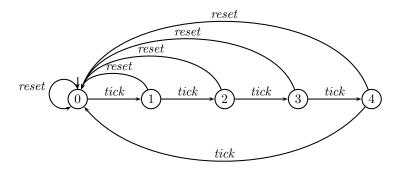

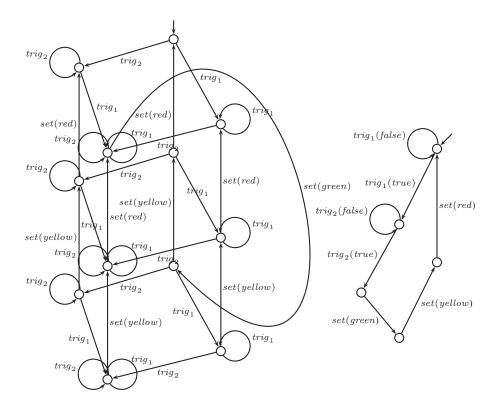

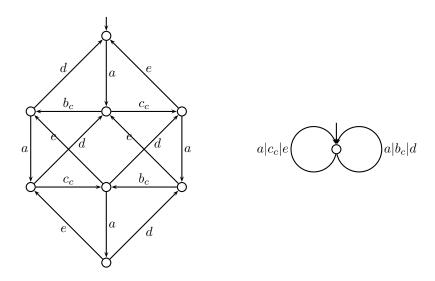

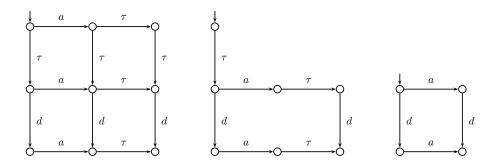

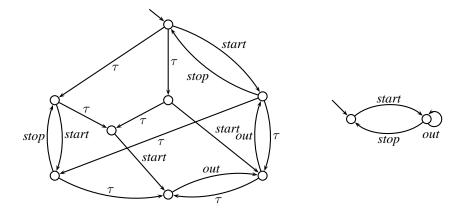

**Figure 2.6** The transition system of the process *Counter*

The following example shows how to specify a simple recursive process. It is declared using the keyword **proc**. It is a timer that cyclically counts up till four using the action

tick, and can be reset at any time. Note that the name of a process, in this case Counter, can carry data parameters. The initial state of the process is Counter(0), i.e., the counter starting with argument 0. Initial states are declared using the keyword **init**. As explained below, we underline actions, if they are not involved in communication between processes.

```

\begin{array}{ll} \mathbf{proc} & Counter(n:\mathbb{N}) \\ & = (n{<}4) \rightarrow \underline{tick}{\cdot}Counter(n{+}1) \diamond \underline{tick}{\cdot}Counter(0) \\ & + \underline{reset}{\cdot}Counter(0); \\ \mathbf{init} & Counter(0); \end{array}

```

In Figure 2.6 the transition system of the counter is depicted. It consists of five states and ten transitions. By following the transitions from state to state a run through the system can be made. Note that many different runs are possible. A transition system represents all possible behaviors of the system, rather than one or a few single runs. The initial state is state 0, which has a small incoming arrow to indicate this. The transition systems referred to in this article are all generated using the mCRL2 toolset [63].

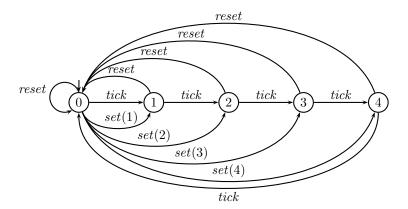

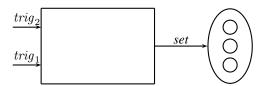

Figure 2.7 The Counter extended with set transitions

Sometimes, it is required to allow a choice in behavior, depending on data. E.g., for the counter it can be convenient to allow to set it to any value larger than zero and smaller than five. Using the choice operator this can be written as

```

\underline{set}(1) \cdot Counter(1) + \underline{set}(2) \cdot Counter(2) + \underline{set}(3) \cdot Counter(3) + \underline{set}(4) \cdot Counter(4)

```

Especially, for larger values this is inconvenient. Therefore, the sum operator has been introduced. It is written as  $\sum_{x:\mathbb{N}} p(x)$  and it represents a choice among all processes p(x) for any value of x. The sort  $\mathbb{N}$  is just provided here as an example, but can be any arbitrary sort. Note that the sort in the sum operator can be infinite. To generate a finite state space, this infinite range must be restricted, for instance by a condition. The example above uses

such a restriction and becomes:

$$\sum_{x:\mathbb{N}} (0 < x \land x < 5) \to \underline{set}(x) \cdot Counter(x)$$

Just for the sake of completeness, we formulate the example of the counter again, but now with this additional option to set the counter, which can only take place if n equals 0. This example is a very typical sequential process (sequential in the meaning of not parallel). In Figure 2.7 we provide the state space of the extended counter.

```

\begin{array}{ll} \mathbf{proc} & Counter(n:\mathbb{N}) \\ & = (n{<}4) \to \underline{tick} \cdot Counter(n{+}1) \diamond \underline{tick} \cdot Counter(0) \\ & + \sum_{x:\mathbb{N}} (n{\approx}0 \land 0{<}x \land x{<}5) \to \underline{set}(x) \cdot Counter(x) \\ & + \underline{reset} \cdot Counter(0); \\ \mathbf{init} & Counter(0); \end{array}

```

Processes can be put in parallel with the parallel operator  $\parallel$  to model a concurrent system. The behavior of  $p \parallel q$  represents that the behavior of p and q is parallel. It is an interleaving of the actions of p and q where it is also possible that the actions of p and q happen at the same time in which case a multi-action occurs. So,  $a \parallel b$  represents that actions a and b are executed in parallel. This behavior is equal to  $a \cdot b + b \cdot a + a \mid b$ .

Parallel behavior is the second main source of a state space explosion. The number of states of  $p \parallel q$  is the product of the number of states of p and q. The state space of p processes that each have p states is p and p larger than 10 this is too big to be stored in the memory of almost any computer in an uncompressed way. Using the allow operator introduced in the next paragraph, the number of reachable states can be reduced substantially. But without care the number of states of parallel systems can easily grow out of control.

In order to let two parallel components communicate, the communication operator  $\Gamma_C$  and the allow operator  $\nabla_V$  are used where C is a set of communications and V is a set of data free multi-actions. The idea behind communication is that if two actions happen at the same time, and carry the same data parameters, they can communicate to one action. In this article we use the convention that actions with a subscript r (from receive) communicate to actions with a subscript s (from send) into an action with subscript s (from communicate). Typically, we write  $\Gamma_{\{a_r \mid a_s \to a_c\}}(p \mid q)$  to allow action s to communicate with s resulting in s in a process s in a process s in order to make the distinction between internal communicating actions and external actions clearer, we underline all external actions in specifications (but not in the text or in the diagrams). External actions are those actions communicating with entities outside the described system, whereas internal actions happen internally in components of the system or are communications among those components.

To enforce communication, we must also express that actions  $a_s$  and  $a_r$  cannot happen on their own. The allow operator explicitly allows certain multi-actions to happen, and blocks all others. So, in the example from the previous paragraph, we must add  $\nabla_{\{a_c\}}$  to

block  $a_r$  and  $a_s$  enforcing them to communicate into  $a_c$ . So, a typical expression putting behaviors p and q in parallel, letting them communicate via action a, is:

$$\nabla_{\{a_c\}}(\Gamma_{\{a_r\mid a_s\rightarrow a_c\}}(p\parallel q))$$

Of course, more processes can be put in parallel, and more actions can be allowed to communicate.

Actions that are the result of a communication are in general internal actions in the sense that they take place between components of the system and do not communicate with the outside world. Using the hiding operator  $\tau_I$  actions can be made invisible. So, for a process that consists of a single action a,  $\tau_{\{a\}}(a)$  is the empty multi-action  $\tau$ , an action that does happen, but which cannot directly be observed.

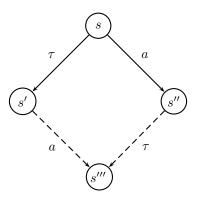

If a system has internal actions, then the behavior can be reduced. For instance in the process  $a \cdot \tau \cdot p$  it is impossible to observe the  $\tau$ , and this behavior is equivalent to  $a \cdot p$ . The most common behavioral reductions are weak bisimulation and branching bisimulation [67, 82]. We will not explain these equivalences here in detail. For us it suffices to know that they reduce the behavior of a system to a unique minimal transition system preserving the essence of the external behavior. This result is called the transition system modulo weak/branching bisimulation. This reduction is often substantial.

Finally, the mCRL2 toolset supports analyzing systems using a number of nice visualization tools and the possibility of verifying properties of systems using the modal  $\mu$ -calculus. Since these means were not used in this work we instead refer to [38, 40, 56] for more information.

## **Chapter 3**

# Formal Methods in the BasiX Project

$<sup>^1</sup>$  Analyzing a Controller of a Power Distribution Unit Using Formal Methods. In: Proceedings of the 5th International Conference on Software Testing, Verification and Validation (ICST 2012)

<sup>&</sup>lt;sup>2</sup> Incorporating Formal Techniques into Industrial Practice: an Experience Report. In: Proceedings of the 9th International Workshop on Formal Engineering Approaches to Software Components and Architectures (FESCA 2012)

#### 3.1 Introduction

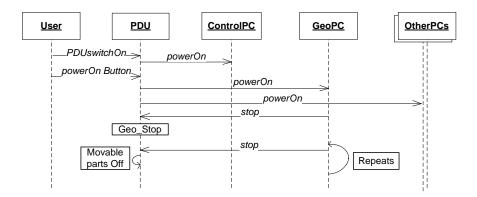

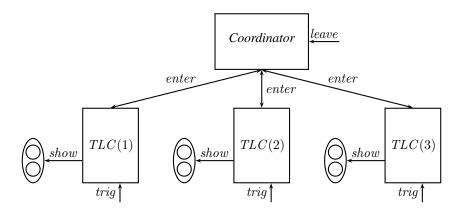

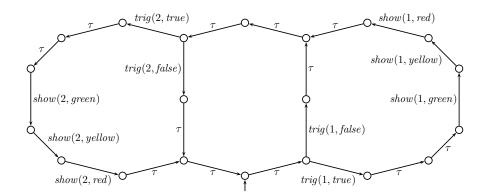

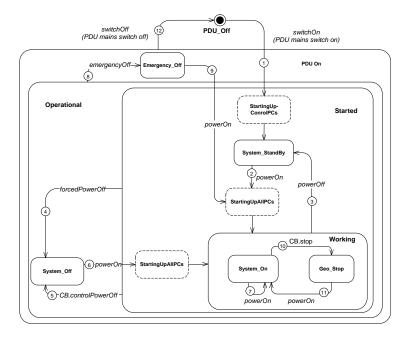

The BasiX project aims at developing a number of infrastructural services of the X-ray machine, such as the systematic startup/shutdown of devices, installation and upgrading of software. The startup/shutdown service is responsible of providing facilities related to the powering aspects between a central power distribution unit (PDU) and a number of PCs that host the clinical applications through a power and a control network.

The BasiX also provides other important services used for automatic installation of both required operating systems and clinical applications on the PCs through the network. Moreover, it provides generic services for logging to allow easy debugging by field service engineers, and for tracing to facilitate debugging by the in-house developers.

In this chapter we introduce two industrial cases where the ASD technology has been applied to the development of control components. In each case we concentrate on distinct aspects related to the application of ASD to the development process.

The first industrial case is introduced in Section 3.2 and is concerned with detailing the steps performed to specify and formally verify a controller of the PDU that supplies the X-ray machine with the required power. In this industrial case, there was no code generated from the specified models; therefore, the ASD formal techniques were merely used for formal specification and verification.

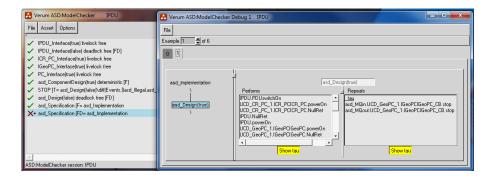

We exploit the PDU controller design to show how interface and design models were specified using the ASD:Suite, how ASD components interact with one another and what types of formal properties are provided by the ASD technology. As a result, two errors were detected in the design of the controller, although the design was thoroughly reviewed by development team before ASD was used.

The second industrial case is introduced in Section 3.3 and is concerned with detailing the processes accomplished for developing the power control service (PCS). This service is replicated and deployed on the PCs of the X-ray machine and interact with the PDU through a communication network. Through this project we propose a workflow to combine ASD and the test driven development approach, answering a few questions regarding the challenges of incorporating ASD to industrial practices and integrating ASD with other tools and methods being currently applied in industry.

#### 3.2 The Power Distribution Unit

#### 3.2.1 Introduction

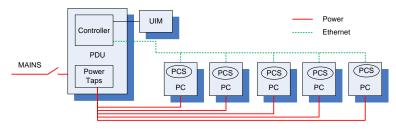

The X-Ray system consists of a number of distributed devices and computers that require a reliable source of power control. The distribution of power to these components is controlled by a power distribution unit (PDU) attached to the main source of power in hospitals.

External users of the system interact with the PDU through an external console, which includes a number of buttons. The console is attached to an embedded controller that controls the flow of power to the components through a number of power taps. The controller communicates with the devices via a network regarding required changes to the powering status of the system. If the PDU does not function correctly components may unpredictably be with or without power when they desire, rendering the system useless or even dangerous.

Throughout this section we illustrate the verification steps of the PDU controller using the ASD approach. Although the design of the controller was thoroughly reviewed, the design included two previously uncovered errors, detected via model checking and specification review enforced by ASD, prior to implementation, at the phase where designers and architects explored various design alternatives.

As will be demonstrated below, specification completeness, specification review and formal behavioral verification provided a key benefit by easily locating design errors in the PDU controller that would be hard to find through conventional testing.

We report about the work accomplished for verifying the controller in this industrial project as follows. Section 3.2.2 introduces the context of the PDU controller. Our experimental method of modeling and verifying the PDU controller is demonstrated in Section 3.2.3, where we further explain the unveiled errors and how precisely they had been discovered. The efforts of modeling and verifying the PDU controller are described in Section 3.2.4.

#### 3.2.2 The design description

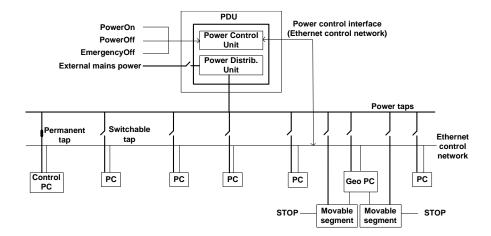

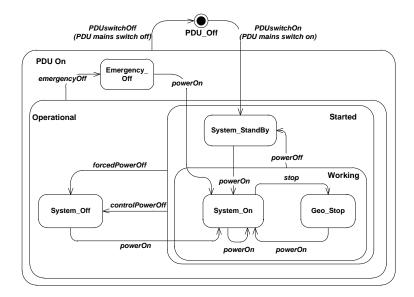

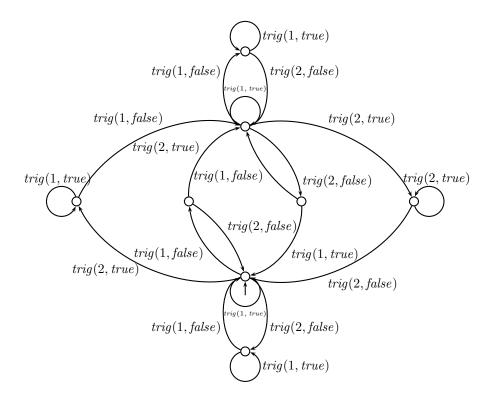

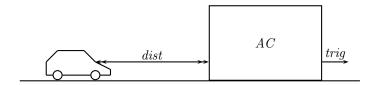

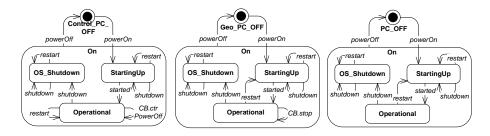

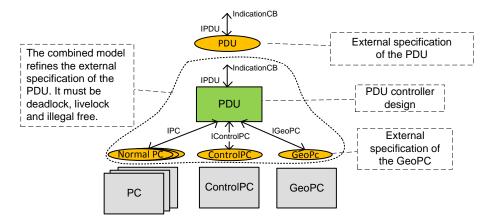

We provide an overview of the design context, hardware and software components, and the signals exchanged through the system. Figure 3.1 demonstrates the structure of the X-ray system depicting a number of distributed devices and PCs connected to a Power Distribution Unit (PDU).

The PDU is attached to an external power source, via a mains switch. The PDU is responsible for distributing power and related communication signals to the attached devices and PCs. Below we detail these components to the extent relevant for this work.

**The Power Distribution Unit** The PDU interacts with its external users by a user console, which contains a number of buttons: *PowerOn*, *PowerOff* and *EmergencyOff*. The PDU also comprises a base module that hosts a number of power taps. It further houses internal units: a Power Control Unit, which controls the flow of network messages, and a Power Distribution Unit, which controls the distribution of power (Figure 3.1).

Through switching the power taps the PDU controls the flow of power to the devices and the PCs. The type of power taps can either be switchable or permanent. The switchable taps can potentially be switched on/off by the PDU upon requests of external users, issued

Figure 3.1 Power, network, and device distribution

by pressing the buttons. For example, when the X-ray system is operational and an external user presses the *PowerOff* button for 3 seconds, all switchable taps are switched off so that all attached components are powered off except those attached to the permanent taps (powering off the system in an orderly fashion).

The permanent taps constantly supply power to a number of components that must always be up-and-running (e.g., for remote access purposes). The permanent taps can also be switched off in some special cases. For example the PDU switches off all taps when the external user presses the *PowerOff* button for 10 seconds (forcing all components to be powered off).

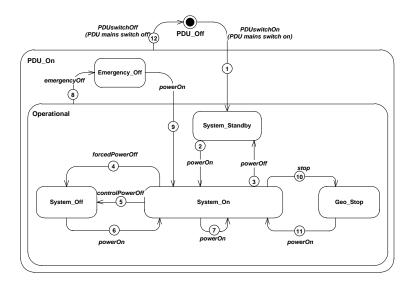

The PDU comprises a controller that includes a state machine for maintaining the states of the system. The state machine is introduced below.

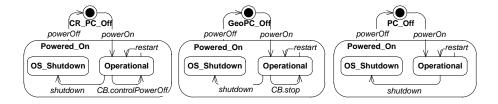

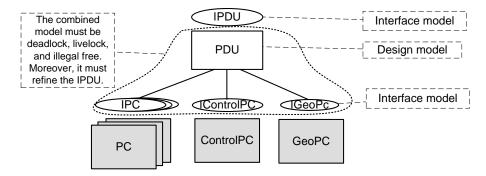

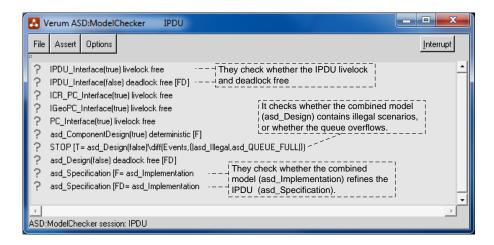

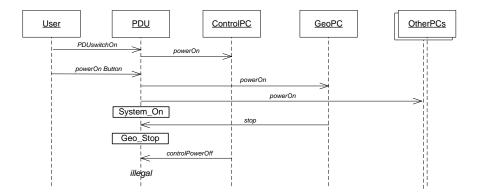

For supplying power to the system in case of failure of the main source of power in the field, an uninterruptible power supply (UPS) is attached to the PDU.