# Cell libraries and verification

Citation for published version (APA):

Raffelsieper, M. (2011). Cell librariés and verification. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Mathematics and Computer Science]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR717717

DOI:

10.6100/IR717717

Document status and date:

Published: 01/01/2011

Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 16. Nov. 2023

# **Cell Libraries and Verification**

### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus, prof.dr.ir. C.J. van Duijn, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op woensdag 2 november 2011 om 16.00 uur

door

Matthias Raffelsieper

geboren te Recklinghausen, Duitsland

Dit proefschrift is goedgekeurd door de promotoren:

prof.dr. H. Zantema en prof.dr.ir. J.F. Groote

Copromotor: dr. M.R. Mousavi

# © 2011 Matthias Raffelsieper

IPA dissertation series 2011-15

The work in this thesis has been carried out under the auspices of the research school IPA (Institute for Programming research and Algorithmics).

A catalogue record is available from the Eindhoven University of Technology Library ISBN: 978-90-386-2799-1

# Contents

| Pr | eface                                                   |                                                                   | iii |  |  |

|----|---------------------------------------------------------|-------------------------------------------------------------------|-----|--|--|

| 1  | Intr                                                    | oduction                                                          | 1   |  |  |

| 2  | Introduction to Cell Libraries                          |                                                                   |     |  |  |

|    | 2.1                                                     | Different Views of a Cell                                         | 7   |  |  |

|    | 2.2                                                     | Transistor Netlist                                                | 8   |  |  |

|    | 2.3                                                     | Verilog Simulation Description                                    | 11  |  |  |

| 3  | Equivalence Checking in Cell Libraries                  |                                                                   |     |  |  |

|    | 3.1                                                     | Semantics of VeriCell                                             | 16  |  |  |

|    | 3.2                                                     | Encoding VeriCell into Boolean Transition Systems                 | 26  |  |  |

|    | 3.3                                                     | Equivalence Checking VeriCell and Transistor Netlist Descriptions | 29  |  |  |

|    | 3.4                                                     | Experimental Results                                              | 30  |  |  |

|    | 3.5                                                     | Summary                                                           | 31  |  |  |

| 4  | Efficient Analysis of Non-Determinism in Cell Libraries |                                                                   |     |  |  |

|    | 4.1                                                     | Order-Independence of VeriCell Descriptions                       | 34  |  |  |

|    | 4.2                                                     | Order-Independence of Transistor Netlists                         | 44  |  |  |

|    | 4.3                                                     | Using Non-Determinism to Reduce Power Consumption                 | 61  |  |  |

|    | 4.4                                                     | Summary                                                           | 71  |  |  |

| 5  | Rela                                                    | ating Functional and Timing Behavior                              | 75  |  |  |

|    | 5.1                                                     | Timing Checks                                                     | 76  |  |  |

|    | 5.2                                                     | Module Paths                                                      | 83  |  |  |

|    | 5.3                                                     | Summary                                                           | 92  |  |  |

| 6  | Productivity Analysis by Context-Sensitive Termination  |                                                                   |     |  |  |

|    | 6.1                                                     | Term Rewriting, Specifications, and Productivity                  | 96  |  |  |

|    | 6.2                                                     | Productivity of Orthogonal Specifications                         |     |  |  |

|    | 6.3                                                     | Productivity of Non-Orthogonal Specifications                     |     |  |  |

|    | 6.4                                                     | Proving Productivity of Hardware Cells                            |     |  |  |

|    | 6.5                                                     | Summary                                                           | 123 |  |  |

| 7  | <b>Productivity Analysis by Outermost Termination</b>   |                                                                   |     |  |  |

|    | 7.1                                                     | Proving Productivity by Balanced Outermost Termination            |     |  |  |

|    | 7.2                                                     | Transformational Outermost Termination Analysis                   |     |  |  |

|    | 7.3                                                     | Summary                                                           | 149 |  |  |

| 8  | Con                                                     | clusion                                                           | 151 |  |  |

## Contents

| Bibliography                        | 155 |

|-------------------------------------|-----|

| Summary                             | 163 |

| Curriculum Vitae                    | 165 |

| A Nangate Open Cell Library License | 167 |

# **Preface**

While finishing my diploma thesis at the RWTH Aachen, I was approached by my then supervisor Jürgen Giesl whether I would be interested in a PhD position in Eindhoven. Thanks to one the regular TeReSe meetings, that in Aachen were dubbed the "Dutch term rewriting community meetings" (including Aken), I was able to meet in Eindhoven with my future supervisors Hans Zantema and Jan Friso Groote, and also with Chris Strolenberg who would be involved in the ValiChip project. Due to the friendly atmosphere and the interesting ValiChip project, that would combine theory with practical applications from the hardware domain, I accepted the position and moved to Eindhoven.

In the beginning, it took me some time to become acquainted with the hardware domain, in particular cell libraries, that was to be the topic of my research. However, both Chris Strolenberg and Jan-Willem Roorda of the industrial partner Fenix Design Automation gave me good pointers, for which I am very thankful. Furthermore, I am grateful for their expert input during the rest of the ValiChip project, which led to the research questions treated in this thesis. It was quite sad that the economic crisis did not spare Fenix Design Automation, so that it had to go out of business in 2009.

I would also like to thank my daily supervisors and (co-)promotors Hans Zantema and MohammadReza Mousavi, who both gave me good advice and helpful technical feedback. Especially, I appreciated their different backgrounds which complemented each other well and that I could always walk into their offices with any problems I had. It was a pleasure working together with both Hans and Mohammad, and resulted in numerous co-authored publications which form the basis of this thesis.

My second promotor was Jan Friso Groote, head of the OAS group and the later MDSE section. He entrusted my daily supervision with Hans and Mohammad, which I believe was a wise choice. I enjoyed working in his group, and profited from the discussions I had with him.

The constructive comments and suggestions I received from the members of my thesis committee, Twan Basten, Hubert Garavel, Jürgen Giesl, Jan Friso Groote, MohammadReza Mousavi, and Hans Zantema, helped to improve the text substantially. I am therefore indebted to the aforementioned people for carefully reviewing my manuscript. Also, I would like to thank Wan Fokkink for agreeing to serve as an opponent in the defense.

During the last four years, I enjoyed meeting numerous people, mostly as members of the MDSE section, on joint projects, at conferences, and through the IPA research school. I really appreciated the inspiring conversations I had with them, which sometimes also went beyond just technical discussions.

Finally, I want to thank my family and friends. I feel deep gratitude towards you for supporting me both before and throughout my PhD period. Thank you.

Matthias Raffelsieper, September 2011

Chapter

# Introduction

Electronic devices have become ubiquitous in modern life. This trend is expected to continue, with devices becoming even faster and even smaller at the same time. Such a development would not have been possible without the tremendous advances in the implementation of digital logic. Moore's Law [Moo65, Sch97], which states that the transistor count of integrated circuits doubles approximately every 18 months, continues to explain these trends, despite having been declared expired a number of times. The most prominent force driving Moore's law is technology scaling; smaller structures consume less power and operate faster. Furthermore, as more transistors are available, there is more opportunity to parallelize computations, thereby leading to another performance improvement.

Due to the increase in transistor count, the functionality implemented in a specific piece of hardware become larger and more complex. Thus, techniques are sought to verify hardware correct, as bugs are inevitable once a certain size or complexity of the hardware design has been reached. One approach to guarantee correct behavior is by testing. However, testing can only investigate a limited number of test cases, thus there can still be untested corner cases in which the device does not function properly. Formal verification is another approach that is not limited to pre-conceived test cases. Instead, it tries to mathematically prove that a model of the device behaves as expected under all circumstances. This approach of formally verifying correctness is the technique used in this thesis to guarantee correctness of hardware devices. Guaranteeing correctness is especially important for hardware, since more and more safety-critical applications make use of it, where a failure can be devastating.

Computer hardware is nowadays mainly designed in a top-down fashion: First, high level descriptions are created which are iteratively refined into a gate-level description (consisting only of simple logic functions and registers) and finally into transistors. This last refinement step, going from gates to transistors, is often performed using cell libraries, which are a collection of basic building blocks, called *cells*, that are both described at a higher abstraction level and at the level of transistors. Hence, it is vital for the correct functioning of a hardware design that these libraries are correct and always describe the same behavior. The main focus of this thesis is to present methods that formally prove different cell descriptions to be consistent with each other. In this way, a hardware design that works correctly at a higher description level is guaranteed to still be correct when implemented. Additionally, some techniques are presented to analyze other aspects of cells, such as power consumption and stabilization, i.e., that always stable output values are computed.

### **Consistency Checking in Cell Libraries**

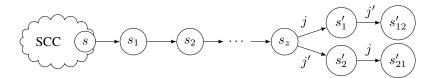

The first technique presented in this thesis verifies that both the simulation level description of cells and the transistor implementations correspond to each other. If this were not the case then a device that seemed to be implemented correctly in simulation runs could fail when implemented as hardware. To faithfully represent both descriptions, the simulation description and the transistor netlist, it is imperative that all possible behaviors that could occur are also present in the model created for them. Otherwise, the model is not general enough and might therefore hide inconsistent behaviors. In the considered cell libraries, a source of non-determinism, i.e., the possibility of multiple behaviors, is a race between inputs that are changed simultaneously. Due to physical effects, such changes are not perfectly synchronized, but arrive in some random order. Such non-determinism is undesired as the final result of a computation cannot be predicted anymore. Most simulators for Verilog [IEE06], a commonly used hardware description language, only implement one fixed order of considering inputs to maximize performance. This however is not backed by the behavior of real hardware; thus it might lead to a mismatch between the simulation and the real behavior.

Faithfully modeling all possible behaviors of hardware descriptions is addressed in this thesis by two methods. First, a formal semantics for a subset of Verilog, large enough to cover most cells from industrial cell libraries, is presented that allows for all possible behaviors. If such a model can be verified to always correspond to the transistor netlist implementation, then also any simulation will do so, since it is contained in the possible behaviors modeled. Implementing and checking such a semantics is however usually very inefficient. Thus, the method only implements one possible behavior. To guarantee that this restriction is not hiding allowed behavior, this thesis presents an efficient technique to analyze non-determinism of cell libraries, both for simulation and transistor level descriptions. If it can be established that the behavior is the same for all possible input orders, then the modeled behaviors and the actually possible behaviors are the same.

Energy consumption of chips has become a very prominent issue lately for numerous reasons. The high integration level of hardware is causing thermic problems if too much heat is produced, which could possibly destroy the chip. Also, mobile applications are ever growing, which are powered by batteries. In these mobile devices, long battery life is desirable, however the weight of the batteries is also limited. Therefore, in mobile applications, energy consumption is a key factor. To analyze the power consumed by a cell, the cell is usually triggered with a large number of input sequences (all input sequences, if possible) in every possible state of the cell and its power consumption is being measured. This thesis proposes a way to reduce the number of required power characterizations by making use of the non-determinism analysis. To this end, the analysis is extended to also consider the number of wires charged when some inputs are changed. Then, only those situations have to be measured where these chargings differ, i.e., for situations resulting in the same power consumption, only one representative has to be considered. A related technique does not determine equal power consumption, but instead the computation that consumes the minimal amount of power without affecting functionality. By enforcing this computation, one can therefore save power without affecting the cell's externally visible behavior. This again makes use of the extended non-determinism analysis, and selects among functionally equivalent computations the one consuming the minimal amount of power.

Hardware descriptions are not only required to be correct from a functional perspective, but also timing must be verified. In case a cell does not satisfy certain timing assumptions, such as independence of the arrival order of certain inputs or stability of outputs, then it cannot be used in designs requiring precisely these assumptions. Timing descriptions are often decoupled from the functional description, however timing and functioning are of course highly related. This link is taken into account in this thesis. It is observed that non-determinism in cells, as already introduced above, has a relation to the constraints on stability windows of its inputs, called the setup and hold times in hardware description languages such as Verilog. These constraints on the inputs of a cell rule out certain sources of non-determinism, thus a cell, which can behave non-deterministically, becomes deterministic when these constraints are satisfied. Therefore, the analysis of non-determinism takes timing information into account. On the contrary, if a cell is found to be non-deterministic even when considering the timing information, then it might be the case that the cell has not been characterized sufficiently, i.e., that additional timing restrictions have to be imposed.

Another requirement on a chip design is that it meets certain desired performance goals. Because hardware designs are mostly synchronous (with respect to a clock signal), all computations have to be finished before the next cycle. Otherwise, old or intermediate values would be used, thereby invalidating the functionality. From a cell level perspective, it is therefore interesting to check how long a change at some input signal takes until all output signals of the cell have reached their final response value. Using this information, one can then go up the design hierarchy to approximate the performance of the complete chip design using the timing information of the cells. For this purpose, each cell is accompanied by a number of *module paths*, which are paths from input to output signals associated with delays. However, as in the case of setup and hold times, these module paths are not linked to the functional description of the cell, i.e., they could possibly not reflect the actual behavior of the cell. In this thesis, a method is presented to check whether both are describing the same cell, by requiring that the module paths and the functional description correspond to each other. This is done on the one hand by verifying that a specified module path exists in the cell, i.e., that a change in the specified input can have an effect on the value of the specified output. If this were not the case, then the module path would describe unobservable behavior, and thus overconstrain the design of the whole chip. In the worst case, a chip design could be found not to meet the desired performance goals due to such a false path. On the other hand, one wants to make sure that for every possible path through a cell timing information is specified, since otherwise no delay is considered and therefore the performance is overapproximated. To this end, a technique is described that enumerates all possible paths through a cell where a changing input can have an effect on the value of an output. Therefore, delays have to be determined for these paths. This allows to ensure that all possible delay behaviors have been considered.

### **Hardware and Streams**

To compute output values from some input values, hardware implemented as transistor netlist is often employing feedback loops, where the output of some function is also being used as its input. This way, for example, on-chip memories (such as flip-flops) are implemented. Thus, it is also interesting to study whether such computations will eventually produce a stable output value, or whether they keep looping forever. This

question is, on an abstract level, the same as that of productivity of streams. There, one is given with a system to compute a stream, i.e., an infinite sequence of (output) values, and is interested whether each of its elements is eventually stable. Hardware can be viewed as a stream function, which has a number of input streams from which it then computes a number of output streams. In this thesis, productivity of streams is studied on a very abstract level, namely that of Term Rewrite Systems. This is a very basic, but powerful technique to describe computations by a number of rules. In this setting, productivity has already been studied before. Some of the previous work abstracted away the concrete values or were restricted to deterministic specifications only. This is different in techniques for checking productivity presented in this thesis, which especially allow arbitrary Boolean streams. Thereby, productivity analysis can be used to prove stabilization of hardware circuits for arbitrary sequences of input values. Removing the approximations however comes with a price, in this case the question whether a given specification is productive or not becomes undecidable. Despite this negative theoretical result, there are numerous systems for which an answer can be given. This is based on the advances in termination analysis, for which nowadays powerful automatic tools are available. Thus, the approach is to transform the productivity question into a termination question, so that existing tools can be employed.

#### Structure of the Thesis

This thesis first gives a brief introduction into the functional descriptions encountered in cell libraries in Chapter 2. As stated above, these will be the main focus of this thesis. Chapter 3, which is based on [RRM09], then presents a technique, together with an implementation and an evaluation thereof, to verify that both simulation description and transistor netlist description of a hardware cell describe the same functional behavior. There, it is observed that cells can behave nondeterministically. This is the topic of investigation in Chapter 4, which is based on [RMR<sup>+</sup>09, RMZ10, RMZ11, RM11]. There, techniques are presented that identify non-determinism that can lead to different functional behavior, and techniques to identify functionally equivalent behavior that differs in power consumption. All of these techniques have been implemented and have been evaluated on industrial cell libraries. In Chapter 5 some non-functional descriptions are considered, namely timing checks and module paths. As already discussed above, they do have a connection to the functional descriptions, in that they also describe functional behavior. The chapter presents techniques to verify that the functional behavior described by these non-functional descriptions is consistent with the simulation description. Also these techniques were implemented and evaluated for industrial cell libraries. They were previously described in [RMR<sup>+</sup>09, RMZ10, RMZ11, RMS10].

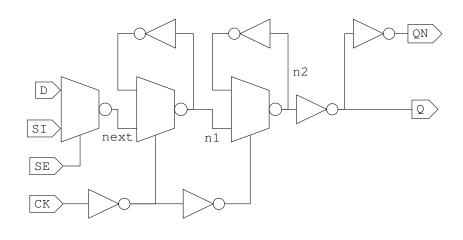

Productivity is studied in Chapters 6 and 7, which, as already mentioned above, can be used to prove stabilization of hardware circuits. In Chapter 6, which presents work from [ZR10a, Raf11], productivity is proven using context-sensitive termination analysis. The approach is also applicable to non-orthogonal specifications, which are natural when checking stabilization of hardware. For both orthogonal and non-orthogonal specifications a tool has been developed that tries to automatically prove productivity. An example application of the latter tool is presented in Section 6.4, where it is proven that an implementation of a scanable D flip-flop taken from an industrial cell library always computes a stable next state.

The technique presented in Chapter 7 was previously presented in [RZ09, ZR10b] and relies on outermost termination to prove productivity. For that purpose, it also presents a transformation from outermost termination problems into standard termination problems, such that state-of-the-art termination provers can be used. This transformation has been implemented in a tool which participated in the outermost category of the annual termination competition 2008 [Wal09] (see [MZ07] for more details on the termination competition), proving some examples outermost terminating for which no other tool was able to do so.

Finally, the thesis is concluded in Chapter 8, where also some possible topics for future work are discussed.

# Introduction to Cell Libraries

A *cell library* is a collection of different combinatorial and sequential elements, called *cells*, that are used to realize larger chip designs. Examples of combinatorial elements are logic functions such as an and gate or an xor gate, whereas sequential elements, such as a flip-flop, provide some kind of memory. Ultimately, a cell is described as a number of lithographic masks, that are read by a wafer stepper to produce the physical implementation of the final chip. Hence, this description is the most important from a manufacturer's point-of-view. However, for a designer working at a higher abstraction level this description is useless, as it does not allow to evaluate the function of the designed chip. Thus, cells are also described from a functional perspective to allow simulation of the final design.

A cell library is typically used by compilers that take as input a higher-level description of a chip design and create a netlist description containing numerous instances of the available cells. Cell libraries are usually provided by external sources and are specifically designed and optimized for a single production technique. To simplify the layout of cells in a chip, all cells have the same height and their power supply connections are at the top and at the bottom. Thereby, cells can be aligned in rows and their power supplies can be connected easily.

In order to produce a final chip design, multiple constraints have to be met, such as timing, total area of the silicon required to implement the chip, constraints regarding power consumption, and more. Furthermore, the chip design should of course implement the desired functionality. To check whether these requirements are satisfied for a concrete chip design, different kinds of information are needed. For example, *timing closure*, the process of repeatedly altering a chip design until it meets its timing constraints, needs detailed information about the timing behavior of the chip's components, i.e., the cells. In contrast, the verification that the logic is correct does not need any timing information; instead the precise computation is interesting. Such pieces of information, relevant to certain parts of the chip design process, are stored in so called *views* in the cell library.

### 2.1 Different Views of a Cell

For a single cell, a cell library contains numerous different descriptions of it. In this thesis, these are divided into *functional* descriptions, that describe the logic operations performed by the cell, and *non-functional* descriptions, that describe other aspects such as timing, layout, or power consumption. The thesis' main focus is

on the functional descriptions, non-functional ones are only considered later and with respect to a functional description. Therefore, in the remainder of this chapter, the functional descriptions will be explained further. They can be subdivided into transistor netlists and simulation descriptions. A transistor netlist of a cell describes the transistors that are present in the physical implementation of that cell and the interconnections among the transistors. Thus, such a description is very close to the finally manufactured chip. On the other hand, a simulation description only models the functional behavior, but is not required to model the exact working of the physical implementation. Thus, in such a simulation description special constructs offered by the language are frequently being used, an example being the User Defined Primitives (UDPs) of Verilog [IEE06]. These help to speed up simulations, but are not easily mapped into a hardware implementation. This thesis will only cover simulation descriptions in a subset of the commonly used language Verilog [IEE06]. However, with some adaptations also other languages, such as VHDL [IEE09], could be used instead.

#### 2.2 Transistor Netlist

Ultimately, any chip design will be implemented using transistors for the logic. A transistor netlist describes these transistors and how they are connected. In the current *CMOS* (Complementary Metal Oxide Semiconductor) design style, two different kinds of transistors are used, *PMOS* (P-channel Metal Oxide Semiconductor) and *NMOS* (N-channel Metal Oxide Semiconductor). In a very rough abstraction, both can be seen as switches, where an NMOS transistor conducts between its *source* and *drain* whenever the *gate* has a high voltage (which is interpreted as a logic 1). A PMOS transistor on the other hand is conducting between source and drain whenever the gate voltage is low (representing a logic 0). MOS transistors also have a fourth connection, called *bulk* or *substrate*, which defines the reference for the gate voltage, but is usually not of relevance in integrated circuits such as cells.

The description of a cell in terms of a transistor netlist is then a number of PMOS and NMOS transistors, together with a number of connections between source, drain, and gate terminals of these transistors, implementing the logic of the cell. Since this is implemented in CMOS style, the logic in the p-doped part and in the n-doped part are *complementary* (hence the 'C'), meaning that a conducting path exists through the PMOS transistors to the high voltage rail (also called  $V_{dd}$ , carrying a logic 1) only if there is no conducting path through the NMOS transistors to the low voltage rail (also called  $V_{ss}$  and carrying a logic 0), and vice versa. If this were not the case, then a direct connection between high and low voltage rail would exist, giving a short-circuit which would burn the chip.

A transistor netlist description is usually given in the input language of the tool *SPICE* (Simulation Program with Integrated Circuits Emphasis) [NP73]. In contrast to the SPICE tool, the exact working of a transistor is not of importance in this thesis and a transistor is, as already explained above, simply viewed as a switch. Thus, in this thesis, a logic function is read from a SPICE netlist.

An example of a (simplified) SPICE netlist taken from a cell library is presented in Figure 2.1. It shows the transistors of a D flip-flop taken from the Nangate Open Cell Library [Nan08]. First, it defines two global signals, the high voltage source VDD and the low voltage source VSS. After that, the subcircuit named  $DFF\_X1$  is defined, which has as interface the input signals CK and D, the output signals Q and QN,

```

.GLOBAL VDD

.GLOBAL VSS

.SUBCKT DFF_X1 CK D Q QN VDD VSS

M_instance_184 VSS CK net_000 VSS NMOS

M_instance_191 net_001 net_000 VSS VSS NMOS

M_instance_197 VSS net_004 net_002 VSS NMOS

M_instance_204 net_003 D VSS VSS NMOS

M_instance_209 net_004 net_000 net_003 VSS NMOS

M_instance_215 net_005 net_001 net_004 VSS NMOS

M_instance_220 VSS net_002 net_005 VSS NMOS

M_instance_226 net_006 net_004 VSS VSS NMOS

M_instance_230 net_007 net_001 net_006 VSS NMOS

M_instance_236 net_008 net_000 net_007 VSS NMOS

M_instance_240 VSS net_009 net_008 VSS NMOS

M_instance_246 net_009 net_007 VSS VSS NMOS

M_instance_254 VSS net_007 QN VSS NMOS

M_instance_261 Q net_009 VSS VSS NMOS

M_instance_267 VDD CK net_000 VDD PMOS

M_instance_274 net_001 net_000 VDD VDD PMOS

M_instance_281 VDD net_004 net_002 VDD PMOS

M instance 288 net 010 D VDD VDD PMOS

M instance 293 net 004 net 001 net 010 VDD PMOS

M_instance_299 net_011 net_000 net_004 VDD PMOS

M_instance_305 VDD net_002 net_011 VDD PMOS

M_instance_311 net_012 net_004 VDD VDD PMOS

M_instance_316 net_007 net_000 net_012 VDD PMOS

M_instance_322 net_013 net_001 net_007 VDD PMOS

M_instance_327 VDD net_009 net_013 VDD PMOS

M_instance_333 net_009 net_007 VDD VDD PMOS

M_instance_339 VDD net_007 QN VDD PMOS

M_instance_346 Q net_009 VDD VDD PMOS

. ENDS

```

**Figure 2.1:** Simplified SPICE netlist of a D flip-flop taken from the Nangate Open Cell Library

and the two voltage sources. Inside the body of the subcircuit, which ends at the keyword .ENDS, the transistors are defined. Every transistor is assigned a name, which has to start with the letter M. After the name of a transistor, its four connections are given, which are *drain*, *gate*, *source*, and *bulk*. The bulk connection is not of importance here, and it is always connected to the corresponding voltage rail (VSS for NMOS transistors, VDD for PMOS transistors). Finally, the type of the transistor is given. In the actual SPICE descriptions, there are additional parameters given after the type in the form of equations, describing physical properties of the transistor. However, these parameters are not of importance when viewing transistors as switches. As an example, the first line M\_instance\_184 VSS CK net\_000 VSS NMOS instantiates an NMOS transistor that connects the low voltage rail VSS to the internal signal net\_000 in case the interface signal CK is high. Together with the PMOS transistor M\_instance\_267 VDD CK net\_000 VDD PMOS, which connects the high voltage rail VDD to net\_000 in case CK is low, it forms an *inverter* which provides the logic negation of signal CK on signal net\_000.

Viewing transistors as switches has already been done by Bryant [Bry87]. In that paper, an algorithm is given to create from a given transistor netlist a description consisting of Boolean equations. These equations describe the logic function of the transistor netlist and hence are taken as the netlist's semantics in the remainder of this thesis. For the example netlist given in Figure 2.1, the following equations are created after simplification (where the logic "and" conjunction  $\land$  binds stronger than the logic "or" disjunction  $\lor$ , as usual):

In these equations, it can be observed that the equations for variables net\_004 and net\_009 implement two latches, with inverted enable signals. The latch net\_004 outputs the negated value of input D if the clock input CK is 0 and it keeps its old value if the clock input CK is 1. For the latch net\_009, the old output value is kept if the clock input CK is 0 and it sets its output value to the value of net\_004 if the clock input CK is 1. The output Q is assigned the negated value of net\_009, since the two transistors M\_instance\_261 and M\_instance\_346 form an inverter with Q as output and net\_009 as input. Finally, the output QN always has the same value as net\_009, as it is the negation of net\_007, which in turn is the negation of net\_009. Therefore, the output QN always is the negation of output Q, as expected.

Note that the method of [Bry87] to extract equations from SPICE netlists works with ternary values, where the third value X denotes "an uninitialized network state or an error condition caused by a short circuit or charge sharing" as is described in [Bry87]. However, it can easily be detected that an equation never outputs the value X. This was used above; thus the variables can only be one of the binary values 0 and 1.

# 2.3 Verilog Simulation Description

To allow simulations of a chip design implemented as cells without resorting to simulating the numerous transistors, cells are also described at a higher abstraction level. For this purpose, the standardized hardware description language *Verilog* [IEE06] is often employed. However, the Verilog language allows for descriptions at various abstraction levels, hence only a certain subset of this language is used. This subset is called VeriCell in the rest of this thesis and is described below. It differs from other subsets of Verilog, such as for example the synthesizable register-transfer level subset described in [IEE05], in that it does not cover behavioral descriptions. Instead, VeriCell focuses on the constructs found in cell library descriptions such as built-in and user-defined primitives, which are not contained in other subsets of Verilog.

The values that signals can take in a VeriCell description are the *ternary constants*  $\mathbb{T} = \{0, 1, X\}$ . Here, the values 0 and 1 behave like the values false and true of the Boolean values  $\mathbb{B}$ , respectively. The third value X is usually understood as representing an unknown value, however the Verilog standard defines it as a third logic value unrelated to both 0 and 1. It should be remarked that the language Verilog also allows a fourth value Z, which represents a high impedance. However, for the VeriCell subset of Verilog this value is equivalent to the value X. This can easily be seen for the considered built-in primitives from Tables 7-3 and 7-4 in the Verilog standard [IEE06]. For user-defined primitives, this is explicitly stated in [IEE06, Clause 8]. Therefore, the value Z is not considered any further.

Furthermore, VeriCell descriptions contain single-bit variables (e.g., CK, D) ranging over  $\mathbb{T}$ , built-in primitives (e.g., **not**, **and**), and user-defined primitives (UDPs). All of these components are defined in a single module, which constitutes the cell. As an example, the VeriCell description of a D flip-flop taken from the Nangate Open Cell Library [Nan08] is given in Figure 2.2. This description has been simplified by leaving out some details that are not of relevance here and writing it in a more compact form.

The example cell is defined in the **module** named DFF\_X1. In parentheses, the interface of the module is defined, which are those variables connecting the module to its environment. The example module has two inputs, the variables CK and D, and two outputs, variables Q and QN, declared in the **input** and **output** lines, respectively. After these declarations, instances of primitives are created. In Vericell, it is required that every primitive instance has a unique output variable, i.e., no two primitive instances share a common output. Primitives **not** and **buf** are built-in primitives. The built-in primitive of **buf** copies the input (the last argument) to its output (the first argument), whereas the built-in primitive **not** provides the negation of the input on its output. Further built-in primitives that are allowed in the Vericell subset are **and**, **nand**, **or**, **nor**, **xor**, and **xnor**, all of which behave as suggested by their name. The syntax and semantics of all of these built-in primitives is defined formally in [IEE06, Clause 7].

The line seq43 (IQ, nextstate, CK) instantiates a *User Defined Primitive* (*UDP*), whose function has to be defined in the source code. This is done between the keywords **primitive** and **endprimitive**. The UDP is first given a name, in this case seq43, which is used in modules to instantiate it. Afterwards, the declaration of the interface and the direction of the variables (input or output) is declared, as is the case for modules. It should be noted that UDPs must always have exactly one output, which must always be the first argument. The number of inputs is allowed to be arbitrary in this thesis (at least one), which corresponds to the general

```

primitive seq43 (IQ, nextstate, CK);

output IQ; reg IQ;

input nextstate, CK;

table

// nextstate

CK

: @IQ :

ΙQ

?

0;

1

?:

r

1;

0

0:

0:

1

1:

?

?:

-;

-;

endtable

endprimitive

module DFF_X1 (CK, D, Q, QN);

input CK, D;

output Q, QN;

seq43(IQ, nextstate, CK);

not(IQN, IQ);

buf(Q, IQ);

buf(QN, IQN);

buf(nextstate, D);

endmodule

```

**Figure 2.2:** Simplified VeriCell description of a D flip-flop taken from the Nangate Open Cell Library

definition of UDPs in the Verilog standard. Note that the standard allows simulators to impose an upper bound on the number of UDP inputs (which must be at least 9), but this does not change the treatment of UDPs presented in this thesis and makes it independent from any specific implementation. The declaration  $\mathbf{reg}\ \$ Q indicates that the UDP is sequential, i.e., the UDPs output does not only depend on the values of the inputs, but also on the previous value of the output, which therefore has to be stored. After the declarations, the logic function of the UDP is defined by means of a table. This table has a column for each input of the UDP, a column separated by a colon to denote the new output value, and another column separated by a colon to denote the new output value. The idea of such a row is that whenever the actual input values match the entries of that row and the previous output value matches the entry in that column of the row, then the new output value is set to the value specified in the last column.

Entries in the input column can either match a single value (called *level* specification) or a transition of values (called *edge* specification). For example, the level specification 0 matches exactly that value, whereas the level specification? matches any value. To match transitions, the first option is to use the syntax (kl) with level specifications k and l. Then, an input changing from an old value  $v \in \mathbb{T}$  to a new value  $w \in \mathbb{T}$  is matched by the specification (kl) if  $v \neq w$ , v is matched by k, and

w is matched by l. It should be noted that the requirement  $v \neq w$  is not demanded in the Verilog standard [IEE06], but is imposed by all Verilog simulators that were tested. Additional abbreviations of common edge specifications exist. In the example, the specification r is an edge specification (rising edge), which is equivalent to the edge specification (01). Other edge specifications used there are f (falling edge) which is equivalent to f (10), and f, which is equivalent to f (10) are transition from some value to any other value). Any row in a UDP may contain at most one edge specification. If there exists an edge specification, then the whole row is called f edge-sensitive. Otherwise, if there are only level specifications, the row is called f level-sensitive.

Since the new value of the output is yet to be determined, the column matching the previous output value may only use level specifications. Finally, the last column, denoting the new output value, may only contain single value level specifications, which are the specifications 0, 1, and x. Additionally, it is permitted to put the special specification –, which can be read as "no change". This specification indicates that the old value of the output is also the new value of the output. As an example, the last row ? f: ?: – of the UDP shall be considered. This row states that if the input CK makes a transition from 1 to 0, then regardless of values of the signal nextstate and the previous output value the new output value is the same as the old output value. Here, it can be seen that adding the specification – can make a UDP definition more compact. If it were not allowed, then one could remove the – by expanding the previous output value specification ? to all three single value specifications 0, 1, and x and then copying the same value into the last column, so that one would replace for example the last row by the following three rows:

```

? f : 0 : 0;

? f : 1 : 1;

? f : x : x;

```

To evaluate a UDP, one therefore searches for a matching row in its table, and takes the output that is denoted in that rows last column. If none of the rows of a UDP matches, then the standard defines the new output to be X. In case multiple rows match, the standard imposes some rules to select the row to be used. These rules will be explained in full detail later in Section 3.1.

The syntax of Verilog, and hence also that of the VeriCell subset, is defined formally in the standard [IEE06]. However, the semantics is not defined formally. In the case of VeriCell descriptions, the exact semantics of UDPs, which is described informally in [IEE06, Clause 8], is ambiguous. Hence, to be able to verify VeriCell descriptions, a formal semantics is defined in Section 3.1 which is used throughout this thesis.

# CHAPTER 3

# **Equivalence Checking in Cell Libraries**

As explained in the previous chapter, cell libraries contain multiple functional descriptions for each cell. Therefore, it should be ensured that every cell has the same behavior in all of these descriptions. If this is not the case, then a design that worked for example in a simulation might fail when produced as a chip, incurring huge costs.

This chapter addresses the problem of verifying that the functional description given in Verilog (or, more precisely, in the VeriCell subset introduced in Section 2.3) exhibits the same behavior as the transistor netlist description. This chapter is based on [RRM09] and presents an operational semantics for VeriCell and encodes it into Boolean equations. Together with the Boolean equations created from the transistor netlist, which are extracted using the algorithm of [Bry87] as discussed in Section 2.2, equivalence can be checked using a model checker, such as for example the NuSMV model checker [CCG<sup>+</sup>02] or the Cadence SMV model checker [McM97], which are specialized on transition systems described as Boolean equations.

The syntax of Verilog, and therefore also the syntax of the VeriCell subset, is formally defined in the IEEE Verilog standard [IEE06]. However, the semantics of this language is left ambiguous in certain parts. It is only explained how certain example situations should be treated, which leaves room for different interpretations. Quite a few publications exist that try to fill the semantic gap, for example in [Dim01, Gor95, HBJ01]. However, they usually address higher level constructs and not those elements found in cell libraries; especially, they do not consider the User Defined Primitives (UDPs). An approach covering some aspects of UDPs is reported in [WW98]. This approach, however, is mainly geared towards an encoding of Verilog into gate level networks (via Ordered Ternary Decision Diagrams, OTDDs). To that end, [WW98] uses heuristics/pattern recognition to detect more complex functions, such as multiplexers and **xor** gates, in the Verilog description. The encoding itself is however not formalized and hence it is unclear how the problems that were identified in the semantics given below are dealt with. An example are multiple inputs to a cell changing at the same time, which gives rise to non-deterministic behavior, as will be shown. Furthermore, the goal of [WW98] was to create correct-by-construction gate level descriptions, whereas here the goal is to enable formal verification of given Verilog cells.

```

1

module flip_flop (q, d, ck, rb);

2

output q; input rb, d, ck;

3

4

not (ckb, ck);

5

latch (iq , d , ck , rb);

latch (qint, iq, ckb, rb);

6

7

buf (q, qint);

8

endmodule

10

primitive latch (Q, D, CK, RB);

output Q; reg Q; input D, CK, RB;

11

12

table

13

//

D

CK

RB

Q:

14

0

(?1)

?

?:

0;

15

?:

1

(?1)

1;

?:

16

?

(?0)

?

17

?

0

0:

?

(?0)

?:

18

?

19

?

(?1)

0

?:

0:

20

0

1

(?1)

:

?:

21

1

1

(?1)

:

1;

22

0

?:

?

:

-;

23

?

0

0:

:

-;

24

(?0)

1

?

?:

0;

:

25

(?1)

1;

26

endtable

27

endprimitive

```

Figure 3.1: VeriCell description of a resettable flip-flop

Traditional equivalence checking techniques used for higher level descriptions, e.g., those based on [vE00], are not applicable to this problem, as they rely on certain structures (for example a synchronous gate-level model and a given set of flip-flops) to perform matching and to apply retiming. However, in the presented setting of cell libraries, no such generic structures exist and the elements are custom made.

### 3.1 Semantics of VeriCell

The language VeriCell is a subset of the Verilog Hardware Definition Language, which is defined in the IEEE standard 1364-2005 [IEE06]. It was already explained in Section 2.3 that VeriCell consists of the built-in primitives, user defined primitives (UDPs), and of modules that define the interconnection of these primitives. An example VeriCell program is given in Figure 3.1, which defines a flip-flop that can be reset.

In the remainder only sequential UDPs will be considered, i.e., UDPs that may contain edge specifications matching input transitions and which furthermore may match the previous value of the output in order to determine their next output value, cf. Section 2.3. This is a syntactic restriction and does not influence the semantics: any combinational UDP can be converted into a sequential UDP by ignoring the previous value of the output, which can be achieved by adding a new penultimate

entry? in every row. For sequential UDPs, the full syntax given in the standard is included in the syntax of VeriCell. Below however, the handling of initial UDP output values is not presented, since it is a rarely used feature and can easily be accommodated by adjusting the initial configuration in which evaluations start.

#### **Preliminaries**

The semantics of VeriCell is defined in an operational style by transforming configurations. In order to define the semantics, first some notations used in the remainder of the section are introduced.

All variables in Verilog can have one of the four values Z, 0, 1, or X. However, for the primitives allowed in the VeriCell subset of Verilog, the values Z and X always have the same meaning, representing an unknown value. Therefore, only the ternary values  $\mathbb{T} = \{0, 1, X\}$  are considered. Here, the values 0 and 1 correspond to the values false and true of the Booleans B, respectively. The value X is intended to represent an unknown Boolean value. Hence, the usual Boolean operations are extended in a pessimistic way, i.e.,  $\neg X = X$ ,  $0 \land X = 0$ ,  $1 \land X = X$ , and  $X \land X = X$ . All other basic Boolean functions on ternary values can be derived from these definitions. Note however that the Verilog standard [IEE06] defines the value X to be a third value, unrelated to the Boolean values 0 and 1. In this thesis, its intended interpretation is that it stands for an unknown Boolean value; however there are even different interpretations in different application domains. For example, the value X also be viewed as a "don't care" during synthesis, see for example [Tur03] for an in-depth discussion of the problems with the value X that occur in higher-level Verilog descriptions. In VeriCell, problems with the value X occur since it can be explicitly matched by UDPs. Hence, a UDP can behave completely different from when an X value is instantiated arbitrarily with either 0 or 1. Thus, the semantics presented here treats the value X as a separate third value, which is exactly the same as in the Verilog standard. A single ternary value  $y \in \mathbb{T}$  is also called a *level*, whereas a pair of two ternary values  $(y^p, y) \in \mathbb{T} \times \mathbb{T}$ , representing a transition, is also called an edge.

Given a VeriCell program, let UDPs (UDPs<sub>n</sub>) denote the set of UDPs in the program (that have exactly n inputs). The set Prims denotes the set of all primitives that are used in the program, comprising both UDPs and built-in primitives.

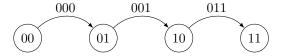

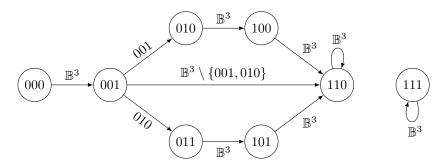

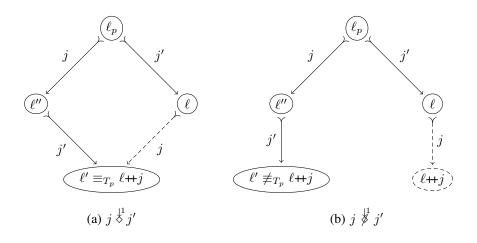

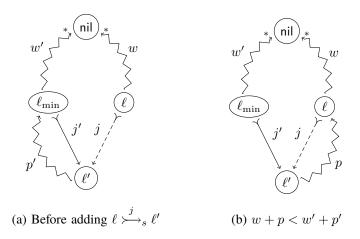

Multiple inputs of a UDP can change simultaneously, even if the inputs of the complete cell are required to only change one at a time. Since UDPs only allow one input to transition, this is treated by considering the changing inputs sequentially. This order is assumed to be subject to influences that are not under the designer's control, hence the order is assumed to be random. To represent these orders, *permutations* are used. For a given number  $n \in \mathbb{N}$  of inputs,  $\Pi_n$  denotes the set of all permutations of the set  $\{1,\ldots,n\}$ . To also be able to represent parts of a permutation, these are generalized to *lists*. A list  $\ell \in \mathcal{L}_n$  is a sequence of numbers from the set  $\{1,\ldots,n\}$  without duplicates, and the set  $\mathcal{L}_n$  represents all such lists. The empty list is denoted by nil, a list having first element j and a tail list  $\ell'$  is denoted by  $j:\ell'$ . As a notational convention, it is allowed to leave out the trailing nil of a non-empty list, thus, for example, the list 1:2: nil may also be written as 1:2. The length of a list is the number of elements it contains. This can be defined inductively by |nil| = 0 and  $|j:\ell'| = 1 + |\ell'|$ . Then, permutations are those lists  $\pi \in \mathcal{L}_n$  with  $|\pi| = n$ . A list  $\ell = j_1: \cdots: j_{|\ell|} \in \mathcal{L}_n$  can be constructed by *concatenating* two lists  $\ell_1, \ell_2 \in \mathcal{L}_n$ , denoted  $\ell_1 + \ell_2$ , if  $\ell_1 = j_1: \ldots j_k$  and  $\ell_2 = j_{k+1}: \cdots: j_{|\ell|}$  for some  $1 \le k \le |\ell|$ .

Next, the semantics of the primitives is defined. This semantics specifies the output value of a primitive given the previous and current values of the inputs and the previous value of the output, which can be expressed by a denotation function. Afterwards, this semantics is lifted to capture the instantiation of primitives and their interconnections. The latter takes the form of deduction rules.

### **Output Value of Primitives**

For the semantics of built-in primitives the straight-forward intuitive semantics given in [IEE06, Tables 7-3 and 7-4] is formalized. However, no such definition exists for UDPs, which therefore will be given below. Then, at the end of this sub-section, the built-in primitives are included to create an evaluation function for both built-in and user defined primitives.

#### Non-Deterministic Output Value Computation of UDPs

The idea of a UDP is to look up the corresponding output value in the table that is given in its declaration for given previous and current values of its inputs and its previous output value, as described in the Verilog standard [IEE06, Clause 8]. The standard requires that level-sensitive rows take precedence over edge-sensitive rows, i.e., if there are both a level-sensitive and an edge-sensitive row applicable to the current input values, then the output is determined by the level-sensitive row. For example, consider a UDP containing the two rows (0?):0:1 and 1:?:0. If the previous output value of this UDP is 0 and the input changes from 0 to 1 then both rows are applicable. But due to the above-mentioned requirement the output must always be 0, since this is the output of the level-sensitive row.

However, the standard does not define how to handle the case of multiple inputs changing at the same time. To this end, the outcome of several Verilog simulators such as CVer [Pra07], ModelSim [Men08], VeriWell [Wel08], and Icarus [Wil07] were compared (unfortunately, some simulators such as Verilator [Sny08] do no support UDPs). It was observed that each of these simulators implements a slightly different semantics for UDPs, where the open source simulator CVer and the commercial simulator ModelSim provide the outcome that is consistent with what is specified in the standard and also closest to the intuition of the designers. One particular difference is the order used by the simulators to evaluate multiple changing inputs. The selection of such an order is not required for the semantics presented here, hence the semantics allows for each of the different simulator behaviors in this respect.

Ultimately, the concrete order used for evaluation should not be affecting the computation results in cases where it cannot be controlled. Otherwise, a simulator that always chooses exactly one order of evaluating changing inputs cannot faithfully model the behavior of the finally produced chip, where the input changes might occur in different orders at different times. This problem is addressed in Chapters 4 and 5, which present analysis techniques to guarantee equivalent behavior for all possible orders.

The level specifications 0, 1, and x that may occur in a truth table of a primitive directly correspond to the ternary values 0, 1, and X, respectively. Hence, for  $l \in \{0,1,x\}$  and  $y \in \mathbb{T}$ , the predicate  $\mathrm{match}(l,y)$  is defined to be true if and only if l and y correspond. This is formally defined in Table 3.1. The additional level specifications b and? are syntactic sugar, where the first one corresponds to both 0

Table 3.1: Matching of UDP specifications to inputs

```

y^p, y, o^p \in \mathbb{T}, e \in \mathbb{T} \times \mathbb{T}, i_1, \dots, i_n \in \mathbb{T} \cup (\mathbb{T} \times \mathbb{T})

\operatorname{match}(1, y) \doteq y = 1

\operatorname{match}(0, y) \doteq

y = 0

\doteq y = x

\operatorname{match}(x, y)

\operatorname{match}(b, y) \doteq \operatorname{match}(0, y) \vee \operatorname{match}(1, y)

\operatorname{match}(?, y) \doteq \operatorname{true}

\mathrm{match}\big(\,(\mathtt{vw})\;,(y^p,y)\big)\;\;\doteq\;\;y^p\neq y\wedge\mathrm{match}(\mathtt{v},y^p)\wedge\mathrm{match}(\mathtt{w},y)

match(r, e) \doteq match((01), e)

\operatorname{match}(f, e) \doteq

\operatorname{match}((10), e)

\operatorname{match}(\star, e) \doteq

\operatorname{match}((??), e)

\operatorname{match}(p, e) \doteq

\operatorname{match}((01), e) \vee \operatorname{match}((0x), e) \vee \operatorname{match}((x1), e)

\operatorname{match}(n, e) \doteq \operatorname{match}((10), e) \vee \operatorname{match}((1x), e) \vee \operatorname{match}((x0), e)

\text{matchRow}(s_1...s_n:s_{n+1}:o,(i_1,...,i_n),o^p) \doteq \bigwedge_{1 \leq j \leq n} \text{match}(s_j,i_j) \wedge \text{match}(s_{n+1},o^p)

```

and 1 and the latter one corresponds to all of the ternary values. Thus,  $\operatorname{match}(b,y)$  is true if and only if y is either 0 or 1, whereas  $\operatorname{match}(?,y)$  is always true, regardless of the value of y.

An edge specification in a UDP has the general form (vw), where v and w are level specifications. Given two values  $y^p, y \in \mathbb{T}$ , the predicate  $\mathrm{match}((vw), (y^p, y))$  is defined to be true if and only if  $\mathrm{match}(v, y^p)$  and  $\mathrm{match}(w, y)$  are true and  $y^p \neq y$ . This latter requirement, which states that indeed a transition must take place, is left ambiguous by the standard, however it is enforced by all simulators of Verilog that were tested, listed previously. The remaining edge specifications  $\mathbf{r}$ ,  $\mathbf{f}$ ,  $\mathbf{p}$ ,  $\mathbf{n}$ , and  $\mathbf{r}$  are expressed using the above and their definitions as given in [IEE06, Table 8-1], as can be seen in Table 3.1. For example, for the rising specification  $\mathbf{r}$  the predicate  $\mathrm{match}(\mathbf{r},(y^p,y))$  is true if and only if  $\mathrm{match}((01),(y^p,y))$  is true, which in turn is true if and only if  $y^p$  is 0 and y is 1, whereas  $\mathrm{match}(\mathbf{r},(y^p,y)) = \mathrm{match}((??),(y^p,y))$  is true if and only if  $y^p$  and y are different values.

The above matching of single values is combined into a predicate matchRow that checks whether a row of a UDP is applicable for a certain vector of inputs. This predicate, whose formal definition is given in Table 3.1, has as first argument a row of a UDP, in which at most one edge specification may occur. As the second argument, it takes a tuple that contains both levels and edges, where there must be at most one edge. This tuple must have the same length as the number of inputs of the UDP. The last argument of matchRow is the previous output value, which must be a level. It follows from the definition of match that a level specification only matches a level and an edge specification only matches an edge. Therefore, the row matches the inputs if all level inputs have been matched by a level specification and the edge specification, in case the row is edge-sensitive, matches an edge at the same position in the vector of inputs. Furthermore, there must be at most one edge in the inputs, since there is at most one edge specification allowed in a row. To illustrate this, consider the UDP from Figure 3.1. For the input values D = 1, CK = (1,0), and RB = 1, the previous output value Q = 0, and the row in line 16, it holds that matchRow(? (?0) ? : ? : -, (1, (1, 0), 1), 0) is

true. But if the input CK is the level 0 and the other values are kept equal, then  $\mathrm{matchRow}(?\ (?0)\ ?\ :\ ?\ :\ -,(1,0,1),0)$  is false since  $\mathrm{match}((?0)\ ,0)$  is false (this even holds when identifying 0 with (0,0), since it is required that the values are different for an edge to match, as discussed previously).

The output of a UDP row is given by the ternary value that corresponds to the level specification in the last column. Additionally, the special symbol "–" is also allowed there. This value indicates that no change happens, i.e., the output value is the same as the previous output value. Thus, the row ?  $\star$  0 : 0 : – occurring in line 17 of the flip-flop example in Figure 3.1 could also be written as ?  $\star$  0 : 0 : 0, as was already discussed in Section 2.3.

Using this and the matching of rows, it would be desired to construct a function that computes the output of a UDP given the previous and current values of the inputs and the previous value of the output. For this purpose, the Verilog standard does define two rules that govern the selection of a row when computing a new output value. The first requirement is that level-sensitive rows take precedence over edge-sensitive rows, as already mentioned above. The second requirement is that two rows of the same type (i.e., either both level-sensitive or both edge-sensitive with the edge in the same column) that are both applicable to some inputs and previous output, must not disagree on the output value.

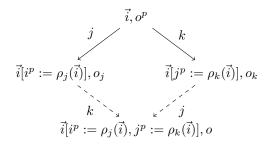

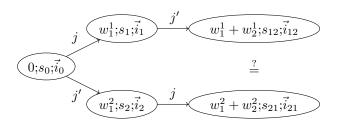

These rules however are not precise enough to induce a function for the computation of a UDP's next output value. If multiple inputs of a UDP change at the same time, then it is not clear how to handle this. In order for the semantics to be as general as possible, it is therefore assumed that non-deterministically an order is chosen and according to this order the changed inputs are considered one change at a time. Hence, the semantics of a UDP is defined to be a function that is parametrized by the current UDP, the previous and current values of the inputs, the previous output value, and some order. Such an order is given by a permutation of the numbers from 1 to n that dictates the order of checking the inputs whether their values have changed. This gives the following signature of the evaluation function  $\llbracket \cdot \rrbracket$  for a UDP  $udp \in UDPs_n \colon \llbracket \cdot \rrbracket : UDPs_n \times (\mathbb{T} \times \mathbb{T})^n \times \mathbb{T} \times \mathcal{L}_n \to \mathbb{T}$ . Here, permutations are generalized to lists without duplicates, to allow for the below recursive definition, given some previous and current input values  $i_1^p, i_1, \ldots, i_n^p, i_n \in \mathbb{T}$ , some previous output  $o^p \in \mathbb{T}$ , and some list  $j: \ell \in \mathcal{L}_n$ :

$$\begin{split} & [\![ \mathrm{udp}, ((i_1^p, i_1), \dots, (i_n^p, i_n)), o^p, \mathrm{nil} \quad] \quad \dot{=} \quad o^p \\ & [\![ \mathrm{udp}, ((i_1^p, i_1), \dots, (i_n^p, i_n)), o^p, j : \ell \,] ] \quad \dot{=} \\ & [\![ \mathrm{udp}, ((i_1^p, i_1), \dots, (i_j, i_j), \dots, (i_n^p, i_n)), o', \ell ]\!] \end{split}$$

The next output value o' is defined as follows. If  $i_j^p = i_j$ , then  $o' = o^p$ , i.e., the value remains unchanged. Otherwise, o' is defined to be the corresponding output value of either a level-sensitive row r of the UDP udp for which  $\mathrm{matchRow}(r,(i_1^p,\ldots,i_j,\ldots,i_n^p),o^p)$  is true, or o' is the corresponding output value of an edge-sensitive row r of the UDP for which  $\mathrm{matchRow}(r,(i_1^p,\ldots,(i_j^p,i_j),\ldots,i_n^p),o^p)$  is true and for all level-sensitive rows r' of the UDP the property  $\mathrm{matchRow}(r',(i_1^p,\ldots,i_j,\ldots,i_n^p),o^p)$  is false. If no such row exists, then the next output value o' is defined to be X.

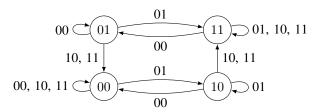

As an example, consider the user defined primitive latch given in Figure 3.1. Its output value shall be determined for the input values D=(1,X), CK=(1,0), and RB=(1,1) and the previous output value Q=0. If the order  $\pi=2:1:3$  is used, then the first intermediate output value is 0, since line 16 satisfies

$\mathrm{matchRow}(?\ (?0)\ ?\ :\ ?\ :\ -,(1,(1,0),1),0),$  as already illustrated before. Now the previous value of CK is updated and the change of input D is considered. Here, line 22 matches, giving a next output value  $\mathbb{Q}=0$ . Finally, since the input RB did not change, this is also the output of this instance given these inputs, the previous output, and the considered order.

However, when changing the order to  $\pi' = id = 1:2:3$ , then the following computation gives as new output value X, which shows that the order can change the result of a computation.

Thus, UDPs can behave differently depending on the order in which input changes are processed. This order is chosen non-deterministically, which therefore also makes the evaluation of UDPs non-deterministic. As mentioned previously, this is investigated further in Chapters 4 and 5. Chapter 4 presents an efficient technique to guarantee that the output value of a UDP is independent of the concrete order chosen. This however is not the case very often, since certain order-dependencies such as the above, where the relative order of the clock and data inputs matters, are expected. This information is contained in the timing checks, which constrain the possible orders and are therefore incorporated into the analysis of order-independence in Chapter 5.

#### **Output Value Computation of Built-In Primitives**

Finally, the function  $\llbracket \cdot \rrbracket$  is extended to also incorporate the semantics of built-in primitives. In this way, a function  $\llbracket \cdot \rrbracket$ :  $\operatorname{Prims} \times (\mathbb{T} \times \mathbb{T})^n \times \mathbb{T} \times \mathcal{L}_n \to \mathbb{T}$  is obtained, that uses the semantics of the built-in primitives as given in [IEE06, Table 7-3 and Table 7-4]. Note that all built-in primitives are combinational, therefore the list indicating the order of evaluating inputs, the previous input values, and the previous output value can simply be ignored for them. This can be seen in their definitions show below, which use only the operations  $\wedge$  and  $\neg$  extended to the ternary values  $\mathbb{T}$ , as given in the Preliminaries. There, the previous input values  $i_1^p, i_2^p \in \mathbb{T}$  and the previous output value  $o^p \in \mathbb{T}$ , as well as the orders  $\pi_j \in \Pi_j$  for j=1,2 are ignored; the output values are only computed from the input values  $i_1,i_2\in\mathbb{T}$ .

```

\begin{split} & [\mathbf{buf}, \left((i_1^p, i_1)\right), o^p, \pi_1] ] & \doteq i_1 \\ & [\mathbf{not}, \left((i_1^p, i_1)\right), o^p, \pi_1] ] & \doteq \neg i_1 \\ & [\mathbf{and}, \left((i_1^p, i_1), (i_2^p, i_2)\right), o^p, \pi_2] ] & \doteq i_1 \wedge i_2 \\ & [\mathbf{nand}, \left((i_1^p, i_1), (i_2^p, i_2)\right), o^p, \pi_2] ] & \doteq \neg (i_1 \wedge i_2) \\ & [\mathbf{or}, \left((i_1^p, i_1), (i_2^p, i_2)\right), o^p, \pi_2] ] & \doteq i_1 \vee i_2 & \doteq \neg (\neg i_1 \wedge \neg i_2) \\ & [\mathbf{nor}, \left((i_1^p, i_1), (i_2^p, i_2)\right), o^p, \pi_2] ] & \doteq \neg (i_1 \vee i_2) & \doteq \neg i_1 \wedge \neg i_2 \\ & [\mathbf{xor}, \left((i_1^p, i_1), (i_2^p, i_2)\right), o^p, \pi_2] ] & \doteq i_1 \oplus i_2 & \doteq \neg \left(\neg (i_1 \wedge \neg i_2) \wedge \neg (\neg i_1 \wedge i_2)\right) \\ & [\mathbf{xnor}, \left((i_1^p, i_1), (i_2^p, i_2)\right), o^p, \pi_2] ] & \doteq \neg (i_1 \oplus i_2) & \doteq \neg (i_1 \wedge \neg i_2) \wedge \neg (\neg i_1 \wedge i_2) \end{split}

```

The Verilog standard allows for an arbitrary number of output variables for the **buf** and **not** primitives, and an arbitrary number of input values (at least 1) for

the built-in primitives **and**, **nand**, **or**, **nor**, **xor**, and **xnor**. Multiple output variables are treated by copying the primitive instantiations, so that every instantiation has exactly one output variable. If only a single input value is given for any of the (normally binary) primitives, then this input value is also the output value. More than 2 input values provided for such a primitive are treated by repeating the evaluations multiple times, for example,  $[\![\mathbf{and}, \left((i_1^p, i_1), (i_2^p, i_2), (i_3^p, i_3)\right), o^p, \pi_3]\!] = [\![\![\mathbf{and}, \left([\mathbf{and}((i_1^p, i_1), (i_2^p, i_2))o^p, \pi_2]\!], (i_3^p, i_3)\right), o^p, \pi_2]\!] = i_1 \wedge i_2 \wedge i_3$ , where the order  $\pi_2 \in \Pi_2$  can be chosen arbitrarily, since it is ignored.

#### **Simulation Semantics**

After having defined how to evaluate a single primitive, the semantics of a complete VeriCell program is given. Such a program usually contains a number of instantiations of primitives. As already noted above, the possible values of variables are the ternary values in  $\mathbb{T}$ . To keep track of such values in a current configuration, variable valuations are defined. A variable valuation val is a partial function mapping identifiers to values from  $\mathbb{T}$ . If for some identifier x the value val(x) is not defined, then it defaults to X. A variable valuation is denoted as a set of pairs of identifiers and values, e.g.,  $\{(x,0)\}$  represents the variable valuation that maps the identifier x to 0 and all other identifiers to the default value x. To update variable valuations, the operation juxtaposition is used. Given two variable valuations  $val_1$  and  $val_2$ , this operation is defined as  $val_1 \ val_2(x) = val_2(x)$  if  $val_2(x)$  is defined, otherwise  $val_1 \ val_2(x) = val_1(x)$ . For example,  $\{(d,0), (ck,1)\}$   $\{(ck,X), (rb,0)\} = \{(d,0), (ck,X), (rb,0)\}$ .

The simulation semantics of Verilog is sketched in [IEE06, Clause 11], however it does not deal with the details of when and how to update values. For example, it is not defined when a transition of a variable can be observed by primitives that have this variable as an input. Therefore, when the simulation semantics sketched in [IEE06, Clause 11] is ambiguous, the formal semantics is based on the observations of simulators. As stated before, the choices regarding ambiguities match the interpretation used by CVer and ModelSim.

The execution is split into three different phases, namely, *execute*, *update* and *time-advance*. Execute and update phases are performed iteratively until the current state is stabilized. Only then, the time-advance phase advances the global simulation clock. In the execute phase, all *active* primitives, i.e., primitives for which an input has changed its value, compute their new output values. The output values are stored in a separate location and are not directly used for the evaluation of other primitives, thereby modeling a parallel execution of the primitives. In the update phase, which follows the execute phase, all these values are stored as the new values of the variables. This can again make primitives active, in this case another execute phase is performed.

For example, in the module flip\_flop shown in Figure 3.1 a change of the variable d might result in a change of the variable iq. Since this variable is used as an input to another primitive instantiation with the output variable qint, this primitive will be activated and executed. The computation is repeated until no more updates are pending and no primitives are active anymore. Then, the third phase, called time advance phase, is entered in which the global simulation time advances and new inputs are applied. These can again activate primitives in the program, since

Table 3.2: Deduction Rules for the Semantics of VeriCell Programs

for example the input d might be assigned a different value, so that the execute phase is entered again.

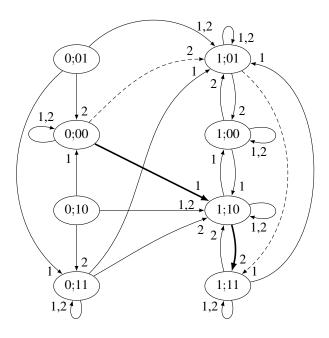

Configurations, i.e., operational states of the simulation semantics, comprise a natural number t, denoting the current simulation time, and the previous and the current valuations of variables in the module, denoted by prev and cur, respectively. Another component of a configuration is a set act of primitive instantiations that have to be evaluated due to the change of some input. Furthermore, a third variable valuation up is contained that collects the updates to be performed. Finally, in order to distinguish the current phase, a flag called phase is introduced that is either E for Execute or U for Update. The flag phase does not model the time-advance phase, since this phase it is modeled as a transition from an update to an execute phase. A configuration is written as  $\langle t, prev, cur, act, up \rangle_{phase}$ .

Initially, a Verilog program starts in a configuration where the time is 0, all variables have the value X, no primitives are active, and no updates have to be executed, which is denoted by  $\langle 0,\emptyset,\emptyset,\emptyset,\emptyset\rangle_U$ . Starting in this initial configuration, the deduction rules presented in the remainder of this section are used to transform a current configuration into a next configuration until this is not possible anymore.

It is assumed that a sequence  $\overrightarrow{in_1}, \overrightarrow{in_2}, \ldots$  of variable valuations called *input* vectors is given. These variable valuations only assign values to the external inputs declared in the module of the VeriCell program. They are applied whenever the simulation time is allowed to advance.

The operational semantics of a VeriCell program is defined by the deduction rules given in Table 3.2.

In the execution phase, an active primitive is non-deterministically chosen, executed, and removed from the set of active primitives. This is expressed by rule (ex) in Table 3.2. There,  $\pi$  is an arbitrarily chosen order for the evaluation of inputs. Note that this order may differ for each evaluation of a primitive.

When no more active primitives exist then the simulation changes into the update phase. During this change the current transitions of variables are cleared, since all primitives having a changed variable as input have been executed. The new previous values are contained in the *cur* variable valuation, hence this variable valuation will be used as the new previous variable valuation, as can be seen in rule (ex-up) in Table 3.2.

In the update phase, the new output values are written back into the current variable values. Furthermore, all primitives are activated that have a changed variable as one of their inputs. This is accomplished by the rule (up) in Table 3.2, where it is required that  $up \neq \emptyset$ , i.e., there must be pending updates. The function sens computes for two variable valuations the set of primitives that have a changed variable as an input. Formally, this function is defined as  $sens(val_1, val_2) = \{p(o, i_1, \dots, i_n) \in Prims \mid \exists 1 \leq j \leq n : val_1(i_j) \neq val_2(i_j)\}.$

When all updates have been performed, then the execute phase is entered again if there are active primitives. This is expressed in the rule (up-ex) in Table 3.2, which is only applicable if  $act \neq \emptyset$ . Otherwise, if there are no active primitives, then time advances and the new input values are applied. Furthermore, the new previous values are the current values, because the current state is stable and any present changes can be disregarded. The changed inputs can however activate primitives. To determine these, the function sens is used again in the rule (time) in Table 3.2.

If no input vector  $in_{t+1}$  is available anymore, then the simulation terminates. The trace of output values generated by a certain trace of input vectors is defined to consist of the values in the stable states, i.e., states in which the time can advance or simulation terminates.