## Concepts for smart AD and DA converters

Citation for published version (APA):

Harpe, P. J. A. (2010). Concepts for smart AD and DA converters. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR656578

DOI:

10.6100/IR656578

Document status and date:

Published: 01/01/2010

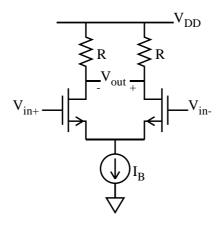

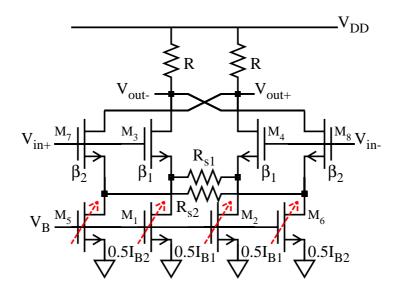

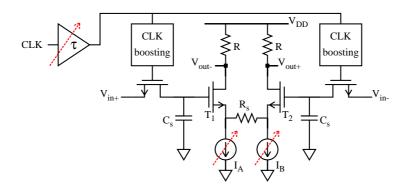

Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

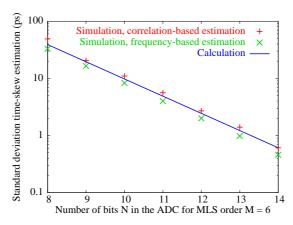

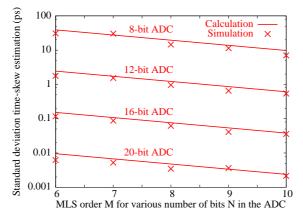

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 04. Oct. 2023

# Concepts for Smart AD and DA Converters

Pieter Harpe

# Concepts for Smart AD and DA Converters

Pieter Harpe

This work was supported by the Foundation for Technical Sciences (STW) under project 06655.

Cover design by Xiaoyan Wang, Cui Zhou and Pieter Harpe.

Harpe, P.J.A.

Concepts for Smart AD and DA Converters

Proefschrift Technische Universiteit Eindhoven, 2010.

A catalogue record is available from the Eindhoven University of Technology Library ISBN 978-90-386-2120-3

NUR 959

Trefw.: analog-to-digital conversion, digital-to-analog conversion, correction, calibration.

©P.J.A. Harpe 2010

All rights reserved.

Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

## Concepts for Smart AD and DA Converters

## PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus, prof.dr.ir. C.J. van Duijn, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op woensdag 27 januari 2010 om 16.00 uur

door

Pieter Joost Adriaan Harpe

geboren te Middelburg

Dit proefschrift is goedgekeurd door de promotor:

prof.dr.ir A.H.M. van Roermund

Copromotor: dr.ir. J.A. Hegt

# Contents

|          | List                   | of symbols and abbreviations     | 9  |

|----------|------------------------|----------------------------------|----|

| 1        | Intr                   | roduction                        | 11 |

|          | 1.1                    | Background                       | 11 |

|          | 1.2                    | Aim of the thesis                | 12 |

|          | 1.3                    | Scope of the thesis              | 12 |

|          | 1.4                    | Outline of the thesis            | 13 |

| <b>2</b> | $\mathbf{A}\mathbf{D}$ | and DA conversion                | 15 |

|          | 2.1                    | Introduction                     | 15 |

|          | 2.2                    | Trends in applications           | 16 |

|          | 2.3                    | Trends in technology             | 17 |

|          | 2.4                    | Trends in system design          | 18 |

|          | 2.5                    | Performance criteria             | 20 |

|          | 2.6                    | Conclusion                       | 20 |

| 3        | Sma                    | art conversion                   | 21 |

|          | 3.1                    | Introduction                     | 21 |

|          | 3.2                    | Smart concept                    | 22 |

|          | 3.3                    | Application of the smart concept | 25 |

|          | 3.4                    | Focus in this work               | 26 |

|          | 3.5                    | Conclusion                       | 27 |

|          |                        |                                  |    |

5

Contents

| 4 | Sma | art DA conversion                        | 29  |

|---|-----|------------------------------------------|-----|

|   | 4.1 | Introduction                             | 29  |

|   | 4.2 | Area of current-steering DACs            | 31  |

|   | 4.3 | Correction of mismatch errors            | 33  |

|   | 4.4 | Sub-binary variable-radix DAC            | 35  |

|   | 4.5 | Design example                           | 43  |

|   | 4.6 | Conclusion                               | 49  |

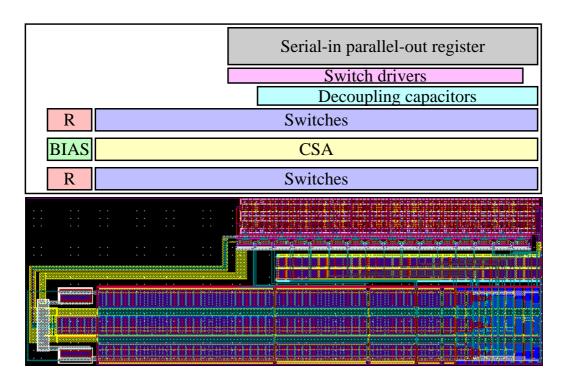

| 5 | Des | sign of a sub-binary variable-radix DAC  | 51  |

|   | 5.1 | Schematic design                         | 51  |

|   | 5.2 | Layout                                   | 55  |

|   | 5.3 | Self-measurement-circuit implementation  | 56  |

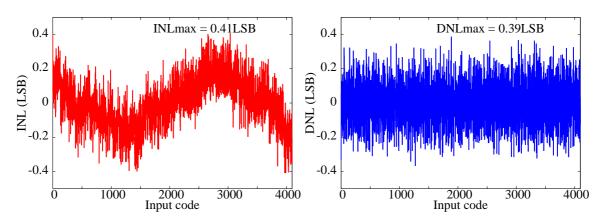

|   | 5.4 | Experimental results                     | 57  |

|   | 5.5 | Conclusion                               | 64  |

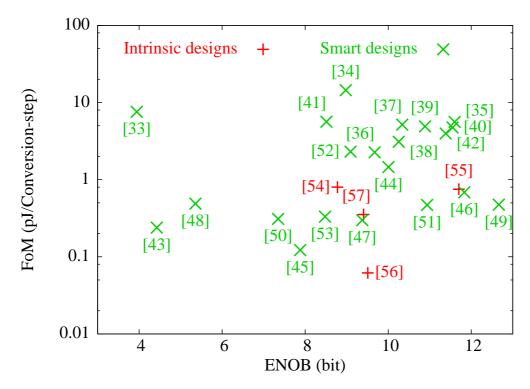

| 6 | Sma | art AD conversion                        | 67  |

|   | 6.1 | Introduction                             | 67  |

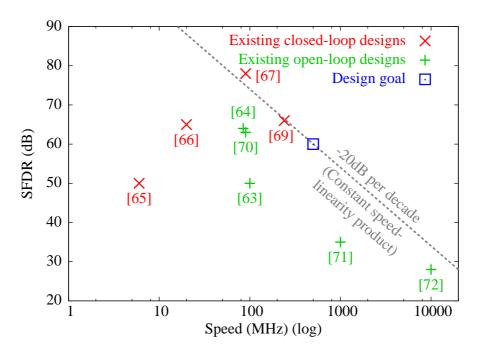

|   | 6.2 | Literature review                        | 68  |

|   | 6.3 | High-speed high-resolution AD conversion | 71  |

|   | 6.4 | Smart calibration                        | 77  |

|   | 6.5 | Conclusion                               | 80  |

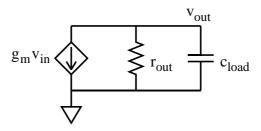

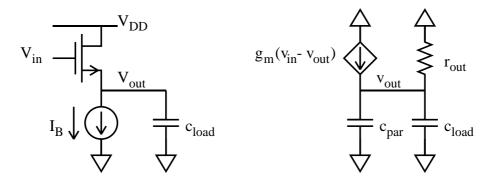

| 7 | Des | sign of an open-loop T&H circuit         | 81  |

|   | 7.1 | Literature review                        | 81  |

|   | 7.2 | Design goal                              | 83  |

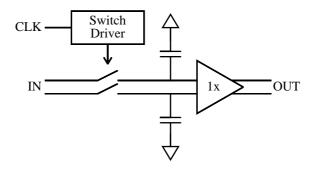

|   | 7.3 | T&H architecture                         | 83  |

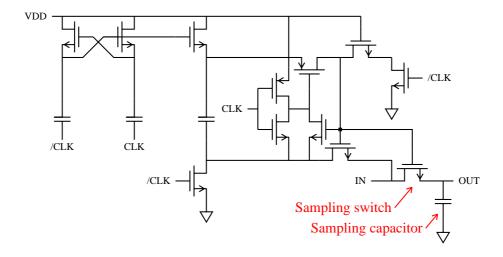

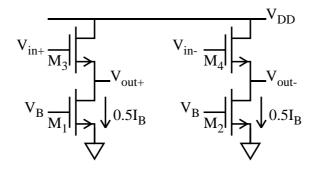

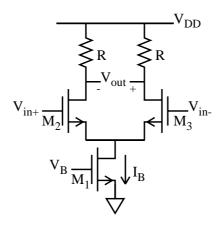

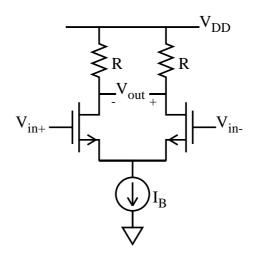

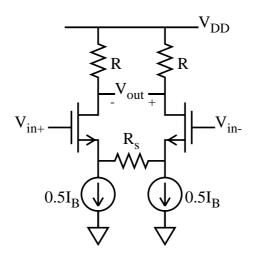

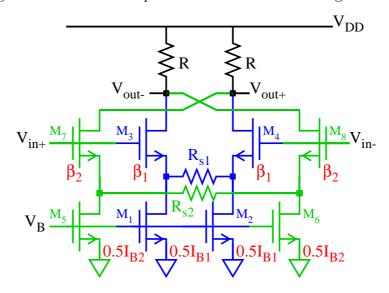

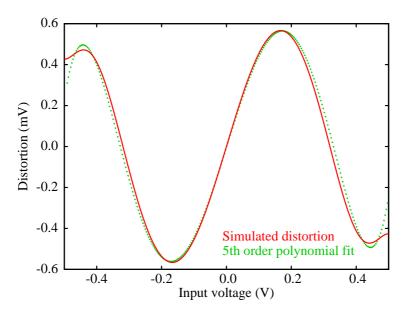

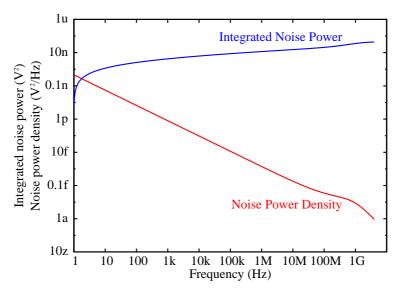

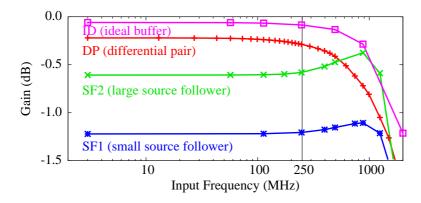

|   | 7.4 | Sampling core architecture               | 85  |

|   | 7.5 | Output buffer architecture               | 86  |

|   | 7.6 | T&H design                               | 97  |

|   | 7.7 | Experimental results                     | 100 |

|   | 7.8 | Conclusion                               | 110 |

G Contents

| 8  | <b>T</b> &: | H calibration                                                             | 111 |

|----|-------------|---------------------------------------------------------------------------|-----|

|    | 8.1         | Introduction                                                              | 111 |

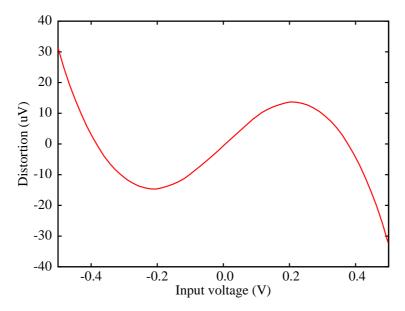

|    | 8.2         | T&H accuracy                                                              | 112 |

|    | 8.3         | T&H calibration method                                                    | 113 |

|    | 8.4         | Analog correction parameters                                              | 114 |

|    | 8.5         | Digitally assisted analog correction                                      | 121 |

|    | 8.6         | Simulation results                                                        | 124 |

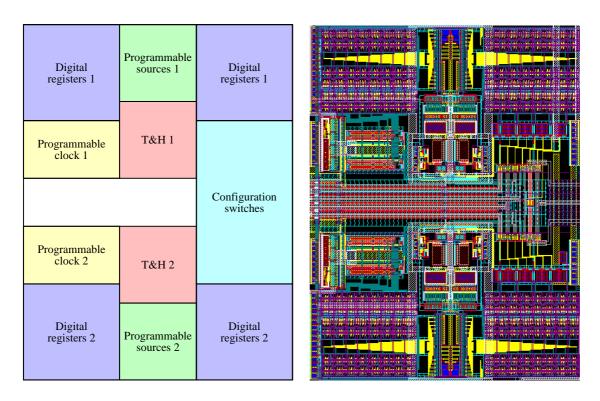

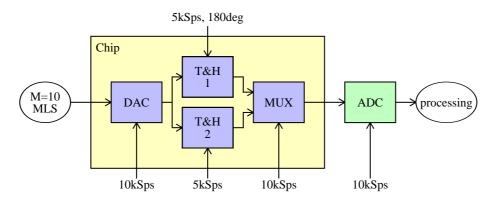

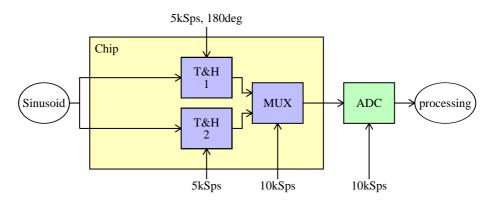

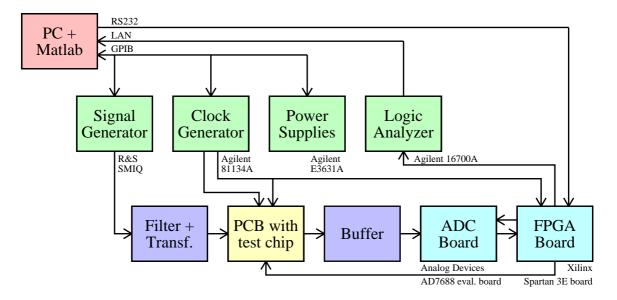

|    | 8.7         | Implementation of the calibration method and layout $\dots \dots \dots$ . | 127 |

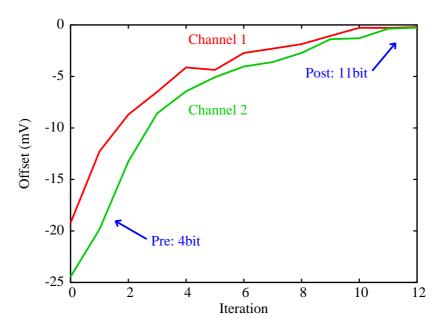

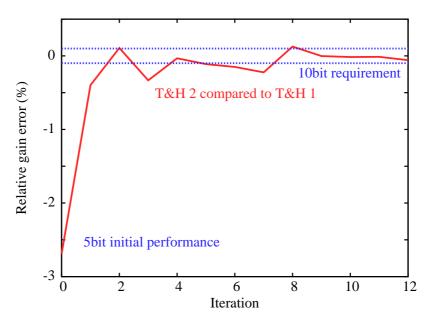

|    | 8.8         | Experimental results                                                      | 128 |

|    | 8.9         | Conclusion                                                                | 132 |

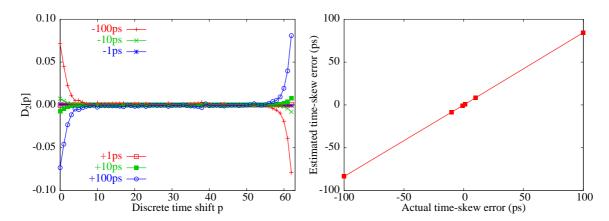

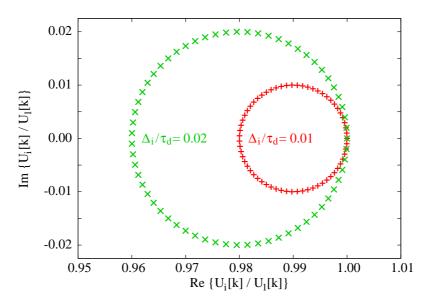

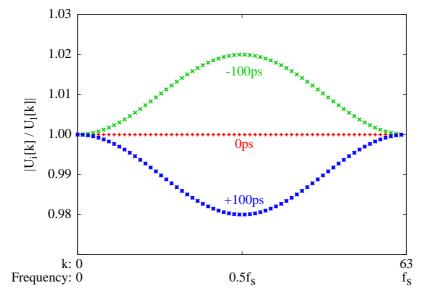

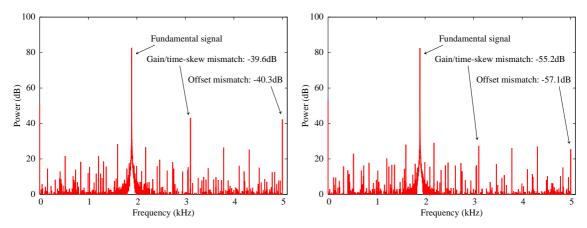

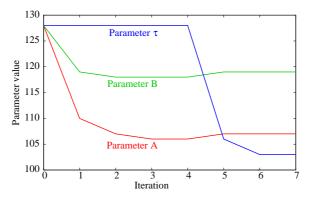

| 9  | <b>T</b> &: | H calibration for time-interleaved ADCs                                   | 133 |

|    | 9.1         | Introduction                                                              | 133 |

|    | 9.2         | Channel matching in time-interleaved T&H's                                | 136 |

|    | 9.3         | Channel mismatch calibration                                              | 137 |

|    | 9.4         | Channel mismatch detection                                                | 140 |

|    | 9.5         | Channel mismatch correction                                               | 153 |

|    | 9.6         | Simulation results                                                        | 155 |

|    | 9.7         | Implementation of the calibration method and layout $\dots \dots \dots$ . | 156 |

|    | 9.8         | Experimental results                                                      | 157 |

|    | 9.9         | Conclusion                                                                | 161 |

| 10 | Cor         | nclusions                                                                 | 163 |

|    | Ref         | erences                                                                   | 165 |

|    | Ori         | ginal contributions                                                       | 171 |

|    | List        | of publications                                                           | 173 |

|    | Sun         | nmary                                                                     | 177 |

|    | San         | nenvatting                                                                | 179 |

|    | Wo          | rd of thanks                                                              | 181 |

|    | Bio         | graphy                                                                    | 183 |

Contents 7

# List of symbols and abbreviations

| Symbol    | Description                               | Unit              |

|-----------|-------------------------------------------|-------------------|

| ADC       | Analog to digital converter               |                   |

| CSA       | Current source array                      |                   |

| $D_a$     | $R_{1,a} - R_{1,1}$                       |                   |

| DAC       | Digital to analog converter               |                   |

| DNL       | Differential non-linearity                | LSB               |

| $\Delta$  | Time-skew error                           | S                 |

| ENOB      | Effective number of bits                  | bit               |

| ERBW      | Effective resolution bandwidth            | Hz                |

| FoM       | Figure of merit                           | J/conversion-step |

| FS        | Digital full scale amplitude              |                   |

| $f_s$     | Sampling frequency                        | Hz                |

| $G_e$     | Gain error                                |                   |

| INL       | Integral non-linearity                    | LSB               |

| LSB       | Least significant bit                     |                   |

| M         | MLS order                                 |                   |

| m         | MLS length                                |                   |

| MLS       | Maximum length sequence                   |                   |

| MSB       | Most significant bit                      |                   |

| N         | Resolution                                | bit               |

| $O_e$     | Offset error                              | V, LSB            |

| $R_{a,b}$ | Discrete cross-correlation of $a$ and $b$ |                   |

| $R_s$     | Discrete auto-correlation of $s[n]$       |                   |

| r[n]      | Single-bit MLS                            |                   |

| s[n]      | Multi-bit MLS                             |                   |

| SFDR      | Spurious free dynamic range               |                   |

| SNDR      | Signal to noise and distortion ratio      |                   |

| SNR       | Signal to noise ratio                     |                   |

| THD       | Total harmonic distortion                 |                   |

| T&H       | Track and hold                            |                   |

| u[n]      | Response to a multi-bit MLS               |                   |

| $V_{CM}$  | Common-mode voltage                       | V                 |

| $V_{fs}$  | Analog full scale amplitude               | V                 |

|           |                                           |                   |

# Chapter 1

## Introduction

## 1.1 Background

The history of the application of semiconductors for controlling currents goes back all the way to 1926, in which Julius Lilienfeld filed a patent for a "Method and apparatus for controlling electric currents" [1], which is considered the first work on metal/semiconductor field-effect transistors. More well-known is the work of William Shockley, John Bardeen and Walter Brattain in the 1940s [2, 3], after which the development of semiconductor devices commenced. In 1958, independent work from Jack Kilby and Robert Noyce led to the invention of integrated circuits. A few milestones in IC design are the first monolithic operational amplifier in 1963 (Fairchild  $\mu$ A702, Bob Widlar) and the first one-chip 4-bit microprocessor in 1971 (Intel 4004).

Ever since the start of the semiconductor history, integration plays an important role: starting from single devices, ICs with basic functions were developed (e.g. opamps, logic gates), followed by ICs that integrate larger parts of a system (e.g. microprocessors, radio tuners, audio amplifiers). Following this trend of system integration, this eventually leads to the integration of analog and digital components in one chip, resulting in mixed-signal ICs: digital components are required because signal processing is preferably done in the digital domain; analog components are required because physical signals are analog by nature. Mixed-signal ICs are already widespread in many applications (e.g. audio, video); for the future, it is expected that this trend will continue, leading to a larger scale of integration.

Given the trend of mixed-signal integration, this leads to both new challenges and new opportunities with respect to the integrated analog components. Challenges are for example testing of the performance of analog components that are embedded inside a large system, or the fact that the IC technology is optimized for digital circuitry, which can be disadvantageous for analog components. On the other hand, the mixed-signal integration also gives opportunities, like the possibility to shift parts of the system from the analog to the digital domain, or vice versa. From this point

1. Introduction 11

of view, the aim of this work is to investigate concepts to improve the performance of analog components by making use of the opportunities that are offered by mixed-signal system integration. This 'smart' concept will be applied to analog-to-digital and digital-to-analog converters, as these components are essential in mixed-signal systems.

#### 1.2 Aim of the thesis

The aim of this thesis is to investigate the feasibility of relevant smart AD and DA converter concepts to improve their performance<sup>1</sup>. For both AD and DA converters, the following aspects will be taken into account:

- Selection of relevant performance criteria.

- Evaluation of prior-art and identifying their limitations.

- Selection of relevant smart concepts to improve the performance.

- Development and analysis of the selected smart concepts, including methods for detection, processing and correction.

- Implementation and evaluation of the selected smart concepts.

## 1.3 Scope of the thesis

Some limitations on the scope of the thesis are explained below:

#### • Current-steering DAC architecture

The current-steering DAC architecture will be studied for the smart DA concepts. This is motivated by the fact that for high-speed DA conversion, this type is predominantly used.

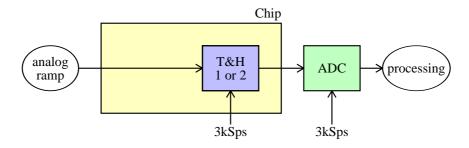

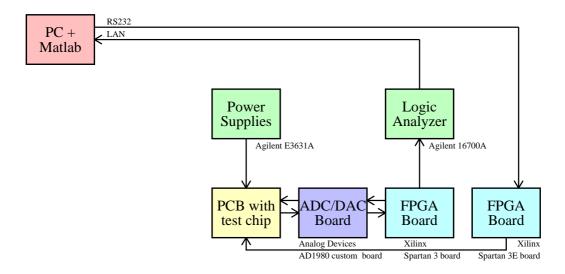

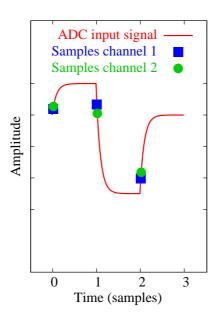

• (Time-interleaved) pipelined ADC architecture, focus on Track&Hold The (time-interleaved) pipelined ADC architecture will be studied for the smart AD concepts. Moreover, most of the work is limited to the front-end track-and-hold, in the context of a (time-interleaved) pipelined ADC. The limitation to a (time-interleaved) pipelined ADC architecture is motivated by the fact that for high-speed, high-resolution AD conversion, this is a commonly used and reasonable solution. The limitation to the track-and-hold is motivated by the fact that it is sufficient for the demonstration of the proposed smart concepts.

1. Introduction

<sup>&</sup>lt;sup>1</sup>In this work, performance is defined in a wide sense, including e.g.: speed, accuracy, power consumption, area, yield, reliability, portability, etc.

#### • CMOS technology

CMOS is the preferred technology choice for the implementation of digital circuits. As the smart concept implies analog circuits integrated in large digital systems, the limitation to CMOS technology is a logical choice. Because of limited technology availability, all simulations, calculations and implementations are limited to a  $0.18\mu m$  CMOS technology. However, the proposed concepts could be implemented in other technologies as well.

#### • General purpose

The proposed solutions do not aim for a specific target application. Because of that, the concepts and designs are 'general purpose' in the sense that they do not pose any constraints on the input signal, nor do they take advantage of certain assumptions on the input signal.

#### 1.4 Outline of the thesis

The outline of this thesis is briefly explained below.

Chapter 2 studies trends and expectations in converter design with respect to applications, technology evolution and system design. Problems and opportunities are identified, and an overview of performance criteria is given. In chapter 3, the smart concept is introduced that takes advantage of the expected opportunities (described in chapter 2) in order to solve the anticipated problems.

Chapters 4 and 5 apply the smart concept to digital-to-analog converters. In the discussed example, the concept is applied to reduce the area of the analog core of a current-steering DAC. In chapter 4, the theory is presented while chapter 5 discusses the implementation and experimental results.

Chapter 6 up to chapter 9 focus on the application of the smart concept to analog-to-digital converters. The main goal here is to improve the performance in terms of speed/power/accuracy. Chapter 6 introduces the general concept and defines key factors for the analog design and the smart approach in order to achieve the targeted high performance. Then, chapter 7 deals with the analog design of an open-loop track-and-hold circuit. Experimental results are presented and compared against prior art. In chapters 8 and 9, two calibration techniques are presented and experimentally verified by using the track-and-hold from chapter 7.

Finally, conclusions are drawn in chapter 10.

1. Introduction 13

# Chapter 2

## AD and DA conversion

This chapter studies trends and expectations in converter design with respect to applications, technology evolution and system design. Problems and opportunities are identified, and an overview of performance criteria is given. In chapter 3, the smart concept is introduced that takes advantage of the expected opportunities in order to solve the anticipated problems.

## 2.1 Introduction

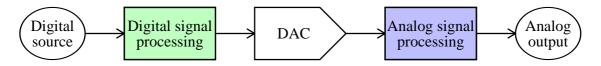

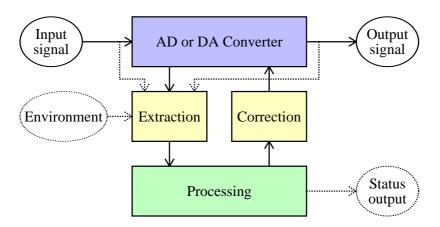

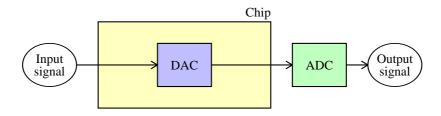

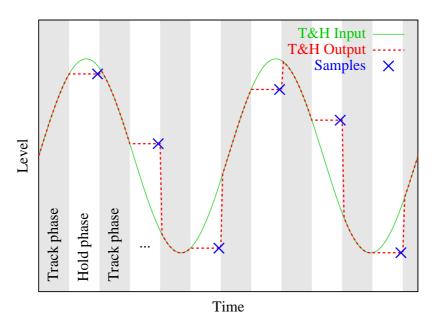

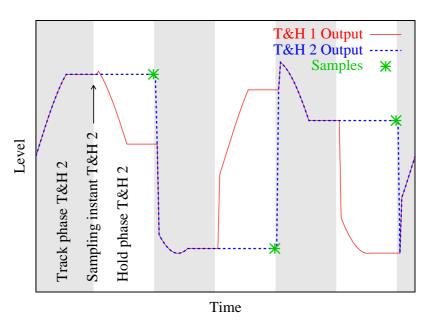

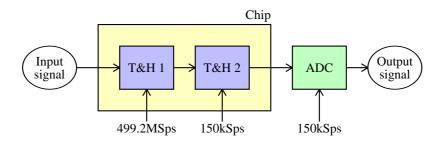

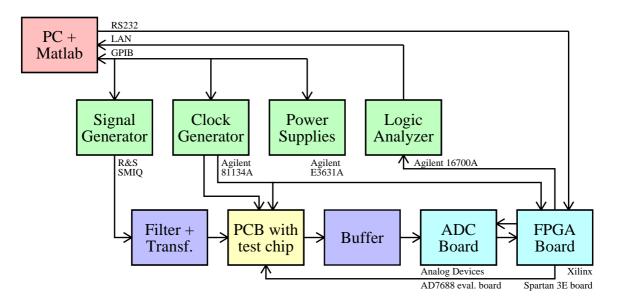

Electronic systems perform functions on many different types of signals, like: audio, video, medical images or RF communication signals. Despite the large variety, all signals are analog by nature in the physical world. However, at present most of the signal processing or signal storage is preferably performed in the digital domain. This leads to the need for analog-to-digital and digital-to-analog conversion. Actual systems can include both AD and DA conversion, or either one of the two. A general view on AD conversion is given in fig. 2.1: the analog input signal is transferred to the digital domain through an ADC. Dependent on the situation, analog signal processing can be applied before the actual conversion, like pre-amplification, filtering or demodulation. Also, digital signal processing can be applied after the conversion, like error correction, filtering or data compression.

Figure 2.1: General view on AD conversion.

A general view on DA conversion is given in fig. 2.2: the digital input signal is transferred to the analog domain through a DAC. Dependent on the situation, digital

signal processing can be applied before the actual conversion, like encoding or filtering. Also, analog signal processing can be applied after the conversion, like modulation or filtering.

Figure 2.2: General view on DA conversion.

This work focusses on the actual AD and DA conversion, neglecting the other components of the signal processing chain.

## 2.2 Trends in applications

A trend in applications is that they typically demand a higher performance in terms of speed, accuracy, power consumption and chip-area. A motivation for the increase in demand is illustrated below.

#### • Speed and accuracy

Over time, speed and accuracy requirements of an application are typically increasing. For example, the audio CD standard used 16bit/44.1kHz data, while current DVD players often use 24bit/192kHz. For digital still cameras, a 3megapixel sensor with 12bit dynamic range was state-of-the-art in 1999. 10 years later, state-of-the-art evolved to 25megapixel sensors with 14bit dynamic range. For wireless communication, the data-rate requirements are increasing, thus leading to a higher speed and/or accuracy requirement for the converters.

#### • Power

In many situations, the power consumption is an important factor: e.g. to prevent problems due to thermal heating or to extend the lifetime of a battery-operated device. For example, for the previously mentioned still cameras, the battery lifetime improved from 400 shots to 4000 shots on one battery. Though the reasons for this improvement are diverse, it shows that reducing power consumption is an important feature.

#### • Area

For all applications, the chip-area is a cost-factor. Thus, area reduction is preferable when possible.

Concluding, the trends in applications lead to the challenge that more and more performance is expected from the AD/DA converters. To meet this challenge, two important opportunities are: trends in technology and trends in system design. Both these factors might be used beneficially as will be discussed in the following sections.

## 2.3 Trends in technology

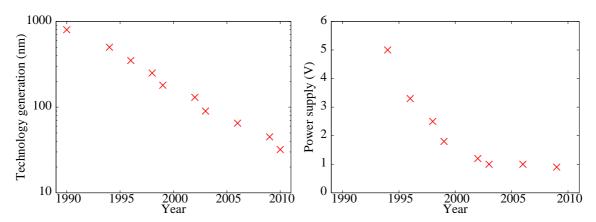

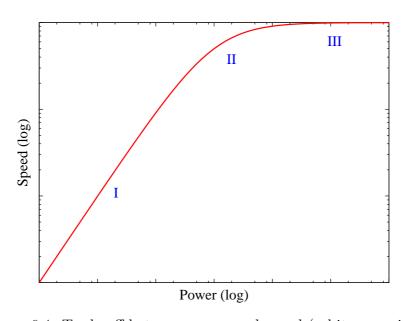

In technology development, the most important trend is down-scaling of the devices for each technology generation. Next to that, also the power supply is being reduced. Figure 2.3 shows the development of technology and power supply as a function of time for the UMC foundry [4]. While the technology scales down at a relatively constant rate, the power supply scaling flattens out because of threshold limitations.

Figure 2.3: Technology scaling and supply scaling as a function of time.

For digital designs, both trends are beneficial as they enable:

#### Higher speed

Because of the reduction of the dimensions of the devices and the interconnect, the associated capacitances are also reduced, resulting in a higher speed of operation.

#### • Lower power-consumption

The power consumption of digital circuits is proportional to  $CV_{DD}^2$ . As both the capacitances and the supply are being reduced, the power consumption will also decrease.

#### • Smaller area

The smaller dimensions result in a smaller area or a higher integration density.

On the other hand, the same trends are not necessarily beneficial for analog designs. For a noise-limited system, the noise-power requirement (kT/C) results in a minimum C-value to be implemented. Moreover, as the supply scales down, the signal power most likely also scales down, thus requiring even an increase in C to maintain the SNR. Because of that, analog circuits do not directly take advantage of scaling to achieve a higher speed or a lower power-consumption. Apart from that, technology scaling also complicates analog design because of the following reasons:

#### • Short channel effects

For smaller transistor geometries, secondary effects become more and more important. Because of that, the complexity of the transistor behavior increases, which complicates accurate circuit design.

#### • Low voltage operation

The reduced supply voltage limits the number of transistors that can be stacked, which complicates the implementation of certain circuit topologies.

While digital circuit design benefits from technology scaling, analog circuit design is getting more complicated. For mixed-signal designs, like AD and DA converters, it seems a logical option to shift some of the analog problems to the digital domain to be able to benefit from technology scaling.

## 2.4 Trends in system design

As mentioned previously in chapter 1, there is a tendency to integrate more and more components of a system into a single chip. As signal processing is predominantly performed in the digital domain while physical signals are analog by nature, this leads to the integration of analog and digital components in one chip, resulting in mixed-signal ICs. For the integrated analog components, the system integration offers both new challenges and new opportunities. Some of the challenges that become more important because of the mixed-signal integration are the following:

#### • Hostile environment

Digital circuits create a hostile environment for the analog circuits by causing interference, which potentially reduces the performance of the analog circuits.

#### • Testing

A stand-alone analog component can be tested directly for functionality or performance. On the other hand, analog components embedded in a large integrated system can not be accessed directly, thus complicating test methodologies. A dedicated test-mode or an internal self-test strategy might be necessary to facilitate testing.

#### • Yield

Especially when combining many different components into one integrated chip, the overall yield might be affected adversely by critical components. Also, when a single component has an unsatisfactory performance, the total system might fail. In general, design for high yield becomes more important for integrated components when compared to stand-alone components.

#### • Technology portability

Though technology portability is a general issue, it becomes more relevant for

mixed-signal ICs. For stand-alone analog components, a suitable technology might be selected by the designer. However, for integrated mixed-signal designs, the technology is most likely determined by the digital part and the analog circuits have to adopt this technology. Thus, analog designs are required that perform well in digital technologies. Moreover, they should be portable to future technologies as well, as the digital part of the system benefits from scaling. A second issue with respect to portability is the fact that expertise on analog design is required to transfer an existing design to a new technology.

#### Flexibility

Many digital systems are flexible by using programmable hardware like microprocessors or FPGAs. Flexibility in mixed-signal integrated systems can be a useful aspect as it widens the application range for a single design and it allows software updates to accommodate post-production modifications. To achieve a higher level of flexibility, also the analog components need to be flexible (e.g. speed, power, accuracy), while maintaining an appropriate performance level.

#### • Design time and risk

The digital design flow is highly automated, which reduces the design time and risk, especially when porting an existing design to a new technology. On the other hand, analog circuit design, simulation and layout are mainly manual tasks with a potentially longer design time and a higher risk. Even when porting an existing design to a new technology, schematics, simulations and layout need to be redone to a large extent. Techniques to reduce the design time and risk of analog components are required to suit better to the digital design flow, and to prevent that analog design becomes the overall design bottleneck.

Apart from these challenges, mixed-signal integration also gives opportunities for analog circuit design:

#### • Reuse of resources

In a large integrated system, not all components will be actively used at all times. Especially the digital hardware might have free time-slots in which it can be used for other purposes like self-test or calibration of analog components. The freedom to use these already available resources can enhance the overall system performance. Particularly in case of flexible digital platforms like FPGAs or microprocessors, hardware reuse can be implemented in a relatively simple way.

#### • System optimization

In integrated systems, the main goal is not to optimize the individual components, but to optimize the overall system. Then, the components can be optimized given the specific task inside the larger system. Taking this approach into account, a better optimization might be possible when compared to standard stand-alone circuit design. Also, in a system-level approach, problems can be shifted from the analog to the digital domain whenever this is beneficial for the overall performance.

### 2.5 Performance criteria

From the described trends and requirements with respect to applications, technology and system design, a set of relevant performance criteria for AD and DA converters can be identified. Classified into these three trends, the following list of performance criteria is obtained:

#### • Application driven criteria

- Speed

- Accuracy

- Power consumption

- Area

#### • Technology driven criteria

- Short-channel effect compatibility

- Low-voltage compatibility

#### • System driven criteria

- Interference compatibility

- Testability

- Yield

- Portability

- Flexibility

- Design time and risk

Typically, the application driven performance criteria are the most important ones; these are also the most widely used performance criteria for the evaluation of converters. However, in view of technology development and system integration, it will become necessary to achieve sufficient performance for the other criteria as well.

## 2.6 Conclusion

In this chapter, it was shown that trends in applications, technology and system design complicate analog circuit design. It was also shown that apart from these challenges, technology scaling and system integration offer new opportunities to improve the performance of analog circuits. In the next chapter, a concept is introduced that takes advantage of these opportunities in order to solve the anticipated problems.

# Chapter 3

## Smart conversion

This chapter introduces the smart concept for AD/DA converters, that aims at improving performance in a way that suits to the trends in technology and system design as described in chapter 2. First, the smart concept (as published in [5]) will be defined. Then, various applications of the concept will be discussed and the main focus of this work will be explained.

## 3.1 Introduction

In the previous chapter, several challenges in AD/DA converter design were identified, namely:

- The performance in terms of speed/accuracy/power-consumption/area should improve because of the increasing demand from the applications.

- Technology properties limit the achievable performance. Moreover, the achievable performance range might be reduced for future technologies because of process down-scaling.

- Mixed-signal system integration introduces new challenges with respect to e.g. testing, yield, portability, interference.

Especially the first two trends are contradictory: the performance demand increases while for some situations, the intrinsically achievable performance decreases. Because of that, a solution is required that can overcome the intrinsic limitations.

## 3.2 Smart concept

The smart converter concept<sup>1</sup> implies on-chip intelligence to extract information after production in order to improve the performance beyond intrinsic limitations. The concept includes three main components:

- 1. **Extraction** of information: to obtain more knowledge about e.g. imperfections that limit the performance, or specific requirements from the application.

- 2. **Processing** of this information: to decide how the performance can be optimized.

- 3. **Correction**: to realize the performance optimization.

The fundamental reason why a smart converter can potentially achieve a better performance than a conventional converter is because it has more information available. When appropriately used, this additional knowledge should allow a better optimization of the performance. Note that a-priori expertise is still required to decide how to extract, process and correct appropriately.

A second motivation for the smart concept is that several parts (as will be shown later) can be implemented in the digital domain. By doing so, these parts will benefit automatically from technology scaling, leading to a future-proof solution.

An illustration of the smart concept is shown in fig. 3.1; the various options for extraction, processing and correction will be discussed in the following sections.

Figure 3.1: Smart converter concept.

<sup>&</sup>lt;sup>1</sup>In this work, the smart concept is limited to AD and DA converters. However, the smart concept can be applied in a similar way to other circuits or systems.

#### 3.2.1 Extraction

The first step of the smart concept is the extraction of performance-relevant information. Three different information sources can be distinguished: system information, signal information and environmental information:

#### • System information

In this case, that is information from the ADC or DAC, like: functionality, mismatch of components (random or due to process-spread), non-linearity, frequency dependent behavior. As an example, consider the mismatch of components: before production only the statistics of the mismatch are known. After production, for a specific chip, the mismatch has a deterministic value. When this value can be measured on-chip it gives more precise knowledge on the mismatch compared to the pre-production statistical information. With this additional information and an appropriate correction technique, this imperfection could be counteracted to improve the performance.

#### • Signal information

Information from signals at the input, output or at an intermediate stage, like: amplitude, bandwidth, probability density function, spectral properties. For example, when the input signal has a limited amplitude, the converter's resources could be optimized for that specific amplitude instead of being optimized for the full-scale range of the converter.

#### • Environmental information

Environmental information includes information from the ambience (e.g. temperature, supply voltage), the user and the application. For example, dependent on the user/application requirements, the relevant performance criteria might change, and thus require a different optimization goal of the smart converter.

When considering mixed-signal circuits like AD and DA converters, part of the information to be extracted will be available in the digital domain and part of it will be available in the analog domain. In both cases, additional hardware might be required to extract the information.

## 3.2.2 Processing

The second step of the smart concept is to process the extracted information to optimize the performance. Two parts can be distinguished in the processing block: a first part in which the relevant information is extracted from the raw data and a second part where the information is processed to achieve a suitable correction. Whether these parts are necessary depends on the methods used for extraction and correction:

#### Processing of extracted information

Dependent on the extraction method, the required information for the performance optimization can be directly available, or it can be embedded in another signal. For example, consider the determination of the offset of an ADC. As a first option, one could set the ADC-input to zero and measure the digital output code, which then directly corresponds to the offset, and no additional processing is required to extract the relevant information. Alternatively, under the assumption that the applied (unknown) input signal has no DC component, the average output code of the ADC corresponds to the offset. In this case, processing (namely averaging) is required to obtain the offset information from the overall signal.

#### • Optimization algorithm

Dependent on the correction method, an optimization algorithm might be required to achieve the optimal performance. Considering the correction of the offset of an ADC, a first option could be to apply a digital correction by subtracting the measured offset digitally for each conversion. In that case, no optimization algorithm is required as the measured offset can be applied directly in the correction method. In a second case, the offset might be corrected by calibration of the analog reference voltage. In that case, several iterations might be necessary to find the best possible setting of the analog reference voltage to minimize the offset.

From the above examples, it can be understood that the complexity of the processing algorithm is strongly dependent on the methods used for extraction and correction.

As shown in fig. 3.1, the processing algorithm could also include a 'status output', which gives relevant information about the status of the converter to the outside world, for example to facilitate an on-chip self-test for specific performance parameters. E.g., suppose a smart correction algorithm is used to compensate a certain imperfection. When the algorithm runs out of range, it might suggest that the converter does not meet the target specification.

The processing algorithm can be implemented either in the analog or in the digital domain. A digital solution seems the most logical choice for the following reasons:

- Digital hardware offers flexibility and memory while it does not add unknown imperfections.

- Given the technology trends described in the previous chapter, digital processing will become cheaper for each technology generation. Thus, a digital implementation can benefit automatically from technology scaling.

- Given the context of mixed-signal integrated systems, it is expected that a large amount of programmable digital resources is present in the system. During free time-slots (e.g. at startup of the system), this hardware could be temporarily used to perform the processing algorithm.

#### 3.2.3 Correction

The third step of the smart concept is to perform the actual correction to optimize the performance. Several examples of correction methods are the following:

#### • Digital correction

Digital signal processing can be used to counteract measured imperfections. In case of ADCs, this results in digital post-correction; for DACs, this results in digital pre-correction. For example, offset could be compensated digitally for both ADCs and DACs by subtracting the measured offset in the digital domain.

#### • Analog correction

By tuning analog components, specific imperfections can be corrected. E.g., the unit elements inside a converter suffer from mismatch. This could be corrected by adding calibration elements to fine-tune the elements to their optimal value.

#### Mapping

A mapping method optimizes the overall performance by selecting a certain order or a certain combination within the available resources. For example, the mismatch of the unit elements inside a converter results in a limited performance. By reordering the unit elements, the overall performance can be optimized, even though the individual errors remain the same.

## 3.3 Application of the smart concept

The smart concept is a general idea to obtain knowledge on-chip in order to enhance the performance. As there are many different performance limitations and performance criteria, the smart concept can be applied in many different ways. The overview below illustrates how the smart concept can be applied advantageously for each of the performance criteria, defined in section 2.5.

#### • Speed, accuracy, power consumption, area

There are many trade-offs between these performance criteria. To illustrate the possibilities of the smart concept, mismatch of components is considered. In a conventional converter, the accuracy is directly related to the mismatch of the unit elements. For sufficient accuracy, large elements are required, resulting in a large area and increased parasitics, which can cause speed limitations and an increase in power consumption. When the mismatch errors could be determined and corrected on-chip, much smaller elements could be used, thereby giving potential improvements in accuracy, area, speed and power consumption.

#### Compatibility to future technologies

Efficient low-voltage compatible circuits (e.g. open-loop instead of closed-loop

amplifiers) often do not meet the performance requirements (e.g. because of non-linearity). The smart concept allows the use of these circuits as their associated limitations can now be overcome by a smart correction.

#### • Interference compatibility

On-chip sensors could be implemented to measure the interference. Based on that, a mapping method for both analog and digital hardware could be used to reduce the interference for the most critical analog blocks.

#### Testability

The extracted information in a smart converter can be used to enable on-chip self-test by measuring relevant test parameters like functionality or accuracy.

#### • Yield

Instead of relying on intrinsic performance, additional correction resources can be built into a smart converter to allow compensation of a larger performance spread, which can improve the yield.

#### • Portability, design time and risk

In an intrinsic design, the performance is determined by the technology, thereby complicating portability as the performance has to be verified again in the new technology. In a smart approach, the technology limitations can be overcome. Because of that, the technology has less influence on the performance which simplifies portability and reduces design time and risk.

#### Flexibility

As a large part of the smart circuitry can be implemented with programmable logic, the smart concept allows optimization of a specific converter for various requirements, thereby adding flexibility to the design.

While the list illustrates the versatility of the smart concept, it should not be expected that all smart designs improve all these parameters at once. For example, in [6] a smart redesign of a conventional pipelined ADC [7] is proposed: an open-loop amplifier is used instead of a closed-loop amplifier to reduce the power consumption. Then, the non-linearity of the open-loop structure is corrected by a smart approach. Nonetheless, the FoM of the smart converter (2.3pJ/conv.step) is worse than the FoM of the original design (1.3pJ/conv.step) <sup>2</sup>. However, the smart design performs better with respect to technology compatibility, which makes it an attractive solution for future technologies.

#### 3.4 Focus in this work

The aim of this work is to investigate the feasibility of relevant smart AD and DA converter concepts. The main focus will be on the application driven performance criteria

<sup>&</sup>lt;sup>2</sup>The FoM definition is given in chapter 6.

(speed, accuracy, power consumption and area), while the technology compatibility is also taken into account. In chapter 4, a smart concept for DA converters is proposed to improve the performance with respect to area; the chip implementation of this concept will be discussed in chapter 5. In chapter 6, a smart concept for AD converters is proposed to improve the performance with respect to the speed/power/accuracy trade-off; the chip implementation is shown in chapters 7 up to 9.

## 3.5 Conclusion

In this chapter, the smart converter concept was proposed. It was shown that this concept can overcome some important technology limitations, thereby improving the performance and the compatibility to future technologies. As the concept is implemented on-chip, it is also compatible with mixed-signal integrated systems. Because of these reasons, the smart concept suits to the trends in applications, technology and system design.

# Chapter 4

## Smart DA conversion

This chapter applies the previously presented smart concept to digital-to-analog converters. In the proposed scenario, the smart concept will be used to reduce the chiparea of a current-steering DAC while maintaining overall accuracy. In this chapter, the theory of the approach will be studied, while the actual proof-of-concept by means of a chip implementation will be given in chapter 5. Parts of this chapter have been published previously in [8, 9, 10].

## 4.1 Introduction

In the previous chapter, the versatility of the smart concept was explained. Comprehensibly, in reality one can only demonstrate the feasibility of a limited part of the overall concept. In this chapter, one relevant item from the smart concept will be selected for further investigation and actual chip implementation. In chapter 6, where the smart concept will be applied to AD converters, different items will be chosen to show another view of the possibilities of the smart concept.

Existing work that includes some of the aspects of the smart concept aims for improving performance by means of correction, calibration or mapping. Typically, the most important goal is to improve the accuracy by counteracting the effect of a certain error (or a set of errors). An overview of error mechanisms and correction methods is described in [11]; the enumeration below gives a summary of the described error mechanisms and examples of work that counteract the errors by means of correction.

- Amplitude mismatch, e.g. [12, 13]

- Timing mismatch, e.g. [14]

- Harmonic distortion, e.g. [11]

- Data-switching errors, e.g. [15]

Apart from improving accuracy, the methods can also have other benefits. For example, when timing mismatch can be corrected, it does not only improve accuracy, it can also extend the usable frequency range, thus increase the speed of operation. Or, when amplitude mismatch can be corrected, one might use smaller (and thus less accurate) elements to reduce the area, and still meet the accuracy requirements.

In this work, the smart concept will be applied with as main goal to reduce the area of the analog part of a DAC as much as possible. Because of the area reduction, a large amount of amplitude mismatch can be expected. Thus, a digitally-implemented smart solution will be applied to maintain high accuracy. The motivation for this goal is that currently, DAC designs do not scale down in size as fast as technology-scaling would permit, because of accuracy requirements. At the same time, digital components do scale down with technology. As a consequence, in mixed analog/digital systems, the DAC becomes relatively larger in size compared to the digital hardware. Because of that, it is worthwhile to investigate solutions to reduce the area of the DAC.

When the area of the DAC is considered, one can refer to either the overall DAC area or the analog-core area:

#### • Overall DAC area

Complete area of the DAC (analog and digital parts) and area of the add-on digital circuitry for the smart solution.

#### Analog core area

Area of the analog parts of the DAC only, excluding digital parts inside the DAC or digital parts added to the DAC.

In situations where the DAC is a stand-alone device, the most relevant goal would be to minimize the overall DAC area instead of minimizing the analog core area. However, the goal in this case is to minimize the analog core area, even when it comes at the cost of an increased area of the digital part. This is motivated by the following reasons:

#### • Application in large-scale mixed-signal ICs

A first motivation is that the smart concept envisions large-scale mixed-signal integrated systems. In these systems, there are applications for which the analog core area is more important than the overall area; two examples where the analog core area is the most relevant area to be optimized are given here:

A first example is when the DAC is used as an accurate on-chip test-signal generator during calibration of another on-chip component. After calibration, the digital hardware required for the DAC can be reprogrammed for another task. Then, because of the flexibility of the digital hardware, the only overhead in terms of area is coming from the analog DAC core.

Another example is a general-purpose digital chip in which, for a few applications, a DAC is required. As the chip is a general-purpose IC and the DAC is only used for a few applications, it would be expensive to implement a large-size DAC on all these devices. On the other hand, when the DAC area would be very small, the overhead would be acceptable to implement the DAC on all chips. Then, only for the few applications that actually use the DAC, digital resources have to be allocated to control the DAC. Even when a substantial amount of digital resources would be required, this can still be the most effective solution on the average, as most application do not use the DAC.

#### Different scaling for analog and digital

A second motivation, as explained before, is that digital scales down with technology much faster than analog. Thus, reducing the area of the analog core will also reduce the overall area on the long term.

Given this background, the aim of area reduction will be limited to the analog core area in this work.

This chapter starts with a discussion on area constraints of DA converters in section 4.2. Existing approaches to reduce the area are reviewed in section 4.3, and a new concept for area reduction is introduced in section 4.4. A design example is shown in section 4.5 and conclusions are drawn in section 4.6.

## 4.2 Area of current-steering DACs

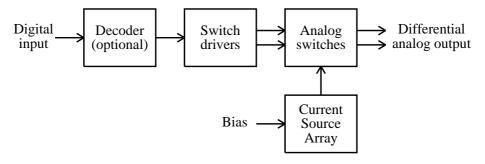

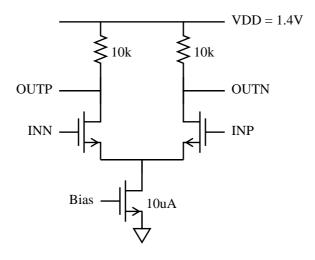

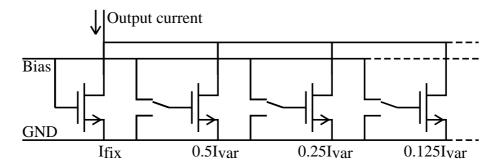

A simplified view of the basic architecture of a current-steering DAC is shown in fig. 4.1. The digital input code is optionally translated in a decoder (e.g. a binary-to-thermometer decoder). Then, the decoded digital signal drives a set of switch drivers that control the analog switches. By means of the analog switches, the current sources from the current-source-array (CSA) are connected to either the positive or the negative output of the DAC, thereby generating the output signal as a function of the applied input code.

Figure 4.1: Architecture of a current-steering DAC.

The decoder, switch drivers and switches can be scaled down as much as the technology permits. However, the size of the CSA is limited by the required accuracy of

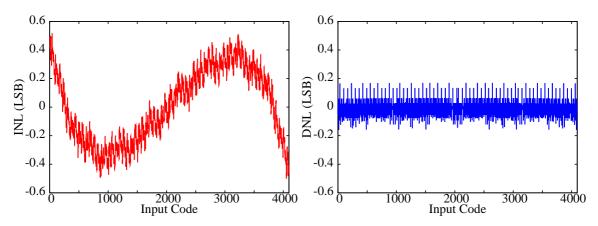

the DAC. In table 4.1, an overview of recent work on current-steering DACs is given. All these designs are based on intrinsic-accuracy, i.e. they do not employ special algorithms or calibration to enhance the performance. The achieved static accuracy is indicated by the ENOB that was calculated as:

$$ENOB = resolution - log_2(max(INL_{max}, DNL_{max})) - 1, \qquad (4.1)$$

where  $INL_{max}$  and  $DNL_{max}$  are expressed in LSB of the native resolution<sup>1</sup>. From the table, where both the total area of the DAC and the (estimated) area of the current-source-array (CSA) are given, it can be observed that:

- The area increases rapidly as a function of the resolution/accuracy.

- The CSA is a major component in the overall area.

| Reference  | Technology            | Sampling rate<br>(MSps) | Resolution (bit) | ENOB (bit) | Total area (mm <sup>2</sup> ) | CSA area (mm <sup>2</sup> ) |

|------------|-----------------------|-------------------------|------------------|------------|-------------------------------|-----------------------------|

| [16], 2001 | $0.35 \mu \mathrm{m}$ | 1000                    | 10               | 11.3       | 0.35                          | 0.1                         |

| [17], 2006 | $0.18 \mu \mathrm{m}$ | 250                     | 10               | 12.3       | 0.35                          | 0.2                         |

| [18], 2004 | $0.18 \mu \mathrm{m}$ | 600                     | 12               | 11.0       | 1.1                           | 0.4                         |

| [19], 2004 | $0.18 \mu \mathrm{m}$ | 320                     | 12               | 12.3       | 0.44                          | 0.2                         |

| [20], 2001 | $0.35 \mu \mathrm{m}$ | 500                     | 12               | 12.7       | 1.0                           | 0.5                         |

| [21], 2009 | $0.065 \mu { m m}$    | 2900                    | 12               | 12.0       | 0.3                           | 0.1                         |

| [22], 2004 | $0.18 \mu \mathrm{m}$ | 1400                    | 14               | 12.2       | 2.5                           | 0.4                         |

Table 4.1: Area of intrinsic-design DA converters.

The reason why the area increases so fast as a function of the resolution, and why the CSA is a major contributor to the overall area is because of accuracy requirements: to achieve appropriate INL/DNL performance, the current sources in the CSA need to be matched to each other. The higher the resolution, the more stringent the matching becomes, which translates into a larger area. A lower-bound for the required area for the CSA will be derived next.

The target requirement is set such that a  $3\sigma$  mismatch-error still achieves 0.5LSB INL performance. From [23], it is known that for a resolution of N bit, this leads to the following matching constraint:

$$\frac{\sigma_u}{I_u} = \frac{1}{6\sqrt{2^{N-1}}} \ , \tag{4.2}$$

where  $\sigma_u/I_u$  represents the relative standard deviation of the unit current element (the LSB current source); i.e.  $\sigma_u$  is the absolute standard deviation and  $I_u$  the nominal current of the unit element.

From a.o. [11], the standard deviation of the unit element can be expressed in terms of the mismatch parameters of the technology  $(A_{\beta} \text{ and } A_{V_t})$ , the biasing condition

<sup>&</sup>lt;sup>1</sup>Note that in this work, *resolution* refers to the number of digital bits of the converter, without referring to the actual accuracy of the converter.

$(V_{qs} - V_t)$  and the dimensions of the unit element  $(W_u \text{ and } L_u)$ :

$$\frac{\sigma_u}{I_u} = \sqrt{\frac{A_\beta^2 + 4A_{V_t}^2/(V_{gs} - V_t)^2}{2W_u L_u}}$$

(4.3)

For a given technology (e.g. a  $0.18\mu \text{m}$  CMOS technology:  $A_{\beta} = 2\%\mu \text{m}$  and  $A_{V_t} = 4\text{mV}\mu \text{m}$ ), and an estimate of the biasing condition (e.g.  $V_{gs} - V_t = 0.5\text{V}$ ), (4.3) simplifies to:

$$\frac{\sigma_u}{I_u} = \frac{0.018}{\sqrt{W_u L_u}} \tag{4.4}$$

Note that for newer technologies,  $A_{\beta}$  and  $A_{V_t}$  are typically improving slightly, thereby improving the matching. However, at the same time, new technologies allow less voltage-headroom, such that the loss of  $V_{gs} - V_t$  counteracts the improved matching properties. As a consequence, little improvement of the relation given by (4.4) is expected for DACs designed in newer technologies.

Combining equations (4.2) and (4.4) yields a relation between the resolution and the area of the unit element:

$$W_u L_u = 0.006 \cdot 2^N \tag{4.5}$$

As the DAC is composed of a total of  $2^N$  unit elements, the total gate-area becomes:

$$A_{dac} = 0.006 \cdot 4^{N} \ [\mu \text{m}^{2}] \tag{4.6}$$

Note that this equation reveals that the area increases with a factor of four for each additional bit of resolution; this explains why in table 4.1 the area increases so rapidly as a function of the resolution. Table 4.2 shows the theoretical minimum area of the CSA for various resolutions, based on (4.6). With the used mismatch-parameters, the values are only valid for a specific  $0.18\mu m$  technology. But, as explained previously, it is expected that the relation is not affected strongly by the evolution of technology. In practice, the CSA area will become even larger due to overhead like wiring, source/drain/gate connections, spacing, etc. Especially for 12-bit resolution and higher, the required area becomes large. For these situations, an area-reduction technique becomes necessary if the area is a critical design parameter.

| Number of bits $(N)$             |        |       |     | 14  |    |

|----------------------------------|--------|-------|-----|-----|----|

| Area $(A_{dac})$ mm <sup>2</sup> | 0.0004 | 0.006 | 0.1 | 1.6 | 26 |

Table 4.2: Lower bound for the active area of the CSA in a  $0.18\mu m$  technology.

## 4.3 Correction of mismatch errors

The fact that for high-resolution current-steering DACs an area reduction technique is advantageous has been recognized, and led to the development of correction techniques that maintain the final overall accuracy while starting with intrinsically less-accurate elements. By requiring less intrinsic accuracy, the area of the CSA can

be reduced. A classification and an explanation of the existing methods for area reduction can be found in [11].

Table 4.3 gives an overview of recent work on designs that include some form of mismatch-correction to achieve area-reduction. In [24], a reshuffling method is used to order the elements in such a way that the accuracy improves. In the other approaches, the main current sources are calibrated by trimming or by adding a calibration current to compensate for the mismatch. In the table, the CSA area includes the area of the nominal current sources plus the area of the calibration sources.

| Reference  | Technology            | Sampling rate | Resolution | ENOB  | Total area | CSA area |

|------------|-----------------------|---------------|------------|-------|------------|----------|

|            |                       | (MSps)        | (bit)      | (bit) | $(mm^2)$   | $(mm^2)$ |

| [13], 2005 | $0.25 \mu \mathrm{m}$ | 50            | 12         | 11.7  | 1.1        | 0.3      |

| [25], 2008 | $0.18 \mu \mathrm{m}$ | 100           | 12         | 13.3  | 0.8        | 0.2      |

| [24], 2007 | $0.18 \mu { m m}$     | 200           | 14         | 12.5  | 3          | 0.28     |

| [26], 2004 | $0.18 \mu { m m}$     | 200           | 14         | 13.6  | 1          | 0.5      |

| [27], 2001 | $0.18 \mu { m m}$     | 100           | 14         | 14    | 1          | 0.3      |

| [28], 2003 | $0.13 \mu \mathrm{m}$ | 100           | 14         | 14.2  | 0.1        | 0.05     |

| [29], 2000 | $0.35 \mu \mathrm{m}$ | 100           | 14         | 14.5  | 11.8       | 1.8      |

| [12], 2003 | $0.25 \mu \mathrm{m}$ | 400           | 16         | 16    | 2          | 0.8      |

Table 4.3: Area of corrected DA converters.

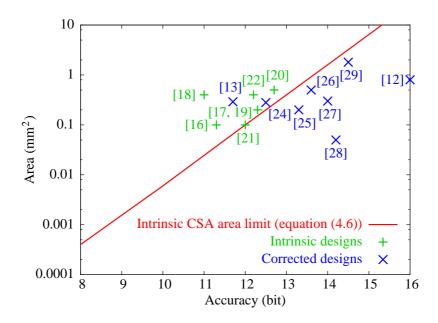

Figure 4.2 shows the area of the CSA for the references from table 4.1 and table 4.3 as a function of the achieved accuracy. Also shown is the theoretical intrinsic CSA area limit (4.6).

Figure 4.2: Area of the CSA for intrinsic and corrected designs.

From the figure, it can be concluded that:

• The corrected designs achieve a higher area-accuracy performance when compared to the intrinsic designs.

- The intrinsic designs can never achieve an area below the intrinsic CSA-limit; the corrected designs can achieve an area around or below the CSA-limit.

- In most cases, the corrected designs aim for a higher resolution and a higher accuracy than the intrinsic designs.

Though the calibration methods can overcome the intrinsic CSA area limitation, the area improvement is practically limited as the number of current elements increases to facilitate calibration: next to the main current sources, also calibration sources are required. As soon as the area of the unit elements becomes substantially reduced, it is not the *area* of the elements but simply the *amount* of elements that determines the overall CSA area. This is because the overhead caused by e.g. wiring and spacing will increase as a function of the number of elements, such that the overhead-area will become dominant.

Concluding from the results of intrinsic and corrected designs, there are two factors that determine the CSA area; and both should be minimized in order to minimize the CSA area:

- The area of the current-source elements.

- The number of current-source elements.

In the following section, an approach is proposed that aims at minimizing both these factors to achieve a further reduction of the CSA area.

## 4.4 Sub-binary variable-radix DAC

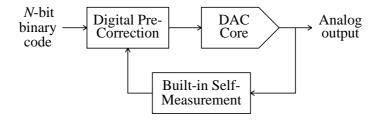

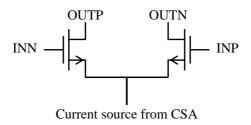

## 4.4.1 System overview

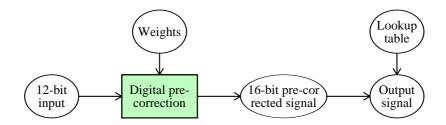

Pursuant to the aim of minimizing the area of the CSA and solving the related issues in the digital domain, a digitally pre-corrected DAC is proposed. A general view of the system is given in fig. 4.3. The DAC core contains the switch drivers, switches and the area-minimized CSA. The mismatch-errors of the current sources

Figure 4.3: Digitally pre-corrected DAC with built-in self-measurement.

are corrected by the digital pre-correction block that re-maps the binary input codes to appropriate combinations of current sources. A built-in measurement algorithm is used to measure the actual deviations of the individual current sources, such that the digital pre-correction algorithm can determine a suitable combination of current sources for each input code.

As a starting point for minimizing the CSA area, a first consideration is the segmentation of the current sources. The segmentation determines the number of independent current sources within the CSA. The three common options are:

- Binary architecture; composed of N binary-scaled current sources.

- Thermometer architecture; composed of  $2^N 1$  unary-scaled current sources.

- Segmented architecture; composed of a M binary-scaled and  $2^{N-M} 1$  unary-scaled current sources, with 1 < M < N.

From these options, the binary architecture has the least number of independent sources. As a consequence, according to the conclusion from the previous section, the binary architecture should have the potential to achieve the smallest CSA area.

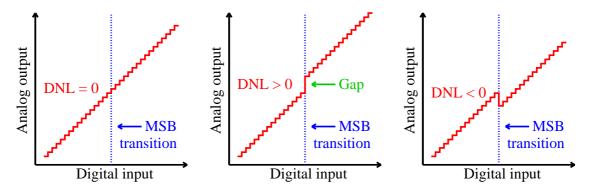

However, when a binary architecture is used without any modification, digital precorrection can not correct all types of mismatch errors. Figure 4.4 illustrates several transfer curves for a 5-bit binary-scaled DAC: the nominal curve, the curve in case of a positive DNL error in the MSB, and the curve in case of a negative DNL error in the MSB. While considering the MSB only in this example, a comparable situation

Figure 4.4: Transfer curve of a 5-bit DAC: no mismatch (left), a 'positive' (middle) and a 'negative' (right) deviation of the MSB.

can occur with the other sources of the DAC. The large DNL error produced for DNL > 0 can not be reduced with pre-correction, as pre-correction can only re-map the input code to an existing combination of current sources that approximates the desired output level. However, for DNL > 0, there is no combination of current sources available to fill the gap in the output range. On the other hand, the large DNL error for DNL < 0 can be corrected with pre-correction, as there is a 'gap-free'

continuum of output levels. By digital re-mapping, the overlap (or non-monotonicity) of the curve can be removed to obtain a smooth transfer curve. However, as a side effect of the overlap, the full-scale range of this converter will be slightly smaller than usual.

In short, for the digital pre-correction to operate properly, 'gaps' (DNL > 0) are not allowed but 'overlap' (DNL < 0) is allowed. As the nominal transfer curve of a normal DAC is designed for DNL = 0, there is a 50% probability that a 'gap' will occur in reality. By means of redundancy, the probability of a 'gap' can be reduced to an arbitrary low value by design: instead of designing the nominal transfer curve as in fig. 4.4 (left), it is designed as in fig. 4.4 (right). Thus, redundancy introduces intentional overlap (DNL < 0) of the nominal transfer curve to guarantee that the continuum of the output range remains, also in case of mismatch. While the figure illustrates redundancy for the MSB only, in reality this redundancy requirement needs to be implemented for each bit of the converter. In a certain way, adding calibration current sources (as in a.o. [11]) adds redundancy. However, that approach also leads to a substantial increase of the amount of current sources; which is undesirable as explained in the previous section. Therefore, in this work, the use of a sub-binary radix is proposed to introduce redundancy while limiting the total number of current sources.

Note that the fundamental principle of a sub-binary radix for DACs is equivalent to the principle of a sub-binary radix for ADCs (as explained in e.g. [30]): in ADCs the redundancy is used to alleviate the effect of comparator mismatch, whereas in DACs, the redundancy is used to alleviate the effect of current source mismatch. Also note that, independently from this work, prior art on sub-binary radix DACs exists [31], but that work does not mathematically optimize the redundancy, uses a fixed instead of a variable radix, and requires a more complex measurement method.

In the following sections, the design of the DAC core with redundancy, the self-measurement structure and the digital pre-correction algorithm will be explained.

## 4.4.2 Redundancy

A normal N-bit binary converter is composed of k=N current sources. These sources  $I_0$  (LSB) up to  $I_{k-1}$  (MSB) are chosen relatively to the unit element  $I_u$  using the ratios  $\alpha_0$  up to  $\alpha_{k-1}$ . The ratios  $\alpha_i$  are chosen such that each source is exactly 1 LSB larger than the sum of all smaller sources:

$$\alpha_j = \sum_{i=0}^{j-1} \alpha_i + 1 \text{ for } 0 \le j < k ,$$

(4.7)

leading to the binary-scaled sequence of  $\alpha$ 's: 1, 2, 4, 8, 16,  $\cdots$ . However, when due to mismatch one of the current sources is actually larger than expected, a 'gap' (as in fig. 4.4) arises, that can not be corrected with digital pre-correction. To avoid this

situation, redundancy is added by making  $\alpha_j$  intentionally smaller than the sum of all smaller sources plus one LSB:

$$\alpha_j < \sum_{i=0}^{j-1} \alpha_i + 1 \text{ for } 0 \le j < k$$

(4.8)

An example of a sequence, fulfilling this constraint, is e.g.: 0.7, 1.3, 2.4, 4.6, 8.8, .... The amount of redundancy  $r_j$  for each source can be expressed as:

$$r_j = 1 - \alpha_j + \sum_{i=0}^{j-1} \alpha_i \text{ for } 0 \le j < k ,$$

(4.9)

Thus, for  $r_j = 0$ , there is no redundancy and (4.9) simplifies to (4.7). To maintain redundancy, for all sources the following requirement has to be satisfied:

$$r_j > 0 \text{ for } 0 \le j < k \tag{4.10}$$

The more redundancy is added, the more severe deviations due to mismatch can be compensated by pre-correction. However, also note that the more redundancy, the more sources k have to be employed to compensate the full-scale reduction of the converter due to redundancy.

Due to the stochastic spread of the unit cells, the actual value of each source becomes a stochastic value  $\underline{\alpha}_i$  with mean  $\alpha_i$  (the designed value) and spread  $\sqrt{\alpha_i} \frac{\sigma_u}{I_u}$ . To guarantee that all required output levels can be produced with sufficient accuracy using pre-correction, the relations from (4.9) and (4.10), taking the stochastic spread of the sources into account, have to be fulfilled. This leads to the following set of requirements:

$$\underline{r}_{j} > 0 \text{ for } 0 \leq j < k \text{ , with:}$$

$$\mathbf{E}\{\underline{r}_{j}\} = 1 - \alpha_{j} + \sum_{i=0}^{j-1} \alpha_{i}$$

$$\sigma_{\underline{r}_{j}} = \frac{\sigma_{u}}{I_{u}} \sqrt{\sum_{i=0}^{j} \alpha_{i}} ,$$

$$(4.11)$$

where  $\mathbf{E}\{\underline{r}_j\}$  is the expectation of  $\underline{r}_j$ , thus the nominal built-in redundancy.  $\sigma_{\underline{r}_j}$  is the spread of  $\underline{r}_j$ , which corresponds to the mismatch of the elements. When all constraints  $\underline{r}_j$  are fulfilled, the largest 'gap' in the transfer curve is guaranteed to be less than 1 LSB. Thus, each required output level can be generated within  $\pm 0.5$ LSB by means of re-mapping the input code, which is sufficient for meeting the target accuracy. The desired probability of fulfilling each constraint  $\underline{r}_j$  can be expressed as a desired level of confidence  $\lambda \sigma$  with which the constraint has to be fulfilled:

$$P\{\underline{r}_j > 0\} = 1 - \frac{1}{2} \operatorname{erfc}\left(\frac{\lambda}{\sqrt{2}}\right) \tag{4.12}$$

The confidence level requires that:

$$\mathbf{E}\{\underline{r}_j\} - \lambda \sigma_{\underline{r}_j} = 0 , \qquad (4.13)$$

i.e.: a  $\lambda \sigma$  deviation from the nominal value  $\mathbf{E}\{\cdot\}$  is still marginally acceptable for the target requirement (4.11). Using equation (4.11), (4.13) can be rewritten as:

$$\mathbf{E}\{\underline{r}_{j}\} = \lambda \sigma_{\underline{r}_{j}}$$

$$1 - \alpha_{j} + \sum_{i=0}^{j-1} \alpha_{i} = \lambda \frac{\sigma_{u}}{I_{u}} \sqrt{\sum_{i=0}^{j} \alpha_{i}}$$

$$\left(1 + \sum_{i=0}^{j-1} \alpha_{i}\right)^{2} + \alpha_{j}^{2} - 2\alpha_{j} \left(1 + \sum_{i=0}^{j-1} \alpha_{i}\right) = \left(\frac{\lambda \sigma_{u}}{I_{u}}\right)^{2} \sum_{i=0}^{j} \alpha_{i}$$

$$\Rightarrow$$

$$\alpha_{j}^{2} - b_{j} \alpha_{j} + c_{j} = 0, \text{ with }$$

$$b_{j} = 2\left(1 + \sum_{i=0}^{j-1} \alpha_{i}\right) + \left(\frac{\lambda \sigma_{u}}{I_{u}}\right)^{2}$$

$$c_{j} = \left(1 + \sum_{i=0}^{j-1} \alpha_{i}\right)^{2} - \left(\frac{\lambda \sigma_{u}}{I_{u}}\right)^{2} \sum_{i=0}^{j-1} \alpha_{i}$$

From this quadratic function of  $\alpha_j$ , the values of  $\alpha_j$  can be derived recursively given the relative spread of the unit cells and a desired confidence level:

$$\alpha_j = \frac{b_j - \sqrt{b_j^2 - 4c_j}}{2}$$

, with  $b_j$  and  $c_j$  as in (4.14). (4.15)

As opposed to previous work [31], where a fixed sub-binary radix was used, the presented approach utilizes a variable radix  $\rho_j$ . The radix is the ratio between two subsequent current sources:

$$\rho_j = \frac{\alpha_j}{\alpha_{j-1}} \tag{4.16}$$

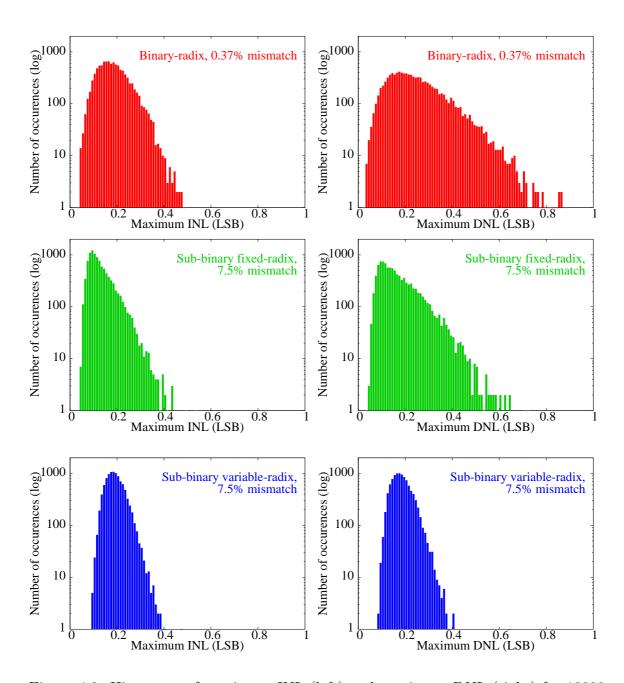

The variable radix stems from the design procedure equalizing the error probability for each constraint (4.15). By equalizing the error probability and adapting the radix, instead of equalizing the radix and adapting the error probability as in [31], the same yield can be achieved with less redundancy and hence less current sources. Moreover, as in the presented approach,  $\rho_j$  approximates 2 for  $j \to \infty$ , the amount of sources k required for a converter with redundancy comes close to the minimal value N as used in a binary-weighted converter without redundancy. Simulation results to confirm the advantages of the variable-radix over the fixed-radix will be shown in section 4.5.

#### 4.4.3 Self-measurement

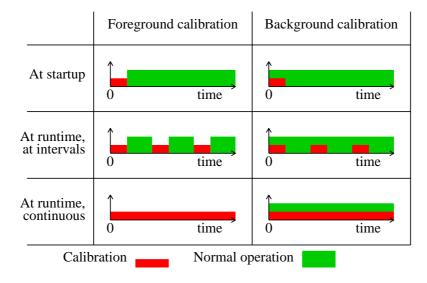

Before being able to pre-correct the mismatch errors of the current sources, a measurement procedure, measuring the actual values of the current sources, is required. After performing the self-measurement procedure at power-up, the actual values of the current sources are known in the digital domain, and the converter can start its normal ADC operation.

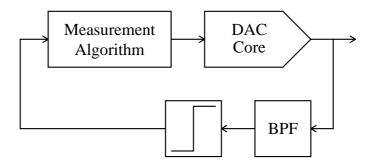

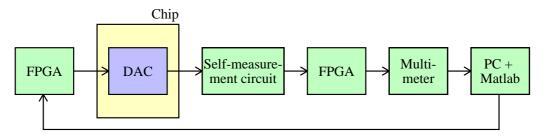

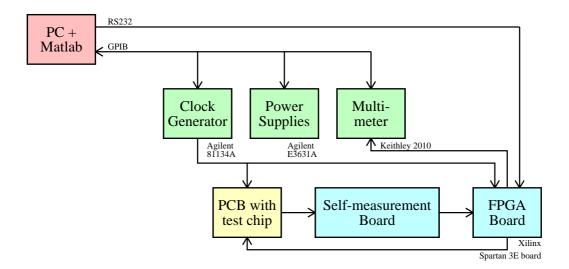

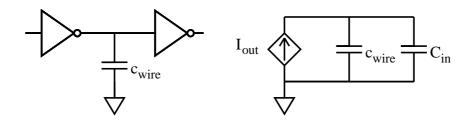

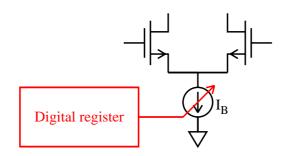

In order to implement the measurement technique on-chip, it has to fulfill several constraints: it has to be reliable, accurate, small, and realizable on-chip. Moreover, it is undesirable to modify the DAC-core to support the measurement procedure by means of additional switches or sources, as this could influence (dynamic) performance of the DAC adversely. To comply with all these constraints, the setup of fig. 4.5 is proposed. It uses a simple analog measurement circuit (composed of a band-pass filter (BPF) and a comparator), and a digital measurement algorithm that provides the digital input code to the DAC-core during the self-measurement. An important advantage of this setup is that it can measure the individual current sources by looking only at the overall (combined) output of the DAC. In that way, the method prevents the need for access to the individual current sources, which would complicate the circuit design.

Figure 4.5: Detailed view of the built-in measurement setup, composed of a band-pass filter, a comparator and an algorithm.

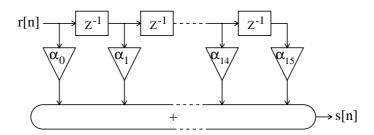

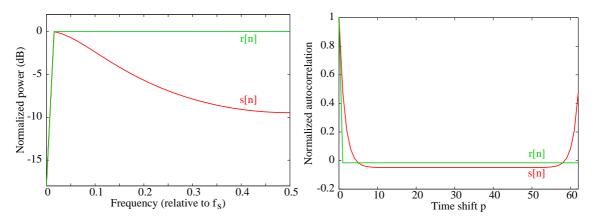

#### Measurement algorithm

The measurement algorithm aims at minimizing analog circuitry of the measurement technique by using digital algorithms as much as possible. Instead of measuring the values of the current sources in an absolute sense (which would require an accurate ADC), sources are measured relatively to each other only.

The idea of the method is to find for each current source j a combination of current sources 0 up to j-1, of which the combined output current  $I_{sum,j}$  approximates the actual current  $I_j$  of source j as good as possible. As the measurement is a relative measurement, the actual values of  $I_j$  and  $I_{sum,j}$  are not important, it is sufficient to find a combination of sources which properly approximates  $I_j$ :  $|\Delta_j| = |I_j - I_{sum,j}| \approx 0$ .  $I_{sum,j}$  can be written as:

$$I_{sum,j} = \sum_{i=0}^{j-1} S_{i,j} \cdot I_i , \qquad (4.17)$$

where  $I_i$  is the actual current of source i, and  $S_{i,j} = 0$  when source i is not used and  $S_{i,j} = 1$  when source i is used in the combination approximating  $I_j$ . The combination of sources composing  $I_{sum,j}$  can be found using a comparator determining the sign

of  $\Delta_j$ , and a successive-approximation algorithm minimizing  $|\Delta_j|$  by controlling the current sources. In the actual design, a BPF was added to the analog circuit as will be explained in the next section. The measurement algorithm determines the values of  $S_{i,j}$ , based on which the digital representation  $\omega_j$  of each current source j can be derived:

$$\omega_j = \sum_{i=0}^{j-1} S_{i,j} \cdot \omega_i \tag{4.18}$$

The measurement algorithm starts with initializing the digital representation of the smallest source (source 0)  $\omega_0$  to 1, an arbitrary unit value. Then, iteratively for all other sources j, starting with source 1, up to source k-1, the measurement procedure determining  $I_{sum,j}$  is performed, and the digitized estimation  $\omega_j$  can be derived. The algorithm determining  $\omega_j$  is illustrated in fig. 4.6. This algorithm is performed iteratively for the sources 1 up to k-1.

```

Turn off all sources (I_{sum} = 0) for i = j - 1 down to 0

Turn on source i (I_{sum} = I_{sum} + I_i) if I_{sum} > I_j

S_i = 0

Turn off source i (I_{sum} = I_{sum} - I_i) else

S_i = 1

end if end for

```

Figure 4.6: Algorithm, finding a combination of sources approximating source j.

At the end of the measurement loop, all weights are scaled to normalize the range to the full-scale range of the N-bit input-code.

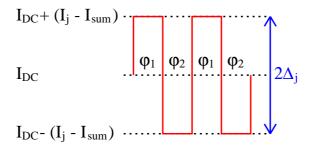

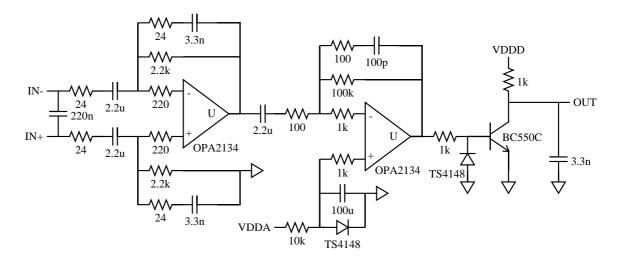

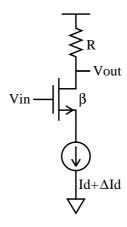

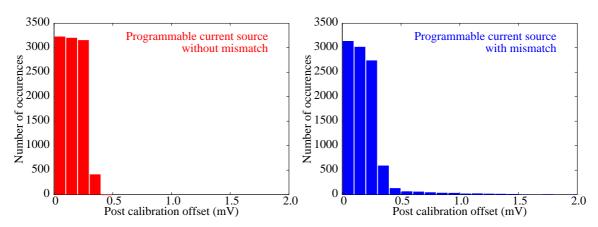

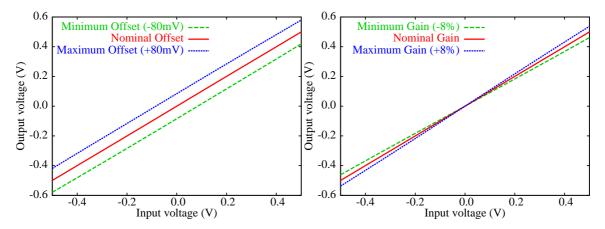

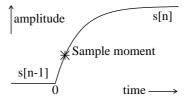

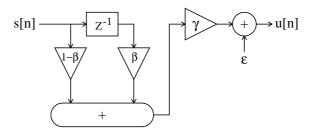

#### Analog measurement circuit

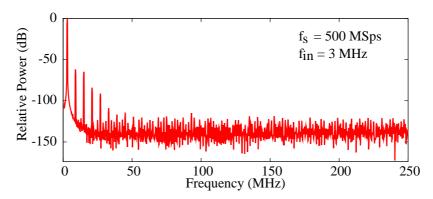

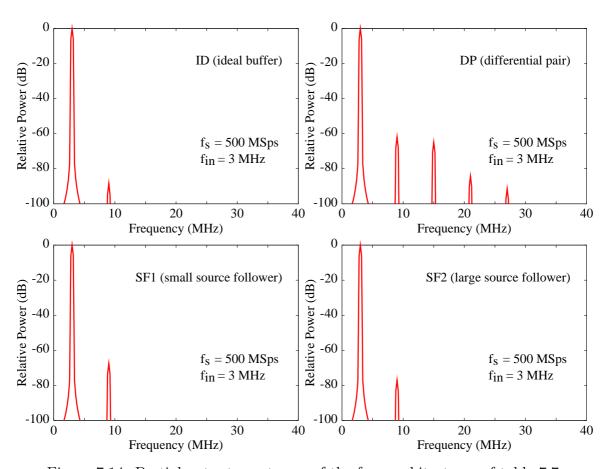

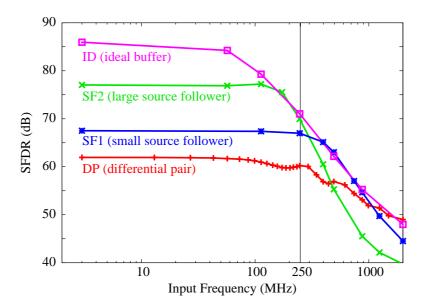

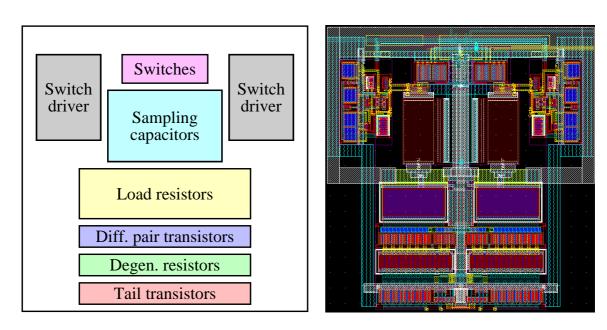

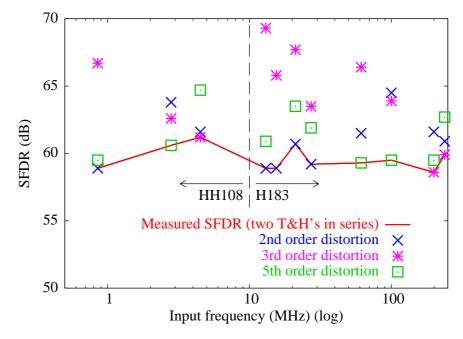

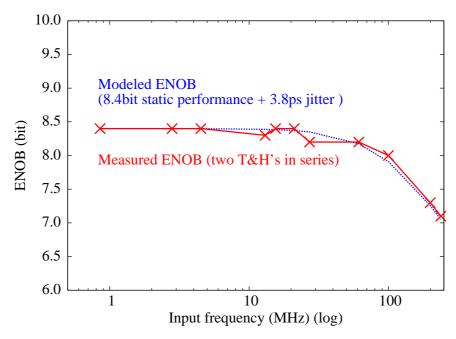

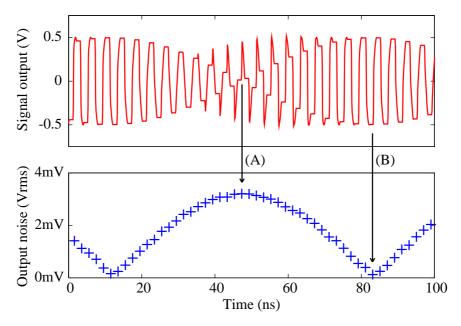

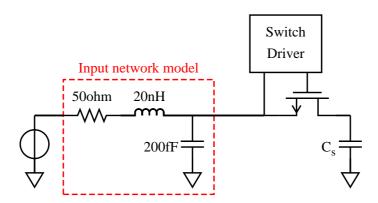

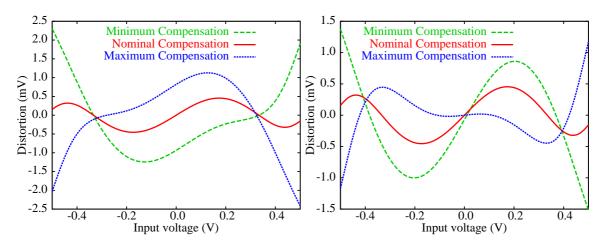

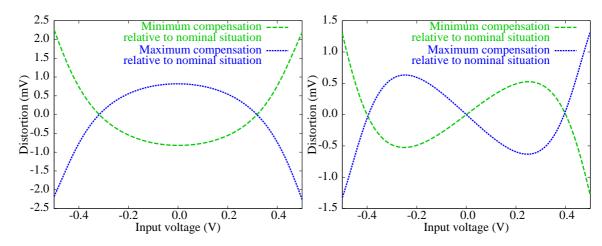

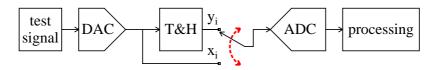

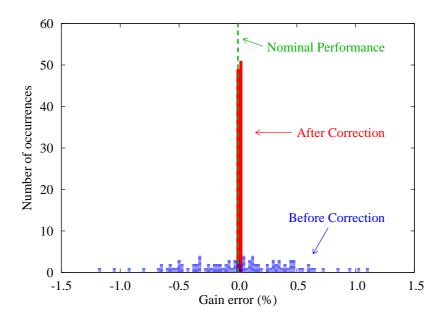

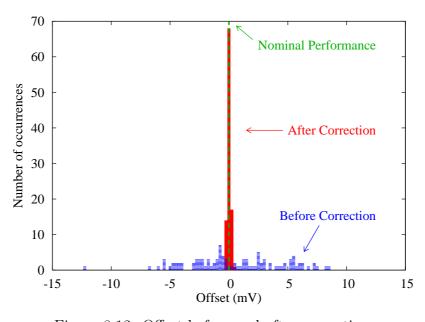

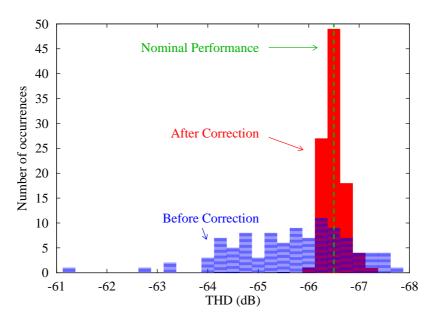

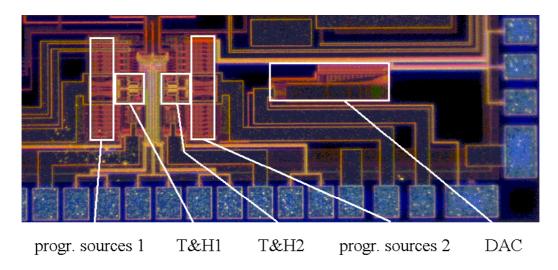

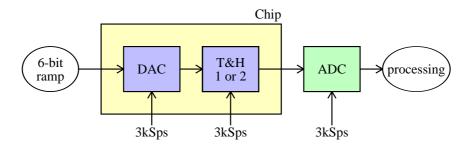

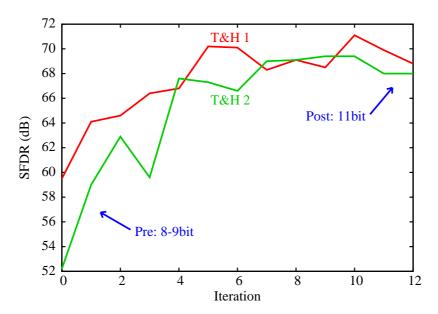

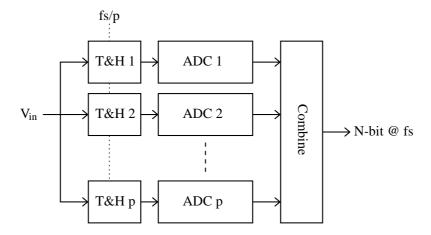

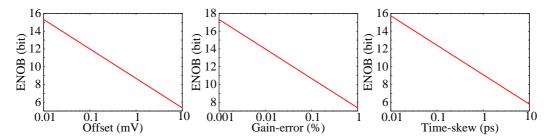

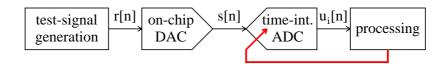

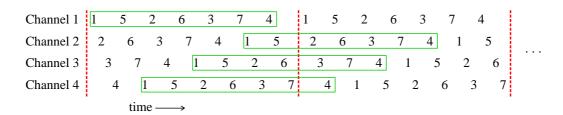

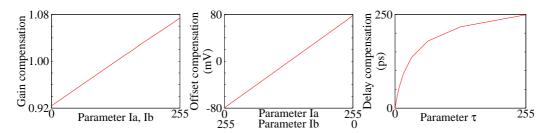

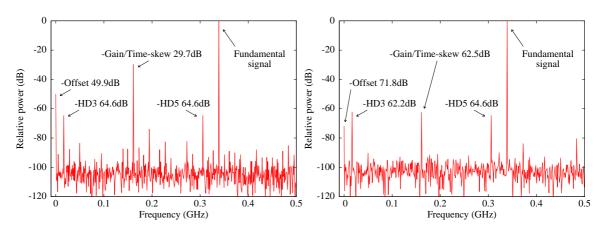

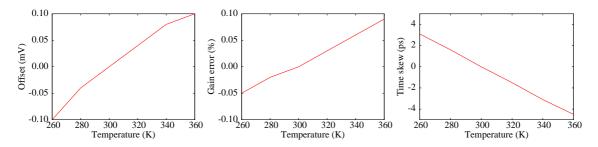

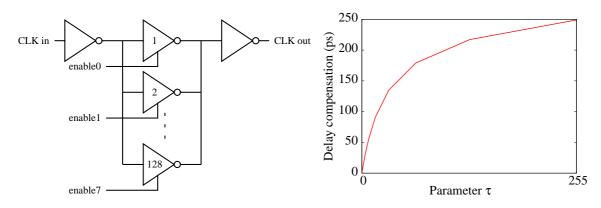

The analog part of the measurement setup has to provide the digital algorithm with the sign information of  $\Delta_j$ . In [31], a two-step approach is used. First the value of  $I_j$  is recorded on a variable current source (implemented as a sub-binary DAC). In the second step, the recorded value is compared to  $I_{sum}$ , yielding the sign of  $\Delta_j$ . The main disadvantage of this method is that it requires a complete DAC, of which the accuracy limits the accuracy of the measurement. Moreover, due to this implementation, the unit elements in the DAC-core have to be disconnected from the normal output and reconnected to the measurement circuitry by means of a switch, which could affect the performance. Therefore, another approach is proposed here requiring neither an additional DAC in the measurement setup nor a switch inside the DAC-core as it measures the voltage rather than sensing the current.