## InP-based membrane photodetectors on Si photonic circuitry

### Citation for published version (APA):

Binetti, P. R. A. (2009). *InP-based membrane photodetectors on Si photonic circuitry*. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR642815

DOI: 10.6100/IR642815

### Document status and date:

Published: 01/01/2009

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# InP-based Membrane Photodetectors on Si Photonic Circuitry

Cover illustration by Paul Verspaget & Carin Bruinink.

# InP-based Membrane Photodetectors on Si Photonic Circuitry

PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr.ir. C.J. van Duijn, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op dinsdag 9 juni 2009 om 16.00 uur

door

Pietro Ruggero Antonio Binetti

geboren te Bologna, Italië

Dit proefschrift is goedgekeurd door de promotor:

prof.dr.ir. M.K. Smit

Copromotor: dr. X.J.M. Leijtens

This work was supported by the Dutch Ministry of Economic Affairs (Smartmix Memphis) and the European Community (IST PICMOS). The devices reported in this thesis were realized in close cooperation with CEA-LETI (Grenoble, France), IMEC-UGent (Gent, Belgium), INL (Lyon, France) and TRACIT (Grenoble, France).

Copyright ©2009 Pietro Ruggero Antonio Binetti

Typeset using  $L_{Y}X$ , printed in The Netherlands. Cover illustration by Paul Verspaget & Carin Bruinink.

A catalogue record is available from the Eindhoven University of Technology Library.

Binetti, Pietro Ruggero Antonio

InP-based Membrane Photodetectors on Si Photonic Circuitry Proefschrift. – ISBN 978-90-386-1812-8 NUR 959 Trefw.: opto-elektronische componenten / heterogene integratïe / optische verbinding / fotodetectoren. Subject headings: optoelectronic devices / heterogeneous integration / optical interconnect / photodetectors.

ai miei genitori e a Paola

# Contents

| Та | ble O                                | ble Of Contents vi                                                                            |    |  |  |  |  |  |  |

|----|--------------------------------------|-----------------------------------------------------------------------------------------------|----|--|--|--|--|--|--|

| 1  | Intro                                | oduction                                                                                      | 1  |  |  |  |  |  |  |

|    | 1.1                                  | Introduction                                                                                  | 1  |  |  |  |  |  |  |

|    | 1.2                                  | Electrical interconnects: options and state-of-the-art                                        | 3  |  |  |  |  |  |  |

|    | 1.3                                  | Optical interconnects on Si ICs                                                               | 4  |  |  |  |  |  |  |

|    |                                      | 1.3.1 Options, challenges and state-of-the-art                                                | 8  |  |  |  |  |  |  |

|    |                                      | 1.3.2 Our approach                                                                            | 11 |  |  |  |  |  |  |

|    | 1.4                                  | Thesis overview                                                                               | 12 |  |  |  |  |  |  |

| 2  | Design of integrated components      |                                                                                               |    |  |  |  |  |  |  |

|    | 2.1                                  | Introduction                                                                                  | 15 |  |  |  |  |  |  |

|    | 2.2                                  | Interconnect waveguides                                                                       | 16 |  |  |  |  |  |  |

|    | 2.3                                  | Photodetector structure                                                                       | 17 |  |  |  |  |  |  |

|    |                                      | 2.3.1 Coupler design                                                                          | 17 |  |  |  |  |  |  |

|    |                                      | 2.3.2 Photodiode heterojunction                                                               | 25 |  |  |  |  |  |  |

|    | 2.4                                  | Conclusions                                                                                   |    |  |  |  |  |  |  |

| 3  | InP-on-Si Heterogeneous Technology 3 |                                                                                               |    |  |  |  |  |  |  |

| •  | 3.1                                  | Introduction                                                                                  |    |  |  |  |  |  |  |

|    | 3.2                                  | Bonding technology                                                                            |    |  |  |  |  |  |  |

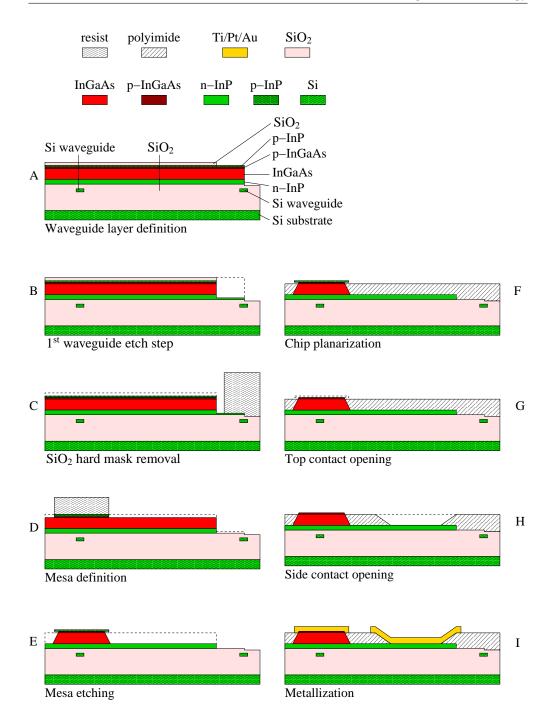

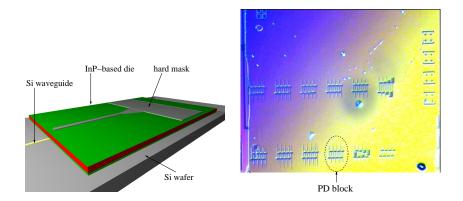

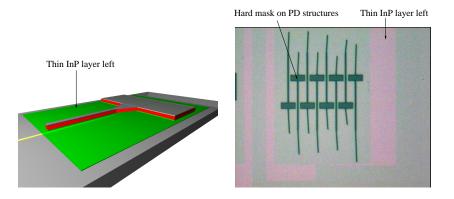

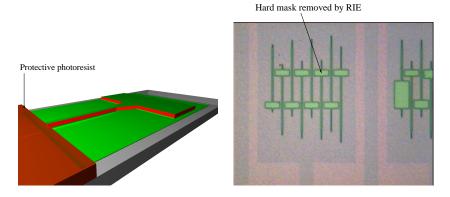

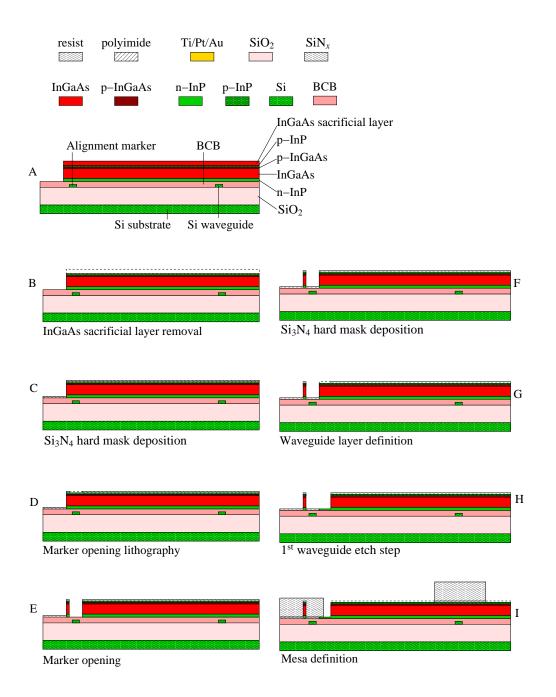

|    | 3.3                                  | InP-based detector processing                                                                 | 41 |  |  |  |  |  |  |

|    | 5.5                                  | 3.3.1 Photodetectors onto Si/Si <sub>3</sub> N <sub>4</sub> waveguides on SOI and CMOS wafers | 41 |  |  |  |  |  |  |

|    |                                      | 3.3.2 Fabrication process for a full optical link on SOI                                      |    |  |  |  |  |  |  |

|    |                                      | 3.3.3 Heterogeneous multiwavelength receivers                                                 |    |  |  |  |  |  |  |

|    | 3.4                                  | Conclusions                                                                                   |    |  |  |  |  |  |  |

|    | 5.4                                  |                                                                                               | 50 |  |  |  |  |  |  |

| 4  | InP-                                 | based Photodetectors on Si                                                                    | 57 |  |  |  |  |  |  |

|    | 4.1                                  | Introduction                                                                                  | 57 |  |  |  |  |  |  |

|    | 4.2                                  | Si and $Si_3N_4$ components                                                                   | 58 |  |  |  |  |  |  |

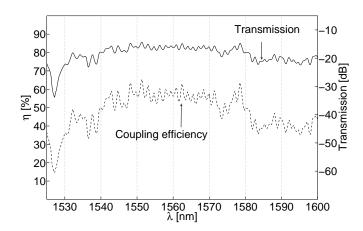

|    | 4.3                                  | Membrane InP couplers                                                                         | 59 |  |  |  |  |  |  |

|    |                                      | 4.3.1 Coupler realization                                                                     | 59 |  |  |  |  |  |  |

vii

|    |                | 4.3.2 Measurement results              |

|----|----------------|----------------------------------------|

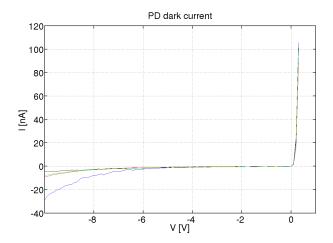

|    | 4.4            | Photodetectors                         |

|    |                | 4.4.1 Device design                    |

|    |                | 4.4.2 Fabrication                      |

|    |                | 4.4.3 Static measurements              |

|    |                | 4.4.4 Dynamic measurements             |

|    | 4.5            | Integrated optical link                |

|    |                | 4.5.1 Link design                      |

|    |                | 4.5.2 Fabrication                      |

|    |                | 4.5.3 Link measurements                |

|    | 4.6            | Photodetectors on CMOS                 |

|    |                | 4.6.1 Measurements                     |

|    | 4.7            | Conclusions                            |

| 5  | Hete           | erogeneous MWRs 83                     |

|    | 5.1            | Introduction                           |

|    | 5.2            | Integrated components                  |

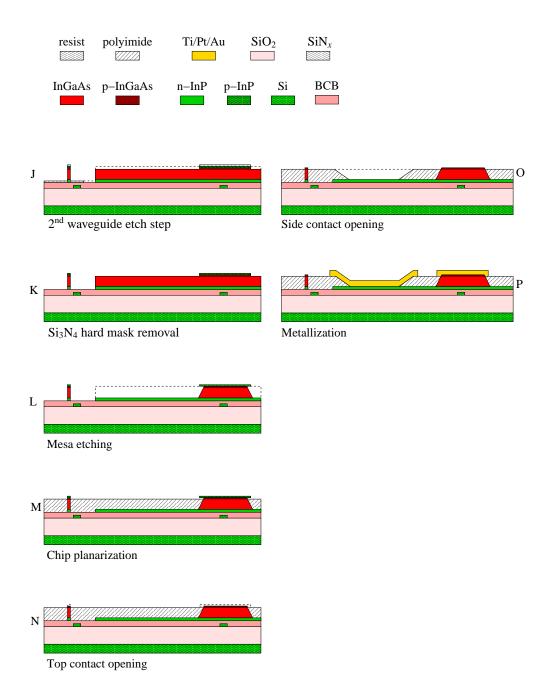

|    |                | 5.2.1 Fiber grating couplers           |

|    |                | 5.2.2 Interconnect waveguides          |

|    |                | 5.2.3 Multi-mode interference splitter |

|    |                | 5.2.4 Arrayed waveguide gratings       |

|    |                | 5.2.5 Photodetectors                   |

|    | 5.3            | Chip realization and characterization  |

|    |                | 5.3.1 Si passive components            |

|    | 5.4            | Conclusions                            |

| 6  | Con            | clusions and recommendations 105       |

|    | 6.1            | Conclusions                            |

|    | 6.2            | Recommendations                        |

| Re | eferen         | ces 107                                |

| No | men            | lature 115                             |

|    |                |                                        |

| Su | ımma           | ry 119                                 |

| Ac | cknov          | eledgments 12                          |

| Cı | ırricı         | lum Vitæ 123                           |

| Li | st of <b>j</b> | publications 125                       |

| In | dex            | 129                                    |

|    |                |                                        |

## **Chapter 1**

# Introduction

This chapter introduces the research carried out to develop the indium phosphide (InP) based photodetectors suitable for optical interconnections on silicon (Si) electronic integrated circuits presented in this thesis. The limitations expected with the use of electrical interconnections in future electronic chips are presented and provide the motivation for this work. Several options that are being investigated to face this problem are discussed and compared. Finally, the approach used in the project framework within which the InP-based detectors were developed is described.

## **1.1 Introduction**

In the last two decades optical fibers replaced conventional electrical wires in long-haul communications and are now a core part of the internet. That is mainly because of the high propagation losses that electrical lines suffer at high frequencies, as compared to the excellent performance of optical fibers in the telecom wavelength windows [1]. A migration from electrical to optical interconnections is underway for short-distance communications as well (in the mm range), namely between server backplanes and multirack machines [2]. Recent research studies discuss and demonstrate the advantage of using optics even for on-chip very short interconnections, in the sub-mm range [3]. Nowadays, electronic Integrated Circuits (ICs) make use of electrical wires to distribute the clock and other signals to different functional blocks of the IC and to provide power and ground connections. The electrical wiring system is currently used for both the intra-chip and chip-to-chip interconnections. Nevertheless, future generation Si ICs are expected to suffer a severe bottleneck in the interconnect level, going toward linewidth dimensions and higher bandwidth requirements [4]. In particular, with the technology scaling down and the signal switching frequency increasing, three main issues are predicted to slow down the steady increase in performance for complementary metal-oxide semiconductor (CMOS) ICs: signal propagation delay, power consumption and integration density. To see how the electrical interconnect wiring influences these characteristics, let us analyze what the

#### 1

wire characteristics are and where the problems occur. Electrical interconnect (EI) wires are normally modeled as *RLC* transmission lines. That is, lines that have:

- Resistance, which is the wire's opposition to the flow of electric current. The resistance (per unit length) depends on the wire's geometry and can be calculated by the material resistivity divided by the conductor's cross-sectional area.

- Capacitance, due to the wire's electrical potential difference relative to the ground and the proximity of adjacent wires. This is changed by adding or removing charge to the wire. The capacitance depends not only on the wire's geometry, but also on the wire's position in the circuit. As a matter of fact, considering the small feature sizes of current electronic ICs, the pitch between the wires is such that side-to-side capacitances are as important as the capacitance relative to the ground.

- Inductance. This wire characteristic is more difficult to identify, both qualitatively and quantitatively. When sending an electrical signal through a wire, a magnetic field is generated by the current flow. When the circuit switches between on and off state, the magnetic flux changes and this induces an electrical field that produces a return current flow. The induced electrical field is proportional to the current variation in time and the constant of proportionality is the inductance. In a complex circuit, the return currents flow in the adjacent wires with the least impedance, but these paths are not fixed, as they depend on the signal frequency. This problem translates into ambiguity in predicting the electromagnetic noise in the IC. The return path uncertainty is tackled by fixing a common reference for the grounding paths, which makes the circuit design more complicated.

With the reduction in feature size, which follows the exponential Moore's law [5], the geometry of the interconnect wires should also scale, and this raises a number of issues. The wire's resistance per unit length quickly increases as the wire's cross-section shrinks, and in most cases this is not compensated by the scaling down of the wire length. This leads to a strong limitation for the bandwidth of the data stream that can be routed through the wire: as the maximum data capacity in an interconnection line is proportional to  $A/l^2$ , where *l* is the length of the interconnect line and *A* the area of its cross-section, the data flow becomes more and more limited by the interconnection scaling problem [6].

Capacitance and inductance are less sensitive to the scaling problem, though [7]. It is unavoidable, however, that the *RC*-time characteristic of interconnect wires becomes a fundamental limitation for the bandwidth that can be used for the data transport across those wires. The reason the time characteristic is important is that it influences the total circuit delay: when a signal is launched through an interconnect wire, a certain time is needed for the residual currents from that transmission to die away before a second signal can be launched, or otherwise inter-symbol interference (ISI) will occur at the receiver side. As a result, the data transported by the buses that interconnect different parts of a digital computer has to flow at a much lower frequency than the clock frequency. This problem affects in particular the off-chip interconnections, but it is predicted to occur for the shorter on-chip interconnections too in the next few years [6]. Furthermore, capacitance and inductance are responsible for the dynamic power consumed by the electrical interconnects, which is the power consumed in the CMOS transistors when switching between on-state and off-state. This issue becomes worse with the signal switching frequency scaling up, and therefore it becomes an increasing limitation for the maximum data rate that can be used through the EIs.

Moreover, the circuit complexity and the integration density increase with the technology scaling, which implies that more wires have to be used to interconnect a larger number of devices. This requires a higher wiring density, which can be achieved with device miniaturization, but paying a price in terms of IC performance: miniaturized wires have a higher resistance and therefore dissipate more electrical power. The reduction in wire pitch increases the wire side-to-side capacitance and the electromagnetic (EM) crosstalk.

These issues are currently addressed in a number of ways. Repeaters are used to lower the wire delay and thus increase the bandwidth: this is analyzed in [7], where a comparison between an EI made with an uninterrupted wire and with a wire segmented into several stages each containing a repeating element is made. It is shown that the delay of the uninterrupted wire grows quadratically with the wire length, while by inserting repeaters periodically along the interconnect line, the total wire delay becomes equal to the number of repeated segments multiplied by the single stage delay, and therefore the total delay grows linearly with the interconnect length. Repeaters also make the interconnect wires more robust towards the device size scaling, as the *RC*-time characteristic of repeated wires stays constant. However, the drawback is that repeaters are relatively large and power-hungry components [7, 8].

For these reasons, a radical change in the architecture of the electronic chips started to take place in the recent years to address the problem at the interconnection level. In the next sections, the options that are being employed and investigated are discussed and the topic is then focused on our approach and the devices developed in that context.

## **1.2 Electrical interconnects: options and state-of-the-art**

The interconnection scaling problem described in Section 1.1 can be tackled in a number of ways, at different level of design of a chip, namely at logic gate design level, at hardware design level, at network-on-chip topology and architecture design level. Some examples are:

- Change the network architecture by using multicore processors, thus taking advantage

of the parallel communication between processor cores and of the shorter wires to interconnect several functional cores [7, 9–11]. Recently, an 8-core processor realized in

90 nm CMOS technology<sup>1</sup> working at frequencies over 4 GHz was deployed for commercial application [12], and an 80-core processor realized in 65 nm CMOS technology

working at frequencies over 5 GHz was demonstrated [13].

- Change the chip architecture by stacking several layers. This leads to a 3D integration scheme, which increases the architecture complexity but keeps the interconnect wires short and therefore keeps low their resistance and their bandwidth limitation [14].

<sup>&</sup>lt;sup>1</sup>Half-pitch between two integrated lines

- Change the IC network topology. Analytical models to optimize area and energy efficiency thanks to optimum layout of interconnect wires were studied [15].

- Minimize and miniaturize the interconnections and equalize the transmission channels [16].

- Optimize the hardware design by focusing on critical aspects. In [17], it was demonstrated that more than 50% of the overall dynamic power of CMOS multicore processors is consumed by the interconnect wiring, and that remains an issue for the most recent multiprocessor electronic chips [18, 19]. An interconnect-power saving design driver is therefore necessary for the next generation of CMOS circuits.

- Optimize the design at the logic gate level. Time optimization in logic paths with significant wire delays for the Very Large Scale Integration (VLSI) circuit design translates into significant improvement on the IC performance. In [20], design considerations for minimizing the delay in logic gates interconnected by electrical wires are presented. More specifically, the optimal size, number and location of the gates and of the repeater blocks in the presence of interconnects are studied.

The bottom line is that, even in state-of-the-art multiprocessor computers, the interconnect wires are the main limiting factor for power consumption and communication speed, rather than computation itself [21]. A limit is predicted on a short term, when machines employing terabit per second (Tbit/s) fast communications will be used (e.g. servers and supercomputers) [2].

## **1.3** Optical interconnects on Si ICs

A promising solution is given by radically changing the means of interconnection into a photonic interconnection layer, suitable for data transport in the optical domain [22, 23]. Clearly, due to the small feature size, the implementation of intra-chip and chip-to-chip interconnections in the optical domain can not rely on optical fibers, but requires the use of photonic integrated circuit (PIC) technology. Changing the means of interconnection into a photonic interconnection layer would provide a number of advantages with respect to the all-electrical solutions, namely:

- Low power consumption, as there would be no need for low impedance terminating lines [24].

- Simpler electronic IC architecture design, thanks to the optical interconnect (OI) immunity to EM noise.

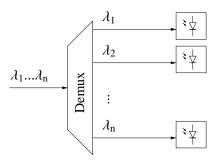

- Opportunity to configure a Wavelength Division Multiplexing (WDM) network-on-chip topology, not possible in the electrical domain. The WDM network is based on the following principle: at the transmitter side, the data from the network users is first converted from electrical to optical. The wavelengths carrying the optical signals are

**Figure 1.1:** WDM network link schematics: the wavelengths  $\lambda_1, \lambda_2, ..., \lambda_n$  carrying the optical signals launched by the transmitters TX1, ..., TXn are multiplexed in one channel and transmitted over the network. At the receiver side, a demultiplexer routes the different wavelengths to different channels. For each channel, the detectors RX1, ..., RXn convert the signals from the optical domain back into the electrical domain.

multiplexed in one channel and transmitted over the network. At the receiver side, a demultiplexer routes the different wavelengths to different channels. Finally, for each channel, a photodetector (PD) converts the signal from the optical domain back into the electrical domain (see Fig. 1.1).

• High-speed interconnects, thanks to the high data capacity allowed by the optical communications.

In [25], a prediction of the on-chip EIs performance is made, based on the ITRS road map, and target requirements for the alternative OI scheme are derived in terms of propagation delay, power consumption and bandwidth density, defined as data throughput through a unit cross-section of an interconnect. More specifically, the following considerations are presented in [25]:

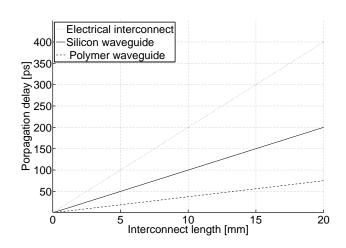

• With the technology scaling down, the minimum achievable electrical interconnect delay is an issue. Predictions were made until the CMOS 22 nm technology node<sup>2</sup>, at which the interconnect delay per unit length remains fixed at approximately 20 ps/mm, limited by the *RLC* impedances characteristic of the EI. The delay can be optimized by using wider wires, but that reduces the bandwidth density. OIs do not have any associated *RLC* delay and offer therefore a very promising solution to this problem. Fig. 1.2 shows a comparison of the signal propagation delay in EIs and two common OIs, based on silicon and polymer waveguides. Unlike the EI *RLC*-associated delay, the signal propagation delay in OIs is only due to the waveguide intrinsic delay, which is not affected by the CMOS technology scaling. However, the implementation of OIs requires an electrical-to-optical (EO) and an optical-to-electrical (OE) signal conversion at the transmitter and receiver side, respectively, increasing the total delay and power consumption. Because of this reason, the longer the interconnect, the more beneficial the choice of the OI over the EI.

<sup>2</sup>Half-pitch between two integrated lines

**Figure 1.2:** Propagation delay of silicon and polymer waveguides as compared to EIs. Both types of optical waveguides have a square cross-section and are assumed to be surrounded by a cladding with an optical refractive index of 1.1 The core of the silicon waveguide is 340 nm wide, with a refractive index of 3.4. The core of the polymer waveguide is 1.36  $\mu$ m wide, with a refractive index of 1.3. *Source: Haurylau et al., JSTQE, 2006.*

- Even considering delay-optimized EIs with optimal repeater stages, the power consumption of chip-length EIs remains in the order of 1 mW/mm and is expected to increase with higher signal switching frequency, as that increases the dynamic power consumption [26]. This sets a target upper limit for the power consumption in OIs (including EO and OE conversions), in order to be competitive with EIs.

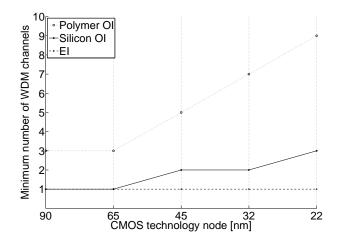

- The bandwidth density that can be reached with EIs can be significantly improved with the use of OIs in WDM on-chip networks. A minimum number of WDM channels is required to exceed the EI bandwidth density. This number of channels is a moving target because the bandwidth density of EIs increases with the technology scaling, as the wire pitch becomes smaller and a higher wire integration density allows for a more powerful parallel communication. Fig. 1.3 shows the number of OI WDM channels required to exceed the EI bandwidth density as a function of the CMOS technology node. For Si photonic OIs, a minimum number of 3 WDM channels is predicted to be necessary to benefit from the OI solution.

Recent studies demonstrate that the delay, power-consumption and density requirements for OIs mentioned above are indeed achievable: in [27], a simulation-based systematic synthesis method for integrated OIs is described. This method was used to extract the performance of mm-long on-chip OIs in terms of interconnect delay, power consumption and integration density in three CMOS technologies, at 65, 45 and 32 nm. In CMOS circuitry, electrical in-

**Figure 1.3:** Number of OI WDM channels required to exceed the EI bandwidth density as a function of the CMOS technology node. *Source: Haurylau et al., JSTQE, 2006.*

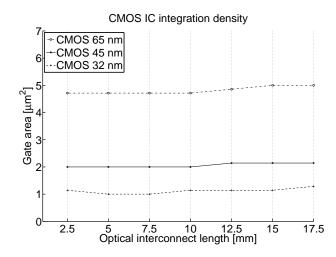

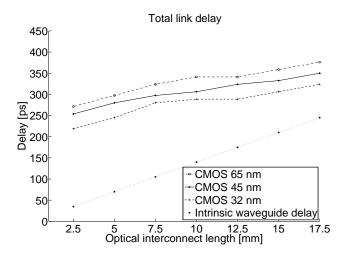

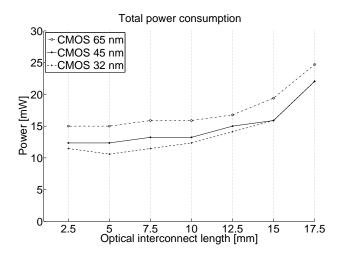

terconnections take a substantial space (CMOS area), at the expense of the device integration density. Therefore, when the interconnections are realized in an optical layer integrated with the CMOS circuitry, the electronic IC density increases. The simulation results in terms of CMOS gate area as a function of the interconnect length are shown in Fig. 1.4. The simulations are made for on-chip OIs, therefore for mm-long interconnects, according to the ITRS projected chip edge length OI of 17.6 mm [4, 25]. As it can be seen in Fig. 1.4, the implementation of OIs in the 65, 45 and 32 nm CMOS circuitry approximately verifies the scaling law for electronic ICs:  $A_{32\,\text{nm}} = A_{45\,\text{nm}} \cdot s = A_{65\,\text{nm}} \cdot s^2$ , where s = 0.7 is the scaling factor between technology nodes. Fig. 1.5 shows the simulation results for the circuit delay when OIs are employed as a function of the interconnect length for the 3 technologies mentioned above. The total circuit delay, which is due to the intrinsic waveguide delay in the OI link and to the delay in the CMOS ICs, decreases with longer interconnects with respect to the intrinsic waveguide delay. This is due to the higher modulation current required in longer OIs to compensate for the higher overall waveguide loss. The higher modulation current drives the source capacitance faster, consuming on the other hand more power. The power analysis results are shown in Fig. 1.6, where the total power is plotted versus the OI length in the three cases of 65, 45 and 32 nm CMOS technology. The total power is the sum of the average static power, which takes into account the power consumed by transmitter, receiver and circuit, and of the dynamic power, which is the power consumed only by the CMOS circuit switching. This analysis shows that the total circuit delay and area and power consumption when on-chip interconnections are implemented in an integrated photonic layer fulfill the requirements set for the future CMOS technology nodes [27].

**Figure 1.4:** Total CMOS gate area ( $\mu$ m<sup>2</sup>) for varying OI length and technologies. The implementation of OIs in the 65, 45 and 32 nm CMOS circuitry approximately verifies the scaling law for electronic ICs:  $A_{32\,\text{nm}} = A_{45\,\text{nm}} \cdot s = A_{65\,\text{nm}} \cdot s^2$ , where s = 0.7 is the scaling factor between technology nodes. *Source: O'Connor et al., Transac. on VLSI Systems, 2006.*

### **1.3.1** Options, challenges and state-of-the-art

The idea of adding a photonic layer on top of the electronic silicon ICs to realize optical interconnections has been investigated by several academic and industrial research groups in the last few years, following the road maps developed for semiconductors [4]. There are several ways to do that, which require different devices and integration schemes, depending on the specific application that needs to be addressed. For example, optical transmitters and receivers in the interconnect layer on top of electronic boards capable of vertically emitting and receiving optical signals are particularly suitable for rack-to-rack interconnections in multirack computer machines and can be used for chip-to-chip on-board interconnections as well. These solutions have been investigated by [28, 29], where Vertical-Cavity Surface-Emitting Laser (VCSEL) sources and substrate illuminated photodetectors fabricated on an interconnect layer on top of an electronic board are employed. A different approach is based on a planar integration scheme, where edge-emitting laser sources and photoreceivers are used. This option is suitable for on-board on-chip and off-chip interconnects and leaves the possibility of integrating more optical devices in the laser-to-detector link path, like modulators, amplifiers, filters, etc. In any case, the main challenges are the integration of the electronic and the photonic components as well as the development of a fabrication process compatible with today's Si IC fabs processing. These two points are essential to consider the optical interconnections in integrated circuits as a real potential alternative to electronics, as they would permit the processing of PIC on a Si wafer scale without requiring substantial changes in current Si IC fabs. The reason why

**Figure 1.5:** Total circuit delay (ps) as a function of OI length for different technologies. The intrinsic delay of a  $SiO_2$  waveguide is plotted as a reference. The total circuit delay decreases with longer interconnects with respect to the intrinsic waveguide delay because of the higher modulation current required in longer OIs to compensate for the higher overall waveguide loss. The higher modulation current drives the source capacitance faster, thus decreasing the delay in the electronic gates. *Source: O'Connor et al., Transac. on VLSI Systems, 2006.*

the integration of electronic and photonic devices is so challenging is basically due to the fact that electronic ICs and PICs utilize different materials: while electronic ICs are based on Si, which is a semiconductor with an indirect energy band gap, optical devices are based on compound semiconductors, like InP or GaAs, which have a direct energy band gap. In direct band gap semiconductors, the electron-hole recombination process between conduction and valence energy bands occurs with a much higher probability. As this recombination is the physical mechanism behind light emission, amplification and detection, indirect energy band gap materials such as Si have an intrinsic substantial limitation in terms of type of functionalities they can provide when working at optical frequencies. In the last years, silicon-on-insulator (SOI) photonic technology has made substantial steps forward and the main passive components have been demonstrated, namely waveguides, splitters, interferometers, wavelength filters, gratings [30]. Recently, active components such as photodetectors and modulators in Si and SiGe have been demonstrated too [31-33], but a Si-based light source remains a missing building block in the current Si-photonics scenario. Materials based on direct bandgap semiconductor compounds, like InP, have excellent optical properties for active photonic operations, namely light emission, modulation and photodetection [34–37]. Therefore, the use of such compounds could compensate for the limitations of the SOI technology. However, that raises a different issue: how to integrate devices made out of different materials on the same wafer. Essentially, the problem is that the lattice constant and the thermal expansion coefficient of these

**Figure 1.6:** Total power (mW) as a function of OI length for different technologies. The total power is the sum of the average static power, which takes into account the power consumed by transmitter, receiver and circuit, and of the dynamic power, which is the power consumed only by the CMOS circuit switching. When OIs are employed, the requirements set for the future CMOS technology nodes in terms of power consumption are fulfilled. *Source: O'Connor et al., Transac. on VLSI Systems, 2006.*

materials are different and that makes it very difficult, and in most cases even impossible, to epitaxially grow optical material layers on a Si substrate. Even when that is possible, the quality of the epitaxially grown layers is poor, due to the high dislocation density caused by the lattice mismatch that affects the material optical properties [38]. Besides these issues related to the epitaxial growth, when III-V compounds such as InP or GaAs are grown on group-IV substrates such as Si a further problem occurs, which has to do with the electronic properties of the materials. The different electron configuration of III-V and group-IV materials leads to a high contact resistance between the epitaxially grown layers, and that compromises the performance of the active photonic devices processed on such layer stack. Moreover, whatever way is used to integrate photonic-based and electronic-based components, an optical device process flow compatible with the fabrication steps of Si electronic circuits has to be developed. Many solutions have been investigated to face these problems: InP nano-wires were successfully grown on a Ge substrate, as demonstrated in [39], and SiGe-based photodetectors and modulators realized by using Ge epitaxial growth lattice-mismatched to Si were recently reported [40-42]. However, the indirect energy band gap of the SiGe compound makes it not suitable for the realization of light emitters and amplifiers. This is, as a matter of fact, the strong argument for introducing direct energy band gap compounds, such as InP. This compound provides excellent light emission, amplification, modulation and detection properties, and therefore has a huge potential as candidate for adding to Si the missing functionalities necessary to the implementation of optical interconnections on Si electronic chips. Due to the

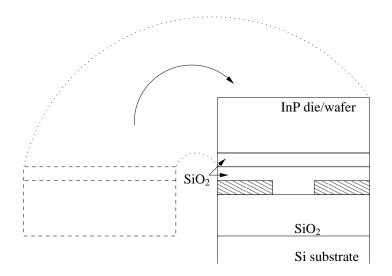

issues mentioned above, related to the growth of III-V compounds on Si, a bonding technology is more suitable for the InP-on-Si heterogeneous integration: the Si and the InP wafers are prepared separately and then bonded together. The bonding approach has the advantage of providing high-index membrane-based devices on a low-index substrate, which is necessary for photonic ultra-compact integrated circuits. Heterogeneous components on a Si/InP platform that make use of the bonding technology were reported by Seassal et al. and Monat et al. [43–45]. Si-based and InP-based devices that exploit the advantages of this technology were more recently reported [46–48]. While several bonding technologies were investigated by [49] to integrate InP-based and Si-based devices, the following main three ones are used:

- Metallic bonding. This technique uses metals for wafer bonding, being the bonding interface Cu-Cu or metal alloys [50, 51]. This has the intrinsic limitation of providing an absorbing bonding layer, which becomes a problem when the optical signal has to be transparently routed between the Si and the bonded InP layer, as a large part of the optical power would be absorbed, and therefore lost, in the metal area used for bonding. On the other hand, this bonding technology is particularly suitable for the hybrid integration of Si and InP chips for which only electrical interconnections are required between the optical and the electronic layers, while the signal processing is done in either one or the other layer. Thanks to that, the bonding alignment does not require a high accuracy (in the order of 10  $\mu$ m) [52].

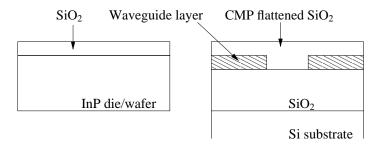

- Direct molecular bonding. With this technique, a layer of silicon dioxide (SiO<sub>2</sub>) is first deposited on the Si and InP wafers. The two wafer silica surfaces are then flattened by Chemical Mechanical Polishing (CMP) and then fused together. This technique provides an optically transparent bonding layer and is therefore suitable for the heterogeneous integration of Si and InP chips but requires advanced CMP processing to control the bonding layer thickness and roughness [45, 53].

- Benzo-Cyclo-Butene (BCB) bonding. This technique uses an optically transparent polymer layer, which is spin coated onto the substrates and used as a bonding agent. The application of this approach is the same as for the direct molecular wafer bonding approach, but it has the advantage that no CMP processing is required and the tolerance towards the wafer surface roughness is relaxed. However, the bonding layer thickness is difficult to control, as well as the thickness uniformity across the wafer [54].

In the next section, the approach used for the realization of the heterogeneous components presented in this thesis is described.

## **1.3.2** Our approach

This thesis describes the realization of InP-based photodetectors suitable for use in optical interconnects on Si and of heterogeneously integrated multiwavelength receivers (MWRs) in InP-on-Si technology. This work has been carried out through the European project PICMOS<sup>3</sup>

<sup>&</sup>lt;sup>3</sup>Photonic Interconnect Layer on CMOS by Wafer-Scale Integration (PICMOS), http://picmos.intec.ugent.be

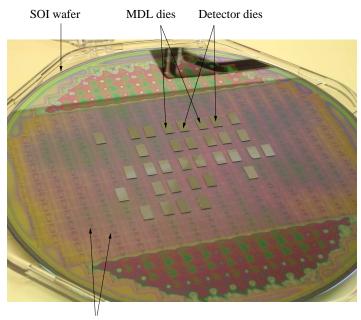

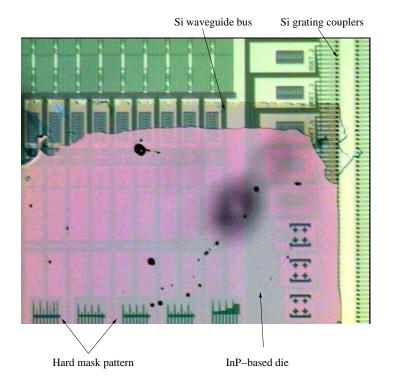

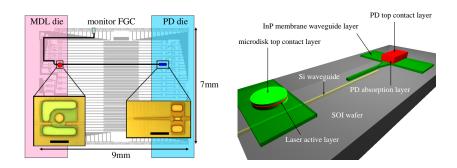

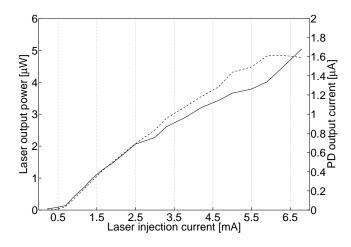

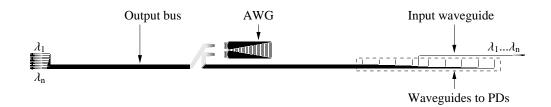

and the Smartmix-MEMPHIS<sup>4</sup> project, funded by Dutch Ministry of Economic Affairs. The detectors developed within the PICMOS project framework are realized by using direct molecular bonding. In the project context, two different InP-based dies containing detector and laser layer stacks are bonded on a Si wafer via direct molecular bonding and then processed. The Si wafer contains an SOI waveguide layer, in which optical waveguides are defined to interconnect the active InP-based devices. This led to the demonstration of the world's first optical link integrated on Si utilizing electrically pumped InP-based microdisk lasers, SOI waveguides and InP-based detectors [55–57]. The MWRs developed within the Smartmix-MEMPHIS project framework are built of InP-based detectors BCB-bonded on an SOI waveguide and demultiplexer structures. These receivers are capable to demultiplex and detect a WDM signal carrying data coded in 10 parallel wavelength channels.

In the next section, a brief overview of this thesis is given.

## **1.4** Thesis overview

This thesis is divided in the following 6 chapters:

- Chapter 1 introduces the work on InP-based detectors presented in this thesis. The bandwidth limitation predicted in the near future for the electrical on-chip and off-chip interconnections in Si electronic ICs is described and provides the motivation for this work. The several options that are being investigated to overcome the interconnection problem are discussed and compared. Finally, the approach used in the project frameworks within which the InP-based detectors described in this thesis were developed is presented.

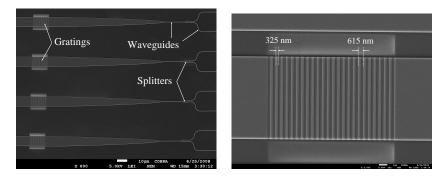

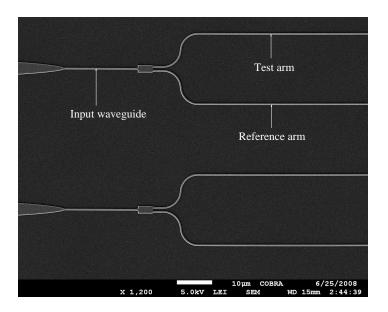

- Chapter 2 discusses the integrated components designed for the realization of the InP based photodetectors developed in this thesis work. The interconnect waveguides defined on the wafer on top of which the detectors are bonded are presented. The detector structure design is described by focusing first on the design of a detector input InP membrane waveguide, used to couple the light of out the interconnect waveguide layer and bring it towards the PD absorption area, and then on the design of the p-i-n diode heterojunction.

- Chapter 3 addresses the technology developed and used for manufacturing the integrated devices presented in this thesis. The type of integration scheme used to heterogeneously integrate the Si-based and the InP-based components on a single chip is first described. The details of the processing of the SOI circuitry and of the bonding technologies used for the integration of the InP active devices are discussed step by step.

- Chapter 4 focuses on the detector developed in InP-on-Si technology. The PD structure is made of a light absorbing layer stacked on top of an InP layer that is also used for the

<sup>&</sup>lt;sup>4</sup>Merging Electronics and Micro & Nano-Photonics in Integrated Systems (MEMPHIS), http://www.smartmixmemphis.nl/

realization of a coupler structure. This coupler is meant to optimize the optical power transfer from the interconnect waveguiding layer to the detector absorption layer, thus improving the device efficiency. In the chapter, the design, fabrication and characterization of a the InP developed coupler structures bonded on a Si wafer are described. After that, detectors bonded on an SOI wafer and on a Si wafer containing CMOS circuitry are described, as well as the integration of lasers and detectors on the same chip for the realization of a point-to-point photonic link on Si.

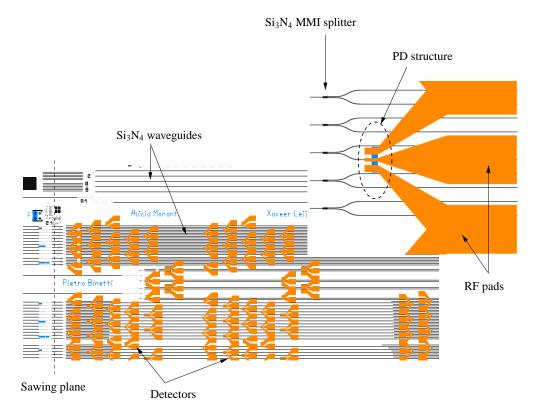

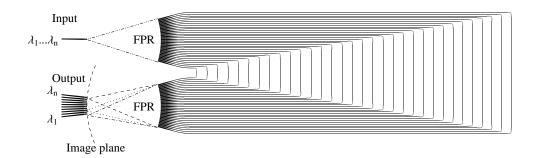

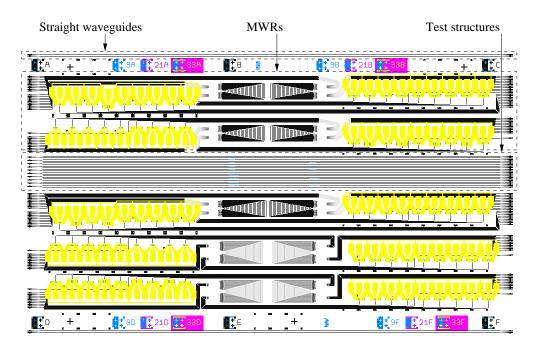

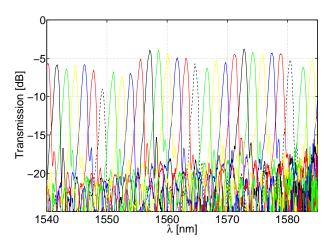

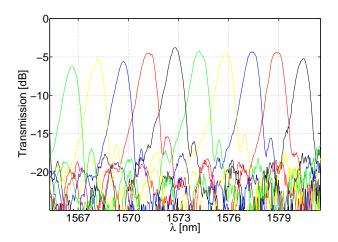

- Chapter 5 is about the multiwavelength receivers heterogeneously integrated in InPon-Si technology. First, the MWR device concept is explained. Then, the attention is focused on the single components the MWR is made of: SOI waveguides, demultiplexer and InP-based detectors. The design of each component and the process flow developed for their heterogeneous integration are discussed. Finally, experimental results are presented and an outlook for the future work is given.

- Chapter 6 summarizes the PhD work carried out to develop the detectors realized in InPon-Si technology described in this thesis. Conclusions are drawn by analyzing the main goals achieved in this research work and the main challenges that are left to be taken up.

## **Chapter 2**

# **Design of integrated components**

This chapter introduces the integrated components designed for the realization of the indium phosphide (InP) based photodetectors (PDs) developed in this thesis work. First, the interconnect waveguides defined on the Si wafer on top of which the detectors are bonded are presented. Then, the detector structure design is described. This description is divided into two parts: the design of the p-i-n diode heterojunction and the design of a detector input InP membrane waveguide, used to couple the light of out the interconnect waveguide layer and bring it towards the PD absorption area.

## 2.1 Introduction

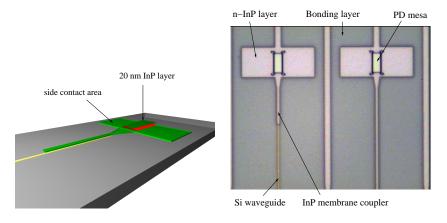

In the previous chapter, the benefits of optical interconnections on Si for the next generation of electronic integrated circuits (ICs) was discussed, as well as the state-of-the-art options to realize heterogeneously integrated opto-electronic chips. Thanks to its excellent properties at optical frequencies, InP is a very promising compound for the fabrication of active photonic devices on a Si optical interconnection layer, and in this thesis an InP-based photodetector (PD) structure suitable for such purpose is presented. As mentioned in Section 1.3.2, this work has been carried out through the European project PICMOS<sup>1</sup> and the Dutch national Smartmix-MEMPHIS<sup>2</sup> project. The detectors developed in this context are based on an InP layer stack grown on an InP wafer. After growth, this wafer is bonded on a Si wafer via direct molecular bonding or Benzo-Cyclo-Butene (BCB) bonding and then the PDs are processed. The Si wafer is either a silicon-on-insulator (SOI) wafer that contains a Si interconnect waveguide layer on a SiO<sub>2</sub> insulator layer, or a complementary metal-oxide semiconductor (CMOS) wafer on top of which waveguides are patterned in a Si<sub>3</sub>N<sub>4</sub> interconnect layer deposited by Plasma Enhanced Chemical Vapor Deposition (PECVD).

15

<sup>&</sup>lt;sup>1</sup>Photonic Interconnect Layer on CMOS by Wafer-Scale Integration (PICMOS), http://picmos.intec.ugent.be <sup>2</sup>Merging Electronics and Micro & Nano-Photonics in Integrated Systems (MEMPHIS), http://www.smartmixmemphis.nl/

Before going into the details of the heterogeneous chip fabrication, which is the focus of the next chapter, the device concept and design are addressed in this chapter.

## 2.2 Interconnect waveguides

The interconnect waveguides are realized in Si or  $Si_3N_4$  on top of a SiO<sub>2</sub> insulator layer on a Si or CMOS substrate, respectively, and are meant to interconnect the active photonic devices processed on top of the bonding layer. The choice of these interconnect waveguide materials leads to different integration schemes, with pros and cons:

- Si waveguides are defined on an SOI substrate, where the insulator layer is SiO<sub>2</sub>. A further bonding step is then required to integrate the SOI structures with the electronic circuitry in the CMOS wafer. Thanks to the high optical refractive index of Si at optical wavelengths (3.48 at 1550 nm [58]), SOI waveguides have a very high optical field confinement, which allows for extremely compact photonic circuitry. For example, bent waveguides with radii of a few microns can be realized without any additional loss with respect to the straight sections [47].

- Si<sub>3</sub>N<sub>4</sub> can be deposited by PECVD on top of an SiO<sub>2</sub> buffer layer flattened by Chemical-Mechanical Polishing (CMP) on a processed CMOS wafer. The Si<sub>3</sub>N<sub>4</sub> waveguides can then be processed on wafer scale by means of standard CMOS-compatible lithography and etching processing steps. SiN<sub>x</sub> has a much lower optical refractive index than Si: 1.8-2.1 at 1550 nm [58], depending on the PECVD deposition process and SiN<sub>x</sub> composition. The Si<sub>3</sub>N<sub>4</sub> waveguides used for this thesis work have an optical refractive index of 1.865 at 1550 nm. Si<sub>3</sub>N<sub>4</sub> waveguides do not allow for the same high wire integration density that can be achieved with Si waveguides, but they do offer an easier integration with the CMOS ICs.

Alternatively, hydrogenated amorphous silicon (a-Si:H) waveguides can be used. This type of waveguides can also be deposited by PECVD on a Si substrate, thus providing a straightforward integration with the CMOS ICs, as compared to the SOI wires. Disadvantages are a lower light confinement in the waveguide core than for the SOI wires, which translates in a lower wire integration density, and higher propagation loss than the  $Si_3N_4$  wires outside the 1550 nm telecom window [59, 60]. However, a-Si:H waveguides were not used in the context of this thesis and therefore we focus on the Si and  $Si_3N_4$  waveguides used for our on-chip optical interconnects.

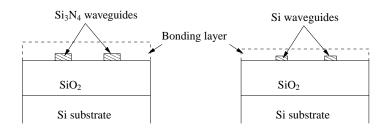

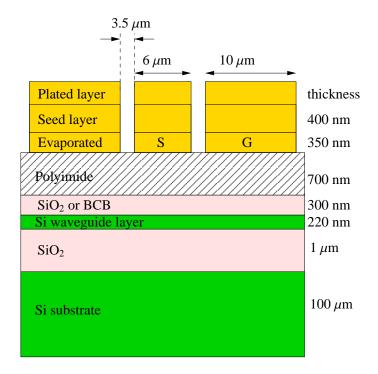

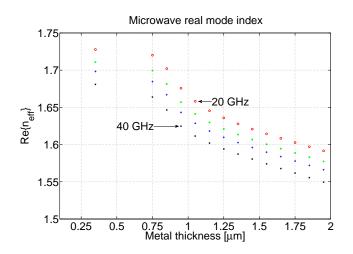

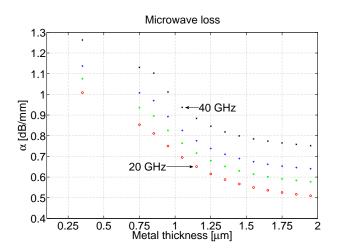

A schematic cross-section of the waveguide geometry is shown in Fig. 2.1. The Si and  $Si_3N_4$  waveguides have dimensions of  $220 \times 500 \text{ nm}^2$  and  $400 \times 800 \text{ nm}^2$ , respectively. The  $SiO_2$  substrate, which is 1-2 µm thick, has a refractive index of 1.45. The top cladding is provided by the bonding layer, for which either  $SiO_2$  or BCB are used. The refractive index of BCB is ~1.54 at 1550 nm and due to the high index contrast with the waveguide core (especially for the Si waveguides), the bonding layer material makes a negligible difference for the optical properties of the interconnect waveguides [61]. Simulations were performed with the Finite Difference (FD) and the Film Mode Matching (FMM) calculation methods implemented

**Figure 2.1:** Cross-section of the interconnect waveguides defined on top of a SiO<sub>2</sub> insulator layer on a Si wafer. The waveguides are realized in Si (right) or Si<sub>3</sub>N<sub>4</sub> (left) with dimensions of  $220 \times 500 \text{ nm}^2$  and  $400 \times 800 \text{ nm}^2$ , respectively. The bonding layer (dashed line), on top of which the InP detector is processed, is also indicated.

in two different full vectorial mode solvers: OlympIOs, by C2V, and FIMMWAVE, by Photon Design, respectively. With this cross-section geometry, simulation results show that the fundamental mode index is about 2.5 and 1.5 for the Si and  $Si_3N_4$  waveguides, respectively. These optical properties have to be taken into account when designing the heterogeneous photonic devices defined on top of the bonding layer. In the next section, the design of the InP-based photodetector is presented.

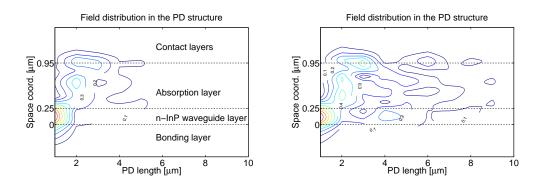

## 2.3 Photodetector structure

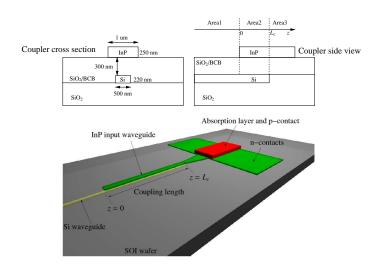

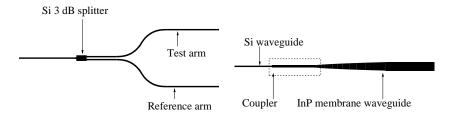

The detector structure consists of two parts: an InP membrane input waveguide on top of the bonding layer, meant to provide a good optical coupling from the photonic interconnect waveguide layer underneath up to the PD, and a p-i-n junction, where the optical signal is absorbed and converted into electrical power. Fig. 2.2 shows a drawing of the PD structure bonded on a Si waveguide. The design of these two detector building blocks is described below.

## 2.3.1 Coupler design

Two different InP coupler structures were investigated, for coupling the optical power out of the Si and the  $Si_3N_4$  interconnect waveguides, respectively.

Before describing the coupler modeling, let us define the symbols and notation that will be used. In general, for an electromagnetic (EM) field propagation in an isotropic medium (in which permittivity and permeability are direction-independent) we can write:

$$\bar{E}(x,y,z,t) = \left[\bar{E}_0(x,y,z) \cdot e^{-j \cdot \left(\beta_x x + \beta_y y + \beta_z z + \phi_1\right)} + \bar{E}_0^*(x,y,z) \cdot e^{+j \cdot \left(\beta_x x + \beta_y y + \beta_z z + \phi_2\right)}\right] \cdot e^{j \cdot 2\pi f t}$$

(2.1)

where  $\beta_x$ ,  $\beta_y$ ,  $\beta_z$  are the field complex propagation constants along the coordinate axis,  $\phi_1$  and

**Figure 2.2:** Photodetector structure. The coupling from the photonic wiring (Si waveguide) layer to the PD takes place by means of an InP membrane input waveguide. The detector is stacked on top of the membrane waveguide layer and the optical power is detected in the absorption layer. A cross section of the coupler is schematically shown.

$\phi_2$  the initial field phase offsets, and

$$\bar{E}_0(x, y, z) = E_x \cdot \hat{x} + E_y \cdot \hat{y} + E_z \cdot \hat{z}$$

(2.2)

where  $E_x$ ,  $E_y$  and  $E_z$  are the complex field components in the  $\hat{x}$ ,  $\hat{y}$ ,  $\hat{z}$  directions. The two terms in Eq. 2.1 correspond to forward and backward propagating modes along the coordinate axis. For our application, we can consider only the forward propagating solutions and set  $\phi_1 = 0$ . For a waveguide, which is a *z*-invariant structure if  $\hat{z}$  identifies the propagation direction, the field solutions do not change in  $\hat{z}$ . In this direction, only the field attenuation and phase rotation occur, due to the propagation. Therefore, the field dependence on  $\hat{z}$  can be factorized and the following expression for  $\bar{E}(x, y, z, t)$  can be written:

$$\bar{E}(x, y, z, t) = \bar{E}_0(x, y) \cdot e^{-j \cdot \beta_z z} \cdot e^{j \cdot 2\pi f t}$$

(2.3)

where  $\beta_z = \beta - j\alpha$ , being  $\beta$  the real propagation constant in the  $\hat{z}$  direction and  $\alpha$  the field attenuation coefficient. From this point, the field time dependence is omitted, for clarity, and the media are supposed to be lossless and, as a consequence, the modes real. Furthermore, we consider modes that satisfy the field power normalization condition:

$$\|\bar{E}(x,y,z,t)\|^{2} = \int_{-\infty}^{+\infty} \bar{E}_{0}(x,y) \cdot \bar{E}_{0}^{*}(x,y) \cdot dxdy = 1$$

(2.4)

and we define the overlap between two fields  $\bar{E}_1$  and  $\bar{E}_2$  that satisfy Eq. 2.3 and Eq. 2.4 as

$$a = \frac{\int_{-\infty}^{+\infty} \bar{E}_1 \cdot \bar{E}_2 \cdot dxdy}{\sqrt{\int_{-\infty}^{+\infty} \bar{E}_1 \cdot \bar{E}_1^* \cdot dxdy \cdot \int_{-\infty}^{+\infty} \bar{E}_2 \cdot \bar{E}_2^* \cdot dxdy}} = \int_{-\infty}^{+\infty} \bar{E}_1 \cdot \bar{E}_2 \cdot dxdy$$

(2.5)

The Si-to-InP coupler was studied by performing a 3D modal analysis, based on the system modes approach [62]. This is explained in the following, with reference to the annotation used in Fig. 2.2. First, the mode indices of the fundamental mode propagating in the Si and InP single-mode waveguides (Area1 and Area3) and of the even and odd system modes excited in the coupling structure (Area2) are calculated. Let us call them  $\bar{E}_{Si}$ ,  $\bar{E}_{InP}$ ,  $\bar{E}_{even}$  and  $\bar{E}_{odd}$ , respectively. The fields propagating in the coupler's Si and InP waveguides are:

$$\bar{E}_{\mathrm{Si}}(x, y, z) = \bar{E}_{\mathrm{0}_{\mathrm{Si}}}(x, y) \cdot e^{-j \cdot \beta_{\mathrm{Si}} \cdot z}$$

$$(2.6)$$

$$\bar{E}_{\text{InP}}(x, y, z) = \bar{E}_{0_{\text{InP}}}(x, y) \cdot e^{-j \cdot \beta_{\text{InP}} \cdot z}$$

(2.7)

where  $\beta_{Si}$  and  $\beta_{InP}$  are the field propagation constants in the propagation direction  $\hat{z}$  and  $\bar{E}_{Si}$ and  $\bar{E}_{InP}$  satisfy Eq. 2.4. Then, the excitation coefficients  $a_{even}$  and  $a_{odd}$  are calculated by overlapping the Si waveguide fundamental mode and the even and odd system modes. As most of the power is carried by the two supermodes  $\bar{E}_{even}$  and  $\bar{E}_{odd}$ ,  $\bar{E}_{Si}$  can be expressed with the superposition of  $\bar{E}_{even}$  and  $\bar{E}_{odd}$ :

$$\bar{E}_{\rm Si} = a_{\rm even} \cdot \bar{E}_{\rm even} + a_{\rm odd} \cdot \bar{E}_{\rm odd} \tag{2.8}$$

As  $\bar{E}_{even}$  and  $\bar{E}_{odd}$  satisfy Eq. 2.4, the excitation coefficients are calculated using Eq. 2.5:

$$\begin{array}{lll} a_{\rm even} &=& \int_{-\infty}^{+\infty} \bar{E}_{\rm Si} \cdot \bar{E}_{\rm even} \cdot dx dy \\ a_{\rm odd} &=& \int_{-\infty}^{+\infty} \bar{E}_{\rm Si} \cdot \bar{E}_{\rm odd} \cdot dx dy \end{array}$$

(2.9)

The guided system modes propagate along the coupling region with different propagation constants  $\beta_{\text{even}}$  and  $\beta_{\text{odd}}$ . After propagating a distance z from the start of the coupler, the field can be written as:

$$\bar{E}_{c} = a_{\text{even}} \cdot \bar{E}_{0_{\text{even}}} \cdot e^{-j \cdot \beta_{\text{even}} \cdot z} + a_{\text{odd}} \cdot \bar{E}_{0_{\text{odd}}} \cdot e^{-j \cdot \beta_{\text{odd}} \cdot z}$$

(2.10)

Eq. 2.10 represents the field propagating through the coupler structure (with a length of  $L_c$ ). At the interface with the p-i-n junction (interface Area2/Area3), Eq. 2.10 can be written as follows:

$$\bar{E}_{\rm c}(z=L_{\rm c}) = e^{-j\cdot\beta_{\rm even}\cdot L_{\rm c}} \cdot \left(a_{\rm even}\cdot\bar{E}_{0_{\rm even}} + a_{\rm odd}\cdot\bar{E}_{0_{\rm odd}}\cdot e^{-j\cdot\Delta\beta\cdot L_{\rm c}}\right)$$

(2.11)

After a distance  $z = L_c = \frac{\pi}{\Delta\beta}$ , defined as coupling length, the maximum transfer of optical power occurs from the Si to the InP waveguide. The difference  $\Delta\beta = \beta_{even} - \beta_{odd}$  is responsible for the system dynamics: by varying the waveguide geometry, system modes with different propagation constants are guided and the coupling length changes accordingly. The excitation

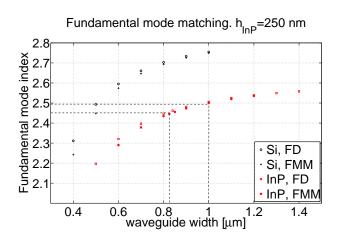

**Figure 2.3:** Si and InP waveguide fundamental mode index as a function of the waveguide width calculated with the FD and the FMM methods. For the Si waveguide, the thickness is fixed to 220 nm, while the width is varied. The 500 nm wide Si wires used for this work have a mode index of 2.45-2.5. Fixing the InP waveguide thickness to 250 nm, the predicted optimum width is 0.85  $\mu$ m (1  $\mu$ m), calculated with the FMM (FD) method, which is the width at which the mode index matches the index of the Si waveguide fundamental mode, as indicated by the dashed lines.

coefficient  $\gamma$  for the InP waveguide at the interface Area2/Area3 is then calculated by overlapping the fundamental mode guided by the InP waveguide with the field at the section  $z = L_c$  (see Fig. 2.2):

$$\gamma = \int_{-\infty}^{+\infty} \bar{E}_{\rm c}^*(z = L_{\rm c}) \cdot \bar{E}_{\rm InP} \cdot dx dy$$

(2.12)

As a last step, the power coupling efficiency

$$\eta_{\rm c} = \|\boldsymbol{\gamma}\|^2 \tag{2.13}$$

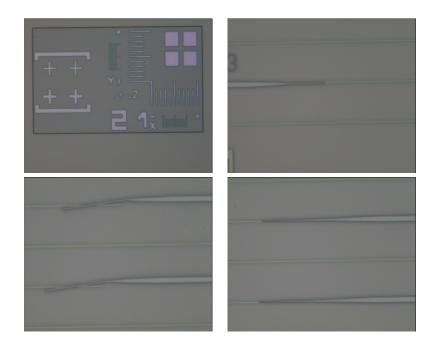

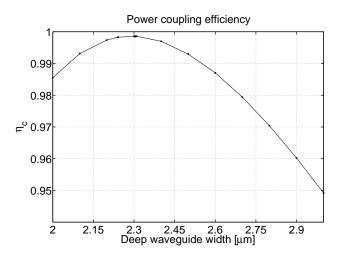

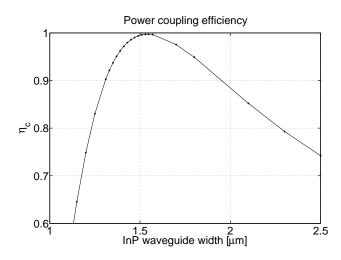

is calculated. The 2D mode index calculations were done with the FD and the FMM methods, while the field propagation calculations were done with FIMMPROP and through Eq. 2.6-2.13 implemented in Matlab, by MathWorks. Fig 2.3 shows the mode indices for the uncoupled waveguides calculated with the two mode solvers. By properly choosing the InP waveguide dimensions, mode matching can be achieved with the Si waveguide, which is 500 nm wide and 220 nm thick. This is shown in Fig. 2.5, where each point is the result of 2D simulations performed by changing the InP waveguide width along with different thicknesses in order to maximize each time the coupling efficiency. When choosing an InP waveguide thinner than 200 nm, the efficiency quickly drops, while choosing a larger thickness would lead to a narrower waveguide, which is more difficult to manufacture. The InP waveguide thickness was therefore fixed to 250 nm, which leads to a predicted optimum waveguide width of 0.85  $\mu$ m

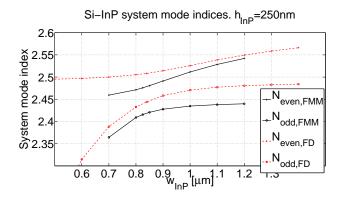

**Figure 2.4:** Si-InP coupler even and odd fundamental mode indices as a function of the InP waveguide width. The Si waveguide's dimensions are  $220 \times 500 \text{ nm}^2$ , while the InP waveguide thickness is fixed to 250 nm. When  $w_{\text{InP}}$  decreases, the even system mode propagates mainly in the Si waveguide and its index approaches the one of the Si waveguide "alone" (as if no InP waveguide was present). In the same time, the odd system mode approaches cut-off. When  $w_{\text{InP}}$  increases, the even system mode propagates mainly in the InP waveguide and the optical field is less confined in the Si waveguide.

**Figure 2.5:** Left: Power coupling efficiency as a function of the InP waveguide thickness. In this plot, each point is the result of 2D simulations performed by changing the InP waveguide width along with different thicknesses in order to maximize each time the coupling efficiency.

#### 2. Design of integrated components

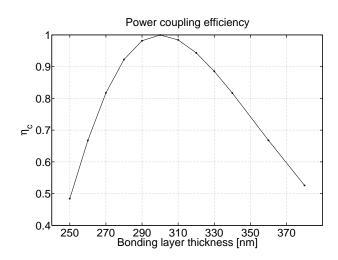

**Figure 2.6:** Power coupling efficiency as a function of the bonding layer thickness. A coupling efficiency of more than 80% is achieved with a tolerance of  $\pm 30$  nm for the bonding layer thickness.

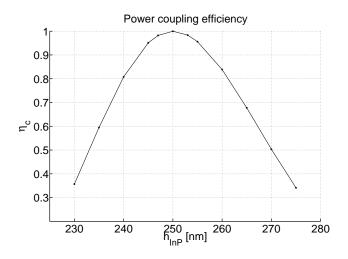

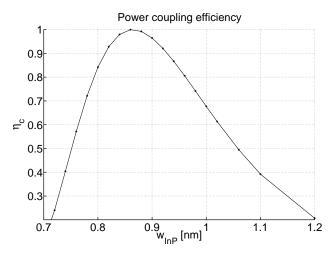

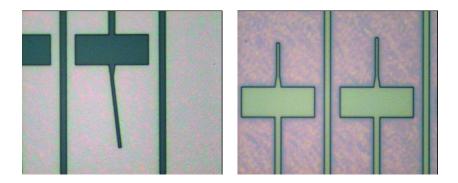

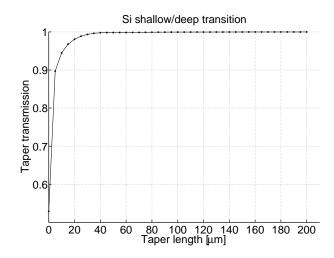

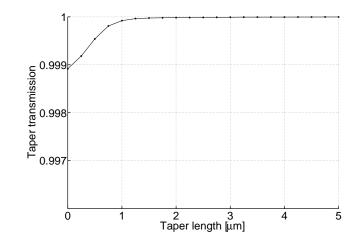

$(1 \mu m)$ , calculated with the FMM (FD) method. The coupler fundamental even and odd system modes were then calculated for an InP waveguide thickness of 250 nm. Fig. 2.4 shows the simulation results obtained with the two calculation methods: the strongest coupling occurs at the InP waveguide width at which the even and of the odd system mode indices are closer. In fact, what happens is explained as follows: when  $w_{InP}$  decreases, the even system mode propagates mainly in the Si waveguide and its index - and therefore its propagation constant approaches the one of the Si waveguide "alone" (as if no InP waveguide was present). In the same time, the odd system mode approaches cut-off. When wInP increases, the even system mode propagates mainly in the InP waveguide and the optical field is less confined in the Si waveguide, which translates in a weaker coupling between the waveguides. The optimum coupler width, at which the even and the odd system mode indices are closer, is around 0.85  $\mu$ m  $(1 \ \mu m)$  when the FMM (FD) calculation method is used, as can be read from Fig. 2.4. According to the simulations, the predicted coupling length varies between 12 and  $14 \,\mu m$ , depending on the calculation method used, and a coupling efficiency of more than 80% is achieved with a tolerance of  $\pm 30$  nm for the bonding layer thickness (see Fig. 2.6) and a deviation from the optimum simulated geometry of  $\pm 10$  nm and  $\pm 70$  nm for the InP waveguide thickness and width, respectively. The simulation results on the power coupling efficiency tolerance towards the waveguide cross-section geometry can be seen in Fig. 2.7 and Fig. 2.8. The tolerances mentioned above for the waveguide cross-section layout are achievable with the current technology limitations. The PD structure shown in Fig. 2.2 allows for the fabrication of laterally tapered membrane waveguides without additional processing steps, which provides an increase of the waveguide alignment tolerance. The finite difference time domain (FDTD) calculation method

**Figure 2.7:** Power coupling efficiency as a function of the InP waveguide thickness. A coupling efficiency of more than 80% is achieved with a tolerance of  $\pm 10$  nm for the InP waveguide thickness.

**Figure 2.8:** Power coupling efficiency as a function of the InP waveguide width. The thickness of the membrane waveguide is 250 nm. In this configuration, a coupling efficiency of more than 80% is achieved with a tolerance for the InP waveguide width of  $\pm 70$  nm.

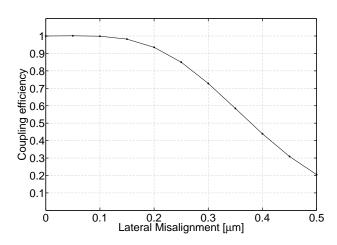

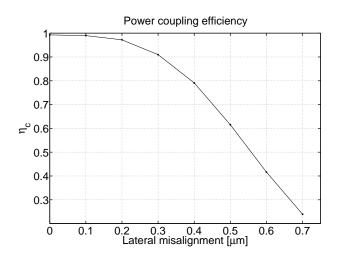

Figure 2.9: Tolerance of the Si-to-InP coupler efficiency as a function of the waveguide-to-waveguide lateral misalignment. The coupling efficiency drops to 50% for a lateral shift of  $\pm 370$  nm.

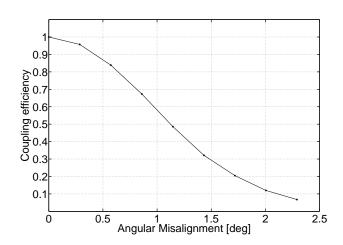

implemented in Fullwave, by Rsoft, was used to investigate the Si-to-InP coupler fabrication tolerance with respect to lateral and angular waveguide-to-waveguide misalignment as shown in Fig. 2.9 and Fig. 2.10, respectively. The coupling efficiency drops to 50% (3 dB drop) for a lateral shift of  $\pm 370$  nm or an angular misalignment of  $\pm 1.1^{\circ}$ , which is within the limitations of our fabrication technology.

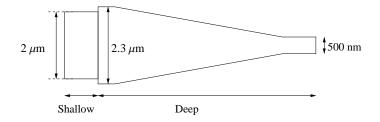

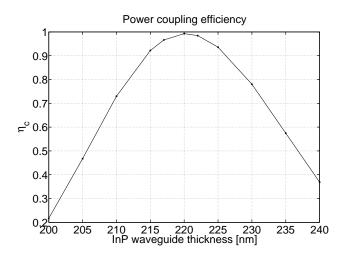

For the coupling between the InP and the Si<sub>3</sub>N<sub>4</sub> waveguide, simulation show that the strongest coupling occurs for an InP waveguide width of 340 nm. This raises a fabrication issue: due to this small feature size, it is not possible to define that waveguide structure by means of the 405 nm Ultra-Violet (UV) optical lithography available in the clean room of the COBRA<sup>3</sup> research institute. This issue can be overcome by the use of electron-beam lithography (EBL), but that requires a definitely more complicated and time consuming processing [63, 64]. The reason why the optimum InP waveguide width is so small is due to the high optical refractive index contrast between the two waveguide materials. An option is to taper out the  $Si_3N_4$  waveguide to  $2\,\mu m$ . This does not solve the lithography issue, as simulations show that the optimum InP waveguide width in this case is 360 nm, but it does relax the fabrication tolerances in terms of waveguide-to-waveguide angular and lateral misalignment. According to 3D BPM simulation results, fabrication tolerances at 3 dB of  $\pm 6.8^{\circ}$  and  $\pm 800$  nm for the InP waveguide angular and lateral misalignment, respectively, were calculated. Comparing these results with the simulations for the Si-to-InP coupler, it can be observed that the fabrication tolerances towards angular and lateral waveguide-to-waveguide misalignment are relaxed. However, the Si-to-InP coupling structure is definitely easier to manufacture, thanks

<sup>&</sup>lt;sup>3</sup>COBRA: COmmunication technology; Basic Research and Applications

**Figure 2.10:** Tolerance of the Si-to-InP coupler efficiency as a function of the waveguide-to-waveguide angular misalignment. The coupling efficiency drops to 50% for an angular misalignment of  $\pm 1.1^{\circ}$ .

|   | Material | Thickness | Doping/Function         |

|---|----------|-----------|-------------------------|

|   | p–InGaAs | 50 nm     | 1.6E19 p-contact layer  |

| • | InGaAs   | 700 nm    | n.i.d. absorption layer |

|   | n–InP    | 200 nm    | 1E18 n–contact layer    |

| • | n–InP    | 50 nm     | n.i.d.                  |

Figure 2.11: Layer stack used for the fabrication of the photodetectors bonded on Si waveguides, shown upside down as bonded on the Si wafer.

to the lower contrast between the InP and the Si optical refractive indices. For this reason, the InP membrane input waveguide is implemented only in the mask set for the realization of the detectors bonded on Si photonic waveguides. As explained further in the thesis, a different approach is used for the PDs bonded on CMOS wafer, with  $Si_3N_4$  waveguides patterned on top of the electronic circuitry.

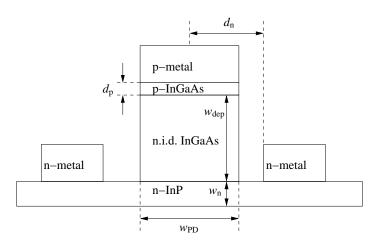

### 2.3.2 Photodiode heterojunction

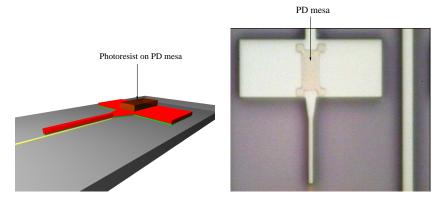

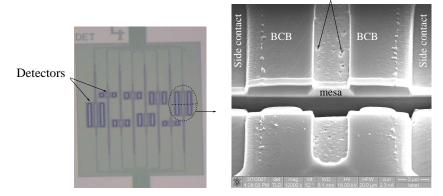

The layer stack used for the fabrication of the photodetectors bonded on Si waveguides is shown upside down, as bonded on the Si wafer, in Fig. 2.11. It is built as a 700 nm n.i.d. InGaAs absorption layer sandwiched by a highly p-doped 50 nm thick InGaAs contact layer and a highly n-doped 250 nm thick InP layer, which is also used for realizing the membrane

waveguide. The photodetectors bonded on Si<sub>3</sub>N<sub>4</sub> waveguides make use of a very similar layer stack, the only difference being the InP membrane waveguide layer, which is 200 nm thick. The PD mesa footprint is  $5 \times 10 \,\mu\text{m}^2$  and the total thickness of the device is 1  $\mu\text{m}$ . The choice of this geometry was driven by the need of reaching a good trade-off between the ease of integration with the micro-disk lasers integrated in the same chip for the PICMOS project, as explained further in the thesis, and detector performance, in terms of efficiency and speed [56, 65]. Following, considerations and calculations on the detector speed and efficiency are presented.

#### **Device speed**

In a p-i-n photodetector, the speed is generally limited by:

- *RC*-time: characteristic time constant of the photodiode, associated to its electrical *RC* circuit.

- Carrier drift transit time: time needed by the photogenerated carriers to travel across the diode depletion region.

- Carrier diffusion time: time needed by the carriers generated outside the depletion region to diffuse to that region. The diffusion process is slow compared to the carrier drift in the high electrical field region. However, the diffusion time can be neglected for the PD presented in this thesis, as most of the carriers are generated in the depletion region and the doped regions are small compared to the absorption area.

Let us first consider the *RC*-time characteristic. With reference to the detector geometry shown in Fig. 2.12, an equivalent electrical *RC*-circuit can be associated to the structure, being *C* the capacitance across the p-i-n junction and *R* the resistance between the p-metal and the n-metal contacts. The capacitance at the heterojunction is

$$C_{\rm j} = \frac{\varepsilon_0 \cdot \varepsilon_{\rm r} \cdot A}{w_{\rm dep}} = 9\,\rm fF$$

where  $\varepsilon_r$  and  $w_{dep}$  are the permittivity and the thickness of the depletion layer and A is the mesa surface. The series resistance  $R_s$  is given by the sum of a number of factors: the contributions of the resistances at the metal-semiconductor interface, for the p-side and the n-side, are

$$R_{\rm p_{metal}} = \frac{\rho_{\rm c,\,p}}{A_{\rm p}} \tag{2.14}$$

and

$$R_{\rm n_{metal}} = \frac{\rho_{\rm c,\,n}}{A_{\rm n}} \tag{2.15}$$

where  $\rho_{c,p}$  and  $\rho_{c,n}$  are the specific contact resistance of the p-metal-semiconductor and nmetal-semiconductor interface, respectively, while  $A_p$  and  $A_n$  are the p-metallization and nmetallization surface, respectively. The  $R_s$  contributions across the heterojunction for the pside and the n-side are

$$R_{\rm Pjunction} = \frac{d_{\rm p}}{q \cdot \mu_{\rm h} \cdot N_{\rm dp} \cdot w_{\rm n} \cdot L_{\rm PD}}$$

(2.16)

Figure 2.12: Schematic diagram of the photodetector.

| Description                                                        | Symbol         | Value                                        |

|--------------------------------------------------------------------|----------------|----------------------------------------------|

| mobility of the electrons                                          | $\mu_{\rm n}$  | $10500 \frac{\mathrm{cm}^2}{\mathrm{Vs}}$    |

| mobility of the holes                                              | $\mu_{ m h}$   | $420 \frac{\mathrm{cm}^2}{\mathrm{Vs}}$      |

| specific contact resistance of the n-metal-semiconductor interface | $ ho_{ m c,n}$ | $10^{-6} \frac{\Omega}{\mathrm{cm}^2}$       |

| specific contact resistance of the p-metal-semiconductor interface | $ ho_{ m c,p}$ | $10^{-4} \frac{\Omega}{\mathrm{cm}^2}$       |

| hole saturation velocity                                           | v <sub>h</sub> | $4.8 \cdot 10^6 \frac{\text{cm}}{\text{s}}$  |

| electron saturation velocity                                       | ve             | $6.5 \cdot 10^6  \frac{\text{cm}}{\text{s}}$ |

**Table 2.1:** Electronic parameters of InGaAs, used as absorption layer in the fabrication of the PD.

and

$$R_{n_{junction}} = \frac{1}{2} \cdot \frac{d_n}{q \cdot \mu_n \cdot N_{dn} \cdot w_n \cdot L_{PD}}$$

(2.17)

where  $d_n$  ( $d_p$ ) is the distance from the middle of the detector to the n-contact (p-contact),  $w_n$  ( $w_p$ ) the thickness of the n-doped (p-doped) layer,  $L_{PD}$  the length of the detector, q the electron charge, and  $\mu_n$  ( $\mu_h$ ) the mobility of the electrons (holes). In Eq. 2.17, the factor  $\frac{1}{2}$  is due to the use of two n-side contacts. The total series resistance is

$$R_{\rm s} = R_{\rm p_{metal}} + R_{\rm n_{metal}} + R_{\rm p_{junction}} + R_{\rm n_{junction}}$$

Using values reported in Table 2.1, the following values are calculated [66, 67]

Figure 2.13: Schematic diagram of a reversely biased p-i-n junction.

$$\begin{array}{rcl} R_{\rm p_{metal}} &=& 2\,\Omega\\ R_{\rm n_{metal}} &=& 100\,\Omega\\ R_{\rm p_{junction}} &=& 1\,{\rm m}\Omega\\ R_{\rm n_{junction}} &=& 5\,\Omega \end{array}$$

The RC-time limited frequency 3-dB cut-off point is defined as

$$f_{\rm RC} = \frac{1}{2\pi C_{\rm j} \left( R_{\rm s} + R_{\rm load} \right)} \tag{2.18}$$

Considering a load resistance of 50  $\Omega$ , substitution of the values brings to  $f_{\rm RC} = 110 \,{\rm GHz}$ .

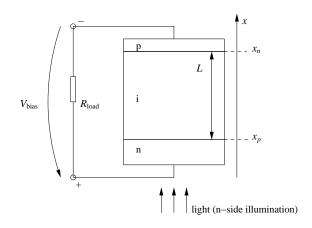

Let us now consider the transit-time limitation. This is analyzed by solving the carrier rate equations for holes and electrons transported in the depletion region of the p-i-n junction and writing the corresponding current density in terms of frequency response. These calculations were outlined by Lucovsky et al. [68] and were used to predict the transit-time limited 3 dB cut-off point of the photodetector frequency response. The following cases were considered for a p-i-n photodiode as schematically sketched in Fig. 2.13:

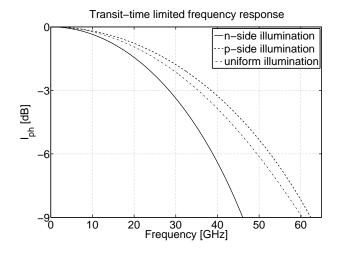

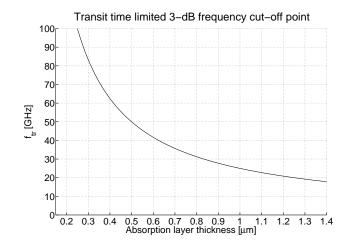

- **Uniform illumination** In this case, for ease of calculation, it is assumed that the photocarriers are uniformly generated in the diode intrinsic region. The frequency response is plotted in Fig. 2.14 (curve labeled "uniform illumination"), for an absorption layer thickness of 700 nm, while in Fig. 2.15 the 3-dB cut-off point as a function of the absorption layer thickness is plotted. An absorption layer thickness of 700 nm brings to a predicted 3-dB bandwidth of about 35 GHz.

- **Exponential absorption** This case corresponds to a more realistic view, in which the light absorption in the depletion region decays exponentially along *x*. The two cases of illumination from the n-side and from the p-side of the p-i-n junction were analyzed. When

**Figure 2.14:** Transit time limited frequency response of the p-i-n photodiode calculated as a function of the type of device illumination. The calculations were made for an absorption layer thickness of 700 nm. These curves were generated by using Eq. 37, Eq. 52 and Eq. 56 of Lucovsky et al. [68].

**Figure 2.15:** Transit time limited frequency 3-dB cut-off point calculated as a function of the detector absorption layer thickness and under the hypothesis that the absorption layer is uniformly illuminated.

the electron-hole pairs are generated near the n-side, it is the holes that must travel across the depletion region (with velocity  $v_h$ ) to reach the p-side. Vice versa, when the photocarriers are generated near the p-side, it is the electrons that must travel across the depletion region (with velocity  $v_e$ ) to reach the n-side. The frequency response for these two cases is plotted in Fig. 2.14.

When reading Fig. 2.14, it clearly appears that a p-side illuminated photodiode is faster as compared to the n-side case. The reason is that electrons and holes have different velocities ( $v_e$  and  $v_h$ , respectively) in the material; in particular,  $v_e > v_h$ , as can be read in Table 2.1. That means the time the electrons take to travel to the n-side in a p-side illuminated PD is less then the time the holes take to travel to the p-side in the case of n-side illumination. For the device reported here, the optical signal carried by the photonic wire underneath the bonding layer is first coupled into the n-InP layer through the membrane coupler and then brought towards the absorption region of the detector, as shown in Fig. 2.2. This type of illumination can be considered close to the case of n-side illumination discussed above, according to which a 3-dB cut-off point  $f_{tr} = 30$  GHz is expected for the transit-time limited frequency response, as it can be read from Fig. 2.14.

The photodetector 3-dB bandwidth is expressed by

$$\frac{1}{f_{3\rm dB}^2} = \tau_{\rm RC}^2 + \tau_{\rm tr}^2, \tag{2.19}$$

where  $\tau_{\rm RC}$  and  $\tau_{\rm tr}$  are the *RC*-time and transit-time constants defined as  $\tau_{\rm RC} = f_{\rm RC}^{-1}$  and  $\tau_{\rm tr} = f_{\rm tr}^{-1}$ , respectively. For the predicted values of  $f_{\rm RC} = 110$  GHz and  $f_{\rm tr} = 30$  GHz, substitution of the values in Eq. 2.19 leads to  $f_{\rm 3dB} = 30$  GHz. Eq. 2.19 shows that, with the chosen device geometry, the most limiting factor for the detector speed is the carrier transit time in the diode depletion region.

#### **Device efficiency**

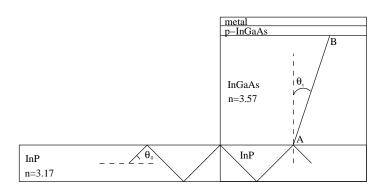

Concerning the internal quantum efficiency, first calculations were performed by applying a ray-tracing model, as schematically shown in Fig. 2.16. Assuming that 100% of the optical signal carried by the photonic wire underneath the bonding layer couples into the n-InP membrane layer, the propagation angle  $\theta_0$  of the fundamental mode guided by the InP membrane waveguide can be obtained by solving the following equation:

$$N_{0,\text{InP}} = \frac{\beta_{0,\text{InP}}}{k_0} = n_{\text{InP}} \cdot \cos(\theta_0)$$

(2.20)

where  $k_0$  is the wave vector and  $N_{0,\text{InP}} \simeq 2.5$  is the fundamental mode index, which was obtained with 2D mode simulations, as described in Section 2.3.1. The solution of Eq. 2.20 in  $\theta_0$ leads  $\theta_0 \simeq 38^\circ$ , for transverse electrical (TE) polarization. At the interface with the absorption region, a TE polarized optical signal is transmitted through the InGaAs absorption region with  $\theta_t \simeq 33^\circ$ , according to Snell's law [69]. The absorption layer was designed 700 nm thick, as shown in Fig. 2.11, which leads to an effective light path length of AB = 833 nm

**Figure 2.16:** Schematic drawing of the detector structure. A ray-tracing model was used to perform the first approximate calculations to investigate the device efficiency.

(see Fig. 2.16). Knowing the InGaAs material absorption constant at  $\lambda = 1550$  nm to be  $\alpha = 0.7 \,\mu\text{m}^{-1}$  [58, 70], the power absorbed in that light path AB can be calculated. If the optical field propagates with an attenuation of  $e^{-\alpha \cdot AB}$ , then the power absorbed in the detector InGaAs absorption layer is

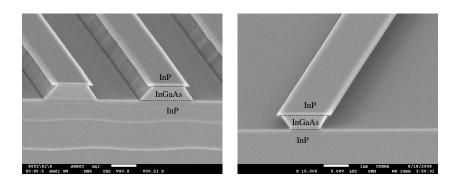

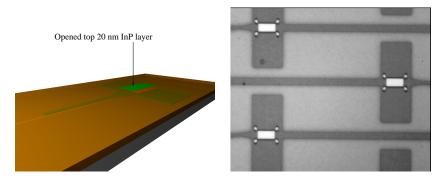

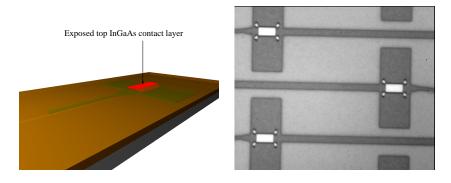

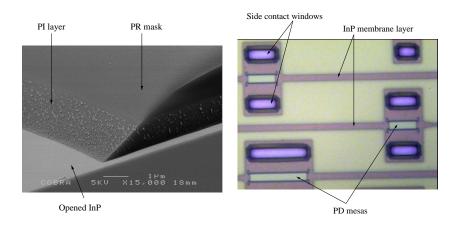

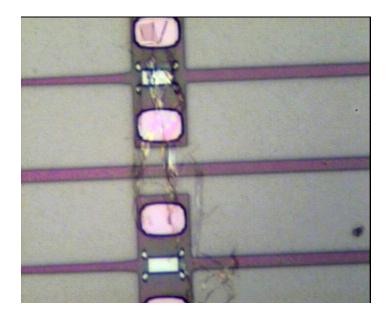

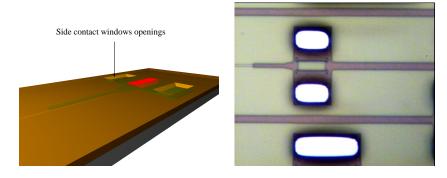

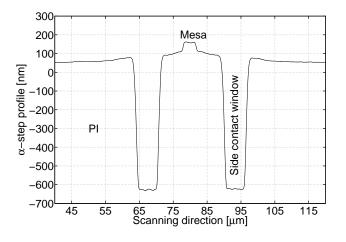

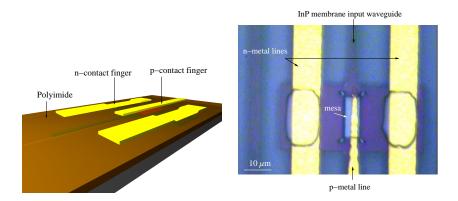

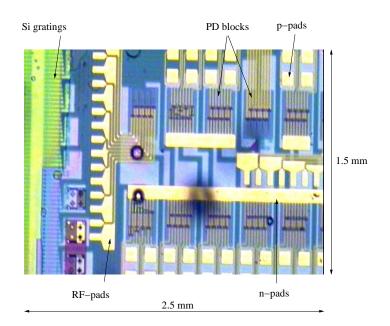

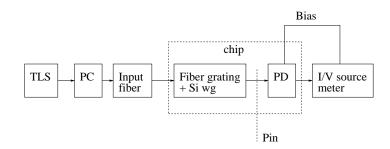

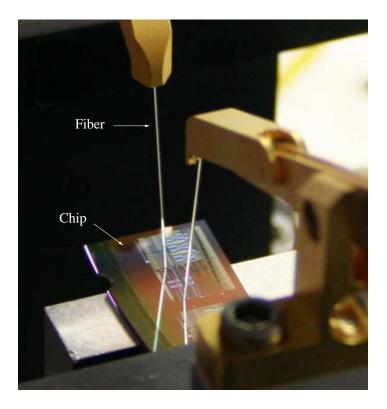

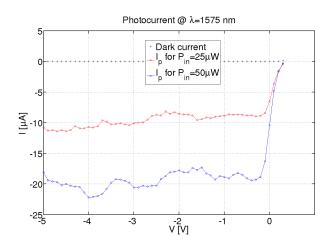

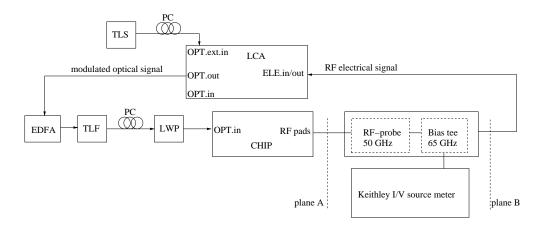

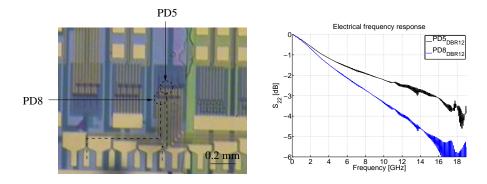

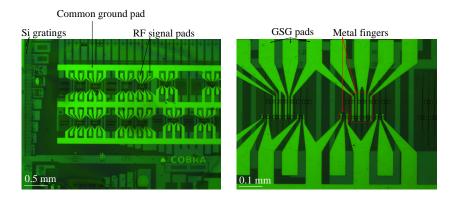

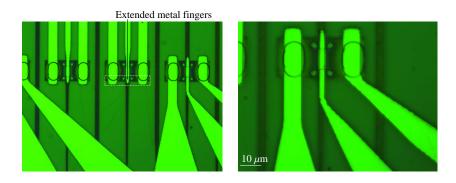

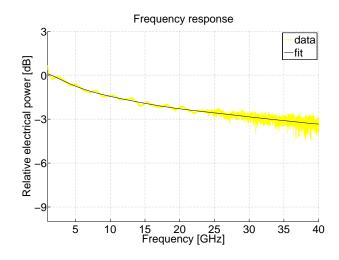

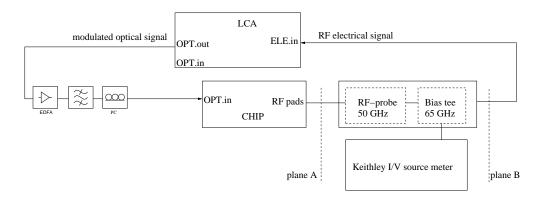

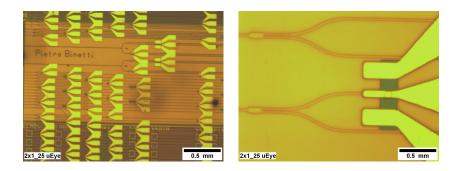

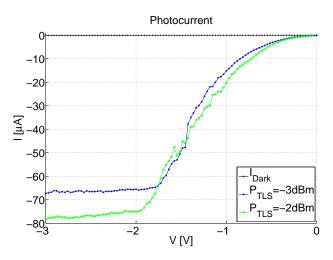

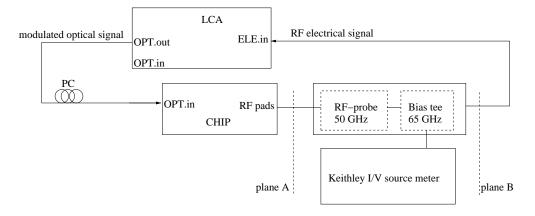

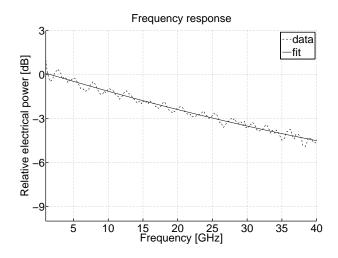

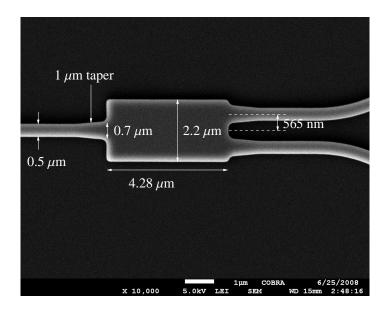

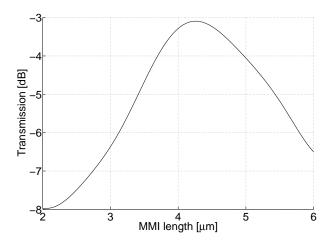

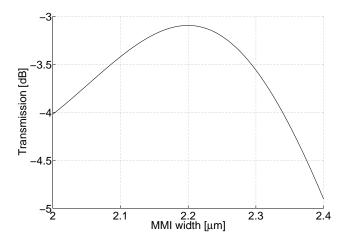

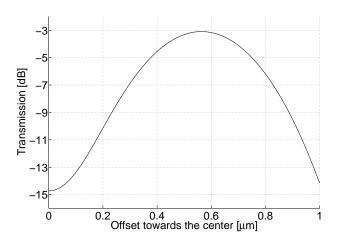

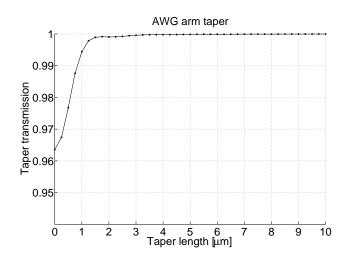

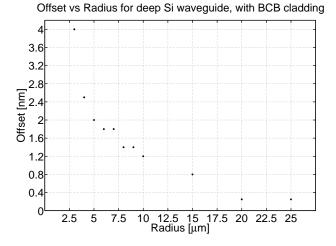

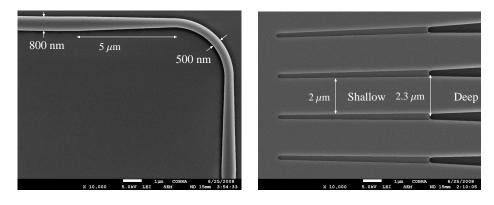

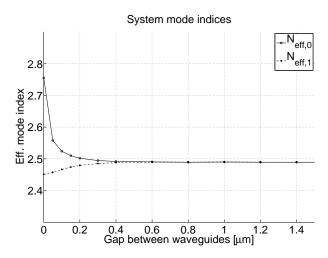

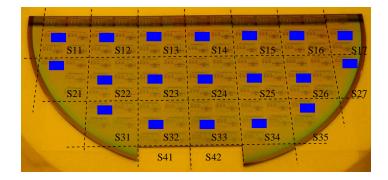

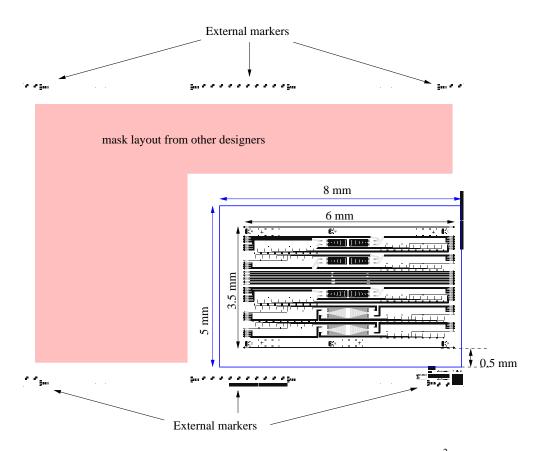

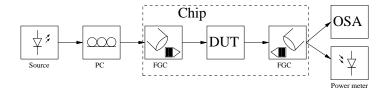

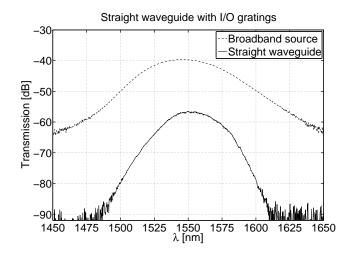

$$P_{abs} = 1 - e^{-2 \cdot \alpha \cdot AB} \simeq 70\% \tag{2.21}$$