### Multi-resource management in embedded real-time systems

Citation for published version (APA):

Holenderski, M. J. (2012). Multi-resource management in embedded real-time systems. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Mathematics and Computer Science]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR735556

DOI:

10.6100/IR735556

Document status and date:

Published: 01/01/2012

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 04. Oct. 2023

# Multi-Resource Management in Embedded Real-Time Systems

### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus, prof.dr.ir. C.J. van Duijn, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op woensdag 17 oktober 2012 om 16.00 uur

door

Michał Jakub Holenderski

geboren te Warschau, Polen

Printed by: Eindhoven University Press, Eindhoven, The Netherlands

© Michał Holenderski 2012

All rights are reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

A catalogue record is available from the Eindhoven University of Technology Library

ISBN: 978-90-386-3237-7

# Contents

| 1 | 1.1 Problem statement                                                                                                                                                                                                           | 1<br>3<br>4                                |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 2 | 2.1 Resource model                                                                                                                                                                                                              | 5<br>7<br>1                                |

| 3 | 3.1 Related work       1         3.2 System model       2         3.3 RELTEQ       2         3.4 Periodic tasks       3         3.5 Servers       3         3.6 Hierarchical scheduling       4         3.7 Evalulation       4 | 7<br>9<br>24<br>29<br>33<br>55<br>14<br>50 |

| 4 | 4.1 Related work       5         4.2 System model       6         4.3 Reducing memory requirements       6         4.4 Handling overload conditions       7         4.5 Bounding the mode change latency       7                | 5<br>67<br>62<br>68<br>77<br>9<br>03       |

| 5 | Multi-resource management 9                                                                                                                                                                                                     | 06<br>07<br>0<br>3<br>28                   |

| 6 | Grasp 13                                                                                                                                                                                                                        | _                                          |

| ii | CONTENTS |

|----|----------|

|                        | 6.2     | Grasp overview                         | 136 |  |  |  |

|------------------------|---------|----------------------------------------|-----|--|--|--|

|                        | 6.3     | Multiprocessor scheduling              | 141 |  |  |  |

|                        | 6.4     | Hierarchical scheduling                | 144 |  |  |  |

|                        | 6.5     | Hierarchical multiprocessor scheduling | 146 |  |  |  |

|                        | 6.6     | Timestamp synchronization              | 147 |  |  |  |

| 7                      | Con     | clusion                                | 151 |  |  |  |

| Bibliography           |         |                                        |     |  |  |  |

| Symbol index           |         |                                        |     |  |  |  |

| Acronyms               |         |                                        |     |  |  |  |

| Accomplishments        |         |                                        |     |  |  |  |

| $\mathbf{S}\mathbf{u}$ | Summary |                                        |     |  |  |  |

| Curriculum Vitae       |         |                                        |     |  |  |  |

# Chapter 1

### Introduction

The history of the modern computer starts in 1944 with the Colossus. It was the world's first electronic, digital programmable computer, used by the British to decrypt German messages during World War II. It used vacuum tubes instead of mechanical or electrical relay switches found in its predecessors. The vacuum tubes were the computational units and were interconnected by simple copper wires. The machine was programmed by manually routing the wires. The first general-purpose electronic computer was the ENIAC, completed in 1946. Like the Colossus, it was colossal, weighing 30 tons, occupying 165 m<sup>2</sup>, and consuming 174kW of power (McCartney, 1999). Its 18 000 vacuum tubes could perform 5000 additions per second, and were initially used by the US army for computing the behavior of chemical reactions inside of a hydrogen bomb for the Manhattan project and later for ballistic analysis.

The invention of the transistor and the integrated circuit in the late 1940s, followed by their mass production in the 1950s, made it possible to shrink computers and to reduce their cost, making them available for many new applications. Initially they found their application in large and powerful mainframe computers, where several users at a time could execute their computations on a shared mainframe computer.

With their ever shrinking size, however, digital computers could also be used for controlling smaller systems. A prominent example is the Apollo Guidance Computer, which was responsible for guidance, navigation and control of the Apollo spacecrafts on their lunar missions in the late 1960s. It weighed 32kg, occupied 1 cubic foot, had 2K of RAM, and 36K of hard-wired core-rope memory with copper wires threaded or not threaded through tiny magnetic cores. It consumed 55 Watts and could perform 40 000 additions per second (O'Brien, 2010). The state of the art in scheduling in those days was to divide the entire control application into individual tasks, and to schedule them according to a round robin, First-In-First-Out, or table driven scheme. However, the safety critical nature of the Apollo Guidance Computer, combined with its limited resources, required new task scheduling methods, giving rise to one of the earliest priority-based schedulers. In the case of an overload, the scheduler would continue executing the highest priority tasks, at the cost of dropping those with a

2 Introduction

lower priority (Martin, 1994).

As digital computers were increasingly used for controlling safety critical systems, theories for reasoning about the behavior of these systems started to emerge, in particular, the real-time scheduling theory. Its goal is to analyze the mapping of the digital resources (such as the processor, memory or network) to tasks to ensure that the tasks' timing constraints (derived from the system timing constraints) are met. The seminal paper by Liu and Layland (1973) is often regarded as the beginning of the real-time scheduling theory. It proposed sufficient and necessary utilization bounds for fixed priority preemptive scheduling on uniprocessor systems. Since then, real-time theory has addressed more complicated systems, such as multiprocessor and distributed platforms, with dependencies between tasks, and various other constraints. Even though significant progress has been made, real-time scheduling and analysis still offers many challenging and fundamental open problems, in particular in the multiprocessor domain (Davis and Burns, 2011).

The Apollo Guidance Computer can be regarded as the precursor of modern embedded systems. Unlike large super computers, embedded devices have stringent operational constraints, such as weight, size, and cost. Consequently, embedded systems are characterized by limited processing, storage and energy resources. For example, due to the weight constraints, an airplane will reuse the same computer hardware to run the control software during different modes of operation, such as takeoff, flight, and landing. Switching between the different modes of operation must be efficient and predictable, without disturbing the operation of the entire system.

It is often too costly to develop dedicated hardware for solving a particular problem, which has lead to a wide adoption of general purpose computers, exemplified already by the Colossus vs. ENIAC. General purpose computers offer the flexibility to reuse the same hardware for different applications. As computer platforms and applications become ever more complex, however, the programmers must rely on operating systems providing higher level abstractions for managing the resources. In embedded systems this is often achieved by explicit fine-grained multi-resource management of the various resources comprising the platform. A popular abstraction are resource reservations (Mercer et al., 1994), which aim at providing temporal isolation between independent tasks. They form the basis for virtual platforms, which provide tasks with the illusion of executing on a dedicated platform, often comprised of several different resources.

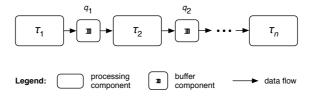

As applications became increasing complex, comprised of hundreds of tasks, it became more difficult and costly to develop large systems. This gave rise to component-based engineering, which offers a modular approach for designing and developing complex systems by grouping the tasks performing a particular function inside of components. Several component models for real-time systems were proposed since, most notably the periodic resource model (Shin and Lee, 2003), aiming to facilitate independent development and analysis of components. Hierarchical scheduling is then used to schedule components on the global level, and tasks locally within components. Due to the limited resources in embedded systems, it is important that the mechanisms provided by an operating system, such as task scheduling and timer management, are efficient and introduce little overhead.

Problem statement 3

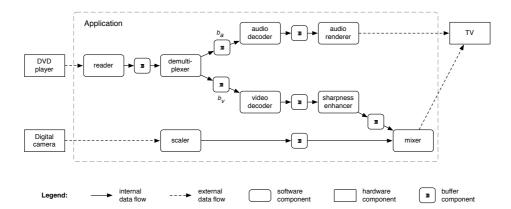

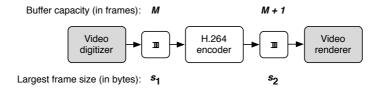

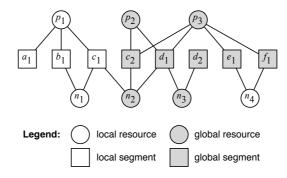

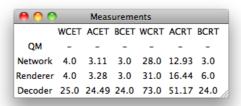

We conducted our work within the context of multimedia processing systems in the surveillance domain. The hardware platforms in this domain are usually resourceconstrained embedded systems, comprised of multiple different resources, such as a processor, memory and digital signal processors. The multimedia applications which are mapped to these platforms have real-time constraints, are data intensive, and experience high variability of resource requirements due to data-dependent workload. For example, an MPEG encoder will require more processing time for a scene with a lot of movement. Consequently, the encoded video frames will vary in size, requiring variable amount of network bandwidth during transmission and memory during decoding. If several video streams are processed on the same platform, and their total resource requirements exceed the available resources, then a tradeoff needs to be maintained between the resource requirements and the quality of the individual streams (expressed in terms of e.g. timing constraints on individual frames), to guarantee a system wide quality of service. We considered multimedia processing applications comprised of several scalable components, which can operate in different modes and are scheduled by a hierarchical scheduling framework.

### 1.1 Problem statement

This thesis addresses the problem of mapping multiple heterogenous resources to tasks in the context of resource constrained embedded real-time systems. It focuses on three research questions:

- 1. How can we design an efficient hierarchical scheduling framework for supporting independent development and analysis of component based systems, to provide temporal isolation between components?

- 2. How do we change the mapping of resources to tasks and components during run-time efficiently and predictably, and how do we analyze the latency of such a system mode change in systems comprised of several scalable components?

- 3. How do we schedule and analyze a set of parallel-tasks which require simultaneous access to several different resources, while guaranteeing that all tasks meet their deadlines?

### 1.2 Contributions

In Chapter 2 we propose a system model, comprised of a resource model, an application model, and a mapping between the two. The novel resource model abstracts the key properties of heterogenous resources from a scheduling perspective, providing a uniform model for different resources, such as a processor, memory or network. The application model is based on the notions of tasks and components, and supports the modeling and analysis of hierarchical and reservation-based systems.

4 Introduction

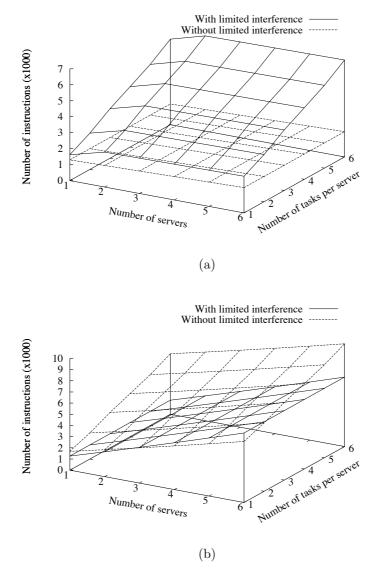

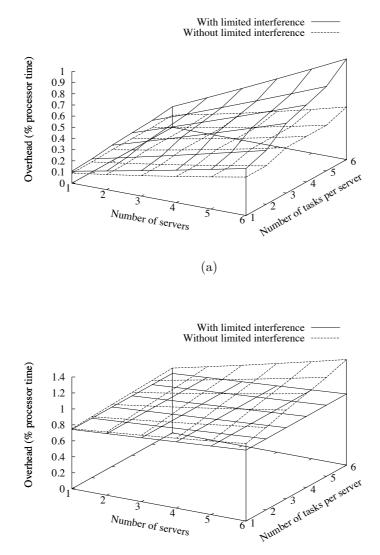

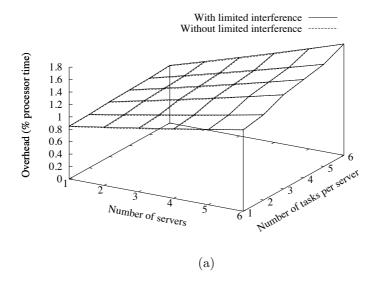

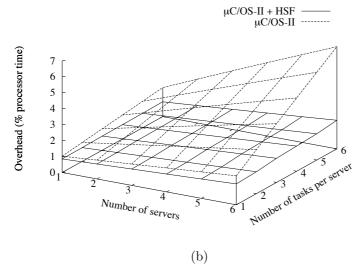

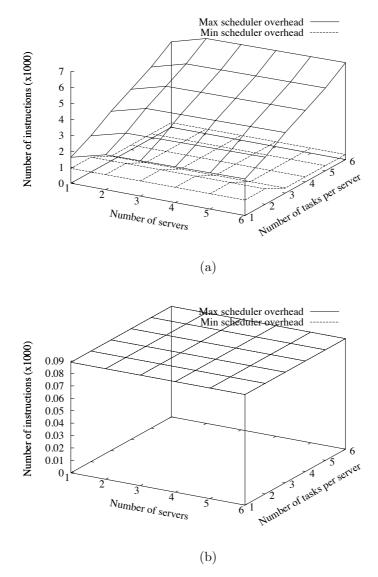

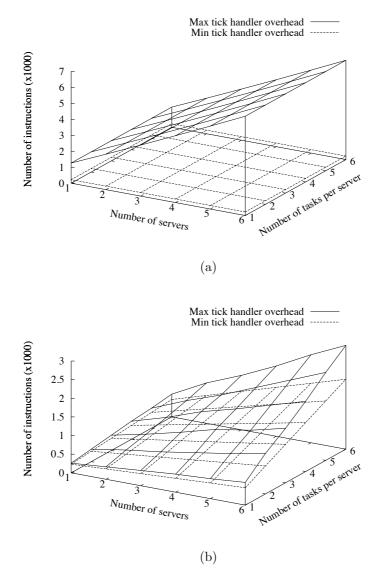

In Chapter 3 we present RELTEQ, which is a general timer management system exhibiting low processor and memory overheads. We then leverage RELTEQ to design and implement an efficient hierarchical scheduling framework, which provides temporal isolation between components. The system overheads are evaluated based on an implementation within  $\mu C/OS-II$ , a real-time operating system used in the industry in various domains, such as aerospace, automotive, medical, and surveillance.

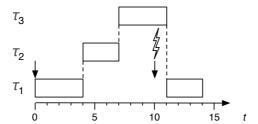

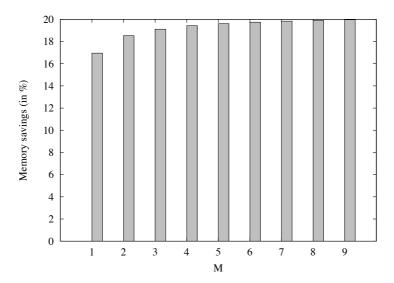

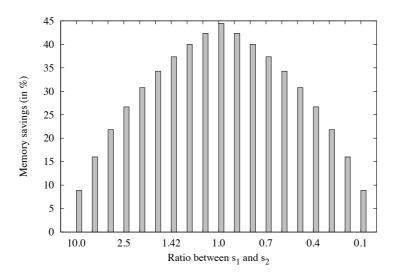

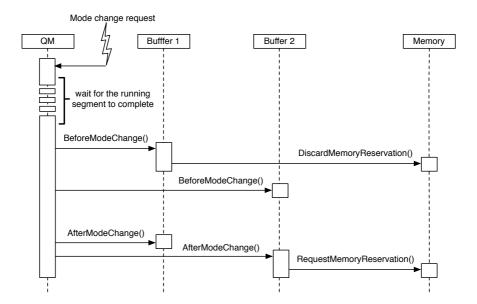

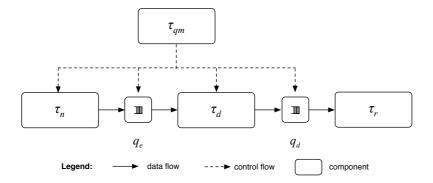

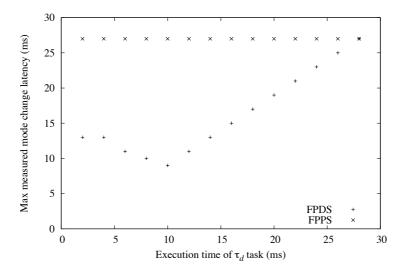

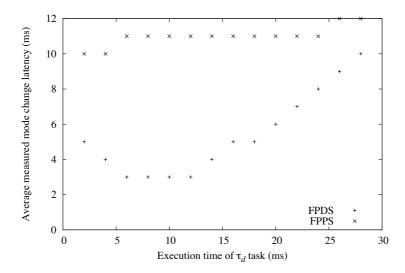

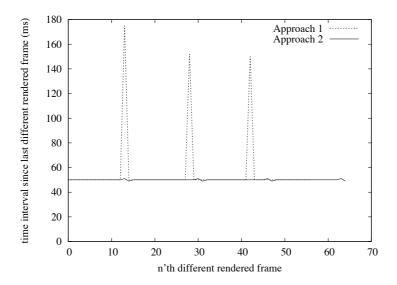

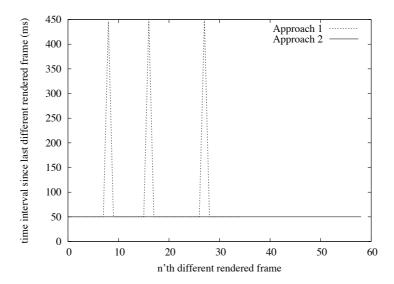

In Chapter 4 we investigate scalable applications operating in a memory-constrained system. A scalable application, comprised of scalable components, can operate in one of several predefined system modes, defined in terms of component modes. A component mode defines a trade-off between its resource requirements and its output quality. During runtime the system may reallocate the resources between the components, resulting in a system mode change. The latency of a system mode change, defined as the time duration between a mode change request and the time that it has been effected, should satisfy an upper bound. We first show how to reduce the memory requirements in a streaming multimedia application. We then show how to provide guaranteed resource access in spite of mode changes, while at the same time minimizing the mode change latency bound. We present a novel mode change protocol called Swift Mode Changes, which relies on fixed priority with deferred preemption scheduling. The design, analysis and implementation are presented and evaluated based on a quantitative analysis.

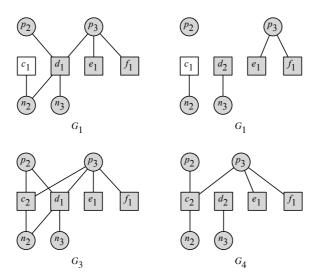

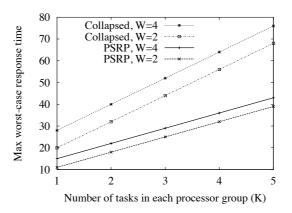

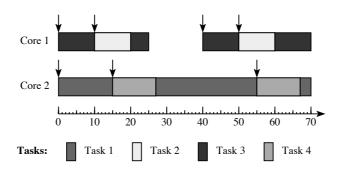

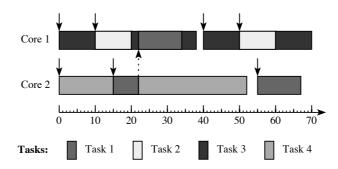

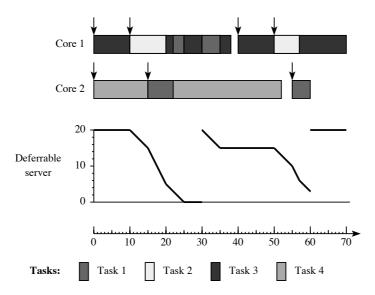

In Chapter 5 we address the problem of scheduling periodic parallel tasks on a multi-resource platform, where tasks have real-time constraints. The goal is to exploit the inherent parallelism of a platform comprised of multiple heterogeneous resources. A new scheduling algorithm called PSRP is presented, together with the accompanying schedulability analysis. The benefits of PSRP are demonstrated by means of simulation results and an example application showing that PSRP indeed exploits the available concurrency in heterogeneous real-time systems.

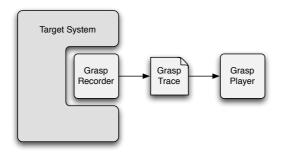

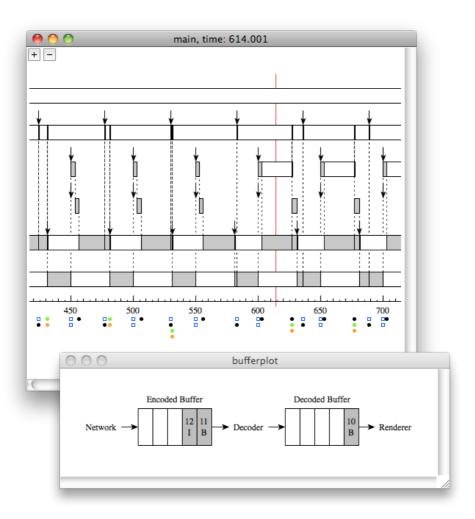

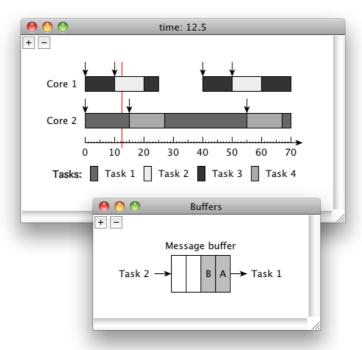

In Chapter 6 we present a trace visualization toolset called Grasp, which we have used extensively during the design and development of the various real-time operating system extensions described in this thesis. It provides and clear and intuitive user interface and a simple architecture, making it easy to extend Grasp with new visualizations.

### 1.3 Outline

This thesis is structured as follows. Chapter 2 introduces the system model, which is used later in Chapters 3, 4, and 5. Each of these chapters instantiates and extends the model for its particular needs. Chapters 3, 4, 5, and 6 discuss the main contributions outlined in Section 1.2. Chapter 7 concludes this thesis. A list of publications contributing to this thesis can be found in the Accomplishments appendix.

# Chapter 2

# System model

A system consists of applications, resources and a mapping between them. Application workload is expressed in terms of tasks, where a task represents the work which needs to be done in response to an event, such as processing a newly arrived video frame. The mapping of resources to tasks describes how the "ownership" of resources changes during runtime, i.e. which task "owns" a particular resource at a particular time. The ownership may change, e.g. if several tasks need to access the same memory region or the same processor. A mapping must satisfy certain soundness constraints, e.g. every mutually exclusive resource is owned by at most one task at a time. In real-time systems there are additional timeliness constraints, which are often expressed in terms of task deadlines. Embedded systems exhibit additional constraints which address the overheads associated with the mapping due to limited resources, such as scheduling, and context switching overheads.

In this chapter we present an abstraction which allows us to model the scheduling of tasks on *different* resources in a uniform way. The essential abstraction is that any resource (such as a processor, memory space or bus) can be represented as a multi-unit preemptive or non-preemptive resource.

### 2.1 Resource model

The purpose of a resource model is to provide a certain level of abstraction helping to describe the mapping of physical resources to tasks. It has to be simple enough to reason about, while at the same time expressive enough to use the available resources efficiently. The main contribution of our model is the ability to schedule tasks on various different resources, such as processor and memory, in a uniform way. At the core of our resource model is the multi-unit resource.

**Definition 2.1** (Multi-unit resource). Let  $\mathcal{R}$  be the set of all resources in the system. A multi-unit resource  $r \in \mathcal{R}$  consists of multiple units, where each unit is a serially accessible entity. A resource r is specified by its capacity  $N_r \geq 1$ , which represents the maximum number of units the resource can provide simultaneously.

Memory space is an example of a *multi-unit resource*. In this thesis, when talking about the memory space resource we are interested in the memory requirements in terms of memory size, and ignore the specifics of memory allocation and the actual data stored in the memory. A memory, managed as a collection of fixed sized blocks, can be regarded as a multi-unit resource with capacity equal to the number of blocks. In this sense our multi-unit resource is similar to a multi-unit resource discussed by Baker (1991).

The capacity of a multi-unit resource represents essentially the maximum number of tasks which can use the resource simultaneously. A multi-core processor can therefore be modeled as a resource with capacity equal to the number of cores.

Resource management is about managing access to scarce resources, i.e. resources for which at times the demand may exceed their provision. If the total requirement for a resource never exceeds its capacity, then the management is trivial: we can always provide access to the resources. When modeling systems we can therefore ignore resources for which the demand never exceeds their provision.

Single-unit resources are a special case of multi-unit resources.

**Definition 2.2** (Single-unit resource). A single-unit resource  $r \in \mathcal{R}$  is a multi-unit resource such that  $N_r = 1$

A single-core processor is an example of a *single-unit resource*, since only a single task can be using it at a time. A memory controller synchronizing the access to a memory space can also be regarded as a single-unit resource<sup>1</sup>. In the remainder of the thesis we assume multi-unit resources with capacity greater than 1, unless explicitly stated otherwise.

### 2.1.1 Preemptive vs. non-preemptive resources

A preemption is the change of ownership of a resource unit before the owner is ready to relinquish the ownership. In terms of the traditional task model, a job (representing the ownership of a resource) may be preempted by another job before it completes. We can classify all resources in one of two categories:

**Definition 2.3** (Preemptive resource). The usage (or ownership) of a unit of a preemptive resource can be preempted without corrupting the state of the resource. We use  $\mathcal{P} \subseteq \mathcal{R}$  to denote the set of all preemptive resources in the system.

**Definition 2.4** (Non-preemptive resource). The usage (or ownership) of a unit of a non-preemptive resource may not be preempted without the risk of corrupting the state of the resource. We use  $\mathcal{N} \subseteq \mathcal{R}$  to denote the set of all non-preemptive resources in the system.

Every resource is either preemptive or non-preemptive, i.e.

$$(\mathcal{N} \cup \mathcal{P} = \mathcal{R}) \wedge (\mathcal{N} \cap \mathcal{P} = \emptyset). \tag{2.1}$$

<sup>&</sup>lt;sup>1</sup>A memory can therefore be modeled by *two* resources: one representing the memory space and the other representing mutually exclusive access to the memory.

A processor is an example of a preemptive resource, as the processor state of a running task can be saved upon a preemption and later restored. A bus is an example of a non-preemptive resource, as an ongoing message transfer cannot be preempted without loosing the message. A logical resource (e.g. a shared variable) is another example of a non-preemptive resource.

Preemption is usually provided on the software level, by the operating system. For example, when an interrupt arrives, the operating system first stores the processor state, then executes the interrupt handler, and finally restores the saved processor state. Note that actually the usage of nearly any resource can be preempted: e.g. memory space (usually considered a non-preemptive resource) can be "switched out" to a memory higher in the memory hierarchy (e.g. data can be moved from the processor cache to the RAM), or the data can be simply overwritten and recomputed later. However, this will come at the cost of a performance penalty (incurred by storing-and-restoring or recomputing the state of the resource). A non-preemptive resource is basically one for which the system designer has decided that its preemption overhead is too large.

We assume mutually exclusive access to resources, meaning that each unit of a multi-unit resource can be accessed by at most one task at a time. For example, each core in a multicore processor can be accessed by at most one task at a time. Notice that preemptiveness is orthogonal to mutual exclusion, as mutual exclusion holds for both preemptive and non-preemptive resources.

### 2.1.2 Physical vs. virtual resources

Physical resources are the hardware resources provided by the platform, such as a processor, memory or bus. As we will see later in Section 2.2.2, application components can provide their own *virtual* resources. We use  $\mathcal{R}$  to denote both physical and virtual resources. Similar to physical resources, each virtual resource is either preemptive or non-preemptive.

### 2.2 Application model

Let  $\mathcal{T} = \mathbb{R}_0^+$  be the time domain (of non-negative real numbers), with  $t \in \mathcal{T}$  representing a time instant or the duration of a time interval.

### 2.2.1 Tasks

We model applications in terms of a set of *tasks*. Each task specifies the resource requirements which are required to do a particular work.

**Definition 2.5** (Task). A task  $\tau_i$  is specified by its

- fixed and unique priority  $\pi_i$  (lower number indicating higher priority),

- period  $T_i$ , which specifies the inter-arrival time between two consecutive instances of  $\tau_i$ ,

- initial offset (or phasing)  $O_i$ , which specifies the arrival time of the first instance of  $\tau_i$ ,

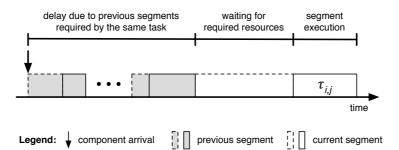

- relative deadline  $D_i$ , with  $D_i \leq T_i$ ,

- sequence of segments  $S_i$ , where the j-th segment  $\tau_{i,j} \in S_i$  is specified by its worst-case execution time  $E_{i,j}$ , and a set of resource requirements  $R_{i,j}$ . Each resource requirement  $(r,n) \in R_{i,j}$  represents a requirement for n > 0 units of resource  $r \in \mathcal{R}$ .

We use  $\Gamma$  to denote the set of all tasks in the system, and S to denote the set of all segments in the system, i.e.

$$\mathcal{S} = \bigcup_{\tau_i \in \Gamma} S_i$$

Our task therefore models programs which can be expressed as a sequence of segments, where each segment  $\tau_{i,j}$  is wrapped between a  $lock(R_{i,j})$  and  $unlock(R_{i,j})$  operation. The semantics of these operations is similar to the primitives used in (Havender, 1968) for locking resources collectively.

Priorities are used for resolving conflicts during runtime when more than one task tries to access a shared resource. All segments  $\tau_{i,j} \in S_i$  share its priority  $\pi_i$ . We use  $\pi_{\perp}$  to denote a priority lower than the lowest priority, and  $\pi_{\top}$  to denote a priority higher than the highest priority among all tasks.

**Notation** To keep the notation short, if a segment  $\tau_{i,j}$  requires only single-unit resources, or if the number of required units is not important, we will write  $R_{i,j} = \{r_1, r_2, r_3\}$  instead of  $R_{i,j} = \{(r_1, 1), (r_2, 1), (r_3, 1)\}$ .

We use a shorthand notation to refer to the resources which are required by a segment, where  $r \in R_{i,j}$  means that  $\exists (x,n) \in R_{i,j} : x = r$ .

When specifying segments we use a shorthand notation, where  $(e, \{r_1, r_2, \ldots\})$  represents a segment  $\tau_{i,j}$  with  $E_{i,j} = e$  and  $R_{i,j} = \{r_1, r_2, \ldots\}$ .

When applying set operations to sets of resource requirements we are usually interested only in the identity of the resources (and not the number of units). Therefore, for simplicity, we will use  $R_{i,j} \cap R_{x,y}$  to denote  $\{r \mid (r,n) \in R_{i,j} \land (r,m) \in R_{x,y}\}$ , and  $R_{i,j} \cup R_{x,y}$  to denote  $\{r \mid (r,n) \in R_{i,j} \lor (r,m) \in R_{x,y}\}$ .

We use  $E_i = \sum_{\tau_{i,j} \in S_i} E_{i,j}$  to denote the worst-case execution time of task  $\tau_i$ .

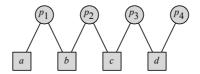

**Example 2.1.** Our model distinguishes between 2 single-core processors (modeled as 2 single-unit resources) and a single 2-core processor (modeled as one multi-unit resource). In the 2 single-core processors case, we can specify a task requiring simultaneous access for t time units to particular single-core processors, e.g.

$$\mathcal{P} = \{p_1, p_2\}, N_{p_1} = 1, N_{p_2} = 1, \Gamma_{=}\{\tau_1\}, S_1 = \langle (t, \{p_1, p_2\}) \rangle.$$

In the 2-core processor case we can only specify a task requiring simultaneous access for t time units to a particular number of cores, e.g.

$$\mathcal{P} = \{p\}, N_p = 2, \Gamma = \{\tau_1\}, S_1 = \langle (t, \{(p, 2)\}) \rangle.$$

### 2.2.2 Components

Next to the notion of physical resources (described in Section 2.1.2) we introduce the notion of *virtual* resources, which are provided by *components*.

**Definition 2.6** (Component). A component c is specified by its

- fixed and unique priority  $\pi_c$  (lower number indicating higher priority),

- period  $T_c$ , which specifies the inter-arrival time between two consecutive instances (or replenishments of the budget) of c,

- initial offset (or phasing)  $O_c$ , which specifies the arrival time of the first instance (or replenishment of the budget) of c,

- relative deadline  $D_c$ , with  $D_c \leq T_c$ ,

- set of resource requirements  $R_c$ , where each resource requirement  $(r, n) \in R_c$  represents a requirement for n > 0 units of resource  $r \in \mathcal{R}$ ,

- set of resource provisions  $P_c$ , where each resource provision  $(r, n) \in P_c$  represents a provision of n > 0 units of resource  $r \in \mathcal{R}$ ,

- time capacity (or budget)  $E_c$ , which specifies the amount of time during each period that component c will provide the resources in  $P_c$ , while requiring the resources in  $R_c$ .

We use C to denote the set of all components in the system.

A component c provides *virtual* resources, which are specified in  $P_c$ . We include these resources in the set of all resources in the system, i.e.

$$\forall c \in \mathcal{C} : P_c \subseteq \mathcal{R}.$$

The following two examples demonstrate how to express a processor server and a memory buffer in terms of our component model.

Example 2.2 (A processor server component). A single core processor can be modeled as a preemptive resource  $cpu \in \mathcal{P}$  with  $N_{cpu} = 1$ . A processor server s provides a share of a processor bandwidth, which is specified by its replenishment period  $\Pi_s$  and capacity  $\Theta_s$  (Shin and Lee, 2003). When a server is running, every time unit its remaining budget is decremented by one. Every  $\Pi_s$  time units its remaining budget is replenished to  $\Theta_s$ . In systems with global fixed-priority scheduling each server also has a fixed priority  $\pi_s$ .

A server s providing a share of processor cpu, can be modeled as a component  $c \in \mathcal{C}$  with

$$\pi_{c} = \pi_{s}

T_{c} = \Pi_{s}

O_{c} = 0

D_{c} = \Pi_{s}

E_{c} = \Theta_{s}

R_{c} = \{(cpu, 1)\}

P_{c} = \{(cpu_{s}, 1)\}$$

(2.2)

with  $cpu_s \in \mathcal{P}$ .

**Example 2.3** (A memory buffer component). A memory containing M bytes can be modeled by a non-preemptive resource  $mem \in \mathcal{N}$  with  $N_{mem} = M$ . A memory buffer component manages a part of the memory space in terms of buffer elements and provides a FIFO access to these elements. Each buffer q has a finite capacity  $NumElems_q$ , defining the maximum number of elements which can be stored in the buffer, where each element has a fixed size of  $ElemSize_q$  bytes.

A buffer q, which resides in memory mem and is created during the initialization of the system and never destroyed, can be modeled as a component  $c \in \mathcal{C}$  with

$$T_{c} = \infty$$

$$O_{c} = 0$$

$$D_{c} = \infty$$

$$E_{c} = \infty$$

$$R_{c} = \{(mem, ElemSize_{q} * NumElems_{q})\}$$

$$P_{c} = \{(elements_{q}, NumElems_{q}), (mutex_{q}, 1)\}$$

$$(2.3)$$

with  $elements_q, mutex_q \in \mathcal{N}$ .  $T_c = \infty$  means that the component is aperiodic.  $O_c = 0$  and  $D_c = E_c = \infty$  mean that the buffer will be created at the system initialization and live until the system terminates. During that time it will require  $ElemSize_q * NumElems_q$  units of the mem resource, and in return it will provide a virtual  $elements_q$  resource containing  $NumElems_q$  buffer elements.

A buffer provides interface methods to store and retrieve elements from the buffer. These methods manipulate the buffer's internal data structures and have to execute in a mutually exclusive fashion. A common implementation will guard these methods with a mutex. A call to the buffer's interface methods is modeled by a requirement for one unit of the virtual  $mutex_q$  resource for the duration of the call. Since  $N_{mutex_q} = 1$  and  $mutex_q \in \mathcal{N}$ , only one task may access the buffer's interface methods at a time. Note that a buffer requires mutually exclusive access only to its internal data structures. This means that one task can be reading from the buffer's head element, while another task is writing to the tail element, provided that the internal data structures keeping track of the pointers to the head and tail are updated in a mutually exclusive manner.

Note that since buffers live in the memory for the entire duration of the system execution, during runtime there is no need for arbitration between two buffers com-

Mapping 11

peting for memory: all buffers need to fit in the memory or the application cannot start executing. Hence, the priority of the buffer component is irrelevant.  $\Box$

### 2.2.3 Applications

We can group tasks and components which together perform a particular function to form an application.

**Definition 2.7.** An application a is specified by its

- $task \ set \ \Gamma_a \subseteq \Gamma$ ,

- component set  $C_a \subseteq C$ .

We use A to denote the set of all applications in our system.

Every task (or component) belongs to at most one application. We assume that applications are independent and do not share tasks (or components), i.e.

$$\forall a, b \in \mathcal{A} : a \neq b \Rightarrow (\Gamma_a \cap \Gamma_b = \emptyset \land \mathcal{C}_a \cap \mathcal{C}_b = \emptyset). \tag{2.4}$$

### 2.3 Mapping

In Sections 2.1 and 2.2 we have defined the static models describing the resources and the applications. Now we move on to the mapping of resources to applications. The mapping is responsible for time sharing the access to resources during runtime, and is defined by *allocation* and *scheduling*. An allocation assigns task segments and components to their required resources, while a schedule describes *when* segments and components gain access to their assigned resources.

### 2.3.1 Allocation

In this thesis we assume static allocation of resources (also referred to as partitioning), which is specified in our system model by the resource requirements of task segments and components. In embedded systems, where hardware platforms are usually comprised of several different resources (e.g. CPU, DSP, DMA controller), tasks must be explicitly mapped to the various resources. In such systems static allocation of tasks to resources is often desired. It also simplifies the scheduling of the entire platform during runtime, since the decision of allocation has been taken offline.

### Resource identity in multi-unit resources

When a task or component requests memory space for storing its data, it assumes that no other task or component will modify and corrupt the data inside of its memory space. This suggests that two parameters should be associated with each granted memory request: its size and its identity. The scheduling function makes sure that a resource request for n units of a multi-unit resource is granted only if the resource

12 System model

has at least n units available. When a request is granted, the requesting task or component has complete control over these units. Protection mechanisms preventing tasks and components from corrupting each others resources are outside the scope of this model.

However, when a task or component accessing a resource is preempted it may be critical that it is later resumed on the *same* resource units. For example, when a job is preempted while it is writing to a particular memory location, once it is resumed it should continue writing to the same location. Our model abstracts from the identity of individual units in a multi-unit resource and therefore it cannot be used to reason about particular resource units. However, we can assume the context switch to be responsible for making sure that a segment is resumed on the appropriate resource units. In the example of a preemption of a task writing to memory, upon preemption the system may store the partially written data to the disk and later restore it to the memory upon resuming.

### 2.3.2 Scheduling

The schedule needs to maintain the timing constraints of tasks and components and mutually exclusive access to shared resources. All these constraints can be resolved offline, giving rise to a time-driven schedule. Alternatively, the scheduling can be done online, where scheduling decisions are event-driven and performed according to a predefined scheduling policy. In this thesis we consider the latter, focusing on Fixed-Priority Preemptive Scheduling (FPPS) and Fixed-Priority with Deferred-preemption Scheduling (FPDS).

We can schedule both tasks and components. When a task segment (or a component) is scheduled on a resource during runtime, we say that the segment (or component) is *using* the resource, or that it *owns* the resource. The ownership of a resource may change. However, at any point in time each unit of a multi-unit resource may be used by at most one segment (or component).

The scheduling of segments on a multi-unit resource r can be visualized by means of  $N_r$  "tracks", where each track represents the usage of a single unit of resource r, as illustrated in Example 2.4.

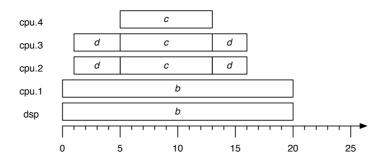

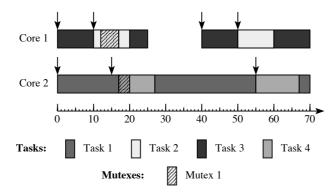

**Example 2.4.** Figure 2.1 represents a schedule of segments b, c, and d on resources cpu and dsp, with b scheduled at time 0, d scheduled at time 1 and c scheduled at time 5 and preempting segment d. The arrival pattern of a segment is determined by the task it belongs to, which is discussed in the next section.

A resource manages its units internally, meaning that we cannot specify a requirement for a particular unit of a multi-unit resource. A segment can only specify a requirement for a certain number of arbitrary units within a multi-unit resource. However, we assume that while a segment is "executing" on a resource unit the segment will not be migrated to another unit. For example, in Figure 2.1, once d's requirement for 2 cores of the cpu is granted, d will own the same cpu cores throughout its execution in the time interval [1,5). Note that the cpu resource may decide to migrate d to different units when it is preempted at time 5.

Mapping 13

Figure 2.1: Example of a mapping of segments  $S = \{b, c, d\}$  with  $E_b = 20$ ,  $R_b = \{(cpu, 1), (dsp, 1)\}$ ,  $E_c = 8$ ,  $R_c = \{(cpu, 3)\}$ ,  $E_d = 7$ ,  $R_d = \{(cpu, 2)\}$ , on a platform containing a 4-core cpu and a single dsp, i.e.  $\mathcal{R} = \{cpu, dsp\}$  with  $N_{cpu} = 4$ ,  $N_{dsp} = 1$ . We use a dot notation to refer to the individual units in a multi-unit resource.

### Scheduling of tasks

**Definition 2.8** (Task schedule). A schedule  $\sigma^{S}: \mathcal{T} \times \mathcal{S} \times \mathcal{R} \to \mathbb{N}$  expresses resource ownership by task segments during runtime, where  $\sigma^{S}(t, s, r)$  is the number of units of resource r which are owned by segment s at time t.

Saying that "at time t segment s owns n units of resource r" is synonymous to saying that "at time t segment s executes on n units of resource r" or that "at time t segment s is scheduled on n units of resource r".

**Definition 2.9.** We define  $\eta^{\mathcal{S}}: \mathcal{T} \times \mathcal{S} \times \mathcal{R} \to \{0,1\}$ , where  $\eta^{\mathcal{S}}(t,s,r)$  returns 1 if at time t segment s is scheduled on resource r, and 0 otherwise, i.e.

$$\eta^{\mathcal{S}}(t, s, r) = \begin{cases} 1 & \text{if } \sigma^{\mathcal{S}}(t, s, r) > 0, \\ 0 & \text{otherwise.} \end{cases}$$

(2.5)

The scheduling function  $\sigma^{\mathcal{S}}$  must satisfy the following criteria:

1. A segment is scheduled only on resources which it requires, i.e.

$$\forall t \in T, s \in \mathcal{S}, r \in \mathcal{R} : \sigma^{\mathcal{S}}(t, s, r) > 0 \Rightarrow r \in R_s. \tag{2.6}$$

2. A segment is scheduled on all of its required resources, or not at all, i.e.

$$\forall t \in T, s \in \mathcal{S} : (\exists r \in R_s : \sigma^{\mathcal{S}}(t, s, r) > 0) \Rightarrow (\forall (r, n) \in R_s : \sigma^{\mathcal{S}}(t, s, r) = n).$$

(2.7)

3. The scheduling function must satisfy the realtime constraints, by making sure that every segment receives its worst-case execution time on its required resources before its parent task's deadline, i.e.

$$\forall k \in \mathbb{N}, \tau_{i,j} \in \mathcal{S}, r \in R_{i,j} : (k+1)E_{i,j} \le \int_0^{k*T_i + D_i} \eta^{\mathcal{S}}(x, \tau_{i,j}, r) dx. \tag{2.8}$$

14 System model

### Scheduling of components

**Definition 2.10** (Component schedule). A schedule  $\sigma^{\mathcal{C}}: \mathcal{T} \times \mathcal{C} \times \mathcal{R} \to \mathbb{N}$  expresses resource ownership by components during runtime, where  $\sigma^{\mathcal{C}}(t,c,r)$  is the number of units of resource r which are owned by component c at time t.

Saying that "at time t component c owns n units of resource r" is synonymous to saying that "at time t component c executes on n units of resource r" or that "at time t component c is scheduled on n units of resource r".

**Definition 2.11.** We define  $\eta^{\mathcal{C}}: \mathcal{T} \times \mathcal{C} \times \mathcal{R} \to \{0,1\}$ , where  $\eta^{\mathcal{C}}(t,c,r)$  returns 1 if at time t component c is scheduled on resource r, and 0 otherwise, i.e.

$$\eta^{\mathcal{C}}(t,c,r) = \begin{cases} 1 & \text{if } \sigma^{\mathcal{C}}(t,c,r) > 0, \\ 0 & \text{otherwise.} \end{cases}$$

(2.9)

**Definition 2.12.** We define  $\beta: \mathcal{T} \times \mathcal{C} \to \mathcal{T}$ , which captures the remaining budget (or time) of components during runtime, where  $\beta(t,c)$  is the remaining budget of component c at time t.

The scheduling function  $\sigma^{\mathcal{C}}$  must satisfy the following criteria:

4. A component is scheduled only on resources which it requires, i.e.

$$\forall t \in T, c \in \mathcal{C}, r \in \mathcal{R} : \sigma^{\mathcal{C}}(t, c, r) > 0 \Rightarrow r \in R_c. \tag{2.10}$$

5. A component is scheduled on all of its required resources, or not at all, i.e.

$$\forall t \in T, c \in \mathcal{C} : (\exists r \in R_c : \sigma^{\mathcal{C}}(t, c, r) > 0) \Rightarrow (\forall (r, n) \in R_c : \sigma^{\mathcal{C}}(t, c, r) = n).$$

(2.11)

6. The scheduling function must satisfy the realtime constraints, by making sure that every component receives its required time capacity on its required resources before its deadline. The exact specification may differ for different components. For the periodic-idling server component (see Section 3.2.2), the real-time requirement can be formalized as

$$\forall k \in \mathbb{N}, c \in \mathcal{C}, r \in R_c : (k+1)E_c = \int_0^{k*T_c + D_c} \eta^{\mathcal{C}}(x, c, r) dx. \tag{2.12}$$

7. Only components with remaining budget are scheduled, i.e.

$$\forall t \in \mathcal{T}, c \in \mathcal{C} : (\exists r \in \mathcal{R} : \sigma^{\mathcal{C}}(t, c, r) > 0) \Rightarrow \beta(t, c) > 0. \tag{2.13}$$

8. The remaining budget should never exceed component's time capacity, i.e.

$$\forall t \in \mathcal{T}, c \in \mathcal{C} : 0 \le \beta(t, c) \le E_c. \tag{2.14}$$

Mapping 15

9. The remaining budget of a component c is replenished periodically, with period  $T_c$ . Each budget is consumed at a uniform rate whenever it is scheduled. The exact specification may differ for different components. For the periodic-idling server component (see Section 3.1.2), the periodic replenishment and uniform consumption requirement can be formalized as

$$\forall k \in \mathbb{N}, c \in \mathcal{C}, t \in [kT_c, (k+1)T_c), r \in R_c : \beta(t, c) = E_c - \int_{kT_c}^t \eta^{\mathcal{C}}(x, c, r) dx.$$

$$(2.15)$$

### Scheduling of tasks and components

The scheduling functions  $\sigma^{\mathcal{S}}$  and  $\sigma^{\mathcal{C}}$  must satisfy the following criteria:

10. The scheduling functions never schedule more units than a resource can provide, i.e.

$$\forall t \in \mathcal{T}, r \in \mathcal{R} : \sum_{s \in \mathcal{S}} \sigma^{\mathcal{S}}(t, s, r) + \sum_{c \in \mathcal{C}} \sigma^{\mathcal{C}}(t, c, r) \le N_r.$$

(2.16)

Note that several segments and component may be scheduled on a resource at the same time, as long as together they do not require more units than the resource can provide.

11. A task or component is scheduled on a virtual resource provided by another component only when that component is itself scheduled on its required resources, i.e.

$$\forall t \in \mathcal{T}, s \in \mathcal{S}, c \in \mathcal{C}, p \in P_c : \sigma^{\mathcal{S}}(t, s, p) > 0 \Rightarrow (\forall q \in R_c : \sigma^{\mathcal{C}}(t, c, q) > 0)$$

$$(2.17)$$

$$\forall t \in \mathcal{T}, c_1, c_2 \in \mathcal{C}, p \in P_{c_2} : \sigma^{\mathcal{C}}(t, c_1, p) > 0 \Rightarrow (\forall q \in R_{c_2} : \sigma^{\mathcal{C}}(t, c_2, q) > 0)$$

$$(2.18)$$

# Chapter 3

# Processor management

Modern real-time systems have become exceedingly complex. A typical car is controlled by over 100 million lines of code executing on close to 100 Electronic Control Units (ECU). With more and more functions being implemented in software, the traditional approach of implementing each function (such as engine control, ABS, windows control) on a dedicated ECU is no longer viable, due to increased manufacturing costs, weight, power consumption, and decreased reliability and serviceability (Nolte et al., 2009). With the ECUs having increasingly more processing power, it has become feasible to integrate several functions on a single ECU. However, this introduces the challenge of supporting independent and concurrent development and analysis of individual functions which are later to be integrated on a shared platform. A popular approach in the industry and literature is component-based engineering, where the complete system is divided into smaller software components which can be developed independently. The Automotive Open System Architecture (AUTOSAR) (AUTOSAR, 2011) standard is an example of such an approach in the automotive domain. It relies on a formal specification of component interfaces to verify the functional properties of their composition. Many functions in automotive systems, however, also have real-time constraints, meaning that their correct behavior is not only dependent on their functional correctness but also their temporal correctness. AUTOSAR does not provide temporal isolation between components. Verifying the temporal properties of an integrated system requires complete knowledge of all functions comprising the components mapped to the same ECU, and therefore violates the requirement for independent development and analysis.

In this chapter we address the problem of providing temporal isolation to components in an integrated system. Ideally, temporal isolation allows to develop and verify the components independently (and concurrently), and then to seamlessly integrate them into a system which is functioning correctly from both a functional and timing perspective (Shin and Lee, 2008; Nolte, 2011). The question is how to provide true temporal isolation when components execute on a shared processor. We address this problem by means of an hierarchical scheduling framework (HSF).

An HSF provides the means for the integration of independently developed and

analyzed components into a predictable real-time system. A component is defined by a set of tasks, a local scheduler and a *server*, which defines the component's time budget (i.e. its share of the processing time) and its replenishment policy.

### Problem description

An HSF-enabled platform should provide the following general functionalities:

- 1. Interface for the creation of servers and assigning tasks to servers.

- 2. Virtual timers, which are relative to a components's budget consumption, as well as *global timers*, which are relative to a fixed point in time.

- 3. Local scheduling of tasks within a component, and global scheduling of components on the system level.

In this chapter we focus on providing temporal isolation and preventing interference between components. We aim at satisfying the following additional requirement:

4. Expiration of events local to a component, such as the arrival of periodic tasks, should not interfere with other components. In particular, the handling of the events local to inactive components should be deferred until the corresponding component is activated. The time required to handle them should be accounted to the corresponding component, rather than the currently active one.

These requirements should be met by a modular and extensible design, with low performance overhead and minimal modifications to the underlying RTOS. It should exhibit predictable overhead, while remaining efficient to support resource-constrained embedded systems in the automotive domain.

Real-time applications will often require support for periodic task arrival. Periodic tasks rely on timers to represent their arrival time. For servers, we also need timers representing the replenishment and depletion of a budget. Vital, and a starting point for our design, is therefore the support for simple timers (or timed events), i.e. the assumption that an event can be set to arrive at a certain time. This simple timer support is typically available in an off-the-shelf Real-Time Operating System (RTOS) (Labrosse, 2002). Some RTOSes provide much more functionality (for which our work then provides an efficient realization) but other systems provide just that. As a result, the emphasis lies with the management of timers. The timer management should support long event inter-arrival times and long lifetime of the system at a low overhead.

### Contributions

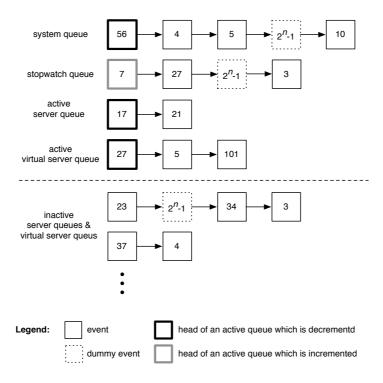

We first present the design of a general timer management system, which is based on Relative Timed Event Queues (RELTEQ), an efficient timer management system targeted at embedded systems. Pending timers are stored in a queue sorted on the expiration time, where the expiration time of each timer is stored relative to the

Related work 19

previous timer in the queue. This representation makes it possible to reduce the memory requirements for storing the expiration times, making it ideal for resource constrained embedded systems. We have implemented RELTEQ within  $\mu$ C/OS-II, and showed that it also reduces the processor overhead compared to the existing timer implementation.

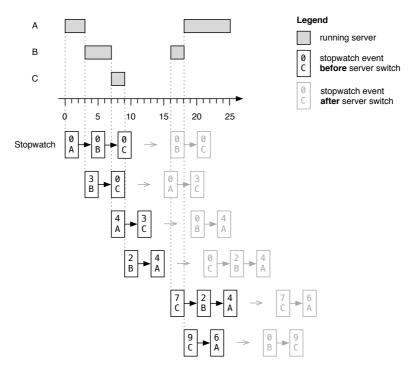

We then leverage RELTEQ to implement periodic tasks and design an efficient HSF. The proposed HSF extension of RELTEQ supports various servers (including the polling, idling-periodic, deferrable and constant-bandwidth servers), and provides access to both virtual and global timers. It supports independent development of components by separating the global and local scheduling, and allowing each server to define a dedicated scheduler. The HSF design provides a mechanism for tasks to monitor their server's remaining budget, and addresses the system overheads inherent to an HSF implementation. It provides temporal isolation and limits the interference of inactive servers on the system level. Moreover, it avoids recalculating the expiration of virtual events upon every server switch and thus reduces the worst-case scheduler overhead.

The proposed design is evaluated based on an implementation within  $\mu$ C/OS-II, a commercial operating system used in the automotive domain. The results demonstrate low overheads of the design and minimal interference between the components.

In this chapter we focus on the means for implementing a HSF. The corresponding analysis falls outside of the scope.

### **Publications**

We have introduced RELTEQ in (Holenderski et al., 2009c). In (Holenderski et al., 2010a, 2012a) we have presented an HSF extension of RELTEQ supporting fixed-priority servers. We have extended the design with the constant bandwidth server in (van den Heuvel et al., 2011), and applied it to priority processing in multimedia systems.

### 3.1 Related work

In this section we summarize the existing work related to the processor management discussed in this chapter.

### 3.1.1 Processor reservations

Resource reservations have been introduced by (Mercer et al., 1994), aiming at providing temporal isolation for individual components comprising a real-time system, to guarantee resource provisions in a system with dynamically changing resource requirements. They focused on the processor and specified the reservation budget by a tuple (C, T), with capacity C and period T. The semantics is as follows: a reservation will be allocated C units of processor time every T units of time. When a reservation

uses up all of its C processor time within a period T it is said to be *depleted*. Otherwise it is said to be *undepleted*. At the start of the period T the reservation capacity is replenished.

(Rajkumar et al., 1998) identify four ingredients for guaranteeing resource provisions:

- 1. Admission: When a reservation is requested, the system has to check if granting the reservation will not affect any timing constraints.

- 2. Scheduling: The reservations have to be scheduled on the global level, and tasks have to be scheduled within the reservations.

- 3. Accounting or monitoring: Processor usage of tasks has to be monitored and accounted to their assigned reservations.

- 4. Enforcement: A reservation, once granted, has to be enforced by preventing other components from "stealing" the granted budget.

(Rajkumar et al., 1998) aim at a uniform resource reservation model and extended the concept of processor reserves to other resources, in particular the disk bandwidth. They schedule processor reservations according to FPPS and EDF, and disk bandwidth reservations according to EDF. They extend the reservation model to (C, T, D, S, L), with capacity C, period T, deadline D, starting time S and the life-time L of resource reservation, meaning that the reservation guarantees of C, T and D start at S and terminate at S + L. Note that (Rajkumar et al., 1998) apply their uniform resource reservation model only to single-unit resources, such as processor or disk-bandwidth. They do not show how their methods can be applied to multi-unit resources, such as memory.

### 3.1.2 Hierarchical scheduling frameworks

A hierarchical scheduling framework (HSF) facilitates independent analysis and development of components, which can be integrated into a complete system based only on the information provided on their interfaces. A compositional system model is therefore critical.

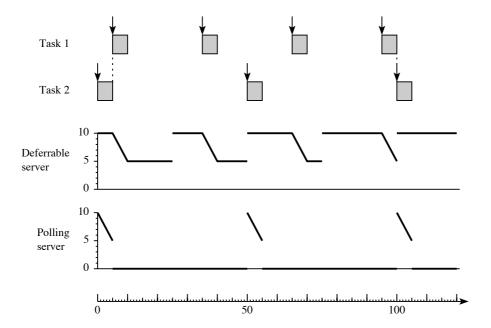

Shin and Lee (2003) introduce the periodic resource model, allowing the integration of independently analyzed components in compositional hard real-time systems. Their resource is specified by a pair  $(\Pi_i, \Theta_i)$ , where  $\Pi_i$  is its replenishment period and  $\Theta_i$  is its capacity. They also describe the schedulability analysis for a HSF based on the periodic resource model under the Earliest Deadline First and Rate Monotonic scheduling algorithms on local and global level. While the periodic-idling (Davis and Burns, 2005) and deferrable (Strosnider et al., 1995) servers conform to the periodic resource model, the polling (Lehoczky et al., 1987) server does not. The HSF presented in this chapter supports various two-level hierarchical processor scheduling mechanisms, including the polling, periodic idling, deferrable servers, and constant-bandwidth (Abeni and Buttazzo, 1998) servers. We have reported on the benefits of our constant-bandwidth server implementation in (van den Heuvel et al., 2011).

Related work 21

In this chapter we focus on the underlying timer management and illustrate it with fixed-priority servers.

Åsberg et al. (2009) make first steps towards using hierarchical scheduling in the AUTOSAR standard. They sketch what it would take to enable the integration of software components by providing temporal isolation between the AUTOSAR components. In (Nolte et al., 2009) they extend their work to systems where components share logical resources, and describe how to apply the SIRAP protocol (Behnam et al., 2007) for synchronizing access to resources shared between tasks belonging to different components. In this work we consider independent components and focus on minimizing the interference between components due to them sharing the timer management system.

### **HSF** implementations

Saewong et al. (2002) present the implementation and analysis of an HSF based on deferrable and sporadic servers using an hierarchical rate-monotonic and deadline-monotonic scheduler, as used in systems such as the Resource Kernel (Rajkumar et al., 1998).

Inam et al. (2011) present a FreeRTOS implementation of an HSF, which is based on our earlier work in (Holenderski et al., 2010a). It supports temporal isolation for fixed-priority global and local scheduling of independent tasks, including the support for the idling-periodic and deferrable servers. Their goal is to minimize the changes to the underlying OS. Consequently they rely on absolute timers provided by FreeRTOS. They do not address virtual timers. The HSF presented in this chapter relies on relative times, which allow for an efficient implementation of virtual timers. Also, our HSF implementation is modular and supports both fixed-priority as well as EDF scheduling on both global and local levels, as well as constant-bandwidth servers.

Kim et al. (2000) propose a two-level HSF called the SPIRIT  $\mu$ Kernel, which provides a separation between components by using partitions. Each partition executes a component, and uses the Fixed-Priority Scheduling (FPS) policy as a local scheduler to schedule the component's tasks. An offline schedule is used to schedule the partitions on a global level.

Behnam et al. (2008) present an implementation of a HSF based on the periodic resource model in the VxWorks operating system. They keep track of budget depletion by using separate event queues for each server in the HSF by means of absolute times. Whenever a server is activated (or switched in), an event indicating the depletion of the budget, i.e. the current time plus the remaining budget, is added to the server event queue. On preemption of a server, the remaining budget is updated according to the time passed since the last server release and the budget depletion event is removed from the server event queue. When the server's budget depletion event expires, the server is removed from the server ready queue, i.e. it will not be rescheduled until the replenishment of its budget.

Oikawa and Rajkumar (1999), describe the design and implementation of the Linux/RK, an implementation of a resource kernel (Portable RK) within the Linux kernel. They minimize the modifications to the Linux kernel by introducing a small

number of call back hooks for identifying context switches, with the remainder of the implementation residing in an independent kernel module. Linux/RK introduces the notion of a resource set, which is a set of processor reservations. Once a resource set is created, one or more processes can be attached to it to share its reservations. Although reservations are periodic, periodic tasks inside reservations are not supported. The system employs a replenishment timer for each processor reservation, and a global enforcement timer which expires when the currently running reservation runs out of budget. Whenever a reservation is switched in the enforcement timer is set to its remaining budget. Whenever a reservation is switched out, the enforcement timer is cancelled, and the remaining budget is recalculated.

AQuoSA (Palopoli et al., 2009) also provides the Linux kernel with EDF scheduling and various well-known resource reservation mechanisms, including the constant bandwidth server. Processor reservations are provided as servers, where a server can contain one or more tasks. Periodic tasks are supported by providing an API to sleep until the next period. Similar to Oikawa and Rajkumar (1999) it requires a kernel patch to provide for scheduling hooks and updates the remaining budget and the enforcement timers upon every server switch.

Faggioli et al. (2009) present an implementation of the Earliest Deadline First (EDF) and constant bandwidth servers for the Linux kernel, with support for multicore platforms. It is implemented directly into the Linux kernel. Each task is assigned a period (equal to its relative deadline) and a budget. When a task exceeds its budget, it is stopped until its next period expires and its budget is replenished. This provides temporal protection, as the task behaves like a hard reservation. Each task is assigned a timer, which is activated whenever a task is switched in, by recalculating the deadline event for the task.

Eswaran et al. (2005) describe Nano-RK, a reservation-based RTOS targeted for use in resource-constrained wireless sensor networks. It supports fixed-priority preemptive multitasking, as well as resource reservations for processor, network, sensor and energy. Only one task can be assigned to each processor reservation. Nano-RK also provides explicit support for periodic tasks, where a task can wait for its next period. Each task contains a timestamp for its next period, next replenishment and remaining budget. A one-shot timer drives the timer ISR, which (i) loops through all tasks, to update their timestamps and handle the expired events, and (ii) sets the one-shot timer to the next wakeup time.

Unlike the work presented in (Behnam et al., 2008), which implements a HSF on top of a commercial operating system, and in (Oikawa and Rajkumar, 1999; Faggioli et al., 2009; Palopoli et al., 2009), which implement reservations within Linux, our design for HSF is integrated within a RTOS targeted at embedded systems. Kim et al. (2000) describe a micro-kernel with a two-level HSF and time-triggered scheduling on the global level.

Our design aims at efficiency, in terms of memory and processor overheads, while minimizing the modifications of the underlying RTOS. Unlike Oikawa and Rajkumar (1999); Behnam et al. (2008); Palopoli et al. (2009) it avoids recalculating the expiration of local server events, such as budget depletion, upon every server switch. It also limits the interference of inactive servers on system level by deferring the handling

Related work 23

of their local events until they are switched in. While Behnam et al. (2008) present an approach for limiting interference of periodic idling servers, to the best of our knowledge, our work is the first to also cover deferrable servers.

### Monitoring

Run-time monitoring of the consumed resources is intrinsic to realizing correct implementation of the scheduling and enforcement rules. Monitoring of real-time systems can be classified as synchronous or asynchronous (Chodrow et al., 1991). In the synchronous case, a constraint (e.g worst-case execution time) is examined by the task itself. In the asynchronous case, a constraint is monitored by a separate task. The approaches in (Chodrow et al., 1991) are based on program annotations and, hence, are synchronous. In reservation-based systems, however, monitoring should be asynchronous to guarantee enforcement without relying on cooperation from tasks. Moreover, monitoring should not interfere with task execution, but should be part of the operating system or middleware that hosts the real-time application. Our HSF takes the asynchronous monitoring approach.

### 3.1.3 Timer management

The two most common ways to represent the timestamps of pending timers are: absolute timestamps are relative to a fixed point in time (e.g. January 1st, 1900), while relative timestamps are relative to a variable point in time (e.g. the last tick of a periodic timer).

In (Oikawa and Rajkumar, 1999; Palopoli et al., 2009) each timer consists of a 64-bit absolute timestamp and a 32-bit overflow counter. The timers are stored in a sorted linked list. A timer Interrupt Service Routine (ISR) checks for any expiring timers, and performs the actual enforcement, replenishment, and priority adjustments. In (Oikawa and Rajkumar, 1999) the timer ISR is driven by a one-shot high resolution timer which is programmed directly. Palopoli et al. (2009) use the Linux timer interface, and therefore their temporal granularity and latency depend on the underlying Linux kernel.

The Eswaran et al. (2005) implementation is based on the POSIX time structure timeval, with two 32-bit numbers to represent seconds/nanoseconds. The authors assume the absolute timestamp value is large enough such that it will practically not overflow.

Carlini and Buttazzo (2003) present the Implicit Circular Timers Overflow Handler (ICTOH), which is an efficient time representation of absolute deadlines in a circular time model. It assumes a periodic timer and absolute time representation. It's main contribution is handling the overflow of the time due to a fixed-size bit representation of time. It requires managing the overflow at every time comparison and is limited to timing constraints which do not exceed  $2^{n-1}$ , where n is the number of bits of the time representation. Buttazzo and Gai (2006) present an implementation of an EDF scheduler based on ICTOH for the ERIKA Enterprise kernel (Evidence, 2010) and focus on minimizing the tick handler overhead.

The  $\mu$ C/OS-II (Labrosse, 2002) real-time operating system stores timestamps relative to the current time. The timers are stored in an unordered queue. It assumes a periodic timer, and at every tick it decrements the timestamp of all pending timers. A timer expires when its timestamp reaches 0. Timestamps are represented as 16-bit integers. The lifetime of their queue is therefore  $2^{16}$  ticks.

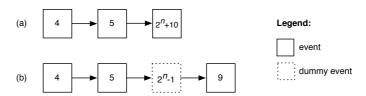

In (Holenderski et al., 2009c) we introduced the Relative Timed Event Queues (RELTEQ), which is a timed event management component targeted at embedded operating systems. It supports long event interarrival time (compared to the size of the bit representation for a single timestamp), long lifetime of the event queue, and low memory and processor overheads. By using extra "dummy" events it avoids the need to handle overflows at every comparison due to a fixed bit-length time representation, and allows to vary the size of the time representation to trade the processor overhead for handling dummy events for the memory overhead due to time representation. Similar to (Engler et al., 1995; Kim et al., 2000), our RELTEQ implementation is tick based, driven by a periodic hardware timer.

### 3.2 System model

In this section we specialize the system model presented in Chapter 2 and extend it with notions which are specific to this chapter.

### 3.2.1 Resource model

In this chapter we consider a uniprocessor platform and assume that the task or component which has access to the processor has access to the complete platform. Also, we assume no blocking between tasks and components. Hence, we have  $\mathcal{R} = \{cpu\}$ , with  $N_{cpu} = 1$ ,  $\mathcal{P} = \{cpu\}$  and  $\mathcal{N} = \emptyset$ .

### 3.2.2 Application model

In this chapter we assume a system is composed of independently developed and analyzed subsystems. A subsystem consists of a set of tasks which implement the desired application, a local scheduler, and a server. There is a one-to-one mapping between subsystems and servers.

### Servers

We consider a set of server components (or simply servers)  $\Sigma \subseteq \mathcal{C}$ , where each server  $s \in \Sigma$  is specified according to Example 2.2.

### Tasks

We assume that tasks are preemptive and independent, and that each task  $\tau_i$  is mapped to exactly one server.

System model 25

**Definition 3.1.** We define  $\gamma: \mathcal{C} \to 2^{\Gamma}$ , where  $\gamma(c)$  is the set of tasks requiring component c, i.e.

$$\gamma(c) = \{ \tau_i \in \Gamma \mid \exists \tau_{i,j} \in S_i : c \in R_{i,j} \}$$

Since we assume that each task is mapped to exactly one server, we have

$$\bigcup_{s \in \Sigma} \gamma(s) = \Gamma \wedge \bigcap_{s \in \Sigma} \gamma(s) = \emptyset.$$

(3.1)

**Definition 3.2.** We define  $\lambda : \Gamma \to 2^{\mathcal{C}}$ , where  $\lambda(\tau_i)$  is the set of components required by task  $\tau_i$ , i.e.

$$\lambda(\tau_i) = \{ c \in \mathcal{C} \mid \exists \tau_{i,j} \in S_i : c \in R_{i,j} \}$$

**Notation** We will use  $\rho(\tau_i)$  to denote the server which task  $\tau_i$  is mapped to, i.e.  $\rho(\tau_i) = s \in \Sigma \mid \tau_i \in \gamma(s)$ .

Since tasks are independent and mapped to a single server, it sufficient to model the resource requirements of each task  $\tau_i$  with a single segment  $S_i = \langle \tau_{i,1} \rangle$ , with  $E_{i,1}$  representing the worst-case execution time of  $\tau_i$ , and  $R_{i,1} = \{(cpu_{\rho(\tau_i)}, 1)\}$ , where  $cpu_{\rho(\tau_i)}$  is the virtual processor provided by server  $\rho(\tau_i)$  (see Example 2.2).

### Component states during runtime

During runtime, a component may be in one of five states: running, ready, blocked, depleted or waiting. In this section we define these states in terms of our system model.

**Definition 3.3.** We define  $\nu : \mathcal{T} \times \mathcal{R} \to \mathbb{N}$ , where

$$\nu(t,r) = N_r - \sum_{b \in S} \sigma(t,b,r)$$

is the number of units of resource r which are available at time t.

**Definition 3.4.** We define  $\alpha : \mathcal{T} \times \Gamma \to \mathcal{S}$ , where  $\alpha(t, \tau_i)$  is the segment of task  $\tau_i$  which is active at time t.

Note that  $\alpha$  is a partial function, as during the time interval between the completion of a task and its next arrival, the task will not have an active segment.

We will use  $\alpha(t, \tau_i)$  mainly for identifying the resources which are required by task  $\tau_i$  at time t.

**Definition 3.5.** We define  $R_{\alpha(t,\tau_i)}: \mathcal{T} \times \Gamma \to 2^{\mathcal{R}}$ , where  $R_{\alpha(t,\tau_i)}$  is the set of resources required by task  $\tau_i$  at time t. If  $\alpha(t,\tau_i) = \tau_{i,j}$ , then  $R_{\alpha(t,\tau_i)} = R_{i,j}$ . For those values of t for which  $\alpha(t,\tau_i)$  is not defined, we assume  $R_{\alpha(t,\tau_i)} = \emptyset$ .

**Definition 3.6.** We say that there is demand for component c at time time t, referred to by the predicate demand(t,c), iff at time t there is (i) a segment which is active and is requiring a resource provided by c, or (ii) a component which has a remaining budget and is requiring a resource provided by c, i.e.

$$demand(t,c) \equiv (\exists \tau_i \in \Gamma : R_{\alpha(t,\tau_i)} \cap P_c \neq \emptyset) \lor (\exists d \in \mathcal{C} : \beta(t,d) > 0 \land R_d \cap P_c \neq \emptyset) \quad (3.2)$$

**Definition 3.7.** A component c is said to be running at time t, referred to by the predicate running(t,c), iff at time t it is scheduled on any of its required resources<sup>1</sup>, i.e.

$$running(t,c) \equiv \exists r \in R_c : \sigma^{\mathcal{C}}(t,c,r) > 0.$$

(3.3)

**Definition 3.8.** A component c is said to be blocked at time t, referred to by the predicate blocked (t, c), iff at time t it requires a resource r which is owned by a task or component with a lower priority and there are insufficient units of r available for c, i.e.

$$blocked(t,c) \equiv \beta(t,c) > 0 \land (\exists (r,n) \in R_c : \nu(t,r) < n \land (\exists \tau_i \in \Gamma : (\sigma^{\mathcal{S}}(t,\tau_i,r) > 0 \land \pi_c < \pi_i) \lor (\exists d \in \mathcal{C} : (\sigma^{\mathcal{C}}(t,d,r) > 0 \land \pi_c < \pi_d)).$$

(3.4)

**Definition 3.9.** A component c is said to be ready at time t, referred to by the predicate ready(t,c), iff at time t it requires a resource r which is owned only by tasks or components with a higher priority and there are insufficient units of r available for c, i.e.

$$ready(t,c) \equiv \beta(t,c) > 0 \land (\exists (r,n) \in R_c : \nu(t,r) < n \land (\forall \tau_i \in \Gamma : \sigma^{\mathcal{S}}(t,\tau_i,r) > 0 \Rightarrow \pi_c > \pi_i) \land (\forall d \in \mathcal{C} : \sigma^{\mathcal{C}}(t,d,r) > 0 \Rightarrow \pi_c > \pi_d)).$$

(3.5)

**Definition 3.10.** A component c is said to be depleted at time t, referred to by the predicate depleted(t,c), iff its remaining budget has been exhausted, i.e.

$$depleted(t,c) \equiv \beta(t,c) = 0.$$

(3.6)

**Definition 3.11.** A component c is said to be waiting on demand at time t, referred to by the predicate waiting (t, c), iff at time t it has remaining budget but there is no demand for it, i.e.

$$waiting(t,c) \equiv \beta(t,c) > 0 \land \neg demand(t,c).$$

(3.7)

<sup>&</sup>lt;sup>1</sup>According to the scheduling condition 5 in Section 2.3.2, a running component will be scheduled on all of its required resources.

System model 27

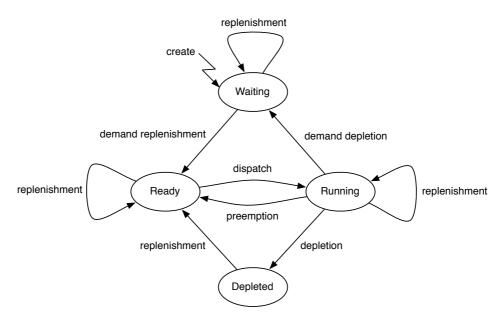

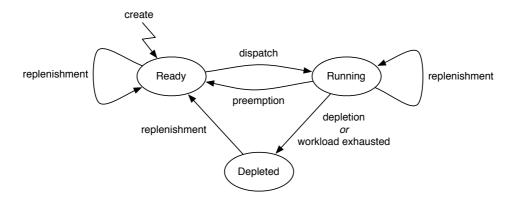

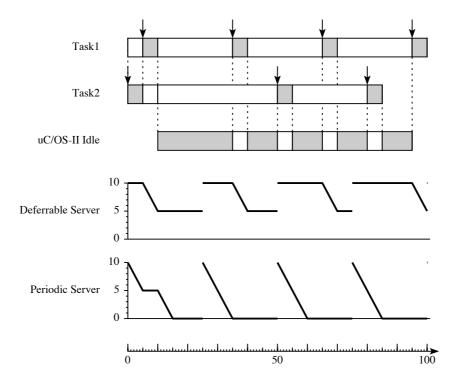

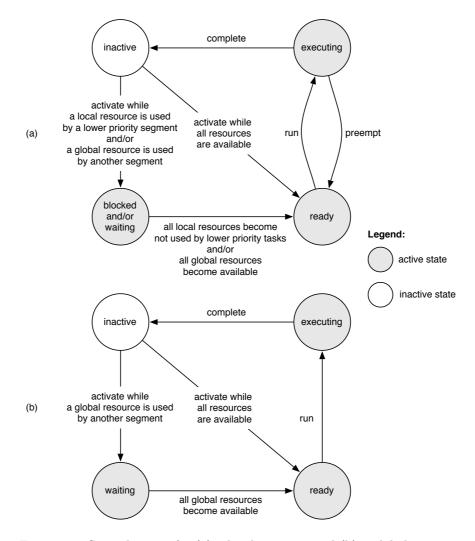

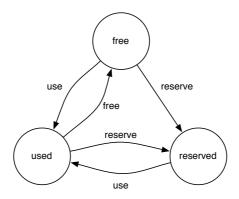

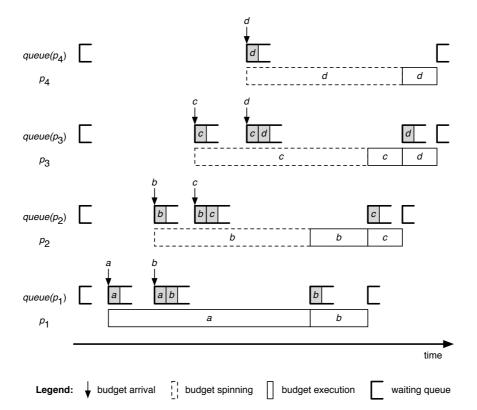

**Deferrable server** The deferrable server by Strosnider et al. (1995) is bandwidth preserving. This means that when a server is switched out because none of its tasks are ready, it will preserve its budget to handle tasks which may become ready later. A deferrable server can be in one of the states shown in Figure 3.1. A server in the running state is said to be active, and in either ready, waiting or depleted state is said to be inactive. A change from inactive to active or vice-versa is accompanied by the server being switched in or switched out, respectively.

Figure 3.1: State transition diagram for the deferrable server.

A deferrable server  $s \in \mathcal{C}$  is created in the waiting state, with its remaining budget equal to its capacity, i.e.  $\beta(O_s, s) = \Theta_i$ . As soon as there is demand for it, it moves to the ready state. When it is dispatched by the scheduler it moves to the running state. A running server s may become inactive for one of three reasons:

- It has been preempted by a higher priority server, upon which it preserves its budget and moves to the ready state.

- It has remaining budget, but none of its tasks in  $\gamma(s)$  are ready to run, upon which it preserves its budget and moves to the waiting state.

- Its budget has become depleted, upon which it moves to the depleted state.

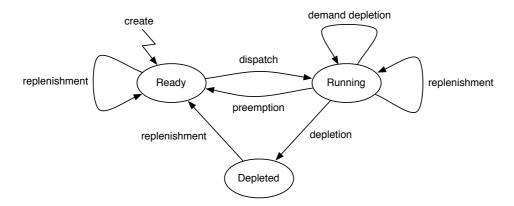

When a depleted server is replenished it moves to the ready state and becomes eligible to run. A waiting server may be woken up by a newly arrived periodic task or a delay event. Idling periodic server When the idling periodic server by Davis and Burns (2005) is replenished and none of the tasks in  $\gamma(s)$  is ready, then it idles its budget away until either a task arrives or the budget depletes. An idling periodic server follows the state transition diagram in Figure 3.2. It resembles the state transition diagram

Figure 3.2: State transition diagram for the periodic-idling server.

of a deferrable server, however, due to its idling nature the periodic-idling server will never reach the waiting state. The idling property can be regarded as artificial demand for it when there is no proper demand from its tasks.

**Polling server** The polling server by Lehoczky et al. (1987) is not bandwidth preserving. Therefore, when it is replenished and none of the tasks in  $\gamma(s)$  is ready, or when its workload is exhausted, then its budget is immediately depleted.

A polling server can be in one of three states, shown in Figure 3.3. The difference

Figure 3.3: State transition diagram for the polling server.

between a polling and a deferrable server lies in what happens when the workload of

RELTEQ 29

a running server is exhausted. Rather than moving to the waiting state (and thus preserving its budget), the polling server discards any remaining budget and moves to the depleted state.

### Hierarchical scheduling

In two-level hierarchical scheduling one can identify a global scheduler which is responsible for selecting a server component. The server is then free to use any local scheduler to select a task to run.

In order to facilitate the reuse of existing server components when integrating them to form larger systems, the platform should support (at least) fixed-priority preemptive scheduling at the local level within servers (since it is a de-facto standard in the industry). To give the system designer the most freedom it should support arbitrary schedulers at the global level. In this chapter we will focus on a fixed-priority scheduler on both local and global level.

### Timed events

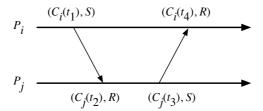

The platform needs to support at least the following timed events: task delay, arrival of a periodic task, server replenishment and server depletion, which are generated by the timer handler.

Events local to server s, such as the arrival of periodic tasks in  $\gamma(s)$ , should not interfere with other servers, unless they wake a server, i.e. the time required to handle them should be accounted to s, rather than the currently running server. In particular, handling the events local to inactive servers should not interfere with the currently active server and should be deferred until the corresponding server is switched in.

### 3.3 RELTEQ