# Enhanced applicability of loop transformations

Citation for published version (APA):

Palkovic, M. (2007). Enhanced applicability of loop transformations. [Phd Thesis 2 (Research NOT TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR629342

DOI:

10.6100/IR629342

Document status and date:

Published: 01/01/2007

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 04. Oct. 2023

# Enhanced Applicability of Loop Transformations

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr.ir. C.J. van Duijn, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op maandag 24 september 2007 om 16.00 uur

door

Martin Palkovič

geboren te Bratislava, Slowakije

Dit proefschrift is goedgekeurd door de promotoren:

prof.dr. H. Corporaal en prof.dr.ir. F. Catthoor

This work was carried out at IMEC.

#### © Copyright 2007 M. Palkovič

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission from the copyright owner.

Cover design: Martin Palkovič Printed by: PROCOPIA nv

#### CIP-DATA LIBRARY TECHNISCHE UNIVERSITEIT EINDHOVEN

Palkovič, Martin

Enhanced applicability of loop transformations / by Martin Palkovič. – Eindhoven : Technische Universiteit Eindhoven, 2007.

Proefschrift. - ISBN 978-90-386-1584-4

NUR 959

Trefw.: ingebedde systemen / dataopslag / compilers ; optimalisering / real-time computers ; toepassingen.

Subject headings: embedded systems / storage management / optimising compilers / Pareto optimisation.

# Acknowledgements

La reconnaissance est la mémoire du coeur. Jean Baptiste Massieu (1743-1818)

Then reaching a milestone in your life, which a PhD certainly is, you should look back in time and acknowledge people who have been important to you and have contributed to your personal and professional growth. Maybe returning to your childhood is a little bit too far, but perhaps somewhere, in 1986, at elementary school, trying to write my first programs in BASIC using the PMD-85 computer (MHB 8080A 2.048MHz CPU, 48kB RAM and 4kB ROM), there was the beginning of what I am trying to finish now. Two years after my first programs, my parents bought me my first computer, an ATARI 800 XE, so I could continue my programming experiments at home. I realize now that at that time it cost a few times their monthly salaries, and maybe they do not yet realize how grateful for that I was and still am. Next to that, I also had excellent math and physics teachers at elementary school, who encouraged my further interest in those subjects and technology in general.

Later at comprehensive school, I specialized in mathematics, physics and informatics. I also met great teachers there who supported me in my interests and enriched my professional growth. I would like to express my gratitude to all of them. In the early 90's, when the Coordinating Committee for Multilateral Export Controls (CoCom) became obsolete, the first computers based on the Intel 80286 and 80386 appeared in Czechoslovakia (with some delay, because at that time the Intel 80486 was already available in the U.S.). I believe I still have still a leaflet from the shop with the price for a 286 machine at home. It was more than 120.000 Czechoslovak koruna's at that time, which is roughly 5000 USD when using exchange rates for the Czechoslovak koruna of 1990. Fortunately, those machines were available at the Technology club (T-club) of the Faculty of Electrical Engineering at the Slovak University of Technology, which I intended to became my "alma mater" anyhow. And (again thanks to my parents) I chose a cheaper but still relatively good Amiga 500 for home usage.

I believe I experienced the best times of my student life when I was enrolled at the Faculty of Electrical Engineering and Information Technology of the Slovak Univer-

sity of Technology. It was a pleasure for me to study all those interesting subjects of technology and I believe the teachers there did a very good job, for which I am really grateful. Here, I also have to thank my father, who "forced" me to study International Economics in parallel at the University of Economics. These studies gave an extra dimension to my vision of the world. After the third year at university, I felt that I would like to apply the theory I had learned in a practical working environment and gain some experience abroad. Thanks to the International Association for the Exchange for Students for Technical Experience (IAESTE) I spent two wonderful summer months in Aachen working in the motivating environment of the Zentrallabor für Elektronik in Forchungszentrum Jülich, Germany. I am thankful to all my colleagues there for all the interesting discussions. Encouraged by the positive experience, after the fourth year of my studies I also looked for a summer internship abroad. From Prof. Daniel Donoval I heard about the Inter-University Micro-Electronics Center (IMEC), where some of the PhD students from our Department of Microelectronics were already doing their research. Thus, I asked him if it would be possible to visit IMEC as an undergraduate student for a summer internship, with the potential to return there the following year for a master's thesis if IMEC was interested. The answer from IMEC was positive and so I came to Leuven, Belgium, in 1999.

After doing the summer internship at IMEC, I returned one year later for my master's thesis. I have to express my gratitude to Miguel Miranda and Arnout Vandecappelle who made my first days and years at IMEC much easier. Also I have to thank Miguel Miranda for the daily guidance during my master's thesis and Prof. Francky Catthoor for all the discussions and feedback during those days.

After finishing my master's thesis I got the opportunity to stay at IMEC as an employee working on the Data Transfer and Storage Exploration (DTSE) methodology, in particular the Global Loop Transformations (GLT) step. Even though the Geometrical Model (GM) used by this step was powerful and the transformations were easily expressible I believed it had severe limitations. This belief became even stronger after my return from my three week visit to Tanguy Risset's Compsys group at ENS Lyon, France, in 2003. Thus, my main task at IMEC was to discover how to apply the techniques based on GM to realistic applications. The result of this research is the dissertation you are now reading. Of course, it would not have happened without the help and support of my colleagues at IMEC and cooperating universities, the responsible persons at TU/e and IMEC who allowed me to became a PhD candidate and the support of my two promotors, Prof. Henk Corporaal and Prof. Francky Catthoor.

At IMEC I have many people to thank and even those who are not mentioned by name know they deserve my gratitude. Erik Brockmeyer, Rogier Baert, Arnout Vandecappelle, Vincent Nollet, Eddy De Greef, Sven Wuytack, and Robo Paško, are just a few who helped me in my daily work. Also Michel Eyckmans for being my activity lead. It has been a pleasure. I would also like to mention Diederik Verkest, Johan Vounckx, and Wilfried Verachtert for making this research possible.

At cooperating Universities I have to thank Sven Verdoolaege (at that time from the Katholieke Universiteit of Leuven, now at the Universiteit of Leiden, the Netherlands) for very interesting discussions about GLT and GM and all the help with his toolchain; Per Gunnar Kjeldsberg and his PhD student Qubo Hu from the Nor-

wegian University of Science and Technology in Trondheim, Norway and Benny Thörnberg from the Mid-Sweden University, Sundsvall, Sweden, for very intensive and fruitful cooperation in the field of high-level memory estimators; Valentin Stefan Gheorghita from the Technische Universiteit Eindhoven for enthusiasm and cooperation in scenario research and many others from the Computer Science Department at the Katholieke Universiteit of Leuven and the Electronics and Information System Department at Ghent University.

I would like to express my appreciation to Erik Brockmeyer for sharing an office with me for more than 6 years and all the discussions, professional or non-professional, we had during those years.

Special thanks go to my two promotors, Prof. Henk Corporaal and Prof. Francky Catthoor for all the discussions, support and feedback during my research and during the writing of this dissertation. Also special thanks to Prof. Koen De Bosschere, Twan Basten and Albert Cohen for being members of my reading committee and for the final feedback, which certainly improved the quality of this text.

Special thanks also to Sven Verdoolaege for reading the whole text, for his detailed feedback and for all the interesting discussions during my research; Eddy De Greef for reading the conclusions section, its translation to Dutch, and for his patience when explaining the ATOMIUM library internals to me; Andrew Fort for proof-reading some parts of this dissertation and Tom Ashby for proof-reading the summary and these acknowledgments.

Life is not only work, and thus I would like to thank people who were part of my social life here in Leuven; Théodore Marescaux, for being not only a good colleague but also a good friend hanging around since 1999; Radim Cmar, Miro Čupák, Petr Dobrovolný, Štefan Kubiček, Robo Paško, and Rišo Stahl for all the coffee breaks and professional help at work; The previous, Soňa Pallayová and their families for creating a small home for me here in Leuven, sharing time outside work with me and always being helpful when I needed it; Prof. Francky Catthoor for all the excellent prepared bike and cross-country skiing trips and for showing me that Belgium can indeed be hilly and that during winter you can find 60 cm of snow if you go to the right places.

Finally, I would like to thank again (and again) my parents for much more than is written in this text, for their love, understanding and all their support during my student years. The same gratitude goes also to my two great sisters, Helena and Soňa, and my beloved Jana. Without them, life would not be as beautiful and fun as it is.

Martin Palkovič Leuven, July 2007.

# **Enhanced Applicability of Loop Transformations**

Summary

ata transfers and storage of large arrays in background memories are dominating contributors to the chip area and power consumption of all modern multimedia embedded systems. Modern high-level memory optimizations contribute to the cost-efficient realization of these systems. In these optimizations an important step involves loop transformations across the global program scope. These transformations can be performed on a geometrical model extracted from the program. The geometrical model captures all the memory access dependencies in the program. Loop transformations in general modify the order in which the iterations and statements within a loop body are executed. This could be beneficial for different reasons such as enabling more parallelism or improving locality of the accessed data.

Due to the limitations of current geometrical models, the applicability of the transformations is limited. In this dissertation, we propose several applicability-enhancing techniques for loop transformations. First, hierarchical rewriting separates and encapsulates the details of the application into functions, reducing the complexity of the problem by hiding undesired constructs.

Second, we instantiate and extend the scenario technique for loop transformations. A scenario is defined as a selected set of paths in the program which we choose to exploit in the same way. A careful exploitation of scenario information, similar to inlining, path predication or hyperblock creation, can significantly enlarge the exploration space for optimizations. Unlike path predication or inlining, however it can work across several conditional branches, merge several condition bodies, and still control the exponential code explosion. Applying scenarios introduces several tradeoffs. The most obvious is that of code duplication vs. more optimizations (similar to tail duplication during hyperblock creation) when additional loop transformations are enabled by scenario usage.

The exploration space of the scenario creation technique grows exponentially with the number of paths in the control-flow graph of the application. In this dissertation we propose several heuristics for the scenario creation technique. These heuristics have different time requirements and accuracy limitations. Thus the designer has the possibility to choose the heuristic based on his time and accuracy constraints and the size of the problem.

In addition, most current (global scope) loop optimizations target the best solution for locality. In this dissertation we show that targeting the best solution for locality is not necessarily optimal for a particular platform instance, and that trade-offs should be involved during loop transformations when the platform is unknown. This dissertation provides real-life examples of trade-offs during loop transformations and gives an overview of the joint research work in high-lever estimators for loop transformations which will make the loop transformations trade-off oriented.

# Contents

| A  | cknov | wledgements                            | i   |

|----|-------|----------------------------------------|-----|

| Sι | ımma  | nry                                    | v   |

| Ta | ble o | f contents                             | vii |

| 1  | Intr  | oduction                               | 1   |

|    | 1.1   | Application domain description         | 2   |

|    | 1.2   | The platform description               | 4   |

|    | 1.3   | Mapping problem                        | 6   |

|    |       | 1.3.1 Optimizing compiler              | 7   |

|    |       | 1.3.2 High-level mapping techniques    | 9   |

|    | 1.4   | Problem statement and objective        | 10  |

|    | 1.5   | Solution on an illustrative example    | 11  |

|    | 1.6   | Thesis contributions                   | 13  |

|    | 1.7   | Thesis overview                        | 15  |

| 2  | The   | DTSE methodology                       | 17  |

|    | 2.1   | Platform independent steps             | 18  |

|    | 2.2   | Platform dependent steps               | 22  |

|    | 2.3   | Other related methodologies and stages | 24  |

|    | 2.4   | Open issues                            | 26  |

| 3  | Glo   | bal loop transformations               | 27  |

|    | 3.1   | GM and its limitations                 | 28  |

|    | 3.2   | Loop transformation tool               | 31  |

|    | 3.3   | Preprocessing for GLT                  | 32  |

|    | 3.4   | GM extractors                          | 35  |

|    | 3.5   | Array dependency analysis tool         | 36  |

viii Contents

|   | 3.6  | Transf  | ormations on the GM                                        | . 40 |

|---|------|---------|------------------------------------------------------------|------|

|   | 3.7  | GM sc   | anner                                                      | . 42 |

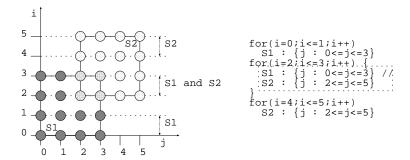

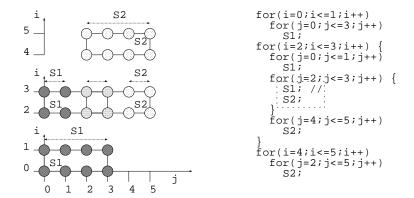

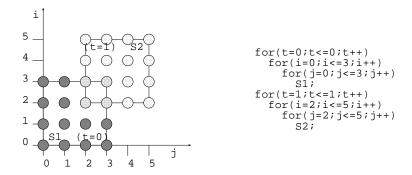

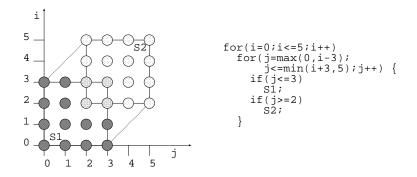

|   |      | 3.7.1   | Quilleré et al. algorithm                                  | . 43 |

|   |      | 3.7.2   | Scanning with the time dimensions                          |      |

|   |      | 3.7.3   | Scanning for compact code                                  | . 45 |

|   | 3.8  | Postpr  | ocessing                                                   | . 46 |

|   | 3.9  | Open i  | issues                                                     | . 46 |

| 4 | Prep | rocessi | ng for innermost conditions                                | 49   |

|   | 4.1  | Proble  | m definition                                               | . 50 |

|   | 4.2  | Hierar  | chical rewriting                                           | . 52 |

|   |      | 4.2.1   | Moving data dependent conditions to innermost loops        | . 53 |

|   |      | 4.2.2   | Rewriting the innermost if conditions to ternary operators | . 54 |

|   |      | 4.2.3   | Encapsulation of if-converted basic blocks                 | . 57 |

|   | 4.3  | Result  | s                                                          | . 60 |

|   | 4.4  | Conclu  | asions                                                     | . 61 |

| 5 | Prep | rocessi | ng for outermost conditions                                | 63   |

|   | 5.1  |         | m definition                                               | . 64 |

|   | 5.2  |         | GM model                                                   |      |

|   | 5.3  | Synthe  | etic graphs                                                | . 67 |

|   | 5.4  | ,       | fe graphs                                                  |      |

|   | 5.5  |         | arus path profiling in DAG                                 |      |

|   | 5.6  |         | rio technique                                              |      |

|   |      | 5.6.1   | Dividing the CFG into CFsGs                                |      |

|   |      | 5.6.2   | Cost: Instruction memory size increase                     |      |

|   |      | 5.6.3   | Gain: Data memory size decrease                            |      |

|   |      | 5.6.4   | Trading-off instruction vs. data memory size               |      |

|   | 5.7  | Prunir  | ng the exploration space and heuristics                    |      |

|   |      | 5.7.1   | Selecting the most frequent paths                          | . 84 |

|   |      | 5.7.2   | Coverage criterion heuristic                               |      |

|   |      | 5.7.3   | Loss/Similarity heuristic                                  | . 84 |

|   |      | 5.7.4   | Heuristic based on Fruchterman-Reingold layout             |      |

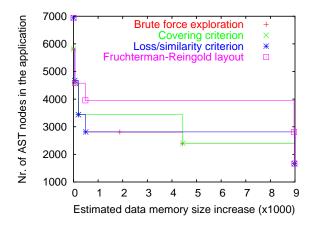

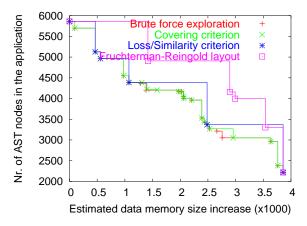

|   |      | 5.7.5   | Results                                                    | . 87 |

|   | 5.8  | Code 8  | generation and results                                     | . 91 |

|   | 5.9  | Dealin  | g with while loops                                         | . 94 |

|   |      | 5.9.1   | Profiling of the loops with varying trip count             |      |

|   |      | 5.9.2   | Scenario technique for loops with varying trip count       |      |

|   | 5.10 | Switch  | ing cost                                                   |      |

|   |      |         | Description of the profiling algorithm                     |      |

|   |      |         | Minimal switching activity scenarios                       |      |

|   |      |         | - · · · · · · · · · · · · · · · · · · ·                    |      |

| C        | •  |

|----------|----|

| Contents | 1V |

| Contents | 13 |

|                              | 5.11                                            | Conclusions                                                  | 107 |  |  |

|------------------------------|-------------------------------------------------|--------------------------------------------------------------|-----|--|--|

| 6                            | Trade-offs in the GLT                           |                                                              |     |  |  |

|                              | 6.1                                             | 1 Problem definition                                         |     |  |  |

|                              | 6.2                                             |                                                              |     |  |  |

|                              |                                                 | 6.2.1 Intra in-place vs. inter in-place                      |     |  |  |

|                              |                                                 | 6.2.2 Intra in-place vs. data reuse                          |     |  |  |

|                              |                                                 | 6.2.3 Intra in-place vs. control flow complexity             |     |  |  |

|                              |                                                 | 6.2.4 Intra in-place vs. ILP trade-off (for parallelization) |     |  |  |

|                              |                                                 | 6.2.5 Code size vs. code complexity                          |     |  |  |

|                              | 6.3                                             | GLT trade-off cost components                                |     |  |  |

|                              | 6.4                                             | Case study and results                                       |     |  |  |

|                              |                                                 | 6.4.1 Intra in-place vs. inter in-place                      |     |  |  |

|                              |                                                 | 6.4.2 Intra in-place vs. data reuse                          |     |  |  |

|                              |                                                 | 6.4.3 Data reuse vs. control flow complexity                 |     |  |  |

|                              |                                                 | 6.4.4 Intra in-place vs. control flow complexity             |     |  |  |

|                              |                                                 | 6.4.5 Combination of trade-offs                              |     |  |  |

|                              |                                                 | 6.4.6 Evaluation on ARM platform                             | 132 |  |  |

|                              | 6.5                                             | High-level estimators                                        | 134 |  |  |

|                              |                                                 | 6.5.1 STOREQ high-level estimator and the GLT engine         | 135 |  |  |

|                              |                                                 | 6.5.2 Hierarchical memory storage estimation and the GLT     | 137 |  |  |

|                              | 6.6                                             | Algorithmic kernel optimisations and GLT                     | 139 |  |  |

|                              | 6.7                                             | Conclusions                                                  | 144 |  |  |

| 7                            | Rela                                            | ted work                                                     | 145 |  |  |

|                              | 7.1 Hierarchical rewriting and condition hiding |                                                              | 145 |  |  |

|                              | 7.2                                             | Scenarios                                                    | 146 |  |  |

|                              | 7.3                                             | Loop transformations                                         | 149 |  |  |

| 8                            | Con                                             | clusions and future work                                     | 155 |  |  |

|                              | 8.1                                             | Summary and conclusions                                      | 155 |  |  |

|                              | 8.2                                             | Directions of future research                                | 157 |  |  |

| A                            | Test                                            | vehicle applications                                         | 161 |  |  |

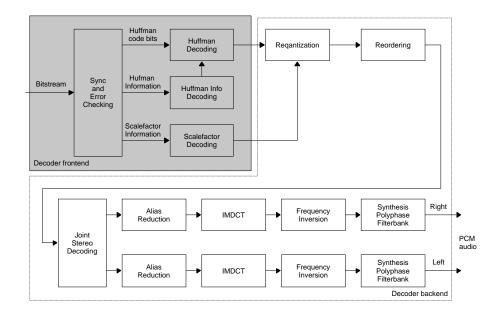

|                              |                                                 | MP3 audio decoder                                            |     |  |  |

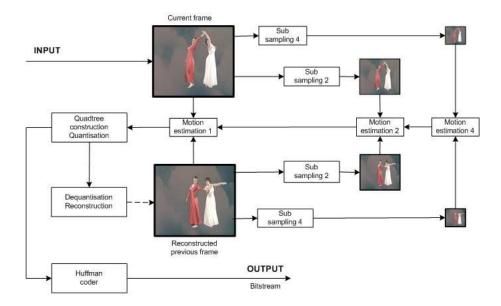

|                              | A.2                                             | QSDPCM video encoder                                         | 162 |  |  |

| Nederlandse samenvatting 165 |                                                 |                                                              |     |  |  |

| Bibliography 169             |                                                 |                                                              |     |  |  |

| List of publications 181     |                                                 |                                                              |     |  |  |

| x                | Contents |

|------------------|----------|

| Acronyms         | 183      |

| Curriculum vitae | 187      |

# CHAPTER 1

### Introduction

Nil tam difficile est quin quaerendo investigari possiet.

Publius Afer Terentius

(185BC-159BC)

owadays, electronic devices are ubiquitous in the world around us. An electronic device can be found nearly in any gadget we take in our hands these days. Handheld devices such as mobile phones, smart phones, handheld television, personal digital assistants (PDA)s and global positioning system (GPS) devices are working in urban areas, on the countryside, when traveling by car at 120 km/h or walking slowly 4km/h. The capturing devices such as digital cameras support different resolutions and can capture and encode both, slowly and rapidly moving objects.

These devices have to work independently on the environment, e.g., urban areas or the countryside, 120km/h or 4km/h, in which they are present. This results in the existence of a lot of different standards which are suited for different environments and have to be integrated into one device. Embedded programmable processors, whose software can be changed, aim to be cost effective and flexible solution for current challenges compared to traditional hardware-only approach using Application Specific Integrated Circuit (ASIC)s. They should be also much more power and performance effective for a given application domain compared to general purpose processors.

The specification of an application for embedded programmable processor is usually written in a high-level programming language. In the past the application was directly hand-written in the machine language or translated directly from a high-level language using a standard compiler. Nowadays, the strict development time constraints due to decreased time to market does not allow to hand-write the machine code. Unfortunately, current compilers do not produce machine code with the same quality as hand-written machine language.

2 Introduction

To bridge the gap between high-quality hand-written machine language and code produced by the compiler source-to-source transformations exist. They perform high-level optimizations improving the quality of the source code resulting also in more power and performance effective translated code.

An important part of these high-level optimizations are Loop Transformations (LT). However, these transformations are not always applicable in the context of modern embedded systems with a lot of control-flow and trade-offs involved. This dissertation aims at solving the applicability problem of LT. It proposes three independent techniques enhancing the applicability of LT in the context of modern embedded systems. The synergetic effect can be achieved by combining these techniques.

This chapter provides an introduction to the application domain targeted in this dissertation, the embedded system virtual platform used, and challenges in current source-to-source transformation techniques. Section 1.1 presents the application domain description. Section 1.2 discusses the embedded system platform description focusing on the memory hierarchy subsystem. Section 1.3 introduces the design flow used in this dissertation. Then it defines the problem statement and objective and the contributions of this dissertation, all supported by an illustrative example. At the end of this chapter a thesis overview is provided.

# 1.1 Application domain description

The main application target domain of this dissertation consists of embedded data-dominated applications, i.e., applications which deal with large amounts of data and data transfers. We can subdivide this target domain into three classes: multimedia applications, front-end telecommunication applications and network component applications [28]. In this dissertation we focus on multimedia applications which have the following main features [28]:

- Deep and large loop nests. Multimedia applications typically contain many deep and large loop nests for processing the multidimensional data. Due to the rectangular shape of images and video streams, the loop bounds are often constant or manifest, i.e., only dependent on the enclosing loop iterators. The loops are typically quite irregularly nested though.

- Mostly manifest affine loop bounds, conditions and array indices. Manifest means that they are a function of the enclosing loop iterators only. Affine means that this function is a linear combination of these loop iterators and a constant. However, more and more recent multimedia applications also contain data dependent conditions and indexing, and while loops. This is not reflected in the state-of-the-art design methodologies for multimedia applications and it is one of the major topics of this dissertation.

- Multidimensional arrays. Multimedia applications mainly work on multidimensional arrays of data. Also large one-dimensional arrays are often encountered. Often, the multidimensional arrays are already linearized to a one-dimensional array.

- Statically allocated data. Most data is statically allocated. Its exact storage location can be optimized at compile time. Also this is starting to change, especially in emerging newer multimedia algorithms. These new algorithms have, besides of the data that is statically allocated, i.e., the data which is analyzable at design time, also the data that is dynamically allocated at run time. This results in the mixed case where both, statically and dynamically allocated data are within a single application. However, the mixed case is a topic of future research and it is not covered in this dissertation. We only deal with the pieces of the code that have fully statically allocated data.

- Temporary data. Most of the data is temporary, only alive during one or at

most a few iterations of the algorithm. When the data is not alive anymore, the

memory space where it was located can be reused and it can be overwritten by

other data.

- Real-time behavior with a form of periodic behavior. Multimedia applications typically have to satisfy soft real-time constraints. They encode or decode the input image stored in multidimensional arrays in the time loop. A time loop is a loop within which a video or audio frame is encoded or decoded. The time loop starts when the first frame is encoded/decoded and ends when the last frame is encoded/decoded. Its loop trip count depends on the number of frames in the encoded/decoded sequence. This designates the application to have a form of periodic behavior.

To demonstrate the described features on real-life applications, in the sequel we briefly describe the structure and code characteristics w.r.t. the list above of two multimedia algorithms, an MPEG-1 Layer 3 (MP3) audio decoder and a Quadtree Structured Difference Pulse Code Modulation (QSDPCM) video encoder. These applications are used in most of our experiments and also give a good overview of the typical applications in the multimedia domain representing both, the audio and the video part. The functional description of these applications is shown in Appendix A.

The MP3 audio decoder application has real-time periodic behavior. It receives a decoded audio frame and decodes it until no frame is present at the input. The frame is decoded in several steps. Each step is composed of a nested loop (or several non-perfectly nested loops) with maximum loop nest depth of 5. The iteration count for the loops is in hundreds of iterations. The loop bounds and array indices are mostly manifest and affine. Typical for this application are a lot of non-manifest outermost data-dependent conditions. We will provide a technique to deal with them in this dissertation in Chapter 5. The application uses three-dimensional arrays and a lot of temporary data storing the frame between the two subsequent processing steps of the decoder.

The QSDPCM video encoder reads input video frames and encodes them using the information from the previous video frame. It also has real-time periodic behavior and encodes the frame in several steps. Each step is again composed of a nested loop (or several non-perfectly nested loops) with a maximum loop nest depth of 8. The iteration count depends on the size of the frame, but for a frame it is again in the hundreds to thousands of iterations. The loop bounds and array indices are mostly manifest and affine. Typical for this application are a lot of non-manifest

Introduction

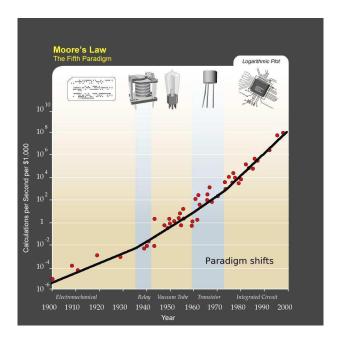

**Figure 1.1:** Kurzweil's expansion of Moore's Law shows that due to paradigm shifts the underlying trend holds true from integrated circuits to earlier transistors, vacuum tubes, relays and electromechanical computers.

*innermost data-dependent conditions*. We will provide a technique to deal with them in this dissertation in Chapter 4. The application uses two-dimensional arrays and a lot of temporary data storing the frame between the two subsequent processing steps of the decoder.

# 1.2 The platform description

The programmable microprocessor architectures proposed in [216] and starting in the 1971 with the Intel 4004, came a long way in the past 35 years. The number of transistors on an integrated circuit has grown from 2300 in the year 1971 to more than  $5 \times 10^8$ . The growth follows Moore's law, i.e., that the transistor density of integrated circuits, with respect to minimum component cost, doubles every 24 months [239]. The performance of the microprocessors follows this trend and improved 35% per year until 1986, and 55% per year since 1987 [99]. This increase is due to different factors. In the past a constant improvement was given by increasing the clock rate. In addition, the introduction of instruction pipelining when going from a Complex Instruction Set Computer (CISC) to Reduced Instruction Set Computer (RISC) and exploiting the Instruction Level Parallelism (ILP) for superscalars and Very Long Instruction Word (VLIW) caused further improvement in the performance measured

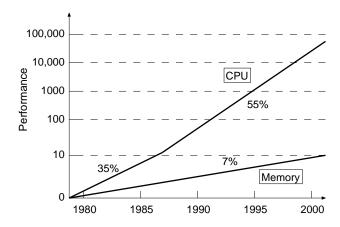

Figure 1.2: The memory gap [99].

as useful work (or instructions) executed per unit time. Nowadays, the clock rate hardly raises. Higher clock speeds may increase the temperature to unacceptable limits. In addition the clock speeds are affected by the scaling problems of wires. Thus, it becomes almost impossible to produce a Central Processing Unit (CPU) that runs reliably at speeds higher than 4.3 GHz or so [239]. Further performance improvements are achieved by using larger caches in the new processors, more functional units [146, 147], and multiple computing cores.

Integrated circuits with the corresponding Moore's Law were not the first computing paradigm. Computing devices have been consistently accelerating price-performance from the *mechanical calculating devices* used in the 1890 US Census, to Turing's *relay-based* "Robinson" *machine* that cracked the Nazi enigma code, to the CBS *vacuum tube computer* that predicted the election of Eisenhower, to the *transistor-based machines* used in the first space launches, to the *integrated-circuit-based personal computers* [131]. This is demonstrated in Figure 1.1 where each paradigm shift caused a further growth of the slope.

Not all aspects of computing technology develop in size and speed according to Moore's Law. Random Access Memory (RAM) speeds and hard drive seek times improve on average 7% each year [99]. This opens the gap between the CPU performance increased so far with 55%/year and the memory performance increase limited to 7%/year. This memory gap is depicted in Figure 1.2. The gap is now so big that it is being referred to as the "memory wall" [220]. Despite the use of advanced memory subsystems during the last 15 years, the "memory wall" is still present [144]. Thus, an intelligent use of the structure and capacity of the memory subsystem by advanced compilation and source-to-source transformation techniques becomes more and more important.

The productivity of software developers most assuredly does not increase exponentially with improvements in hardware, but by most measures has increased only slowly and fitfully over the decades. Software tends to get larger and more complicated over time requiring automated tools helping the designer to manage the increased complexity of the design process.

6 Introduction

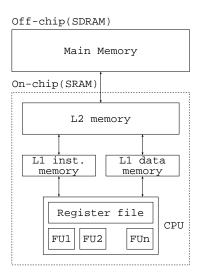

Figure 1.3: A general platform architecture used in this dissertation.

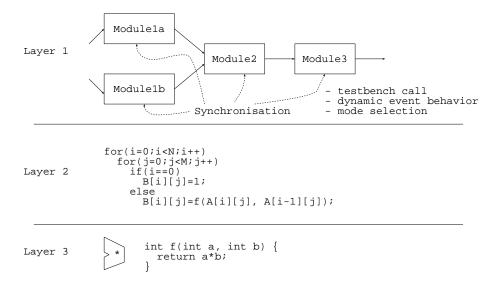

In this dissertation, we focus on the combination of the "memory gap" issue [215] and the software productivity issue. To deal with these issues at a high-level of abstraction, we do not need a concrete instance of a platform. The platform used should have a CPU, at least one level of on-chip memory and an external off-chip main memory. Such a platform architecture with two levels of on-chip memory is depicted in Figure 1.3 and it is a general abstraction of current state-of-the art multimedia platforms. The CPU data-path in the platform has multiple functional units which can be scheduled in hardware (superscalar) or in software (VLIW). The program is stored in the instruction memory and the data is stored in the data memory. The memory subsystem has several layers, at least one resides on-chip and one resides off-chip. The memory is software controlled. However, hardware controlled caches are also allowed in the platform and are used when software control is not possible due to too much unpredictability in the application. Such an abstraction of the platform was already used in previous work dealing with the "memory" gap problem, e.g., [130, 44].

# 1.3 Mapping problem

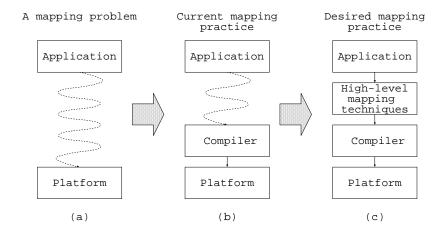

The mapping problem is depicted in Figure 1.4a. We have an application as described in Section 1.1 and we have a platform as described in Section 1.2. Our goal is to translate the application specification, described in a high-level language, to the machine language, achieving low energy and very good performance. To achieve this goal, modern (optimizing) compilers are used to translate the high-level language description to the machine language as depicted in Figure 1.4b. However, the resulting machine code is still far from hand-written machine code w.r.t. energy consumption and/or performance. To improve the result of the compiler, source-to-source transformation frameworks are used as depicted in Figure 1.4c. In Subsec-

Figure 1.4: A mapping problem.

tion 1.3.1, we introduce the state-of-the-art in the compilation process. In Subsection 1.3.2, we introduce the missing compiler optimizations that are covered by the high-level source-to-source transformation frameworks where the description of the algorithm remains in the same language. However, after the compilation process better results are achieved w.r.t. the energy and performance compared to directly compiling the initial specification. (see Figure 1.4c). The introduction to the source to source optimizations is in Subsection 1.3.2. This dissertation targets research in the area of those source-to-source transformations.

#### 1.3.1 Optimizing compiler

The goal of the compiler is to translate the description in the high-level language to the machine language. This is done in several phases of the compilation process. In the front-end of the compiler, the high-level language is translated into a platform independent internal representation. This representation usually has the form of an Abstract Syntax Tree (AST). In the middle-end of the compiler, this representation is transformed to a platform dependent representation. This representation is referred to as a Register Transfer Language (RTL). In the back-end of the compiler, the assembly code is generated from the RTL description.

The output of a compiler should be, in the ideal case, of equal quality to hand-written assembly/machine code. This is rarely achieved. However, the code that is produced by compiling can be made to run faster, to take less space and to consume less power by applying program transformations, commonly called optimizations. Code optimization can take place at many levels, ranging from the algorithmic level down to the assembly level. Higher level optimizations produce more dramatic results, but lower level ones treat and exploit the target machine idiosyncrasies.

Compiler optimizations fall into two general categories: platform independent and platform dependent. The platform independent optimizations are performed on the platform independent internal representation. At this level, the compiler can improve loops, address references, etc. The platform dependent optimizations, that

8 Introduction

include register allocation and utilization of machine idioms, are performed on the platform dependent internal representation and can be largely embedded in the code generation process. At this level, the compiler uses the machine specific information to make good use of the machine resources and idioms.

For the embedded software domain we target, the optimizations performed have to be even more advanced than for the general-purpose domain. This is necessary, because only a small overhead of compiled code versus hand-written assembly code is generally acceptable in the embedded compiler community. With the advent of more sophisticated code optimization technology [135] the overhead of compiled code versus hand-written assembly code has been reduced compared to the past. These novel code optimization methodologies have high runtime requirements. However, in embedded code generation, higher compilation times are acceptable, which may lead to a paradigm shift in code optimization technology. Also, in the embedded domain, the detailed characteristics of the target machines are taken into account resulting in tight development of the compiler with the target architecture [233, 235].

The different optimizations are applied within different optimization passes during the compilation. Nowadays, compilers can have a large number of those passes. E.g., the gcc compiler framework contains 127 possible optimization passes and approximately the same amount of parameters to control the amount of optimization to be performed [232]. Those different passes interact together. This causes synergy in a positive, but unfortunately, also in a negative way. The positive effect is when one pass is enabling more freedom for the second pass, e.g., the loop unrolling enables better instruction scheduling. The negative effect is when one pass limits the freedom for another pass or one pass eliminates the effect of other passes, e.g., the loop unrolling limits the freedom for other high-level loop optimizations like interchange and fusion. We foresee this as a big problem also w.r.t. the optimizations on different levels. Recently, adaptive compilation has been proposed, where the optimization passes are selected and tailored to the compiled application [40]. A similar approach is iterative compilation [124, 125, 83, 97], where many variants of the source program are generated and the best one is selected by actually profiling these variants on the target hardware. Other authors [2, 175] use machine learning to gradually improve the optimization results.

Despite of the large number of optimization passes, current compilers often neglect whole groups of optimizations. Important examples are optimizations for better utilization of the memory hierarchy subsystem. The reason is that the hardware control of the current memory elements of this subsystem (caches) determines only at run-time which data to transfer and where to transfer, preventing a large group of design-time memory optimizations. The hardware controlled caches are one of the most power consuming elements in the platform architecture. Nowadays, power dissipation starts to be the limiting factor in embedded handheld devices. Thus, the embedded system domain is trying to avoid using caches and prefers software controlled Scratchpad Memory (SPM)s. These require different (design-time) optimization techniques which are not implemented in current (embedded system) compilers. This triggers the need for source-to-source transformations of these low energy memory elements with increased emphasis on the energy reduction optimizations. Nowadays, these methodologies are implemented separately as source-to-source optimization frameworks. The application is transformed (source to source) in such a

way that the new source code after compilation performs better and/or consumes less energy by effectively exploiting the memory hierarchy subsystem. Ideally, these transformations should be part of the optimizations in the compilation process.

#### 1.3.2 High-level mapping techniques

The high-level mapping techniques targeting the memory subsystem consisting of SPMs gained attention in recent years. We are not going to list here all the high-level mapping techniques present. Rather, we focus on a few state-of-the-art contributions.

The DTSE methodology developed at IMEC targets the optimal mapping of the application w.r.t. the memory footprint reduction and data transfers on a predefined memory subsystem using source to source transformations. The DTSE methodology will be discussed in more detail in Chapter 2. A lot of work in the efficient use of the memory hierarchy has been done at Uni. California, Irwine [170]. They have analyzed the accesses to variables and chose a set of variables to be placed within the scratch-pad memory. At Uni. Dortmund, a technique integrated into a compiler has been developed which analyzes the application, partitions an array variable whenever its beneficial, appropriately modifies the application and selects the best set of variables and program parts to be placed within the scratch-pad [212]. This work uses static analysis for both data and program parts. At Penn State University, a compiler-controlled dynamic on-chip scratch-pad memory (SPM) management framework using both loop and data transformations has been proposed [115]. The work focuses on the data parts only and uses dynamic copying of these data parts. However, the algorithm is only applicable under simplifying constraints, i.e., perfectly nested loops, exactly known loop bounds and array subscripts being affine functions of all loop indices along with additional constraints. Early work in this area based on static analysis has been performed at Uppsala Uni. [189]. Their approach, which focuses on the data parts only, shows that a static analysis is sufficiently precise and no dynamic analysis is needed. The instruction level power analysis and optimization of software is discussed in [198]. Other system level power optimizations for embedded systems are listed in [172, 22, 34].

The high-level mapping techniques consist of platform independent optimizations and platform dependent optimizations. Platform independent optimizations include data-flow transformations removing the redundant memory accesses, and loop and control-flow transformations enabling transformations for the subsequent steps. Platform dependent optimizations contain data and instruction memory organization and transfer, spatial data and instruction locality improvement and cache organization related issues. Most of this work however requires compile time analyzable code limiting the applicability of those high-level mapping techniques.

The importance of loop transformations for memory aspects in the embedded domain has been recognized quite early in the compiler theory [17]. The loop transformations reorganize the control-flow in the loops to enable better optimizations of the subsequent steps during compilation. Very early work on this has started already at the end of the 70's [137] but that was only a classification of the possible loop transformations. The loop transformations have enabled the parallelization or

10 Introduction

have improved the temporal locality of data accesses. There is a lot of work in this domain that is surveyed in Chapter 7. At IMEC, the loop transformations have been systematically applied for more than 10 years [203, 44, 213]. However, the structure and complexity of novel applications limits the applicability of these transformations and opens new challenges for enhanced applicability of loop transformation techniques.

# 1.4 Problem statement and objective

Loop transformations are an important part of high-level mapping techniques such as the DTSE methodology. To perform DTSE optimizations, the complexity of the optimization problem is reduced by selecting the subset of the program which is the target of memory optimization. This subset involves mainly memory accesses, loops and affine and manifest control-flow. The remaining parts of the program are hidden for optimization purposes. In the current DTSE flow, the selection and separation of the program subset relevant for memory optimization is performed manually by the designer. This takes a lot of time and is error prone. Therefore, formalization of this code separation supported by tools is needed to segregate the original source code. Our approach presented in Chapter 4 makes this task for the designer much easier.

The DTSE methodology is targeting rather static (compile time analyzable) applications or application parts. Nowadays, applications are becoming dynamic and have a lot of different execution paths. The actual execution path depends on the mode selected by the application or user. A mode determines which parts of the application will be used, i.e., it determines the execution path of the application. In the past, multimedia applications usually worked in one concrete mode. Modern multimedia applications have multiple modes which are not used equally and do not require the same resources and optimizations.

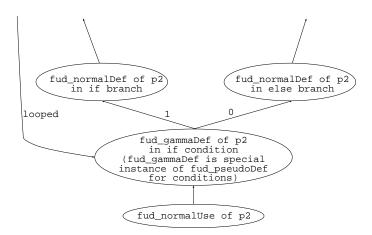

These dynamic modern applications with a lot of modes cause problems for the traditional DTSE methodology. The DTSE methodology can still be applied, but only on each static part, where control can be determined fully at compile time, separately. However, the static parts are getting smaller. All of this prevents the traditional DTSE from performing global optimizations reducing the main strength of the DTSE methodology. Thus, for those applications, DTSE can perform only local optimizations. In Chapter 5, a scenario methodology instance for loop transformations in the global program scope is proposed and elaborated. A scenario is defined as a selected set of paths in the program which we choose to exploit in the same way [225, 85]. The scenario technique should be applied on top of the DTSE methodology and should "open the eyes" for global optimizations in DTSE when a lot of unbalanced modes are present in the application.

During the platform independent source-to-source transformations of the DTSE methodology, decisions are made without propagating important estimation from the platform dependent transformations. The cost functions used in the platform independent steps lead to one particular decision for that transformation step. As it will be shown in Chapter 6, this can lead to suboptimal solutions. We propose considering the effects of the remaining DTSE steps at the higher levels of the methodology using high-level estimators and not going to one "optimal" solution at the

platform independent steps. E.g., during the early GLT step of the DTSE methodology, one concrete decision is made which is not optimal for every platform instance. Instead, a set of decisions which cover the optimal decisions for any platform instance should be propagated to the adjacent steps of the methodology. With such an approach, we can obtain better results as we will see in Chapter 6.

# 1.5 Solution on an illustrative example

In this section we demonstrate the solution to the problems mentioned in Section 1.4 on two illustrative examples. We will not use any code in our first example. Instead we will use an analogy with a laundromat where clothes are washed. In our analogy, the clothes corresponds to the code and the washing process to the optimization (loop transformation) of this code. The code "washing machine" analogy was also used by Hugo De Man at the DATE'02 keynote speech [52].

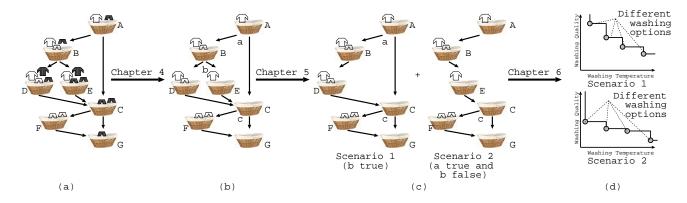

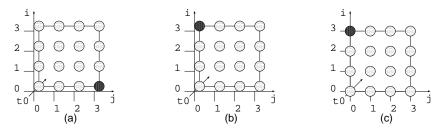

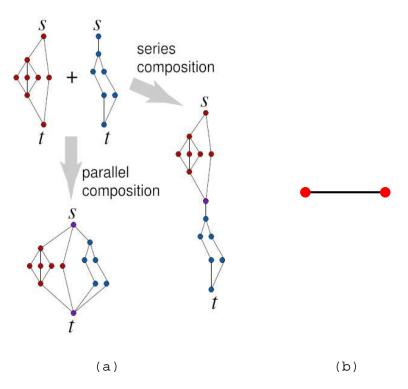

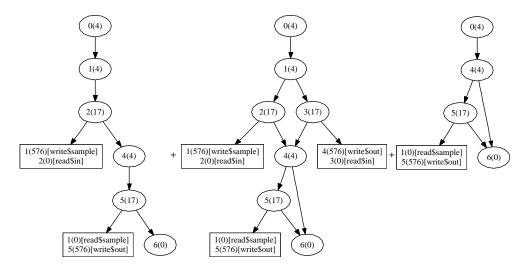

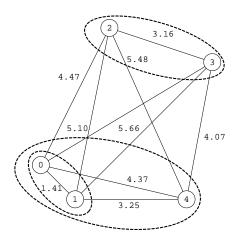

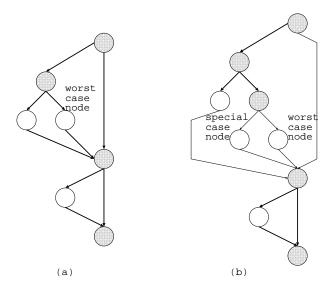

We extend this analogy in Figure 1.5a and define two types of clothes, the white ones that we are going to "wash" and the dark ones that we would like to keep away because of coloring damage. The clothes can only be washed in one public laundromat where different people (Alice, Bob, Carl, Dirk, Erik, Frank and Geert) are coming during the weekend. Each person can bring one laundry basket to the laundromat and not every person is washing each weekend. Which people can meet in the public laundromat during a particular weekend is depicted by following the arrows between a person's laundry baskets in Figure 1.5a starting from the person on the top (Alice) and ending at the person on the bottom (Geert). Thus, Alice, Carl and Geert are washing every weekend. Before going to the laundromat, each person has to separate the white and the black clothes to avoid coloring damage. Thus, at home each person has to remove the dark clothes from the laundry basket. This is demonstrated in Figure 1.5b. How to do so is explained in Chapter 4.

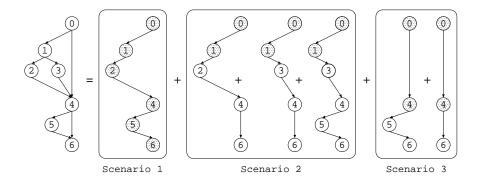

From the Figure 1.5b we can also see that when Alice is in the laundromat, Bob could also be there depending on condition a. If Alice would know that Bob is going that weekend to the laundromat, i.e., a is true, she could phone him and ask him if he would be so kind and also wash her clothes to save the washing powder and gasoline when driving to the laundromat. This is depicted in Figure 1.5c. We created two scenarios, one assuming that Alice, Bob, Dirk, Carl, Frank and Geert are in the laundromat and the other one assuming that Alice, Bob, Erik, Carl, Frank and Geert are in the laundromat. The actual situation in the laundromat will be known only during the weekend. As can be seen from Figure 1.5c, in the first scenario, Bob and Dirk can combine their laundry for sure and in the second scenario, Alice, Bob, Erik and Carl can also combine their laundry for sure because they will surely wash together if that particular scenario occurs. Of course, in the first scenario Alice can also wash together with Carl and Geert, given that there is no dependency between Alice and Bob (e.g., Bob still has Alice's white socks). Note, that the combination of baskets and arrows in Figure 1.5a represents the Control Flow Graph (CFG) of the application. The details about scenarios will be described in Chapter 5. Scenario 1 allows us to combine the two baskets of Bob and Dirk with one T-shirt and one pair of shorts. Scenario 2 allows us to combine two baskets of Alice and Bob with the T-shirt with the basket of Erik with one T-shirt and one pair of shorts and with

**Figure 1.5:** The solution on an illustrative example.

Thesis contributions 13

the empty basket of Carl. In the code, the combination of baskets with more white clothes means enlarging the exploration space for our transformations.

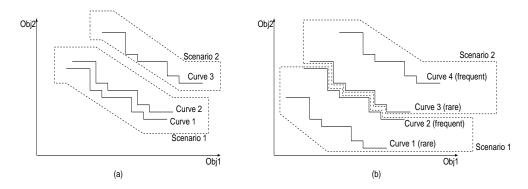

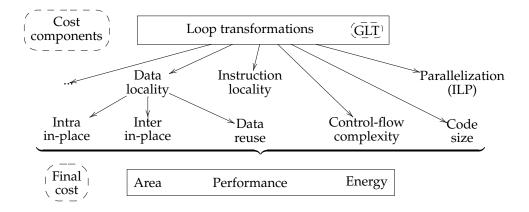

The clothes in the laundry baskets in each scenario (note that some baskets have been combined) are being washed. However different people like to wash their clothes differently and something else is optimal for them. Some people prefer to wash at 30° not to lose the elasticity of the cloth, for other people it is better to wash it at 60° to be sure that it is fully clean. Also, for optimizations, there is not a unifying best optimization for any platform. That is why we provide a set of best solutions that vary over different platforms. This is demonstrated in Figure 1.5d and it will be discussed in Chapter 6.

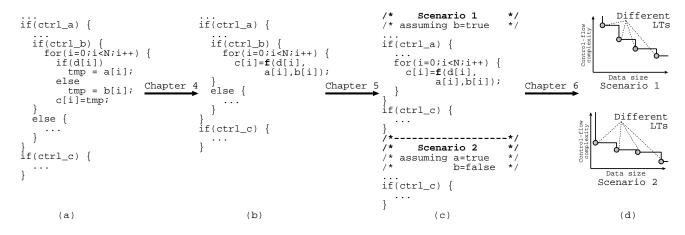

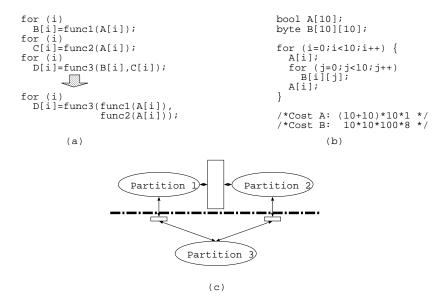

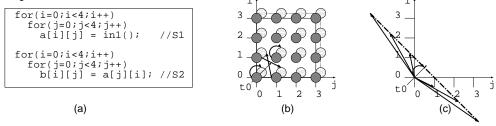

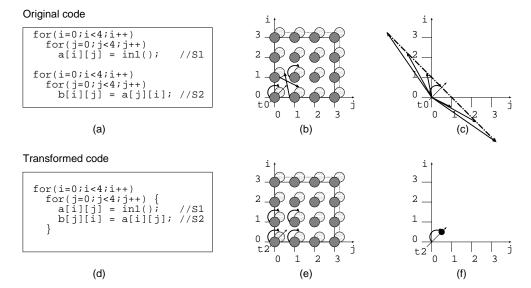

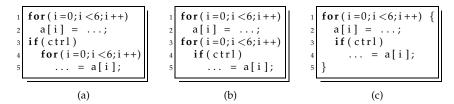

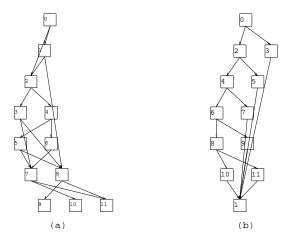

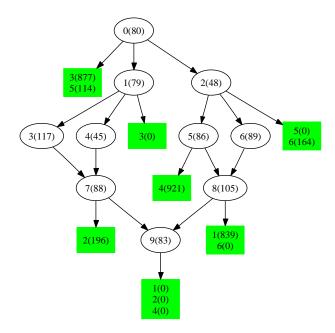

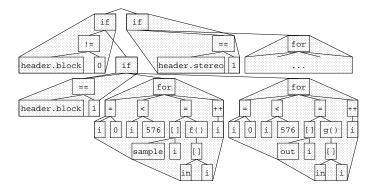

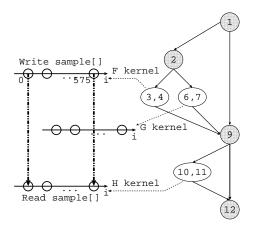

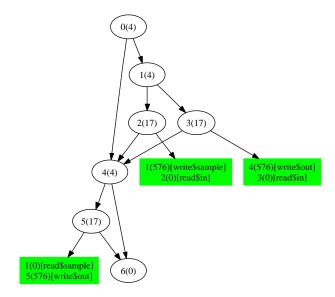

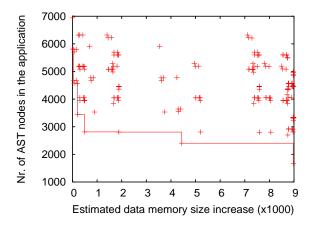

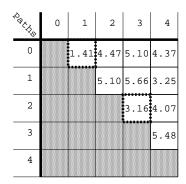

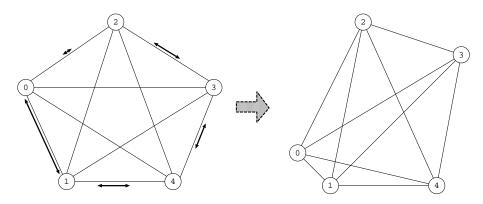

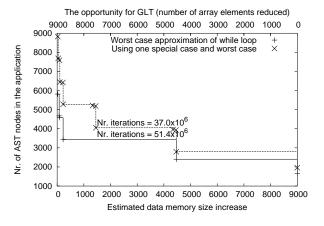

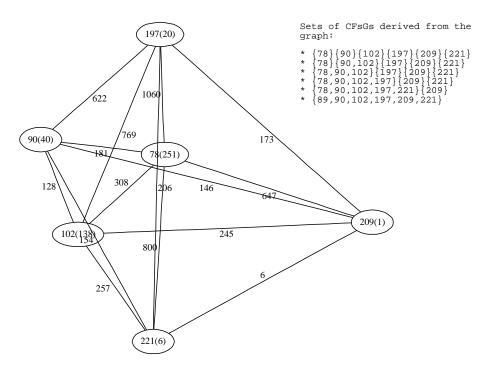

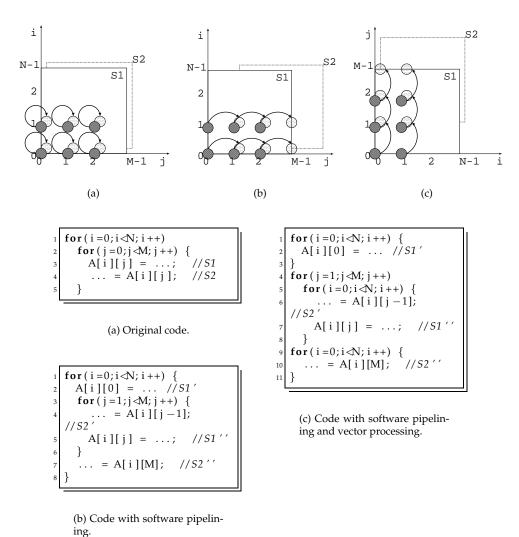

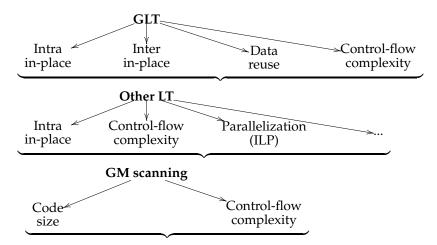

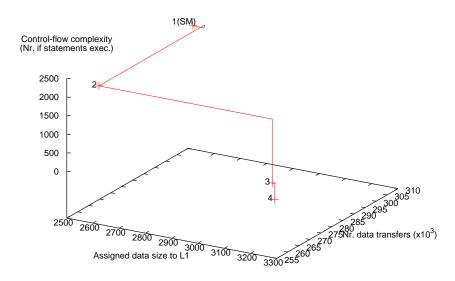

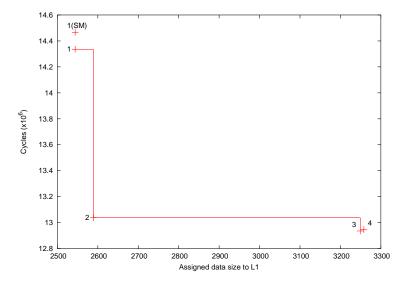

Now we will demonstrate the steps from Figure 1.5 on a small piece of real code which is depicted in Figure 1.6a. In the first step in Figure 1.6b, the code that is not the target of the DTSE optimizations is hidden into function **f()**. Then, in the second step (see Figure 1.6c), the code is specialized into two parts, *Scenario 1* and *Scenario 2*. These specialized codes contain only certain paths from the original CFG (see also Figure 1.5). They also enable more DTSE optimizations compared to the previous code in Figure 1.6b. Note that *Scenario 1* and *Scenario 2* together contain all the paths in the original CFG (see also Figure 1.5). On these codes, different loop transformations are applied resulting in different solutions trading-off Datasize cost for Control-flow complexity cost in the 2-dimensional exploration space as depicted in Figure 1.6d. This approach enables more optimizations compared to the approach without scenarios and multidimensional (Pareto) optimal solutions which enable better utilization of the platform after the platform is known.

#### 1.6 Thesis contributions

This dissertation contributes mainly to the platform independent stage of the DTSE methodology. The primary goal of this dissertation is filling the gaps in the platform independent stage and extending some steps in this stage towards future dynamic applications. The dissertation contributes in four areas:

- DTSE requires prepared code where loop level constructs and arrays to be optimized need to be clearly separated from the remaining part of the application code. In Chapter 4 we formalize and implement this separation of the code.

- DTSE primarily targets static applications where the execution order can be analyzed (and modified by DTSE) at compile time. In Chapter 5 we propose a systematic methodology of scenario usage for extending the applicability of the GLT step, which is one of the most important steps in the methodology, towards more dynamic applications.

- The GLT step in the DTSE methodology currently targets only one particular goal which is the minimal lifetime of the array elements in the application so that the memory locations can be reused. In Chapter 6 we present case studies demonstrating that this goal does not always lead to the optimal solution. The presented case studies show that many trade-offs exist during the GLT step.

**Figure 1.6:** The solution on an illustrative example - a small piece of real code.

Thesis overview 15

The trade-off oriented GLT requires a different steering mechanism compared

to traditional GLT. In Chapter 6 we propose the coupling of high-level estimators to the GLT framework as a steering mechanism for trade-off oriented

GLT and contribute to the definition of the requirements for those high-level

estimators together with other researchers.

#### 1.7 Thesis overview

The dissertation is composed of eight chapters. In this section we provide short overview of the chapters:

- **Chapter 2** presents the DTSE methodology and DTSE related techniques. Note, that this chapter provides only an overview of the methodology, a more detailed description can be found in the DTSE books [32, 28]. It also positions our contributions within the whole DTSE methodology flow.

- **Chapter 3** explains the Geometrical Model (GM) and GLT framework in more detail. Especially, the different GLT frameworks are analyzed and the gaps in these frameworks are defined resulting in the contributions of this dissertation.

- **Chapter 4** formalizes the algorithms for separation of the code to be optimized from the rest of the code. This separation of the code is called hierarchical rewriting in the DTSE methodology. We have implemented the algorithms using the ATOMIUM framework.

- **Chapter 5** proposes a systematic methodology of scenario usage for enhancing the applicability of the GLT step in the DTSE methodology. We implemented the proposed methodology using ATOMIUM framework and Boost Graph Library (BGL). In this chapter, a solution for *while* loops is also proposed as a combination of the preprocessing and scenario approach. In that sense, this extension has a cross-level nature with the previous chapter.

- Chapter 6 provides case studies which show the need for trade-off oriented GLT. Compared to the "best locality" traditional GLT step, which provides only one GLT solution, the trade-off oriented GLT step provides a set of optimal GLT solutions in the multi-dimensional exploration space. This is achieved by using high-level estimators as the steering mechanism for GLT. The explanation of those high-level estimators and their coupling to the GLT framework is also discussed in this chapter.

- **Chapter 7** surveys related work in hierarchical rewriting and condition hiding, scenarios and Global Loop Transformations (GLT).

- **Chapter 8** provides a summary and conclusions, and proposes possible topics for future research.

# The DTSE methodology

Goed geheugen. Om zoveel te kunnen onthouden moet hij weinig hebben beleefd.

Jan A. Emmens

(1924-1971)

The memory subsystem and bus usage consumes over 50% of the energy consumption in embedded systems [53, 148]. This is especially true for modern multi-media systems such as image processing or video encoding/decoding which manipulate large multi-dimensional data sets resulting in a large amount of data storage and transfers. Therefore, optimizing the global memory accesses of an application, using e.g., the DTSE methodology developed at IMEC, is a crucial task for achieving effective low-power realizations. The goal of the DTSE methodology for system-level power optimization is to determine an optimal execution order for the data transfers together with an optimal memory architecture mapping for storing the data of the given application [32, 28]. This leads to a reduction in the number of main (off-chip) memory accesses and more efficient on-chip local memory (cache or SPM) utilization. The cost functions currently incorporated for the storage and communication resources are both power and area oriented [30]. Due to the realtime nature of the targeted applications, the throughput is normally a constraint. Improving the global memory accesses generally also has a positive influence on the performance because it reduces the (external) bus traffic and it improves the cache hit rates [129].

The DTSE methodology is split into several substeps combined in two groups: platform independent and platform dependent steps. The platform independent steps transform the program independently of the parameters of the memory (data storage) target platform, which is, in effect, chosen or constructed based on the results of these steps. The platform is subsequently used to further optimize the program in the platform dependent steps. The platform independent steps optimize the data flow, the regularity and locality of data accesses in general, and make the data reuse possibilities explicit. The subsequent platform dependent steps take physical proper-

ties of the target background memory architecture into account to map and schedule the data transfers in a cost-efficient way.

The starting point is an executable system specification with multi-dimensional array accesses. The output is a transformed source code specification, potentially combined with a (partial) netlist of memories which is the input for the final platform architecture design/linking stage when partly customizable or configurable memory realizations are envisioned. The transformed source code is input for the software compilation stage in the case of instruction-set processors. The flow is based on the idea of constraint orthogonalization [27], where in each step a problem is solved at a certain level of abstraction. The consequences of the decisions are propagated to the next steps and as such decreases the search space of each of the following steps. The order of the steps should ensure that the most important decisions and the decisions that do not put too many restrictions on the other steps are taken earlier. The former criterion is quite obvious. The latter is also intuitively clear because if we would perform the decisions which impose many constraints at the beginning, these constraints would limit the exploration freedom of the remaining steps. This general approach is different from the iterative optimization approaches, e.g., [2, 175], which we mentioned already in Chapter 1. There, the applied transformations are dependent on each other, i.e., we cannot unambiguously determine the order of the transformations. Breaking them up in consecutive steps leads to potentially severe suboptimality. This is generally known as the phase coupling dilemma where quality and scalability have to be traded-off [199, 128]. In our approach we circumvent that phase coupling by carefully selected splits. Still, those phase coupled approaches can be well utilized inside the particular steps of DTSE where the constraint orthogonalization does not apply any further.

The DTSE methodology is partly supported with tools in the ATOMIUM system exploration environment. For the platform dependent part the tools are quite robust, well tested and used for real-life designs. For the platform independent part, most of the tools are prototypes only. The transformations are applied to original source code after program partitioning/pruning. The partitioning/pruning reduces the complexity of the exploration space and ensures that only the relevant parts of the code with (large deeply nested) loops and multidimensional memory accesses are the target of the DTSE optimizations.

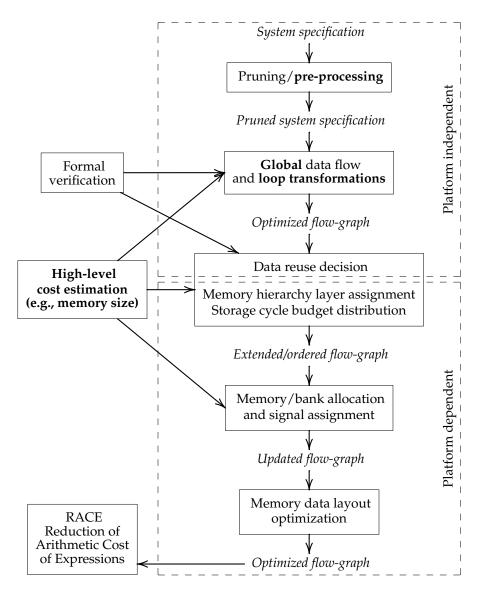

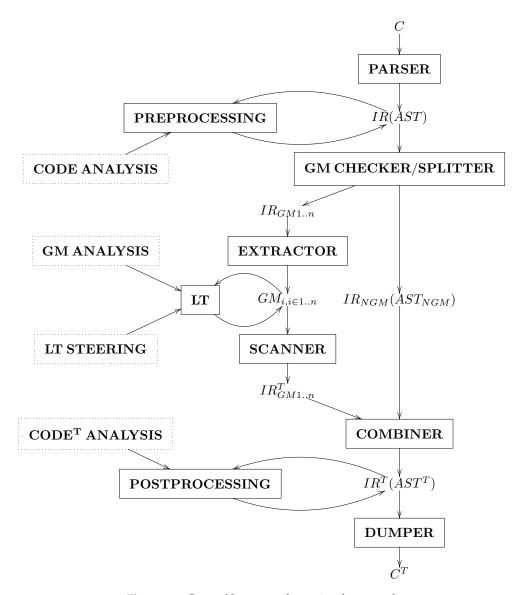

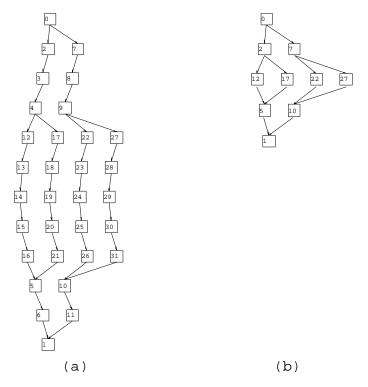

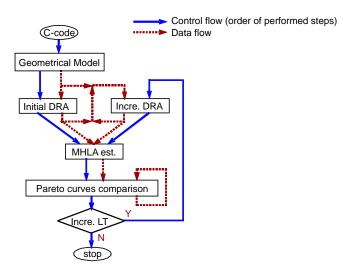

The complete DTSE methodology is described in detail in [32] for customized architectures and in [28] for programmable architectures. The global DTSE framework is shown in Figure 2.1. To situate our research interests in this global framework, we have highlighted the steps we have contributed to in this dissertation with bold text. To put those steps in the global context we give in this chapter a summary of the DTSE methodology. Section 2.1 provides an overview of the platform independent steps of DTSE and Section 2.2 provides an overview of the platform dependent steps. Section 2.3 discuses other DTSE related methodologies and Section 2.4 summarizes the open issues in the DTSE flow.

**Figure 2.1:** DTSE methodology for data transfer and storage exploration: global overview [201, 213].

# 2.1 Platform independent steps

Platform independent steps of the DTSE reduce the number of array accesses and enable later platform dependent optimization steps. They are beneficial for any platform used later in the design-flow. The platform independent steps are pruning and preprocessing, global data-flow transformations, global loop and control-flow transformations and data reuse exploration.

#### 1. Pruning and preprocessing

This step precedes the actual DTSE optimizations; it is necessary to identify and isolate the parts and data structures in the program which are data-dominant and thus relevant for the DTSE. The preprocessing/pruning step also presents this code in a way which is optimally suited for transformations [32]. Thus mostly loops with large bounds and exhibiting good reuse of data and data structures such as array variables are exposed. All the free-dom is exposed explicitly, and the complexity of the exploration is reduced by hiding constructs that are not relevant. Apart from areas of power oriented gain, the parts of the program, which are a bottleneck for obtaining better performance need to be identified. These are mostly the data structures that have very little locality but are accessed heavily.

During the pruning the ATOMIUM analysis tool can be used. This tool identifies the used part of the code dynamically during the profiling phase using given testbench. Thus the testbench for the application has to be carefully selected. ATOMIUM dynamic pruning prunes all the code we are not interested in for further optimization. The ATOMIUM analysis identifies and profiles all array accesses in the program. This gives us the first hint on which parts of the code we should target our optimization effort. After the pruning, the preprocessing, i.e., to expose explicitly all the optimization freedom, is performed.

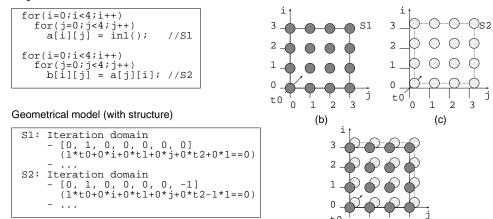

During the preprocessing, pointer accesses are converted to array accesses [63, 75], other constructs that cannot be modeled by the geometrical model are hidden away [162], functions are selectively inlined [1] and the code may be rewritten in Dynamic Single Assignment conversion (DSA) form [69, 209]. Although DSA is not a strict requirement for the following steps, it does increase the freedom potentially allowing better transformations to be performed. For all those preprocessing techniques, mostly prototype tools exist.

We contribute to the preprocessing step by proposing a methodology for dealing with data-dependent conditions. We separate the treatment of outer and inner data-dependent conditions. Inner conditions are hidden by using our technique for hierarchical rewriting and hiding of data-dependent conditions. Outer control-flow is treated with the instantiation and extension of general scenario methodology [225, 85]. This enables better utilization of the GLT step of the DTSE methodology as will be discussed in sequel.

#### 2. Global data-flow transformations

The set of system-level data-flow transformations that have the most crucial effect on the system exploration decisions has been classified, and a systematic

methodology has been developed for applying them [31, 33]. Two main categories exist. The first one directly optimizes the important DTSE cost factors by removing redundant accesses and reducing intermediate buffer sizes. The second category serves as an enabling transformation for the subsequent steps because it removes the data-flow bottlenecks wherever required, especially for the global loop transformations step.

The main goal of the global data-flow optimization step is to reduce the number of bottlenecks in the algorithm that prevent optimizing code restructuring transformations from being applied and remove access redundancy in the data-flow. The transformations consist mainly of advanced signal substitution avoiding unnecessary copies of data, modifying computation order in associative chains enabling certain loop transformations, shifting of "delay lines" through the algorithm to reduce the storage requirements, and recomputation issues to reduce the number of transfers and storage size. For the data-flow transformations only a limited set of prototype tools exists.

#### 3. Global loop and control-flow transformations

The goal of the global loop and control-flow optimization step is to reduce the global lifetimes of the signals and to increase the locality and regularity of the data accesses. Signal is any time-varying quantity in the program that could be either scalar valued or vector valued. In the DTSE methodology we focus on vector-valued signals, i.e., array variables. Locality of data accesses means that the accesses to the same memory location have to be close in time and the regularity means that the order of consumption should be the same as the order of production. The transformations remove system-level buffers introduced due to mismatches in production and consumption ordering (regularity problems). They allow also the data to be stored later in the design flow in smaller memories closer to the data paths.

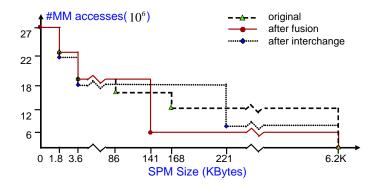

The Global Loop Transformations (GLT) step, the related preprocessing step and the link to high-level estimation leading to trade-off oriented GLTs are the main subjects of this dissertation. The transformations in the GLT aim at improving the data access regularity and locality for multi-dimensional array signals and at removing the system-level buffers introduced due to mismatches in production and consumption ordering (regularity problems). The state of the art in GLT focuses on one cost function resulting in one optimal solution for GLT [204, 76, 44, 213]. In this dissertation we show that an extension of this approach towards different cost functions resulting in trade-offs is needed. We propose to use high-level estimation to steer those trade-off oriented GLTs. For the GLTs a prototype tool and a more robust tool built on top of ATOMIUM framework exists. The results of this dissertation have also contributed to the development of these tools.

The GLTs are applied globally across the full code and not only individual loop nests, also across function scopes because of the selective inlining applied in the preprocessing step. Still, they are applied only within the Static Control Part (SCoP)s which will be defined in Chapter 3. In the preprocessing we propose a novel techniques that enables additional GLT going beyond the scope of SCoPs, e.g., across data dependent conditions. For these novel techniques

also prototype tools based on the ATOMIUM framework, Standard Template Library (STL) and BGL have been developed.

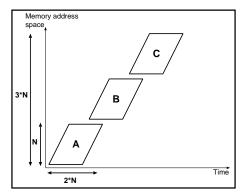

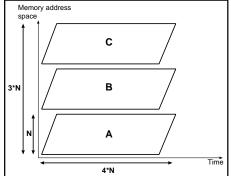

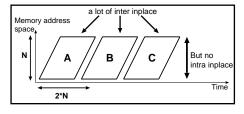

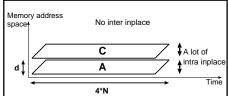

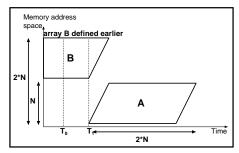

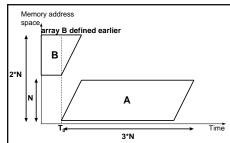

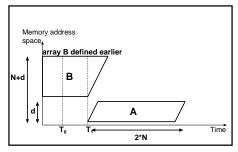

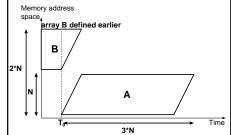

It is crucial that the GLT step is applied before the data reuse exploration and in-place steps. Loop transformations change the execution order such that the production and the consumptions of data elements are moved closer together in time. The result is that the data reuse copies in the memory hierarchy can be made smaller since data is kept in the copy for a shorter time period, and higher data reuse factors can be achieved. Also, the intra/inter in-place optimizations which exploit the reuse of the memory location of the array element/array which is not used any more in the program by newcoming array element/array, can benefit from limited lifetime enabled by GLT.

#### 4. Data reuse exploration

The goal of the data reuse decisions step is to better exploit a hierarchical memory organization to benefit from the available temporal locality in the data accesses. An important consideration here is the distribution of the data over the hierarchy levels such that frequently accessed data can be read from smaller and less power consuming memories. This obviously has a positive effect on the total power consumption of the application because the most frequently accessed data is then read from less power consuming memories. Also the smaller memories can then be closer to the data paths thereby reducing the dissipation in the interconnect, especially if off-chip memory accesses are replaced by on-chip memory accesses.

In this step the data locality introduced by the previous global loop transformation step is exploited. Data reuse possibilities are made explicit by analyzing virtual multi-copy hierarchies (including bypasses) for the trade-off of power and memory size cost. Heavily reused data will be copied to smaller power-efficient on-chip memories, while costly accesses to external memory are reduced.

The basic methodology of [58] and [222] is systematic, though it has restrictions on the actual data reuse behavior that can be handled. [200] and [28] have extended this methodology by introducing some vital cost parameters to describe a more complete search space. They further explored the relationship between these parameters and the cost function for power and memory size, and proposed heuristics to steer the search for a good solution.

[200] formalized the extended search space by introducing an analytical model for the cost parameters as a function of the index expressions and loop bounds. This avoids long simulation times and more importantly, it allows for the identification of exactly which array elements have to be copied to a sub-level for optimal data reuse. This has lead to a fully automated design technique for all loop-dominated applications to find optimal memory hierarchies and generate the corresponding optimized code [201].

#### 2.2 Platform dependent steps

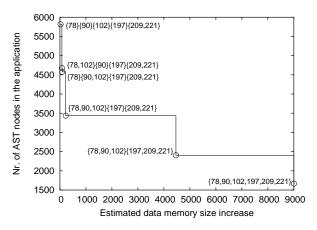

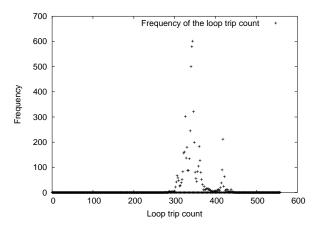

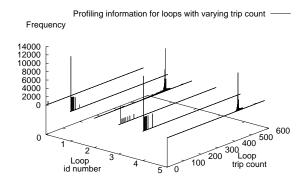

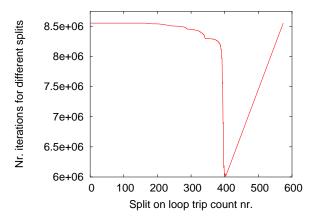

Platform dependent steps of the DTSE uses the information about the predefined memory organization to perform further optimizations. Some substeps only apply for an (embedded) customizable memory organization which is becoming available on several platforms by partly powering down overdimensioned memory blocks that are not fully needed. The platform dependent steps are Memory Hierarchy Layer Assignment (MHLA), Storage Cycle Budget Distribution (SCBD), Memory Allocation and Assignment (MAA) and memory data layout optimizations.