# Reactive machine control : a simulation approach using chi

#### Citation for published version (APA):

Hofkamp, A. T. (2001). Reactive machine control : a simulation approach using chi. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Mechanical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR548334

DOI: 10.6100/IR548334

#### Document status and date:

Published: 01/01/2001

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# Reactive machine control

a simulation approach using  $\boldsymbol{\chi}$

A.T. Hofkamp

Voorkant: Tekening door G.J. Pouw te Naarden.

De tekening laat het interne kruiwerk van de molen te Zeddam (Gld) zien.

Deze stenen torenmolen is tussen 1440 en 1450 gebouwd. Het is de oudste in bedrijf zijnde wind-korenmolen van Europa, en staat in de UNESCO top 100 van Nederlandse monumenten.

De molen is te bezichtigen aan de Bovendorpstraat 14 te Zeddam.

Voor meer informatie, zie http://welcome.to/torenmolen.nl .

Drukker: Universiteitsdrukkerij Technische Universiteit Eindhoven

### / stan ackermans institute, center for technological design

The work in this thesis has been carried out under the auspices of the research school IPA (Institute for Programming research and Algorithmics).

#### © Copyright 2001, A.T. Hofkamp

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior written permission from the copyright owner.

### CIP-DATA LIBRARY TECHNISCHE UNIVERSITEIT EINDHOVEN

Hofkamp, Albert Th.

Reactive machine control : a simulation approach using  $\chi$  / by Albert Th. Hofkamp. - Eindhoven : Technische Universiteit Eindhoven, 2001. - Proefschrift. - ISBN 90-386-3012-3 NUGI 841 Subject headings: virtual machines / reactive machine control / development tools / simulation / chi language

# Reactive machine control a simulation approach using $\chi$

PROEFONTWERP

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr. R.A. van Santen, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op dinsdag 6 november 2001 om 16.00 uur

door

Albert Theo Hofkamp geboren te Leeuwarden Dit proefontwerp is goedgekeurd door de promotoren:

prof.dr.ir. J.E. Rooda en prof.dr. M. Rem

Copromotor: dr.ir. J.M. van de Mortel-Fronczak

# Preface

In March 1997, I started working at the Systems Engineering Group for my final project of OOTI<sup>1</sup>. I liked the work and the environment, and thus agreed to stay for a PhD on design for the design and implementation of a tool set for the development of machine control systems. Now, three years later, I have finished the project, had a lot of fun, and learned a lot.

Since I wrote this thesis, my name is on the front of this thesis. However, I am not the only person that worked on its contents. I would like to thank everybody involved for his or her assistance in this project. First of all, dr.ir. J.M. van de Mortel-Fronczak, prof.dr.ir. J.E. Rooda, and prof.dr. M. Rem for their help and time while writing this thesis.

I would like to thank dr.ir. W.T.M. Alberts, dr. G. Fábián M.Sc, and dr.dipl.-ing. G. Naumoski for their involvement in the compiler design and implementation, and ir. N.Z. Chen for constructing the simulation engine. Also, I thank dr. H. Geuvers for his help with the type checking algorithm, and correcting that part of my thesis.

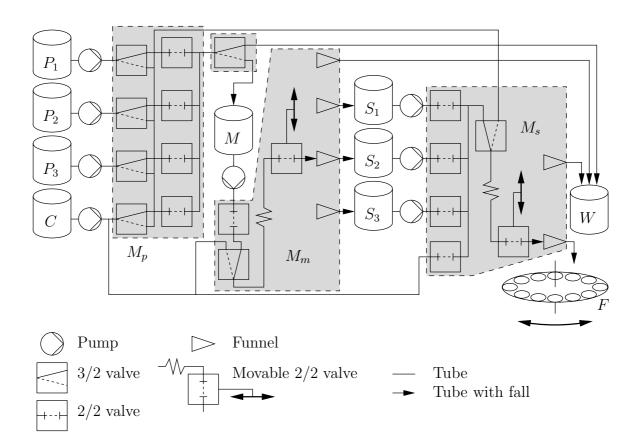

A large number of people invested their time and energy in the paint-factory case study. Without them, the study would not have been possible. Dr.ir. D.A. van Beek defined the global requirements, ir. K.J. Eijsvogels came with the idea of a paint factory and performed the first simulations, ing. H.W.A.M. van Rooij, F.G.J. Soers, and F.A.J.C. van Stiphout created the physical version of the machine that ir. M.H.M. van Duin brought to life by designing and implementing the operational controller.

Last but not least, I thank Mieke, Corry, and Anja for their discussions about the challenges and problems of every day life. They provided the counterweight to prevent me from drifting into the technicalities of work.

In this thesis, Chapter 1 discusses the topic of this project, the design and implementation of reactive control systems for industrial machines using simulation. It introduces an approach to realize the construction of a controller, and discusses a number of important design decisions made in the project. One of these decisions is the simulation language. The chosen language  $\chi$  is explained in the second chapter. This chapter also considers the differences between the real world around us, and the simulation world. Chapters 3

<sup>&</sup>lt;sup>1</sup>Post-graduate designer programme Software Technology.

and 4 explain the design and implementation of the tool to perform the transformation from simulation to the real world. The fifth chapter discusses the paint-factory case study. This case study is the first larger experiment of the approach proposed in the first chapter. Chapter 6, the final chapter of this thesis, reflects on the work done and draws conclusions. Also, suggestions for next steps are made.

# Summary

Customers want their products cheap and tailored to their needs. In the production process, this means that each product is more or less unique, yet they have to be manufactured in large enough quantities to keep the costs low. At the same time, the life time of a product is getting shorter. In order to sell as many products as possible, a short time-to-market is essential. To meet these demands, production machines must be constructed in a short time, with enough flexibility to manufacture each product variant in large enough volume. The short delivery time of machines and the requirements with respect to flexibility makes the design of these machines and their control systems increasingly complex. The Systems Engineering Group is therefore investigating new methods to design machines and their control systems. In particular, methods and practices are devised that allow developers to construct machine control systems with high performance. Realizing this aim means that the controller and the machine have to be designed and used as a *two-unit*. That is, both are separate systems but they are so strongly linked that they cannot function independently.

Designing a machine and its controller as a two-unit is a highly complex task. Due to the strong inter-connections, a change in one system causes changes in the other system and vice versa. To manage the complexity, *virtual machines* are used. Instead of designing the construction of the machine and developing an implementation of the control system, a design of both systems is performed using simulation first. The machine and its control system are described in a specification and tested using simulation. Once the simulation gives satisfactory results, the design can be build. For the control system, the translation from simulation to implementation can be done automatically.

Specifying the machine and the control system enforces the developers to be precise about their ideas. That goes a long way in detecting and correcting potential problems early in the design process. Simulation of the virtual machine and controller allows the machine to 'come to life'. It enables study of the dynamic behaviour of the combination. The study provides insight in the design, and gives feedback about development steps done. Also, data from simulations may be used to guide the development process. For example, if the simulation data suggests that performance will be adequate, improving performance even further is not necessary. This Ph.D. project on design aims to create practically usable means for performing case studies in the research of designing controllers for industrial machines using the virtual machine concept. In particular, a practically usable design technique is discussed, and tools to support the development process have been designed and implemented for the formal specification language  $\chi$ .

The design technique presented in the thesis divides the development process in a number of vertical design steps, and a single horizontal design step at the end. In each vertical design step, a simulation model is designed and specified that is lower in abstraction level compared to the previous model. Simulation experiments are performed with the model, and the output of the experiments is studied. If the output is satisfactory, either the next vertical design step is made to further lower the abstraction level of the model, or the model has the right abstraction level in the sense that it uses the same interface as the real machine. In the latter case, the final horizontal design step is made. In this step, the model of the machine control system is translated to an implementation of the control system on a real-time operating system. Since the model, and since the interface of the machine model is the same as the interface of the real machine, the implementation will be able to control the real machine.

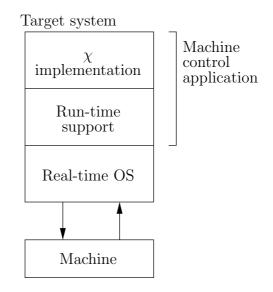

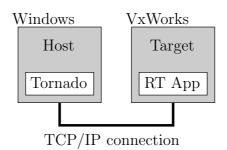

Two tools have been designed and implemented. The first tool is the simulation tool which enables simulation of a specification on a Unix system. The second tool is the translation tool. It translates a controller model to an implementation on the real-time operating system VxWorks. All tools have been written in C++, and consist of a compiler that compiles the specification, and a run-time system that executes the compiled model.

The VxWorks run-time system of the translation tool currently uses a single processor only, but it can easily be extended to run on a distributed system. An important part of the run-time system is the implementation of the communication algorithm. The  $\chi$  specification language uses synchronous communication, whereas the VxWorks real-time operating system only provides asynchronous communication primitives. The implemented communication algorithm, based on Bagrodia [Bag89], performs the mapping of synchronous communication to asynchronous primitives. Several extensions have been added to the algorithm to make it fit the needs of the translated specification. Correctness of the implemented algorithm has been tested with a number of verifications, and a large number of Monte Carlo simulations.

As a test to see whether the virtual machine concept, the developed method, and the tools are useful in reaching the research goals, a case study has been performed. A machine called *the paint factory* and a control system have been developed using the design technique. Although the higher levels of control that optimize scheduling are not yet finished, the case study did produce a functioning machine with its control system. The use of the virtual machine concept seems to be a promising road towards the development of controllers for (complex) industrial machines.

# Samenvatting

Klanten willen hun producten aangepast aan hun wensen en goedkoop. In het productieproces betekent dit, dat elk product min of meer uniek is. Tegelijkertijd moeten ze wel in voldoende aantallen gemaakt worden om de kosten laag te houden. Bovendien wordt de levensduur van een product korter. Om zoveel mogelijk producten te verkopen is een korte time-to-market essentieel. Een korte time-to-market van een product betekent ook, dat de productie-machines snel te leveren moeten zijn. Machines moeten daarom snel te bouwen zijn en voldoende flexibiliteit bezitten, om met wisselingen tussen product-varianten te kunnen omgaan.

De kortere ontwikkeltijd van machines en de eisen ten aanzien van de flexibiliteit maken het ontwerp van deze machines en hun besturingssystemen complexer. De Systems Engineering groep onderzoekt daarom nieuwe methoden om machines en hun besturingssystemen te ontwerpen. De nadruk van het onderzoek ligt daarbij vooral op het ontwerpen van het besturingssysteem. Er worden methodes ontwikkeld die het voor ontwerpers mogelijk maken om machines en besturingen te bouwen die hoge prestaties leveren.

Om dit doel te verwezenlijken moeten de machine en zijn besturing als een *twee-eenheid* ontworpen en gebruikt worden. De machine en de besturing zijn twee losse systemen, maar ze zijn zo sterk met elkaar verbonden dat ze niet zelfstandig kunnen functioneren.

Het ontwerpen van een machine en zijn besturing is een complexe zaak. Door de sterke verbondenheid van beide systemen heeft het veranderen van het ene systeem gevolgen voor het andere en andersom. Om de complexiteit te kunnen beheersen wordt het idee van *virtuele machines* gebruikt. In plaats van het ontwerpen van de machine-constructie en het ontwikkelen van een implementatie van de besturing, wordt er eerst een ontwerp gemaakt van de systemen gezamenlijk door middel van simulatie. De machine en het besturingssysteem worden beschreven in een specificatie en geanalyseerd met behulp van simulatie-experimenten. Wanneer de simulatie-resultaten uitwijzen dat het ontwerp aan de gestelde eisen voldoet, kan het ontwerp gebouwd worden. Voor het besturingssysteem kan de vertaling van simulatie naar implementatie automatisch gedaan worden.

Het specificeren van de machine en de besturing dwingt de ontwerper om zijn ideeën precies te formuleren. Dat helpt veel in het ontdekken en corrigeren van potentiële problemen vroeg in het ontwerpproces. Simulatie van de virtuele machine en zijn besturing zorgt ervoor, dat de machine 'tot leven komt'. Dankzij simulatie is het mogelijk om het dynamische gedrag van de combinatie te analyseren. De analyse levert inzicht in het ontwerp en geeft een terugkoppeling over ontwerpbeslissingen. Bovendien kan data uit simulatie-experimenten gebruikt worden om het ontwerpproces te sturen. Als de gegevens bijvoorbeeld aangeven dat de prestaties voldoende zijn, dan hoeven deze niet verder verbeterd te worden.

Het doel van dit proefontwerp is om praktisch bruikbare middelen te ontwikkelen voor het onderzoek naar het ontwerpen van machine-besturingen, gebruikmakend van virtuele machines. In het proefschrift wordt een ontwerpmethode behandeld, daarnaast heeft het promotieproject geresulteerd in het ontwerp en de implementatie van gereedschappen die het ontwerpproces ondersteunen voor de formele specificatietaal  $\chi$ .

De ontwerpmethode voorgesteld in dit proefschrift verdeelt het ontwerpproces in een aantal verticale ontwerpstappen en één horizontale ontwerpstap aan het einde. In elke verticale stap wordt een simulatiemodel ontwikkeld en gespecificeerd op een lager abstractieniveau dan het vorige model. Dit model wordt gesimuleerd en de simulatie-resultaten worden bestudeerd. Als de resultaten voldoen aan de eisen, kan de volgende verticale ontwerpstap gedaan worden om het abstractieniveau verder te verlagen. Indien het abstractieniveau overeenkomt met de interface die gebruikt wordt bij de echte machine, wordt een laatste horizontale ontwerpstap gemaakt. Het model van de besturing wordt vertaald naar een implementatie op een real-time beheerssysteem (operating system). Omdat het model van de controller ongewijzigd blijft, zal de implementatie hetzelfde gedrag hebben als tijdens de simulatie. Omdat bovendien de echte machine dezelfde interface gebruikt als de machine in de simulatie, zal de implementatie de echte machine kunnen besturen.

Twee gereedschappen zijn ontworpen en gebouwd. Het eerste gereedschap is het simulatiegereedschap, wat simulatie van een specificatie mogelijk maakt op een Unix systeem. Het tweede gereedschap is het vertaalgereedschap, wat een model van een controller vertaalt naar een implementatie op het real-time beheerssysteem VxWorks. Alle gereedschappen zijn geschreven in C++ en bestaan uit een vertaler (compiler) en een run-time systeem, wat het vertaalde model uitvoert. Het run-time systeem op VxWorks gebruikt nu slechts één processor, maar kan eenvoudig uitgebreid worden om te kunnen werken op een gedistribueerd systeem. Een belangrijk deel van het run-time systeem is de implementatie van het communicatie-algoritme. De  $\chi$  specificatietaal gebruikt synchrone communicatie terwijl het VxWorks real-time beheerssysteem slechts asynchrone communicatie-primitieven biedt. Het geïmplementeerde communicatie-algoritme is gebaseerd op Bagrodia [Bag89], en vertaalt synchrone communicatie naar asynchrone primitieven. Er zijn een aantal uitbreidingen toegevoegd aan het algoritme om het passend te maken voor het vertaalde model. Correctheid van het gebouwde algoritme is getest door middel van een aantal verificaties en een groot aantal Monte Carlo simulaties.

Als een test of het virtuele machine concept, de ontwikkelde methode en de gereedschappen nuttig zijn in het bereiken van het onderzoeksdoel, is een casus (case study) uitgewerkt. Een machine, die *verffabriek* wordt genoemd, en het bijbehorende besturingssysteem zijn ontwikkeld, gebruikmakend van deze ontwerp-methode. Hoewel de hogere besturingslagen die de volgorde van orders optimaliseren nog niet af zijn, leverde de casus een functionerende machine en besturing. Het gebruik van virtuele machines lijkt een goede weg naar het ontwikkelen van besturingen voor (ingewikkelde) industriële machines.

# CONTENTS

| 1 | Intro                        | oduction 1                                         |  |  |  |

|---|------------------------------|----------------------------------------------------|--|--|--|

|   | 1.1                          | Control systems                                    |  |  |  |

|   | 1.2                          | Project goal                                       |  |  |  |

|   | 1.3                          | Design technique                                   |  |  |  |

|   | 1.4                          | Implementation of tools                            |  |  |  |

|   | 1.5                          | Reactive machine control                           |  |  |  |

|   | 1.6                          | Thesis outline                                     |  |  |  |

| 2 | The $\chi$ language 15       |                                                    |  |  |  |

|   | 2.1                          | Language definition                                |  |  |  |

|   | 2.2                          | Time-related aspects                               |  |  |  |

|   | 2.3                          | The horizontal design step                         |  |  |  |

| 3 | The real-time platform 27    |                                                    |  |  |  |

|   | 3.1                          | The real-time operating system                     |  |  |  |

|   | 3.2                          | Machine control application                        |  |  |  |

|   | 3.3                          | Data structures of the machine control application |  |  |  |

|   | 3.4                          | Run-time support                                   |  |  |  |

|   | 3.5                          | $\chi$ implementation                              |  |  |  |

|   | 3.6                          | Future extensions                                  |  |  |  |

| 4 | Synchronous communication 45 |                                                    |  |  |  |

|   | 4.1                          | Bagrodia                                           |  |  |  |

|   | 4.2                          | Communication in $\chi$                            |  |  |  |

|   | 4.3                          | Implementation                                     |  |  |  |

|   | 4.4                          | Verification of the implementation                 |  |  |  |

| 5 | Case                         | e study 67                                         |  |  |  |

|   | 5.1                          | Choice of the case                                 |  |  |  |

|   | 5.2                          | Highlights                                         |  |  |  |

i

|              | 5.3                                      | Observations and conclusions | 76  |  |  |

|--------------|------------------------------------------|------------------------------|-----|--|--|

| 6            | Conclusions 79                           |                              |     |  |  |

|              | 6.1                                      | The design technique         | 79  |  |  |

|              | 6.2                                      | Modelling                    | 82  |  |  |

|              | 6.3                                      | Virtual machines             | 84  |  |  |

|              | 6.4                                      | Languages and tools          | 84  |  |  |

| $\mathbf{A}$ | The                                      | type-checking mechanism      | 87  |  |  |

|              | A.1                                      | Introduction                 | 87  |  |  |

|              | A.2                                      | Type matching                | 89  |  |  |

|              | A.3                                      | Type-variables resolving     | 91  |  |  |

|              | A.4                                      | Performance                  | 92  |  |  |

| в            | Promela code and verification results 95 |                              |     |  |  |

|              | B.1                                      | Algorithm                    | 95  |  |  |

|              | B.2                                      | Verification                 | 105 |  |  |

|              | B.3                                      | Simulation                   | 109 |  |  |

| Bi           | Bibliography 113                         |                              |     |  |  |

| Index        |                                          |                              |     |  |  |

# Introduction

In the recent years, computer technology has been introduced in industrial machines on a large scale. The ever-decreasing size and cost has made this technology feasible for use in machine control systems. Also, the ever-increasing computing power of this technology opens new roads and new applications. For example, visual inspection of products can now be done automatically with a sophisticated program rather than manually. Manufacturers of industrial machines therefore extend the functionality of their machines to make them more attractive to customers. Computer technology also allows re-programming of the controller almost at the flick of a switch. Thus, it is much easier to adapt the machine to new situations; the machine has become much more flexible than its predecessor. To some extent, one can say that a machine is becoming a small factory in itself.

The market needs this flexibility. Our society is becoming more oriented towards the individual. Concepts like mass-customization<sup>1</sup> are becoming popular. These personalized products are however more complex to manufacture than products that cannot be personalized. In other words, more is demanded from the industrial machines.

In short, the introduction of computer technology increases the number of possibilities of the machine, and the market wants flexibility. The latter can be realized by clever use of the former. The question however is how to do this in a systematic and controlled way. More precise:

#### How do you systematically design a flexible industrial machine and its controller ?

The Systems Engineering Group has set itself the goal of finding an answer to this question. This project is one of the first steps towards solving this puzzle.

## 1.1 Control systems

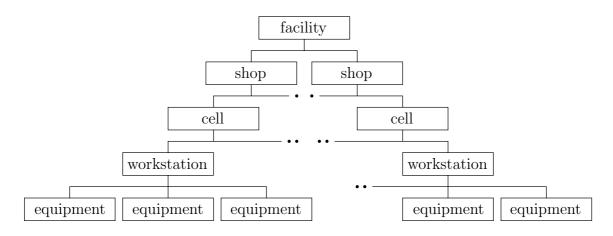

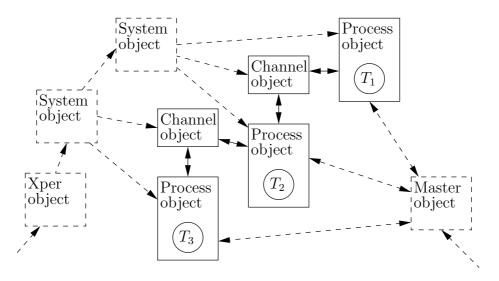

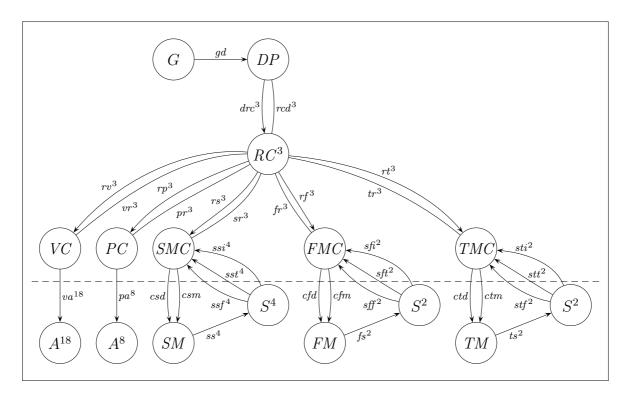

A widely accepted model of a control system for an industrial system is [JM86], published by the National Bureau of Standards, nowadays known as NIST. This hierarchical production control system is a framework composed of five levels of control, as shown in Figure 1.1. The top level *facility* takes care of planning for the entire plant for a relative long planning horizon, but on a global level. Each level below takes orders from above,

<sup>&</sup>lt;sup>1</sup>Every customer his own personalized product, while using mass-production manufacturing techniques.

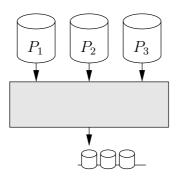

Figure 1.1: Model of a hierarchical control system by NIST.

makes a more detailed plan on a shorter planning horizon, and controls the level below using the computed plan. Below the *equipment* level, machines perform the manufacturing steps, thus realising the plan. Since production never completely follows the plan, status feedback is reported upwards between the levels. The feedback information can be used to adapt the plan, thus making optimal use of the industrial system.

As an example of such a framework we briefly describe the litho area of a chip factory using the above hierarchical control model. The *facility* level is the entire factory, as perceived by the clients and suppliers of the factory. This level accepts orders, agrees on delivery dates, and makes sure that the clients get the requested products. The internal organisation on the factory floor is controlled at the *shop* level. This level controls the various areas of the plant. In other words, it ensures that batches containing wafers are moved and processed in the correct area, and that materials needed for processing are also available.

One of these areas is the litho area. In this area, a number of litho modules and inspection machines are available. The *cell* control system routes the wafers to the machines, and makes sure that all the needed materials and chemicals for the particular wafer are available too at the same machine. For example, the masks necessary for the exposure process step should be on the same machine as the wafers that should be exposed.

Inside an individual litho module, a number of process steps are performed (coating, pre-bake, exposure, development, and post-bake). Routing of wafers through the process steps in a litho module is co-ordinated by the *workstation* control system. Each process step is performed by a machine, controlled by its *equipment* level control system. The machines themselves perform the process steps, and change the wafer surface.

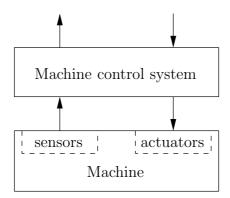

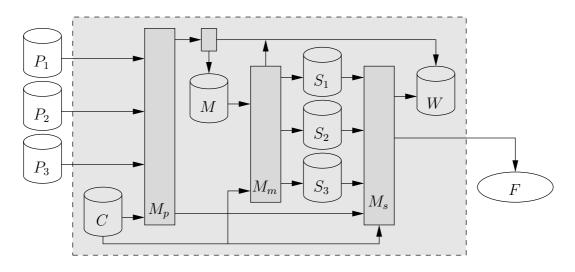

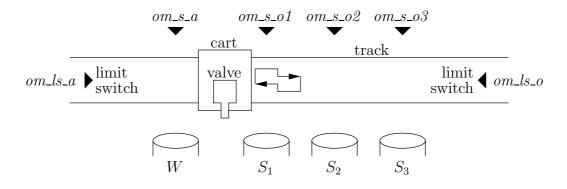

In this project an initial step is taken towards a systematic approach of the development of machine control systems at equipment level in an industrial environment. Figure 1.2 shows a typical machine control system interacting with its environment. From above, orders are given to the machine control system. These orders are translated to actions

#### 1.1. Control systems

Figure 1.2: Model of a machine control system and its environment.

that must be done by the machine, and actuators are given orders to perform physical movements in the machine. Sensors in the machine report the status of the physical components in the machine back to the machine control system, and the latter uses this information as feedback, thus controlling the machine. Also, feedback on the status and progress of the order is given upwards to the higher level.

The end result of the development project of a machine control system is a functioning machine control system, controlling a physical machine. The control system thus has some real-time control properties such as timeliness. Obviously, these matters need to be addressed during the development of the control system. However, before reaching the point where real-time properties of the control system become important, the general design of the controller must be established. Especially for larger machines, this is a difficult subject. With the introduction of computers in machine control, machines have become much more flexible. They are no longer a mechanically-coupled number of parts, the parts can be controlled independently from each other. This delivers a lot of flexibility to the control system, but also makes designing a good controller more difficult because the various parts must co-operate as well as possible in order to utilize the increased flexibility. In a sense, machines can be seen as small factories with their own scheduling problems between the parts.

Another complicating factor is the environment of the machine and the controller, that is, the manufacturing process. For example, in some environments, the machine may be used in a batch system. In other environments, many small orders are manufactured, which requires a lot of switching between different products.

The main objective of a machine control system in an industrial environment is always to deliver maximal performance in the manufacturing process. In other words, the machine has to perform as well as possible in its environment. To achieve this goal, the controller has to be tailored to the environment. The design approach presented here considers the combination of controller and machine to be a *two-unit*. They are separate systems, but they should be developed and used together for the best results.

Development of the control system in this context involves profound knowledge of the

machine as well as its environment. With machines and environments as described above, this is too much knowledge to overlook completely. The systematic approach of the development process will thus focus on *understanding* of the situation.

# 1.2 Project goal

The goal of the research on embedded systems in the Systems Engineering Group is to develop a methodology to design controllers for (complex) industrial machines. Central concept in the research is the *virtual machine* concept. It means that the entire environment around the controller, including the machine, is simulated. In this simulation environment, the controller is developed. Section 1.3 explains these ideas in more detail.

This Ph.D. thesis aims to

create the practically usable means for performing case studies in the research of designing controllers for industrial machines using the virtual machines concept.

'Create practically usable means' is the key-phrase here. The idea is to create means, such that researchers, engineers in industry, and students can perform practical experiments in the design of controllers, in order to get feedback on ideas in research.

The realization of this objective implies two 'deliverables':

• A design technique. The above description about development in a virtual environment is too abstract for students and engineers in industry. A more down-to-earth description is needed. This is called the design technique, and its description can be found in Section 1.3.

Note that this technique is a first attempt. As research progresses, the design technique will quite likely be improved.

• *Tools to support the design technique*. A design technique is only viable for realistic case studies if it is supported by adequate, robust tools.

Experimenters should concentrate on their objective of designing a controller, rather than worry about the limitations of the tools. Therefore, the tools should accept anything that is correct, even if it is big, ugly, or both. More about the tools can be found in Section 1.4.

An important factor in the construction of the technique and the tools are the capabilities of users. The intended audience in this project are designers with a Mechanical Engineering background. That means that knowledge of users about software-engineering techniques and formal methods is limited. The technique and the tools have to take this into account.

# 1.3 Design technique

The basic goal of the design technique is to provide a global framework in which the developer can organize his work. At the same time, it tries not to exclude any design

activity that may be considered useful. In other words, the design technique provides a general guide for the developer that can be tailored to a particular situation.

There are a number of reasons for this approach. First of all, trying to capture the entire design process is not feasible. Each machine control system has its own unique nature. This heavily influences the approach of designing the control system. Also, each developer has his own strong and weak points. The design technique should be flexible enough to allow each developer to use the approach that he prefers. Secondly, there is little or no experience with the development of design techniques for these kind of control systems. Further research must be done in order to decide on a good approach. Until that time, it seems foolish to eliminate any design approach. Also, it is more efficient to do research in this area after this project is finished, because tools are then available to perform realistic tests of different design approaches. Finally, the focus of the project lies on developing tool support rather than designing an optimal design technique.

The design technique is a framework to guide the developer in the design of the machine control system. The main focus of the technique is understanding the controller, the machine, and the environment.

One good way to get a good understanding of a subject is by *modelling* it. Modelling is a common engineering activity used in a lot of disciplines. For example, a new bridge is first modelled as a scale model and as a set of blueprints before construction starts. Software is designed and captured in graphical models like data flow diagrams. In fact, modelling is a technique that forces the developer to specify his thoughts. This aids in structuring the design [BRJ99]. Also, it confronts the designer with unclear areas in the design. Modelling is thus the foundation of the method.

Modelling is good for creating structure, but it gives little information about the dynamics of the system. Software-engineering techniques such as use-case diagrams or state diagrams do allow the developer to capture behaviour, but understanding the diagram as a dynamically changing object is a different matter, especially when the behaviour is complex. One technique to assist the developer in understanding the dynamics is *simulation* [Sha75]. With simulation, the design 'comes to life'. The developer can verify and correct his conceptual model of the dynamics by studying the results of the simulation. Since understanding the dynamics of the machine and its environment is crucial for development of good controllers, simulation is also part of the design method.

Even with modelling and simulation techniques, developers will make mistakes, and some of these mistakes will survive the design process and become bugs in the implemented controller. Obviously, there should be as few bugs in the implementation as possible. Paths to achieve this are extensive testing and formal verification. The former does not give full guarantees, the latter does provide correctness proofs at the cost of a lot of effort. Since failure of a controller for an industrial machine is very expensive, preventing bugs is extremely important. The method should thus allow the use of testing and formal verification techniques. However, the rigorousness of modelling and simulation techniques goes a long way in preventing bugs, see for example [Kar98]. Also, the machine control systems developed with the technique will not include mission-critical systems, for example

nuclear reactors or air planes. For these reasons, formal verification methods are currently considered to be a future extension to the design technique.

Finally, the end result of the development project using the design technique is a functioning controller. In other words, with the modelling and simulation techniques described above, a model is developed, and this model has to be ported to real hardware. That has to be done with a as few changes as possible in the model, because every change may introduce an error, and b little knowledge of software engineering and the real-time domain, because our users do not possess that knowledge.

The development path to the end result is as follows. First, a model is developed in a language formal enough for interpretation by a machine. The modelling process forces the developer to be precise. Since the language is formal enough for machine interpretation, a computer-based simulation of the model is possible. This simulation brings the model to life, allowing the developer to watch his design and check his assumptions. After enough iterations, the model is good enough to be implemented in the real world. Again using the ability to interpret the model by machine, the model is translated to an implementation. This implementation can then be used to control the real machine.

The above development procedure uses a number of assumptions. Two important ones are:

- The real-world machine is controlled in the same way as the simulated machine. The specified controller is translated to the implementation without functional changes. If the translated controller is to control the real machine, the latter should behave just like the simulated machine.

- The implementation should address the real-time properties needed. Numerous books are written on this subject. The properties listed below are from [HS91]. Others use similar lists. Some typical properties of a real-time control system are:

- Timeliness. The system must react timely upon events from external processes.

- *Simultaneity*. There are normally many external processes going on at the same time, and each of them must be controlled.

- Predictability. The system must always (even under extreme conditions) produce predictable responses, both in the processing results themselves, and in the moments when the results become available.

- Dependability. Embedded systems are used in environments where failure of the system may not only cause loss of data, but also endanger people and major investments. In order to minimize these risks, the embedded system must be made as reliable as possible.

Timeliness is a property that needs to be verified already during the early stages of development. The modelling language does need the concept of time in order to allow this. Also, the translation to the implementation must preserve the timeliness

#### 1.3. Design technique

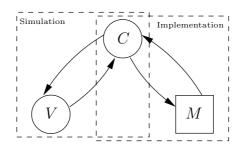

Figure 1.3: Simulation and implementation using virtual machine V, controller C, and real machine M.

property. The simultaneity property should be supported by the language. It cannot be expected that users understand how to incorporate simultaneous handling of multiple tasks in a sequential language. By introducing parallelism in the modelling language, simultaneity can be expressed in the model cleanly. Predictability of the implementation is taken care of by the modelling process. The rigorousness of this process ensures that the developer has at least seen and specified what happens in each situation. Dependability is a property that can only be ensured by systematic and precise working. The modelling and simulation process done by the developer does help here; a model in a formal language does not allow to leave parts of the system unspecified.

The models developed using the design technique look like Figure 1.3. The model consists of two components, the controller and the machine. While the design technique is used in the simulation domain, that is, models are developed and simulated, the controller C is connected with a *virtual machine* V. The latter is used as a representation of the machine in the model. With each iteration, more details are added to the controller, the machine component, or both, and behaviour of the combination is verified by simulating the model. During the translation to the real-world implementation, the virtual machine V is replaced by the real machine M, where M should be a real-world implementation of V. In the controller component, connections to machine V are replaced by connections to machine M, and the new combination can be executed and tested in the real world.

Early experiments show that a developer experiences the development process as three different stages, at least for relatively simple machine control systems:

- 1. Conceptual design. Starting from the requirements, early (abstract) models of the controller and the machine are written and simulated. The developer becomes acquainted with the global operation of the machine, and can check whether the given requirements can be fulfilled.

- 2. *Physical design*. Once the global working of the machine is understood, the developer can concentrate on designing the machine (its sensors and actuators), and the controller. Quite accurate estimates of the performance of the combination can be made,

and these estimates can be used to decide for example on hardware components or control strategy.

3. *Implementation and testing.* In this stage, the transformation to the real world is made. After it, the real machine is controlled by the controller. Correctness of the design (for example regarding reaction time) is verified by performing tests.

If the design technique is followed correctly, the last step should confirm that the machine and the controller are functioning correctly. If that is not the case, then the translation step to the implementation should be postponed, until the design is corrected by performing some extra iterations in the simulation domain.

From a larger distance, the design process first focuses on lowering the abstraction level of the design from requirements to a simulated controller, and then makes a translation step to an implemented controller. The first part is not uncommon in engineering; the principle can be found in many books about design, for example [vdKS98] uses 'doel', 'functie', 'structuur', and 'inrichting' (English translation: goal, function, structure, and layout). Also, [Bra93, Page 20] shows that several methods have the same global-todetailed design-process phases, although the number of phases and the names of the phases differ with each method. The second part where the developed model is translated to an implementation is rare. The step from model to implementation is often made, for example in [Bri97], but these approaches start with an implementation in another language using the developed model as a guide. Aside from the fact that the developer needs to know at least two languages, there is a large chance of introducing errors into the implementation while implementing.

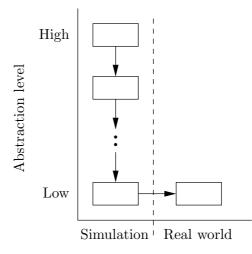

The design technique proposed in this project is depicted in Figure 1.4. In the figure, a rectangle represents a state of the design. Arrows between design states represent development steps or *design steps*. Development starts with a specification at a high level of abstraction. By modelling, simulating, and making design decisions, the design is made more concrete, that is, it is lowered in abstraction level. This is shown in the figure by the downward arrows. Such development steps are called *vertical design steps*. After enough vertical design steps have been taken, the abstraction level is low enough to implement the system in the real world. Translating to an implementation is called a *horizontal design steps*, it does not lower the abstraction level. It is the process of constructing an implementation as specified in the model. In other words, the horizontal design step creates a real-world version of the simulation model.

### Language

The language used in modelling and simulation is very important in the design technique. It is the language in which developers express their design, so it must be easy to use and learn. Also, since it must be interpreted by a machine, it has to be a formal language.

#### 1.3. Design technique

Figure 1.4: Design technique using simulation.

Since the implementation of a controller is a piece of software, it is tempting to use common software-engineering methods, for example described in [HP88, Coo91], or the newer object-oriented method UML [BRJ99]. These methods use diagrams to model the software, and manage to capture a part of the dynamics of the system, but none of them uses simulation which is a powerful technique for our users. Also, they do not treat the software and its environment as a two-unit, they concentrate on software only. For these reasons, the software-engineering methods have been dropped as modelling language.

The Systems Engineering Group already uses their own language  $\chi$  for modelling and simulating, with a lot of success. Also, tools for simulation are already available. This makes the  $\chi$  language the prime candidate. Nonetheless, it should be verified that  $\chi$  is not a wrong choice.

$\chi$  is based on CSP [Hoa78], a formalism where multiple concurrently executing processes work together. The description of behaviour of processes themselves is based on process algebra, except an imperative style of programming is used to describe behaviour rather than a functional style. Data modelling in  $\chi$  is done using constructs commonly found in modern programming languages, such as booleans, integer and real numbers, strings, tuples and arrays, lists, and sets. A more detailed description of the language can be found in Chapter 2. Also,  $\chi$  fulfills the requirements mentioned previously. It has parallel execution, which allows easy specification of simultaneous tasks, and it has the concept of time, allowing timeliness properties to be expressed. Finally, the imperative style of programming and the powerful data handling constructs can be translated to a normal programming language, like C++.

For the implementation of the tools, a language is needed too. The existing simulation tool [NA98] consists of two parts, a compiler that translates  $\chi$  to C++, and a run-time environment that performs the simulation. Both parts are written in C++.

In the horizontal design step, a similar strategy seems beneficial: a compiler for trans-

lating the  $\chi$  model to the language understood by the implementation, and a tool in the run-time environment to support the translated code. For the compiler, an object-oriented programming language is better suited for the job, because the object-oriented paradigm provides better abstraction mechanisms. The cost of object-oriented techniques compared to the imperative paradigm is an increase in processing power and memory. Since the compiler is executed on a normal computer system with plenty of processing power and memory, these costs are not a problem. The two major programming languages in object-oriented programming are Java and C++. Since the compiler for the simulation tool is written in C++, the latter language gives better performance, and the author of this thesis has more experience with the language, the choice of C++ for the compiler will not be a big surprise.

For the run-time environment of the controller implementation, the situation is less clear. In embedded systems, small processors are common. Also, C is a common programming language, often with some processor-specific extensions. The Java language is also used in some cases, for example in set-top boxes. Despite this, the programming language C++ has been chosen for the run-time environment as well. C has been dropped because the project aims at the design of complex industrial machines. In this context, the cost of more processing power and more memory is not very important. Secondly, since the project is done as part of a research programme, it is expected that the software will be changed often. The higher abstraction of object-oriented languages is clearly an advantage then. Thirdly, C++ can be used in combination with C, which means that integration with software written in the latter language is possible. (To be fair, Java can also be used in combination with C, but C++ is designed for backwards compability.) Fourthly, availability of templates in C++ makes the handling of complex data types easier. Finally, in the run-time environment, performance plays a big role, and C++ delivers better performance than Java. Also, run-time maintenance like garbage collection is not performed.

### 1.4 Implementation of tools

In Section 1.2, it was concluded that tools were needed to support the design technique. The latter consists of two kind of steps; vertical design steps and horizontal design steps. The former takes place in the simulation domain, the latter crosses the border from the simulation domain to the real world. For each kind of design step, a computer-based tool is necessary:

• A simulation tool. A vertical design step is a transformation of a simulation model to a lower abstraction level. The design method aims at giving the engineer an understanding of the dynamic behaviour of the developed model. The best way to support this process, is by providing a simulator capable of showing the dynamic behaviour of the specification written by the engineer.

Currently, there is no tool support for formally checking certain properties, for example (lack of) deadlock. Also, equivalence checking or testing between successive

#### 1.4. Implementation of tools

Figure 1.5: Overview of the operation of a tool.

simulation models is not supported by tools. Such tools may be added in the future if the need arises in the research.

• A translation tool. A horizontal design step transforms a specification from the simulation domain to the real world. Tool support is needed to transform the specification to an executable with the same behaviour, running on an embedded controller.

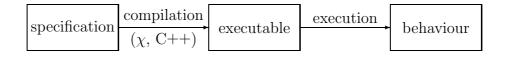

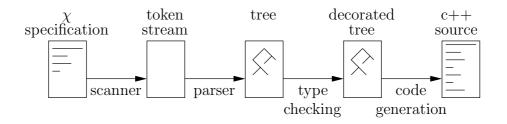

Both tools take a  $\chi$  specification, and produce an executable version of it that shows the specified behaviour. Since the tools should be usable in larger case studies, speed of execution of the result is important. Speed of the transformation from the specification to the executable format is not that important, because the conversion takes little time compared to the execution time of the result. The architecture of an existing simulation tool [NA98] has good properties in this respect, and this architecture is used as blue print for the design of the new tools. The idea is shown in Figure 1.5. Creating behaviour of the specification is done in two stages. First, the specification is compiled to an executable form. This executable form is then executed to obtain the behaviour. The benefit of this approach is that a large number of checks with respect to the correctness of the specification can be done during the compilation instead of during the execution. Furthermore, during the compilation stage, the program temporarily exists as specification in the intermediate implementation language C++, as discussed in the previous section.

The similarities between the simulation and the translation tools, the use of two stages to obtain behaviour of the specification, and the use of C++ as intermediate language also have its impact on the organization of the source code of the tools. In particular, both tools need

- a compiler front-end to parse and check the  $\chi$  specification,

- a compiler back-end to generate C++ code suitable for execution,

- a run-time engine to 'generate' behaviour common for all specifications, and

- libraries to provide additional functionality.

The compiler front-end and back-end is a standard compiler construction approach. The run-time engine is highly coupled to the compiler back-end. It contains for example a

scheduler that chooses statements to execute. It also contains code to represent and compute data values during execution. The libraries contain code that provides functionality used only by some specifications. For example the square root function. In the case of the translation tool, the libraries also provide access to the physical machine. This is discussed in more detail in Section 3.2.

Libraries are also the means to add new functionality to the tools. This is used to experiment with new ideas. For example, recently, the wish to combine a  $\chi$  simulation with other (third party) simulation tools has arisen. By building a new library that allows TCP/IP connectivity to other programs, experiments can be done to investigate this idea.

From maintenance point-of-view, it is advantageous to share as much source code as possible between both tools. The compiler front-end is completely shared by both tools. The run-time engine cannot be shared. The execution stage of both tools occurs at two different platforms, with different semantics (discussed in more detail in Chapters 2 and 3). Therefore, the run-time engines of both tools are separate pieces of source code. The codegenerator of the compiler is tightly connected to the run-time engine, and exists therefore also twice (one generator for each tool). Libraries are common when they are platformindependent. For example, functions like the square root are common, but I/O interfacing functions exist only for the translation tool.

After the decision to construct six pieces of code (one compiler-frontend, two compilerbackends, two run-time engines, and one library), the next question was how to create all this functionality. An existing simulation tool ([NA98]) was available. Analysis showed that the global design ideas of the tool were good. Also, parts of the tool were re-usable, especially pieces of the run-time engine and the libraries. The compiler part was considered not re-usable, because

- The  $\chi$  language had changed since the implementation of the old compiler. Concepts had been changed, or were added to the language.

- There was a fundamental design flaw in the type system of the compiler.  $\chi$  uses both polymorphism and overloading. The type system of the old compiler is based on [Mil78]. This algorithm can handle only polymorphism. As a result, the type checking of the simulation compiler sometimes failed.

- Many features of the  $\chi$  language and the translation to C++ were hard-coded in the compiler.

Especially the change of the type-checking system had a large impact on the existing compiler. Estimation of the amount of work showed that the benefit of re-use of existing compiler code was non-existent due to the huge amount of changes. That opened the path to creating a new compiler with an improved internal structure tailored to the new situation.

In the project, attention was foremost focussed on constructing a functional translation tool. The project started with constructing the compiler-frontend, then the run-time engine, followed by the code generator and the libraries. Once the compiler-frontend was finished, the remaining simulation-tool functionality was implemented by Chen ([Che99b, Che99a]) as a separate sub-project, performed in parallel with the remaining three parts of the translation tool.

# 1.5 Reactive machine control

The title *reactive machine control* is basically a one-line description of the subject. Careful consideration of this description is necessary to give the readers a correct impression of its contents. Particularly important is the choice of the right jargon description. For this thesis, three candidates were considered close enough for a closer look.

Embedded is a recent term. Below are two definitions of the word.

General-purpose systems are not designed for any specific applications but can be programmed to run different applications.

In contrast, application-specific systems are designed for dedicated applications. . . . As these systems are contained in a larger, and often, nonelectric, environment, these are commonly referred to as *embedded systems*. [Gup95]

An *embedded system* is a combination of computer hardware and software, and perhaps additional mechanical or other parts, designed to perform a specific function. [Bar99]

Common to both definitions is the fact that the system has an application-specific purpose, and that other parts outside the system are related to it. A control system for a machine meets this definition, since the application is designed to control a particular machine. Also, the machine is a collection of parts that exists outside the control system and that has a relation to the system (without it, the machine would not function).

**Real-time** is another term which comes to mind when discussing machine control systems. The definitions address the fact that the system must be capable of influencing its environment on time.

A real-time computer system may be defined as one which controls an environment by receiving data, processing them, and taking action or returning results sufficiently quickly to affect the functioning of the environment at that time. [Mar67]

Whenever a computer system is required to acquire data, emit data, or interact with its environment at precise times, the system is said to be a *real-time computer system*. [LM87]

*Real-time* systems are those which must produce correct responses within a definite time limit. Should computer responses exceed these time bounds, then performance degradation and/or malfunction results. [Coo91]

All machine control systems have to react on the machine within a certain time interval to prevent damage or degradation of performance of the machine.

**Reactive** is not often used in literature. It focuses on the fact that the system keeps on running indefinitely.

*Reactive systems* are computer systems that continuously react to their environment at a speed determined by this environment. [Hal93]

A *reactive system* is a system that maintains an ongoing interaction with its environment, as opposed to computing some final value on termination. [MP95]

A machine control system is reactive, since it continuously controls a machine at the speed of the machine without ever stopping (unless powered down).

Since the technique focuses on understanding rather than the combination of control system and its environment, 'embedded' is considered somewhat out of place. In the same way, timeliness of machine control systems is important, but not enough to use the word 'realtime' in the title. The ongoing dynamics of a machine control system is however a keyfeature in understanding the design, making 'reactive' a very appropriate description for such systems in this thesis.

# 1.6 Thesis outline

This chapter explains the goal of the project in more detail, and also discusses the design technique proposed for the development of machine control systems. The next chapter explains the modelling language  $\chi$ , how time is handled by the language and what happens when a  $\chi$  specification is translated to the real-world domain. Chapters 3 and 4 describe the structure of the target system and the real-time environment. Also the translation done by the horizontal design step compiler is briefly described. As an example of usage of the design technique, the case study of 'the paint factory' is discussed in Chapter 5. Finally, concluding remarks, and possibilities for next steps are discussed in Chapter 6.

# The $\chi$ language

In this chapter, the  $\chi$  specification language is informally introduced. More detailed descriptions of the language can be found in [BK00, Fáb99, NA98, Are96]. After the introduction of  $\chi$ , the second part of this chapter discusses the semantics interpretation issue of the horizontal design step. A user develops a specification with simulation using  $\chi$  semantics. The design technique described in the previous chapter should transparently transform the specification to an implementation using a horizontal design step. That implies that interpretation of the specification under real-world semantics should be predictable.

# 2.1 Language definition

Within the Systems Engineering Group, research is being done on the design of industrial systems. Since these systems are highly complex, mathematical theories like queueing theory cannot be applied adequately. Therefore, computer-based simulation is used as a design tool. Around 8 years ago, the simulation language in use at that time was not adequate any more, a new language was needed. It appeared that no existing simulation language met the needs of the application domain, and a decision has been taken to create a new simulation language, now known as  $\chi$ . The language allows specification of discrete-event, continuous-time, and mixed discrete-event/continuous-time (hybrid) systems, thus covering a large range of industrial systems. The user is supported in the development of his model by a computer-based simulation tool, that allows verification and validation of the model. Meanwhile, the discrete-event part of the language has become stable, while the continuous-time part of the language is still being developed. Since this project only uses the discrete-event part only, unless explicitly specified otherwise.

$\chi$  is a parallel language, it has concurrently executing processes that communicate with each other using synchronous communication channels. Its intended users are (mechanical) engineers and students with little or no training in formal methods.

Technically, the language is heavily based on CSP [Hoa78, Hoa85] and ideas from [vdS93]. It is a static language, the number of executing processes as well as the topology of the communication channels between the processes is fixed. Also, the type system is static (can be checked completely during compile time) and uses structural type equivalence (two types

#### Chapter 2. The $\chi$ language

are the same when their structure is the same). The static nature of the language allows the compiler tool to perform a lot of checks for errors.

For the user,  $\chi$  is a small language with few concepts, which are as orthogonal to each other as possible. Much attention has been paid to making the language feel 'natural' to the user, but not at the cost of introducing difficult to understand constructs. Also, the user should be precise when specifying a model. This feeling of preciseness is designed into the language as well. The statically defined data types is one example, other examples are lack of type widening<sup>1</sup>, and no support for 'unnatural' operations on data types, such as projection on a list.

In general, the language is considered to be a kind of mathematical tool for specifying industrial systems. Like in mathematics, short and clear descriptions are possible, not only for small systems but also (especially!) for complex ones.

Since the subject of this thesis does not concern the  $\chi$  language itself, and other documents with more precise descriptions exist, this chapter only gives an informal introduction to the language. The formal language definition can be found in [BK00]. Below, the syntax and an informal description of the semantics of each construct is given. The next section discusses time-related aspects during an 'execution' of a specification.

The syntax of  $\chi$  language constructs is defined by a set of production rules of a grammar. The general form of a production rule is  $T ::= t_1 t_2 \ldots t_n$ . It defines that the sequence of terminals and/or non-terminals  $t_1$  through  $t_n$  can be rewritten to non-terminal T. The symbol  $\epsilon$  denotes an empty sequence. Non-terminals are written in uppercase italics, keywords and symbols are written in roman, while more complex terminals (such as identifiers like *const-id* or *type-id*, or expressions<sup>2</sup> like *e*, *b*, or *c* are written in lowercase italics.

There may be more than one production rule with the same non-terminal at the lefthand side. This means that there may be more than one sequence of terminals and/or non-terminals that can be rewritten to the same non-terminal. The vertical bar is used as a shorthand notation for multiple production rules with the same non-terminal at the left-hand side. As an example, the two production rules W ::= A and W ::= b B specify that the non-terminal A as well as the sequence b B may both be rewritten to the same non-terminal W. Using shorthand notation, both rules can be written in a single line  $W ::= A \mid b B$ . The  $\chi$  language itself also uses the vertical bar as a symbol. In order to differentiate between both uses, the vertical bar used as a terminal in the language is written between quotes, as in '|'.

The top-level production rule of a specification is  $\chi$ :

$\chi \quad ::= \quad \chi \ \chi \ | \ TD \ | \ CD \ | \ FD \ | \ PD \ | \ SD \ | \ XD$

<sup>&</sup>lt;sup>1</sup>Type widening is the implicit conversion of a data type to a larger data type. For example in d := 3, where d is of type real. The integer number 3 is implicitly widened to 'fit' into the floating-point variable.

<sup>&</sup>lt;sup>2</sup>In the implementation, an expression is a non-terminal rather than a terminal. However, the syntax of expressions is considered common knowledge and will not be discussed in this thesis.

non-terminals TD, CD, FD, PD, SD, and XD are type definition, constant definition, function definition, process definition, system definition, and xper definition, respectively. All these definitions are explained below.

#### Data types

$\chi$  is a high-level specification language, and the available data types reflect this. The user may use all types T, where

$$\begin{array}{rcl} T & ::= & void \mid bool \mid nat \mid int \mid real \mid string \\ & \mid & T^* \mid T^+ \mid T^n \mid T_0 \times T_1 \times T_2 \times \ldots \times T_m \\ & \mid & -T \mid ?T \mid !T \mid ~ T \\ & \mid & (T) \mid type\text{-}id \end{array}$$

$$\begin{array}{rcl} TD & ::= & type \ D \\ D & ::= & D, D \mid type\text{-}id = T \end{array}$$

On the first line, the basic data types are listed. The *void* data type is only used for synchronisation channels. The other basic data types are booleans, natural numbers, integer numbers, floating-point numbers, and strings, respectively. More complex data types may be constructed by using type operators.  $T^*$  constructs a list containing values of type  $T, T^+$  does the same for sets, and  $T^n$  constructs statically sized arrays. The data type  $T_0 \times T_1 \times T_2 \times \ldots \times T_m$  constructs a tuple where each field  $i \ (0 \le i \le m)$  has a possibly different type  $T_i$ . The third line describes production rules for constructing data types used for communication. By prefixing a type T with a dash, a communication channel capable of transporting data of type T is constructed. A process does not use channels directly, it accesses them through *ports* instead. The ?-operator constructs a port for receiving a value from a channel, the !-operator is used to construct ports for sending data, and the  $\sim$ -operator is used to construct synchronization ports. On the fourth line, a production rule specifies that a data type may be grouped by surrounding it with brackets. Finally, a data type may be given a name by using a type definition (TD). The name serves as a shorthand notation for the type. Because  $\chi$  uses structural type equivalence, using a name of a type in the specification is equivalent to inserting the type associated with the name at that point surrounded by brackets.

#### Constants

It is often convenient to use symbolic names as a representation of constants.  $\chi$  facilitates this by the following production rules for constant definitions:

$$\begin{array}{rcl} CD & ::= & \mathrm{const} \ X \\ X & ::= & X, X \mid \mathit{const-id}: T = e \end{array}$$

A constant definition CD is a list of definitions, each having an identifier, a type T and a value expressed in e. All values must be constant at compile time, they may only rely on other constants. Using a identifier const-id in an expression is equivalent to using its associated value.

### Functions

Some calculations are too complicated to be expressed in a single line, or are used at many different places in the specification. These calculations can be defined in a function, and be computed by calling the function by name:

The function definition FD defines a function with a unique name *func-id*. The types of parameters needed by the function are specified in the formal parameter list FP. The return type of the function is specified by T. Inside the function, local variables may be introduced (production rule L ::= V '|'), followed by a function statement FS which describes the algorithm of the calculation. Statements allowed in a function are:

- The *skip statement*, which does nothing.

- The assignment statement, which copies the value expressed by  $e_2$  into the variable indicated by  $e_1$ .

- The *return statement*, which ends execution of the function and returns the value expressed by e to the caller.

- The guarded statement, which performs a non-deterministic choice between several alternatives. The statement continues execution with one of the statements  $FS_i$  for which the boolean guard  $b_i$  evaluates to true.  $\chi$  requires at least one guard to evaluate to true. Also, a non-deterministic choice should not influence the resulting value of the function call.

- The repetitive statement, which is a repetitive version of the guarded statement. Repetitively, guards are evaluated, and a statement is non-deterministically chosen and executed, until all guards evaluate to false. At that moment the repetitive statement is finished, and execution continues with the statement following the repetitive statement. Note that repetitive non-deterministic choice is the only property of the statement. Other properties, for example fairness of choice are not part of the language. The form '\*[FS]' is a shorthand notation for '\*[ true  $\longrightarrow FS$ ]', and gives the user an endless loop.

• Finally, the semicolon concatenates two statements. Execution of this statement means execution of the statement before the semicolon, followed by execution of the statement after the semicolon.

A function in  $\chi$  is a function in the mathematical sense. That means that a function *const-id* should always return the same value if it is called with the same parameter values. To enforce this, formal parameters are passed by value, and constructs with side effects (for example communication with another process) are not allowed. The only exception to this rule is the guarded statement which allows a non-deterministic choice. It is assumed that the user will take care of specifying functions with proper functional behaviour.

### Process and system definitions

Process behaviour is defined in process definitions. The topology of multiple concurrently executing processes is specified in system definitions. This division between process specification and process instantiation is a separation of concerns. The former concentrates on the inner working of a process, while the latter concentrates on how the processes are connected to each other.

PD $::= \text{ proc } proc \text{-} id FP = \llbracket L PS \rrbracket$ ::= skip  $|e_1 := e_2 |$  terminate |E| | PG | |\*| PG | |\*| PS | PS; PSPSC $::= c?e | c!e | c? | c! | c^{\sim}$ E $::= C \mid \Delta e$  $PG \quad ::= \quad [\!]_{1 \leq i \leq n} \ b_i \longrightarrow PS_i \ | \ [\!]_{1 \leq i \leq n} \ b_i; \ E_i \longrightarrow PS_i$  $::= \text{ syst } syst-id \ FP \ = \| \ H \ `|` \ N \ \|$ SD $::= H, H \mid I:T$ H $::= N || N | id(e_1, e_2, \dots, e_n)$ N $::= \text{ xper } = [ id(e_1, e_2, \dots, e_n) ]$ XD

The production rule PD specifies a process definition with name *proc-id* and statement PS. Despite the new name of the production rules, the statements are very similar to statements in a function definition. Below, only the new or changed statements are discussed.

- The *terminate statement* terminates execution. The statement is like an instantaneous self-destruct button. The statement is considered a kludge, and will probably be removed in the future.

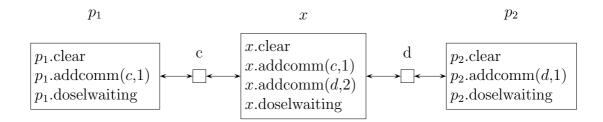

- The communication statements listed in productions rules C are used to communicate with a single other process using a communication channel. In other words, communication channels are point-to-point connections between two processes. In all cases, c is an expression which evaluates to a port. The question and exclamation marks indicate the direction of communication (reception, respectively transmission). In the first two production rules, e is an expression used for data transfer. It respectively evaluates to a variable and a value. The remaining production rules are used

#### Chapter 2. The $\chi$ language

for synchronisation between processes. With synchronisation, no data is transferred. Rules c? and c! still have a sense of direction, while rule  $c^{\sim}$  is a direction-less synchronisation.

- The *delta statement* rule  $\Delta e \ (e \ge 0)$  causes the process to sleep for *e* time units.

- The guarded statement and the repetitive statement have been extended. The first production rule of PG is the same as in the function definition. In the second production rule, the statement waits for communication and/or delta statements, before continuing execution. Effectively, the second form of the statement allows waiting for communication with another process and/or passing of time, which is why it is called the *selective waiting statement*, and the repetitive version is called the *repetitive selective waiting statement*.

The system definition SD creates concurrently executing processes (which may communicate with each other) using the parallel composition operator  $\parallel$ . The instantiation of a process is written as  $id(e_1, e_2, \ldots, e_n)$ . The process definition being instantiated is indicated by *id*. The values of the expressions  $e_i$   $(1 \le i \le n)$  are used as initial values of the actual parameters of the process. Systems may be instantiated in the same way. Instantiation of a system means instantiation of the processes in its body. Nested instantiation of systems is allowed, recursive instantiation is not allowed.

The top-level instantiation used to instantiate the entire model is specified in the xper definition XD.

# 2.2 Time-related aspects

In the previous section, the syntax and informal meaning of each statement was explained. For understanding a specification, the order of executing statements in different processes is also important.  $\chi$  is a language that has the concept of time. How time behaves in relation to execution of the statements is the topic of this section.

#### Language

The operational semantics of the discrete-event part of the  $\chi$  language is formally described in [BK00]. Informally, the instantiated specification is translated to a tree of statements. Execution of a statement is performed by non-deterministically selecting a statement in the tree that can be 'executed' according to the rules of the semantics, followed by modifying the tree. Only one statement can be executed at each time, which naturally leads to *interleaving* semantics.<sup>3</sup>

Another view of an executing  $\chi$  specification is to consider each instantiated process as a separate state machine. A transition in a state machine represents execution of a single statement. All state machines have local state. All those local states together

<sup>&</sup>lt;sup>3</sup>Communication over a channel is regarded as a single distributed assignment here.

form the global state of the specification. At each time, only a single state machine can make a transition, thus resulting in interleaving semantics. This latter view is closer to an implementation, and will be used in this thesis.

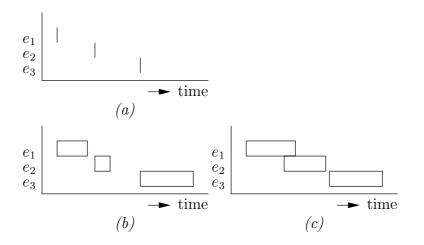

Handling of time in  $\chi$  is done by having different types of transitions. On the one hand there are time-less transitions where time is not progressing, while on the other hand some transitions cause non-zero progress in time. Choosing between transitions is done using the maximal progress principle. As long as time-less transitions are possible, one of these transitions is chosen and executed. When only time-progressing transitions exist, the nonempty set of those transitions is chosen, such that progress in time is as small as possible. When none of the state machines can perform a transition, the system is considered to be in a deadlock.

The above semantics means that most statements in a  $\chi$  program do not cost time. In particular, calculations and communications with co-operating partners are performed time-less. This is known as the *synchrony hypothesis* [Hal93, BCG<sup>+</sup>97]. This abstract notion of time is very convenient during the design of a system, because it simplifies reasoning about its behaviour.

In the real world however, time-less activities do not exist, all activities cost time. Even worse, time is also progressing when you do nothing. In terms of state machines, one would say that a transition between states costs time and staying in a state also costs time.