# Template-based embedded reconfigurable computing

#### Citation for published version (APA):

Leijten-Nowak, K. (2004). *Template-based embedded reconfigurable computing*. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Eindhoven University of Technology]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR577271

DOI: 10.6100/IR577271

#### Document status and date:

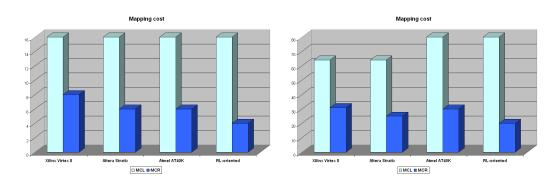

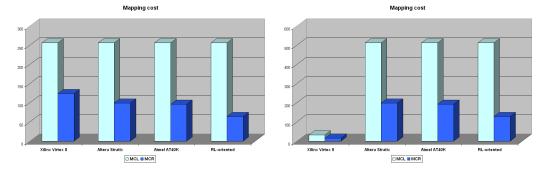

Published: 01/01/2004

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# Template-Based Embedded Reconfigurable Computing

Katarzyna Leijten-Nowak

*The front cover*: Artist impression of a schematic diagram of a logic tile transforming into a layout of an embedded FPGA chip. The logic tile is part of the embedded FPGA architecture template proposed in this thesis. The embedded FPGA chip was designed in accordance with this template. *The back cover*: Subsequent steps of the template-based design methodology: the high-level specification of the embedded FPGA core, the schematic of the core, the VLSI layout of the core, the fabricated embedded FPGA chip.

# Template-Based Embedded Reconfigurable Computing

# PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr. R.A. van Santen, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op vrijdag 9 juli 2004 om 16.00 uur

door

Katarzyna Leijten-Nowak

geboren te Wrocław, Polen

Dit proefschrift is goedgekeurd door de promotoren:

prof.dr.ir. J.L. van Meerbergen en prof.dr.ir. R.H.J.M. Otten

Copromotor: prof.dr.ir. P.R. Groeneveld

#### CIP-DATA LIBRARY TECHNISCHE UNIVERSITEIT EINDHOVEN

#### Leijten-Nowak, Katarzyna

Template-based embedded reconfigurable computing / by Katarzyna Leijten-Nowak. - Eindhoven : Technische Universiteit Eindhoven, 2004. Proefschrift. - ISBN 90-386-1583-3 NUR 959

Trefw.: programmeerbare logische schakelingen / logische schakelingen ; ontwerp / ingebedde systemen / grote geintegreerde schakelingen ; CAD / CMOS-schakelingen.

Subject headings: programmable logic arrays / logic design / system-on-chip / reconfigurable architectures / CMOS logic circuits.

The work described in this thesis has been carried out at the Philips Research Laboratories in Eindhoven, The Netherlands, as part of the Philips Research programme.

© Philips Electronics N.V. 2004 All rights reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

in loving memory of my mother

We shall not cease from exploration And at the end of all our exploring Will be to arrive where we started And know the place for the first time. T.S. Elliot

# PREFACE

This Ph.D. thesis completes the research I was conducting in the period February 1999–April 2003 in the Embedded Systems Architectures on Silicon Group at Philips Research Laboratories in Eindhoven, The Netherlands. My research was done as part of the ARCADE (Applications of ReConfigurable Computing Architectures in Dsp Environment) cluster project, I happened to be the only member of.

I am extremely happy for having received the opportunity to pursue a Ph.D., and maybe even more happy for having it done in the industrial environment. Though, as a Ph.D. student I was not exposed to all industrial problems, I always enjoyed observing trends and the impact they have on our environment. This always puts research objectives in perspective.

I owe thanks to many more people than the limited space on these pages allow me to mention. Still, I would like to thank a few of them especially.

Foremost, I would like to direct my special thanks to Jef van Meerbergen for helping me to understand what research really is about, for his involvement in my work and for support every time I asked for it. I also would like to thank prof. Ralph Otten for his valuable comments on my work and for helping me to shape this thesis to what it has become today. Finally, I want to thank prof. Jochen Jess for encouraging me to aim for a Ph.D. in his group and for his interest in my work.

There are two more people I am especially grateful to. First, I want to thank Harry Veendrick for teaching me the secrets of correct-by-construction digital design and for our cooperation which, to a large degree, impacted my research. Second, I want to thank Bernardo Kastrup for making me believe in reconfigurable computing.

I thank Atul Katoch for his help in designing the ARCADE eFPGA chip during the long evenings of winter 2001, and Peter Poplavko, Alexander Danilin, Peter van de Haar and Frank Linssen for helping to customise the eFPGA mapping flow. I thank my group leaders at Philips Research (in chronological order): Engel Roza, Rob Woudsma, Albert van der Werf and Ad ten Berg for supporting my research. Also, I thank the members of the research groups, I was and still am a member of, at Philips and at the Eindhoven University of Technology.

Finally, I would like to thank my family for the understanding of my wish of pursuing a scientific 'career' and for their great support and encouragement. I owe special thanks to my mother for her belief that I would once reach this stage. I wish she could know she was right. I dedicate this thesis to her.

I also thank my parents-in-law for meaning to me much more than I ever expected and for making me feel in the Netherlands as in my home country.

Last, but definitely not least, I want to thank my husband, Jeroen, for his true love, support, understanding...and for his patience through so many years. Yes, it is time to pursue different types of challenges now...

KS

Hulsel, May 2004

Kasia Leijten.

# Contents

### Preface

| 1 | Intr | oductio  | n                                   | 1 |

|---|------|----------|-------------------------------------|---|

|   | 1.1  | Trends   | s in IC technology and applications | 2 |

|   |      | 1.1.1    |                                     | 2 |

|   |      | 1.1.2    |                                     | 3 |

|   |      | 1.1.3    |                                     | 3 |

|   |      | 1.1.4    |                                     | 3 |

|   | 1.2  | Desig    |                                     | 4 |

|   |      | 1.2.1    |                                     | 4 |

|   |      | 1.2.2    | Design productivity gap             | 5 |

|   |      | 1.2.3    |                                     | 6 |

|   |      | 1.2.4    | Computational efficiency gap        | 6 |

|   | 1.3  | SoC as   |                                     | 8 |

|   |      | 1.3.1    | Implementation trade-offs           | 8 |

|   |      | 1.3.2    | Heterogenous SoC                    | 8 |

|   |      | 1.3.3    | Platform-based design               | 9 |

|   | 1.4  | Embeo    |                                     | 0 |

|   |      | 1.4.1    |                                     | 0 |

|   |      | 1.4.2    | Focus and motivation                | 4 |

|   |      | 1.4.3    | State-of-the-art                    | 7 |

|   |      | 1.4.4    | Key challenges                      | 8 |

|   | 1.5  | Proble   | m statement                         | 9 |

|   | 1.6  | This th  | nesis                               | 0 |

|   |      | 1.6.1    | Towards a solution approach         | 0 |

|   |      | 1.6.2    | Main contributions                  | 0 |

|   |      | 1.6.3    | Organisation of the thesis          | 1 |

| 2 | Арр  | lication | domain specialisation 2             | 3 |

|   | 2.1  |          | Programmable Gate Arrays            | 3 |

|   |      | 2.1.1    | An evolving FPGA                    | 3 |

|   |      | 2.1.2    | Architectural trade-offs in FPGAs   | 8 |

IX

|   |      | 2.1.3 Quantifying the cost                                |

|---|------|-----------------------------------------------------------|

|   | 2.2  | The concept of application domain specialisation          |

|   | 2.3  | Application domain characterisation                       |

|   |      | 2.3.1 Type of processing                                  |

|   |      | 2.3.2 Word-size                                           |

|   |      | 2.3.3 Rent exponent                                       |

|   | 2.4  | Design flow                                               |

|   | 2.5  | Classification of reconfigurable logic architectures      |

|   |      | 2.5.1 Data-path-oriented architectures                    |

|   |      | 2.5.2 Random-logic-oriented architectures                 |

|   |      | 2.5.3 Memory-oriented architectures                       |

|   | 2.6  | Conclusions                                               |

| 3 | Dogi | c concepts 4                                              |

|   |      |                                                           |

|   | 3.1  | I I                                                       |

|   |      | 3.1.1 Background                                          |

|   |      | 3.1.2 Inversion-based folding type I                      |

|   | ~ ~  | 3.1.3 Inversion-based folding type II                     |

|   | 3.2  | Cost metrics                                              |

|   |      | 3.2.1 Architectural concepts                              |

|   |      | 3.2.2 Mapping cost                                        |

|   |      | 3.2.3 Implementation-based cost metrics                   |

|   |      | 3.2.4 Model-based cost metrics                            |

|   | 3.3  | Conclusions                                               |

| Ļ | Data | -path-oriented reconfigurable architecture 6              |

|   | 4.1  | Introduction                                              |

|   |      | 4.1.1 Characteristics of the application domain           |

|   |      | 4.1.2 State-of-the-art                                    |

|   | 4.2  | Applying the inversion-based folding type I               |

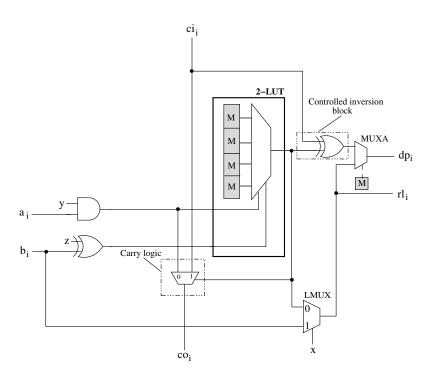

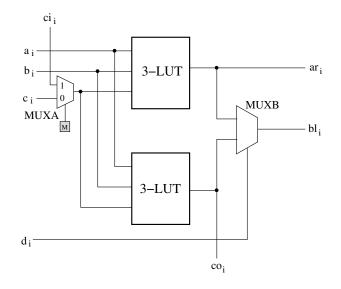

|   | 4.3  | Logic element                                             |

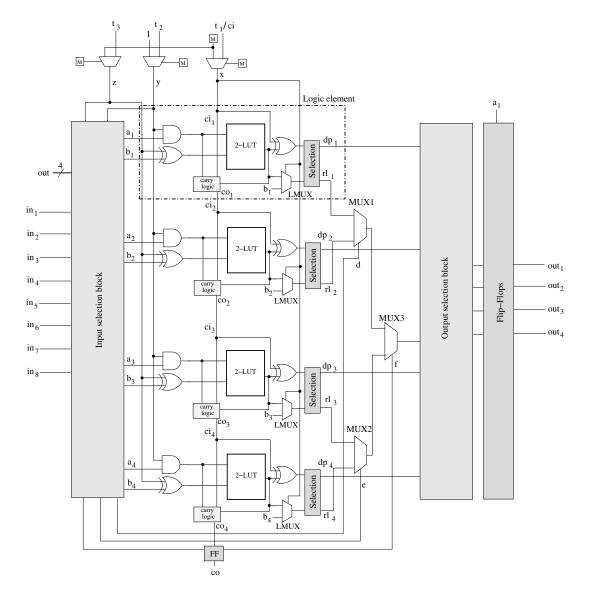

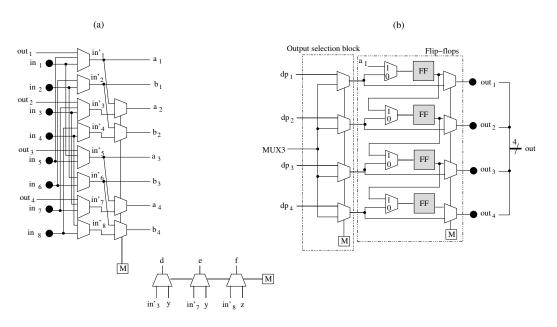

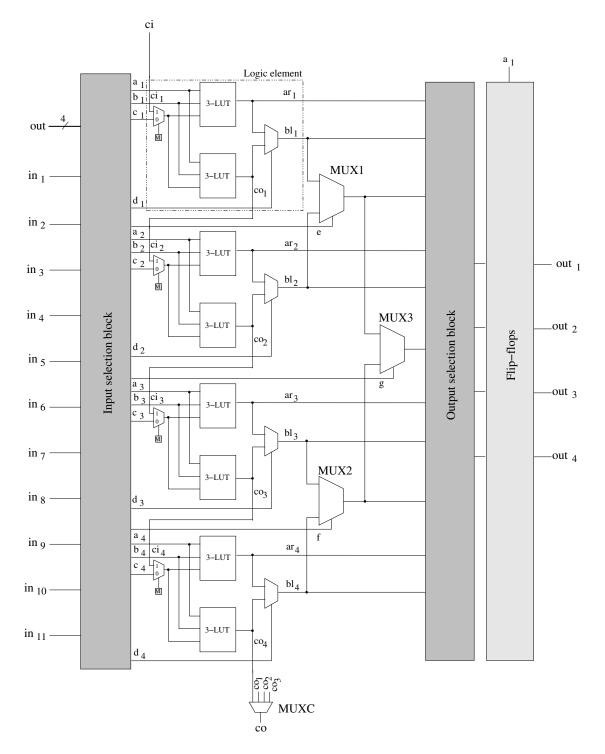

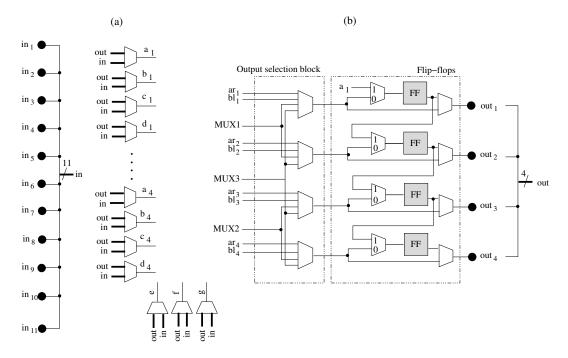

|   | 4.4  | Logic block                                               |

|   |      | 4.4.1 Basic concept                                       |

|   |      | 4.4.2         Structure in detail         7               |

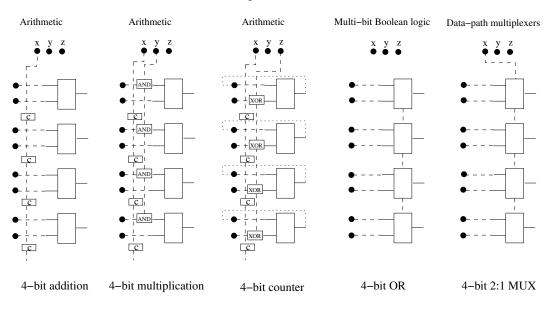

|   | 4.5  | Functional modes                                          |

|   | 4.5  |                                                           |

|   |      | L                                                         |

|   | 10   | 6                                                         |

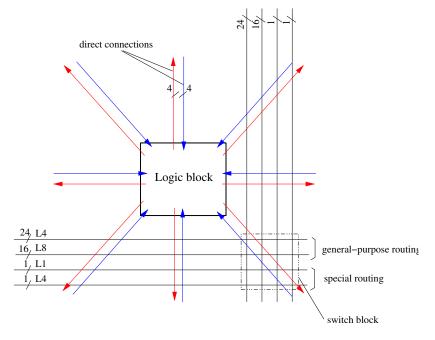

|   | 4.6  | Interconnect                                              |

|   |      | 4.6.1 Optimisation of the interconnect architecture 8     |

|   |      | 4.6.2 Complete interconnect architecture                  |

|   | 4.7  | Modified data-path-oriented reconfigurable architecture 8 |

|   |      | 4.7.1 Basic concept                                       |

|   |      | 4.7.2 Logic block                                         |

|   |      | 4.7.3 Functional modes                                    |

|   |     | 4.7.4 Interconnect                                             | 87 |

|---|-----|----------------------------------------------------------------|----|

|   | 4.8 | Benchmarking                                                   | 88 |

|   |     | 4.8.1 Benchmarking using the implementation-based cost metrics | 88 |

|   |     | 4.8.2 Benchmarking using the model-based cost metrics 9        | 93 |

|   |     | 4.8.3 Discussion                                               | 95 |

|   | 4.9 | Conclusions                                                    | 98 |

| 5 | Ran | dom-logic-oriented reconfigurable architecture                 | 99 |

|   | 5.1 | Introduction                                                   | 99 |

|   |     | 5.1.1 Characteristics of the application domain                | 99 |

|   |     | 5.1.2 State-of-the-art                                         | 99 |

|   | 5.2 | Logic element                                                  | 00 |

|   | 5.3 | Logic block                                                    | 01 |

|   |     | 5.3.1 Basic concept                                            | 01 |

|   |     | 5.3.2 Structure in detail                                      | 01 |

|   | 5.4 | Functional modes                                               | 04 |

|   |     | 5.4.1 Random logic mode                                        | 04 |

|   |     | 5.4.2 Arithmetic mode                                          | 05 |

|   | 5.5 | Interconnect                                                   | 05 |

|   | 5.6 | Benchmarking                                                   | 07 |

|   |     | 5.6.1 Benchmarking using the model-based cost metrics 10       | 07 |

|   |     | 5.6.2 Discussion                                               | 07 |

|   | 5.7 | Conclusions                                                    | 10 |

| 6 | Mer | nory-oriented reconfigurable architecture 11                   | 11 |

|   | 6.1 | Introduction                                                   | 11 |

|   |     | 6.1.1 Characteristics of the application domain                | 11 |

|   |     | 6.1.2 State-of-the-art                                         | 12 |

|   | 6.2 | Applying the inversion-based folding type II                   | 14 |

|   | 6.3 | Logic element                                                  | 16 |

|   | 6.4 | Logic block                                                    | 19 |

|   |     | 6.4.1 Basic concept                                            | 19 |

|   |     |                                                                | 19 |

|   | 6.5 | Functional modes                                               | 23 |

|   |     | 6.5.1 Data-path mode                                           | 23 |

|   |     | 6.5.2 Random logic mode                                        | 30 |

|   |     | 6.5.3 Memory mode                                              | 31 |

|   | 6.6 |                                                                | 37 |

|   | 6.7 | -                                                              | 39 |

|   | 0.7 | Interconnect                                                   | 57 |

|   | 6.8 |                                                                | 40 |

|   |     | Benchmarking                                                   |    |

|   |     | Benchmarking                                                   | 40 |

| 7  | Tem                | late-based methodology for reconfigurable logic design 1 | 147 |  |  |  |  |

|----|--------------------|----------------------------------------------------------|-----|--|--|--|--|

|    | 7.1                | Гhe concept                                              | 147 |  |  |  |  |

|    | 7.2                | The reconfigurable logic architecture template 1         | 149 |  |  |  |  |

|    |                    | 7.2.1 Level I – Logic element                            | 150 |  |  |  |  |

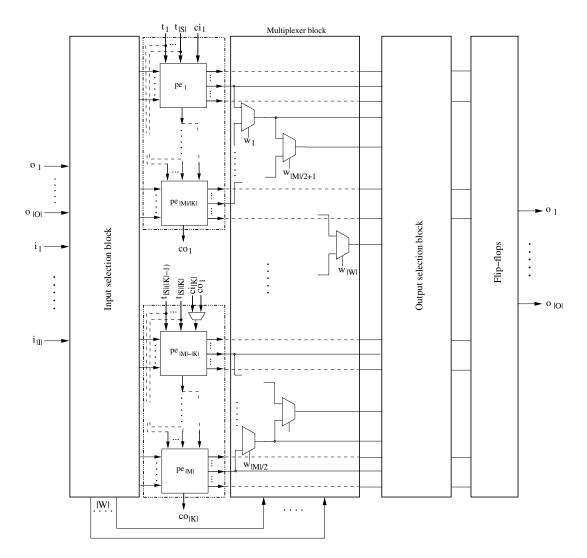

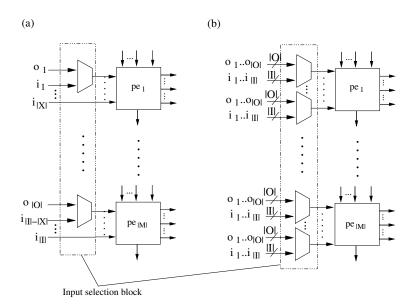

|    |                    | 7.2.2 Level II – Processing element                      | 151 |  |  |  |  |

|    |                    | 7.2.3 Level III – Logic block                            | 153 |  |  |  |  |

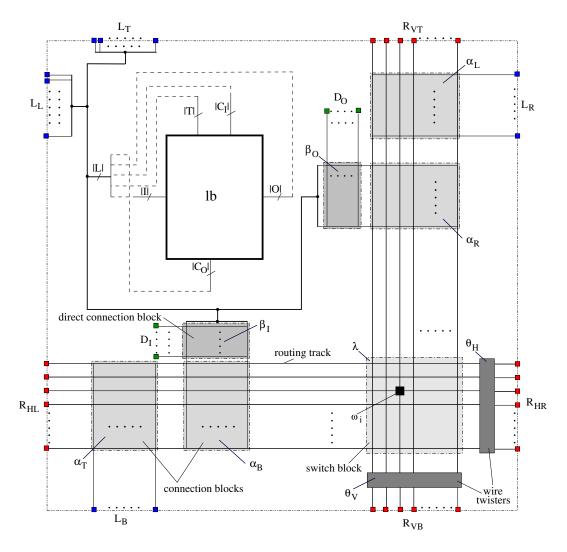

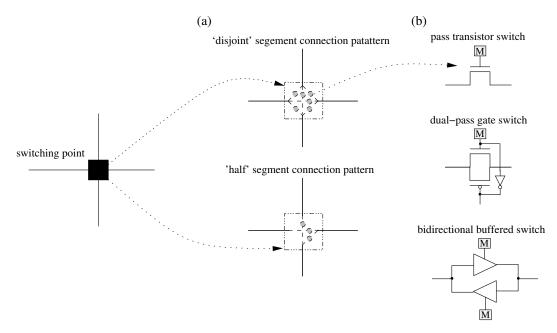

|    |                    | 7.2.4 Level IV – Tiles                                   | 157 |  |  |  |  |

|    |                    | 5                                                        | 166 |  |  |  |  |

|    | 7.3                | e i                                                      | 167 |  |  |  |  |

|    |                    | 1                                                        | 168 |  |  |  |  |

|    |                    |                                                          | 171 |  |  |  |  |

|    | 7.4                | i C                                                      | 172 |  |  |  |  |

|    |                    | 1                                                        | 172 |  |  |  |  |

|    |                    |                                                          | 172 |  |  |  |  |

|    |                    |                                                          | 173 |  |  |  |  |

|    | 7.5                | Conclusions                                              | 175 |  |  |  |  |

| 8  | Cas                | study: memory-oriented eFPGA core                        | 177 |  |  |  |  |

|    | 8.1                | VLSI implementation aspects                              | 177 |  |  |  |  |

|    |                    | 8.1.1 Memory design                                      | 177 |  |  |  |  |

|    |                    | 8.1.2 Programmable interconnect design                   | 181 |  |  |  |  |

|    | 8.2                | Prototype chip                                           | 183 |  |  |  |  |

|    | 8.3                | Cost comparison                                          | 187 |  |  |  |  |

|    | 8.4                | Conclusions                                              | 188 |  |  |  |  |

| 9  | Con                | usions 1                                                 | 189 |  |  |  |  |

| Bi | bliog              | phy 2                                                    | 202 |  |  |  |  |

| Pe | rsona              | contribution 2                                           | 203 |  |  |  |  |

| Su | ımma               | 2                                                        | 207 |  |  |  |  |

| Sa | Samenvatting 20    |                                                          |     |  |  |  |  |

| Cı | Curriculum Vitae 2 |                                                          |     |  |  |  |  |

## INTRODUCTION

We are witnessing today the third phase of computing. To clearly differentiate from the mainframe-oriented and PC-oriented computing of the first two phases, the computing of the third phase is often defined as the *post-PC* or '*post.com*' *computing* [35]. The post-PC computing, featuring applications such as ubiquitous communication and ambient intelligence, has been made possible thanks to advances in integrated circuit (IC) technology within the last few decades. During this time, a positive-feedback-like dependence between computing systems and semiconductor technology has appeared [88]. The ever-continuing CMOS scaling allows the number of transistors per unit area to be doubled every process generation [56]. At the same time, the increased transistor density enables designing more complex yet more demanding systems which, in turn, challenge silicon technology.

The continuous demand for performance and bandwidth has been, and still is, the main driving force behind such technological evolution [28]. However, while silicon area has been the predominant cost function of computing up till now, today power consumption is becoming the main limiting factor [28]. This is because power dissipated in integrated circuits increases with the increase of the IC complexity (the increase of the total switching capacitance), an operating frequency [108] and a bit-rate [83]. Furthermore, a low cost and a small form factor are the key requirements for ICs targeting ubiquitous terminals and ambient devices. According to today's predictions, within a five year scale the price for a 2 mm<sup>2</sup> IC for this type of applications (excluding the battery and package costs) will be about 20 dollar cents [16]. To reach such a cost level, inexpensive chip packages and miniature smart batteries as the main power source will have to be used. Unfortunately, standard chip packages have strictly limited power dissipation capabilities today and the battery life-time is measured in months rather than years.

As the complexity of modern IC increases, so do their design and manufacturing costs. The non-recurring engineering costs (NRE) are the subject of a particularly dramatic growth. For example, the cost of the mask set for a single chip exceeds half a million dollars today [124]. This puts an additional constraint on the design of cost-sensitive consumer electronics products. At the same time, the market-

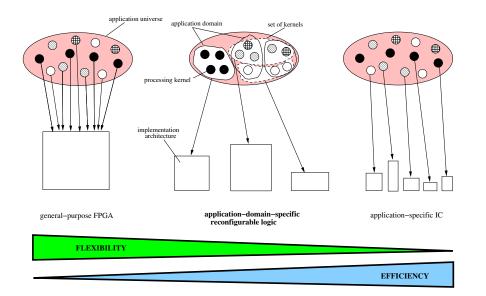

dependent economy enforces very short product design cycles and the frequent change of the product features. In consequence, intrinsic flexibility as a means of reducing design and production costs, but also as a way of extending the product life-time, is of key importance today [39, 62, 88, 20]. We define *flexibility* as a capability of an electronic device to change its function after the device is fabricated. We also use the term '*efficiency*' to describe the degree to which an electronic device uses its resources to realise its function [59].

In the light of the above-presented facts, finding a balanced trade-off between flexibility and efficiency in computing systems, and in particular in embedded systems on silicon, is crucial today. The mature semiconductor technology and rich computing 'know-how' open new possibilities of successfully bridging the costefficiency gap induced by traditional design approaches. In this thesis, we focus on one of such promising paradigms, namely *reconfigurable computing*, and apply it to the design of embedded systems on silicon.

## 1.1 Trends in IC technology and applications

The technology, on the one hand, and applications, on the second hand, define the context. In this section, we survey current trends that can be observed in the IC technology and its applications.

#### 1.1.1 Technology scaling

The idea of *scaling* has been the primary enabler of an exponential growth in semiconductor technology. The scaling principles [40, 10] describe the pace, expressed in a scaling factor  $\alpha$ , at which geometrical parameters of MOS devices, interconnect wires and the supply voltage value scale when moving to smaller process technologies. The actual scaling trend observed throughout the years follows Gordon Moore's predictions from 1975 [74] (the so-called *Moore's law*). The scaling factor  $\alpha = 0.7$  is assumed today to characterise this trend. Assuming the fixed complexity of an IC, the scaling translates into the following effects [108] that accompany each new process generation (about every 18 months [57]):

- the reduction in the silicon area by a factor of 2 ( $\alpha^2$ ),

- the increase of the chip performance by roughly a factor of 1.5 ( $\alpha^{-1}$ ),

- the reduction of power consumption by a factor of 2 ( $\alpha^2$ ).

The key benefit of the scaling phenomenon is thus the reduction of cost and increase in performance.

#### 1.1.2 System-on-a-chip

The dramatically progressing silicon scaling has enabled *ultra-large scale integration.* As a result, various system components, such as memories, logic, RF modules and sensors, which were traditionally integrated on a printed circuit board (PCB), could be integrated on a single chip using silicon as an implementation medium. To express this level of integration, the term '*system-on-a-chip*' (*SoC*) has been introduced.

The SoC market has experienced a steady and consistent growth over the last few years. One estimates that today 50% of all ASICs are produced based on the SoC concept, and this percentage is expected to grow to 80% in 2005 [89]. This can be explained by the advantages of SoCs, such as a greater integration of components, an increased speed of the communication between the system components, lower packaging and test costs, and improved reliability of a system.

#### **1.1.3** Ambient computing

One of the major consequences of the ultra-large scale integration is a clear change in the use of computing. Unlike the first two *general-purpose computing* phases, the third phase features computing which is seemingly hidden in the background and thus almost invisible to a user ('People to the foreground, technology to the background'). This type of computing is referred to as *'ambient computing'*. Its main characteristics are: an embedded context, awareness of the environment, personalisation, and an adaptive and anticipatory character [27].

The ambient computing devices are distributed in the human environment (e.g. home and work) to maximise human efficiency and improve well being. The use of ubiquitous communication networks to connect such devices will be essential in the near future [84].

Ambient computing is considered as a possible future of consumer electronics that can stimulate the market growth [16]. Already today, simple electronic devices with an ambient-like character are being made. Moreover, many institutes all over the world fund research projects aiming at the investigation of new technologies for ambient computing. It has been declared that about four billion dollars will be spent on such activities over the next several years [27].

#### 1.1.4 Embedded systems on silicon

The emerging applications, and ambient computing applications in particular, are realised in the form of embedded systems. An *embedded system* is a system designed to perform a dedicated or a narrow range of functions as a part of a larger system, usually with a minimal end-user interaction. Because of the tight cost constraints (in terms of size, power, performance, unit price, time-to-market, etc.),

today's embedded systems heavily exploit the system-on-a-chip design concept allowing all system components to be integrated on a single piece of silicon. Therefore, in this thesis we will restrict ourselves to embedded systems implemented as systems-on-a-chip.

Unlike other, general-purpose computing systems, embedded systems are application-domain-specific. Furthermore, their behaviour is defined by the interaction with the environment [46]. Due to real-time constrains imposed by the environment, signal processing, which deals with a transformation of signals from the environment (mostly in a digital way), plays an essential role. Therefore, embedded applications impose very high requirements on the overall system performance. For example, the computational load of an ambient intelligence system ranges from 10 MOPS (Mega-Operations-Per-Second) for lightweight audio processing to 1 TOPS (Tera-Operations-Per-Second) for synthetic video generation [16].

### **1.2 Design challenges**

A design is a result of the search for a satisfactory match between a target application and an available technology. However, the design is, to a large extent, also constrained by economic and other factors [20]. To explain this, we describe the main challenges IC designers face today.

#### **1.2.1** Silicon economics

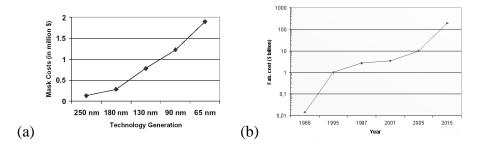

The cost aspect has always been the main consideration in SoC design [56]. Today, the exploding complexity of process technology has reached the point where design and chip fabrication costs impose stronger limitations on the performance and function of produced systems-on-a-chip than physics itself [12, 45] (see Figure 1.1). The NRE (Non-Recurring Engineering) costs related to each design, and mask set costs in particular, are of especially great concern [112]. The cost of a complete photo-mask set in a state-of-the-art 0.13  $\mu$ m process is about 0.75 million dollars today. Due to the continuously raising complexity of sub-length lithography [20], which will be even more significant in nanometre process technologies, this cost will reach a level of almost two million dollars in two process generations from now (that is, for the 65 nm technology node) [124]. This trend is accompanied by sky-rocketing chip fab costs. A basic plant for 0.18  $\mu$ m production costed four billion dollars (\$4 billion) and, according to what is known as Rock's law, the cost of equipment to produce ICs will be doubling every four years [58].

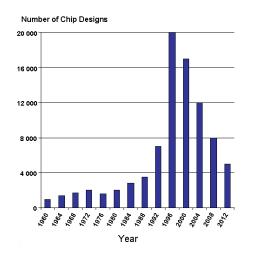

Already today such quickly rising costs have a strong impact on the chip production, especially for low-volume markets. A much higher volume or a much higher cost per unit are required to amortise the expenses. It is predicted that this trend will lead eventually to a considerable decrease in the overall number of chip designs (see Figure 1.2) since only a very few companies will be able to afford them.

Figure 1.1. The increasing IC costs: (a) a mask set costs increase (Source: Zuchowski et al., ICCAD 2002 [124]), (b) a fabs costs increase (Source: Kellog TechVenture, 2001).

Finally, there is an increasing effect of logistic costs. Such costs are associated with managing a large variety of different products or product families, marketing, management, supply chains, etc.

Figure 1.2. The predicted decrease in the number of chip designs (Source: Gartner Dataquest, November 2001).

#### 1.2.2 Design productivity gap

The shift towards more and more advanced process technologies is accompanied not only by the design cost increase but also by a dramatic increase of the design complexity. Firstly, the complexity of components being designed, and consequently the system complexity (in terms of the number of transistors and complexity of embedded software) are growing exponentially [56]. Secondly, due to more devices available on the same die, but predominantly due to deep-submicron effects [108], the technology in which it is being designed is becoming more complex. Finally, the tools that are used to design today's systems are becoming more and more sophisticated in their usability and are characterised by increased runtimes. For example, the verification phase of a design process allocates today more than 50% of the total human and computer resources [56].

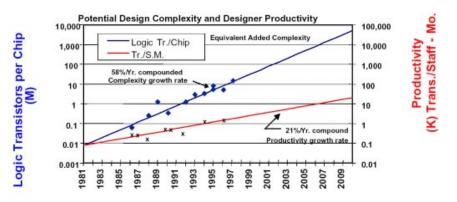

**Figure 1.3**. The design productivity gap being a result of a disproportion between the complexity of silicon and the design complexity which can be handle (Source: ITRS 1999 [56]).

Figure 1.3 illustrates a big gap between design complexity and design productivity which is a direct consequence of the above-mentioned trends. The complexity of designs which can be realised in a state-of-the-art technology grows 58% per year, while the designer's productivity grows at a pace of only 21% per year.

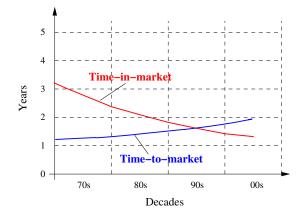

#### 1.2.3 Time-to-market versus time-in-market

The increasing complexity of integrated circuits has led to a considerable increase of the design time that is needed before the release of a new generation of products. This time is often referred to as *'time-to-market'*. At the same time, the constant availability of more and more sophisticated devices on the market has increased the customers' expectations towards the functionality and the frequency of appearance of new products. This caused a steady reduction of the product lifetime, which is often called *'time-in-market'*, resulting eventually in a collision of both, as illustrated in Figure 1.4.

It is not uncommon today that for certain classes of products the time-to-market exceeds the time-in-market. The unpredictable behaviour and the competitive character of the market imply that only economically-healthy companies, which offer products with a clear advantage over the competitors, can survive.

#### 1.2.4 Computational efficiency gap

Because of the key importance of the low-power capabilities, modern ICs are designed for the largest *computational efficiency* expressed in MOPS per Watt, that

Figure 1.4. The collision of the product life-time (time-in-market) and the product development time (time-to-market) (Source: Lautzenheiser & Wersall, November 1999 [66]).

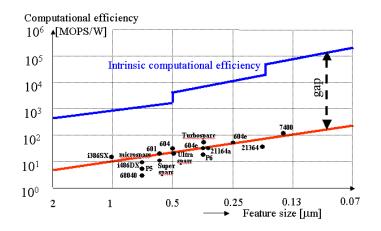

is Mega(million)-Operations-Per-Second-per Watt, rather than for a highest performance only. In Figure 1.5, a comparison between intrinsic computational efficiency of silicon (ICE) and computational efficiency of programmable processors projected onto different technology nodes is shown [88]. The comparison is based on the hypothetical assumption that a full match between the application and the architecture, and thus the maximum performance in operations-per-second, is achieved. A 32-bit addition is used as a basic benchmark function.

Figure 1.5. Computational efficiency of silicon and programmable processors versus technology (Source: Roza, December 2001 [88]).

It is apparent from the figure that there is a two-to-three order of magnitude *gap* between the available (silicon) and achievable (processors) computational efficiency. The gap represents a mismatch between pure-hardware and pure-software implementations that are typical for ASICs and programmable processors, respectively.

### **1.3 SoC architecture**

The realisation of a given computing task (application) involves various trade-offs. The decisions that are made by a designer based on the essential design criteria determine the effectiveness and cost-efficiency of the final IC [59]. In the systemon-a-chip design, different, more complex, design metrics and design constraints are used than in traditional hardware or software implementations. In this section we focus on the trade-offs that are typical for the implementation phase of the design process and we discuss their implications on the SoC architecture.

#### **1.3.1** Implementation trade-offs

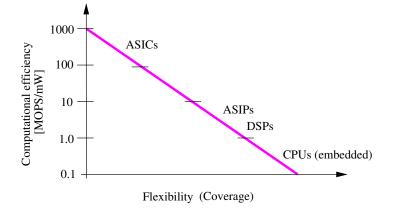

The large disproportion in the computational efficiency of ASICs and programmable processors, which has been shown in Figure 1.5, suggests that there exists a spectrum of possible implementation scenarios that can be deployed to meet the required *flexibility versus cost trade-off*. For example, computational efficency of programmable processors can be increased if processors are optimised towards a target application domain. The potential implementation options, in the order of their increasing cost-efficiency, include then (but are not limited to):

- *CPUs (Central Processing Units)* general-purpose processing units which are characterised by a sequential type of processing and a simple instruction set. CPUs are used typically for control tasks or for handling events that determine the mode or the configuration of the system.

- *DSPs (Digital Signal Processors)* processors which are optimised for processing digital signals. DSPs include dedicated hardware components and exploit instruction level parallelism. They are typically used for the applications requiring a medium throughput and the sampling frequencies in the range of kHz (e.g. audio, speech).

- ASIPs (Application-Specific Instruction-set Processors) domain-specific processors which are characterised by a well-defined intruction set that is tuned to the execution of critical parts of the application code. ASIPs target high-throughput processing with the sampling frequencies in the range of MHz (e.g. video).

The above-described implementation approaches are compared in Figure 1.6 [81]. Each implementation type is characterised by its computational efficiency (in MOPS/mW) and by its flexibility which is regarded here as the range of applications the implementation can cover.

#### 1.3.2 Heterogenous SoC

Despite a large spectrum of possible implementation approaches, none of the presented scenarios fully meets requirements of today's applications. This is because

a homogenous type of architecture is not suited to efficiently deal with numerous computational models and various data and time granularity that such applications require [81]. Therefore, a today's system-on-a-chip is heterogeneous and contains components such as: general-purpose processor cores, DSP cores, ASIP cores, coprocessors, peripherals, buses and network protocols, as well as memories. The size of a typical IC and the area of a single processor core, which in nanometre process technologies usually does not exceed 1-2  $mm^2$ , suggest that a complex SoC may contain between 50 to 100 such cores.

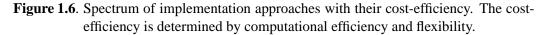

#### 1.3.3 Platform-based design

To guarantee the required level of computational efficiency while avoiding a disproportionate design effort due to the growing complexity and diversity of designs, the concept of system platform has been introduced [44, 62, 20]. The system platform is defined as a family of hardware and software modules, configured in a prescribed communication structure, that can be shared across multiple applications from a target application domain, and to which a unified design process can be applied. We refer to the hardware component of a system platform as a *silicon* system platform [28, 88]. Typically, the architecture of a silicon system platform is described by a means of a generic model called *template*. The template instantiation means in this context a process of the creation of application-domain-specific designs. The designs differ only in the number and kinds of modules integrated together. By the integration of programmable cores, which are preferred from the flexibility point of view (i.e. software mapping), and dedicated coprocessor cores that implement specialised functions, a desired trade-off between flexibility and cost can be achieved. A typical example of a silicon system platform is depicted in Figure 1.7.

Figure 1.7. The architecture of a typical silicon system platform.

## **1.4 Embedded reconfigurable computing**

Although the concept of the system platform represents a significant step towards designing cost-efficient embedded systems-on-a-chip, it is not the ultimate solution [48]. The system platforms reduce the complexity of the design process through the extensive *reuse* of hardware and software components, providing thus a faster time-to-market. The same reduction in the design complexity is obtained, however, at the price of reduced flexibility (silicon platforms with dedicated hardwired co-processors can cover only a specific range of applications) and reduced performance (the need for flexibility favours the use of computationally less efficient programmable cores). Finally, the realisation of a specific instance of a silicon platform is always associated with the fabrication of a new chip. This takes time and money.

These problems can be resolved if the *reconfigurable computing (RC)* paradigm is applied to the design of embedded systems. To differentiate from reconfigurable computing in a traditional sense, that is, concerning stand-alone devices (such as FPGAs; see below), we will refer to reconfigurable computing in the embedded context as *embedded reconfigurable computing (eRC)*. In this section, we explain what reconfigurable computing is, we motivate its importance for embedded systems-on-a-chip, and we survey state-of-the-art systems employing eRC paradigm. Finally, we discuss the key challenges in the design of embedded RC hardware.

#### **1.4.1** Reconfigurable computing up close

*Reconfigurable computing* is a method of performing computations using reconfigurable computing devices [37]. Because programmable and reconfigurable computing architectures can be viewed as two extremes in the unified design space [37], a clear definition of a reconfigurable computing device is difficult. Nevertheless, throughout this thesis we assume that a *reconfigurable computing device* is characterised by a *configuration*, which defines the device functionality and can-

not be changed from cycle to cycle, and by *flexible interconnect* that determines the data-flow between operations [37].

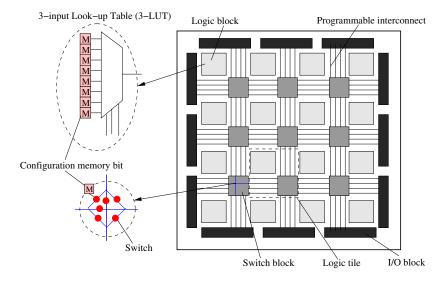

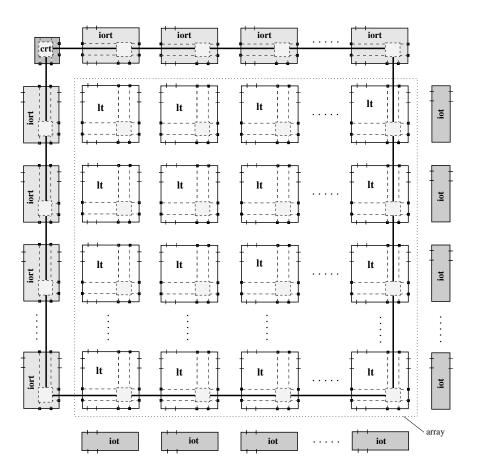

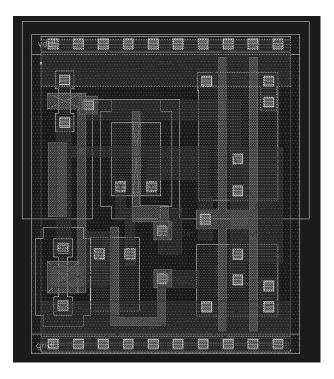

Figure 1.8. An example FPGA architecture.

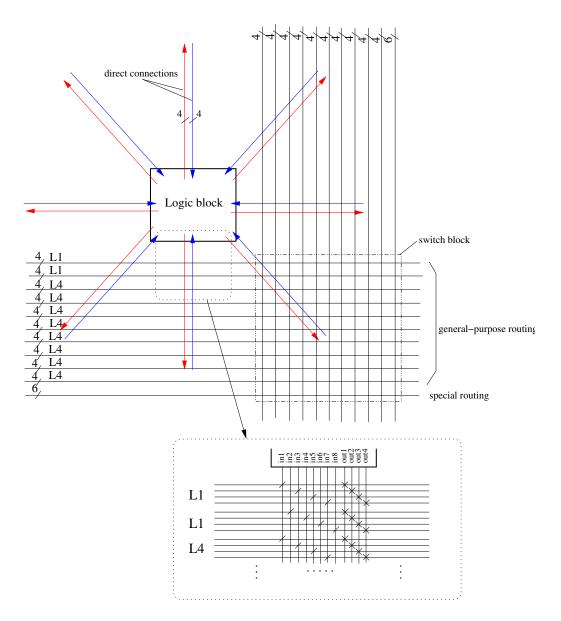

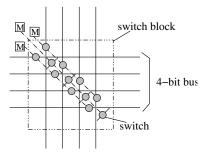

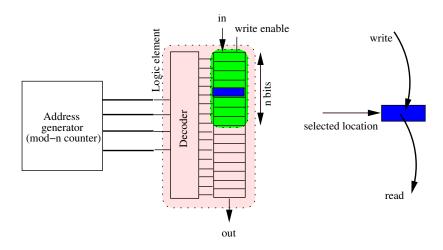

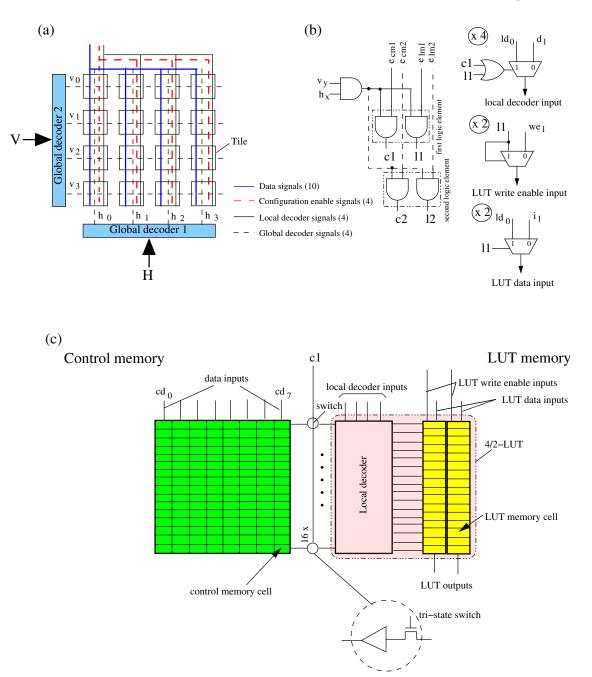

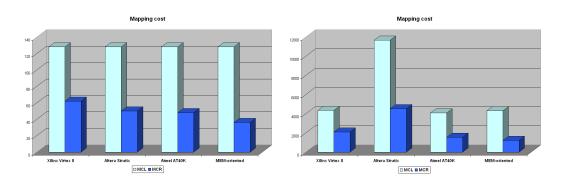

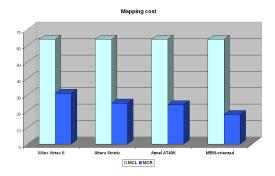

A typical reconfigurable computing device is a *Field Programmable Gate Array* (*FPGA*) (Xilinx, 1985 [24]). The general structure of a classical FPGA is shown in Figure 1.8. An FPGA is built as an array of computing elements called logic blocks. A look-up table (LUT) is commonly used as the basic computing element of a logic block. The logic blocks are connected via a programmable interconnect network and are surrounded by input-output (I/O) blocks. The programmable interconnect network consists of horizontal and vertical routing channels. Each routing channel includes segmented routing tracks of a different length. This allows performance-efficient communication at different distances. The interconnect segments are connected via programmable switches located in switch blocks. In FPGAs, both the functionality of logic blocks and connections between them are programmable. Programming is done by loading configuration data to a configuration (control) memory. Such a memory controls LUT memory bits and multiplexers and switches of the interconnect network.

#### **Reconfigurable devices versus ASICs and programmable processors**

The key advantage of a reconfigurable computing device is the trade-off between flexibility and cost such a device offers. The trade-off is reflected in the organisation of computations and in the functionality binding time [39].

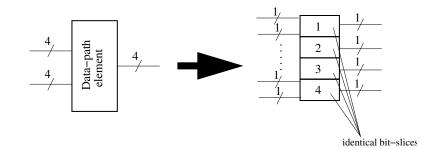

The *organisation of computations* (or the way of implementing computations) relates to the concepts of *computing-in-space* and *computing-in-time* that describe ASIC and programmable processor implementations, respectively. Similarly to ASICs, FPGAs implement computations using *spatially distributed* basic computing elements. When combined together, such elements realise complex operations. This is in contrast to programmable processors in which computing elements are coarser and are *distributed in time*. This means that the availability of such elements is dependent on the supplied instruction on a cycle-by-cycle basis. The important advantages of computing-in-space compared to computing-in-time are lower power consumption and higher performance. This is achieved by matching the word-size of computing elements to the word-size of arguments of operations that are to be executed, and by exploiting lateral parallelism. The result is, however, a more restricted domain of computations that may be executed. Also, the final design is characterised by a larger area, longer delays and higher power dissipation than traditional ASIC designs.

The second aspect, the *functionality binding time*, relates to the technology. It determines the moment of assigning functionality (defining the computations) to the underlying hardware. In this respect, reconfigurable computing devices and programmable processors fall into the same category. In both, the functionality is defined after the fabrication of the device. Furthermore, they both use the notion of software (in the form of a configuration context or an instruction) to define the functionality. But, while the time needed to change the configuration in a traditional reconfigurable computing device is in the order of microseconds to milliseconds, the change of instruction in a programmable processor takes usually only a single cycle. ASICs, unlike reconfigurable and programmable devices, are characterised by the pre-fabrication functionality binding time. Dependent on the type of ASIC, this time may be associated with the moment as early as creating the first mask of a design (custom and semi-custom ASICs) or as late as creating the last (metal) mask(s) (gate arrays and structured ASICs [121, 41]). Furthermore, hardware rather than software is used for the device customisation. The non-permanent, post-fabrication customisation of reconfigurable devices and programmable processors implies flexibility. Therefore, the same piece of silicon may be reused to implement different applications. However, such flexibility is obtained at the cost of larger area, lower performance and higher power consumption compared to ASICs. In programmable processors, the high intrinsic cost is due to the control overhead and the fixed width of the data-path. In reconfigurable logic, the reason for the high intrinsic cost are a large configuration memory, a large number of programmable switches and a rich interconnect structure.

#### Spectrum of reconfigurable computing architectures

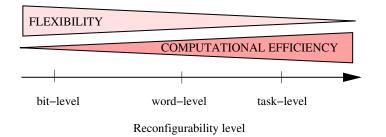

Reconfigurable computing devices can be classified by two main parameters, namely the granularity of computations and a reconfiguration model. The *granularity* expresses the level of complexity of functional primitives (usually defined by the word-size of their arguments) that can be executed in computing elements of such devices. The granularity of reconfigurable devices is thus analogous to the data-path width in programmable processors [39]. Reconfigurability at different levels of granularity is exploited. For example:

- *bit-level granularity* which is characteristic for devices that control and process single-bit-wide or a-few-bit-wide data (e.g. traditional FPGAs),

- *word-level granularity* which is typical for devices with coarse computing elements (e.g. ALUs, multipliers, adders) and reconfigurability at the level of words,

- *task-level granularity* which is typical for architectures in which complete tasks rather than simple operations are reconfigured and switched between.

Often, the bit-level reconfigurability is referred to as *fine-grain reconfigurability*, and the word-level and task-level reconfigurability together as *coarse-grain reconfigurability*. The lower the level of granularity, the larger is the configuration memory and its overhead, and thus the higher is the intrinsic cost of a reconfigurable computing device. On the other hand, the higher the level of granularity, the more complex operations can be directly executed at the expense of lower flexibility. This trade-off is illustrated in Figure 1.9.

**Figure 1.9**. The impact of granularity on the intrinsic cost and flexibility of reconfigurable computing devices.

The *reconfiguration model* defines the frequency of the reconfiguration process and the smallest amount of resources that can be reconfigured at once. Using these parameters as basic characteristics, we can classify reconfigurable computing devices into the following categories:

• *Statically-reconfigurable* devices, the configuration of which can be changed only before the operation of a device, and *dynamically reconfigurable* devices in which the change of the configuration during the device operation is possible. Statically-reconfigurable devices have the single-context configuration memory, while dynamically reconfigurable devices have typically a multi-context configuration memory. The multi-context memory allows a fast context switching. This feature is often utilised for the implementation of the so-called run-time reconfiguration. *Run-time reconfigurable* devices execute computing tasks in phases, with each phase defined by a single configuration context.

• *Fully reconfigurable* devices in which even a minor change in the configuration requires the complete reloading of the entire configuration context, and *partially reconfigurable* devices in which only a portion of the configuration context can be changed with no influence on the rest of the configuration.

The ever-progressing technology scaling has enabled the realisation of computing architectures that offer different cost-efficiency trade-offs. Therefore today, the spectrum of (reconfigurable) computing architectures is the continuum of different computing approaches, and the choice of a particular approach is dictated by design criteria.

#### 1.4.2 Focus and motivation

In this thesis we restrict ourselves to fine-grain reconfigurable computing only. Consequently, we use the term 'embedded reconfigurable logic' (eRL) or simply 'reconfigurable logic' to describe the technology that supports this type of computing and allows the on-chip integration. Note, that reconfigurable logic can be considered as a design (implementation) style that co-exists with other design styles, such as standard cells and gate arrays, for example. In this respect, embedded reconfigurable logic can be viewed as an alternative to the hard-wired logic offered by the ASIC technology. This means that from the design point of view, logic blocks of an embedded reconfigurable logic core (an embedded FPGA) play a similar role as logic cells of a standard cell library. Also, both in the ASIC and eFPGA technology connections between logic elements are customised based on the requirements of the mapped function. The structure and functionality of the logic elements (logic blocks) and the rules governing communication between them define the *implementation architecture*.

The key benefit of applying embedded reconfigurable computing to the design of embedded systems-on-a-chip is the increase of flexibility and computational efficiency of the final silicon product. Thus, in the context of the platform-based design embedded reconfigurable logic may be seen as an extension or a supplement of the spectrum of traditional implementation approaches which are available in the form of hard-wired and programmable cores. Figure 1.10 illustrates two potential application scenarios and the consequence of their use. The scenarios assume the use of embedded reconfigurable logic as a replacement for hard-wired logic (the *ASIC context*) and as the way of augmenting the efficiency of programmable cores (the *programmable processor context*). In the first scenario, the emphasis is on the increase of flexibility at the cost of slightly reduced computational efficiency (and the area increase) compared to a reference ASIC implementation. In the second scenario, the main motivation is the increase of computational efficiency at the cost of some increase in silicon area (not shown in the figure).

**Figure 1.10**. The motivation for using embedded reconfigurable logic for embedded SoC designs. The bold and thin arrows represent real and ideal (no cost penalty) cases, respectively.

The main benefits of embedded reconfigurable logic include thus:

- *Cost reduction*: the opportunity of reusing the same piece of silicon for diverse types of functionality allows sharing the mask set costs between different products, and thus the reduction of NRE costs. By augmenting flexibility, logistic costs that are associated with the maintenance and support of large families of slightly different customised products can also be decreased. Finally, by allowing the implementation of test, debug and repair structures in reconfigurable logic, the number of erroneous products can be decreased.

- *Shorter time-to-market*: a high degree of reuse and direct availability of silicon enable a very fast response to the customer's needs. The long design cycles are avoided and the final, competitive, product is faster on the market (even if it still has to be 'tuned' in the later phase).

- *Prolonged time-in-market*: the 'built-in' flexibility in the offered products allows the functionality updates that are needed because of the changing standards, for example. The risk associated with the market uncertainty can also be decreased.

- *Increase of efficiency (computational efficiency)*: lateral parallelism and matching granularity of operations to the arguments' size allow building of cost-efficient hardware accelerators that augment software-based implementations. The code for the acceleration can be identified on the fly.

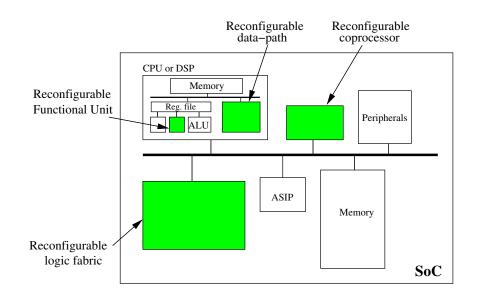

In Figure 1.11, a reconfigurable system-on-a-chip is shown. Typical methods of integrating reconfigurable logic fabric with other system resources are illustrated. The methods are: a reconfigurable functional unit, a reconfigurable data-path, a reconfigurable coprocessor, a reconfigurable logic fabric. Note, that the first three methods relate to the programmable processor context, while the latter method to the ASIC context (see the discussion above).

Figure 1.11. Applying reconfigurable logic in the SoC context.

The application examples of using embedded reconfigurable logic in the SoC context include (but are not limited to):

- Hardware acceleration (*the processor context*). Fine-grain accelerators are used for speeding-up an irregular or a critical type of application code. Such a code may contain both logic and arithmetic operations which are inefficiently implemented using standard resources of programmable processors. Typical examples are bit-level manipulations and arithmetic operations with arguments, the width of which is smaller (or larger) than the width of the processor data-path. The identified code can be replaced by custom instructions which are implemented in reconfigurable logic [36]. Also Application-Specific Units (ASUs) are interesting candidates. Rather than implementing such ASUs in hard-wired logic (as it is done in typical ASIPs), they can be mapped onto reconfigurable logic. This broadens the application area and extends the life-time of a final product.

- **Product differentiation** (*the ASIC context*). To meet requirements of different customers, companies providing hard programmable cores have to manage and support a large spectrum of products that only slightly differ in functionality. This is economically unjustified, even more that a new chip has to be manufactured for each such a product. By integrating some amount of reconfigurable logic with a standard core, it is possible to do per-user-customisations in an already-fabricated chip. As a result, only one version of such a chip rather than very many of them has to be supported. An example are peripherals for microcontroller cores.

- Multi-standards realisation (*the ASIC context*). Today's ICs (cores or complete systems) are often designed to support different standards (e.g.

for interfaces or communication protocols). The typical realisations of such standards are independent dedicated hardware modules that are integrated on the chip. This increases the chip area and causes an overhead since only one or a very few such modules are active at the same time. On the other hand, including all possible standards on a single chip is practically impossible and economically unjustified. Due to insufficient performance, programmable processors are also not an option. For these reasons, using embedded reconfigurable logic for the implementation of various standards is an interesting alternative. Eventually, the total silicon area of the final IC may be even reduced.

#### 1.4.3 State-of-the-art

The methods of using embedded reconfigurable logic in today's SoC products can be categorised in two dimensions. One dimension describes the *use method* of eRL, that is, whether eRL is applied to a complete hardware platform or to a component (core) of such a platform. The second dimension specifies the *scope* of eRL within that application area, that is, whether eRL constitutes the whole element or is only a part of it. Such a taxonomy is shown in Table 1.1 together with examples of state-of-the-art products belonging to each category.

| Use method $\Rightarrow$ | Complete                       | Component               |

|--------------------------|--------------------------------|-------------------------|

| Scope ↓                  | platform                       | of a platform           |

|                          | Xilinx Virtex-II Pro           | Actel VariCore          |

|                          | Altera Excalibur               | Leopard Logic HyperBlox |

| Full                     | Atmel FPSLIC                   | Elixent RAP             |

|                          |                                | PACT XPP                |

|                          | (platform-based FPGAs)         | Systolix PulseDSP       |

|                          | Triscend A7                    | Tensilica Xtensa        |

| Partial                  |                                | Chameleon RCP           |

|                          | (reconfigurable SoC platforms) | Triscend E5             |

Table 1.1. Taxonomy of eRL-based SoC products.

The group of products designed as complete hardware platforms features the socalled *platform-based FPGAs*, which are offered by FPGA vendors, and *reconfigurable SoC platforms*. In the platform-based FPGAs, a traditional FPGA fabric, consisting of logic blocks and programmable interconnect, plays a central role. Such a fabric is, however, enhanced with large chunks of embedded memories (of the total capacity in the range of Mbits), dedicated functional blocks (such as hard-wired multipliers), programmable input/output blocks supporting different interface standards, peripherals, and a sophisticated clock management circuitry. Last but not least, the newest platform-based FPGAs include also single or multiple embedded CPU cores (e.g. four embedded IBM Power PCs cores in the largest Xilinx Virtex-II Pro device) that complete the whole system. Examples of the platform-based FPGAs are: Xilinx Virtex-II Pro [119], Altera Excalibur [7], and Atmel FPSLIC [9]. While embedded reconfigurable logic comprises a dominant part of the platform-based FPGAs, reconfigurable SoC platforms contain only a small amount of eRL supplementing the rest of the platform resources. Furthermore, in this case eRL is used almost exclusively for the implementation of computations. Unlike the platform-based FPGAs, which rely on the FPGA-specific technology (e.g. an increased number of metal layers, relaxed design rules [124], etc.), reconfigurable SoC platforms are typically realised in a standard CMOS process. An example is Triscend A7 platform [102].

In the group of the platform components, two types of products can be distinguished. The first type concerns cores implemented entirely in reconfigurable logic. Such cores may differ in the granularity, which typically ranges from the bit-level, through the nibble-level<sup>1</sup> to the word-level granularity. The bit-level reconfigurable cores are used for mapping 'glue-logic', control logic and sometimes also arithmetic, whereas the nibble-level and especially word-level reconfigurable cores are used predominantly as hardware accelerators. The cores from this group are offered in different shapes and with different aspect ratios. They are available as hard cores (typically bit-level and nibble-level reconfigurable cores), or soft IP cores (typically word-level reconfigurable cores). Examples are: Actel VariCore [1], Leopard Logic's HyperBlox [67], Elixent's Reconfigurable Array Processor [43], PACT XPP processor [76], and Systolix PulseDSP [98]. The second type of cores in the components of a platform group features programmable cores augmented with reconfigurable logic. In this case, eRL comprises only a part of the complete core and is used mainly for the acceleration purposes. Examples are: Tensilica Xtensa [101], Chameleon Systems' Reconfigurable Communication Processor [25], and Triscend E5 [103].

#### 1.4.4 Key challenges

Embedding reconfigurable logic onto a system-on-a-chip poses various hardwarerelated and software-related challenges. One of the main hardware-related challenges is the *reduction of intrinsic cost* of reconfigurable logic. A reconfigurablelogic-based implementation is costly because the high degree of flexibility it offers is obtained by the introduction of a huge number of configuration switches, multiplexers and large configuration memories. This leads to the one-to-three orders of magnitude cost penalty in area, performance and power compared to an ASIC implementation [37, 124]. The finer the reconfigurability grain, the higher is this cost (compare Figure 1.9).

Due to the high intrinsic cost, and particularly the area overhead, only a limited amount of embedded reconfigurable logic can be integrated on a system-on-achip. The question about the exact amount of reconfigurable logic that should be embedded is a fundamental design issue [124], and has to be resolved before a

<sup>&</sup>lt;sup>1</sup>The term 'nibble' is often used to describe groups of four bits.

system-on-a-chip is fabricated. The challenge lies in finding the *optimal size of an eRL fabric* such that it accounts for the potential (future) growth of the complexity of mapped circuits, and in a correct estimation of the eRL utilisation.

During a physical design process, a SoC designer is also confronted with the eRL challenges. For example, the metal-intensive nature of reconfigurable logic cores requires a careful chip *floorplanning*. During the floorplanning procedure, the locations of consecutive cores have to be found such that global interconnect requirements are met and there is no wiring congestion. Furthermore, proper pin positions for each core that guarantee the required timing have to be found. There is also a *testing* challenge. The specific nature of eRL asks for a robust and complex testing approach that differs from standard testing procedures.

Finally, from the software point of view, *partitioning* and *synthesis* of the application code that take into account the presence of reconfigurable logic in a system is a challenge. Even more so because usually different design flows are used for ASICs, FPGAs and programmable processors.

#### **1.5 Problem statement**

We have shown that the today's chip production depends on economic factors and the market behaviour. As a result, programmable (customisable) products offering a fast time-to-market are a preferable solution. At the same time, however, emerging applications enabled by the progress in IC technology impose higher and higher requirements on the computational efficiency of target designs. Such requirements cannot be met using traditional programmable products (e.g. generalpurpose processors or DSPs).

In such a conflicting environment, there is a clear need for a new implementation paradigm which could help to bridge a cost-efficiency gap induced by traditional implementation approaches, that is, ASICs and programmable processors. The new paradigm should allow a cost-efficient design of embedded systems-on-a-chip for consumer electronics market.

Embedded reconfigurable logic appears as an interesting alternative. Nevertheless, because a low-cost production is critical for competitive consumer electronics market, the high intrinsic cost of embedded reconfigurable logic (compared to the cost of hard-wired implementations) has to be reduced to allow a full acceptance of eRL-based products.

The objective of this work is to investigate possibilities of the reduction of intrinsic cost of embedded reconfigurable logic and to develop a methodology that facilitates the design and implementation of cost-efficient embedded reconfigurable logic cores for consumer electronics applications. The cost-efficiency refers to all design levels, and covers thus architecture, implementation, and technologyrelated aspects.

### 1.6 This thesis

#### **1.6.1** Towards a solution approach

As indicated in Section 1.4.2, in this thesis we are concerned with fine-grain embedded reconfigurable logic architectures, that is, architectures with sub-word reconfigurability. The fine-grain architectures are chosen because of their multipurpose role in a system-on-a-chip that goes beyond the acceleration-related functionality typical for coarse-grain architectures.

In Section 1.4.4, we mentioned that application partitioning and finding the required amount of embedded reconfigurable logic are two of the key challenges of the reconfigurable SoC design. We partially resolve these problems by focusing on some typical ways of deploying embedded reconfigurable logic in the SoC context, for example such as discussed in Section 1.4.2. The consequence thereof is the assumption that only relatively small parts of the application code, and with the (to a certain extent) predictable and manageable growth of their complexity, can be mapped onto reconfigurable logic. This implies that only a relatively small amount of reconfigurable logic is required in a system-on-a-chip. Therfore, the impact the embedded reconfigurable logic has on the total cost of an embedded system can be reduced.

Finally, we propose a further reduction of the intrinsic cost of reconfigurable logic by tuning reconfigurable architectures towards requirements of target application domains. In this way, embedded reconfigurable logic is no longer general-purpose but rather application-domain-specific.

#### **1.6.2** Main contributions

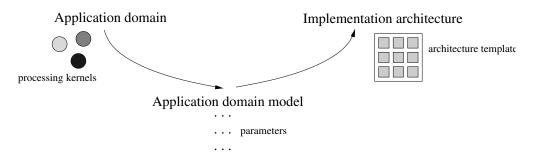

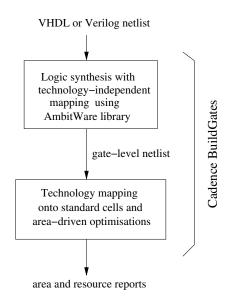

In this thesis, a template-based methodology for the design of embedded reconfigurable logic is proposed. The template describes a generic model of a reconfigurable logic architecture. The template enables a fast architecture exploration, and facilitates the VLSI implementation (netlist and layout generation) and the mapping process (architecture modelling in the CAD tools) of reconfigurable logic.

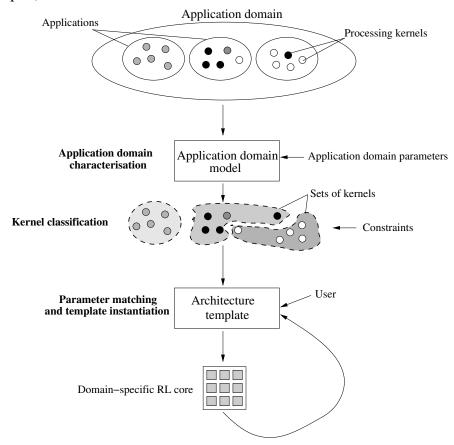

Application-domain specialisation is proposed as a means for the reduction of the intrinsic cost of reconfigurable logic. The method of characterising processing kernels from different application domains and the process of finding a suitable implementation architecture for them based on the application domain characteristics are given.

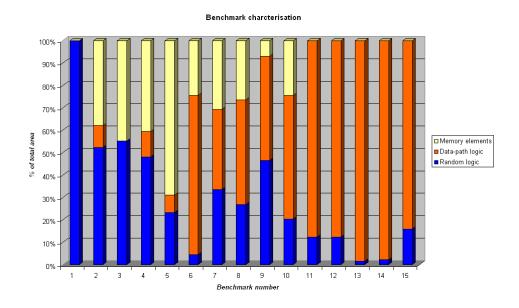

Three basic classes of domain-oriented reconfigurable logic architectures are derived. Each class is illustrated by an example of a reconfigurable logic core, which logic and interconnect architectures are described in detail. Various novel techniques at the architecture level and the application mapping level are introduced to increase cost-efficiency of such cores. Finally, a silicon prototype of one of the cores that has been implemented according to the proposed template concept is presented.

#### **1.6.3** Organisation of the thesis

This thesis is organised as follows. In Chapter 2, we analyse state-of-the-art FP-GAs and identify the reasons for their high intrinsic cost. We also propose the concept of application domain specialisation of reconfigurable logic that aims at the reduction of such cost. The process of the application domain characterisation based on three application parameters, which capture the logic and interconnect requirements, is described. In Chapter 3, generic properties of logic and arithmetic functions are given. Two new properties of binary addition are described that reduce its implementation cost in reconfigurable logic. Cost metrics for the quantification of such cost are also described. Three domain-oriented reconfigurable logic architectures, examples of mapping basic primitives onto such architectures, and the architecture benchmarking are discussed in Chapter 4, Chapter 5 and Chapter 6. In Chapter 7, the template-based methodology that plays a central role in the design process of domain-oriented reconfigurable logic is proposed. The case study, that is the silicon prototype of a reconfigurable logic core is described in Chapter 8. The architecture of the core is based on one of the proposed domain-oriented reconfigurable logic architectures and its implementation is realised according to the template concept. Finally, the main results of the thesis are summarised in Chapter 9.

# **APPLICATION DOMAIN SPECIALISATION**

Although attractive from the design time, manufacturing costs and time-to-market perspective, the inherent flexibility of reconfigurable logic is paid in a considerable cost overhead compared to ASICs. This is the main factor that limits the use of reconfigurable logic in cost-sensitive embedded system-on-a-chip products.

To analyse this cost, a good understanding of modern reconfigurable logic devices, such as FPGAs, and their applications is needed. In this chapter, we describe successive generations of FPGA devices and discuss architectural trade-offs they exploit. We also compare the intrinsic cost of the FPGA and ASIC technologies. Finally, we propose a method for the reduction of the intrinsic cost of reconfigurable logic through application domain specialisation. To illustrate this concept, we analyse a set of kernels from different application domains and we characterise and classify them using the selected criteria. We also present architectural implications of such a classification.

# 2.1 Field Programmable Gate Arrays

# 2.1.1 An evolving FPGA

The primary applications of the first FPGAs were hardware prototyping, lowvolume production series, a 'glue-logic' type of functionality (e.g. interfaces), and somewhat later networking. In all cases, FPGAs were used as system components integrated on a printed circuit board. However, the continuing technology scaling has made FPGA devices attractive for a much broader range of tasks than they were originally meant for. This has resulted in the expansion of the FPGA application area from the 'glue-logic' niche, through hardware acceleration in general-purpose and DSP computing [82, 50, 53], to the system-central position today [89, 100]. Recently, next to traditional stand-alone devices, an alternative way of using FPGAs, that is as embedded intellectual property (IP) cores, has been proposed [1, 68].

One of the consequences of such a shift was a graduate change of FPGA architectures. This can be observed following the evolution of any commercial FPGA. For our analysis we chose the family of Xilinx FPGA devices.

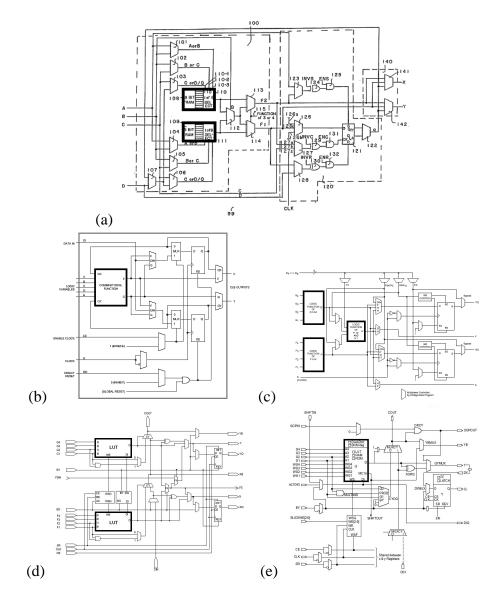

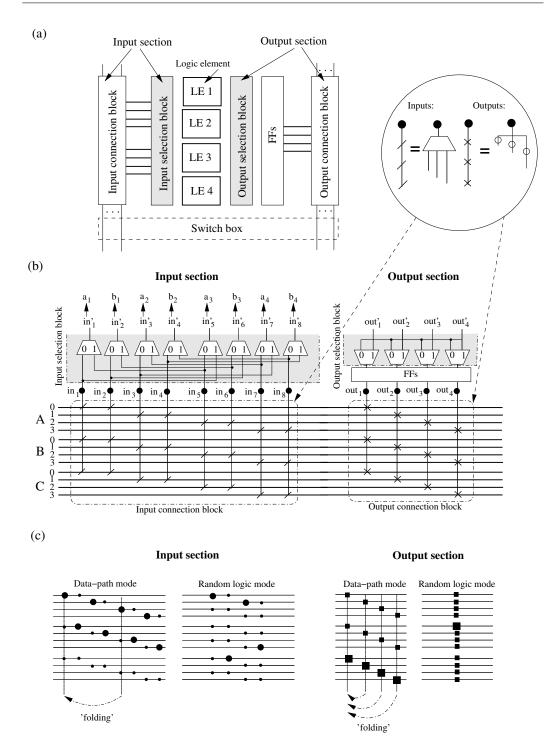

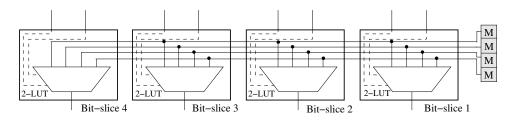

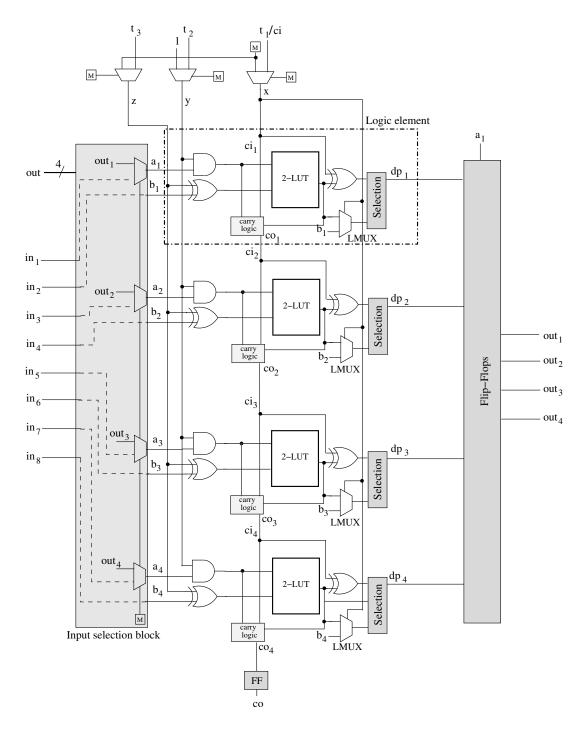

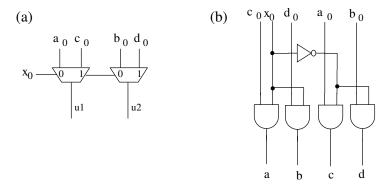

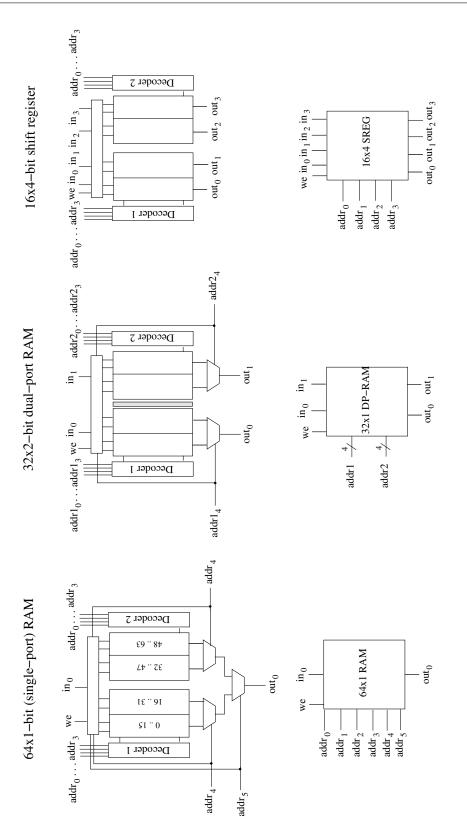

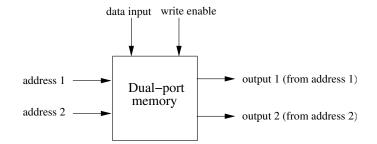

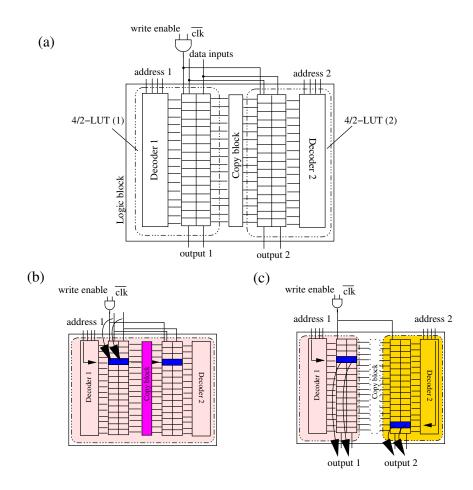

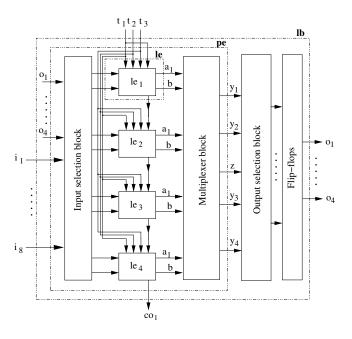

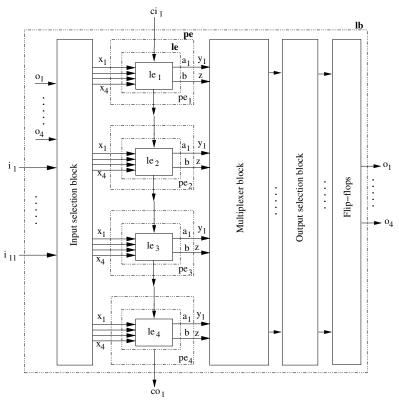

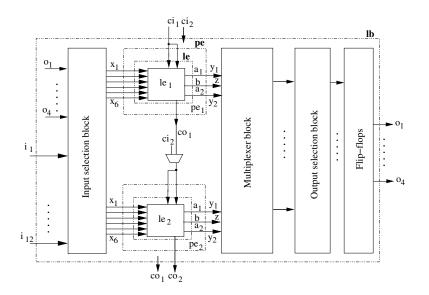

Figure 2.1 shows the logic block structures of five subsequent generations of Xilinx high-end FPGA devices. Despite many similarities (e.g. the use of a look-up table as a basic logic element and the presence of a flip-flop at each logic output), the presented structures also differ. The differences reflect various architectural modifications that FPGAs have gone through. Considering both the logic and interconnect parts of an FPGA architecture, such modifications include:

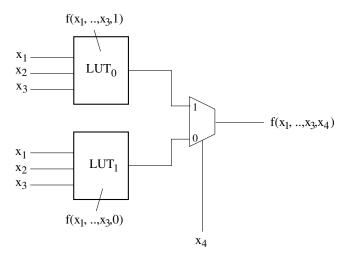

- *Increase in granularity*: the logic blocks of successive generations of FPGAs are made coarser and coarser (e.g. the change from a single 4-LUT in the first generation to eight 4-LUTs in the fifth generation); coarse logic blocks facilitate an implementation of large logic functions (more efficient mapping of combinational logic) and data-paths (support for multi-bit processing).

- *Improvement of the arithmetic mapping capabilities:* from the second generation onwards, FPGAs include dedicated arithmetic resources such as carry logic, carry chains and specialised arithmetic modules (e.g. hard-wired multipliers in Virtex devices). This type of modifications considerably improve the efficiency of mapping arithmetic (i.e. the number of logic blocks required per a given function) and are driven by the increasing importance of signal processing applications.

- *Introduction of the memory mapping capabilities:* embedding large memory blocks into the traditional FPGA fabric is a consequence of the increasing role of signal and image processing applications and the increasing size of FPGAs themselves. Because of the latter, larger designs can be mapped onto FPGAs. Consequently, large off-chip memories that are required for the data storage are replaced with on-chip (embedded) FPGA memories.

- *Introduction of other architectural enhancements:* further mapping efficiency improvement is achieved by providing shift-register mapping capabilities (the third generation) and a means for implementing large sum-of-product structures (the fifth generation). Also, multi-clock domains and programmable high-speed interface logic are introduced to FPGA devices.

- *Embedding of CPU cores:* FPGAs take a full advantage of technology scaling by the on-chip integration of CPU cores (the fifth generation). In this way, FPGAs are becoming independent implementation platforms that enable a realisation of complete systems.

- *Enhancement of interconnect:* the changes in the FPGA logic are accompanied by the changes in the interconnect structure. The reasons are: the performance improvement, dealing with deep-submicron effects and enabling the mapping of larger complex designs. Consequently, carry chains and direct connections, segmented and hierarchical interconnect, and active interconnect technology (fully-buffered interconnect) are introduced.

Figure 2.1. The logic blocks of five successive generations of Xilinx FPGA devices: (a) first generation XC2000, (b) second generation XC3000, (c) third generation XC4000, (d) fourth generation Virtex (the Virtex logic block includes two logic slices; the structure of a single logic slice is shown), (e) fifth generation Virtex-II (the Virtex-II logic block includes four logic slices; only a half of the logic slice is shown). The LUTs in each logic block are marked with bold rectangles.

Essential characteristics of five successive generations of Xilinx FPGAs are summarised in Table 2.1.

The above-described evolution indicates that FPGA architectures evolved from homogeneous 'sea-of-programmable-gates' structures almost two decades ago to *general-purpose* heterogeneous structures today. Though such an evolution has been driven by FPGAs 'riding the wave of Moore's law' [17], it has a strictly

Table 2.1. Characterisation of successive generations of high-end Xilinx FPGA devices.

# Application domain specialisation

26

economical justification. Firstly, a high degree of flexibility of FPGAs allows an implementation of potentially any type of application (as long as it fits the FPGA size, and other parametric requirements, such as performance and power dissipation, are satisfied). This makes modern FPGAs competitive to traditional ASICs, especially if the production volume is low. Secondly, making FPGAs general-purpose is beneficial from the FPGA vendors' perspective. It limits namely their efforts to the support and maintenance of only a few crucial device families.

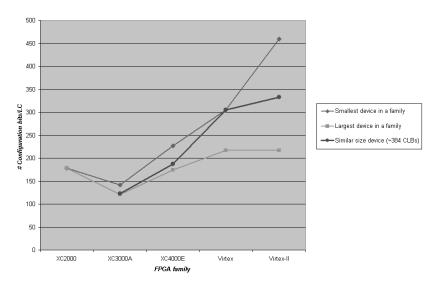

Figure 2.2. The gradual increase in the intrinsic cost of successive generations of Xilinx FPGA devices: XC2000 [24, 11], XC3000 [116], XC4000 [117], Virtex [118], Virtex-II [119]. The cost metric is the number of configuration bits per a logic cell (LC). The cost figures are calculated for the smallest and largest devices in a given family, and assuming a device of the similar capacity (i.e. ~384 CLBs).

The clear drawback of the continuous process of augmenting flexibility of FPGA devices is the increasing cost overhead. Figure 2.2 shows the number of configuration bits per logic cell calculated for five subsequent generations of Xilinx FPGAs. We chose the number of configuration bits as the primary cost metric since it is easily available from the FPGA data sheets. We normalised this cost per logic cell. The 'logic cell' (LC) expresses a fixed amount of functionality that is equivalent to the functionality of a 4-LUT with a flip-flop<sup>1</sup>. The following factors (in the LC equivalents) are used to characterise configurable logic block (CLB) capacities of five generations of Xilinx FPGAs: XC2000 - 1, XC3000A - 1.625, XC4000X - 2.375, Virtex-E - 4.5, and Virtex-II - 9 [115]. (Embedded memories that are present in some of the analysed devices are excluded.)

It is clear from the figure that the cost of the similar amount of functionality in each new generation of FPGA devices is gradually increasing.

<sup>&</sup>lt;sup>1</sup>The LC metric has been proposed by Xilinx to allow the comparison of different FPGAs [115].

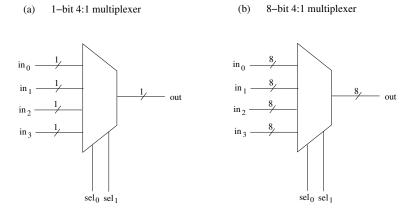

#### 2.1.2 Architectural trade-offs in FPGAs

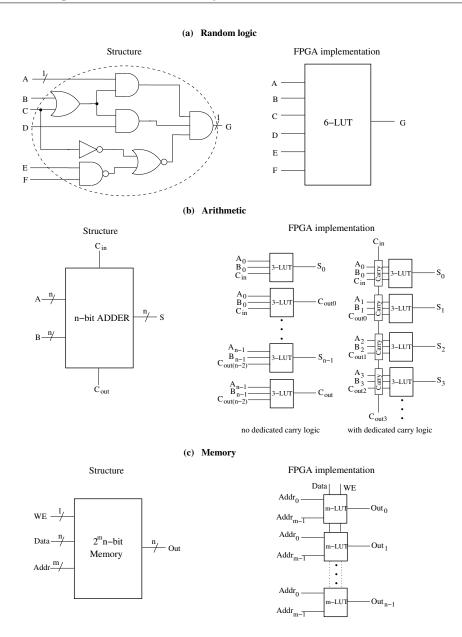

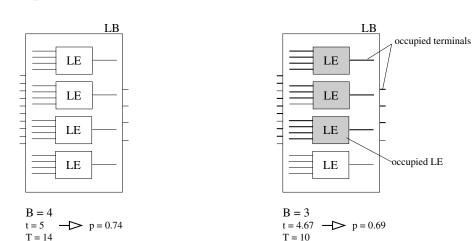

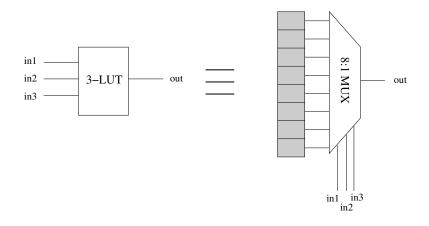

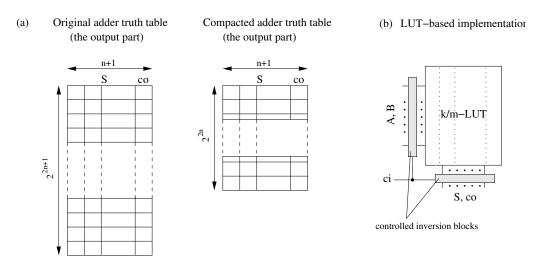

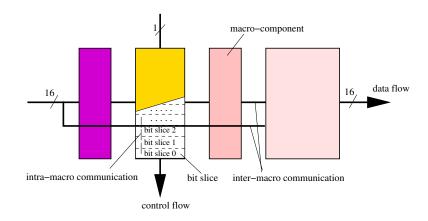

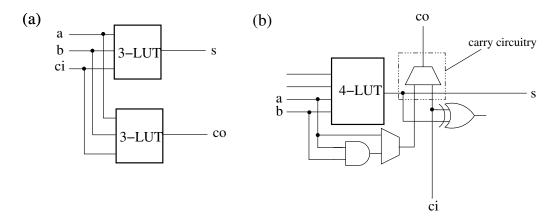

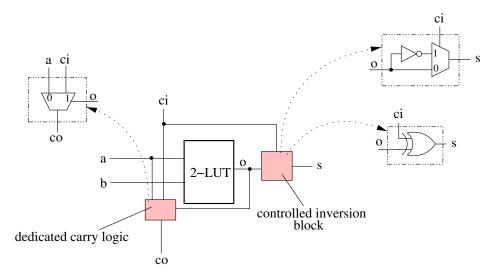

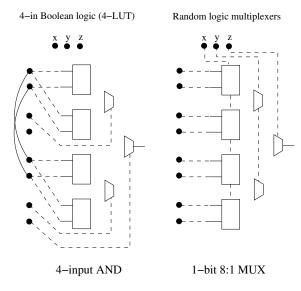

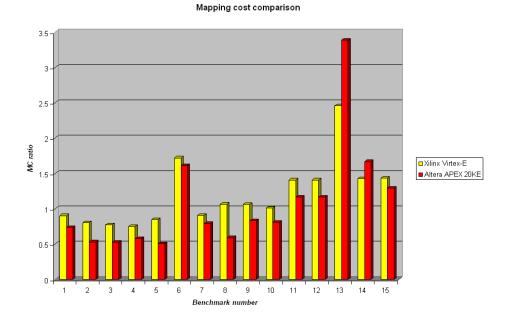

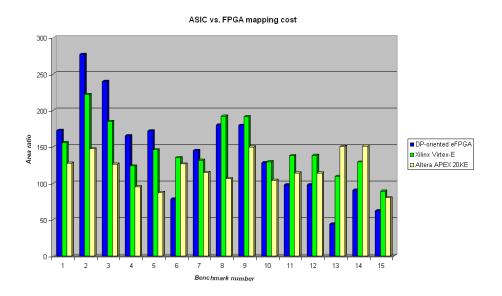

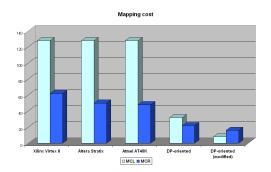

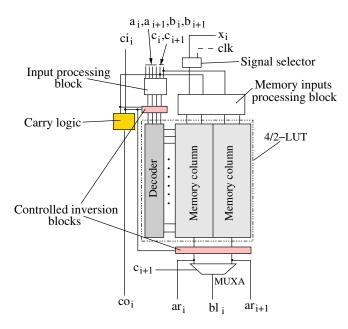

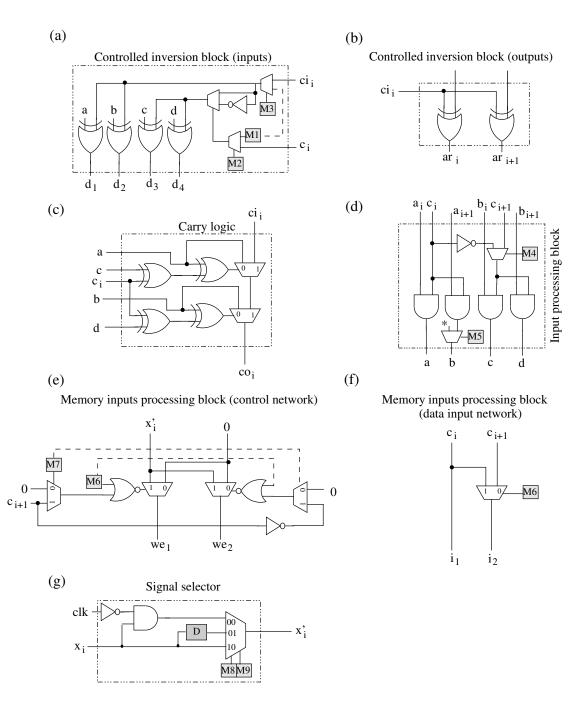

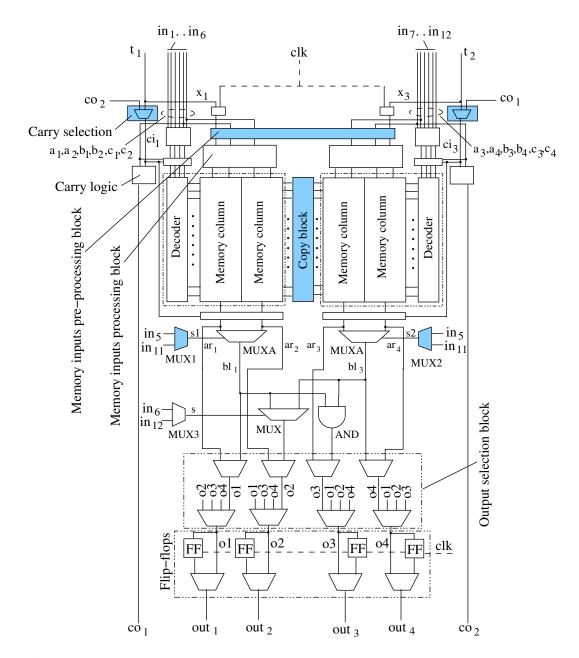

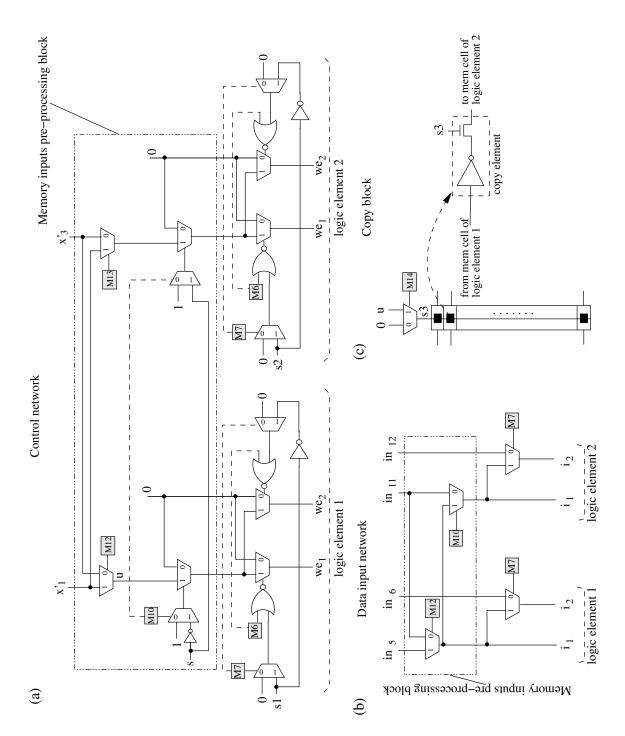

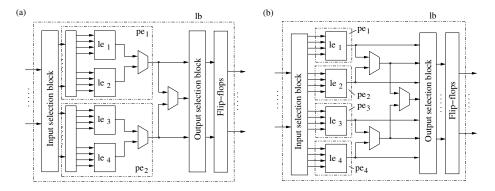

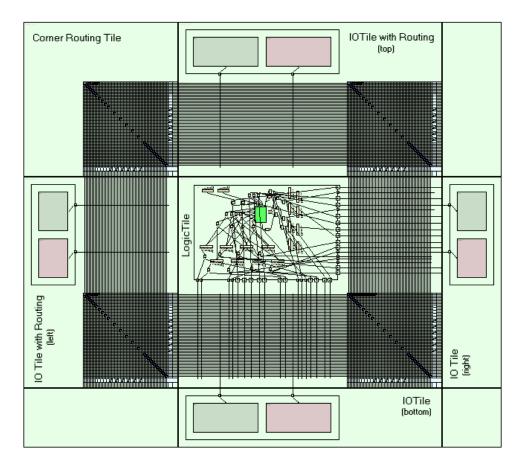

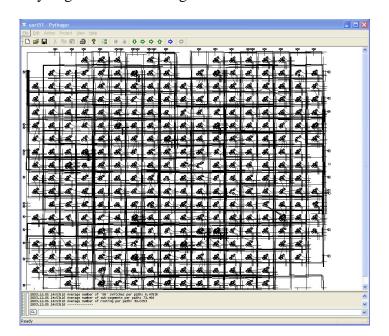

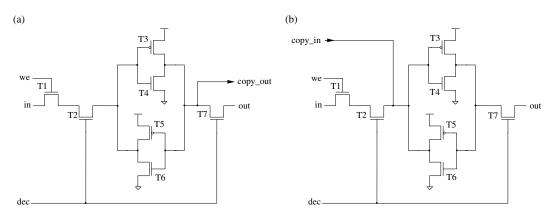

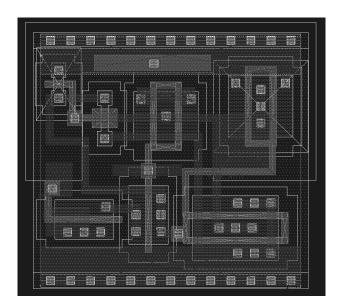

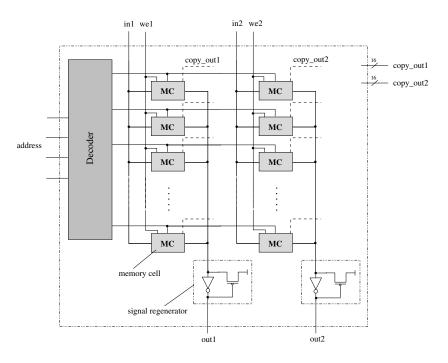

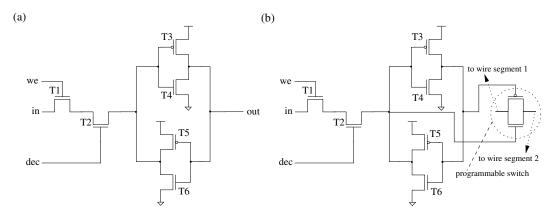

In its broadest sense, the general-purpose nature means the ability of implementing random logic, data-path and memory functions in a single device. The costefficient realisation of such functionality in a homogeneous (i.e. with an unified type of resources) LUT-based FPGA device is fundamentally difficult. This is due to different, often conflicting, requirements that are imposed by logic, arithmetic and memory functions. For example, random logic functions, though being collections of fine-grain elements (logic gates), usually benefit from the mapping onto coarse look-up tables (see Figure 2.3(a)). The coarse look-up tables allow a substantial reduction of the logic depth, and thus reduce delays. Because there is a direct correlation between the granularity of a logic block, a logic delay and the complexity of the FPGA routing resources [87], there is an upper limit on the size of a look-up table<sup>2</sup> that should be used in practice. Based on the study described in [87], 3-input and 4-input look-up tables (3-LUTs and 4-LUTs) have been found to be the best in terms of area. The results of the complementary study published in [94] have shown that 5-input and 6-input look-up tables (5-LUTs and 6-LUTs) are the best in terms of delay. Finally, a similar analysis presented in [3], in which much more accurate area and delay models have been applied and the clustered type of a logic block has been considered, has shown that look-up tables with four to six inputs (4-LUTs to 6-LUTs) and logic block clusters consisting of four to ten look-up tables guarantee the best area-delay product.