### Yield modeling for deep sub-micron IC design

Citation for published version (APA): Simon, P. (2001). Yield modeling for deep sub-micron IC design. [Phd Thesis 2 (Research NOT TU/e / Graduation TU/e), Electrical Engineering. Arts & Boeve Publishers. https://doi.org/10.6100/IR556679

DOI:

10.6100/IR556679

Document status and date:

Published: 01/01/2001

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 16. Nov. 2023

Yield Modeling for Deep Sub-Micron IC Design

Paul Simon

### Yield Modeling for Deep Sub-Micron IC Design

## Yield Modeling for Deep Sub-Micron IC Design

### Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr. R.A. van Santen, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op donderdag 20 december 2001 om 16.00 uur

door

### **Paul Simon**

geboren te Voorschoten

Dit proefschrift is goedgekeurd door de promotoren:

prof.ir. M.T.M. Segers

en

prof. W. Maly

Cover design: Elly van Domburg, Van Domburg Ontwerp, Nijmegen

Cover photos: Physical Characterization Group, Crolles and FA group MOS4YOU

The work described in this dissertation was carried out at MOS4YOU waferfab, Philips Semiconductors, Nijmegen, The Netherlands, as part of a joint research program with Carnegie Mellon University Pittsburgh and Technical University Eindhoven

© Copyright 2001 P.L.C. Simon

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior written permission from the copyright owner.

Published by Arts & Boeve Publishers P.O. Box 31187 6503 CD Nijmegen The Netherlands

#### CIP-DATA LIBRARY TECHNISCHE UNIVERSITEIT EINDHOVEN

Simon, Paul Yield modeling for deep sub-micron IC design / by Paul Simon. Eindhoven: Technische Universiteit Eindhoven, 2001. Proefschrift.

Headings: VLSI, semiconductor manufacturing, VLSI design, yield modeling, DfM

ISBN 90-75341-28-8 NUGI 832

Voor Loes, Daniel, Nina Jules en Tineke

### **Preface**

This thesis is the result of almost five years of work done in the area of DfM and yield engineering at the MOS4YOU wafer fab of Philips Semiconductors in Nijmegen, The Netherlands. Next to being a very stimulating environment to work and learn in, MOS4YOU and its people have given me a fantastic time. Although my name appears on the cover of this dissertation, without the help and support of many people, both technical and moral, the book would not have seen daylight. Here I would like to take the opportunity to express to them my deepest appreciation and thanks.

In particular, I would like to thank:

Professor Wojciech Maly, my thesis supervisor and teacher, for his warmth and understanding throughout these years. During his many tiring visits to Nijmegen I was able to dig in the mine of his great experience and, finally, understood the main issues of DfM. His guidance was a great source of inspiration. The time we worked together was a great pleasure and has a lasting value for me.

Dr. Paul van Wijnen, for his companionship, enthusiasm, and for giving me the opportunity to combine the work at MOS4YOU with the preparation of a Ph.D. thesis.

Professor Rene Segers and Professor Jochen Jess of the Technical University of Eindhoven, to whom I am indebted for reading and correcting the manuscript and giving me the opportunity to carry out the project in cooperation with the university.

Dr. Dirk de Vries, and Dr. Jan-Marc Luchies, my 'paranymphs', for their company, moral support and many invaluable discussions on yield modeling, plasma damage, and gastronomy. From both I learned a lot.

Ir. Kees Veelenturf, my manager during most of the time I spent at MOS4YOU, for always supporting me in my work, and for defending an academic approach in the sometimes 'fire fighting' oriented fab organization.

Drs. ir. Clemens van den Berghe, for his everlasting positivism, encouragement, support and relaxing company during many coffee breaks.

vii

ir. Stanley Sprij and ir. Marc van de Pol former roommates, for their pleasant company and jokes.

Klaas Arts for his advice on the layout of this thesis and the help with printing and publishing.

Dr. Diederik fokkema, ir. Paul Volf, ir. Arjan Mels, and ing. Tony Jurg of the DfM group in MOS4YOU for their company, support in development of tools, and preaching the DfM word.

All my co-workers in MOS4YOU and LTG, they made my stay in Nijmegen a very pleasant one.

Ing. Ronald de Bruijn and ing. Roland Antheunis who were of great importance for helping to develop the layout extraction tools and designing test structures respectively.

My wife, Loes for her moral support and understanding during these difficult years and my children Daniel and Nina. To them and to my parents I dedicate this thesis.

Paul Simon La Terrasse, September 2001

## **Contents**

| Pre | face                                                                                                                                                                                                                                                            | vii                  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1.  | Introduction                                                                                                                                                                                                                                                    | 1                    |

|     | 1.1. Introduction                                                                                                                                                                                                                                               |                      |

| 2.  | Yield Modeling Principles                                                                                                                                                                                                                                       | 7                    |

|     | 2.1. Introduction                                                                                                                                                                                                                                               | 9                    |

|     | 2.2. Yield loss: causes, classification and characteristics                                                                                                                                                                                                     | 11                   |

|     | 2.3. Yield model overview  2.3.1. Basic yield models  2.3.2. Yield models based on design attributes other than area  2.3.3. Critical area yield model derivatives  2.3.4. Yield model for any design attribute  2.3.5. Experimental comparison of yield models | 18<br>21<br>25<br>27 |

|     | 2.4. Conclusions                                                                                                                                                                                                                                                | 33                   |

| 3.  | Yield Prediction Methodology and Model Parameters                                                                                                                                                                                                               |                      |

|     | 3.1. Introduction                                                                                                                                                                                                                                               |                      |

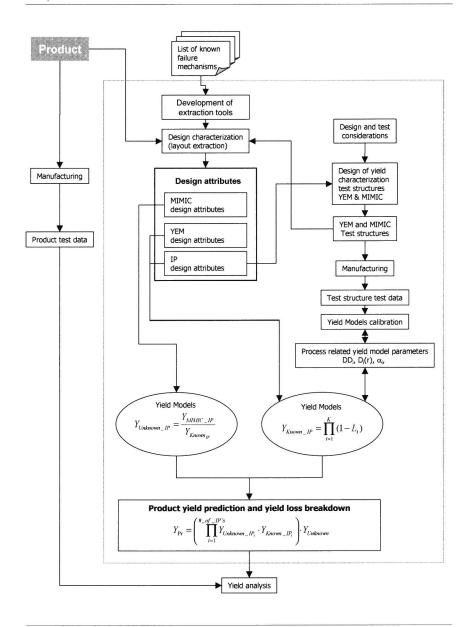

|     | 3.2. Yield prediction methodology                                                                                                                                                                                                                               |                      |

|     | 3.3. Process parameter extraction                                                                                                                                                                                                                               | 42                   |

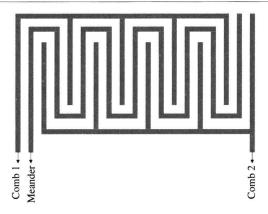

|    | 3.3.3. Examples of test structures for parameter extraction51                                                                                                                   |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 3.4. Design parameter extraction: structural layout characterization                                                                                                            |

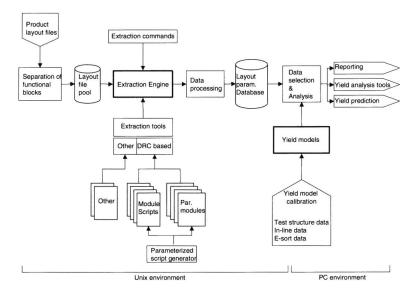

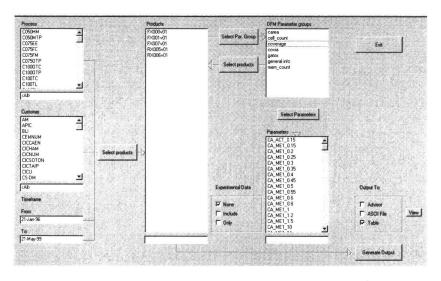

|    | 3.5. Development of a manufacturability assessment environment (MAE) 69                                                                                                         |

|    | 3.5.1. Motivation for the development of an MAE                                                                                                                                 |

|    | 3.6. Conclusions                                                                                                                                                                |

|    | 3.7. References80                                                                                                                                                               |

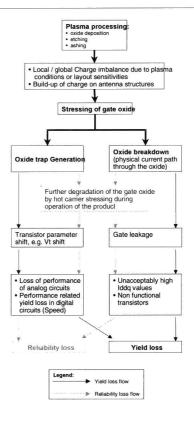

| 4. | Plasma Process Induced Damage: Physics and Modeling                                                                                                                             |

|    | 4.1. Introduction                                                                                                                                                               |

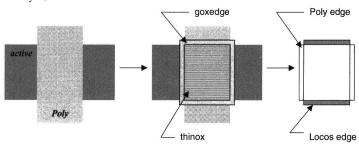

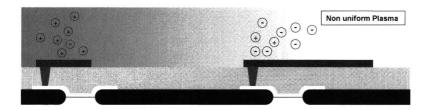

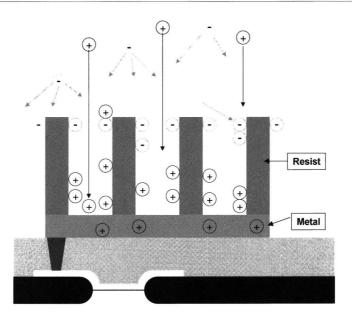

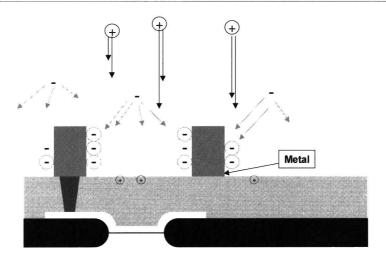

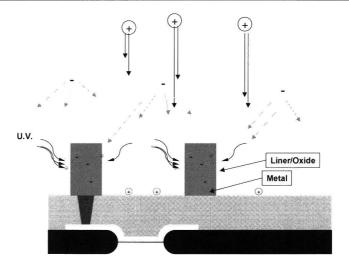

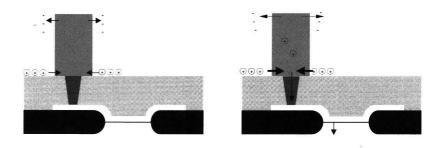

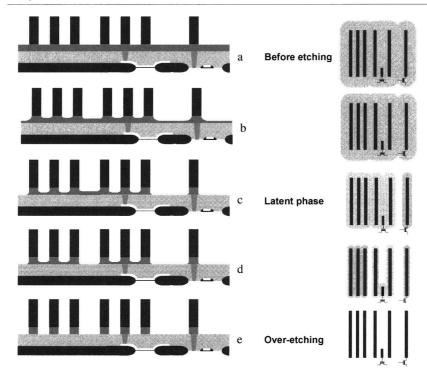

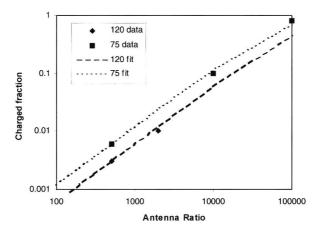

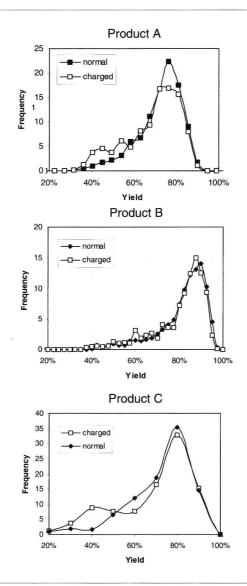

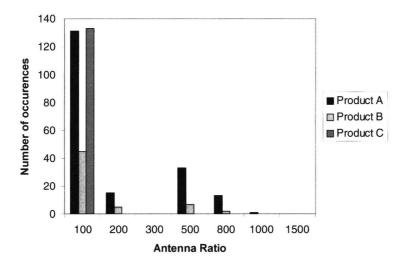

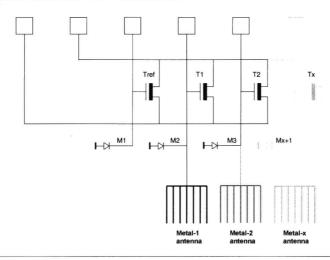

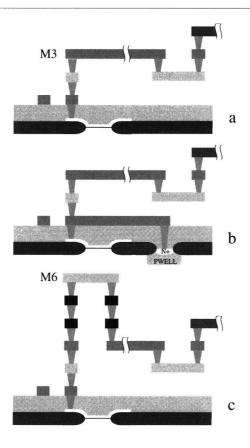

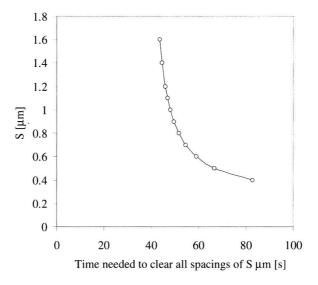

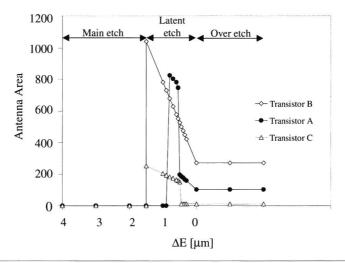

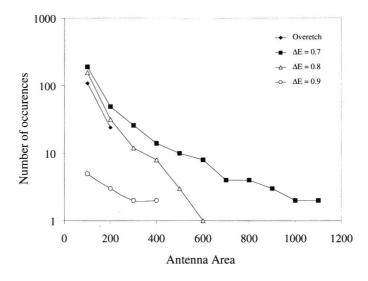

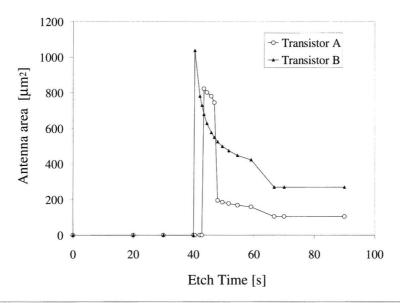

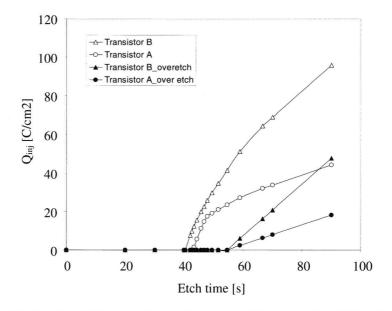

|    | 4.2. Charging failure mechanism864.2.1. Charge imbalance mechanisms884.2.2. Layout dependency of charging93                                                                     |

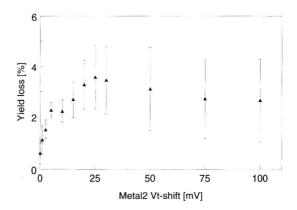

|    | 4.3. Modeling charging induced yield loss.954.3.1. Charging induced yield loss experiment.964.3.2. Modeling charging related yield loss.994.3.3. Conclusions and discussion.100 |

|    | <ul> <li>4.4. Plasma process induced damage characterization</li></ul>                                                                                                          |

|    | 4.5. Robust IC design for charging                                                                                                                                              |

|    | 4.6. Conclusions                                                                                                                                                                |

|    | 4.7. References                                                                                                                                                                 |

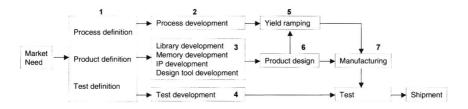

| 5. | Design for Manufacturability in VLSI                                                                                                                   | 131 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | 5.1. Introduction                                                                                                                                      | 133 |

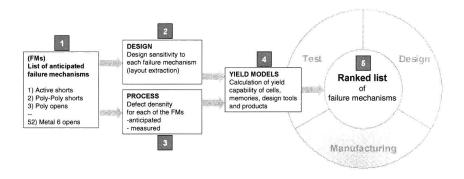

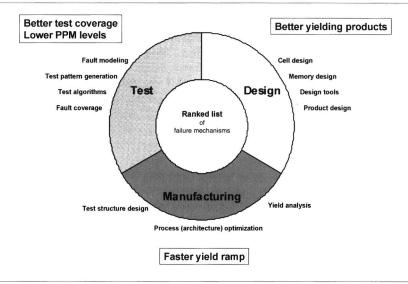

|    | 5.2. A common language between design, manufacturing and test                                                                                          | 134 |

|    | 5.3. DfM methodology                                                                                                                                   | 137 |

|    | 5.4. DfM in IP design                                                                                                                                  | 139 |

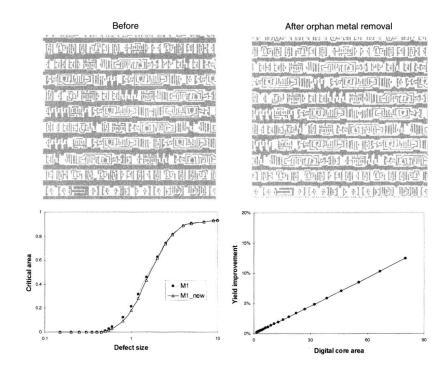

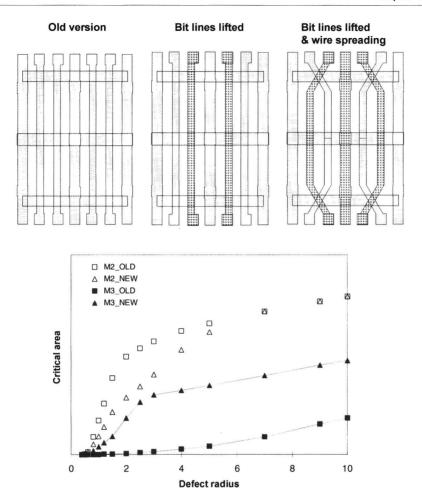

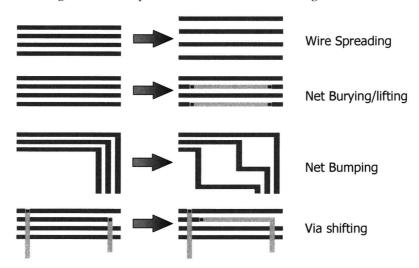

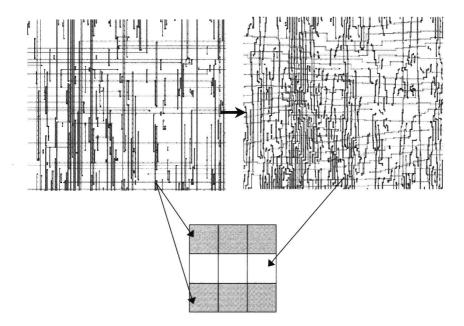

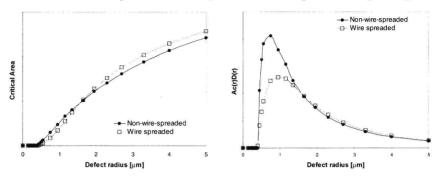

|    | 5.4.1. Standard cells and memories 5.4.2. Synthesis for high yield 5.4.3. Routing                                                                      | 145 |

|    | 5.5. DfM in the manufacturing environment                                                                                                              | 153 |

|    | <ul><li>5.5.1. Process development</li><li>5.5.2. Understanding product variability</li><li>5.5.3. Yield prediction and sensitivity analysis</li></ul> | 156 |

|    | 5.6. DfM in test development                                                                                                                           | 173 |

|    | 5.7. Current R&D needs for DfM implementation                                                                                                          | 173 |

|    | 5.8. Conclusions                                                                                                                                       | 175 |

|    | 5.9. References                                                                                                                                        | 176 |

|    | Summary                                                                                                                                                |     |

| 7. | Samenvatting                                                                                                                                           | 183 |

|    | List of abbreviations                                                                                                                                  | 189 |

|    | List of publications                                                                                                                                   | 191 |

|    | About the author                                                                                                                                       | 193 |

# **Chapter 1**

## Introduction

1

#### 1.1 Introduction

Manufacturing yield has always been an important parameter determining the economic viability of any semiconductor company. Due to the present directions the semiconductor market is moving in, this has become even more so [1]. In order to be able to follow Moore's law over the past few decades, the costs associated with developing and manufacturing VLSI products have grown tremendously. Nowadays, modern manufacturing sites are built at very high costs (2-3B\$) and rapid return on investment is essential for the economic viability of the business. The ability to achieve high yield at an extremely fast rate has consequently become a crucial factor that decides whether a company is successful, or risks to go out of business. It can be easily calculated that a small amount of unnecessary yield loss for a modern semiconductor fab easily translates to the loss of hundreds of millions of dollars per year in terms of revenues from manufactured products and lost manufacturing volume.

Another reason for the increasing significance of a fast yield ramp is the change with respect to the need for ever-faster product introductions and shorter product lifetimes. Driven by market needs, more products are developed that tend to have shorter lifetimes resulting in narrow windows of opportunity. Therefore immediate high yield is vital for products that are introduced into a fab. There is no time for costly re-engineering of the design or process. Sometimes even the first lot of a product is not out of the line when the last lot is put in. It is obvious that in such a case smooth product introduction and high, and even more important, predictable yield, are crucial.

Product yield is not only a function of quality of a manufacturing process, but also of the sensitivity of the design to the failure mechanisms that are present at the time the product is going through the manufacturing steps. Along these lines process development engineers tend to argue: "the yield of a product is determined by how well the design fits the manufacturing process". This is of course true. However, a designer's usual reply is: "as long as the product is

designed according to design rules, the yield is determined by how well the process is capable of accommodating all design attributes".

This example shows well how far design and manufacturing have been drifting apart. Over the past few years both disciplines have increased dramatically in complexity. For both lines of work very differently skilled engineers are needed, and, in addition, activities often take place in different organizations, often situated at distant locations. Therefore communication is very much formalized and, in some cases, over-simplified. As a result, the responsibility for product yield is not shared, nor is the information that is necessary to generate robust designs. Often a simple design manual is the only source of manufacturing information that is used to design a product. This separation of product design and the process development has caused an increased probability that designs do not optimally fit the manufacturing processes.

From the above arguments one can derive the following list of fundamental needs which today's and future IC design and manufacturing technologies should address:

- As feature size will decrease rapidly and more complex processes are being used, not only more failure mechanisms, but also more complex ones will play an increasingly important role. However, conventional test structures and in-line monitoring techniques are no longer adequate tools to characterize all possible failure mechanisms in a process. For both rapid yield learning and robust IC design a methodology is needed that enables the characterization of the manufacturing process with respect to all possible defects.

- For each of the identified defect types, it is then necessary to quantify the yield impact on product level so that its importance can be evaluated. Therefore yield models are needed that take into account both the design sensitivity and defect characteristics of the process. Without such models it is difficult to quantify the yield impact on product level and consequently to set priorities in yield improvement efforts. Yield models that describe layout sensitivities are also needed in order to design products that are as insensitive as possible to the identified failure mechanism.

- In order to be able to apply yield models to IP design (standard cell, memory, IP blocks or products) and to predict their yield capability, a methodology for extensive design characterization is needed.

- The detachment of the design and manufacturing communities over the past few years has led to a communication structure that is inadequate to address the yield problems that are present in modern VLSI technologies. Therefore a reintegration platform for design and manufacturing activities is necessary.

For robust IC design, methodologies, models, tools, and data are needed in order to be able to assess or influence the yielding capability of a product on all levels of design abstraction.

The above needs were also recognized at MOS4YOU, CMOS waferfab of Philips Semiconductors in Nijmegen, Carnegie Mellon University, Pittsburgh and the Technical University of Eindhoven. Consequently a joint research project was started to address the above needs. This document reports the results that were collected during a period of almost five years. The accomplishments reported here are the result of the cooperation in many teams that brought together engineers from many different disciplines of the above organizations.

#### 1.2 Thesis outline

This thesis is structured as follows:

In *Chapter two* an overview and classification of yield loss causes in IC manufacturing is given. Existing yield models are reviewed and the benefits and limitations are described. New yield models are proposed and verified using extensive manufacturing data.

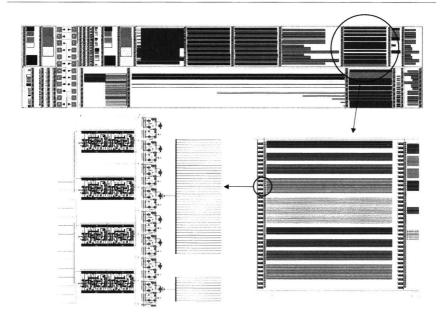

Chapter three presents methodologies for yield model parameter extraction. Both process parameter extraction and design characterization methods are discussed. A rapid yield learning and yield prediction methodology are described and the associated costs of yield model calibration are discussed. The development of an industrial product characterization platform is described.

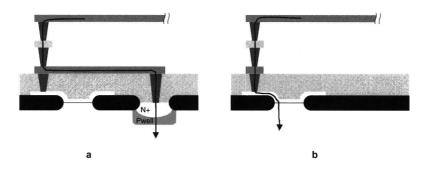

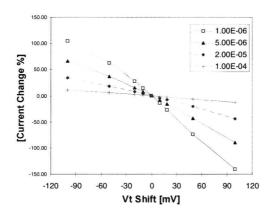

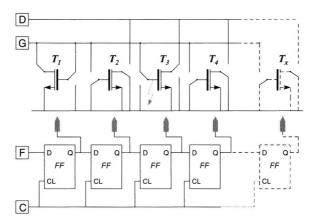

In Chapter four the plasma induced damage mechanism and its layout dependence are studied. Plasma damage is used as a case study to show an implementation of the methodologies developed in chapter 3. Special new test structures are developed and their results are presented. A clear relationship between plasma damage and yield is found and subsequently a yield model is derived and verified with experimental data. Also a new method to quantify product charging sensitivity is proposed in order to achieve a methodology for charging robust design.

Chapter five shows that for better manufacturability it is necessary and possible to better integrate design, process development, and test. A "common language" between these disciplines is proposed that enables faster yield ramp and robust design. Several examples in both the design and manufacturing environment show the effectiveness of the methodology. Recommendations for further research in this field are given.

Finally Chapter six summarizes the research conducted.

#### Reference

[1] W.Maly, "High levels of IC Manufacturability: One of the Necessary Prerequisites of the 1997 SIA Roadmap Vision". IEDM 1998

# **Chapter 2**

# **Yield Modeling Principles**

2

#### 2.1 Introduction

Although the total cost of a VLSI product is only partly determined by the silicon manufacturing costs, the level of its profitability is largely determined by the yield that is achieved during the manufacturing process. Increased yield loss results in fewer functional devices at the same manufacturing costs. Sometimes inefficient wafer usage, wafer damage or miss-processing may be important contributors to the yield loss. But, in general the most important contributors to yield loss are failures caused by local unintended product-process interactions. This chapter focuses on product yield, which can be defined by the ratio of the number of working devices and the total number of devices that are tested.

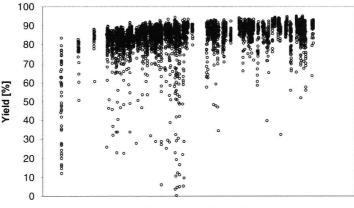

Figure 2.1 shows a characteristic wafer yield trend of a particular product that was produced in a time period of approximately one year. It is clear from this figure that the yield level and its variance change over time. Every wafer is subject to hundreds of different processing steps on many different machines.

Time period: 14 months

Figure 2.1 Product wafer level yield trend over a period of 14 months

In each IC layer a large number of failure phenomena with different probabilities of occurrence and different levels of "killing potential" may take place. Hence, it is obvious that in today's complex process technologies it is naïve to assume that yield loss is caused by only one failure mechanism. Therefore the identification of the major failure mechanisms in a manufacturing process is often a complicated task that requires dedication and detailed knowledge on both the process imperfections and the associated product sensitivities. Throughout the period of yield ramping much effort is put into the continuous debugging of the manufacturing process in order to increase the yield and tighten its distribution. It has been well understood that models that describe failure mechanisms and their relevance for product yield are essential to effectively manage continuous yield improvement activities, and the setting of priorities therein [1, 2-4].

Many types of yield models have been derived over the years and have proven to be useful for many purposes such as:

#### Inside manufacturing environment

- Yield ramping and setting priorities for corrective actions

- Understanding the impact of different types of failure mechanisms on product yield

- Understanding yield differences between products

- Assessing and predicting the yield impact of process changes or options

#### Outside manufacturing environment

- Reporting of process yield capability parameters such as average defect density. D<sub>0</sub>.

- Planning of manufacturing volume

- Assessing the yield impact of decisions that are taken during the design phase of a product

Depending on the application, existing yield models use different (sets of) parameters. However, all yield models contain parameters that characterize both the manufacturing process and the design. Design related parameters may describe, for example, device area, critical area, number of transistors, number of nets, total length of conductors etc. Process parameters may describe defect density, defect size distribution, defect density distribution, defect clustering, line width distribution or layer thickness. In most attempts at yield modeling so far, the focus has been on the yield models themselves and not on the calibration or extraction of the yield model parameters. But, a user of any yield model must always realize that the data that is used to acquire yield model parameters is as important as the accuracy of the model itself. When it is not clear how to obtain the necessary parameters, questions can be raised on the accuracy, reproducibility, and applicability of these models. This is the reason why many yield models are viewed with suspicion and skepticism, even though they may be derived based on sound statistical principles.

This chapter describes the benefits and limitations of existing yield models. In section 2.2 examples of yield loss causes and a yield loss classification is described. In section 2.3 an overview of the most common yield models is given. Yield

models based on device area and other design attributes are discussed. The accuracy of existing and new yield models is compared using extensive amounts of manufacturing data. In section 2.4 conclusions are drawn.

# 2.2 Yield Loss Causes, Classification and Characteristics

Wafer productivity loss can have many causes, some of which are obvious and others are more difficult to trace. To begin with, silicon is lost because of *inefficient wafer usage*. Often at the edge of the wafer, parameters such as layer thickness or defectivity are not within process specifications. Also some equipment may use the edge of the wafer for mechanical positioning, damaging certain layers. In addition wafers contain scribe line test structures, alignment markers or structures for in-line monitoring. Such structures require silicon real estate and therefore reduce the wafer productivity.

Secondly, wafers may be damaged during manufacturing due to wafer handling by humans or machines. Often this kind of yield loss is labeled as *line yield loss*. A third category of yield loss occurs when at the end of the manufacturing line the scribeline test structure results indicate that device parameters are outside manufacturing specifications. In that case product testing costs are reduced by scrapping the entire wafers and the yield loss can be categorized as *PCM* (process control module) yield loss.

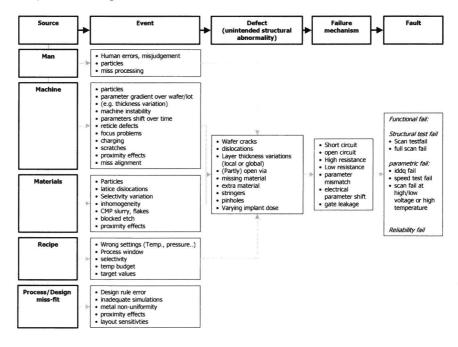

Yield loss due to the above reasons is usually much smaller than the *die yield loss* which is the ratio of the number of failing dies and the number of tested dies. Die yield loss is caused by manufacturing imperfections that occur on each wafer. This chapter focuses only on die yield which will simply be referred to as *yield*. In this context it is useful to distinguish between sources of yield loss, events that cause them, defects, failure mechanisms and faults. Figure 2.2 shows the relationships between those terms and shows some typical examples.

#### Reasons for yield loss

Figure 2.2 shows one of many possible classifications of the relationship between yield loss causes and resulting symptoms. In complex manufacturing processes many sources of yield loss exist. For instance, human errors can never be excluded and will remain an uncontrolled source of yield loss. Yield loss can also be caused by equipment settings that are wrong or drifted because of instabilities. Another important source of yield loss are materials such as the wafers themselves, but also deposited materials such as aluminum or resist may contain particles that cause defects.

Furthermore, the robustness of the process influences the susceptibility to yield loss. Complex interactions between different processing steps and materials sometimes cause a tight "processing window". In such cases only a minor deviation in any of the relevant parameters or chemical properties (such as selectivity of an etching substance) may cause yield loss.

Due to the increasingly complex manufacturing processes and product designs, subtle product-process interactions are becoming an increasingly important source

of yield loss. Design rule checking no longer guarantees an optimal design-process fit and problems such as cross talk, delay faults and device matching are affecting the yield of VLSI products.

Figure 2.2 Classification of sources of yield loss, events, defects, failure mechanisms and faults

Below the terms used in the classification of figure 2.2 are discussed in more detail.

#### **Events**

The manufacturing of VLSI products contains hundreds of steps during which many incidents may cause disturbances in the process. An event may occur randomly and its impact may vary from wafer to wafer and from batch to batch. Events or combinations of events lead to unintended structural abnormalities on the wafer. For example the combination of local oxide thickness variation and proximity effects may cause lithographic problems.

From figure 2.2 it also becomes clear that there are much less symptoms that indicate yield loss than there are possible events causing it. Many different events may lead to exactly the same behavior during device testing.

#### Defects

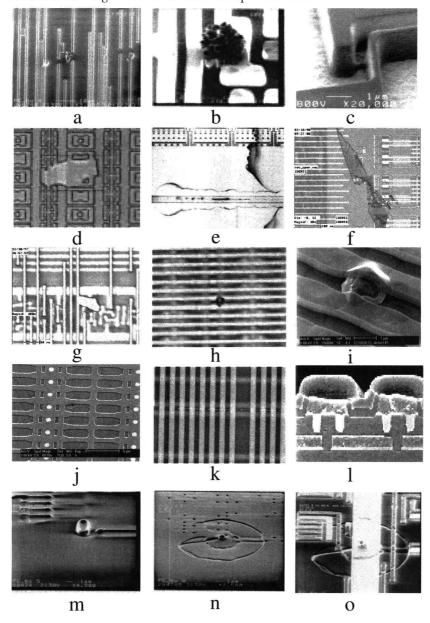

In many cases events lead to unintended structural abnormalities on a wafer called defects. Defects may include extra or missing materials that occur predominantly locally. Such defects are therefore often called spot defects. However, global

defects such as thickness or electrical parameter gradients across a batch, wafer or die exist as well. Figure 2.3 shows some examples of defects.

Figure 2.3 Examples of defects. a: CMP scratch; b: particle; c: bad focus; d: result of a blocked metal etch; e: residual stain; f: flake; g: blocked etch; h: small particle; i: decorated particle; j: gate oxide pinhole; k: stringer; l: open vias; m,n,o: defect integration

#### Failure mechanisms

The failure mechanism describes how a circuit failure results from a defect. For instance, extra or missing material may lead to open or shorted circuits resulting in a scan test fail. The same defect may trigger different failure mechanisms. For example, a gate oxide pinhole may cause gate leakage resulting in Iddq failure. A similar gate oxide pinhole may cause a shift in the threshold voltage of a transistor causing a delay fault.

It is important to realize that *not all defects*, or even the majority of defects, do *result in a failure.* Defects may, for example, occur in areas where they do not affect the structures that determine the functionality of the IC. In some cases ICs are designed in such a way that they are insensitive to certain types of defects by application of for example circuit redundancy or robustness to electrical parameter shift by statistical design methodologies [6,7]. Therefore often the term "killing defects" is used to distinguish defects that have an impact on yield from those that don't. Often the term "kill ratio" is used to quantify the probability that a defect, which is located on a random location on the die, causes an electrical failure. The kill ratio is therefore determined by defect type, defect size, and product sensitivity.

#### **Faults**

Whether a failure mechanism leads to a fault, and degrades the yield as such, depends on whether the product test program covers the affected area of the chip. Although scan tests usually have good test coverage, they never test the complete area of the die, nor all the electrical conditions that make the fail observable at the chip's outputs.

When chips are tested, the yield loss manifests itself in many ways. Therefore yield loss can be classified in many different ways. A few examples are given in the table 2.1.

| Classification of yield loss |                                                               |  |  |  |  |

|------------------------------|---------------------------------------------------------------|--|--|--|--|

| Manifestation                | <ul><li>Functional</li><li>Parametric / performance</li></ul> |  |  |  |  |

| Affected area                | <ul><li>Local</li><li>Global</li></ul>                        |  |  |  |  |

| Pattern                      | Random     Non random / systematic / gross                    |  |  |  |  |

Table 2.1 Classification of yield loss

#### Manifestation

A functional fault in an IC is detected when a test vector doesn't yield the expected result. In some cases the circuit is functional, but does not meet the specifications with respect to accuracy, attainable clock frequency or power due to parametric

variability of the process. In such cases the yield loss can be classified as performance related yield loss or parametric yield loss. The device may operate at certain operating conditions, but fail tests as a function of a continuous parameter such as supply voltage, current, or temperature.

#### Affected area

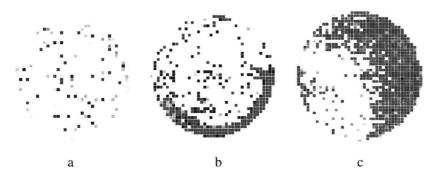

Whereas local yield loss occurs in small areas or points on the wafer, global yield loss is associated with large areas of the wafer such as the wafer center or edge. Local yield loss can for example be caused by random spot defects. Global yield loss can be caused by an electrical parameter gradient over the wafer. See figure 2.4.

#### Pattern

Random failures occur anywhere on the wafer in an unsystematic way. Random yield loss can be caused by for example scratches or particles causing shorts or opens. Both local and global yield loss can be random. Non-random failures tend to group or cluster on the wafer.

Systematic yield loss always occurs on the same dies on the wafer and can be caused by for example reticle defects.

Figure 2.4 Typical wafer maps with random (a) and both random and systematic yield loss (b,c)

#### 2.3 Yield Model Overview

Since the beginning of semiconductor manufacturing history yield models have played an important role in solving technical problems related to wafer productivity as well as in predicting yields for strategic decisions related to process development and shrinking. As a result much effort is put in the development and description of yield models over the years. This section shortly summarizes the main yield models that have been reported so far.

If  $A_s$  is the defect-sensitive area of a product, and D is the average number of killing defects per unit area, then the fault density, often designated as  $\lambda$ , is

$$\lambda = A_s D \tag{2.1}$$

and, if defect density is low, defects are distributed randomly across the wafer, and each failing die is killed by exactly one defect, the yield can be written as

$$Y = 1 - \lambda \tag{2.2}$$

However, in practice multiple killing defects may fall into one product resulting in a better overall yield than predicted by this simple linear model. Under the assumption that defect density is constant and distributed randomly across the wafer, Poisson statistics can be used and the product yield can be derived as [8]:

$$Y = e^{-\lambda} \tag{2.3}$$

In the case of non-random or systematic yield loss defects are not distributed randomly across the wafer. In such cases the yield loss can be translated into the loss of a fraction of the wafer area. See for example figure 2.4. Therefore this kind of yield loss can be accounted for in a yield model simply by adding a factor  $Y_0$  which is often referred to as the gross yield loss factor [9,10].

$$Y = Y_0 \cdot Y_{random} \tag{2.4}$$

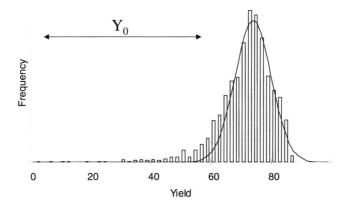

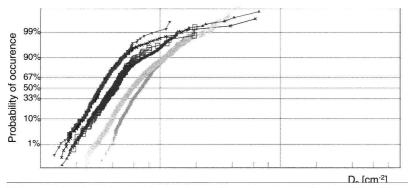

Systematic yield loss affects the 'tail' of the lower part of the yield distribution as is indicated in figure 2.5 that shows a typical wafer level yield distribution of one product for a large number of wafers. High  $Y_0$  values are usually caused by global defects that originate from for example sensitivity of the circuit to electrical parameter gradients over the wafer. Yield excursions on certain lots or wafers may also cause higher  $Y_0$  values. Such low yielding wafers often pose a reliability risk and therefore manufacturers usually set a cutoff limit for low yielding wafers at which they are to be rejected.

Figure 2.5 Example of a wafer level yield distribution for approximately 4000 wafers of one product

Whereas  $A_s$  is determined by design attributes such as die area, structure density, minimum design rules etc., D is determined by the defect characteristics of the manufacturing process. Therefore yield is always expressed in terms of IC design parameters and manufacturing process parameters:

$$Y = f(Manufacturing process, ICdesign)$$

(2.5)

The first yield models were developed for memory applications where the sensitivity to defects is largely determined by the design of the memory cell which is distributed homogeneously over the total chip area [11]. In that case the die area was an adequate design parameter to differentiate different products with respect to sensitivity to defects. Yield modeling was therefore dominated by the search for an accurate statistical description of the defect density distribution on the wafer and from wafer to wafer. This eventually led to the basic yield models of which the benefits and limitations are described in section 2.3.1.

When yield models are used for digital, analog, or mixed signal products with embedded memories, the differences in product sensitivity between products can get quite significant. In such cases other design parameters than just IC area must be considered to predict the yield. Some of the existing models that are based on design attributes are described in section 2.3.2.

### 2.3.1 Basic yield models

The defect density D, in a manufacturing process is not constant, but tends to vary from lot to lot, from wafer to wafer and even across the wafer. Many yield models have been proposed over the years that are based on different defect density distributions. To account for the defect density variability in these yield models, D is summed over all wafers using the following model [12]

$$Y = \int_{0}^{\infty} f(D)e^{-AD}dD \tag{2.6}$$

Where f(D) is the defect density distribution and

$$\int_{0}^{\infty} f(D)dD = 1 \tag{2.7}$$

An overview of the most generally used defect density distributions and the resulting yield models is given in table 2.2.

| Model                   | Compounder<br>function | Yield Formula                                                                                                                                                                 | References |

|-------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Murphy<br>(trangular)   | (iD)                   | $Y = \left(\frac{1 - e^{-\lambda}}{\lambda}\right)^2$                                                                                                                         | 12         |

| Murphy<br>(rectangular) | f(D)                   | $Y = \frac{1 - e^{-2\lambda}}{2\lambda}$                                                                                                                                      | 12         |

| Poisson                 | (iD)                   | $Y = e^{-\lambda}$                                                                                                                                                            | 2          |

| Seeds                   | (iD)                   | $Y = \frac{1}{1+\lambda}$                                                                                                                                                     | 13,14      |

| Gamma                   | (D)                    | $Y = \left(1 + \frac{\lambda}{\alpha}\right)^{-\alpha}$                                                                                                                       | 15         |

| Truncated<br>Gaussian   | f(D)                   | $Y = \exp\left(\frac{A^2 \gamma^2}{2} - AD_p\right)^{1 + erf\left(\frac{A\gamma}{\sqrt{2}} - \frac{D_p}{\gamma\sqrt{2}}\right)} + erf\left(\frac{D_p}{\gamma\sqrt{2}}\right)$ | 16         |

**Table 2.2** Basic yield models and their defect density distributions.  $\lambda$  = fault density, f(D)=defect density distribution,  $\alpha$  = clustering factor, Dp = peak of distribution

#### Murphy's yield model

Murphy was the first to propose a non-constant defect density in manufacturing processes. Murphy's model was the base for the development of many yield models, each assuming a different defect density distribution. To demonstrate the effect that the defect density distribution has on the predicted yield, Murphy tried a triangular and uniform defect density distribution. See also table 2.2.

#### Seeds yield model

Because Seeds observed a large number of wafers with low defect density and only a limited number with high defect density, he assumed an exponential defect density distribution as the compounder of his yield model. Seeds himself found that his model overestimated the yield.

#### Poisson model

Probably the best-known and most used yield model is the Poisson yield model [2]. The Poisson model uses a delta function as compounder in Murphy's yield integral, which means that it assumes that defects are uniformly distributed and constant across the wafer. Due to the relatively good accuracy and simplicity, [5], the Poisson model is often used for planning purposes and for reporting yield performance trends of manufacturing processes. In an attempt to make this reporting independent of the products that are made in the process, not the yield is reported, but the average defect density. For this purpose the Poisson model is rewritten as:

$$D_0 = \frac{1}{K} \sum_{i=1}^{K} \frac{-\ln(Y_i)}{A_i}$$

(2.8)

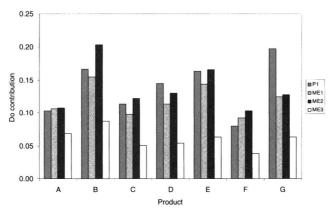

Where  $D_0$  is the average density of killing defects and K is the number of products on which yield is measured. This methodology for defect density reporting can only be adequate if the variance in product sensitivities is small. When the differences between products become too large, more design parameters have to be taken into account.

The Poisson model is known to underestimate the yield of large products. This is a result of the assumption that defects are randomly distributed across the wafer, which is often not the case.

#### Negative Binomial model (Gamma defect density distribution)

Defects have the tendency to cluster on the wafer. The negative binomial or Gamma model introduces an extra parameter to account for this effect. The negative binomial model is a very widely used model as well. It uses an extra parameter  $\alpha$  which is equal to the inverse square of the coefficient of variation of the Gamma distribution, but also can be interpreted as a parameter that characterizes the level of defect clustering. Parameter  $\alpha$  increases with decreasing variance in the defect distribution. An important attribute of the Gamma distribution is that  $\alpha$  can be used to emulate other distributions. For instance, when there is little clustering,  $\alpha$  is high and the yield model approaches the Poisson model.

$$Y = \lim_{\alpha \to \infty} \left( 1 + \frac{\lambda}{\alpha} \right)^{-\alpha} = e^{-\lambda}$$

(2.9)

Similarly, if the clustering is high,  $\alpha$  will be close to 1, and the yield model approaches the Seeds model:

$$Y = \lim_{\alpha \to 1} \left( 1 + \frac{\lambda}{\alpha} \right)^{-\alpha} = \frac{1}{1 + \lambda}$$

(2.10)

α can be derived from the mean and variance of failing devices [17]. The more defect mechanisms exist with varying degrees of clustering, the larger is the overall clustering factor [18,19]. The negative binomial model has proven to be accurate in several cases [20]. The advantage of the model is that the extra clustering parameter gives more fitting capability than in the single parameter yield models such as the Poisson model or Seeds model. However, an extra parameter means also extra parameter extraction costs.

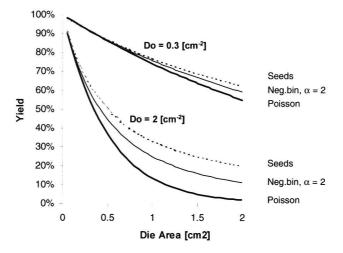

Figure 2.6 compares the yield models described above at typical and high defect densities (~0.3 cm<sup>-2</sup> and 2 cm<sup>-2</sup>). At typical defect densities and device areas (0.5-1cm<sup>2</sup>) the yield models results do not differentiate very much. For high defect densities the differences in yield model results can be substantial.

Figure 2.6 Comparison between yield models

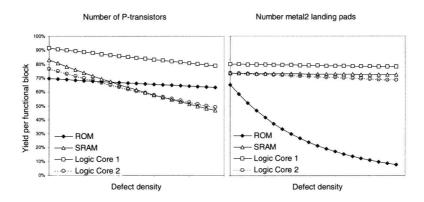

### 2.3.2 Yield models based on design attributes other than device area

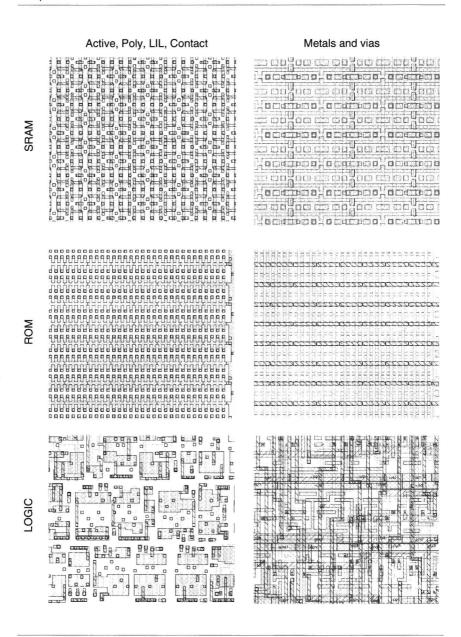

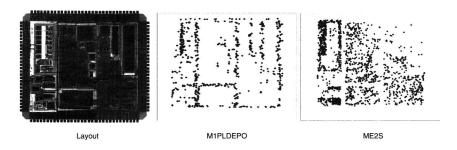

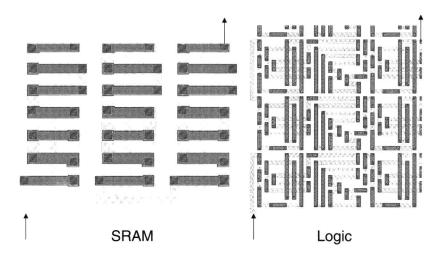

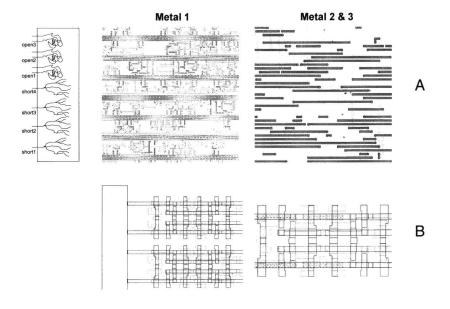

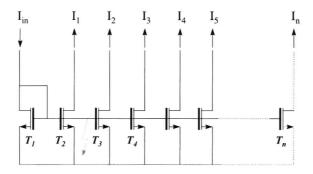

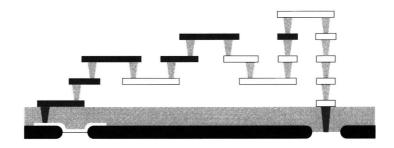

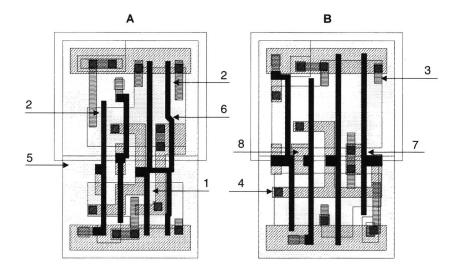

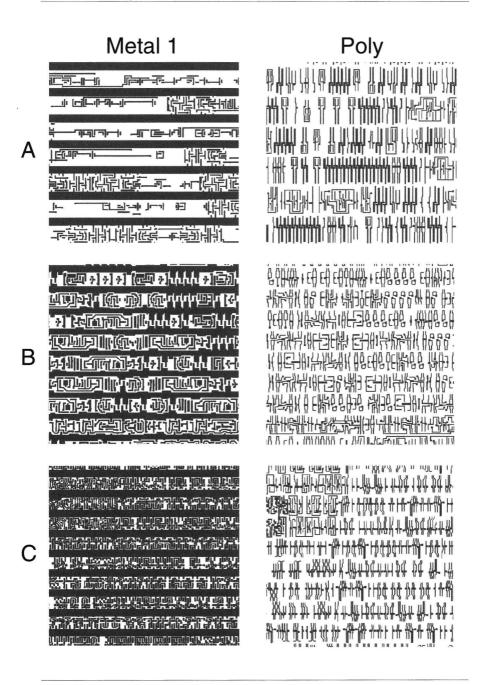

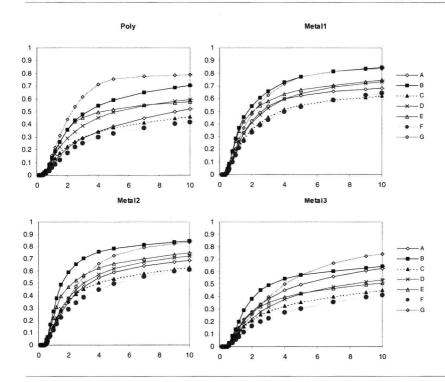

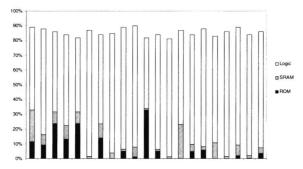

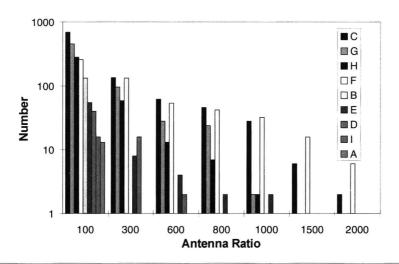

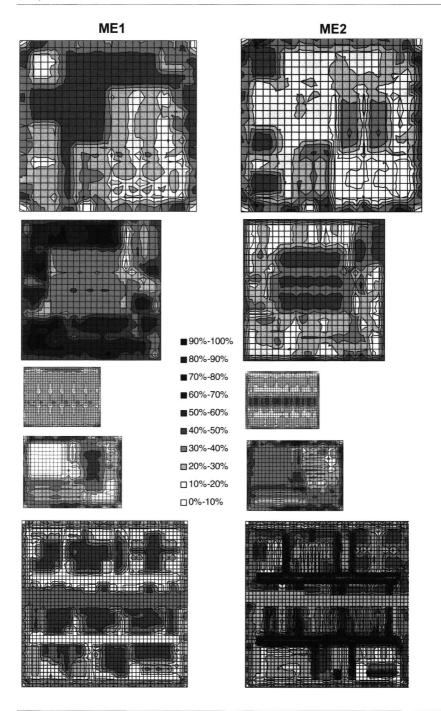

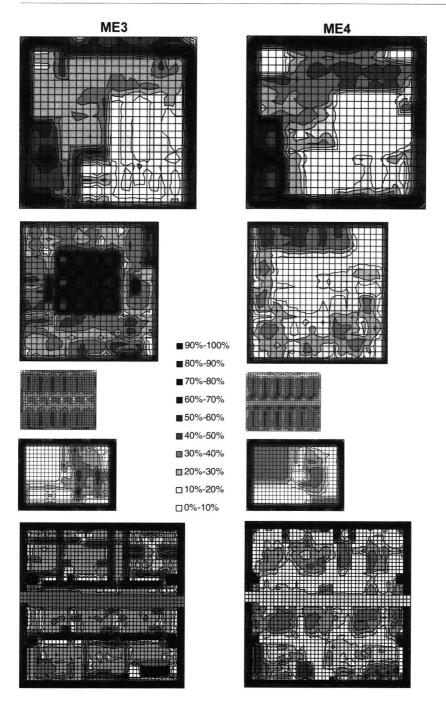

Whether or not a defect will affect the functionality of a device depends on the local sensitivity of the product in the area where the defect occurs. The local density of designed structures can for example determine the sensitivity of this area. Under the condition that there is little variance of the sensitivity within the product nor between different products, the product yield can be adequately predicted using the models described in the previous section. This is for example the case in the manufacturing of products that consist of mainly one design style such as memories or completely digital products. In these design styles the structure density is homogeneously distributed across the die, and once the average sensitivity is known, the sensitivity (critical area) of similar products with different sizes can be assumed proportional to the die area and can thus be extrapolated. However, if within the same die, different design styles are used as in applications for mixed signal or digital logic with embedded memory, the spatial sensitivity distribution within a product and also the sensitivity differences between different products can be quite significant [1]. The probability that a defect will kill the die, strongly depends on what location of the IC it occurs. In figure 2.7 an example of different design styles that can exist within one product are shown. SRAM is very densely packed in the front-end layers, but uses only the lower metal layers. Logic area is much less dense than SRAM or ROM, but uses more high metal layers. The particular ROM shown in figure 2.7 uses many more vias than SRAM and logic. It is obvious that the extent of the yield loss for those different design styles will be very different, even though they are manufactured at the same time in the same process. The yield of a product is therefore determined by the sensitivity of each design style itself and by how the die area is divided between the different design styles. This section describes how design sensitivity can be accounted for in the various yield models.

Figure 2.7 Different design styles with different structure densities and sensitivities

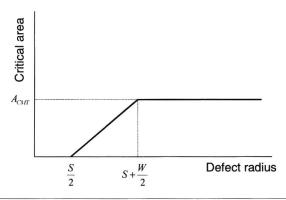

#### Critical area yield model

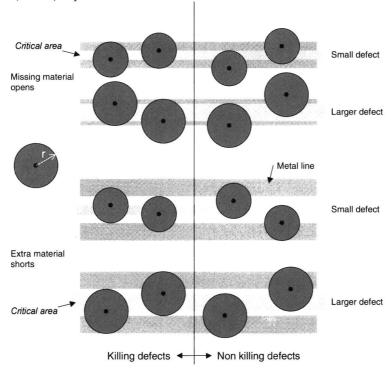

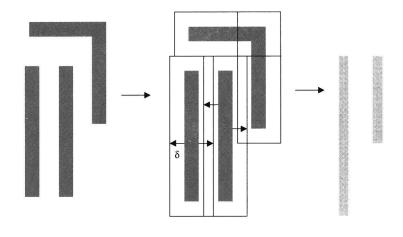

As was indicated before, not the total die area, but only part of it is sensitive to defects. The part of the circuit that is sensitive to yield loss is often expressed in terms of *critical area*, which can be defined as the area in the die in which the center of a defect must be situated to create a fault [21-23]. Because the critical area depends both on the type and size of the defect, it is always reported for a specific defect type and is measured as a function of the size of the defect. The defect model that is used to describe the failure mechanism is crucial for the critical area yield model.

Figure 2.8 shows an example where the killing defects are modeled by disk shaped material of extra or missing material. As can be seen from the figure, the critical area (shaded) depends on the radius of the defect.

Figure 2.8 Concept of critical area (shaded) for shorts and opens

When the critical area  $A_{ci}(r)$  as a function of defect size r can be calculated for defects of type i, and the corresponding defect size distribution of the manufacturing process  $D_i(r)$  is known, the fault density can be calculated as:

$$\lambda_i = \int_0^\infty A_{Ci}(r)D_i(r)dr \tag{2.11}$$

and if there are N defect types for which, based on the defect density distribution, a Poisson based yield model can be used, the total yield of a product can be calculated as

$$Y = \prod_{i=1}^{N} e^{-\lambda_i} \tag{2.12}$$

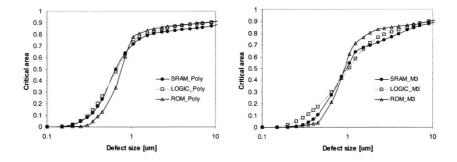

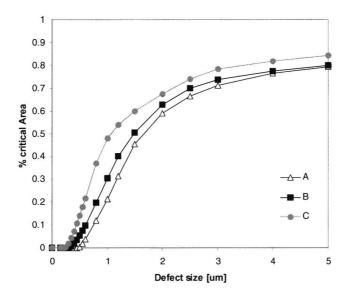

Figure 2.9 shows typical normalized critical area curves for poly and metal 3 for SRAM, ROM and standard cell logic blocks, as shown in figure 2.7.

Figure 2.9 Critical area curves for poly and metal 3 shorts extracted from SRAM, ROM and random logic designs

The defect size distribution is often modeled using

$$D_i(r) = \frac{K}{r^p} \tag{2.13}$$

Where K describes the defect density level and p describes the rate of increase of defect population with the defect size [24-26]. Values between 2 and 4 are reported in literature for p.

The value of p for a manufacturing process is a very important factor in yield calculations. It describes the relationship between the number of small and large defects. It can be shown that the value of p determines whether it makes sense to shrink ICs [25]. When a die is shrunk with a certain factor, the die becomes smaller and therefore will contain less defects when the defect density remains unchanged. However, at the same time, due to the shrink the die will be more sensitive to the defects. When p equals 3, these two effects exactly compensate each other, and the yield for the shrunk die and the original die will remain equal,

but more dies can be placed on the wafer and thus the wafer efficiency is increased. When p is larger than 3, the impact of the smaller defects on the shrunk die will be relatively larger and the yield of the shrunk die decreases.

Critical area yield models have been derived for opens and shorts for conducting materials such as metals, poly and diffusion areas. Yield models based on the extraction of critical area for vias and contacts exist as well [27,28].

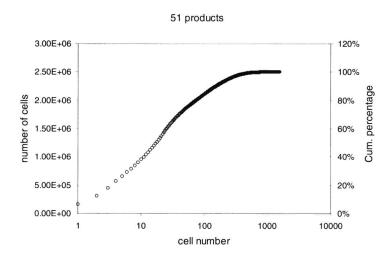

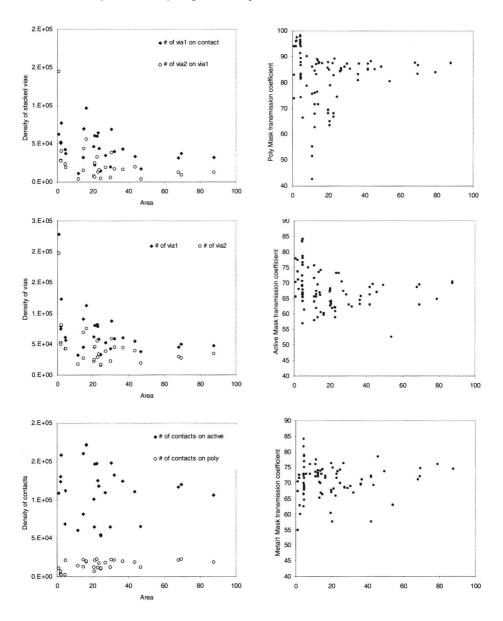

#### 2.3.3 Critical area model derivatives

In real life situations, critical area yield models have proven to accurately predict spot defect related yield loss in various memory, digital and mixed signal applications. However, the continuous characterization of the manufacturing process in terms of defect size distributions is a difficult task which involves many in-line inspections or test structure measurements on silicon [29-33]. In addition, substantial costs are involved in the computation of critical area for different products and for different types of defects for each manufacturing layer. (See also chapter 3). The costs associated implementing a critical area model are therefore often the reason why simpler models are derived from the critical area model. Such models can then be based on the notion that the critical area of an IC is determined by the density of structures in the circuit which usually correlates well with much simpler design attributes such as the transistor density, the number of nets, the total interconnect length, the number of vias, or mask transmission coefficients. Such attributes do not require extensive product and process characterization because they are much easier to obtain. An additional advantage in the application of such models is that often the necessary design parameters are already available in an early stage of the design phases of a product. Yield predictions and the related design tradeoffs can therefore be made before the complete layout is finished. Such yield models can be classified as critical area yield model derivatives.

#### One layer critical area model

Within a category of products there is a high probability that the critical area in one layer correlates well with critical area in other layers. A high transistor density usually means a high number of nets and therefore the critical area in the metal layers will be high as well. Therefore, in [34] for example, a one-layer critical area model is proposed in which metal 1 critical area is taken for product sensitivity characterization. The advantage being that only critical area of only one metal layer needs to be extracted.

#### Critical area slope model

To simplify the extraction even more, in [34] it is shown that the initial slope of the critical area curve characterizes critical area very well and can be used adequately to predict the yield loss due to spot defects. This can be explained by the fact that small defects occur much more frequently than large defects. (See equation 2.13)

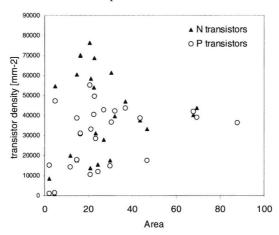

#### Transistor based yield models

In some applications metal 1 is mostly used as a local interconnect and therefore the critical area of metal 1 correlates well with the number of transistors in the circuit. In such cases the fault density can be modeled by

$$\lambda = NPoF \tag{2.14}$$

where N is the number of transistors and PoF the probability of failure that needs to be fitted to the actual measured product yields. It is obvious that the extraction of the number of transistors from the design takes only a fraction of the time that is required for calculation of the critical area of an IC.

A more advanced transistor based model is described in [35]. This model takes into account the number of minimum feature size squares that are needed to define a single "average" transistor (d<sub>d</sub>), minimum feature size of the manufacturing process (f),

$$\lambda = \frac{N_{tr} d_d D}{f^{p-2}} \tag{2.15}$$

D and p are defect characterization parameters.

#### Yield model based on the netlist

In [36] a model is described that takes the netlist of a circuit and defect size distribution parameters as an input to predict the yield. For standard cell logic the model produces adequate results because the number of nodes in the netlist of a product correlates well with the average critical area that is generated after routing. This is especially the case when the different products are designed using the same design tools.

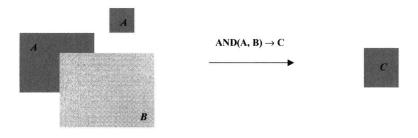

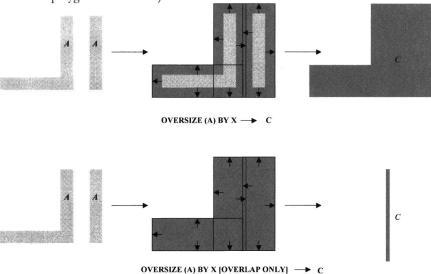

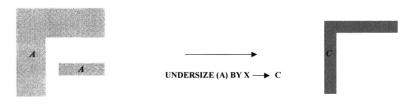

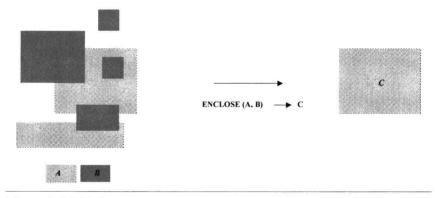

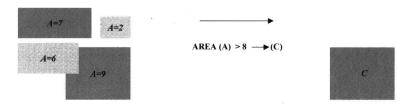

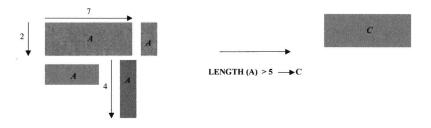

### 2.3.4 Yield model for any design attribute

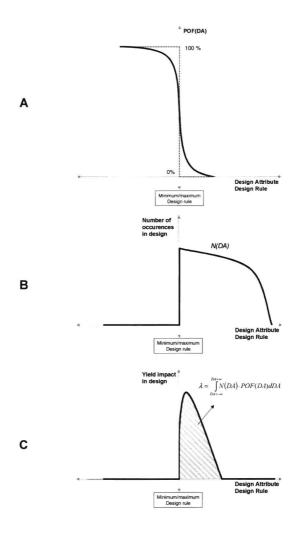

Design rule manuals are often interpreted in a "digital" manner: structures that are designed according to design rule have a 0% probability of fail, while structures that violate the design rules always have a 100% probability of fail. In practice however this is not the case as is shown in figure 2.10A that shows the probability of fail of a structure as a function of a design attribute. The yield of any designed structure is a function of the applied design attributes such as spacings, widths, areas, overlaps, extensions or combination of those.

If the probability of fail for a structure as a function of the design attributes is known PoF(DA), and the number of occurrences in an IC layout of each of those structures as a function of that same attribute is N(DA), then the total fault density of the design attribute in the product is:

$$\lambda_{DA} = \int_{DA-\infty}^{DA=\infty} N(DA) \cdot PoF(DA) dDA$$

(2.16)

as is shown in figure 2.10B,C.

If the probability of fail for a design attribute is varying across the wafer (x,y) then the fault density can be expressed as

$$\lambda_{DA} = \int_{y=-\infty}^{y=+\infty} \int_{x=-\infty}^{x=+\infty} \int_{DA=-\infty}^{DA=\infty} N(DA, x, y) \cdot PoF(DA, x, y) dDA dx dy \quad (2.17)$$

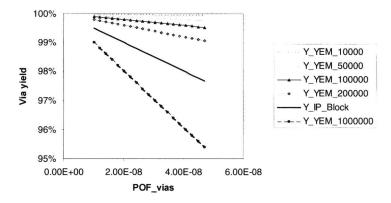

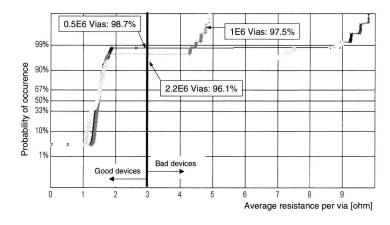

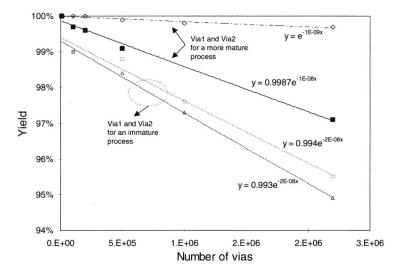

If the probability of fail for a designed structure is constant over a wafer and there is no dependency on a design attribute (This can for example be the case for vias that are implemented in only one size) then

$$\lambda_{DA} = N_{DA} PoF_{DA} \tag{2.18}$$

Where  $N_{\rm DA}$  is the number of occurrences of the structure in the product (e.g. number of vias) and  ${\rm PoF_{\rm DA}}$  is the failure rate of that structure, as is measured from for example a test structure.

Critical area yield models for vias exist, however, because of the computational effort calculating critical area of vias as a function of defect size, often model (2.18) is used for calculating yield loss due to vias. It is obvious that the extraction of the number of vias from the design takes only a fraction of the time required for critical area extraction.

**Figure 2.10** Probability of fail, occurrence in a product, and fault density of a structure as a function of a design attribute such as spacing, area, width, or overlap

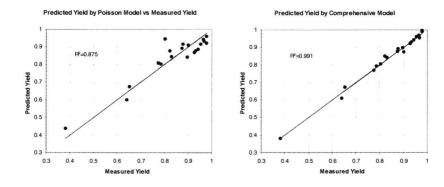

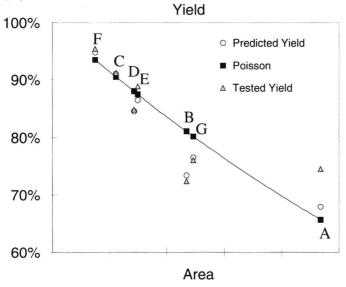

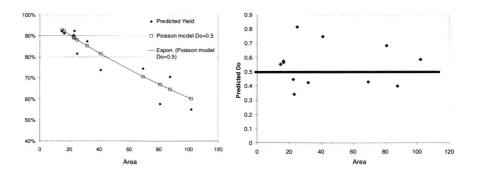

# 2.3.5 Experimental comparison of yield models

In the experiment described below a comparison was made between different yield models [36]. The purpose of this experiment was to verify whether it is possible to develop a yield model that is as simple as the Poisson model with respect to design parameter extraction and at the same time is as adequate as a critical area model to explain the yield differences between products with different design styles in the same manufacturing process.

## Models

The set of models as listed in table 2.3 were chosen, assuming that the yield equals  $e^{-\lambda}$ . Models 1-4 are described in the previous sections. Models 5-8 are new transistor-based models.

| Model # | λ                                                         | Parameters                                                                                                                                                                                        |

|---------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | $A_{ch} 	imes D_0$                                        | $A_{ch}$ : chip area; $D_0$ :defect density;                                                                                                                                                      |

| 2       | $\int_0^\infty A_{cr}(r) \times D(r) dr$                  | $A_{cr}(r)$ :critical area for defects of radius $r$ : $D(r)$ :defect density for defects of radius $r$ :                                                                                         |

| 3       | $Ntr \times Dd \times Fs^p \times D$                      | $egin{align*} Ntr: & 	ext{number of transistors; } Dd: & 	ext{design density;} \ Fs: & 	ext{feature size; } D: & 	ext{defect density;} \ p: & 	ext{power factor for feature size;} \end{aligned}$ |

| 4       | $Ntr \times Dd \times Fs^p \times D^{\frac{d^*}{Dd}}$     | $Ntr, Dd, Fs, p, D$ : same as above; $d^*$ : power factor for defect density;                                                                                                                     |

| 5       | $P_{of1} \times Ntr$                                      | $Ntr$ : same as in Simple Model 1; $P_{of1}$ : possibility of fail;                                                                                                                               |

| 6       | $P_{of2} \times Ntr \times Dd^r$                          | Ntr, Dd : same as in Simple Model I;<br>r :power factor for design density;<br>$P_{of2}$ : possibility of fail;                                                                                   |

| 7       | $P_{of3} \times Ntr \times Dd^r \times Fs^p$              | $Ntr, Dd, Fs, p$ : same as in Simple Model 1; $r$ : same as in design density model; $P_{of3}$ : possibility of fail;                                                                             |

| 8       | $P_{of 4} \times NTr \times Dd^r \times Fs^p \times Lm^k$ | $Ntr, Dd, Fs, p, r$ :same as above; $Lm$ : number of metal layers; $k$ : power factor for number of metal layers; $P_{of\ 4}$ : possibility of fail.                                              |

Table 2.3 Models under investigation

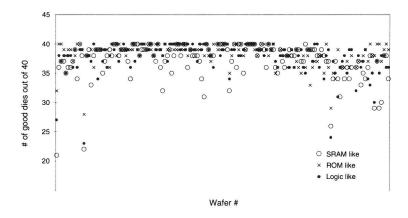

## Manufacturing data

Manufacturing yield data was taken from products running in one CMOS fab line with different (0.5μm, 0.4μm, 0.35μm and 0.25μm) feature sizes. In total a subset of 23 products were selected for analysis. Only mature products with no known parametric yield loss components were chosen for the analysis. Immature products and products with substantial analog components were also excluded from the experiment. Special attention was paid to the choice of the period of time in which data was collected. To make sure that the estimated yield model parameters were stable (i.e. were unaffected by the ongoing yield learning process), the periods of observation were limited to relatively short intervals of approximately 100 days, covering a total period of 300 days. Within each time interval it can be assumed that the large variety of products is exposed to the same process conditions. Information about the sample size is indicated in table 2.4. For proprietary reasons only three categories of sizes are mentioned: SMALL – if sample size is more than 100, MEDIUM - if more than 500 and LARGE - if the sample size is more than 1000 wafers. In total the number of wafers used for this experiment was more than 40000. Figure 2.11 shows examples of the wafer level yield trends that were used for the experiment.

Figure 2.11 Scatter plots of the yield for three different products

| Product | Technology  |           | Area * | Num. Of | Time  | Zone 1  | Time  | Zone 2  | Time  | Zone 3  |

|---------|-------------|-----------|--------|---------|-------|---------|-------|---------|-------|---------|

| Product | F.Size( µm) | #M.Layers | Area   | Tr.*    | Yield | S. Size | Yield | S. Size | Yield | S. Size |

| 1       | 0.50        | 3         | 1.00   | 0.0017  |       |         | 0.979 | Small   | 0.985 | Small   |

| 2       | 0.50        | 3         | 1.98   | 0.0062  |       |         | 0.979 | Small   | 0.978 | Small   |

| 3       | 0.40        | 3         | 4.33   | 0.1357  | 0.890 | Medium  | 0.895 | Large   | 0.900 | Small   |

| 4       | 0.40        | 3         | 2.16   | 0.0425  | 0.958 | Medium  | 0.953 | Medium  |       |         |

| 5       | 0.40        | 3         | 1.70   | 0.0590  | 0.967 | Small   | 0.967 | Small   |       |         |

| 6       | 0.40        | 3         | 3.03   | 0.0611  | 0.943 | Large   | 0.943 | Large   | 0.945 | Large   |

| 7       | 0.40        | 3         | 3.53   | 0.0967  | 0.912 | Large   | 0.926 | Large   | 0.917 | Large   |

| 8       | 0.40        | 3         | 2.99   | 0.0613  | 0.946 | Small   | 0.942 | Small   | 0.941 | Small   |

| 9       | 0.40        | 3         | 3.22   | 0.0803  | 0.931 | Large   | 0.931 | Large   | 0.930 | Large   |

| 10      | 0.40        | 3         | 1.42   | 0.0317  | 0.965 | Small   | 0.964 | Small   | 0.964 | Small   |

| 11      | 0.35        | 5         | 6.63   | 0.5852  | 0.643 | Small   |       |         | 0.741 | Small   |

| 12      | 0.35        | 5         | 3.24   | 0.2161  | 0.829 | Large   | 0.822 | Large   |       |         |

| 13      | 0.35        | 5         | 2.14   | 0.1597  | 0.886 | Medium  | 0.877 |         |       | Small   |

| 14      | 0.35        | 5         | 2.38   | 0.1990  | 0.875 | Medium  | 0.900 | Medium  | 0.897 | Small   |

| 15      | 0.35        | 5         | 5.27   | 0.3552  | 0.752 | Large   | 0.775 | Medium  | 0.791 | Small   |

| 16      | 0.35        | 5         | 4.17   | 0.2086  | 0.796 | Medium  | 0.829 | Large   | 0.847 | Large   |

| 17      | 0.35        | 5         | 5.49   | 0.2782  | 0.762 | Medium  | 0.785 | Medium  |       |         |

| 18      | 0.35        | 5         | 9.85   | 0.4603  | 0.653 | Small   | 0.652 | Small   | 0.722 | Medium  |

| 19      | 0.35        | 5         | 12.71  | 0.5640  | 0.597 | Medium  | 0.640 | Large   | 0.630 | Large   |

| 20      | 0.35        | 5         | 2.84   | 0.1637  |       |         | 0.873 | Medium  | 0.910 | Small   |

| 21      | 0.35        | 5         | 20.54  | 1.2391  |       |         | 0.382 | Small   | 0.416 | Small   |

| 22      | 0.35        | 5         | 10.07  | 0.5784  | 0.562 | Small   |       |         | 0.632 | Small   |

| 23      | 0.25        | 5         | 1.40   | 0.2173  |       |         | 0.804 | Small   | 0.801 | Small   |

**Table 2.4** Product manufacturing data. \*Note: All data has been normalized for proprietary reasons

#### Results

In order to filter out low yielding wafers due to accidents, for each time period the median value of the wafer level product yields was taken to fit the yield models listed in table 2.3. The model parameters were tuned to minimize the average error. Table 2.5 shows the obtained average error, maximum error and correlation coefficient. Figure 2.12 shows the predicted yield versus the measured yield for all the models listed in table 2.3. The obtained results with model-8 are the most accurate.

| Model # | Average error for time zone |       |       | Maximum error for time zone |        |        | R <sup>2</sup> for time zone |       |       |

|---------|-----------------------------|-------|-------|-----------------------------|--------|--------|------------------------------|-------|-------|

|         | 1                           | 2     | 3     | 1                           | 2      | 3      | 1                            | 2     | 3     |

| 1       | 5.20%                       | 5.10% | 5.00% | 9.80%                       | 14.10% | 14.70% | 0.863                        | 0.875 | 0.89  |

| 2       | 2.10%                       | 3.60% | 4.10% | 4.50%                       | 12.00% | 15.50% | 0.975                        | 0.963 | 0.947 |

| 3       | 2.90%                       | 2.20% | 1.90% | 7.20%                       | 6.40%  | 5.00%  | 0.952                        | 0.976 | 0.983 |

| 4       | 2.40%                       | 2.80% | 3.30% | 5.10%                       | 9.30%  | 11.20% | 0.977                        | 0.96  | 0.953 |

| 5       | 2.10%                       | 1.90% | 2.90% | 4.70%                       | 5.00%  | 8.20%  | 0.973                        | 0.983 | 0.964 |

| 6       | 1.60%                       | 1.80% | 2.20% | 3.80%                       | 4.50%  | 7.30%  | 0.988                        | 0.985 | 0.978 |

| 7       | 1.40%                       | 1.40% | 1.40% | 3.50%                       | 3.30%  | 3.30%  | 0.989                        | 0.991 | 0.992 |

| 8       | 1.40%                       | 1.50% | 1.30% | 3.50%                       | 3.20%  | 3.20%  | 0.989                        | 0.991 | 0.991 |

**Table 2.5** Model tuning results per time zone. Each time zone represents 100 days of manufacturing

Figure 2.12 Predicted versus modeled yield for model 1 (Poisson) and model 8

#### Conclusions

Based on the results above it can be concluded that accurate spot defect related yield prediction is feasible with simple models. The more design parameters that correlate with critical area are included in the model the better the model predicts the differences in yield loss between products. The advantage of the models used for the above comparison is that the necessary design attributes can easily be determined before the design process is completed. Therefore yield prediction can be performed at very low cost and still be accurate enough to enable appropriate design-manufacturing tradeoffs.

## 2.4 Conclusions and discussion

With the small windows of opportunity for modern VLSI products on the market, yield and the predictability thereof are important parameters determining economic success or failure. Thus, predictive yield modeling capabilities are crucial in both the design and manufacturing environments of VLSI products.

In this chapter existing yield models are described. In specific situations the models are reported to adequately describe yield loss for many different failure mechanisms. As an example, in a practical situation of a stable manufacturing process of which the yield loss was mainly driven by random defects, a comparison of existing and new yield models was done. Results show that in such a situation accurate spot defect related yield prediction is feasible. Whereas models that only take into account the area of the IC do not predict the yield very accurately, models that take into account design density parameters do. The more design parameters that correlate with critical area are included in the model, the better the differences in yield loss between products is predicted.

The challenge of yield prediction for a user now does not lie in the development of even more new yield models, but in the accurate extraction of parameters to calibrate these models. What models and parameters to use depends on the specific goal and on the ability to accommodate the associated costs of yield model parameter extraction. For some applications parameter extraction may be easy and inexpensive, for others difficult and costly. Therefore the user of a yield model should always clearly determine what are the goals and corresponding costs of the yield prediction. Is absolute yield prediction accuracy for example really important? Or does he only need to explain relative differences between products? The yield prediction and yield model parameter extraction methodology described in the next chapter plays an important role in dealing with this trade-off.

# **References Chapter 2**

- Stapper C.H. and R.J. Rosner, Integrated Circuit Yield Management and Yield Analysis: Development and Implementation, IEEE Trans. SEM, 8,1995, pp.95-102

- Cheek G. and G. O'Donoghue, Yield Models in a Design for Manufacturability Environment: A bibliography, IEEE/SEMI int. Semiconductor Manufacturing Science Symposium, -, 1993, pp. 133-135

- 3. Maly W., Yield Models: A Comparative Study, Int. Workshop on Defect and Fault Tolerance in VLSI Systems, 2,1990, pp.15-31

- Stapper C.H., Fact and fiction in yield modeling, Microelectron. J., 20,1989, pp.129-151

- 5. Ferris-Prabhu A.V.,On the Assumptions Contained in Semiconductor Yield Models, IEEE Trans. CAD,11,1992, pp.966-975

- 6. Li M., Milor L.", Computing Parametric Yield Using Adaptive Statistical Piecewise Linear Models, IEDM, 1996, pp.473-476

- Milor L., A. Sangiovanni-Vincentelli", Computing Parametric Yield Accurately and Efficiently, IEDM, 1990, pp.116-119

- 8. Hofstein, S.R and Heiman, F.P", The silicon insulated gate field effect transistor, "proc. IEEE, vol.51, no 9", 51 no. 9,1963, pp.1190-1202

- Paz, O, Lawson. T.R", Modification of Poisson statistics: modeling defects induced by diffusion, IEEE J. Solid State Circuits, SC-12 no.5, 1977, pp.540-546

- 10. Stapper, C.H",LSI yield modeling and process monitoring, IBM J. Res. Dev,20,1976, pp.228-234

- 11. Stapper C.H.,The Defect-Sensitivity Effect of Memory Chips,IEEE J. SC,21,1986, pp.193-198

- 12. Murphy B.T. ,Cost-Size Optima of Monolithic Integrated Circuits,Proc. IEEE,52,1964, pp.1537-1545

- 13. Seeds R.B, Yield and Cost Analysis of Bipolar LSI, IEEE int. electron Devices Meeting, oct, 1967.

- 14. Seeds R.B, Yield Economic and Logistic Models for Complex Digital Arrays, "IEEE int. Conv. Rec, Pt.6", 1967, pp.60-61

- 15. Okabe T. et al., Analysis of Yield of Integrated Circuits and a New Expression for the Yield, Electrical Engineering in Japan, 92, 1972, pp. 135-141

- Stapper C.H., On Murphy's Yield Integral, IEEE Trans. SEM, 4,1991, pp.294-297

- 17. Stapper C.H.,The effects of wafer to wafer defect density variatons on integrated circuit defect and fault distributions,IBM J. Res. Develop.,29,1985, pp.87-97

- 18. Collica R.S., The Effect of the Number of Defect Mechanisms on Fault Clustering and its Detection Using Yield Model Parameters, IEEE Trans. SEM, 5,1992, pp.189-195

- 19. Ferris-Prabhu A.V., A Cluster-Modified Poisson Model for Estimating Defect Density and Yield, IEEE Trans. SEM, 3,1990, pp.54-59

- 20. Cunningham J.A,The Use and Evaluation of Yield Models in Integrated Circuit Manufacturing,IEEE Trans. SEM,3,1990, pp.60-71.

- 21. Maly W, Modeling of Point Defect Related Yield losses for CAD of VLSI Circuits, Proc. Of ICCAD-84, Nov, 1984, pp.161-163.

- 22. Maly W. and J.Deszczka, Yield Estimation Model for VLSI Artwork evaluation, Electronics Letters, 19,1983, pp.226-227.

- 23. Maly W., Modeling of Lithography Related Yield Losses for CAD of VLSI Circuits, IEEE Trans. CAD, 4,1985, pp.166-177.

- 24. Maly W. et al., "Characterization of Type, Size and Density of Spot Defects in the Metalization Layer", Yield Modeling and Defect Tolerance in VLSI, Adam Hilger Philadelphia", 1988, pp.71-90.

- 25. Stapper C.H. Modeling of defects in integrated circuit photolithographic patterns, IBM J. Res. Develop.,28,1984, pp.461-475.

- 26. Unsoeld A. Stromdichte von Teilchen verschiedener Massen, Der neue Kosmos, 1967, pp.70.

- Ouyang C. and W. Maly, Efficient Extraction of Critical Area in Large VLSI IC's, Proc. IEEE Int. Symposium on Semiconductor Manufacturing, 1996, pp.301-304

- 28. Ouyang C., W. Pleskacz and W. Maly, "Extraction of Critical Area for Opens in Large VLSI Circuits", Proc. IEEE In. Workshop on Defect and Fault Tolerance of VLSI Systems,-,1996, pp.21-29.

- 29. Hess C, L. H. Weiland, "Novel Methodology to Include all Measured Extension Values per Defect to Improve Defect Size Distributions", IEEE/SEMI Advanced Semiconductor Manufacturing Conference,-,1998, pp.197-202.

- 30. Milor L. et al., "Yield Modeling Based on In-Line Scanner Defect Sizing and Circuit's Critical Area", IEEE Trans. SEM,12,1999, pp.26-35.

- 31. Dudivier F., M. Rivier, "Approximation of Critical Area of IC's with Simple Parameters Extracted from the Layout", Int. Workshop on Defect and Fault Tolerance in VLSI Systems, 1995, pp.1-9.

- 32. Khare J.B., W. Maly, and M.E. Thomas, "Extraction of Defect Size Distributions in an IC Layer Using Test Structure Data", IEEE Trans. SEM,7,1994, pp.354-368

- 33. Maly W. et al, "Double Bridge Test Structures for the Evaluation of Type, Size and Density of Spot Defects", Carnegie Mellon University Research Report CMUCAD-87-2, 1987.

- 34. Heineken H.T., J. Khare, and W. Maly, "Yield Loss Forecasting in the Early Phases of the VLSI Design Process", IEEE Custom IC Conf., 1996.

- 35. Maly W., H.T. Heineken, and F. Agricola", A Simple New Yield Model, Semic. Int., July ,1994, pp.148-154.

- 36. Yanwen Fei, Paul Simon, and Wojciech Maly "New Yield Models for DSM Manufacturing", IEDM Conference 2001

# **Chapter 3**

# Yield Prediction Methodology and Model Parameter Extraction

37

3

## 3.1 Introduction

Yield modeling is not a goal in itself neither in a design environment nor in a manufacturing environment. However, as discussed in the previous chapter, predictive yield models are essential both for forecasting product cost and for managing yield improvement activities. The usefulness of any yield model depends on the ability of the user to calibrate the necessary parameters. This chapter describes the extraction of the yield model parameters related to the design and the process.

Section 3.2 discusses yield prediction methodology in general. In section 3.3 the extraction of process related yield model parameters is presented. Section 3.4 discusses design related yield model parameter extraction and section 3.5 describes the development and implementation of an industrial manufacturability assessment environment (MAE).