# Semiconductor-technology exploration: getting the most out of the MOST

Citation for published version (APA):

Veendrick, H. J. M. (2002). Semiconductor-technology exploration: getting the most out of the MOST. [Phd Thesis 2 (Research NOT TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR556906

DOI:

10.6100/IR556906

Document status and date:

Published: 01/01/2002

Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 04. Oct. 2023

# Semiconductor-Technology Exploration getting the most out of the MOST

Harry Veendrick

Dit proefschrift is goedgekeurd door de promotoren:

prof.dr.ir. A.H.M. van Roermund en prof.dr.ir. R.H.J.M. Otten

Colophon:

Cover design: Hennie Alblas Figures: Hennie Alblas

Type setting: Ivonne Hermens

Printed by: University Press, Eindhoven

#### *Explanation of the cover:*

The cover shows the limits of the Semiconductor Road, symbolically represented by the icebergs appearing on the horizon.

The work described in this thesis has been carried out at Philips Research Laboratories Eindhoven.

© Royal Philips Electronics N.V. 2002

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior written permission of the copyright holder.

#### CIP-DATA LIBRARY TECHNISCHE UNIVERSITEIT EINDHOVEN

Veendrick, Harry

Semiconductor-Technology Exploration: getting the most out of the MOST by Harry Veendrick. - Eindhoven: Technische Universiteit Eindhoven, 2002. Proefschrift. - ISBN 90-74445-56-X

NUGI 832

Trefw.: CMOS circuits / performance / density / signal integrity / speed / power / noise / robustness / semiconductor technology scaling

# Semiconductor-Technology Exploration getting the most out of the MOST

# **Proefschrift**

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr. R.A. van Santen, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op vrijdag 28 juni 2002 om 16.00 uur

door

**Harry Veendrick**

geboren te Hummelo en Keppel

# **Preface**

This thesis describes part of the research that has been done at Philips Research Laboratories in Eindhoven, The Netherlands, during a period of 25 years from 1977 to 2002.

This research was particularly focussed on three different aspects of circuit design: optimising performance (speed, power), maximising density (area) and improving robustness (signal integrity and noise). Although the selected subjects for this thesis share the same motivation: *getting the most out of the MOS transistor (MOST)*, they are very diverse regarding the fundamentally different requirements dictated by the various application areas. The level of detail in the underlying scientific publications is quite different, mainly because of the available publication space, e.g. as a short paper in a conference digest or as a long and detailed article in a journal. Therefore this thesis is divided into two parts.

Part I presents an anthology of the work, in which the most important research topics and results of each subject are discussed at an equal level of detail.

*Part II*, on the contrary, includes the related detailed scientific papers as they were published in the conference digests, magazines or journals.

I leave it to the readers' interest in the specific subject, which level of detail he prefers.

This work could not have been done without the inspiring environments of both the Philips Research Labs and the large number of high-talented colleagues. I want to thank all of them, and particularly those with whom I have closely worked together in different IC design and research projects and whose co-operation has resulted in co-authorship of several of the papers and patents during this 25 years period of time.

I want to acknowledge Philips Research management for allowing me a great deal of freedom in selecting relevant research subjects and for the opportunity to publish them all. I also like to thank them for supporting this work.

Finally, I want to thank my family for their understanding and allowing me to spend again many private hours on professionally related activities, such as the writing of this thesis.

Eindhoven, June 2002 Harry Veendrick

# **Contents**

| Preface                  |                                                                                                                                                               |                      |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Introd                   | uction                                                                                                                                                        | 9                    |

| Part I                   | Anthology of selected work                                                                                                                                    |                      |

| 1                        | Design for performance improvement                                                                                                                            | 15                   |

| 1.1<br>1.2               | High-speed circuit design<br>Low-power circuit design                                                                                                         | 15<br>21             |

| 2                        | Design for high density                                                                                                                                       | 31                   |

| 2.1<br>2.2               | High-density CCD video memories<br>High-density gate arrays                                                                                                   | 32<br>38             |

| 3                        | Design for robustness                                                                                                                                         | 45                   |

| 3.1<br>3.2<br>3.3        | Reliable communication between asynchronous systems<br>Wire self-heating in current and future VLSI design<br>Signal integrity in deep-submicron CMOS designs | 46<br>52<br>60       |

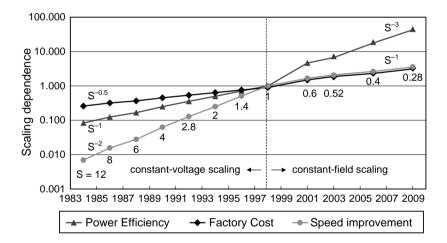

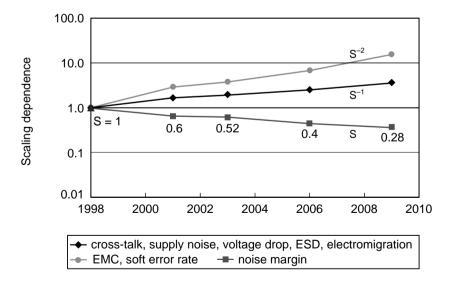

| 4                        | Effects of scaling on MOS IC design and consequences for performance and robustness                                                                           | 75                   |

| 4.1<br>4.2<br>4.3<br>4.4 | Transistor scaling effects Interconnection scaling effects Scaling consequences for overall IC design Potential future design challenges                      | 77<br>78<br>82<br>86 |

| Refere                   | nces                                                                                                                                                          | 91                   |

## Contents

# Part II Detailed scientific work

| 1.1 | A An nMOS Dual-Mode Digital Low-Pass Filter for Colour TV                                                    | 95         |

|-----|--------------------------------------------------------------------------------------------------------------|------------|

|     | <b>B</b> A 40MHz Multi-applicable Digital Signal Processing Chip                                             | 105        |

|     | C A 1.5GIPS video signal processor (VSP)                                                                     | 117        |

| 1.2 | Short-Circuit Dissipation of Static CMOS Circuitry and Its Impact on the Design of Buffer Circuits           | 127        |

| 2.1 | <ul> <li>A 40MHz 308Kb Charge Coupled Device Video Memory</li> <li>B An 835Kb Video Serial Memory</li> </ul> | 145<br>151 |

| 2.2 | An Efficient and Flexible Architecture for High-Density Gate Arrays                                          | 157        |

| 3.1 | The Behaviour of Flipflops Used as Synchronisers and Prediction of Their Failure Rate                        | 171        |

| Cor | nclusions                                                                                                    | 191        |

| Sun | nmary                                                                                                        | 193        |

| San | nenvatting                                                                                                   | 195        |

| Pub | olications of the author                                                                                     | 199        |

| Abo | out the author                                                                                               | 201        |

# Introduction

## **Background and motivation**

The complexity of a VLSI chip has increased from just a few components in the early sixties, to several tens of millions of devices today. It was Moore, already in 1964, who predicted this enormous increase. There are several factors that drove this complexity to the level that has been reached today. First of all, the rapid scaling of the minimum feature sizes allowed us to almost double the number of devices on the same silicon area every new technology generation. Particularly in the first three decades, also the speed of the circuits doubled. As a result, we could have about four times more functionality (or computing power) on the same die area, every 18 to 24 months. However, the complexity of an IC not only depends on what is offered by the technology. A large part of it is also dominated by the requirements of the application area for which they are designed. Important parameters in this respect are:

- *1* functionality/features (density)

- 2- performance (speed and power)

- *3* product volume (density)

- 4- system size (density)

- 5- time-to-market (turn-around time)

- 6- robustness (signal integrity and reliability)

The order of priority in these parameters depends on the application area.

In personal computers, for example, speed is the most important requirement because it determines how fast they can run the complex software programs. A state-of-the-art PC system is built around very high-speed microprocessors, such as the Pentium 4 (Intel), the PowerPC (IBM) or the Thunderbird (AMD) processor.

Consumer electronic applications like audio and video, however, are less driven by speed and more by an increased functionality (features: stereo sound, Dolby surround, teletext, noise reduction, 100Hz, wide and dual screen, picture-in-picture, and MPEG applications such as set-top boxes, DVD, etc.

In portable electronics, both the advances in semiconductor technology and design have been used to reduce the physical sizes and simultaneously increase the system features while keeping the power budget constant. Mobile phones show the strongest improvements in this category of electronic products. They may include lots of different features: calculator, radio, games, MP-3 player, remote control, GPS, Internet access, email, digital camera, etc.

Because of the high innovation rate, the lifetime of a new generation of most of these products is only six to twelve months. Time-to-market has become one of the most critical requirements for many of today's products.

Finally, the increase in complexity of current ICs has led to a rapid increase of signal activity on a chip: more signals switch at the same time and at a higher rate. Moreover, they propagate at smaller mutual distances. The resulting physical effects, such as supply noise, voltage drop, cross-talk and electromigration have a negative influence on circuit behaviour and require special design solutions. The continuous drive to improve the performance of integrated circuits, while reducing the physical dimensions of both the transistors and the interconnect, causes an increased manifestation of these so-called deep-sub-micron effects. This will put a burden on maintaining circuit performance and robustness and will have severe consequences for the design of complex VLSI chips.

This work is the result of this continuous drive for more speed, less power and/or an increased density, to get the most out of the MOST (MOS transistor). At the same time it is tried to keep the robustness of circuit operation at a sufficiently high level.

Although the selected subjects for this thesis share the same motivation, they are very diverse regarding the fundamentally different requirements dictated by the various application areas.

Several research topics are more or less dated, however, the basic solutions or implementations are still valid and used today and the results have been placed in a today's perspective.

# Outline of the thesis

This thesis describes the research that has been done regarding three important aspects of IC design: performance (speed, power), density (area) and robustness (signal integrity and noise). Although the research covered different levels of IC design, the focus here will be particularly on circuits and circuit design techniques. Also examples of ICs will be given in which the particular techniques have been applied. Most of the underlying work has been published, e.g. as a short paper in a conference digest or as a long and detailed article in a journal. The level of detail of these publications is quite different. Therefore this thesis is divided into two parts.

Part I highlights the main research topics and results with an equal level of detail. In fact, it presents an anthology of the work. The different subjects are presented in an order, which almost reflects the order in which the research was performed.

Part II contains the detailed papers as they were published in the scientific magazines and conference digests. The order in which these publications are presented here, is synchronised with Part I.

Therefore, the outline is as follows:

### Part I contains four chapters.

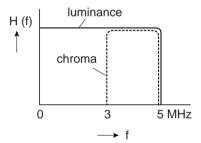

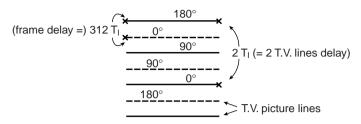

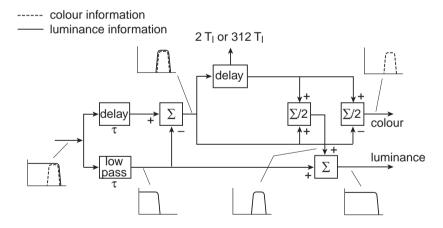

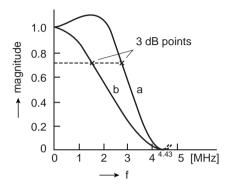

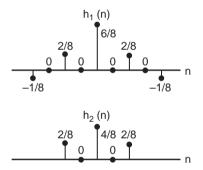

Chapter 1 describes the work that has been done with respect to performance optimisation. The first circuits presented here, were designed in nMOS technology and used in digital video applications. A special circuit technique was developed to achieve high-speed operation in a digital chrominance filter and is also used in the design of a digital potentiometer. The second topic in this chapter discusses the design of a programmable high-speed video signal processor. In this design, various circuit techniques are applied to accommodate the high-speed requirements and support the signal integrity. The discussions, however, are mainly focussed on the high-bandwidth switch matrix that enables the high-speed communication between the different video processing elements on that chip.

Power consumption is an important parameter that also reflects the performance of a chip. There are several different factors that contribute to the total power consumption of a CMOS chip. One of them is called short-circuit dissipation. The third topic discusses the cause of this short-circuit power dissipation. It also presents an expression to estimate this power and ways how to limit it.

Chapter 2 is focussed on the optimisation of the density of different types of integrated circuits. Due to coding of the large number of pixels in a TV screen, the data storage of one complete TV picture requires relatively large memories. The first topic in this chapter is the design of two digital video memories, implemented in charge-coupled device (CCD) MOS technologies. The operation of a CCD perfectly matches the serial character of video samples transmission.

Since the product life cycle for many application areas is reduced, time-to-market has become an important aspect for a lot of different ASIC products. Fast turn-around time in the waferfab is one way to support a short time-to-market. This can be achieved by using prefab wafers (off-the-shelf available), which already contain the processed transistors. A few remaining contact and metal interconnect masks can then 'simply' complete its functionality. In this way the turn-around time in the waferfab is reduced from an average 10 to 13 weeks for a custom IC, to about two to four weeks for these so-called gate-arrays. Because these gate-arrays are less customised, they show a lower gate density than other IC implementations like standard-cell or bit-slice layout. Therefore, as a second topic in this chapter, an efficient and flexible gate-array architecture is described, which supports a relatively high-density realisation of both logic and memory circuits.

Due to the continuous process of technology scaling, the feature sizes of the transistors and their interconnections reduce while their numbers increase. At the same

time the clock frequencies increase. This poses a burden on the robustness of circuit operation: their reliability and signal integrity.

Chapter 3 therefore discusses several of these aspects of IC design. The discussion starts with the design of a synchroniser, which is based on the basic operation of a flipflop. Due to the sampling of asynchronous signals, a flipflop may reach a metastable state, in which its output levels are logically undefined, causing a glitch. The research was focused to optimise the reliability of synchronisers such that the chance of occurrence of a glitch was minimised. This could not be done without a detailed study of the influence of noise on the meta-stable state behaviour.

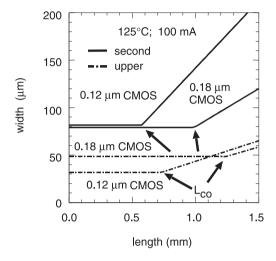

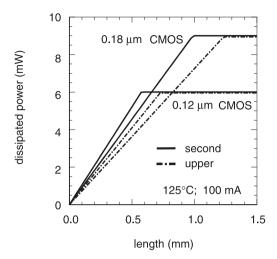

The continuous process of scaling also causes an increase of the supply currents every new technology. As a result, the current density in the on-chip supply lines can easily reach the maximum allowed levels defined by electromigration requirements. These requirements are strongly related with the temperature of these supply lines. The power consumed in these supply lines will increase their temperature. A quantitative discussion on this so-called wire self-heating is presented in the second subject in this chapter.

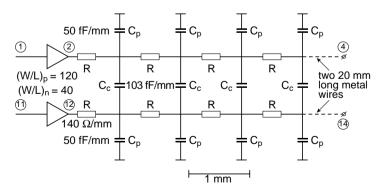

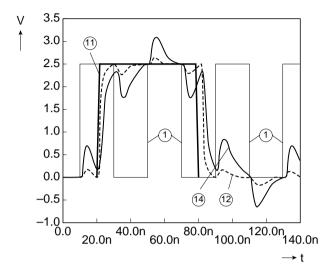

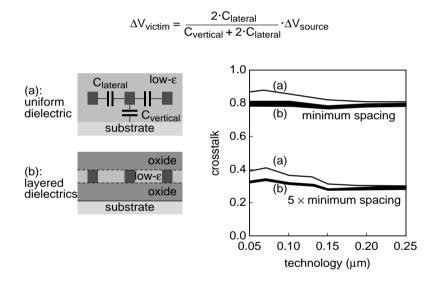

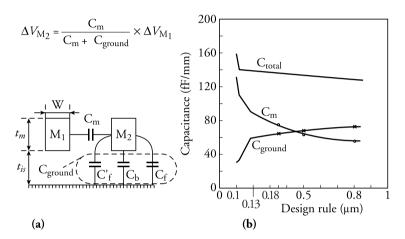

The third topic of this chapter is related to signal integrity. More devices are produced at smaller distances and switch at higher frequencies, causing much more on-chip noise and interference. Particularly the cross-talk between neighbouring signal lines and the noise on the supply lines may have a dramatic impact on the performance and signal integrity of deep-sub-micron ICs. For compensation of the huge peak currents that occur during heavy simultaneous switching and which are the cause of the supply noise, de-coupling capacitors are implemented on-chip. Finally, *chapter 4* discusses the effects and challenges of scaling with respect to the three previous chapters: performance, density and robustness of future ICs.

Part II contains the detailed scientific papers, which are presented in three different chapters. The subjects and numbering of these chapters and their sections correspond with those of Part I.

Part I is directly following by its reference list. The detailed papers in Part II all have their own reference lists.

The overall conclusions have been placed at the end of the thesis, directly after the final detailed paper.

The thesis ends with a list of patents and recent publications of the author.

# Part I

Anthology of selected work

# Chapter 1

# **Design for performance improvement**

The consumer market knows a large variety of different integrated circuits applications. Some of the applications are performance (power, speed) driven, while others are features driven: more functionality. The subjects in this chapter are focussed on performance and particularly on performance improvement. The first topic that will be discussed here is related to circuit design optimisation for high-speed video applications.

High performance does not only mean high speed. It may as well reflect the efficiency of a circuit in terms of power usage. So, low power is an equally important performance indicator as high speed. The second topic is therefore a power related subject that describes how the short-circuit component in the total power consumption can be reduced to negligible values.

# 1.1 High-speed circuit design

#### 1.1.1 Introduction

There are many ways in which the speed of integrated circuits can be improved. This can be done at architecture level, at logic implementation level, at circuit level and at device (technology) level. This section first discusses an example of achieving high speed circuits by the development of a new style of nMOS logic gates, which could approach the speed of CMOS circuits at that time. The second example, the design of a high-bandwidth communication bus, shows that both the architectural and circuit levels are used to achieve high speed.

# 1.1.2 High-speed logic gates: race-compensated MOS logic

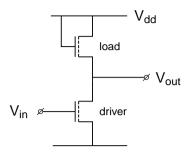

Before the move to CMOS in the early eighties, most digital MOS circuits were made in nMOS technology [Mavor, 1983]. Initially nMOS technology only contained one type of transistor: the enhancement transistor. Fig. 1 shows an (E/E) inverter that is built up with an enhancement (E) driver and an enhancement (E) load transistor (positive threshold voltage ( $V_t > 0$ V).

Fig. 1 Inverter in Enhancement/Enhancement (E/E) nMOS logic

A major disadvantage of this type of E/E logic is that, when the output is rising, the gate-source voltage of the load is reducing with as final result that the output level can not get higher than a voltage level equal to  $V_{dd} - V_t$ , in which  $V_{dd}$  represents the supply voltage. In a 5V technology this threshold voltage loss can be as high as 1.5V, such that the output high level of an E/E logic gate may only reach 3.5V. This reduced high level is received by the connected logic gates, which on their turn become more than a factor of three slower than when they would receive a high level as high as  $V_{dd}$  (so without the threshold voltage loss).

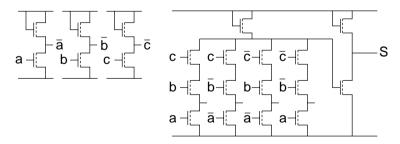

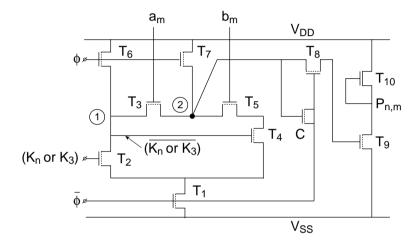

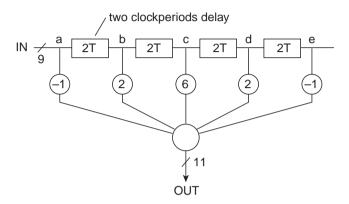

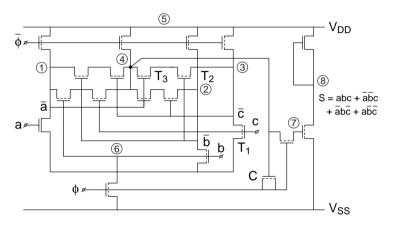

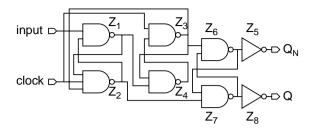

Arithmetic type of circuits, such as adders, multipliers and filters usually use half and full-adder type of cells to perform their functionality. Fig. 2 shows the sum function of an E/E full-adder cell. Including the generation of the inverse inputs, this cell consists of 21 transistors. Normally, when a logic function uses the direct inputs and their inverse ones, it takes two gate delays to perform this function. Using race-compensated MOS logic allows both creating and using the inverse data in one single logic gate. It results in a hardware reduction (smaller chip size) as well as in a relatively large increase in circuit speed. Fig. 3 shows an alternative realisation for this cell. This race-compensated MOS logic cell contains only 18 transistors and is much faster (about a factor of two).

Fig. 2 Full adder Sum function in E/E nMOS logic

Fig. 3 The same Sum function in race-compensated MOS logic

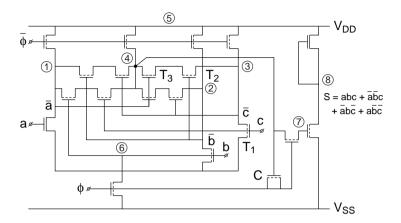

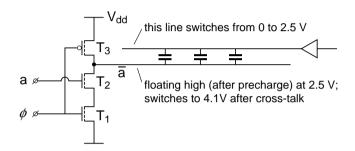

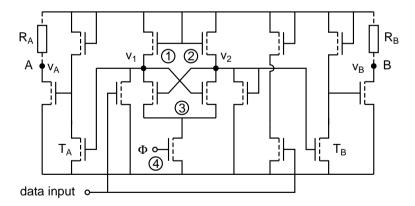

The operation of this cell is as follows. When the clock  $\phi$  is low, nodes 1, 2, 3 and 4 are pre-charged high. During  $\phi$ , the data at the input nodes a, b and c are sampled and at the same moment the inverse data  $a_{not}$ ,  $b_{not}$  and  $c_{not}$  are generated and used to control other gates. Under certain input conditions this introduces a race, by causing a voltage drop at node 4, right after a rising edge of clock  $\phi$ , at a moment that it is not allowed. For instance, when the inputs a and c are at high level and input b is low, then transistors  $T_1$  and  $T_2$  must conduct, while  $T_3$  should not. However, when the sample clock  $\phi$  is switched on, it will take some time before node  $a_{not}$  has been discharged, meaning that transistor  $T_3$  is conducting during a very short period of time, which causes a temporary conducting path from node 4 through transistors  $T_3$ ,  $T_2$  and  $T_1$  to ground. This results in a voltage drop at node 4. The bootstrap capacitor C is charged during the pre-charge period (clock  $\phi$  is low) and right after the clock switches to high, its charge is used to compensate any voltage drop at node 4 caused by either charge sharing or by a race.

This circuit design technique has been used in two different video signal processing ICs made in nMOS technology to increase the circuit speed by more than a factor of two: a digital low-pass filter for the separation of the luminance and chrominance (see Part II, Chapter 1.1A) and a digital potentiometer for high-speed video applications (see Part II, Chapter 1.1B and US patent US04513388).

#### **Conclusions**

In nMOS circuits that consist of enhancement transistors only, the output high level of a logic gate suffers from a threshold-voltage loss, causing a reduced high level at the inputs of the connected gates. These gates therefore show a relatively slow switching operation. A new dynamic logic-gate concept has been introduced, which allows generating both the logic function and its inverting inputs in one

single gate. Without any further design measure, this would lead to races causing additional voltage drops at the gate's output. By using a bootstrap capacitor, charge can be pumped from the clock node to the logic gates' output nodes to compensate for both types of voltage drop. The circuits that were built with this type of logic show a 15% higher density and a two times improvement in speed.

## In today's perspective

Since we have CMOS technologies today, it is not needed to use charge-pumping (bootstrap) techniques to speed up the basic logic circuits. The subject described here shows that there are on-chip electronic solutions to improve the performance even more then what is intrinsically available from a technology. Today, bootstrap concepts are still used, e.g. in such non-volatile memories as flashes and E(E)PROMs, to generate the higher voltages needed during the programming and/ or erasure mode.

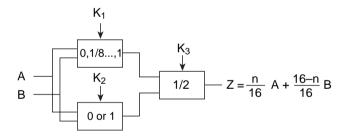

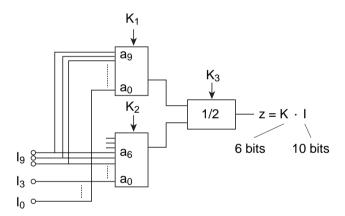

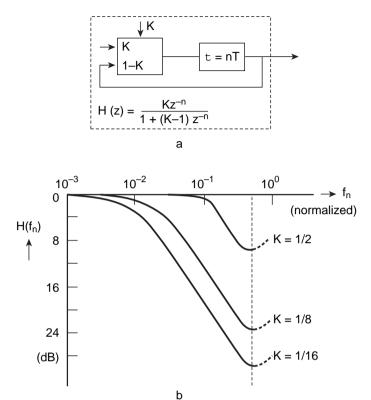

## 1.1.3 A switch-matrix for high-bandwidth communication

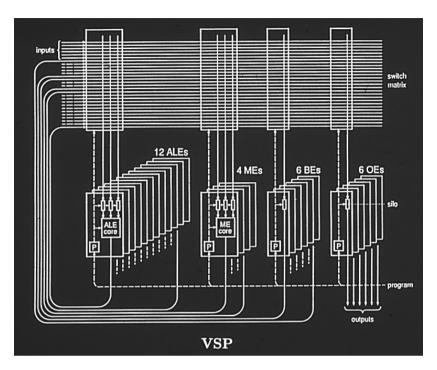

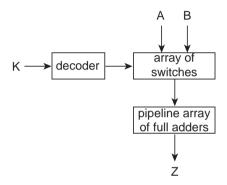

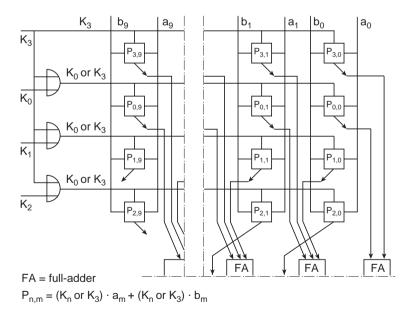

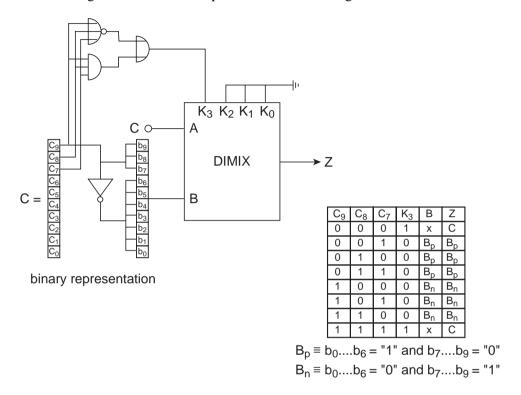

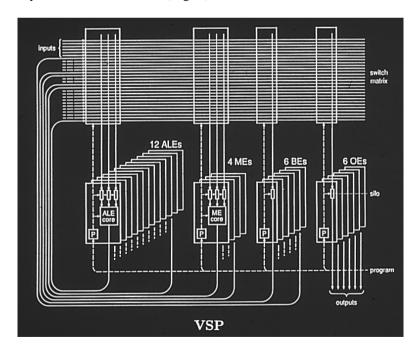

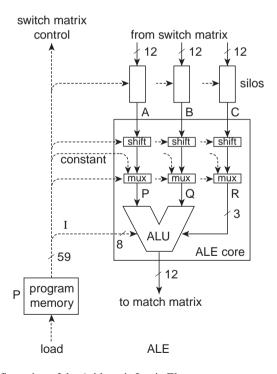

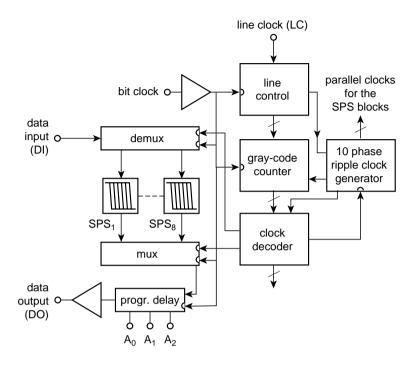

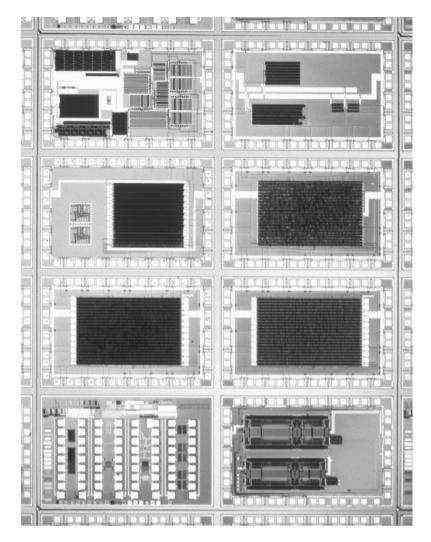

One of the most important characteristics of real-time video signal processing is its relatively high sample rate. This may range from 3MHz for a single chrominance signal in a conventional TV receiver, up to 108MHz or higher, for advanced high-definition TV signals. Accordingly, the required signal-processing power and communication bandwidth can be very high [Roizen, 1986; Chen, 1992]. For this purpose, a programmable general-purpose video signal processor (VSP) has been developed. The amount of parallelism, combined with the speed of operation resulted in a total processing power of 1.5GIPS (Giga Instructions per Second). Fig. 4 shows the modular architecture of this VSP.

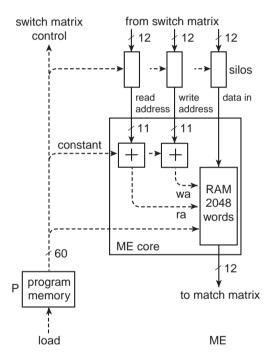

The chip contains 28 pipelined processing elements (PE): twelve Arithmetic Logic Elements (ALE), four Memory Elements (ME), six Buffer Elements (BE) and six Output Elements (OE). Every input sample of a PE can temporarily be stored in a small buffer memory (silo). The number of each category of PEs is chosen to cover most of the intended real-time video processing algorithms. Such an algorithm can be regarded as a combination of several operations (add, subtract, multiply, store, read, etc.). According to Fig. 4, there are 28 PEs, with a total of 60 PE inputs. Each operation must be assigned to one of the PEs in the proper time slot, such that these PEs are optimally used. As a result of this requirement, each PE input must be able to select either an output of any of the PEs, or of any of the six external inputs. In fact, the efficiency of such an architecture is determined by the flexibility and throughput of its communication structure. Therefore, a switch matrix is used to perform the complete communication interface between the blocks on the chip as well as to the chip inputs and outputs.

**Fig. 4** Architecture of the VSP chip

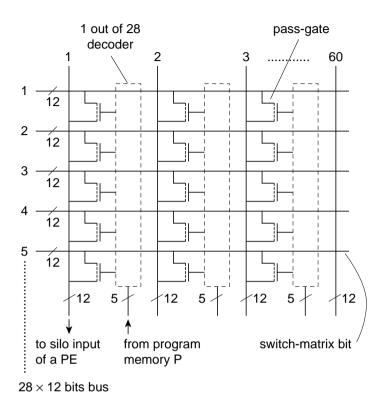

Fig. 5 shows the schematic of the switch-matrix.

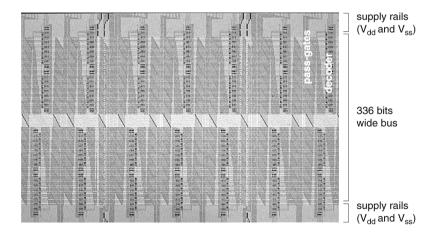

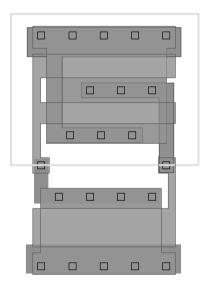

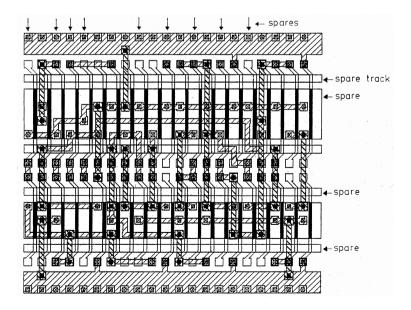

Since the word width is twelve bits, the switch matrix consists of a  $28 \times 12$  bits = 336 bits wide bus, which crosses the complete chip, from left to right (see Part II, Chapter 1.1C, Fig. 6). The biggest challenge in the design of this switch-matrix was its complexity (28 inputs and 60 outputs, each of 12 bits) and its minimum required switching speed of 54MHz. Every clock cycle it must be able to connect each PE input to any of the 28 12-bits busses of the switch-matrix. This also allows one input to be connected to multiple outputs. The connections are done by pass-gates, which are located on every crossing of a PE input line with a switchmatrix bit. These pass-gates are selected by a decoder, which is located in the switch-matrix, below the metal busses. Since each PE input requires its own decoder, 60 of these decoders had to fit in this switch-matrix. Each decoder is controlled by the program memory P of the related PE (Fig. 4). So, within one clockcycle it is required to read out the program memory P, decode its data to select the switches in the switch-matrix, and then store the selected data into the PEs input buffers (silo in Fig. 4). The combination of the necessary speed and density required a full-custom design of this switch-matrix. Fig. 6 shows the layout of a part of the switch-matrix.

Fig. 5 Schematic diagram of the switch-matrix

Fig. 6 Layout of a part of the switch-matrix

In the worst-case switching situation, all switch-matrix busses could switch simultaneously in the same direction. This would have caused huge peak currents and related supply noise across the supply network. For this reason the switch-matrix has been encapsulated within a large supply rail network, which, in turn, is connected to many supply pins in the chip periphery. Next to this, 20 nF of decoupling capacitance has been implemented on the chip to reduce the supply noise. This capacitance is charged during steady-state and its charge is used during peak activity.

By means of extensive area optimisation, this custom-designed switch-matrix is very compact and offers a flexible and programmable high-speed communication structure between the PEs. As discussed before, this switch-matrix has been used in the design of a high-speed video-signal processor (Part II, Chapter 1.1C).

#### Conclusions

General-purpose video-signal processors require many different processing elements operating at a relatively high frequency. In many cases the intermediate or final results of these operations need to be stored as well. This requires a very flexible and high-speed interface. The developed switch-matrix with 28 inputs and 60 outputs, each of 12 bits, offers a minimum bandwidth of 18 Gbit/s. It allowed the developed video signal processor to run even at 100MHz on some dies.

## In today's perspective

Because this switch-matrix architecture allows each input of a processing element to be connected to any of the others' or its own output, it is still used today as one of the most flexible communication interfaces in modern complex signal processors.

# 1.2 Low-power circuit design

#### 1.2.1 Introduction

As long as the existence of the integrated circuit, its power consumption, limitation and reduction have been a major subject for research. During the seventies and early eighties, the most dominant MOS technology was the enhancement/depletion nMOS technology [Veendrick, 2000]. Through the eighties, however, due to the increase in both IC complexity and speed (clock frequency), the power consumption of an average nMOS ASIC chip reached 1W, which is the maximum power consumption of a cheap plastic package. This was one of the

main driving forces for moving from nMOS to CMOS technologies in the first place. Now, after about two decades, the average CMOS ASIC chip has reached this 1W power limitation again, however with the difference that we don't have an alternative technology this time. Next to this average ASIC category of ICs, also the two other categories, namely the ICs in hand-held devices (battery-operated products like cordless and cellular phones, PDAs, palmtops, etc.) and those in high-speed microprocessors (Pentium (Intel), PowerPC (IBM), Thunderbird (AMD)) face a strong pressure on power limitation/reduction. Therefore, power limitation (reduction) has become one of the most important requirements for IC design in this new millennium.

To describe the work that has been done with respect to the power reduction of CMOS circuits, it is good to present an overview of the different sources that contribute to the total power consumption of a CMOS circuit.

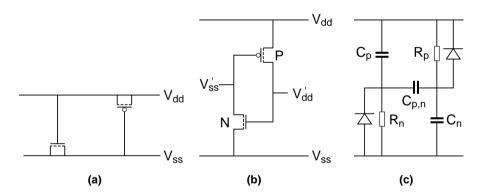

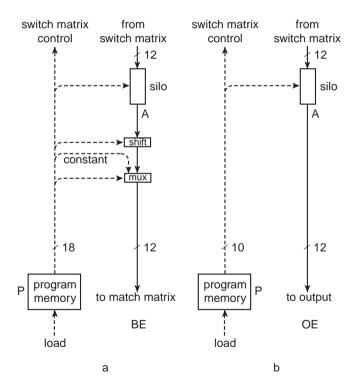

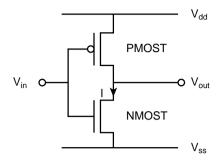

Consider in this respect the two CMOS inverters presented in Fig. 7.

Fig. 7 (a) Basic CMOS inverter;

(b) Pseudo nMOS inverter

During the operation of CMOS circuits their total power consumption consists of four different components:

$$P_{total} = P_{dyn} + P_{stat} + P_{short} + P_{leak} \tag{1}$$

$P_{dyn}$  is the power consumed during charging and discharging (switching) of the output (see Fig. 7):

$$P_{dyn} = C \cdot V^2 \cdot a \cdot f \tag{2}$$

where C is the total capacitance at the output node (load + parasitic capacitance), V is the voltage swing, f is the clock frequency. The activity a factor of a logic gate represents the number of its switching transients per clock period, which can vary

from below 0.1 (low activity) to 1 (high activity). Sometimes a gate may even switch more than once in a clock period, due to the occurrence of glitches, causing the activity factor to be higher than 1.

$P_{stat}$  represents the static dissipation, which is the power consumed as a result of static current. This current can only flow when a circuit, in steady-state, has a DC current path from supply to ground, when its output is low. Although the circuit in Fig. 7b is a CMOS circuit, it is called *pseudo nMOS* because it operates similar to an nMOS gate (see Fig. 1). In such a gate the logic function is implemented in the nMOS transistors only, while all pMOS transistors are replaced by only one pMOST with its gate connected to the  $V_{ss}$ . The static power of such a logic gate is expressed as:

$$P_{stat} = I_{average} \cdot V \tag{3}$$

where  $I_{average}$  represents the average DC current. Due to this DC current, pseudo nMOS logic gates consume 10 to 20 times as much as their *full CMOS* counterparts. Particularly in low-power applications, this type of logic is not used, thereby eliminating the static power component.

$P_{leak}$  is the power dissipated as a result of substrate leakage, sub-threshold leakage and gate leakage currents. In current technologies the sub-threshold leakage is by far the largest contribution to this power component. Due to scaling of the technology, also the supply voltage is reduced. Because of the speed requirement of a new technology, also the threshold voltage is reduced. However, a reduction of 100 mV in the threshold voltage  $V_t$  leads to an increase of the leakage current (at  $V_{gs} = 0$ V) of a factor between 10 to 16 [Veendrick, 2000]. So, on the one hand, the high-speed requirement demands a low  $V_t$  while, on the other hand, the low-power requirement demands a high  $V_t$ . Because of these contradictory requirements, most advanced CMOS technologies offer both a low and high  $V_t$ .

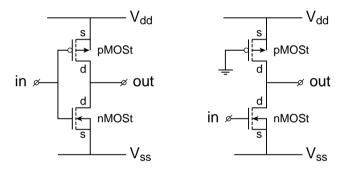

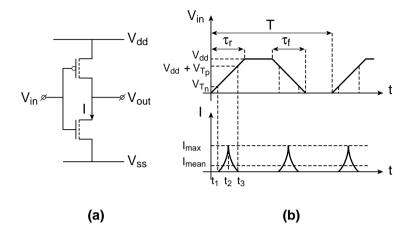

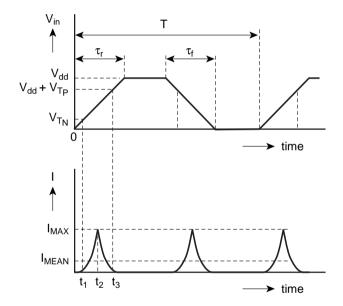

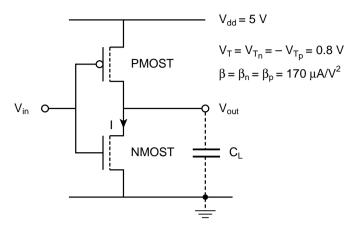

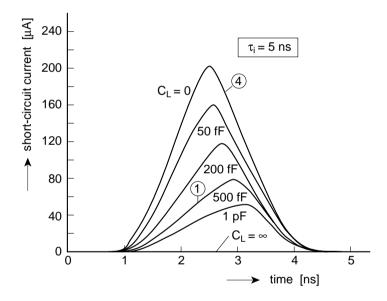

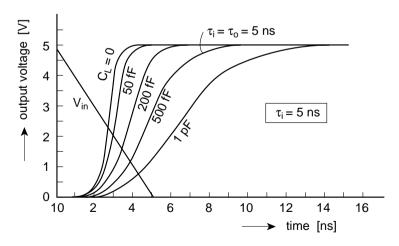

$P_{short}$  is the power consumption in an inverter (or in a logic gate), whenever transients on the inputs cause a temporary current to flow directly from supply to ground. Let us assume that the input of the CMOS inverter without a load (Fig. 8a) is at low level and its output is at high level. In this case the pMOS transistor is on, while the nMOST is off.

Next, let us assume that the input switches slowly to high level. When its level passes the  $V_{t_n}$  of the nMOST, this transistor switches on, while the pMOST is still on. This causes a short-circuit current from supply to ground. This current flows as long as the input voltage is higher than  $V_{t_n}$  above  $V_{ss}$  and more than  $|V_{t_p}|$  below  $V_{dd}$ . It creates a temporary short between  $V_{dd}$  and  $V_{ss}$  and is responsible for the short-circuit power component.

Fig. 8 (a) CMOS inverter without a load (b) Current behaviour of an inverter without load

The following paragraph focuses on circuit design techniques to reduce this short-circuit component.

## 1.2.2 Design concepts to reduce the short-circuit power dissipation

Fig. 8b shows the input voltage waveform, when it switches from low to high level and back, and the corresponding short-circuit current.

The short-circuit dissipation can then be described as the product of the average current  $I_{mean}$  and the voltage V:

$$P_{short} = I_{mean} \cdot V \tag{4}$$

For simplicity we assume that the inverter has a symmetrical behaviour, which means that:

$$\beta_n = \beta_p = \beta \quad \text{and} \quad V_{t_n} = -V_{t_p} = V_t \tag{5}$$

where  $\beta_n$  and  $\beta_p$  are the gain factors of the nMOST and pMOST, respectively. We also assume that the rise and fall times of the input signal,  $\tau_r$  and  $\tau_f$ , respectively, are equal:

$$\tau_r = \tau_f = \tau \tag{6}$$

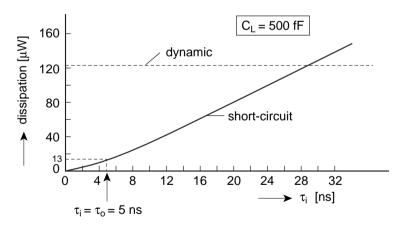

In Part II, Chapter 1.2 it is derived that for this inverter the short-circuit dissipation equals

$$P_{short} = \frac{\beta}{12} \cdot (V_{dd} - 2V_t)^3 \cdot \frac{\tau}{T} \tag{7}$$

where T represents a full period of the input signal.

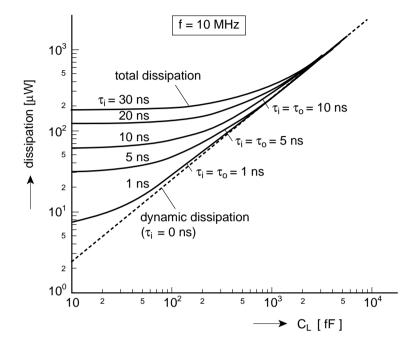

From this expression we can see that the short-circuit dissipation not only depends on the switching frequency (f = 1/T) and rise and fall times  $(\tau)$  of the input signal, but also on the technology  $(V_t \text{ and } \beta)$  and on the design of the inverter  $(\beta)$ .

From expression (7) it is clear that the short-circuit power consumption is largest in circuits that contain transistors with large  $\beta$ s. There is a linear relation between  $\beta$  and the width W and length L of the transistor channel:

$$\beta = \beta_{\square} \cdot \frac{W}{L} \tag{8}$$

where  $\beta_{\square}$  is the gain factor ( $\beta$ ) of a square transistor (with W = L).

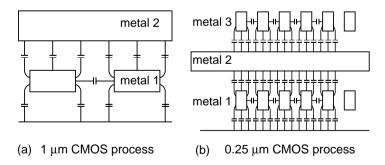

In other words, circuits that contain large W/L ratios will generate the largest short-circuit dissipation. In digital CMOS ICs, the on-chip driver (buffer) circuits, such as bus drivers, clock buffers and output buffers may contain transistors that have W/L ratios between 20 and 500 to drive large load capacitances. On the other hand, the W/L ratios used in a typical logic gate usually varies from 1 to 10.

## CMOS buffer design

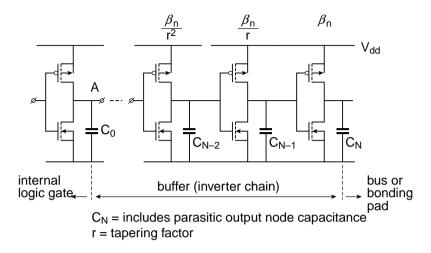

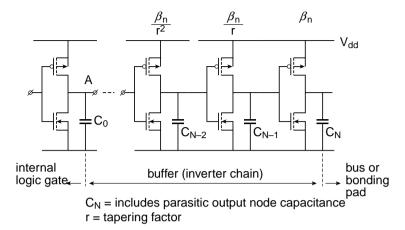

Suppose the signal on a bus line (or bonding pad) with capacitance  $C_N$  must follow a signal at the output node A of a logic gate, which is capable of (dis)charging a capacitance  $C_0$  in  $\tau$  ns. An inverter chain such as illustrated in Fig. 9 can be used as a buffer circuit between node A and the bus line (or bonding pad).

From formula (7), it is clear that the rise and fall times on each input of the inverters in the above chain should be short. Moreover, it has been shown in Part II, Chapter 1.2 that minimum dissipation can be achieved when the rise and fall times on each of these inputs are equal to the rise and fall times ( $\tau$ ) at the buffer output. The inverter chain must therefore be designed such, that the rise and fall times on the inputs of each of its inverters are also equal to  $\tau$ . According to literature [Mead, 1980], a minimum propagation delay time across the buffer is obtained when the 'tapering factor' r between the  $\beta$ 's of successive inverters is e, the base of natural logarithm. In terms of dissipation and silicon area, however, this tapering factor will not lead to an optimum design. Design for minimum dissipation and silicon area requires a different approach.

Fig. 9 A buffer circuit comprising an inverter chain

#### Example

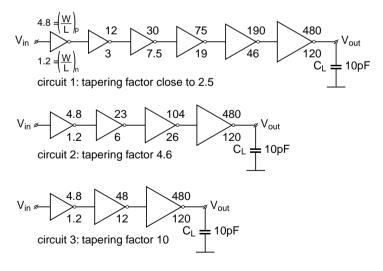

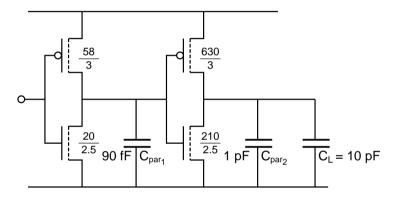

A signal is produced by a logic gate and must be buffered to drive a capacitive load  $C_L = 10 \text{pF}$  with a rise and fall time  $\tau$  equal to 1ns. The channel length of both the pMOS and nMOS transistor is  $0.25 \mu \text{m}$ , while  $\beta_{\Box n} = 240 \mu \text{A/V}^2$  and  $\beta_{\Box p} = 60 \mu \text{A/V}^2$ . To determine the right tapering factor for minimum area and power consumption, three different inverter chains are examined (Fig. 10).

Fig. 10 Inverter chains with different tapering factors, all driving the same load with almost equal rise times

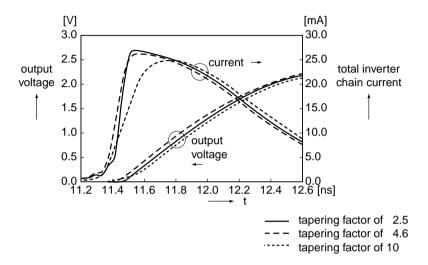

The characteristics of these inverter chains can be expressed with the variables: power dissipation, propagation delay, maximum current change dI/dt and area. The importance of a low value for dI/dt will be explained in section 4.2. Fig. 11 shows the simulation results of these inverter chains.

**Fig. 11** Simulation results for inverter chains of Fig. 10

The input signal,  $V_{\rm in}$ , to the three different inverter chains, is connected to identical first inverters with the same effective W/L ratio which mimic an equivalent logic. The diagram shows the total inverter chain currents and the output signals. Detailed overall results for these circuits are given in Table 1.

|                                       |                  |                    | -                | D         |

|---------------------------------------|------------------|--------------------|------------------|-----------|

| Circuit number                        | 1                | 2                  | 3                | Dimension |

| Tapering factor                       | 2.5              | 4.6                | 10               |           |

| Number of inverters                   | 6                | 4                  | 3                |           |

| Total power (relative)                | 1.14             | 1.11               | 1                |           |

| Total area (relative)                 | 1.55             | 1.21               | 1                |           |

| Max d <i>I</i> /d <i>t</i> (relative) | 4.6              | 3                  | 1                |           |

| Max d <i>I</i> /d <i>t</i> (absolute) | $2.8 \cdot 10^8$ | $1.8 \cdot 10^{8}$ | $0.6 \cdot 10^8$ | [A/s]     |

| Propagation delay (relative)          | 0.98             | 0.94               | 1                |           |

| Propagation delay (absolute)          | 0.92             | 0.88               | 0.94             | [ns]      |

**Table 1** Comparison of inverter chain buffers with different tapering factors

The tapering factor e (close to 2.5), which is derived in literature [Mead, 1980] to achieve minimum propagation delay, scores very badly with respect to the maxi-

mum dI/dt and to the area. Since the noise margins of a CMOS IC reduce with every new technology, due to the voltage reduction, the dI/dt should be as low as possible, but without deteriorating the performance too much. The table shows that the inverter chain with a tapering factor of 10, which was derived to achieve minimum power, also yields optimum overall performance (power, delay, area and noise). Research from previous CMOS technology generations (2.5 $\mu$ m CMOS and 1 $\mu$ m CMOS) had also resulted in an optimum tapering factor of around 10 (Part II, Chapter 1.2). Generally we can conclude that a tapering factor close to 10 will still result in optimum buffer design.

#### 1.2.3 Conclusions

An important contribution to the total power consumption in CMOS circuits is the short-circuit power, which occurs during signal transients on the input(s) of a logic gate. An expression for this short-circuit power is derived and it shows that it could be a relatively large part of the total power, if it is not given proper attention during the design phase. Particularly in circuits that have large transistors, such as in clock drivers, bus drivers and output buffers, this power consumption could be large. These circuits usually consist of a chain of inverters, of which the sizes of the successive inverter transistors are tapered. It turns out that a tapering factor equal to about 10 shows the best circuit characteristics in terms of power consumption, area and noise.

## In today's perspective

Over several generations of CMOS technologies, the transistor channel length has reduced while keeping the supply voltage constant. The resulting high electrical field across the channel causes so-called velocity saturation of the charge carriers in the channel. The transistor saturation current then changes from a quadratic relation with the voltage to a more linear one. This will also have its impact on expression (7) for the short-circuit power consumption, which will now change to:

$$P_{short} = \frac{\beta}{12} \cdot (V_{dd} - 2V_t)^j \cdot \frac{\tau}{T}$$

with 2 < j < 3.

However, the reduced saturation current would increase the rise and fall time au to:

$$\tau = \frac{C \cdot V}{I} = \frac{C \cdot V_{dd}}{\frac{\beta}{2} \cdot (V_{gs} - V_{t})^{j-1}}$$

To maintain the same rise and fall time  $\tau$ , the  $\beta$  of the transistors, and so their W/L-ratios have to be increased. As a result of these considerations, relatively, the short-circuit contribution to the total power consumption will hardly change. Regarding the optimum tapering factor (see Table 1) it can be stated that this hardly changes with technology scaling, since almost all capacitances scale with about the same factor. In a  $0.12\mu m$  CMOS, a tapering factor of 10 still shows the best numbers in terms of area, max dI/dt and power consumption (from simulations).

# Chapter 2

# **Design for high density**

The smaller the chip area, the more dies will fit on a wafer. Moreover, the production yield of integrated circuits is exponentially proportional with the chip area. So, the size of a chip has a great influence on the eventual selling price. Since the price erosion of consumer products is relatively high compared to other goods, the main focus in the design of a consumer IC is on its chip area. This generally holds for video signal processing functions, but even more particular for video memories, as they require relatively large capacities for storing complete video frames. The charge-coupled device (CCD) concept was known to offer two to three times higher bit density compared to dynamic random-access memories (DRAMs) in the same technology node. The first topic to be discussed in this chapter describes two generations of low-cost video memories, implemented in different CCD-MOS technologies. With only one or two additional masks, these technologies offered the combination of high-density memory with specific video processing on the same chip. Because most of the vendors of high-density memories focused their technologies on the DRAM concept, the learning curve of these devices eventually surpassed that of the CCD memories.

Introducing new features into a TV or VCR, requires a fast turn-around time and short-time-to-market of the different ICs from which these features are built. In many cases new-feature TV sets are put onto the market as prototypes, to allow fast market penetration and market survey. In many cases such prototype systems are implemented as gate arrays, which are pre-fabricated unfinished ICs, containing large arrays of transistors or logic gates. These gate arrays are available off the shelf in different categories and only need one or a few interconnect and contact layers to complete their functionality. This allows turn-around times of just a couple of weeks (2-4), compared to the relatively long throughput times of a complete CMOS process (10-15 weeks). Since the volumes for prototyping were usually not so large (a couple of thousands per design), the cost of silicon was only a fraction of the design, test and packaging costs. It was thus not so much of a problem that these gate arrays did not offer the density that could be achieved by implementing the same function with a standard-cells. However, the volumes for prototyping steadily increased from a couple of thousands to several ten thousands per design, thereby relatively increasing the silicon costs per chip. This was a drive for research into the density improvement of gate arrays. The second part of this chapter discusses, as an outcome of this research, an efficient and flexible architecture for high-density gate arrays.

# 2.1 High-density CCD video memories

#### 2.1.1 Introduction

The introduction of digital memories in TV and VCR equipment has made it possible to enhance TV pictures with additional features, such as 100Hz, noise reduction, still picture, fast teletext page access, etc. [Berkhoff, 1983; Fisher, 1982]. Storage of complete TV pictures requires relatively large memories due to the number of pixels from which the TV field is built. By the time this research was executed, the charge coupled device (CCD) concept offered two to three times higher bit-density than DRAMs in comparable technologies. The next sections discuss the implementation of two CCD video memories: a 308Kb and an 835Kb respectively. The contributions made to this subject were mainly pointed at the integration level, rather than at the CCD device level.

## 2.1.2 A 308Kb CCD video memory

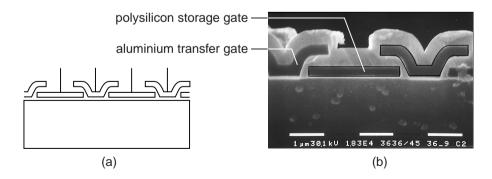

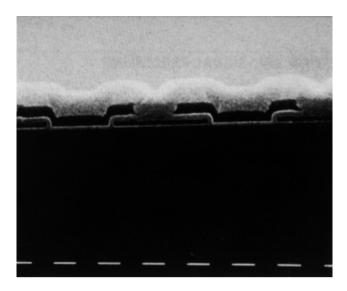

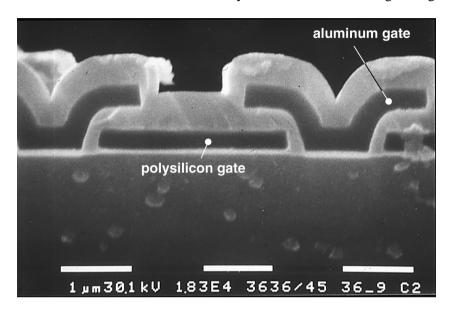

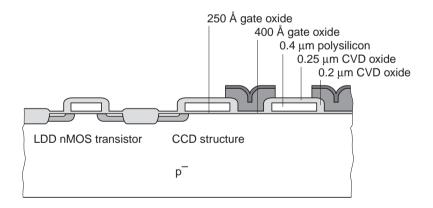

The basic CCD cell used in this memory is built from two transistors, one with an aluminium transfer gate and one with a polysilicon storage gate. Fig. 12 shows the CCD cell concept.

Both transistors, which are controlled by the same clock signal, are fabricated with a different gate oxide thickness, resulting in different threshold voltages. Data transfer in a CCD memory can be achieved by switching neighbouring memory cells by different clock signals. A short description of the basic data (charge) transfer will be given first.

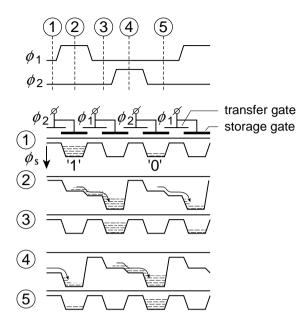

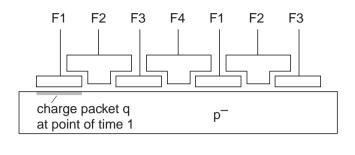

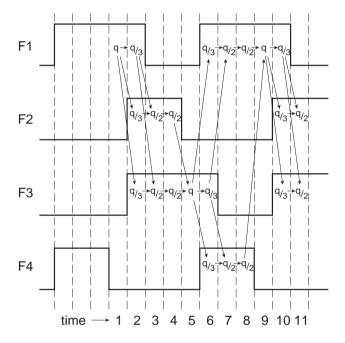

In many cases a 2-phase clock is used for this shift operation. Fig. 13 shows the basic shift operation of a 2-phase CCD.

Fig. 12 CCD cell concept (a) and technology cross section of the cell (b)

Fig. 13 The shift operation in a basic 2-phase CCD

According to the figure, this shift operation is similar to a repetitive operation of filling buckets with water and then empty them again. The *depth of the buckets*, in this CCD, is determined by the difference between the threshold voltages of the storage and transfer gate.

Suppose the first and third storage gates contain a full and an empty charge packet, representing the logic levels '1' and '0', respectively. The charge packet stored in the first cell is then full of electrons. This is represented by a full charge packet under its storage gate. The charge packet stored in the third cell, however, is almost empty, i.e. it is practically devoid of electrons. At time point 1, both  $\phi_1$  and  $\phi_2$  are 'low' and the storage gates are separated from each other. At time point 2,  $\phi_1$  has switched from a low to a high level and the charge is transferred from the  $\phi_2$ storage gates to the  $\phi_1$  storage gates. At time point 3, both  $\phi_1$  and  $\phi_2$  are 'low' again and the charge is now stored under the next  $\phi_1$  storage gates. The description of the shift behaviour at time points 4 and 5 is obtained by replacing  $\phi_1$  by  $\phi_2$  in the above descriptions for time points 1 and 2 respectively. A comparison of the time points 1 and 5 shows that the charge has been transferred from the first to the third bucket in one complete clock period. In fact, the charge is transferred from one CCD 'cell' to another in one single clock period. So, each CCD memory cell, here, clearly requires two storage elements, which are analogous to the master and slave latches in a *D-type flipflop*.

The potential of a CCD cell to collect charges also holds for the leakage charge from thermal generation of minorities [Slotboom, 1981]. This charge is able to slowly fill the buckets of a CCD. The CCD that is described here is a surface-channel CCD, meaning that the charge transfer occurs right at the silicon surface under the gates. Unfortunately, the surface is somewhat inhomogeneous and plagued by surface states able to trap electrons. Usually the time that charge is being trapped by such surface states is relatively longer than one shift period of a packet transfer. So, the charge, which is 'stolen' from one packet, can be released some time later, thereby joining another packet. If the charge is conducted through a very long chain of CCD cells, the full buckets loose charge, while the empty packets will get filled. The amount, to which packet charge is lost, is called charge-transfer efficiency. The leakage and the transfer efficiency are two important effects in a CCD, which influence the architecture and design of a CCD memory.

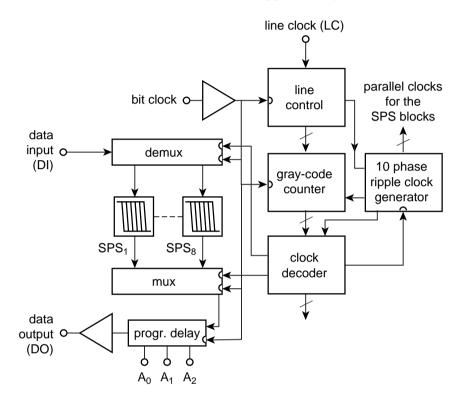

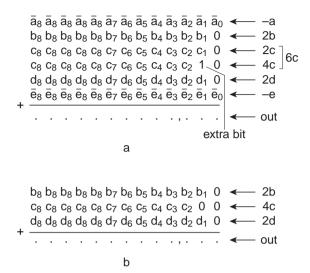

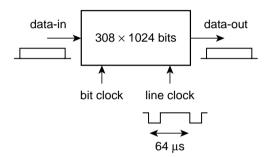

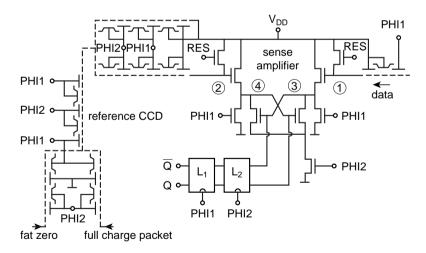

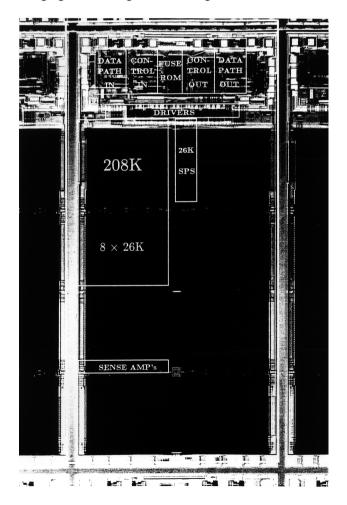

Storage of one bit of a digitised TV field requires a memory capacity of 308 lines of 1024 bits, with a storage time of 10 or 20ms, depending on the application. So, coding 8-bit video samples requires eight times this memory capacity and so eight of these 308Kb memory chips. If the 308Kb was implemented in one large SPS CCD block, the density would be high, but each individual sample would be subjected to many transfers, thereby gradually loosing its charge due to the transfer inefficiency. A good compromise between area, speed and power and the number of transfers, lead to the choice to realise this 308Kb memory with eight 39Kb serial-parallel-serial (SPS) CCD structures (Fig. 14).

The serial stream of video samples at the input (DI) is de-multiplexed over these eight SPS blocks and the data at the outputs of these SPS blocks is multiplexed again to regenerate the serial bit stream. Each SPS block contains two serial CCD registers, one for the input and one for the output, each implemented as a 2-phase 128b register. The 128 parallel registers in the SPS contain 170 storage gates each. First the serial register is filled with a high-speed clock and then a parallel transfer empties this serial register into the parallel registers. So, the frequency of the parallel clock registers is only 128-th of the serial register clock frequency, leading to much less power consumption compared to the case that all samples would shift through one large 39Kb serial register. Each charge packet thus faces a limited number of total transfers (128 transfers in the serial register and another 170 in the parallel register) making it less sensitive to charge-transfer loss. A 10-phase ripple-clock is used in these parallel registers, which results in one empty bit followed by nine data bits. First the ninth data bit moves its charge to the neighbouring empty bit position, thereby moving the empty bit to the ninth position. Next the eighth data bit moves its charge to the empty bit, thereby moving the empty bit to the eighth bit position, and so on. In this way, a storage density close to one-

electrode-per-bit is achieved. As a consequence of this architecture of an SPS, it can store a data bit up to 20ms without refresh. The serial and parallel clock signals needed to operate an SPS block, are generated by the combination of the Gray-code counter, the clock decoder and the ripple-clock generator.

**Fig. 14** Block diagram of the 308Kbit memory

Storing a 'still picture' in the memory requires the data to re-circulate within the CCD memory, meaning that the data output (DO) samples have to be fed back to the data input (DI). The programmable 7b-delay has to take care of a correct data synchronisation during re-circulation. The line clock control block allows this memory to be easily locked to the TV picture.

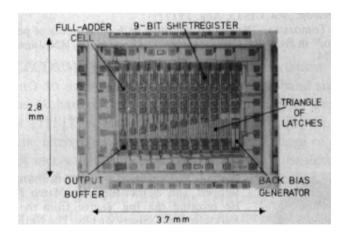

An optimised technology (2  $\mu$ m CCD-nMOS) resulted in a high transfer efficiency ( $\varepsilon \simeq 5.10^{-4}$ ) and a very low leakage current (0.2 $\mu$ A/cm² at 90°C). This technology, combined with a dedicated chip architecture and an optimised SPS structure, allowed a very dense integration of this video memory, whose area was less that 35mm² (somewhat more than half the size of a 256Kb DRAM at that time). Bootstrap techniques are used to speed up the driver circuits and clock buffers (US

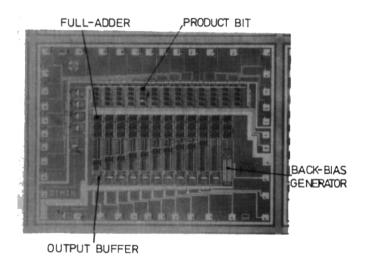

patent 04697111). More, design considerations, performance parameters and a chip photograph of this memory can be found in Part II, Chapter 2.1A.

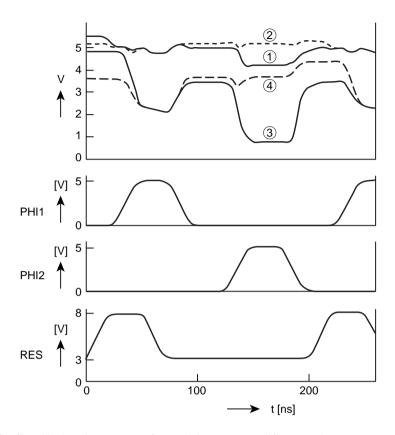

#### 2.1.3 An 835Kb video serial memory

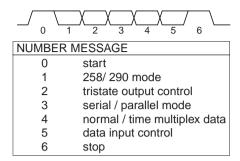

The major differences between this CCD memory and the previously discussed one are the technology, the architecture and the bit density. The discussions in this section will therefore mainly be focused on these topics only. The elementary CCD cell in this memory concept is built from a first polysilicon storage gate (on 25 nm thick oxide) and a second polysilicon transfer gate (on 40 nm thick oxide). Due to the 4-phase clock used in this device, the basic shift operation is somewhat different from the previous one. Fig. 3 in Part II, Chapter 2.1B shows this shift operation in detail.

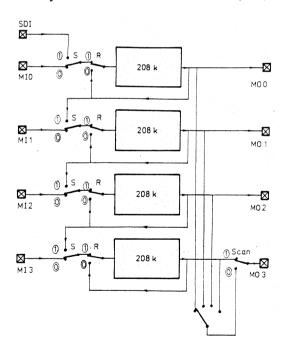

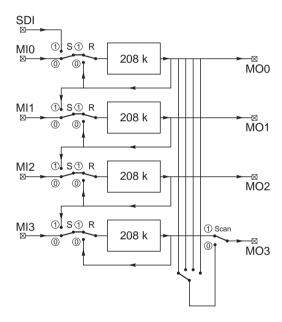

According to the CCIR standard, in the PAL system each field contains 288.5 lines of 720 active samples. In the 4b wide memory (Fig. 15), each bit plane is thus implemented as a memory block of 290 lines of 720 bits (208,800 bits).

Fig. 15 Block diagram of the 835Kb memory

To avoid problems with speed, power and transfer efficiency, the data-flow within a bit-plane is de-multiplexed over eight SPS memory arrays of 26Kb each. The operation of an SPS is analogous to the one discussed in the previous section. The major topic of this chip is the minor technology adaptation (only two more masks) of a baseline  $1.2\mu m$  CMOS process to a CCD-CMOS technology. This allows an effective combination of dense memory with logic and enabled the inclusion of features into the chip that support several operation modes which facilitate its use in digital video systems:

- 1- the 258 lines mode to support the NTSC system (240 active lines per field).

- 2- the normal 208Kb by 4 mode (switches S and R in positions 0 and 1 respectively).

- 3- the multiplex mode, in which the four inputs and outputs are multiplexed over two pins each, saving four I/O pins per memory.

- 4- the serial mode allows an 835Kb by 1 operation of the chip (both switches S and R in position 1).

- 5- The re-circulate mode (switches R in position 0) for still picture applications.

The memory requires no addressing and can be controlled with only two external clock signals, identical to the memory bit clock and the memory line clock in Fig. 14, through which it can be locked to the TV picture. This application-specific design combined with the high bit rate of this memory resulted in a reduction of system overhead at the printed-circuit board level. The dense integration of the CCD memory cell, together with an optimised architecture resulted in a chip area of 29mm<sup>2</sup>, which was about 30% smaller than a comparable DRAM implementation. The power consumption of only 250mW, was more than a factor of three less than video memories implemented in DRAM technology.

More details on this chip and a micro-photograph can be found in Part II, Chapter 2.1B.

#### 2.1.4 Conclusions

Basically, a CCD is a device that shifts charge packets through a serial chain of cells. Each packet contains an amount of charge, which can represent both analogue and digital values. The serial character of operation and the fact that a logic zero and a logic one can easily be represented by an empty and a full charge packet, makes the CCD concept particularly suited for the storage of video pictures. No random access is required, which means that we don't need bit lines and word lines to be pre-charged every clock cycle. This saves a lot of area overhead

and improves both the power consumption and density of video memories by almost a factor of two.

#### In today's perspective

CCD memories lost attention in the late eighties, not because they lost their density and power advantages, but due to the fact that there were many DRAM competitors sharing the development costs of these memories resulting in a faster DRAM learning curve. Today, the CCD devices are still used in digital and video cameras as sensors to capture the picture. These CCDs also contain a storage part, which is used during read out. The parallel data is then transferred into a serial bit-stream. Charge transfer efficiency is currently less of an issue, because of two reasons. First, the use of polysilicon gates allows optimised annealing steps to reduce the number of surface states that could trap charge. Second, in stead of surface-channel devices, buried-channel devices are now used, which are much less sensitive to surface states since the charge transport is now below rather than at the silicon surface.

## 2.2 High-density gate arrays

#### 2.2.1 Introduction

Gate arrays already exist for several decades to support fast prototyping of new system concepts. Since these gate arrays must support a wide range of potential applications, their architecture has to be flexible. However, the flexibility of general-purpose architectures is usually at the cost of additional area. Therefore, several high-density gate array (HDGA) architectures have been proposed in literature, to accommodate a dense integration of prototype circuits. The goal of the research performed in this area was to increase the efficiency of the functions mapped onto the gate array, without loosing any of the gate arrays' flexibility.

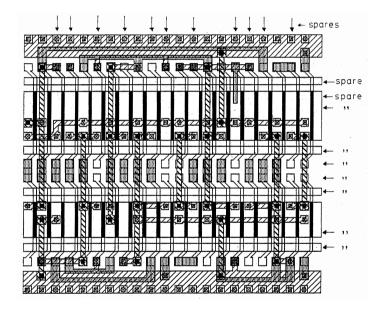

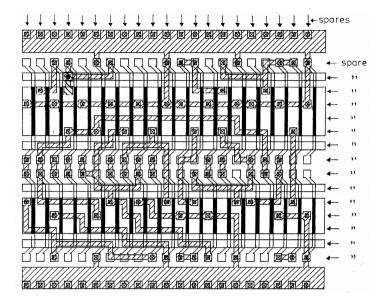

## 2.2.2 An efficient and flexible architecture for high-density gate arrays

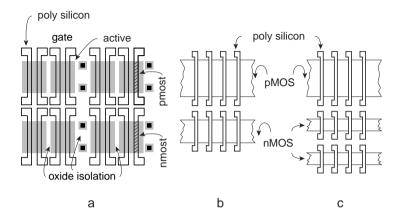

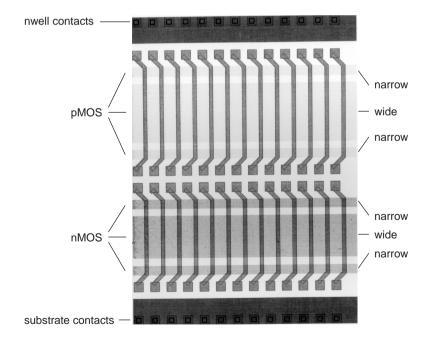

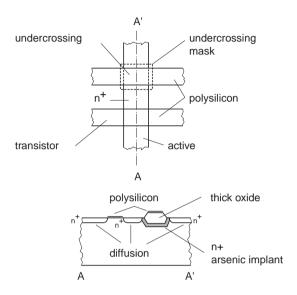

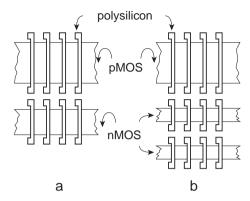

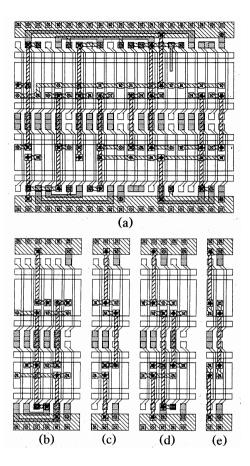

In gate arrays, the basic devices or cells can be isolated by means of oxide isolation [Wong, 1986; Takahashi, 1985] (Fig. 16a), often referred to as 'sea-of-gates', or by means of the gate-isolation technique [Ohkura, 1982] (Fig. 16b), which is often associated with the 'sea-of-transistors' architecture. This architecture consists of a continuous array of transistors, in which the logic gates are separated

from one another by transistors that are switched off. This can be done by including one couple of nMOS and pMOS isolation transistors in every logic cell. Their gates are then connected to the ground and supply lines, respectively.

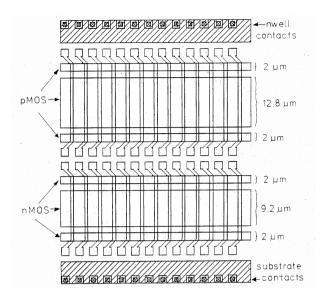

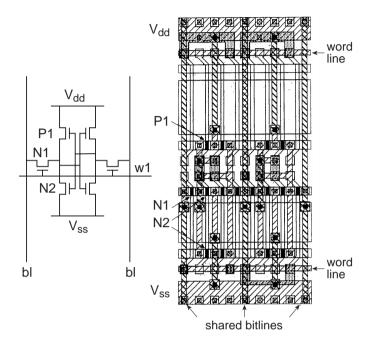

Either of these gate arrays, however, offer nMOS and pMOS transistors of only one size each. Particularly, circuits such as transmission-gate flipflops, ROMs, RAMs and PLAs, as well as dynamic CMOS circuits, require transistors of different sizes. In the sea-of-gates architecture as proposed by [Duchene, 1989] and shown in Fig. 16c, the nMOS transistor is split up into two smaller ones in parallel, each having its own connection(s). However, in memory arrays, many transistor gates usually share a common word line and thus do not require individual connections. These considerations have been used in the development of a new HDGA architecture (US patent US05250823) (Fig. 17).

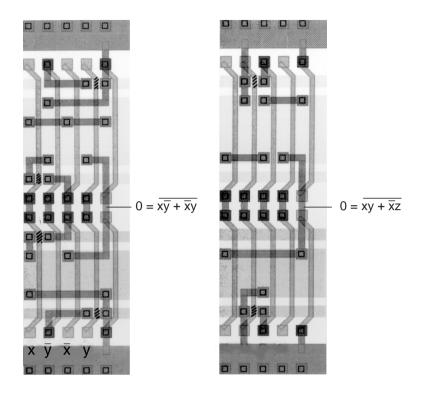

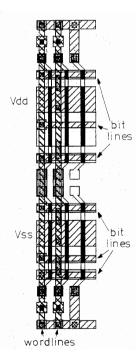

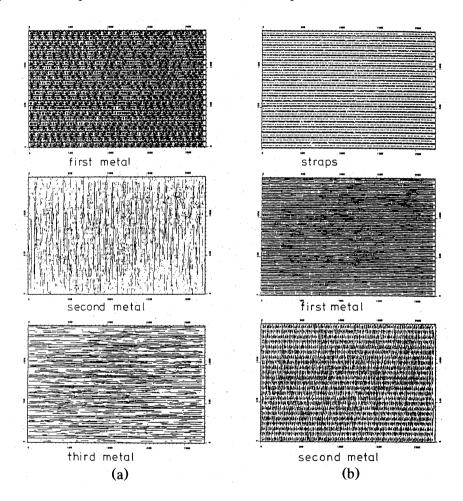

Each basic cell in this architecture provides three nMOS and three pMOS transistors. Every wide transistor lies in between two narrow ones. Both the nMOS and pMOS transistors each share a common gate. The contact positions in both horizontal and vertical directions are on the same grid, defined by the routing pitch. By the time this research was done, triple-metal CMOS processes were used to implement HDGAs. However, due to additional complex planarisation and contact-etching steps, the third metal layer in this technology would increase the silicon cost by up to 25% and turnaround time by 35%. Replacing this third metal layer by a titaniumsilicide (TiSi<sub>2</sub>) layer, increases the silicon cost and processing time by no more than 5 to 10%, because connections in this layer, called straps, enable direct contact between polysilicon gates and source or drain areas of transistors, without the use of metal layers and contact holes. These straps are used to bridge only short distances, such as those within library cells. A detailed description of using these straps to efficiently implement ROM cells (US patent US05053648), RAM cells, D-type flipflops and basic logic gates on the developed architecture can be found in Part II, Chapter 2.2. It is clear that the small (narrow) transistors offered by the architecture allow smaller memory cells. In this section, however, the focus will be on the use of the straps in combination with the architecture, to show that it also allows a dense integration of logic gates. The Exclusive-NOR (EXNOR) and multiplexer gates of Fig. 18 are realised with only one metal layer in a three metal layer technology. The other two metal layers are then completely available for routing purposes.

The narrow transistors connected as inverters to create the inverse functions x and y. The wide transistors create the EXNOR-gate. The polysilicon tracks that carry the inverted signals x and y not only act as inputs to the wide transistor gates, but also serve to connect the drains of the widely spaced narrow nMOS and pMOS transistors that form the inverters. So, creating logic gates that have inverting input signals, such as in the above examples in Fig. 18, these inputs need no separate large inverters, because these are implemented in the small transistors, parallel to

the large ones, which create the logic gate. This architecture is therefore particularly suited to realise multiply and add functions with two times higher densities than previously presented gate arrays, in a three metal layer technology.

Fig. 16 (a) Typical example of a sea-of-gates architecture

- (b) Typical example of a sea-of transistors architecture

- (c) A sea-of-gates example that supports memory implementation

Fig. 17 The new common-gate HDGA architecture

Fig. 18 The use of small transistors in creating logic gates: an EXNOR (a) and a multiplexer (b)

#### 2.2.3 Evaluation and results

A test chip has been designed, which includes several different implementations of a 10 by 10 bits multiplier, a 24Kb ROM and some performance and technology evaluation modules. However, the regularity of a multiplier is probably not representative for a general logic circuit. Therefore a further evaluation of the HDGA architecture has been performed. The results of this evaluation are presented in Table 2. Next to two different multipliers, also a complex logic block of a compact disc servo-control chip (CD-BLOCK) and two different fast-fourier transform (FFT) designs (FFT A and FFT B) have been mapped onto the HDGA architecture. FFT B is also realised with three different layout aspect ratios ( $W/L \approx 1$ , 4,  $\frac{1}{4}$ , respectively), to investigate the relation between this ratio and the eventual layout area. Their densities are compared with a standard-cell implementation in a two-metal layer and straps CMOS technology.

|             |                         | Standard cell (SC) | Common-gate HDGA |                        | HDGA/SC               |  |

|-------------|-------------------------|--------------------|------------------|------------------------|-----------------------|--|

| Design      | # of gates (2-<br>NAND) | Aspect ratio       | Aspect ratio     | Transistor utilisation | Area ratio<br>HDGA/SC |  |

| MPY (20×20) | 20800                   | 1.5                | 1.50             | 96%                    | 0.97                  |  |

| MPY (10×10) | 5000                    | 1.51               | 1.51             | 95%                    | 1.00                  |  |

| CD-BLOCK    | 1350                    | 2.06               | 2.34             | 94%                    | 1.00                  |  |

| FFT A       | 2637                    | 1.02               | 1.07             | 87%                    | 0.68                  |  |

| FFT B (1)   | 1980                    | 1.06               | 1.03             | 86%                    | 0.77                  |  |

| FFT B (4)   | 1980                    | 3.92               | 3.92             | 74%                    | 0.82                  |  |

| FFT B (1/4) | 1980                    | 0.33               | 0.27             | 81%                    | 0.82                  |  |

Table 2 Comparison of different logic functions in standard-cell and HDGA design

The 10 by 10 bits multiplier and the more complex 20 by 20 bits multiplier occupy about the same area as their standard-cell counterparts. The HDGA implementation of the CD-BLOCK (a logic block of a compact disc servo control chip) occupies exactly the same area as the standard-cell version. All HDGA versions of the FFT designs score even better than the standard-cell versions. Because their net lengths and transistor sizes are also about equal, the HDGA circuits show the same performance as the standard-cell versions. The overall conclusion from this table is that the HDGA implementation showed equal performance at comparable or even smaller chip areas. This is quite a good result, since usually there was an area difference of a factor of 1.5 to 2, in favour of the standard-cell versions. There are two reasons for this increased HDGA efficiency. First, the use of straps in HDGAs turns out to be very efficient compared to the metal interconnections in the standard-cell designs. Second, the use of the narrow transistors in the HDGA architecture enables a very dense implementation of a large variety of cells. More details on this subject can be found in Part II, Chapter 2.2.

#### 2.2.4 Conclusions

A flexible high-density gate-array architecture is presented. The inclusion of narrow transistors in parallel with wide transistors in the basic cell shows a lot of advantages. First they are used to generate local inversions within logic gates, without any area penalty. Next, it supports the mapping of flipflops that require small feedback transistors. Finally, memory cells like SRAM and ROM cells are

easily mapped onto this architecture. A test chip shows that even with a regular array of transistors logic gates and memories could be implemented with a density improvement of about a factor of two compared to existing gate arrays.

#### In today's perspective

High-density gate arrays are still used for fast prototyping in many different applications. However, due to the increased density of the transistors over the years, the number of metal layers that these gate arrays currently use, has gone up to about four or five. This has lengthen the turn-around time to four to five weeks, compared to about two weeks that it took more than a decade ago. Also the NRE costs (non-recurring engineering costs, which includes almost all costs related to design, test and packaging, except for the silicon costs) have increased to above US\$ 100,000. Because of the expected increase in the costs of a mask set, more flexibility in terms of design and redesign is required. Over the last couple of years, programmable logic, such as FPGAs (field-programmable gate arrays) gained much more attention and, in some cases, have overtaken applications which were formerly implemented with gate arrays.

Regarding future VLSI design, hundreds of millions of transistors are expected to be integrated on a digital chip. A higher degree of regularity and a lower variety of differently shaped transistors could help to improve yield. The concepts of a regular array of transistors, such as in the HDGA discussed in this paragraph, could very well be applied to the development of a standard-cell library, to allow technologists to only focus on a limited number of transistor topologies to increase yield.

## Chapter 3

## **Design for robustness**

The robustness of an integrated circuit has been a major topic already since the early days of its existence. Two important issues regarding this robustness are reliability and signal integrity. Reliable circuit operation includes the design tolerance with respect to the requirements of the application (specification) as well as to those of the process technology (design rules). Signal integrity reflects the degree to which the shape of a signal is affected by cross-talk, noise or propagation delay. Due to the continuous process of scaling of the minimum features sizes, the supply voltage and the clock periods, the design margins have dramatically reduced, thereby threatening the reliability and signal integrity of current and future ICs.

Two subjects relate to circuit reliability. The first one is an example in which the reliability requirements are defined by the application. It describes the problems that arise from communication between asynchronous (sub)systems and the solutions that have been developed to guarantee a reliable communication between such systems. As such, the design of a synchroniser will be presented together with a prediction of its failure rate. The second subject is an example in which the reliability requirements are defined by the technology design rules. Due to the increased current densities in the on-chip metal supply and interconnect lines, electromigration is becoming increasingly important. Particular its exponential dependence on the temperature has intensified the research in such effects as wire self-heating due to the expected increase of the power consumption in these resistive metal lines. Both a qualitative and quantitative discussion of wire self-heating is presented.

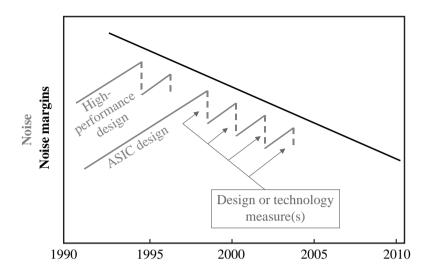

An increased number of devices on a chip, combined with reduced feature sizes and reduced physical spacing, causes an increase of on-chip generated switching noise and interference. At the same time the supply and transistor threshold voltages decrease, thereby reducing the noise margins. In other words, due to scaling the noise increases, while the margins reduce. This puts a burden on the signal integrity within an IC and on the reliability of its operation. Maintaining signal integrity and design robustness at a sufficiently high level will increasingly require specific design measures. These signal integrity issues will be discussed in the third subject in this chapter.

# 3.1 Reliable communication between asynchronous systems

#### 3.1.1 Introduction

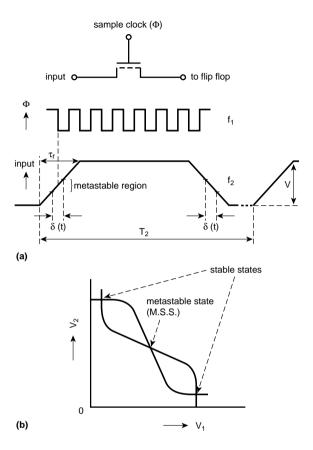

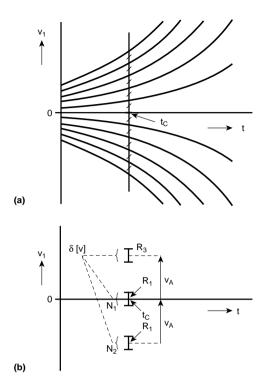

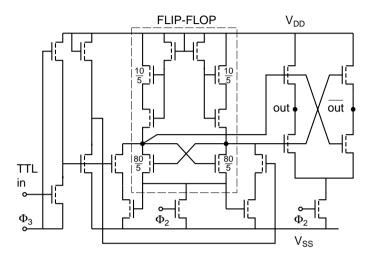

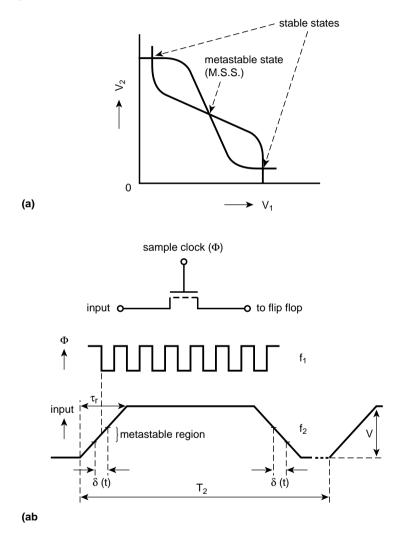

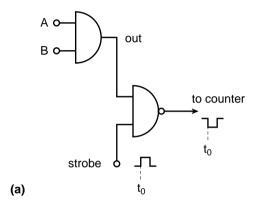

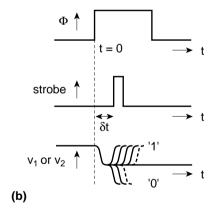

Most signals that are input to a synchronous chip, are sampled by flipflops, which are controlled by a clock signal. In the communication between digital (sub)systems that do not share a common time reference, signals may occur which are not logically defined [Chaney, 1973]. This means that signals are generated randomly in time (asynchronous), with respect to each other. It is particularly possible that an input signal will change during an edge of the sample-clock. There is a large possibility that such a situation will cause a system failure. This can only be prevented by using a synchroniser circuit, most commonly a flipflop, which must support reliable communication between such asynchronous systems. A flipflop can adopt three different states: a logic 'one', a logic 'zero' and a meta-stable state (MSS). In a (differential) flipflop, the exact meta-stable point is defined to be the point in which both flipflop nodes show equal voltages. Sampling asynchronous (random) data may put the synchronising flipflop into an undefined MSS. Due to the feed-back loop in the flipflop, it will recover from such an MSS. The closer to the meta-stable point, the more time it takes to recover from it, and the longer an MSS lasts. If such an MSS lasts almost a full clock period, it will cause anomalous response times [Pechoucek, 1976]. Part II, Chapter 3.1 describes the design, operation and performance of a synchroniser in detail, as well as the influence of noise on its MSS behaviour. The next subsection discusses the most important topics and results of this research.

#### 3.1.2 Synchroniser behaviour

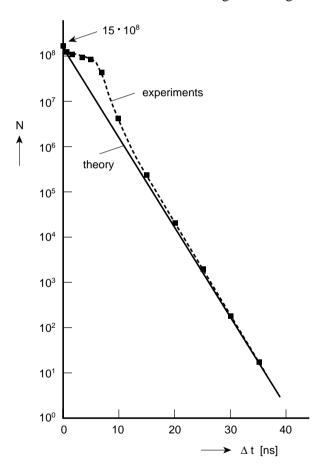

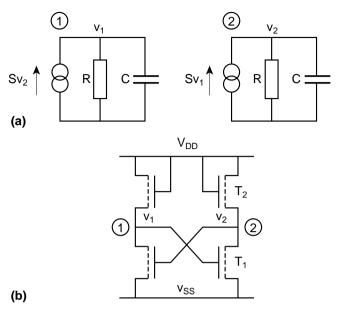

Sampling asynchronous data signals at an input of a chip, may result in situations in which the input signal is changing (e.g. from a '0' to a '1') during the sample moment of the clock signal  $\phi$  (Fig. 19a). For a better understanding, slow rising and falling edges of the input signal are drawn in this figure.

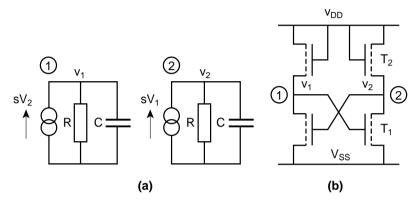

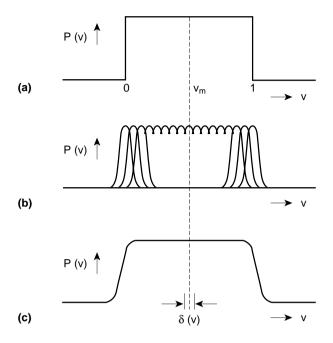

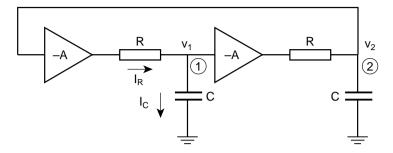

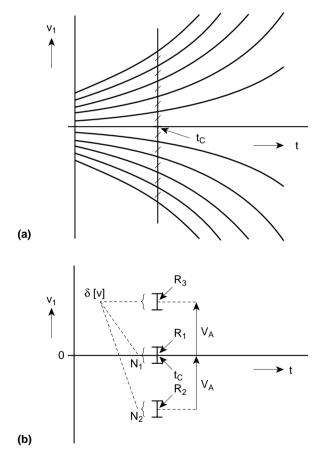

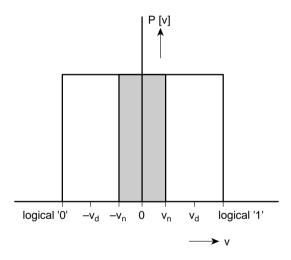

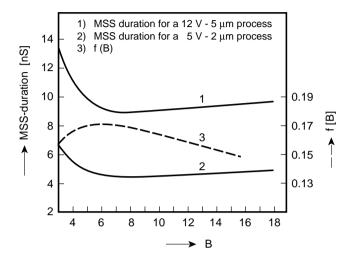

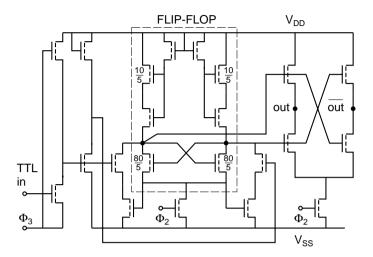

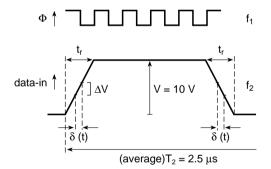

The sample transistor is drawn as a MOS pass transistor, whose output is connected to a flipflop, which consists of two cross-coupled inverters only. Let us assume that the feed-back loop in the flipflop is very weak compared to the sample transistor. Now, this flipflop will reach a MSS (Fig. 19b), when the falling edge of the sample clock appears within a small time interval  $\delta(t)$  during a rising or falling edge of the input signal.

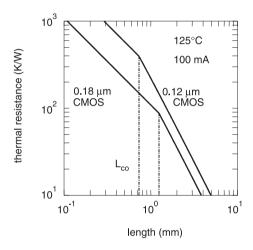

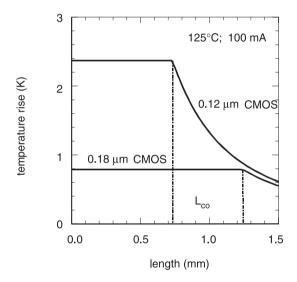

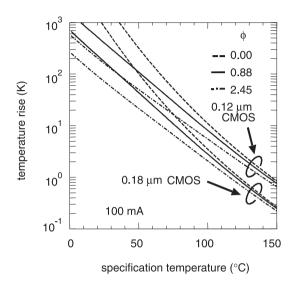

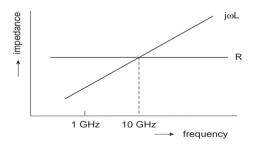

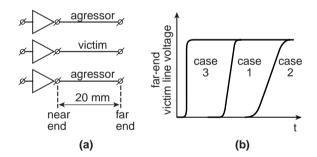

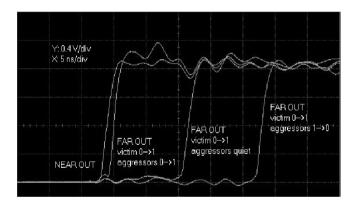

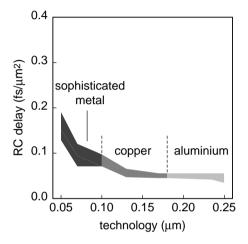

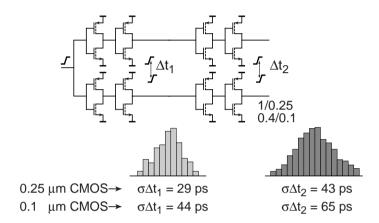

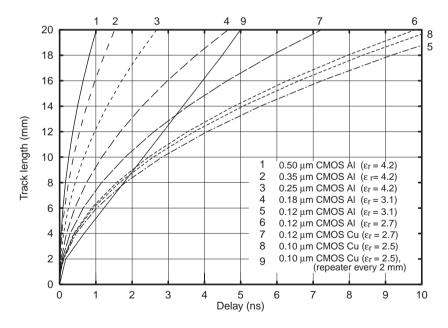

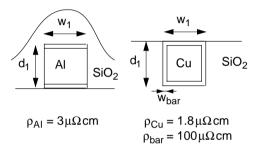

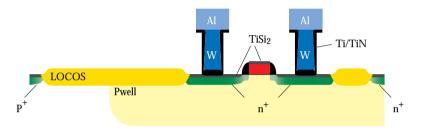

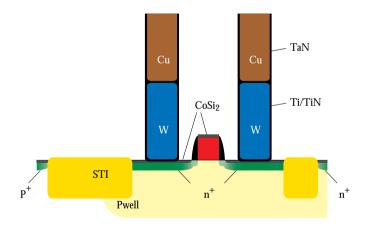

Fig. 19 (a) Possible signal configuration at asynchronous communication (b) Possible states of a flipflop, consisting of two inverters of which the transfer characteristics are given