## Constraint driven operation assignment for retargetable VLIW compilers

#### Citation for published version (APA):

Bekooij, M. J. G. (2004). Constraint driven operation assignment for retargetable VLIW compilers. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR573284

DOI: 10.6100/IR573284

### Document status and date:

Published: 01/01/2004

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# Constraint Driven Operation Assignment for Retargetable VLIW Compilers

Marco Bekooij

## Constraint Driven Operation Assignment for Retargetable VLIW Compilers

## PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr. R.A. van Santen, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op maandag 12 januari 2004 om 16.00 uur

door

Marco Jan Gerrit Bekooij

geboren te Doorn

Dit proefschrift is goedgekeurd door de promotoren:

prof.Dr.-Ing. J.A.G. Jess en prof.dr.ir. J.L. van Meerbergen

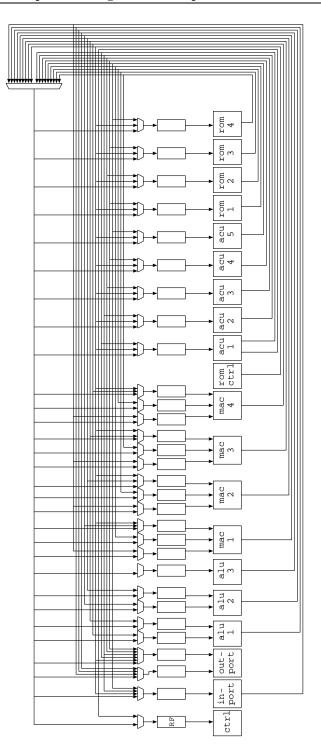

Cover: Layout of a VLIW processor which can execute 41 operations in parallel. Many of the techniques applied in the compiler for this processor are described in this thesis. The VLIW processor and the compiler are products of Silicon Hive.

#### CIP-DATA KONINKLIJKE BIBLIOTHEEK, DEN HAAG

Bekooij, Marco Jan Gerrit

Constraint Driven Operation Assignment for Retargetable VLIW Compilers Marco Bekooij.-Eindhoven: Eindhoven University of Technology Thesis Eindhoven. - With ref. - With summary in Dutch ISBN 90-74445-60-8 Subject heading: constraint analysis, constraint satisfaction, compiler technology, code generation, signal processor architectures, VLIW-processors.

The work described in this thesis has been carried out at the Philips Research Laboratories in Eindhoven, The Netherlands, as part of the Philips Research programme.

©Philips Electronics N.V. 2004 All rights are reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

# Preface

The thesis in front of you is a result of my efforts at the Philips Research Laboratories. In this unique laboratory I have had the possibility to do for 4 years research on the same industrial relevant problem. This thesis would not be there without the contribution of fellow-researchers which I like to thank personally.

The major part of the research has been done in the Core Compiler Codesign (COCOON) project which was headed by Jeroen Leijten. I am grateful to him that he gave me the opportunity to work on constraint driven operation assignment techniques despite the large uncertainty about their applicability and the potential benefits of this approach. Exchange of valuable insights developed in the COCOON project have made a significant contribution to the approach presented in this thesis.

Without Jef van Meerbergen I wouldn't be able to obtain the same research success. He established the right boundary conditions and put my research in a broader context. He also urged me, often earlier then I wished, to apply the developed techniques on real-life design cases.

I also like to thank professor Jochen Jess for given me the change to obtain my Ph.D. degree from the Eindhoven University of Technology. He pushed me from the beginning in the right direction with his remark that a Ph.D. thesis should preferably be about a single small indepth worked out problem. I would also like to thank Albert van der Werf for the opportunity he gave to continue the research on constraint driven code generation in the Monarch project.

The presented operation assignment techniques are an essential extension of the constraint driven scheduling techniques which were introduces by Adwin Timmer approximately 10 years ago. So called value lifetime serialization techniques were added by Bart Mesman. Koen van Eijk implemented these scheduling and serialization techniques in the research tool FACTS. This tool has been extended with an implementation of the in this thesis described operation techniques.

I am also thankful for the development version of A|RT-designer that was provided by the company Adelante Technologies. With this processor synthesis and compilation tool suite I was able to do an extensive evaluation of the developed operation assignment techniques. The animated discussions with Koen van Nieuwenhoven, André Collignon, Ivan Indinge and Kurt Du Pont of Adelante Technologies were experienced as very valuable.

Finally, I would like to thank Renée and her mother Clara Jacobs for their pleasant distraction

during writing of this thesis and I would like to thank my father for supporting me through the years.

# Contents

## Preface

| 1 | Intro | oduction                                               | 1 |

|---|-------|--------------------------------------------------------|---|

|   | 1.1   | Application domain specific VLIWs                      | 1 |

|   | 1.2   | Compiler flow                                          | 3 |

|   | 1.3   |                                                        | 3 |

|   | 1.4   |                                                        | 5 |

|   | 1.5   |                                                        | 7 |

|   | 1.6   |                                                        | 9 |

| 2 | Inpu  | ts of the Code Generator 1                             | 1 |

|   | 2.1   | Target processor                                       | 1 |

|   |       | 2.1.1 Data path template                               | 1 |

|   |       | 2.1.2 Register file architecture                       | 2 |

|   |       | 2.1.3 Network model of the data path                   | 6 |

|   |       | 2.1.4 Instruction encoding                             | 7 |

|   | 2.2   | Intermediate representation of the application program | 0 |

|   |       | 2.2.1 Data flow graph                                  | 0 |

|   |       | 2.2.2 Flow graph representations                       | 3 |

|   | 2.3   | Timing constraints                                     | 6 |

|   | 2.4   | Problem statement                                      | 8 |

| 3 | Cod   | e Generation by Traversing the Search-Space 2          | 9 |

|   | 3.1   | Code generation phases                                 | 9 |

v

|   |      | 3.1.1   | Schedule search-space pruning                                          | 32 |

|---|------|---------|------------------------------------------------------------------------|----|

|   |      | 3.1.2   | Operation assignment infeasibility detection                           | 33 |

|   | 3.2  | Phase c | coupling                                                               | 34 |

|   |      | 3.2.1   | Phase coupling example                                                 | 35 |

|   |      | 3.2.2   | Schedule search-space pruning given a partial assignment of operations | 35 |

|   | 3.3  | Constra | aint analysis strategy                                                 | 37 |

|   |      | 3.3.1   | The relation between combinatorial problems                            | 37 |

|   |      | 3.3.2   | Search algorithm based on constraint analysis                          | 38 |

|   |      | 3.3.3   | Releated work on constraint analysis                                   | 40 |

|   |      | 3.3.4   | Computational complexity of the assignment problem                     | 41 |

| 4 | Assi | gnment  | Search-Space Representation                                            | 49 |

|   | 4.1  | Conflic | t graph concepts                                                       | 49 |

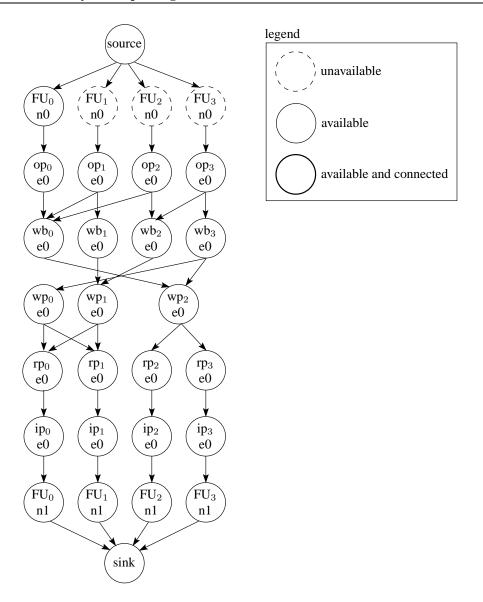

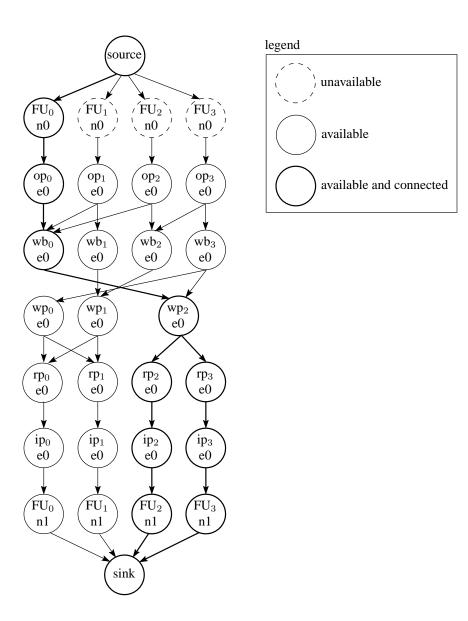

|   | 4.2  | Networ  | k model                                                                | 51 |

|   | 4.3  | Assign  | ment search-space model                                                | 54 |

|   |      | 4.3.1   | Modeling of interconnect constraints                                   | 54 |

|   |      | 4.3.2   | Modeling of hard resource conflicts                                    | 55 |

|   |      | 4.3.3   | The assignment conflict graph                                          | 56 |

|   |      | 4.3.4   | Redundancy in the assignment conflict graph                            | 61 |

| 5 | Assi | gnment  | Search-Space Pruning                                                   | 65 |

|   | 5.1  | Pruning | g of colors of nodes in a clique.                                      | 65 |

|   | 5.2  | Connec  | ctivety driven pruning                                                 | 71 |

|   |      | 5.2.1   | Pruning example                                                        | 71 |

|   |      | 5.2.2   | Communication path graph                                               | 71 |

|   |      | 5.2.3   | Communication path graph pruning algorithm                             | 75 |

|   |      | 5.2.4   | Communication path graphs for cyclic data flow graphs                  | 78 |

|   |      | 5.2.5   | Data dependency chains                                                 | 82 |

|   |      | 5.2.6   | Diverging data dependencies                                            | 85 |

|   |      | 5.2.7   | Converging data dependencies                                           | 90 |

|   |      | 5.2.8   | Guarantees after pruning                                               | 91 |

#### Contents

| 6  | Mul    | ti-casting                                             | 95  |

|----|--------|--------------------------------------------------------|-----|

|    | 6.1    | Multi-casting concept                                  | 95  |

|    | 6.2    | Modeling of multi-casting in the ASCG.                 | 96  |

|    | 6.3    | Copy operations                                        | 98  |

|    | 6.4    | Global write-back busses                               | 99  |

|    |        | 6.4.1 Write-back bus assignment                        | 99  |

|    |        | 6.4.2 Scalability considerations                       | 100 |

| 7  | Hier   | archy, Operation Merging and the Decision Heuristic    | 103 |

|    | 7.1    | Hierarchical data flow graphs                          | 103 |

|    | 7.2    | Operation merging                                      | 111 |

|    | 7.3    | Decision heuristic applied during operation assignment | 112 |

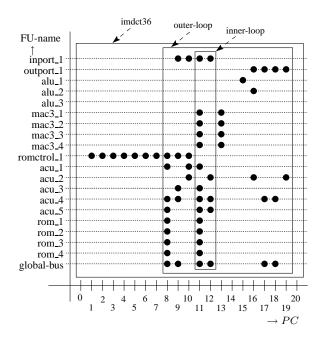

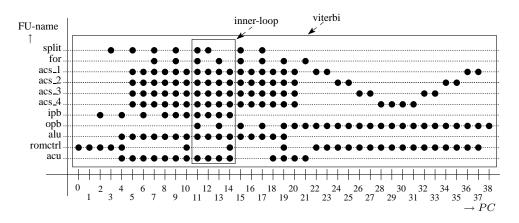

| 8  | Qua    | ntitative Evaluation                                   | 115 |

|    | 8.1    | Experimental compiler flow                             | 115 |

|    | 8.2    | Evaluation of the operation assignment techniques      | 116 |

|    |        | 8.2.1 Operation assignment examples                    | 116 |

|    |        | 8.2.2 Assignment results                               | 121 |

|    | 8.3    | Lifetime serialization after operation assignment      | 125 |

|    | 8.4    | Scheduling results                                     | 126 |

| 9  | Con    | clusion                                                | 129 |

| A  | Con    | straint Graph Representation                           | 131 |

| Bi | bliogi | raphy                                                  | 137 |

| Sa | menv   | atting                                                 | 143 |

| Cu | ırricu | ılum Vitae                                             | 145 |

ix

## **Chapter 1**

# Introduction

This thesis describes constraint driven operation assignment techniques. These techniques are intended for application in a retargetable compiler that generates code for application domain specific Very Long Instruction Word (VLIW) processors. Multiple register files and an incomplete communication network in the data path are applied in these processors to improve their power-efficiency and scalability. However the use of more than one register file and an incomplete communication network make the assignment of operations to the functional units in the processor an important but difficult subtask in the compiler.

To derive a proper operation assignment, we apply constraint analysis techniques. These analysis techniques take explicitly the interconnect in the data path of the processor into account and remove infeasible operation assignment options from the assignment searchspace. This way assignment decisions that would inevitably lead to violation of resource or timing constraints are prevented.

The organization of the remaining part of this chapter is as follows. In Section 1.1 we motivate why we focus on compilation techniques for application domain specific VLIWs. The retargetable compiler flow is presented in Section 1.2. Why operation assignment is an important but difficult subtask in the compiler is described in Section 1.3. The major contributions of this work are listed in Section 1.4. In Section 1.5 the differences between this work and operation assignment techniques known from the literature are indicated. Finally, Section 1.6 describes the organization of the thesis.

## **1.1 Application domain specific VLIWs**

Today's embedded systems typically contain several processors, memories and peripherals that communicate with each other via an on chip network. Power dissipation usually limits the functionality that can be offered by these systems. Approximately 100 mW is seen as an acceptable power dissipation for battery supplied mobile systems, while the use of cheap plastic IC-packages limits the power dissipation to approximately 1 W for wired systems.

Specialization of processors towards their task can significantly improve their power-efficiency [HMV]. Therefore event driven and control dominated tasks are usually executed on general purpose processors such as offered by ARM [Fur96] or MIPS [MIP], while signal processing tasks are often carried out on classical Digital Signal Processors (DSPs) like the TI C54x [Lea97] or the R.E.A.L. [KLMW98].

Programming of general purpose processors is usually done in a high level language like C which is translated by a compiler into micro-code. On the other hand classical DSPs are often manually programmed in assembly code because the micro-code delivered by a compiler is often of an insufficient quality for these processors [Leu97]. However, programming in assembly code is a time-consuming and error-prone task which requires detailed knowledge of the DSP's instruction set.

For classical DSPs efficient code generation with a compiler is prohibited by the irregularities in the data path of these processors and the non-orthogonality of their instruction sets [ZVSM94]. Contrarily, for VLIW processors a compiler can generate high quality code because these processors have a regular data path and an orthogonal instruction set. However these processors have, for embedded applications, an often unacceptably low powerefficiency and micro-code density.

The code generation techniques described in this thesis are intended for the next generation VLIW processors. Unlike the first generation VLIW processors, exhibiting a single register file, the targetted VLIWs may contain several register files, an incomplete communication network and a refined instruction set optimized for digital signal processing. These processors are more difficult compiler targets but are more power-efficient than the first generation VLIW processors. On the other hand they are typically less power-efficient, yet significantly more compiler friendly compared to classical DSPs.

| embedded processor<br>type                               | performance |       |       | compiler friendliness |       |        |       |

|----------------------------------------------------------|-------------|-------|-------|-----------------------|-------|--------|-------|

|                                                          | ILP         | m. RF | rate. | ILP                   | c. RF | o. enc | rate. |

| general purpose                                          | low         | no    | -     | low                   | yes   | yes    | ++    |

| classical DSP                                            | medium      | yes   | +     | medium                | no    | no     |       |

| first generation VLIW                                    | medium      | no    | +     | medium                | yes   | yes    | +     |

| second generation<br>application domain<br>specific VLIW | high        | yes   | ++    | high                  | no    | yes    | -     |

Table 1.1: Characteristics of processors in the case they are applied for DSP applications. In this table stands the abbreviation "ILP" for instruction level parallelism, "m. RF" for multiple register files, "c. RF" for central register file, "rate." for rating and "o. enc" for orthogonal instruction encoding.

Another important characteristic of VLIW processors with multiple register files is that the number of parallel computation units in the data path is better scalable than the data path of processors with a central register file. The data path of a processor is well scalable if an increase of the number of parallel computation units in the data path does not result in a more than proportional increase in silicon area or in a significant decrease in the power-efficiency of

#### 1.2 Compiler flow

| embedded processor                                       | power efficiency |       |      |       | code size |       |       |

|----------------------------------------------------------|------------------|-------|------|-------|-----------|-------|-------|

| type                                                     |                  |       |      |       |           |       |       |

|                                                          | ILP              | m. RF | Iset | rate. | i. enc    | m. RF | rate. |

| general purpose                                          | low              | no    | RISC |       | medium    | no    | -     |

| classical DSPs                                           | medium           | yes   | CISC | +     | high      | yes   | ++    |

| first generation VLIW                                    | medium           | no    | RISC | -     | none      | no    |       |

| second generation<br>application domain<br>specific VLIW | high             | yes   | CISC | ++    | low       | yes   | +     |

Table 1.2: Continuation of Table 1.1 with characteristics of processors in the case they are applied for DSP applications. In this table stands the abbreviation "ILP" for instruction level parallelism, "m. RF" for multiple register files, "RISC" for Reduced instruction set, "CISC" for complex instruction set, "Iset" for instruction set, "rate." for rating and "i. enc" for instruction encoding.

the processor. In processors with multiple register files the number of register fields and ports per file is typically lower than in processors with a central register file. Register files with a smaller number of ports and register fields are faster and more power-efficient than register files with a large number of ports and register fields. Therefore, processors with multiple register files are potentially more power-efficient and able to deliver a significantly higher computational performance than processors with a central register file. The characteristics of the processor types discussed above are summarized in Table 1.1 and Table 1.2.

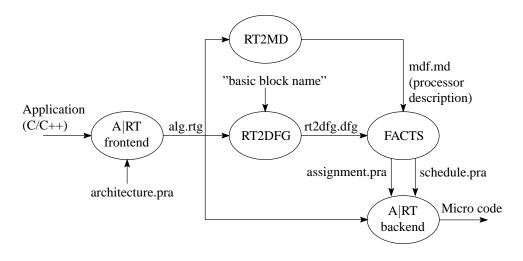

## **1.2 Compiler flow**

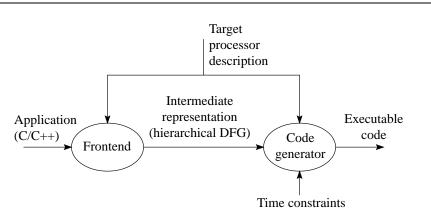

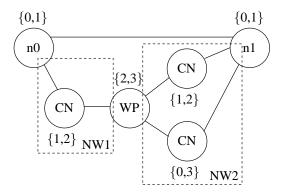

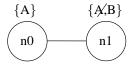

Our work is based on the retargetable compiler flow as shown in Figure 1.1. The algorithmic description of the application, for example in the C++ language, is the input to the compiler frontend. The frontend translates the description into an intermediate representation. During this translation the functionality offered by the data path of the processor, is taken into account. The intermediate representation together with a description of the target processor and a specification of the time constraints are the inputs of the code generator. The code generator produces an executable program. The operation assignment techniques, that are described in this thesis, are essential entities of the code generator.

## **1.3** Operation assignment challenges

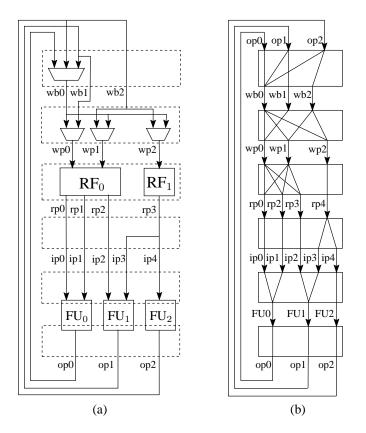

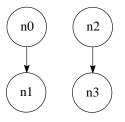

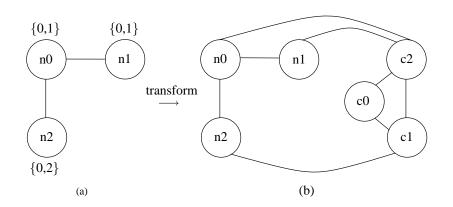

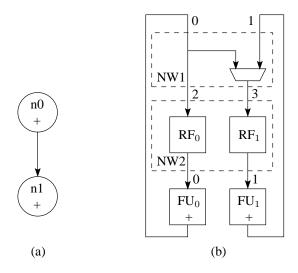

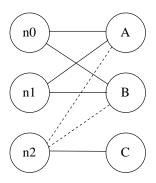

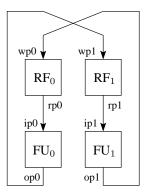

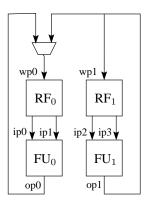

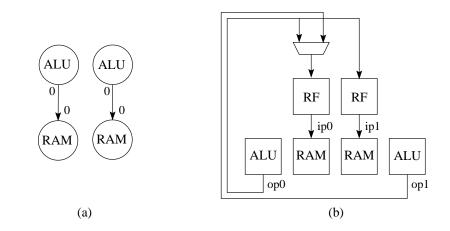

Operation assignment is a difficult task in the case that processors are targeted with more than one register file and an incomplete network. In this case, a functional unit can access only a subset of the register files for reading or writing. Therefore, operations must be assigned to the functional units in such a way that these units are able to access the Register Files (RFs) in which their input values are stored. This is illustrated with a small example below.

Figure 1.1: The applied compiler flow.

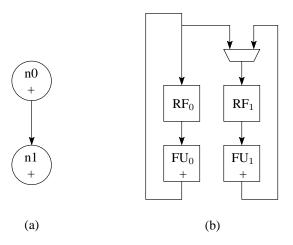

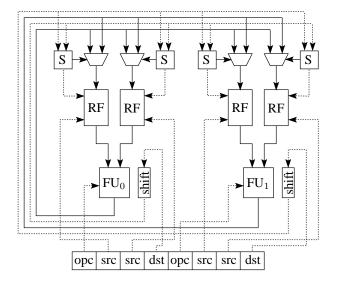

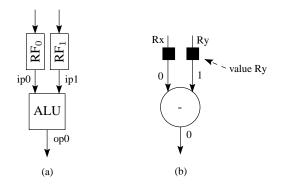

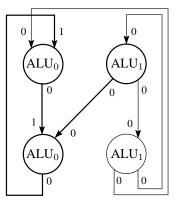

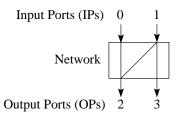

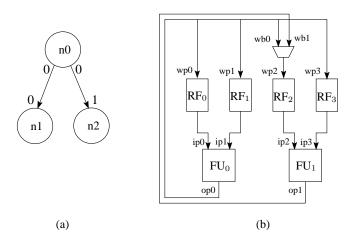

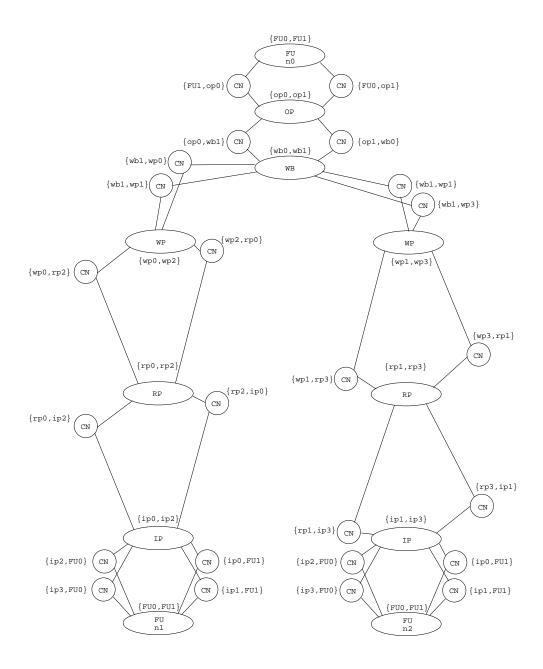

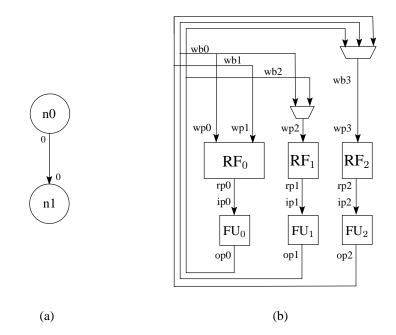

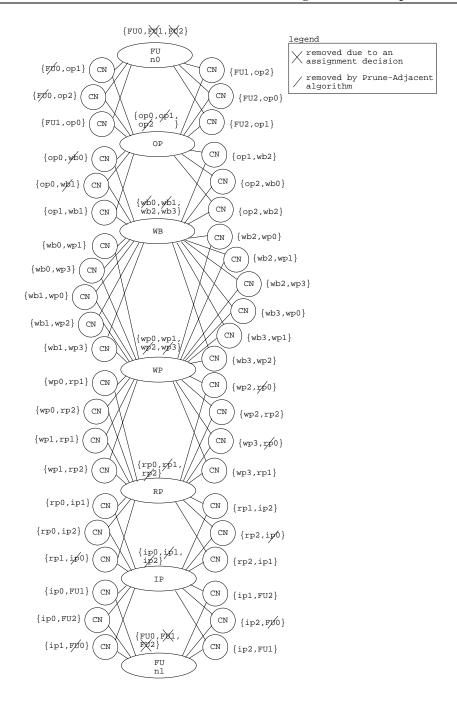

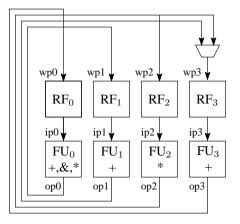

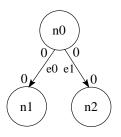

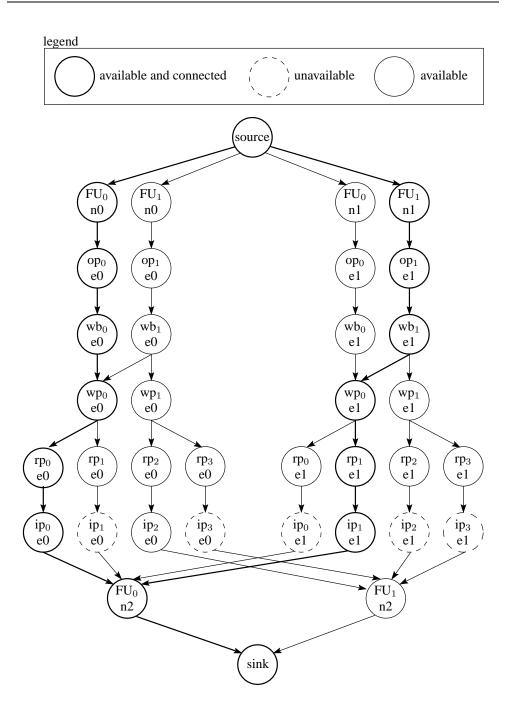

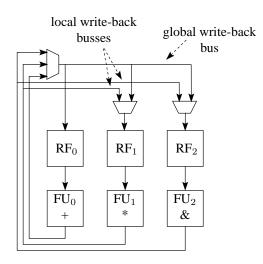

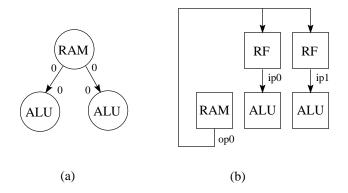

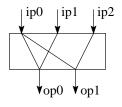

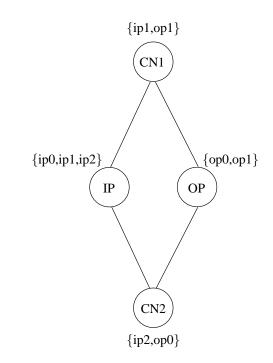

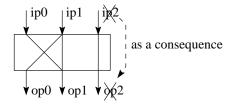

In Figure 1.2 a Data Flow Graph (DFG) and a data path of a processor are shown. The resources in the data path are the Functional Units (FUs), the registers in the register files, the interconnect in the connection network, and the input ports and output ports of those building blocks. All these resources are controlled by VLIW-instruction bits and can be used in parallel.

Figure 1.2: A DFG (a) and a data path instance (b).

A communication path is a path from the output port of a functional unit to the input port of a functional unit. This path traverses the connection network and a register file. Assignment of the operations in the DFG to the functional units of the target processor should be such that the required communication paths exist. For the DFG and the architecture of Figure 1.2, the requirement that a communication path from the producing FU to the consuming FU, has consequences for the assignment of the operations n0 and n1 to the functional units. For example, if operation n0 is assigned to FU<sub>1</sub> then also operation n1 must be assigned to FU<sub>1</sub>.

In the case that the DFG is folded then operation n0 and n1 of succeeding loop iterations are executed in the same clock cycle. In this case those operations must be assigned to different FUs. There must also be a communication path from the FU that executes operation n0 to the FU that executes operation n1. These requirements can only be satisfied by assigning operation n0 to FU<sub>0</sub> and operation n1 to FU<sub>1</sub>.

This example illustrates that the assignment of operations is complicated by the use of an incomplete communication network in the processor. Besides that the assignment should be such that there is a communication path between the functional unit that produces a result and the functional unit that consumes this result, this communication path should also be available. The communication path should be available, that is, the same path should not be used for the transfer of another result in the same clock cycle.

In the case that more than one register file is applied in the data path then the intermediate results produced by a functional unit must also be assigned to a register file. A register file has a limited capacity determined by the number of register fields it contains. The register file assignment should be such that the data to be held in a file does not exceed its capacity. The register file assignment is usually a result of the assignment of the operations and vice versa. Therefore, these two problems are tightly interrelated.

Multi-casting allows a result of a functional unit to be stored in more than one register file. With multi-casting it is often possible to generate an optimal schedule despite the use of many small register files in the data path. Multi-casting complicates operation assignment, because the number of used register file write ports depends on the assignment of the operations. The in this thesis described assignment techniques are intended for processors that support multi-casting.

Loop folding [Lam88] [Goo89] - which is also known as loop pipelining, or software pipelining - is supported because time critical parts in signal processing application are often encoded as for-loops. In folded loops successive for-loop iterations are executed simultaneously such that more instruction level parallelism can be exploited. An important challenge for code-generators is that loop folding requires that the application can be represented in a cyclic data flow graph.

We assume an hierarchical data flow graph [KMN<sup>+</sup>92] as the intermediate representation of the application. Our techniques cover entire applications ranging over sets of basic blocks.

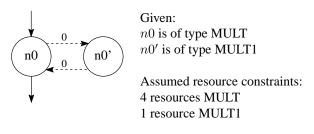

Another issue is that operations without a resource conflict may use the same hardware resource in the same cycle. This is called operation merging. An example of the absence of a resource conflict is established by memory read operations that access the same memory location. An often occurring case is a constant being fetched by multiple read operations from the same memory location.

## **1.4 Main contributions**

In this thesis constraint driven operation assignment techniques are described that effectively cope with multiple register files and an incomplete network in the data path of VLIW pro-

cessors. A tight coupling between operation assignment and scheduling (time assignment) is obtained by making use of constraint analysis techniques [EMAP<sup>+</sup>00].

We introduce in this thesis a conflict graph model of the assignment search-space. The consequences of an assignment decision are derived by pruning algorithms that operate on the conflict graph. Pruning of the conflict graph prevents unfortunate assignment decisions that could lead to a violation of resource or time constraints.

The assignment of the operations to the functional units was assumed as given, in previous work on constraint driven code generation for processors with an incomplete network [Tim95] [Mes01]. Given this assumption accurate bounds of the earliest as possible and the as late as possible start times of the operations could be derived with analysis techniques. These bounds are also needed to derive an operation assignment for which there is a schedule with a predefined schedule length or throughput. However, during the operation assignment process, some of the operations are assigned and others not. Given this partial assignment, similar analysis techniques are used to derived bounds on the start times of the operations. For run-time efficiency reasons we introduce operations of which the type can be adapted during the operation assignment process. After an operation is assigned, its type is adapted which reflects that this operation can only be executed on a specific functional unit.

A global write-back bus has been introduced in the network of the processor in order to guarantee that there exists at least one connection from an output of any functional unit to the input of any other functional unit. The bus eliminates the need for copy operations which simplifies the assignment problem drastically. The process of storing values in the background memory in case a register file capacity is exceeded is called "spilling". The global write-back bus also guarantees that every intermediate value can be spilled.

The global write-back bus also makes the assignment of operations in a basic block to a large extend independent of the assignment of the operations in surrounding basic blocks. The reason is that the bus always provides a communication path from a producing operation in a surrounding basic block to a consuming operation in the inner basic block.

A so called block operation has been introduced which models a scheduled basic block. Block operations are used during the assignment of operations that belong to a basic block that surrounds other basic blocks. Value lifetime serialization of block operations and ordinary operations is possible because the number of registers per register file that are used inside a scheduled basic block is included in a block operation.

Most of the operation assignment techniques that are presented in this thesis have been implemented in our research tool FACTS. Interfaces with the A|RT Designer VLIW-DSP development environment [Ade] have been accomplished. This has allowed us to verify the correctness of the assignment techniques and has enabled the evaluation of the assignment techniques on industrially relevant examples.

## **1.5 Related work**

A number of combined operation assignment and scheduling techniques are described in literature. An technique often used is list scheduling [Muc97] in which a priority function is used to select an operation to be assigned to a functional unit and a clock cycle. Sometimes "un-scheduling" of operations is applied [Goo89]. Close to optimal results are reported for processor architectures with a regular data path and an orthogonal instruction encoding. Contrarily a poor schedule quality is reported [Leu97] for processors with irregular data paths or a non-orthogonal instruction encoding.

Other assignment and scheduling techniques have been developed that generate high quality code at the expense of long compilation times. Examples are [HD98] which uses branch and bound techniques, [WLH00] which transforms the scheduling in an integer linear programming formulation, [Bea91] which solves the scheduling problem by means of genetic algorithms and [GFO92] which employs simulated annealing. Due to their time complexity, these techniques cannot ensure optimality given a limited time budget, and are only applicable to small code fragments and situations where long compilation times are acceptable.

The assignment technique described in this thesis is intended for VLIW processors with an orthogonal instruction set and almost homogeneous data path. In a homogeneous data path all functional units support the same data types. The described assignment techniques are intended for processors with more than one register file and an incomplete communication network.

Rather than optimizing cost according to a cost function, our assignment technique tries to satisfy the constraints imposed by a completely specified data path and the specified timing constraints. The technique searches for an assignment of operations that satisfies these constraints. The search-space is reduced by applying pruning algorithms that eliminate infeasible cases. This makes it possible to derive an assignment and a schedule or to detect infeasibility for DFG instances of a reasonable size (< 100 operations) and data paths with up to 50 FUs in typically less than a minute compilation time.

A difference with the operation assignment techniques described in the literature as compared to our techniques is that most other techniques insert so-called copy operations into the DFG. Copy operations are used to copy a value from a register file into another register file such that it is accessible by the appropriate functional unit. Usually the data path is designed in such a way that a valid mapping of the DFG can always be obtained by insertion of copy operations into the DFG. A disadvantage of the use of copy operations is that they can introduce a significant number of additional cycles to execute the application on a processor with multiple registers files compared to a processor with a single register file. It is also a difficult problem to decide during code generation where to insert copy operations into the DFG such that the performance penalty is minimized.

Our operation assignment techniques exploit multi-casting. Multi-casting implies storing of an intermediate value produced by a functional unit in more than one register file simultaneously. By making use of multi-casting there is usually hardly any performance penalty for the use of multiple register files in the processor. Also important is that the DFG does not change during operation assignment if multi-casting is applied. This enables the use of powerful assignment search-space pruning algorithms. It also enables a computationally efficient incremental update of the schedule search-space.

Table 1.3 gives an overview of relevant properties of the assignment techniques for VLIW processors as described in the literature. The name of the first author of the article is in the first column. In the second column it is indicated whether assignment is done in an independent pre-processing step before scheduling (Y) or integrated with scheduling (N). A disadvantage of an independent pre-processing step is that the effect of the assignment of operations on the schedule cannot be taken into account, a situation that is avoided with our techniques. The third column contains an 'Y' if the technique is able to insert copy operations in the DFG. Some evidence is provided in Chapter 2 that copy operations typically impair the quality of the schedule. If the technique is intended for loops, an 'Y' can be found in the fourth column. The fifth column contains an 'Y' if the assignment technique takes the interconnect in the data path of the processor into account. Overall, a 'N' is preferable in column 2 and 3, while a 'Y' is the entry to be preferred in columns 4 and 5.

| Author           | Pre-  | Insert    | Loops | Inter- |

|------------------|-------|-----------|-------|--------|

|                  | proc. | copy ops. |       | con.   |

| Mattson [Ban98]  | N     | Y         | Y     | N      |

| Banerjia [Ban98] | N     | Y         | N     | Y      |

| Bashford [BL99]  | N     | Y         | N     | Y      |

| Desoli [Des98]   | Y     | Y         | N     | N      |

| Ellis [Ell86]    | Y     | Y         | Y     | N      |

| Kock [Koc95]     | Y     | Y         | Y     | Y      |

| Nystorm [NE98]   | Y     | Y         | Y     | Y      |

| this work        | N     | N         | Y     | Y      |

Table 1.3: Characteristics of the operation assignment technique.

This thesis describes operation assignment techniques which make use of constraint analysis. Therefore, the techniques match seamlessly with the other constraint analysis based code generation techniques [EMAP<sup>+</sup>00] which are implemented in our research tool FACTS. The use of constraint analysis distinguishes this assignment technique from the operation assignment techniques described in the literature. The premise is that with constraint analysis, high quality schedules can be generated for processors that can execute many (> 10) operations in parallel. The data paths of these processors may contain many small register files and a sparsely connected network.

Processors with these characteristics are difficult compiler targets for which, as far as we know, all other code generation techniques often produce inferior schedules. However, the attractiveness of these processors is their superior power-efficiency.

Our code generation techniques can be re-targeted such that their effectiveness can be easily evaluated for a variety of processors. Retargetability requires that the techniques are, to a large extend, processor independent. Because the code generation techniques are intended for DSP processors they should support complex operations which are operations with more than two inputs and one output and can have several (pipeline) registers. An example of a complex operation is the Multiply ACcumulate (MAC) operation. This operation has 3 inputs

of which one input is typically sampled one cycle after the other two. The accumulation register can be considered as holding the state of the MAC-unit.

The described assignment techniques are intended to be applied on loops of which the schedule has a large impact on the performance. Loop folding is applied to obtain an increase in parallelism and performance at the cost of a slight increase in code size.

## **1.6** Thesis organisation

This thesis is organized as follows. Operation assignment implies that the operations of a data flow graph are assigned to functional units in the processor. The data flow graph and the target processors are defined in Chapter 2. In the same section the operation assignment problem is formulated. The data flow graph and a description of the target processor are the inputs of the code generator. The tasks performed by the code generation are described in Chapter 3. These code generation tasks are based on the constraint analysis strategy. This strategy requires that all possible assignments as well as the constraints are modeled in a representation which is called the "assignment search-space". The assignment search-space is described in Chapter 4. It is pruned with the rules described in Chapter 5. Pruning prevents decisions that lead to infeasibility and provides this way a kind of look-ahead. Multi-casting is a very efficient way to distribute intermediate results into more than one register file. This essential feature of the presented operation assignment techniques is described in Chapter 6. How hierarchical dataflow graphs and merging of operations is supported is described in Chapter 7. These features make it possible to test the operation assignment techniques on processors and hierarchical data flow graphs generated with the A|RT-designer tool-suite. The quantitative results obtained in this environment are presented in Chapter 8. Finally, conclusions are drawn in Chapter 9.

## **Chapter 2**

# **Inputs of the Code Generator**

The inputs of the retargetable code generator are the intermediate representation of the application, a description of the data path of the target VLIW processor and the timing constraints. These three inputs are defined more precisely in this chapter.

The organization of this chapter is as follows. In Section 2.1 the characteristics of the class of target VLIW-processors dealt with in this thesis are described. Section 2.2 describes the intermediate representation of the application that will be mapped on the VLIW processor. Section 2.3 describes the timing constraint which can be specified by the user or derived automatically. Given the description of the inputs of the code generator the addressed operation assignment problem is restated in Section 2.4.

## 2.1 Target processor

The characteristics of the VLIW-processors, for which our operation assignment techniques are intended, are described in this section. The organization of this section is as follows. First, the characteristics of the processor's data path are given in the form of a data path template. This is followed by the motivation of the choice for processors with a distributed register file architecture. Then the connection network of the processor is defined. Finally, the applied instruction encoding is described.

#### **2.1.1 Data path template**

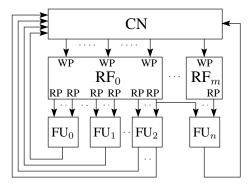

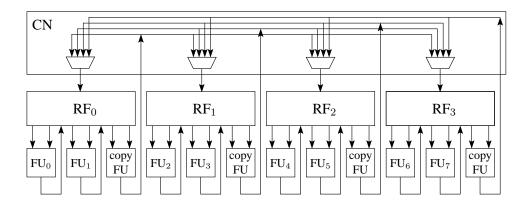

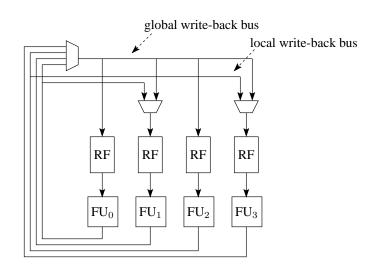

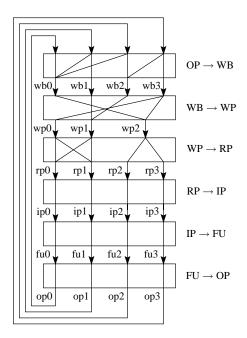

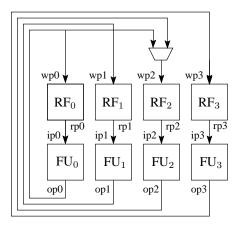

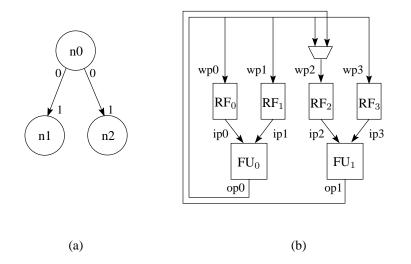

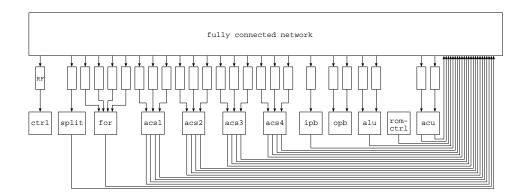

The template of the data path of the target VLIW processors is shown in Figure 2.1. Processors that adhere to this template have the following characteristics:

• Multiple Register Files (RFs). These register files can have more than one Write Port (WP) and more than one Read Port (RP),

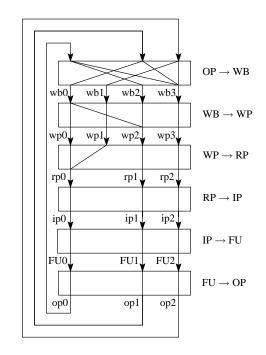

Figure 2.1: VLIW-processor data path template.

- Multiple Functional Units (FUs). These functional units can differ in the type of the operations that they can execute. Examples of operation types are addition, multiplication and memory load/store,

- A Connection Network (CN) between the outputs of the functional units and the write ports of the register files. This connection network could be incomplete and may contain shared busses. An example of a shared bus is the so-called "global communication bus" which will be introduced in Section 3.2.1,

- An orthogonal instruction encoding. An instruction encoding is orthogonal if the encoding of the instructions allows all combinations of operations to be executed in parallel [Wul81].

The data path template does not prescribe the register file architecture nor does it specify the internals of the connection network or the instruction encoding. The next subsection describe the register file architecture, connection network and the instruction encoding scheme for which our operation assignment technique is intended.

### 2.1.2 Register file architecture

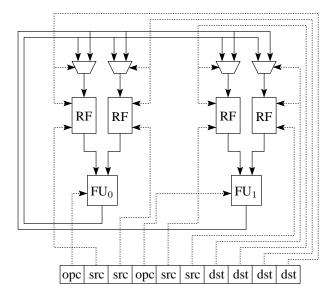

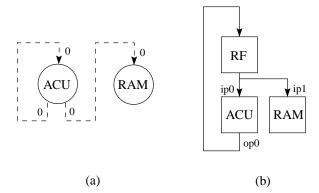

From the data path template described in the previous section, processors with a central, a clustered and a distributed register file architecture can be derived. In this section we motivate the distributed register file architecture as being the most suitable architecture for our objectives.

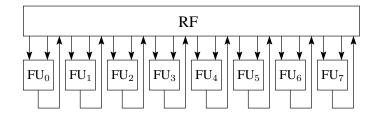

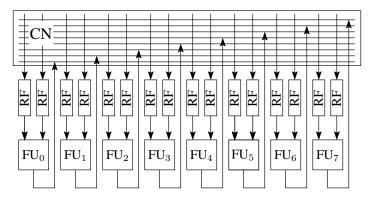

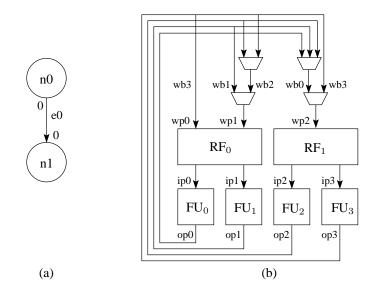

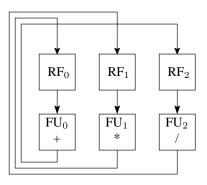

For a processor with a central register file (see Figure 2.2) operation assignment is almost trivial because every functional unit can access all register fields in the central register file. A drawback of processors with a central register file is however the severely limited scalability of the data path of such a processor. The reason is that if the number of functional units in the data path is increased, in order to increase the peak performance of the processor, then the number of register file ports must be increased. It is likely that the number of intermediate

Figure 2.2: A VLIW-processor data path instance with a central register file architecture.

values that must be stored in the register file will also increase. Therefore, the number of register fields in the register file must be increased. In each register field an intermediate value can be stored. A larger number of ports and fields makes the register file slower and decreases its power-efficiency [RDK<sup>+</sup>00]. Therefore, it is likely that additional functional units in the data path reduce the power-efficiency and the maximal clock frequency of a processor with a central register file. A reduction of the clock frequency decreases the processors performance and makes the added functional units less effective.

This is confirmed by the results of our own experiments which are shown in Table 2.1. This table presents the critical path length and the logic cell area obtained with logic synthesis of register fields of 32 bits in an CMOS  $0.18 \ \mu m$  technology at 1.5V and 125  $C^{\circ}$ . Given that the total number of registers in the processor is kept the same, these experiments confirm that it is likely that the use of register files with a larger number of ports will have a negative effect on the processor's clock frequency. The reduction in clock frequency becomes more significant if it is taken into account that the actual critical path length after layout is approximately twice as long. This increase in critical path length is due the fact that the estimate of the critical path length made by the synthesis tool is based on a typical wire density in standard cell blocks while the wire density in register files is typically much higher. If we assume the validity of the rule of thumb that the power dissipation is proportional with the area, then the results also indicate that the power-efficiency of the processors is reduced if the number of register file ports is increased.

| [ | data ports | register    | critical path | logic cell area | total logic cell area |

|---|------------|-------------|---------------|-----------------|-----------------------|

|   |            | fields/file |               |                 | (32 fields)           |

|   |            |             | ns            | $\mu m^2$       | $\mu m^2$             |

| ĺ | 2          | 4           | 4.5           | 12550           | 100400                |

| ĺ | 4          | 8           | 4.3           | 39326           | 157304                |

| Ī | 8          | 16          | 7.0           | 122065          | 244130                |

| Ī | 16         | 32          | 8.3           | 205005          | 205005                |

Table 2.1: Characteristics of synthesized register files with 32 bit/field in 0.18  $\mu$ m CMOS.

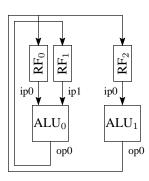

Multiple register files are applied in processors with a clustered register file architecture (see Figure 2.3) in order to improve the scalability of the data path. In such an architecture a register file together with the functional units that can read input data from this file and can

Figure 2.3: A VLIW-processor data path instance with a clustered register file architecture.

Figure 2.4: A VLIW-processor data path instance with a distributed register file architecture.

write the results to this file is called a cluster. The communication of data between clusters is performed by copy operations that are executed on the copy functional units which are indicated as "copy FU" in Figure 2.3.

A major disadvantage of the clustered register file architecture, compared to a processor with the same functional units but a central register file, is the performance loss caused by the copy operations. The performance loss reported by Faraboschi et.al. [FDF98] is 15-20% in terms of clock cycles for a data path with 2 clusters and 25-30% in terms of clock cycles for a data path with 4 clusters. Similar results are reported by Gageldonk [Gag01]. These results were obtained for processors with a sufficient number of fields in the register files and a modest utilization of the copy units. Therefore, these results indicate that the performance loss is primarily caused by the latency of the copy operations. Because the performance loss increases significantly with the number of clusters we conclude that the scalability of the data path of a clustered architecture is limited.

A processor with a distributed register file architecture (see Figure 2.4) can become more

favorable in the case a large number of functional units is applied in the data path of the processor. By applying multi-casting it is possible to store an intermediate value produced by a functional unit in more than one register file without any additional operations for communication purposes. A performance loss of only 2% for processors with a distributed register file architecture that support multi-casting compared to a processor with a central register file is reported by Mattson et.al. [MDR<sup>+</sup>00]. We have obtained similar results with A|RT designer.

Also the width of the VLIW instruction word is affected by the register file architecture of the processor. The reason is that, with a central register file, every functional unit can access all the registers in the processor. Therefore, the number of bits per source or destination field in the VLIW instruction word equals  $\lceil 2log(fields) \rceil$ . However, the number of fields per file tend to be much smaller in a processor with a distributed register file architecture and thus also the number of bits per source and destination field. This reduction in bits is partially compensated by the fact that besides the register field also the producing functional unit output port and the destination register file must be specified in the destination field. If the connection network in the data path is sparsely connected then only a few functional unit output ports are connected to a register file write port. In this case only a few additional bits are needed in the destination field to specify one of these ports. For these processors it is plausible that the instruction width is smaller than for a processor with a central register file. This is supported by the figures in Table 2.2. This table contains the instruction width and the number of instructions for three applications that are mapped on an application specific VLIW processors with a central or a distributed register file architecture. The same functional units are applied in the processors with a central register file as in the processors with the distributed register file architecture. The processors were generated and programmed with A RT designer.

| design      | centr                 | al RF        | distribu     | ited RF      |

|-------------|-----------------------|--------------|--------------|--------------|

|             | instruction number of |              | instruction  | number of    |

|             | width (bits)          | instructions | width (bits) | instructions |

| fir         | 37                    | 19           | 30           | 16           |

| fft         | 72                    | 61           | 64           | 60           |

| ray-tracing | 619                   | 50           | 420          | 51           |

Table 2.2: Instruction code size of VLIW processors with a central and a distributed register file architecture.

It is likely that the instruction word size for a distributed register file architecture with a dedicated register file per input port is sub-optimal. The reason is that there are approximately twice the number of write ports as there are functional unit output ports in this architecture. A reduction in the number of write ports could possibly reduce the number of destinations fields in the VLIW instruction word. A reduction of the number of write ports can be achieved by merging several register files in one register file.

Our operation assignment techniques are intended for processors with a distributed register architecture because multi-casting can be relatively easily supported by our constraint analysis based code generation techniques while insertion of copy operation seems to be virtually impossible. Also the data path of a processors with a distributed register file architecture scales well and the usage of a large number of small register file reduces the instruction word

Figure 2.5: Generic network model of the data path template of Figure 2.1.

width and the code size.

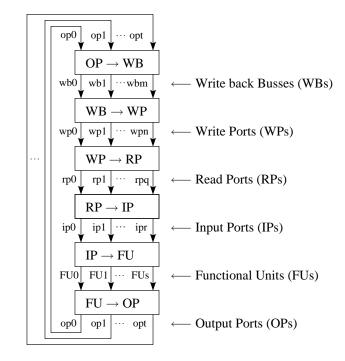

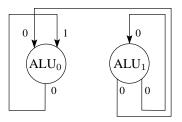

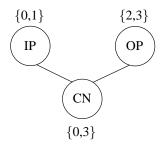

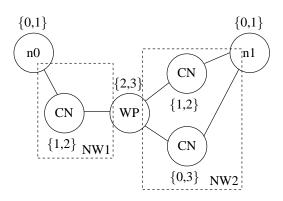

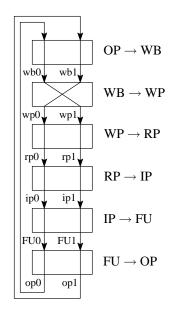

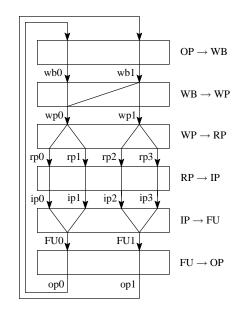

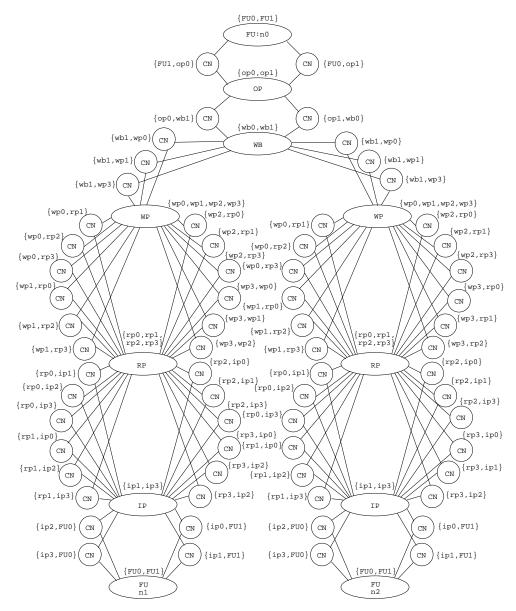

#### 2.1.3 Network model of the data path

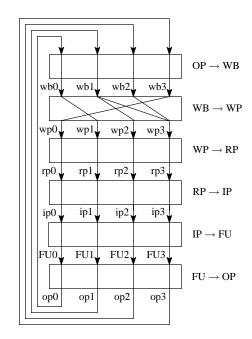

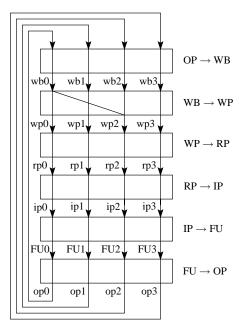

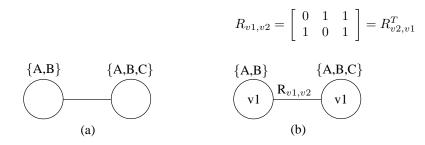

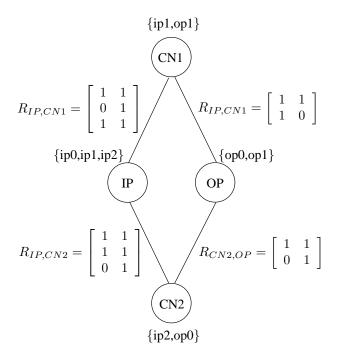

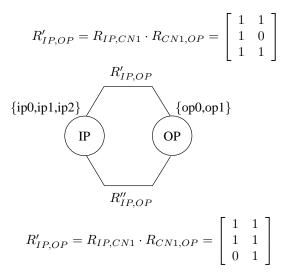

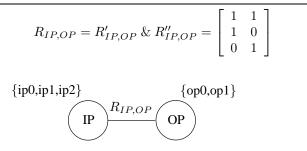

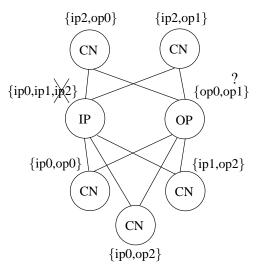

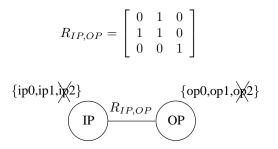

There can be several communication paths in a processor from an output port of a functional unit, to an input port of a functional unit, through the connection network and a register file. All possible paths through the data path template of Figure 2.1 are captured in a network model which is shown in Figure 2.5. In Chapter 4 it is described how the assignment search-space is constructed by making use of this network model.

The network model of Figure 2.5 contains several sub-networks which are represented by boxes. These sub-networks are non-blocking in the sense of [Clo53]. That is, simultaneous data transport through this network from idle network input ports to idle network output ports can be performed if a connection can been made between these ports in the network. Within these networks not all possible connections may actually exist.

Every sub-network output port is in Figure 2.5 connected to one input port of another subnetwork. Also, every sub-network input port is connected to one network output port. The input port of one sub-network has the same label as the output port of another sub-network to which it is connected.

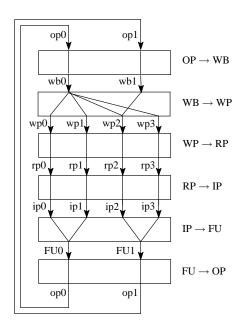

Figure 2.6: Processor data path (a) and corresponding network model (b).

An example of a network model of a data path is shown in Figure 2.6. This example illustrates how the shared bus wb0 can be included in the network model. This is a shared bus inside the connection network of the processor. Figure 2.6 also illustrates the possibility that more than one functional unit can obtain it's input data via the same register file read port.

The sub-network "WP $\rightarrow$ RP" is incomplete if more than one register file is applied in the data path. Therefore routing problems and network port conflicts should be taken into account during code generation even if all other networks are fully connected. These routing and port conflicts complicate operation assignment.

#### 2.1.4 Instruction encoding

In this section we introduce "data-stationary instruction encoding" and "time-stationary instruction encoding".

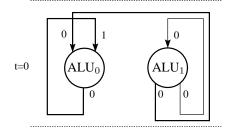

In the data-stationary encoding [LBSL94] every instruction controls a complete sequence of operations that have to be executed on a specific data item, as it traverses the data pipeline. To

Figure 2.7: Control of the data path by the fields in a data-stationary encoded instruction.

achieve this, the opcode, which specifies the operation type to be executed, and the register source and destination addresses are located in the same instruction word. Once the instruction word has been fetched from program memory and decoded, the controller makes sure that the destination addresses become available in the correct clock cycle. Therefore, if an operation has a latency of two cycles then the destination address needs to be available one clock cycle later.

The data path and instruction word of a processor that uses a data stationary instruction encoding is shown in Figure 2.7. The dashed lines in these figures indicate how the bits in the fields are connected to the data path elements. In the destination field the destination register and the destination register file are specified. The content of this field is send to a shift register. If the latency of the functional unit is N cycles then the destination is delayed N-1 cycles by the shift register. After the destination field is delayed, it is send to the select units (S). These units determine whether the result should be stored in the register file and extract from the destination the control bits for the switches in the network as well a the destination register field.

An important disadvantage of the data-stationary instruction-encoding is that no efficient encoding scheme is known that supports multi-casting. The reason is that multi-casting requires the option to specify a variable number of destination addresses per opcode. If the length of the instruction word is fixed then the worst-case number of destinations, which equals the number of register file write ports in the data path, must be specified for every opcode. This increases the instruction word size more than necessary because in the typical case there is only one destination per opcode. For the same reason it is virtually impossible to encode efficiently, operations that consume in a time multiplexed fashion several input values via the same input port or that produce multiple output values. Modeling of this complex in-

Figure 2.8: Control of the data path by the fields of a time-stationary encoded instruction.

put/output behavior with ordinary operation such that traditional scheduling techniques can be applied, is described in [BWB00]. Another drawback of the data-stationary instructionencoding is that operations with a long latency require a lot of memory bits in the data path because the destinations are needed several cycles after the start of the operation and are delayed by a shift register in the processor. Multi-casting and operations with complex timeshapes and multiple destinations can be efficiently supported by applying a time-stationary instruction encoding [GPL<sup>+</sup>97]. This encoding scheme is described below.

Figure 2.8 shows how the data path is controlled by the fields of a time-stationary encoded instruction. The opcode (opc) field in the instruction determines the operation type that is executed on a functional unit. The source (src) fields determine the registers, from which the operands are retrieved. A destination field (dst) is associated with every register file write port. The destination field determines in which register a result is stored and from which functional unit output port this result is read. The dashed lines in Figure 2.8 indicate which data path elements are controlled by a field in the VLIW instruction. The bits in a field of a VLIW instruction word control these data path elements directly. Directly means that only wires are used to connect the bits to the right data path elements and that the content of the fields are not temporarily stored. Therefore, if an operation has a latency larger than one then the register destination is specified in a instruction word different from the one holding the corresponding opcode.

For time-stationary instruction encoded processors it is highly desirable that the scheduler schedules beyond *basic block* boundaries. A basic block is a maximal sequence of instructions that can be entered only at the first of them and exited only from the last of them [Muc97]. Without scheduling beyond basic block boundaries the pipeline registers

in the functional units must be empty at the end of a basic block. With deeply pipelined functional units this could lead to many extra instructions at the end of a basic block.

The operation assignment techniques described in this report are able to exploit multi-casting and are therefore intended for time-stationary encoded processors with a distributed register file architecture. The performance and code size penalty due to the time-stationary instruction encoding is in our case negligible because most of the functional units in the processors that we target are not deeply pipelined. Another reason is that the time critical for-loops in DSP applications are typically folded which is a form of scheduling of operations beyond basic block boundaries.

A data transport from a functional unit output port to a register file write port is encoded with a mix of bus-programming and socket-programming [Cor95]. Per write port it is encoded from which bus the data should be read (socket-programming) and per bus it is encoded from which functional unit output port the data should be read (bus-programming).

## 2.2 Intermediate representation of the application program

The second input of the code generator is a representation of the application program. This representation describes one basic block, which is a fragment of the application, in the form of a data flow graph. The complete application is represented in a hierarchical data flow graph. Executable code for complete applications is generated, by applying the operation assignment and scheduling techniques on all the basic blocks in the hierarchical data flow graph.

The organization of this section is as follows. First, the characteristics of the data flow graph representation of a basic block are described. Then, the characteristics of a flow graph and a hierarchical data flow graph representation of an application are described. For the case of processors with multiple register files it is motivated why a hierarchical data flow graph representation is likely to be a more suitable then a flow graph.

### 2.2.1 Data flow graph

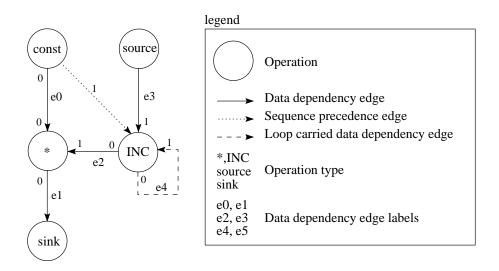

Operation assignment is the assignment of operations in a data flow graph to resources in the processor. The data flow graph [KM92] represents the operations and the data and sequence dependencies of a basic block. Our data flow graph is defined as follows:

#### **Definition 2.1 (Data Flow Graph.)**

The tuple  $(V, E_d \cup E_l \cup E_s, w_e, id, t_i, t_o)$  defines a Data Flow Graph (DFG), where

- V is the set of nodes (operations),

- $E_d \subseteq V \times V$  is the set of data dependency edges,

- $E_l \subseteq V \times V$  is the set of loop carried data dependency edges,

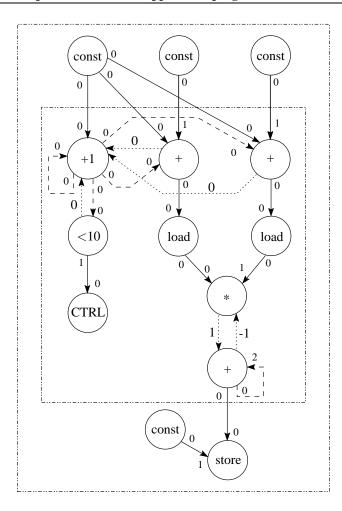

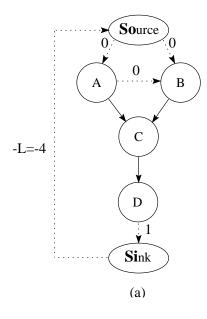

Figure 2.9: An arbitrary Data Flow Graph (DFG).

- $E_s \subseteq V \times V$  is the set of sequence precedence edges,

- $w_e : E_s \cup E_d \cup E_l \to \mathbb{Z}$  is a function describing the timing delay (in clock cycles) associated with each sequence precedence edge and data dependency edge. The timing delay  $w_e$  associated with an edge  $e \in E_d$  is 1 and the timing delay  $w_e$  associated with an edge  $e \in E_d$  is 0.

- id: E<sub>s</sub> ∪ E<sub>d</sub> ∪ E<sub>l</sub> → {0, 1} is a function describing the iteration distance. The iteration distance of a loop carried data dependency edge e ∈ E<sub>l</sub> is 1. The iteration distance of the other edges is 0,

- $t_i: E_d \to \mathbb{N}$  is a function describing the operation input port number of the succeeding node, and

- $t_o: E_d \to \mathbb{N}$  is a function describing the operation ouput port number of the preceding node.

A DFG example is shown in Figure 2.9. An operation in this DFG has a type and can be executed on data path resources that support this type. Examples of data path resources are functional units and network ports. When an operation is executed it uses a data path resource.

Operations in a basic block can consume values produced by operations outside the basic block. The operations outside the basic block are represented in the DFG by source operations. Conversely, a value produced in a basic block can be consumed by an operation that does not belong to the basic block. These consuming operations are represented in the DFG by sink operations.

The data dependency edges in the DFG specify that an operation can only be executed after its input values are produced. Data edges might be labeled with a unique label. These labels are used to refer to a specific data edge. The input and output port associated with a data dependency edge are respectively specified at the head and the tail of the edge. Source and sink operations have dummy ports. All input and output ports, except dummy ports, are respectively mapped on input and output ports of a functional unit. The convention is used that operation input port 0 is mapped on the left most functional unit input port. Operation input port 1 is mapped on the next functional unit input port to the right, and so on. Operation output ports are mapped in a similar way to functional unit output ports. If the mapping of operation ports is irrelevant or trivial for a problem that is discussed then the port labels are left implicit.

If the DFG is executed repeatedly then a value produced in one iteration can be consumed by an operation executed in the next iteration. This type of data dependency is called a loop carried data dependency and is represented in Figure 2.9 with a dashed edge.

Multiple data precedence edges leave the same output port of an operation if this operation produces a result that is consumed by multiple operations. However, typically only one data edge enters an input port of an operation. Only in the case that the execution of producing operations is mutually exclusive then the data dependency edges that leave these mutual exclusive operations can enter the same input port of an operation.

Sequence precedence edges are depicted in Figure 2.9 with dotted edges. A timing delay  $w_e$  is specified in the middle of a sequence precedence edge.

A data dependency edge has a weigth of 1. Operations with a latency larger than one clock cycle are modelled as a chain of operations in the DFG. Sequence precedence edges are used to enforce that operations in the chain must start in consecutive clock cycles. This way of modeling typically results in modest increase of the run-time of the scheduler.

The iteration distance id defines a weight of an edge in multiples of the initiation interval (II) of the schedule. The total weight of an edge  $e \in E_s \cup E_d \cup E_l$  is  $w(e) = -II \times id(e) + w_e(e)$ . The iteration distance id(e) is 1 for loop carried data dependency edges and 0 for the other edges.

The task of the scheduler is to assign each operation  $v \in V$  a start time s(v). The start times are constrained by the available resources and the data dependencies and sequence precedences. A data dependency edge or sequence precedence edge  $(v_i, v_j)$  states that:

$$s(v_j) \ge s(v_i) + w(v_i, v_j) \tag{2.1}$$

The weight w of an edge can be negative. In this case equation 2.1 can be rewritten in the form of equation 2.2 to make the interpretation easier. Equation 2.2 states that if  $w(v_i, v_j) < 0$  then  $v_i$  may not start more than  $|w(v_i, v_j)|$  cycles after the start of  $s(v_j)$ . Negative sequence edges are used for example to model pipelined operations. An example of a pipelined operation is a multiply accumulate operation in which the addition must start one cycle after the multiplication. A fragment of a DFG with a multiply accumulate operation is shown in Figure 2.10.

Figure 2.10: A fragment of a DFG with a multiply accumulate operation.

$$s(v_i) \le s(v_j) + |w(v_i, v_j)|$$

if  $w(v_i, v_j) < 0$  (2.2)

Before we define the distance between two operation, the notion of a path is introduced:

#### **Definition 2.2 (Path)**

A path P of length d from operation  $v_i$  to operation  $v_j$  is a chain of precedences  $v_i \to v_k \to \dots \to v_l \to v_j$  that implies  $s(v_j) \ge s(v_i) + d$  with  $d = \sum_{e \in P} w(e)$ .

#### **Definition 2.3 (distance)**

The distance  $d(v_i, v_j) \in \mathbb{Z} \cup -\infty$  from operation  $v_i$  to  $v_j$  is the length of the longest path from  $v_i$  to  $v_j$ . If there is no path from  $v_i$  to  $v_j$  then the distance  $d(v_i, v_j) = -\infty$ . The distance  $d(v_i, v_j)$  is per definition 0.

### 2.2.2 Flow graph representations

Application programs can be represented in a flow graph [ASU86], in which edges indicate the flow of control and nodes represent basic blocks. In these graphs there is a directed edge from basic block B1 to block B2 if B2 can immediate follow B1 in some execution sequence, that is if:

- 1. there is a conditional or unconditional jump from the last statement of B1 to the first statement of B2, or

- 2. B2 immediate follows B1 in the order of the program, and B1 does not end in an unconditional jump.

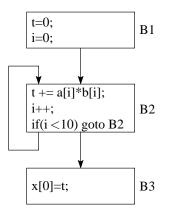

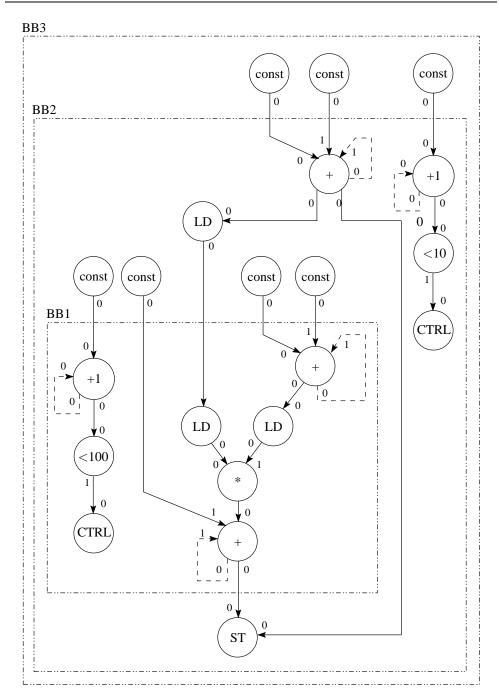

A C-source code fragment is shown in Figure 2.11. The corresponding flow graph is shown in Figure 2.12.

```

t=0;

for(i=0; i<10; i++){

t+=a[i]*b[i];

}

x[0]=t;

```

Figure 2.11: C-source code fragment.

The values that are alive at the end of a basic block are typically transferred into background memory. In order to reduce the number of store and corresponding load operations, it is possible to save some of the values in registers. Because these registers hold values across basic block boundaries they are called global registers and the values saved in these registers are called global values.

Figure 2.12: Flow graph of a C-source code fragment.

The assignment of a fixed number of global values to the global registers is typically performed by the compiler frontend. This approach has a couple of drawbacks. First, the available number of global registers is not always the best. It can, for example, be desirable to use fewer global registers because a larger number of registers is required to hold the local intermediate values of the basic block. Another drawback of this approach is that unfortunate global variable assignments made by the compiler frontend could lead to the situation that global values must first be copied into another register file before they can be accessed by the appropriate functional unit. It is likely that these copies will significantly impair the schedule quality in the case of processors with a large number of register files.

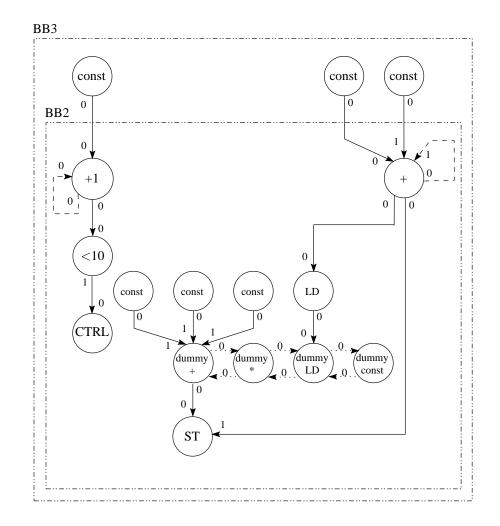

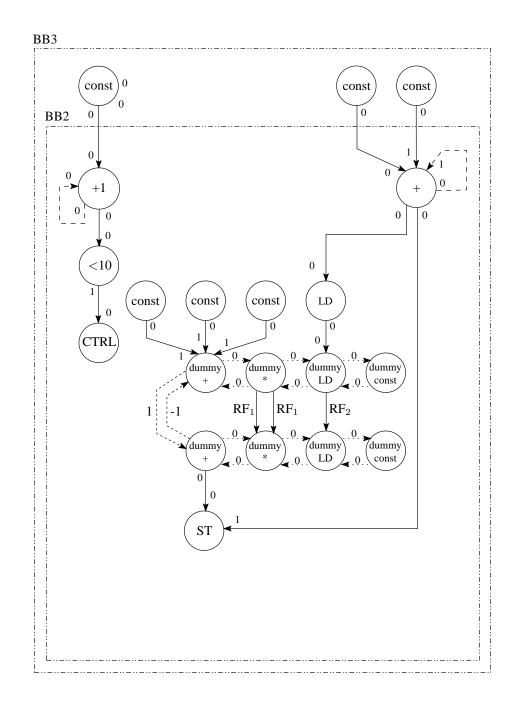

An alternative representation of an application is a hierarchical data flow graph [Lam88]. In this hierarchical data flow graph, control-flow primitives such as branching and iteration are modeled by means of the hierarchy [Mic94]. The edges in such a graph represent data dependencies or sequence precedence constraints and the nodes represent ordinary operations or block operations. Block operations can be expanded in operations and precedence edges.

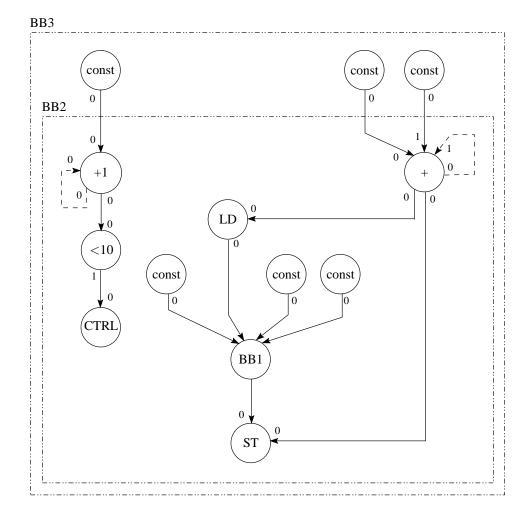

Figure 2.13: Hierarchical data flow graph of the C-source code fragment in Figure 2.11.

A hierarchical data flow graph can be scheduled by making use of hierarchical reduction [Lam88]. In this technique, the operations in the deepest nested block operation are scheduled first. Then this block operation is scheduled together with the other operations of the surrounding block operation. This is repeated until all operations in the block operations are scheduled.

An example of a hierarchical data flow graph is shown in Figure 2.13. This graph is the intermediate representation of the C-source code fragment shown in Figure 2.11. In this graph the comparison operation produces an output value which signals the controller whether the loop should be terminated.

During the hierarchical reduction all values are implicitly assigned to register files during operation assignment. There is no difference between values that are local to one basic block

and values that cross basic block boundaries. The operation assignment routines take the communication paths in the network into account and can be made aware of the register file pressure. Also complete basic blocks, which are represented as block operations, and other operations can be serialized [Mes01] in order to adapt the lifetimes of variables such that the values that are alive across basic blocks fit in the register files. Therefore hierarchical data flow graphs seem to be a more suitable intermediate representation for our purpose.

# 2.3 Timing constraints

The timing constraints are specified as the latency and the initiation interval of the schedule. The Latency (L) of a schedule is the number of clock cycles after which all the operations in the DFG are executed. For loops an initiation interval can be specified. The Initiation Interval (II) of a schedule is the number of clock cycles after which the next execution of the same DFG is started. If II < L then the loop is folded. The user can specify these timing constraints or a shell around the code generator can be used to determine sharp lower bounds of these timing constraints.

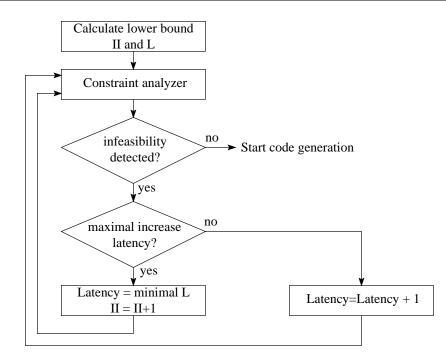

The steps performed in this shell, are shown in Figure 2.14. In the first step, a lower-bound estimate of the initiation interval is calculated. A lower bound on II can be derived from the number of available resources of a certain type and the number of operations of the same type in the DFG. This resource lower bound  $II_{res}$  ignores the data dependencies and sequence precedences in the DFG. Another lower bound on II can be derived from the length of the loops in the DFG. This lower bound  $II_{loop}$  ignores the number of available resources. A more accurate lower bound on II is the maximum of  $II_{res}$  and  $II_{loop}$ , so

$$\mathbf{II} = max(\mathbf{II}_{res}, \mathbf{II}_{loop}) \tag{2.3}$$

With equation 2.4 the resource lower bound is derived. In this equation rsu is the number of operations of type  $\tau_i$  and rsa the number of available resources of that type.

$$\mathbf{II}_{res} = \max_{\tau_i \in \tau} \left\lceil \frac{\operatorname{rsu}(\tau_i)}{\operatorname{rsa}(\tau_i)} \right\rceil$$

(2.4)

According to definition 2.2 implies a path P in the DFG from operation  $v_i$  to operation  $v_j$  that:

$$s(v_j) \ge s(v_i) + \sum_{e \in P} w_e(e) - \operatorname{II} \times \sum_{e \in P} \operatorname{id}(e)$$

(2.5)

For a loop c in the DFG, for which  $s(v_i) = s(v_i)$ , equation 2.5 can be rewritten as:

$$II \ge \frac{\sum_{e \in c} w_e(e)}{\sum_{e \in c} id(e)}$$

(2.6)

Figure 2.14: Procedure to determine sharp lower bounds for the Latency (L) and Initiation Interval (II) constraint of the schedule.

Because this must hold for every loop  $c \in C$  in the DFG, a lower bound on II due to loops in the DFG becomes:

$$\mathbf{II}_{loop} = \max_{c \in C} \left\lceil \frac{\sum_{e \in c} w_e(e)}{\sum_{e \in c} \mathrm{id}(e)} \right\rceil$$

(2.7)

The longest path in the DFG from which the loop carried data dependencies are removed is used as the lower bound on the latency of the schedule.

Given the initial timing constraints the schedule search-space is pruned by the constraint analyzer which is described in more detail in Section 3.1.1. If the schedule search-space is empty after pruning then infeasibility is reported and the latency constraint is increased with 1 cycle. If the latency constraint is increased a predefined number of times and still infeasibility is reported then the initiation interval is increased with 1 cycle and the latency constraint is reset to the longest path in the DFG. This process is repeated until constraint analysis stops reporting infeasibility. In this process the latency is increased before the initiation interval is increased because the initiation interval determines to a large extend the execution time of a folded loop.

During the process, which is described in the previous paragraph, the timing constraints are relaxed. Another approach would be to start from a situation with a feasible schedule and then tightening the timing constraints. This approach was not chosen because our benchmark

results indicate (see Chapter 8) that often solutions can be found close to the lower bound timing constraints. Therefore, it takes less compilation time when the search process is started from the lower bound timing constraints.

The lower bound timing constraints are derived given a DFG and a target processor. These lower bounds are used as initial timing constraints. In the case a schedule is found that respects these initial timing constraints, then this schedule is also an (performance wise) optimal schedule. However in the case the compiler frontend generates for the same C-program another DFG then it could be that for this DFG a schedule exists for even tighter timing constraints. Another example is that in the compiler frontend, the selection of the operation input ports is performed. If this input port selection is left undefined for commutative operations then this additional freedom could be exploited in order to obtain a better schedule. Our assignment techniques do not exploit this freedom.

# 2.4 Problem statement

Given the definition of the target processor and the intermediate representation of the application, the operation assignment problem can be stated as follows:

**Problem 1**: Given a DFG, find an assignment of operations to functional units and intermediate values to register files such that a schedule can be established which satisfies the specified initiation interval and latency constraints.

If the initiation interval is smaller than the latency then loop-folding should be applied. It is assumed that the assignment of operation ports to functional unit ports is specified beforehand. It is also assumed that the assignment of memory read and write operations to a memory is specified. Each memory is modeled as a functional unit in the data path. Scheduling of operations together with block operations should be possible. It is assumed that the VLIW-processors have a distributed register file architecture, a potentially incomplete communication network, and that they support multi-casting.

# **Chapter 3**

# **Code Generation by Traversing the Search-Space**

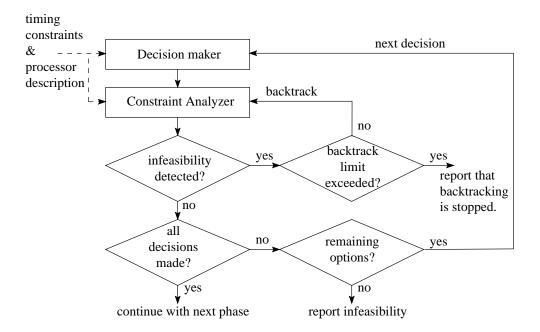

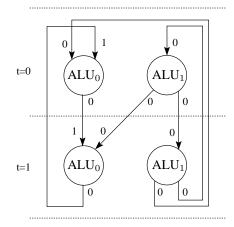

During code generation a DFG is mapped on the data path of a target VLIW processor. The code generation task is split is several subtasks which are performed after each other in order to obtain high quality schedules in a reasonable compilation time. These subtasks, which are also called phases in literature, are described in Section 3.1. The phases are mutually dependent, that is, decisions in one phase potentially affect the decisions in another phase. How dependencies between phases are handled, is described in Section 3.2. All code generation phases are based on constraint analysis. The basic principles of constraint analysis are described in more general terms in the last section of this chapter.

# **3.1** Code generation phases

Our code generator gets as input a DFG, an abstract description of the target processor and timing constraints and produces executable code (see Figure 1.1). The code generation task is partitioned in subtasks, which are called phases because they are successively executed. These subtasks are supposed to be easier to handle individually. This procedure should lead to a better result than solving the problem in one piece. In every phase, only one type of decision is made by an algorithm, which is special for this phase. An example of a decision type is the assignment of operations to functional units.

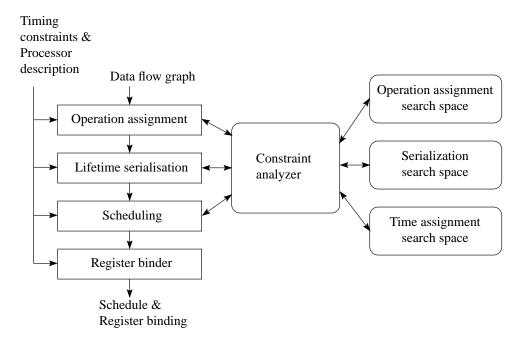

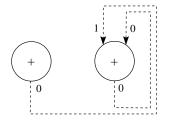

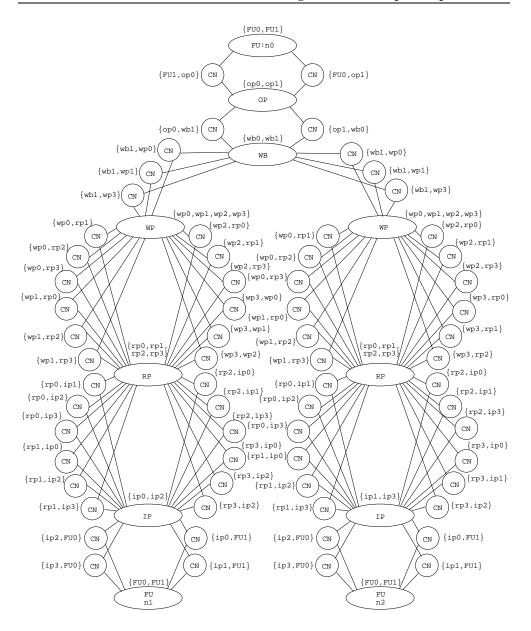

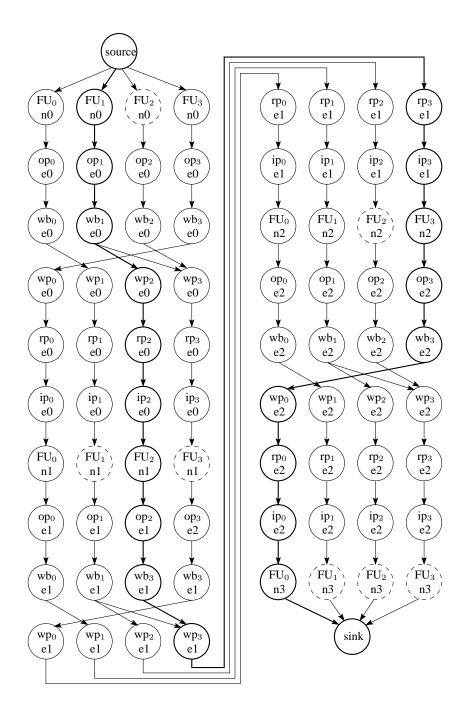

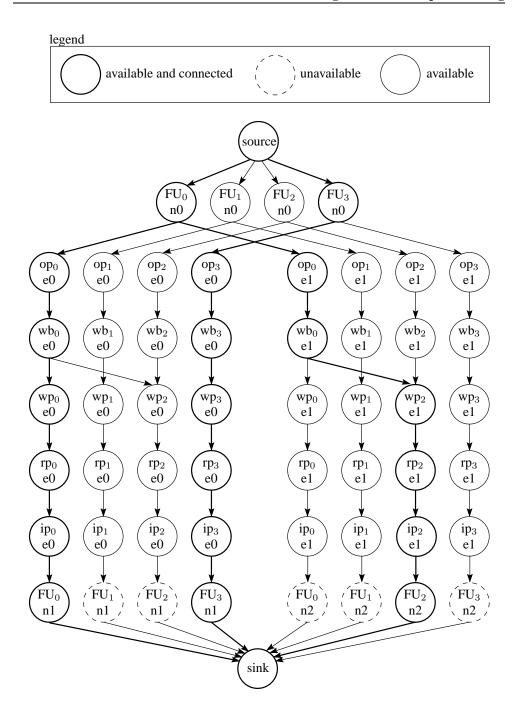

In the code generator there is an operation assignment phase, a value lifetime serialization phase, a scheduling phase, and finally a register binding phase (see Figure 3.1). During the operation assignment phase, operations are assigned to functional units. During the lifetime serialization phase, operations are ordered in time in such a way that a valid register binding exists after the scheduling phase. During the scheduling phase, the start times of operations are determined. After scheduling, the register binder selects a register for every intermediate value.

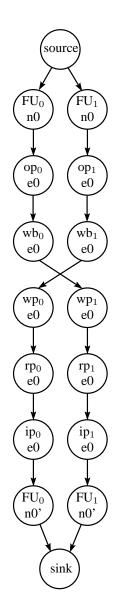

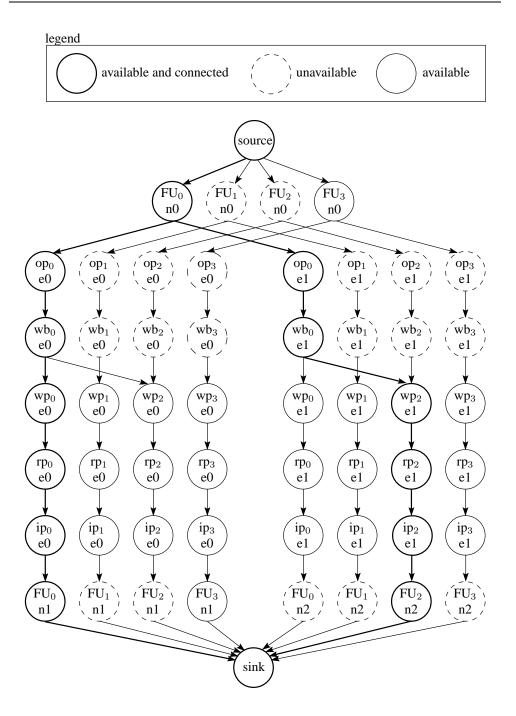

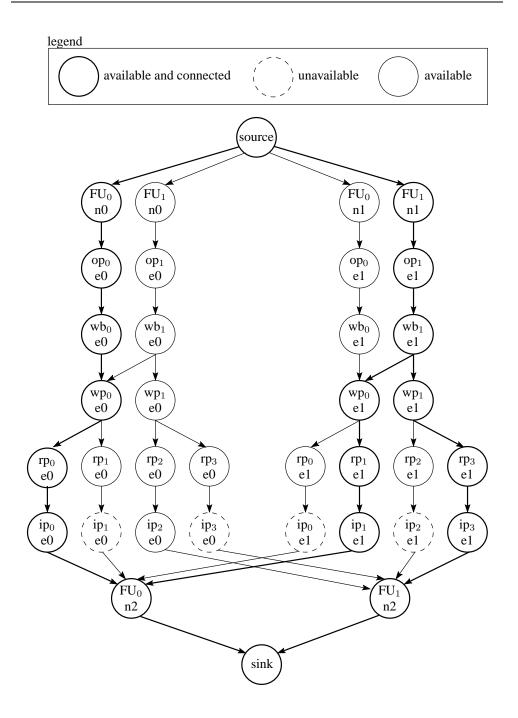

Figure 3.1: Code generation phases.