# **Delay-insensitive communication**

*Citation for published version (APA):* Schols, H. M. J. L. (1992). *Delay-insensitive communication*. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Mathematics and Computer Science]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR387170

DOI: 10.6100/IR387170

# Document status and date:

Published: 01/01/1992

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# Delay-insensitive Communication

Huub Schols

Copyright © Huub M.J.L. Schols, 1992

Copying without fee is permitted provided that the copies are not made or distributed for direct commercial advantage, and credit to the source is given. Abstracting with credit is permitted. To copy otherwise, or republish, requires written authorization by Huub M.J.L. Schols.

# Delay-insensitive Communication

# PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof. dr. J.H. van Lint, voor een commissie aangewezen door het College van Dekanen in het openbaar te verdedigen op woensdag 9 december 1992 om 14.00 uur

DOOR

Hubert Marie Jean Louis Schols

Geboren te Amby

# Dit proefschrift is goedgekeurd door de promotoren

prof. dr. M. Rem

en

prof. C.E. Molnar, Sc. D.

to my friends

If the car industry behaved like the computer industry over the last 30 years, a Rolls-Royce would cost \$5, get 300 miles per gallon, and blow up once a year killing all passengers inside.

origin unknown

# Acknowledgments

The author thanks the members of the Institute for Biomedical Computing of Washington University in St. Louis for their contributions to his understanding of the material in this monograph; in particular the intense and enthusiastic co-operation of Charles E. Molnar has sharpened many ideas and has been very stimulating during the development of the theory presented. Furthermore, the author gratefully acknowledges the discussions with and suggestions from Martin Rem, Ting-Pien Fang, Jan Tijmen Udding, Alain Martin, Jan van de Snepscheut, Jo Ebergen, Wilbert Körver, Tom Verhoeff, Frans Kruseman Aretz, and Cees Jan Koomen. Thanks also go to the members of the Department of Computer Science of Washington University, particularly Jerome R. Cox jr. and Takayuki (Dan) Kimura, to Alain Martin and his graduate students for their helpful criticisms and suggestions at several presentations of parts of this material, to Mohammed Gouda, and to the members of the Eindhoven VLSI club for their criticisms on this material. Furthermore, the author thanks Occo Nolf for pointing out many typographical errors in the final draft of this monograph.

Acknowledgments

# Contents

| A | ckno         | wledgements                           | i  |  |  |  |  |  |  |

|---|--------------|---------------------------------------|----|--|--|--|--|--|--|

| C | Contents     |                                       |    |  |  |  |  |  |  |

| 0 | Introduction |                                       |    |  |  |  |  |  |  |

|   | 0.0          | Synchronous and asynchronous          | 1  |  |  |  |  |  |  |

|   |              | 0.0.0 Asynchronous communication      | 3  |  |  |  |  |  |  |

|   |              | 0.0.1 Communication Model             | 4  |  |  |  |  |  |  |

|   |              | 0.0.2 Computation interference hazard | 4  |  |  |  |  |  |  |

|   | 0.1          | Subsequent chapters                   | 5  |  |  |  |  |  |  |

|   | 0.2          | Denotations in the English language   | 6  |  |  |  |  |  |  |

|   | 0.3          | Notions related to "asynchronous"     | 6  |  |  |  |  |  |  |

|   | 0.4          | Delay-insensitivity                   | 7  |  |  |  |  |  |  |

|   | 0.5          | Proofs                                | 7  |  |  |  |  |  |  |

| 1 | For          | Formalism and notation                |    |  |  |  |  |  |  |

|   | 1.0          | Sets                                  | 9  |  |  |  |  |  |  |

|   | 1.1          | Operators                             | 11 |  |  |  |  |  |  |

|   |              | 1.1.0 Priority of operators           | 11 |  |  |  |  |  |  |

|   | 1.2          | Quantification                        | 11 |  |  |  |  |  |  |

|   | 1.3          | Denotation of proofs                  | 12 |  |  |  |  |  |  |

|   | 1.4          | Trace theory.                         | 13 |  |  |  |  |  |  |

|   |              | 1.4.0 Basic notions of trace theory   | 14 |  |  |  |  |  |  |

|   |              |                                       | 17 |  |  |  |  |  |  |

|   |              | 1.4.2 State graphs                    | 20 |  |  |  |  |  |  |

|   |              |                                       | 22 |  |  |  |  |  |  |

|   |              |                                       | 22 |  |  |  |  |  |  |

|   |              |                                       | 23 |  |  |  |  |  |  |

|   |              |                                       | 25 |  |  |  |  |  |  |

## Contents

| 2 | Con | nmuni  | cation Model                                         | 27 |

|---|-----|--------|------------------------------------------------------|----|

|   | 2.0 | Defini | tion of Communication Model                          | 28 |

|   |     | 2.0.0  | Commports                                            | 28 |

|   |     | 2.0.1  | Comminsts and commsigs                               | 29 |

|   |     | 2.0.2  | Comminstorders and commsigorders                     | 30 |

|   |     | 2.0.3  | Iodirs and modules                                   | 32 |

|   |     | 2.0.4  | Opdirs and interconnections                          | 33 |

|   | 2.1 | Interp | retation of Communication Model                      | 34 |

|   |     | 2.1.0  | Commports                                            | 34 |

|   |     | 2.1.1  | Comminsts                                            | 35 |

|   |     | 2.1.2  | Comminstorders                                       | 35 |

|   |     | 2.1.3  | Modules                                              | 36 |

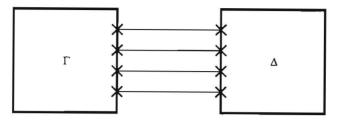

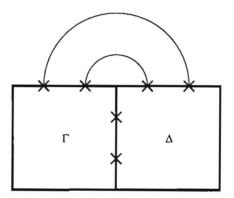

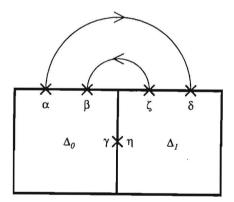

|   |     |        | 2.1.3.0 Connected modules                            | 38 |

|   |     | 2.1.4  | Commsigs                                             | 40 |

|   |     | 2.1.5  | Commsigorders                                        | 40 |

|   |     | 2.1.6  | Interconnections                                     | 41 |

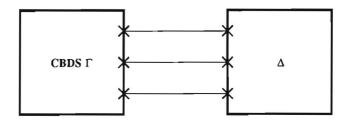

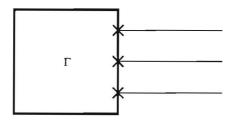

|   |     |        | 2.1.6.0 Interconnection between two modules          | 42 |

|   |     | 2.1.7  | Overview of interpretative issues                    | 46 |

|   |     | 2.1.8  | Notational convention                                | 47 |

|   | 2.2 | Introd | uction of trace theory in our Communication Model    | 47 |

|   |     | 2.2.0  | Commports, comminsts, and comminstorders             | 48 |

|   |     | 2.2.1  | Commsigs and commsigorders                           | 49 |

|   |     | 2.2.2  | Opdirs and iodirs                                    | 50 |

|   |     | 2.2.3  | Components.                                          | 51 |

|   |     |        | 2.2.3.0 Enabling and disabling                       | 57 |

|   |     | 2.2.4  | Channels.                                            | 59 |

|   |     | 2.2.5  | Comparison with the use of directed trace structures | 61 |

|   | 2.3 | Exam   | ples of components                                   | 61 |

|   | 2.4 | Event  | -based model                                         | 73 |

| Contents |

|----------|

|          |

| 3 | Cor | nputat                                  | tion interference hazard                              | 75  |  |  |  |  |  |

|---|-----|-----------------------------------------|-------------------------------------------------------|-----|--|--|--|--|--|

|   | 3.0 | Hazar                                   | Iazards                                               |     |  |  |  |  |  |

|   | 3.1 | Conne                                   | ected components                                      | 79  |  |  |  |  |  |

|   | 3.2 | Abser                                   | ace of computation interference hazard                | 79  |  |  |  |  |  |

|   |     | 3.2.0                                   | Direct connection                                     | 80  |  |  |  |  |  |

|   |     | 3.2.1                                   | Acceptance of commsigs                                | 82  |  |  |  |  |  |

|   | 3.3 | Transi                                  | formation into computation interference hazard        | 83  |  |  |  |  |  |

|   |     | 3.3.0                                   | 3.3.0 The technique                                   |     |  |  |  |  |  |

|   |     | 3.3.1                                   | Example of transformation technique                   | 85  |  |  |  |  |  |

|   |     |                                         | 3.3.1.0 Ambiguous quiescence hazard                   | 85  |  |  |  |  |  |

|   |     |                                         | 3.3.1.1 Transformation of ambiguous quiescence hazard | 87  |  |  |  |  |  |

|   |     |                                         | 3.3.1.2 Examples                                      | 89  |  |  |  |  |  |

| 4 | Con | nmuni                                   | cating delay-safely                                   | 99  |  |  |  |  |  |

|   | 4.0 | lity                                    | 100                                                   |     |  |  |  |  |  |

|   |     | 4.0.0                                   | Composability diagram.                                | 103 |  |  |  |  |  |

|   |     | 4.0.1                                   | Properties of composability                           | 106 |  |  |  |  |  |

|   |     | 4.0.2                                   | 0.2 Composability versus independence of comminsts    |     |  |  |  |  |  |

|   | 4.1 | Communication in channels               |                                                       |     |  |  |  |  |  |

|   |     | 4.1.0                                   | 4.1.0 Delay-safe channels                             |     |  |  |  |  |  |

|   |     | 4.1.1                                   | Delay-safe closure                                    | 111 |  |  |  |  |  |

|   | 4.2 | .2 Communication behavior of components |                                                       |     |  |  |  |  |  |

|   |     | 4.2.0                                   | Computation interference hazard                       | 113 |  |  |  |  |  |

|   |     | 4.2.1 Delay-safe enclosure              |                                                       |     |  |  |  |  |  |

|   |     | 4.2.2                                   | Properties of delay-safe enclosure                    | 122 |  |  |  |  |  |

|   |     |                                         | 4.2.2.0 Computation interference hazard               | 123 |  |  |  |  |  |

|   |     |                                         | 4.2.2.1 Trace structure inclusion                     | 124 |  |  |  |  |  |

|   |     |                                         | 4.2.2.2 Regularity and choice                         | 129 |  |  |  |  |  |

|   |     | 4.2.3                                   | Behavior of delay-safely communicating components     | 133 |  |  |  |  |  |

|   |     | 4.2.4                                   | Impact of delay-safe communication on components      | 139 |  |  |  |  |  |

|   |     | 4.2.5 'Off-the-shelf' mechanisms        |                                                       |     |  |  |  |  |  |

| 5 | Cor                                      | nmuni                                          | icating delay-insensitively 14                        | 43 |  |

|---|------------------------------------------|------------------------------------------------|-------------------------------------------------------|----|--|

|   | 5.0                                      | Comn                                           | nunication in channels                                | 44 |  |

|   | 5.1                                      | Comn                                           | nunication behavior of components                     | 46 |  |

|   |                                          | 5.1.0                                          | Transformation into computation interference hazard 1 | 46 |  |

|   |                                          |                                                | 5.1.0.0 Initializability                              | 46 |  |

|   |                                          |                                                | 5.1.0.1 Delay-insensitive enclosure                   | 48 |  |

|   |                                          |                                                | 5.1.0.2 Properties of delay-insensitive enclosure 1   | 53 |  |

|   |                                          |                                                | 5.1.0.3 Behavior of delay-insensitively communicating |    |  |

|   |                                          |                                                | components                                            | 59 |  |

|   |                                          | 5.1.1                                          | 'Off-the-shelf' mechanisms                            | 63 |  |

| 6 | Cor                                      | nposit                                         | ion 10                                                | 65 |  |

|   | 6.0                                      | Conne                                          | ection of components                                  | 65 |  |

|   |                                          | 6.0.0                                          | External input and output 1                           | 67 |  |

|   |                                          | 6.0.1                                          | General composability                                 | 69 |  |

|   |                                          |                                                | 6.0.1.0 Relation to composability                     | 71 |  |

|   |                                          |                                                | 6.0.1.1 General composability diagram                 | 72 |  |

|   | 6.1                                      | Comp                                           | osition without computation interference hazard 1     | 76 |  |

|   | 6.1.0 Combining two connected components |                                                |                                                       |    |  |

|   |                                          | 6.1.1                                          | Absence of computation interference hazard1           | 84 |  |

|   |                                          | 6.1.2                                          | Hiding the internal communication                     | 91 |  |

|   | 6.1.3 Composite of two components.       |                                                |                                                       |    |  |

|   |                                          | 6.1.4                                          | Examples                                              | 00 |  |

|   |                                          | 6.1.5 Interpretation of the composition method |                                                       |    |  |

|   | 6.2                                      | Comp                                           | osition without transmission interference hazard      | 03 |  |

|   |                                          | 6.2.0                                          | Transformation into computation interference hazard 2 | 03 |  |

|   |                                          | 6.2.1                                          | Condition for composition                             | 04 |  |

|   |                                          | 6.2.2                                          | Composite of two components                           | 05 |  |

|   | 6.3                                      | Decor                                          | nposition                                             | 08 |  |

|   | 6.4                                      | Other                                          | correctness concerns                                  | 10 |  |

| Contents |

|----------|

|----------|

| 7                                   | Con                             | luding remarks 2                                          | 11 |  |  |  |

|-------------------------------------|---------------------------------|-----------------------------------------------------------|----|--|--|--|

|                                     | 7.0                             | Formal definitions of delay-insensitive                   | 13 |  |  |  |

|                                     |                                 | 7.0.0 Relation between self-timed and delay-insensitive 2 | 13 |  |  |  |

|                                     |                                 | V.0.1 Modular approach to delay-insensitivity             | 15 |  |  |  |

|                                     |                                 | V.0.2 Delay-safety and delay-insensitivity                | 18 |  |  |  |

|                                     |                                 | 2.0.3 Fairness and delay-insensitivity                    | 19 |  |  |  |

|                                     |                                 | 7.0.4 Testing for delay-insensitivity                     | 20 |  |  |  |

|                                     | 7.1                             | Sopics for further research                               | 20 |  |  |  |

| Appendix A Proofs                   |                                 |                                                           |    |  |  |  |

| A.3 Computation interference hazard |                                 |                                                           |    |  |  |  |

| A.4 Communicating delay-safely      |                                 |                                                           |    |  |  |  |

|                                     | A.5                             | Communicating delay-insensitively                         | 47 |  |  |  |

| Re                                  | eferei                          | ces 20                                                    | 65 |  |  |  |

| Glossary of symbols and operators   |                                 |                                                           |    |  |  |  |

| Su                                  | bjec                            | index 2                                                   | 82 |  |  |  |

| Summary                             |                                 |                                                           |    |  |  |  |

| Sa                                  | Samenvatting (summary in Dutch) |                                                           |    |  |  |  |

| Cı                                  | Curriculum vitae                |                                                           |    |  |  |  |

|                                     |                                 |                                                           |    |  |  |  |

vii

Contents

viii

# 0

# Introduction

In the middle of the 20th century Huffman, cf. [Huffman 54], and Muller and Bartky, cf. [Muller-Bartky 59], started to develop theories for designing asynchronous circuits. Since then, interest in asynchronous design has existed at just a few places. Only in the last decade, asynchronous design seems to have become a topic of general interest, cf. [Barney 85], culminating in Sutherland's Turing Award lecture, see [Sutherland 89], and spreading over many research institutes since then.

# 0.0 Synchronous and asynchronous

In this section we indicate how we interpret the terms "synchronous" and "asynchronous". These interpretations are inspired by [Molnar92].

The terms "synchronous" and "asynchronous" have been used with different meanings in different contexts. As applied to circuits, the terms have generally distinguished those

that employ a "clock signal" that serves as a reference to separate consecutive circuit states from one another

from those

that do not make use of such a signal, but that define states in terms of input values and internal actions that result in changes of circuit conditions.

Some circuits, such as those designed with "fundamental mode" restrictions on the changes of input values, may be interpreted either way. As applied to communications rather than circuits, the term "synchronous" has been used to mean that the sending and the reception of a communication signal are regarded as the same event. In the case of CSP, cf. [Hoare 85], there is an even stronger requirement that both "sender" and "receiver" must agree upon a communication signal, and hence that there is no distinction between sender and receiver. In a more general case, the term "synchronous" has been taken to mean that there is no delay between the sending of a signal and its reception, or, more abstractly, that the actions of sending and receiving a particular signal each stand in precisely the same ordering relation to other signaling actions. In comparison, "asynchronous" communication signals have distinct sending and receiving actions associated with them, which, in general, have different ordering relations to other signaling actions. In other words, there may be a non-zero delay between the sending of an asynchronous communication signal and its arrival at the receiver.

The different usages of the terms "synchronous" and "asynchronous" have arisen in the context of, on the one hand, circuit design and, on the other hand, abstract process communication models. They threaten no confusion when used exclusively within these distinct domains. Opportunities for severe confusion arise when these domains overlap, as they do in the discussion of the design of circuits to implement structures that are defined in the language and formalism of communication models, as in this monograph.

At this point we want to distinguish and discuss three kinds of communication :

- (i) The sending of a communication signal and its arrival are not identified; there is a condition that the arrival of such a signal must not precede the sending of this signal. The sender alone controls if and when a signal is sent.

- (ii) The sending of a communication signal and its arrival are identified; the sending and arrival actions of each communication signal are identically ordered with respect to all other actions. The sender alone controls if and when a signal is sent.

- (iii) The sending of a communication signal and its arrival are identified; the sending and arrival actions of each communication signal are identically ordered with respect to all other actions. Both sender and receiver jointly control if and when such a joint action occurs. As a consequence, there is no difference in the role of "sender" and "receiver".

There may exist general agreement that (i) and (iii) are in the categories "asynchronous communication" and "synchronous communication", respectively; however, (ii) might be classified either way. In this monograph we discuss communication in a physical context. We consider (ii) to be in the

category "synchronous communication"; the connection between components that model mechanisms that communicate as described by (ii) is called *direct*. Furthermore, the connection between components that model mechanisms that communicate as described by (i) is called *indirect*. In the kind of communication described by (iii) sender and receiver share the control whether and, if so, when a joint action occurs; we consider this to constitute a higher level communication primitive that falls outside the scope of this monograph.

# 0.0.0 Asynchronous communication

There exist various reasons why one may be interested in asynchronous communication. Here, we mention scaling, variable or unknown delays, and metastability.

When integrating circuits at an increasingly larger scale, delays in the interconnections between the switching elements tend to increase relatively to the delays in the switching elements, cf. [Seitz80, van de Snepscheut85]. In order to obtain a lot of freedom for placement and routing, we are interested in separating the functional and geometrical design tasks. This can be established by designing circuits that behave correctly independent of the size of the delays. This goal is achieved in the area "delay-insensitive communication" in the discipline "asynchronous communication design".

Another source of motivation for studying delay-insensitive communication is the occurrence of metastable behavior in digital circuits. We consider a system that has a continuous state space with at least two stable states and at least one unstable state. The system will converge to one of its stable states. Which stable state the system will end up in depends on the initial condition. For such a system and a given finite interval of time, there exists an initial condition such that the system doesn't reach any stable state within this interval. This phenomenon is called *metastability*. Chaney and Molnar, cf. [Chaney – Molnar73], presented experimental evidence showing metastable behavior in digital circuits. Hurtado, cf. [Hurtado75], argued that metastable behavior is an important and intrinsic issue; therefore we mention it next to (other) variable delays, see also [Kleemann – Cantoni 87].

Furthermore, asynchronous communication can be used as a model for the communication in distributed systems, e.g. transputers, Cosmic Cubes, cf. [Seitz 85, Dally-Seitz 86], or the FFP-machine, cf. [Mago 85]. Asynchronous communication can also be used in an interface between internally synchronous parts.

In this monograph we address communication between mechanisms. Mechanisms communicate by sending and receiving (physical) signals. We treat communication between mechanisms that are modeled to have an indirect connection. This results in the formal definitions of delay-safe and delay-insensitive communication. Our notion of delay-safe (and also delayinsensitive) communication comprises that the value of the delay between the sending and the reception of each such signal has an unknown non-negative value.

# 0.0.1 Communication Model

We introduce the formal Communication Model. In the Communication Model we use trace theory as a tool. The trace theory formalism has been developed at Eindhoven University of Technology by Rem and others, cf. [Rem 85, Rem – van de Snepscheut – Udding 83, van de Snepscheut 85, Kaldewaij 86]. The interpretation of trace theory in the Communication Model yields a formalization of delay-safe (and delay-insensitive) communication. Our research is concerned with three topics:

- delay-safe communication,

- delay-insensitive communication, and

- absence of computation interference hazard.

We address these topics at three levels:

- the relation between the Communication Model and the underlying physics,

- notions in the Communication Model and the relations between them, and

- the use of the trace theory formalism in the Communication Model.

Although we like to play formal games, the formal game presented in this monograph has been inspired by physical problems. We think that the material presented in this monograph may be a helpful tool for designers who are concerned with asynchronous communication; we show the limitations of delay-safe and delay-insensitive communication. Furthermore, our work provides a starting point for the integration of synchronous communication design and asynchronous communication design.

# 0.0.2 Computation interference hazard

Molnar and Fang pointed out that a specification of the mechanism to be designed should not only be interpreted as a specification for the mechanism itself, but that, in general, such a specification puts restrictions upon the communication between the mechanism and its environment, see [Molnar-Fang83]. Our study of asynchronous communication has revealed the urge to distinguish between the reception (arrival) of a signal and its acceptance. The arrival of a signal at a moment that it cannot be accepted by a mechanism is called "computation interference". The danger that this might happen is called computation interference <u>hazard</u>. The correctness concern "absence of computation interference hazard" is the basic correctness concern in this monograph. The distinction between the "reception" and "acceptance" of a signal provides the context that is needed for the discussion of computation interference hazard originally has emerged within the context of "asynchronous communication". Separating the correctness concern from this context has enabled us to address synchronous as well as asynchronous communication, using direct and indirect connections respectively, within one formal framework: our Communication Model.

# 0.1 Subsequent chapters

In chapter 1 we present some tools that we use in this monograph. The Communication Model is presented in chapter 2. We use the word "model" to relate notions in our Communication Model to notions in the underlying physics. Our Communication Model provides a clear separation between the interpretation of physical issues and the formalism. We distinguish between the communication behavior of a module and the communication of an interconnection. Furthermore, we introduce abstractions: we define components as equivalence classes of modules and we define channels as equivalence classes of interconnections. We address computation interference hazard in chapter 3. Absence of computation interference hazard being our basic correctness concern, we present a technique to transform other correctness concerns into absence of computation interference hazard. In chapter 4 we are concerned with delay-safe communication; absence of computation interference hazard is the correctness concern. In this chapter we focus on the communication behavior of mechanisms that communicate in a delay-safe way. Within the context of delay-safe communication, we address in chapter 5 an additional correctness concern. viz. absence of transmission interference hazard. Transmission interference hazard models that it is possible that some signals interfere with each other. The communication is delay-insensitive if and only if the communication is delay-safe and there is no transmission interference hazard. In chapter 6 we address composition and decomposition. We present necessary and sufficient conditions for composition under some given correctness concerns and a method to calculate the composition under these conditions. In this chapter we are concerned with connections that are partially direct and partially indirect. Within our study at the

level of process communication, an indirect connection between components models allowing for delays of unknown size in signals exchanged between mechanisms, whereas a direct connection between components models allowing only for zero delays in signals exchanged between mechanisms. Both direct and indirect connections are discussed in chapter 6. We present a relation between our research and the work of others in chapter 7; there, we also give some concluding remarks and we pinpoint some topics for future research.

# 0.2 Denotations in the English language

We use double quotes to indicate that we refer to the enclosed passage as a concept, not as a part of the sentence. Single quotes are used to indicate that we are skeptical about the enclosed passage. We use underlining to stress a part of a sentence. Italics are used to indicate the first appearance and/or definition of a formal notion in this monograph.

We also use italics to distinguish the formal objects from the words in the English language; furthermore, boldface printing is used to indicate formal operators.

# 0.3 Notions related to "asynchronous"

In this section we present terms that have been used in literature to refer to asynchronous communication design; we have included a lot of references which can be a starting point for exploring this area. Readers familiar with the research in this area may want to continue reading in section 0.4. At Eindhoven University of Technology a public bibliography on asynchronous communication has been set up. A compressed version of the bibliography file is available for anonymous ftp on Internet from <ftp.win.tue.nl> (address: [131.155.70.100]) as file async.bib.Z in directory /pub/tex. All communication concerning this library can be sent to the corresponding e-mail address:

<async-bib@win.tue.nl>

Many people have been concerned with notions that are related to delayinsensitivity. In the literature one encounters a variety of terms: <u>asynchronous</u>, <u>speed-independent</u>, <u>self-timed</u>, <u>delay-safe</u>, <u>delay-insensitive</u>, <u>delay-independent</u>. Although distinct terms are used, people are dealing with related intuitive notions. Attempts have been made to formalize these notions stressing distinct characteristics. Furthermore, the same term has been used by different people to indicate different aspects of the intuitive notions.

The term asynchronous arose to distinguish between synchronous, e.g. globally clocked, and not synchronous, e.g. locally clocked or not clocked, systems, cf. [Muller-Bartky59, Unger69, Rosenberger69, Keller75, Molnar-Fang81, Dill-Clarke 85, Molnar 86, Brzozowski-Seger 89, Brzozowski-Ebergen 89, Yoeli 87]. In [Josephs-Hoare-Jifeng 89] Josephs, Hoare, and Jifeng have introduced asynchronous processes in CSP, cf. [Hoare 85]. Muller, cf. [Miller 65], Keller, cf. [Keller 74], Fang and Molnar, cf. [Fang – Molnar 83], and Dill. cf. [Dill88], use the term "speed-independent", and Seitz is among others concerned with "self-timed" systems, cf. [Seitz 79, Martin 85b, Yakovlev 85, Greenstreet - Williams - Staunstrup 88]. Van de Snepscheut and Martin both use "delay-insensitive". They stress the internal communication, cf. [van de Snepscheut 85, Martin 86]; the external communication between the mechanisms and an external environment need not be delay-insensitive. Molnar, Fang, and Rosenberger apply delay-insensitivity to the external communication of Macromodules, cf. [Molnar-Fang-Rosenberger 85, Clark-Molnar 74, Molnar-Fang81, Rosenberger-Molnar-Chaney-Fang88]. The internal communication is, generally, not delay-insensitive. Based upon the latter approach several formalizations have emerged, cf. [Udding 84, Schols 85, Verhoeff 85, Black 86, Ebergen 87].

Udding was the first to capture delay-insensitivity formally. He has presented a set of rules, i.e. predicates on trace structures, that are necessary and sufficient for delay-insensitivity, cf. [Udding84]. Udding is concerned with the communication behavior of components rather than with the communication in channels. He distinguishes four classes; the largest class he has called the "delay-insensitive class", see also chapter 5 and subsection 7.0.1.

Within the study of asynchronous communication design the multiple use of terms has led to argument and confusion. In this monograph, see chapter 5, we will work within the area "delay-insensitive communication", see [Udding 84].

# 0.4 Delay-insensitivity

Restricting communication to delay-insensitive communication turns out to reduce the class of implementable specifications of circuits. Many questions arise, e.g.:

- what are the limitations of delay-insensitive communication?

- can delay-insensitive communication be integrated with more synchronized forms of communication?

- is any liveness property implementable when using delay-insensitive communication?

In this monograph we address the first two questions extensively. Regarding the third question, it has been argued that liveness properties are not expressable using finite trace theory. We have shown that it is possible to express some liveness properties in finite trace theory, e.g. absence of ambiguous quiescence hazard, cf. "absence of unspecified termination hazard" in [Schols 88]; in this monograph ambiguous quiescence hazard is presented as an example of the transformation technique shown in chapter 3.

Seitz argues that a strict protocol of signaling conventions has to be imposed throughout a system in order to deal with the complexity of the design, cf. [Seitz80]. We agree with him. On the other hand, confining oneself to such a restriction may make the design problem fundamentally unsolvable or require unacceptable penalties in cost, performance, manufacturability, or testability. We would like to know whether our inability to find an acceptable solution for such a problem, is fundamentally due to the problem itself or to a possibly too severe restriction that we imposed and that perhaps should be relaxed. In chapters 4 and 5 we present tools that help to answer this question.

# **0.5** Proofs

Within this monograph we present formal statements in theorems, lemmas, and properties. We present properties without formal proofs, since the proofs of them are either trivial, easy, presented elsewhere, or analogous to other proofs; we do give hints when this is appropriate. The proofs of lemmas and theorems are presented in appendix A; this is done in order not to interrupt the flow of the discourse by the rather technical proofs. Theorems represent the formal conclusions drawn in this monograph; lemmas are intended for local use within the context of this monograph only.

# 1

# Formalism and notation

In this chapter we present some tools and notational conventions that we use in the remainder of this monograph.

# 1.0 Sets

In this monograph a *set* is denoted by a pair of curly brackets. The elements of a set are listed between these brackets. The elements are separated from each other by commas. We also use quantification to denote sets, see section 1.2.

We denote the *empty set* by " $\emptyset$ ". Between an element and a set there exists a binary relation, viz. "*is an element of*"; this relation is denoted by the infix operator " $\in$ ". The negation of this relation, i.e. the binary relation "*is not an element of*", is denoted by the infix operator " $\notin$ ".

### example 1.0

$\{3, 8\}$  denotes the set that consists of the natural numbers 3 and 8.

$0 \in \{0, 1, 2\}$

4∉{0,1,2}

end of example

The *intersection* of two sets is denoted by the infix operator " $\cap$ ". The *union* of two sets is denoted by the infix operator " $\cup$ ". The binary relation "*subset*" is denoted by the infix operator " $\subseteq$ ".

# example 1.1

$\{2,3\} \cap \{2,4\} = \{2\}$  $\{2,3\} \cup \{2,4\} = \{2,3,4\}$  $\{2,4\} \subseteq \{2,3,4\}$  $\{2,3,4\} \subseteq \{2,3,4\}$ end of example

The binary relation "proper subset" is denoted by the infix operator " $\subset$ ". For sets M and N,  $M \subset N$  is equal to  $(M \subseteq N) \land (M \neq N)$ . For sets M and N, we denote the asymmetric set difference of M and N by  $M \setminus N$ . In definition 1.2 we use quantification to denote the set that is defined as  $M \setminus N$ ; we explain this notation in section 1.2.

definition 1.2 asymmetric set difference For sets M and N,  $M \setminus N \stackrel{\text{def}}{=} \{m : m \in M \land m \notin N : m\}.$ end of definition

For sets M and N, the symmetric set difference of M and N is denoted by  $M \div N$ .

definition 1.3 symmetric set difference For sets M and N,  $M \div N \stackrel{\text{def}}{=} (M \setminus N) \cup (N \setminus M).$

end of definition

```

example 1.4

```

$\{2,3\}\setminus\{2,4\}=\{3\}$

$\{2,3\} \div \{2,4\} = \{3,4\}$

end of example

The set of *natural numbers* is denoted by  $\mathbb{N}$ ; in this monograph, zero is a natural number. The set of all positive natural numbers is denoted by  $\mathbb{N}^+$ .

```

property 1.5

```

```

(i) 0 \in \mathbb{N}

(ii) \mathbb{N}^+ = \mathbb{N} \setminus \{0\}

end of property

```

# 1.1 Operators

We assume that the reader is familiar with the following operators in propositional calculus: *equality*, denoted by "=", *inequality*, denoted by " $\neq$ ", *negation*, denoted by " $\neg$ ", *conjunction*, denoted by " $\wedge$ ", *disjunction*, denoted by " $\vee$ ", and *implication*, denoted by " $\Rightarrow$ ". The disjunction is <u>inclusive</u>, i.e.  $x \lor y$  does not imply  $x \ne y$ .

# 1.1.0 Priority of operators

We define the *priority* of operators in order to save on parentheses. To do this we have grouped the operators; within each group all operators have equal *binding power*. The groups of operators are listed in table 1.0 in order of increasing binding power.

| =        | ¥       |           |         |          |           |     |

|----------|---------|-----------|---------|----------|-----------|-----|

| ٨        | v       | ⇒         |         |          |           |     |

| e        | ∉       | ⊆         |         |          |           |     |

| ١        | ÷       | $\cap$    | υ       | h        |           |     |

| all othe | r opera | tors that | have at | least tw | o paramet | ers |

| all unar | y opera | tors      |         |          |           | _   |

| catenati | ion     |           |         |          |           |     |

table 1.0

Priority of operators in order of increasing binding power.

As a consequence, catenation has the highest binding power; equality and inequality have the lowest binding power.

# **1.2 Quantification**

In order to denote quantification, we need a variable binding construct. For such a construct we use a slightly unconventional notation. For instance, *universal quantification*, i.e. generalized conjunction, is denoted by

$(\mathbf{A}l: R: E),$

where A is the quantifier, l is the list of bound variables, R is the predicate that delineates the range of the variables, and E is the quantified expression. Both R and E will, in general, contain variables from l. Analogously, we denote *existential quantification*, i.e. generalized disjunction, by

$(\mathbf{E}l: R: E).$

Furthermore, we may use quantification to denote sets:

$\{l: R: e\},\$

where e denotes an element of the set.

In this monograph, all variables that range over numbers, range over the natural numbers, unless stated otherwise.

# example 1.6

$(A i: 6 \le i < 9: P_i) \text{ is equal to } P_6 \land P_7 \land P_8.$ (E i, j: (2 \le i \le 5) \lapha EVEN(j) \lapha(i=j): P\_i) is equal to P\_2 \lapha P\_4. {i: 2 \le i \le 4: i^2} is equal to {4,9,16}. end of example

# 1.3 Denotation of proofs

Proofs are often split into a number of steps. For instance, for expressions E, F, and G, we can prove  $E \Rightarrow G$  by arguing that E = F and  $F \Rightarrow G$ . The sameness of the two occurrences of F is essential for the argument that the total proof is correct. To establish this sameness, a string comparison is needed. In order to prevent that the reader has to perform such comparisons, we denote proofs like this in the following way:

$$= \begin{cases} E \\ + \text{ hint why } E = F \end{cases}$$

$$\Rightarrow \begin{cases} \text{ hint why } F \Rightarrow G \end{cases}$$

$$G$$

In an analogous way, we denote the proof of  $A \subseteq C$  that consists of the steps A = B and  $B \subseteq C$ . This denotation of proofs is called *hint calculus*. It has been adopted from [Dijkstra-Feijen 88].

# 1.4 Trace theory

When we refer to *trace theory* in this monograph, we mean the trace theory that has been developed at Eindhoven University of Technology by Rem and others, cf. [Rem-van de Snepscheut-Udding 83, van de Snepscheut 85, Kaldewaij 86, Rem 85]. Trace theory is a tool that has been developed to formalize communication. In this section we present the trace theory notions that are used in this monograph. In subsection 1.4.3 we present the notions that we have added to the notions that exist in trace theory. For a detailed overview of trace theory we refer to [Kaldewaij 86]. In subsection 1.4.4 we present a notational convention that may make it easier to appreciate trace theory.

# remark 1.7

Mazurkiewicz, cf. [Mazurkiewicz85], has developed a formalism that is also called trace theory. Mazurkiewicz's trace theory differs from our trace theory. Mazurkiewicz's traces correspond to equivalence classes over our traces.

# end of remark

In our trace theory all traces have finite length. For this reason it is also called finite trace theory. Finite trace theory has been extended by Van Horn, cf. [Van Horn 86], and Black, cf. [Black 86], with infinite traces; this extension is used by them in order to deal with liveness properties. Although liveness properties are not a primary concern in this monograph, we use a liveness

property as an example of a correctness concern in section 3.4. From this we conclude that some liveness properties can be expressed in finite trace theory.

# 1.4.0 Basic notions of trace theory

We assume the existence of a finite set  $\Omega$ ;  $\Omega$  is called the *universe*. The elements of  $\Omega$  are called *symbols*. We assume that  $\Omega$  is large enough, i.e. we will not run out of symbols. A subset of  $\Omega$  is called an *alphabet*. A sequence of symbols is called a *trace*. A set of traces is called a *trace set*. The sequence containing no symbols is denoted by  $\varepsilon$ ; trace  $\varepsilon$  is called the *empty trace*. We link sequences by *catenating* them. Catenation is denoted by juxtaposition. In trace theory the noun "concatenation" is sometimes used instead of "catenation", cf. [Kaldewaij 86].

The set of all finite-length sequences of symbols chosen from an alphabet is called the *Kleene-closure* of this alphabet.

#### definition 1.8 Kleene-closure of alphabet

For alphabet A, the trace set that is the Kleene-closure of A is denoted by  $A^*$ ; it is defined recursively by:

- (i)  $\varepsilon \in A^*$

- (ii)  $(As, a: s \in A^* \land a \in A: sa \in A^*)$

- (iii) completeness axiom: A\* contains no elements that are not required by (i) or (ii).

# end of definition

Notice that  $\emptyset^* = \{\varepsilon\}$ . Furthermore, traces are elements of  $\Omega^*$ . We extend definition 1.8, "Kleene-closure of alphabet", to trace sets.

#### definition 1.9 Kleene-closure of trace set

For trace set S, the trace set that is the Kleene-closure of S is denoted by  $S^*$ ; it is defined recursively by:

- (i)  $\epsilon \in S^*$

- (ii)  $(\mathbf{A}s, t: s \in S^* \land t \in S: st \in S^*)$

- (iii) completeness axiom: S\* contains no elements that are not required by (i) or (ii).

#### end of definition

### 1.4 Trace theory

We define the binary operation prefix on traces.

### definition 1.10 prefix

For traces s and t, s is called a prefix of t, denoted by s prefixt, if and only if

$(\mathbf{E} u : u \in \Omega^* : su = t)$

end of definition

In trace theory the symbol " $\leq$ " has been used to denote the operation "prefix", cf. [Kaldewaij86]; since the operator " $\leq$ " has been used in literature to denote many different operations, we prefer to use prefix to denote the operation prefix.

For trace sets we define the unary operation prefix-closure.

```

definition 1.11prefix-closure of trace setFor trace set S, prefS denotes the trace set that contains all prefixes of S:prefS \stackrel{def}{=} \{s, t : (sprefixt) \land (t \in S) : s\}

```

end of definition

We call a trace set S prefix-closed if and only if S = pref S.

We denote the *length* of trace t by *lt*.

definition 1.12 *length of trace*

We define the length of a trace recursively by:

(i)

$$l \varepsilon \stackrel{\text{def}}{=} 0$$

(ii) for trace t and symbol a,

$$lta \stackrel{\text{def}}{=} lt + l$$

end of definition

For trace t and alphabet A we denote the projection of t on A by t|A.

```

definition 1.13 projection of trace

We define projection of a trace on an alphabet A recursively by:

(i) \varepsilon \upharpoonright A \stackrel{\text{def}}{=} \varepsilon

(ii) for trace t and symbol a such that a \in A,

ta \upharpoonright A \stackrel{\text{def}}{=} (t \upharpoonright A)a

(iii) for trace t and symbol a such that a \notin A,

```

$$a \mid A \stackrel{\text{def}}{=} t \mid A$$

end of definition

We extend the definition of projection to trace sets.

definition 1.14 projection of trace set

For trace set S and alphabet A,

$S \upharpoonright A \stackrel{\text{def}}{=} \{t : t \in S : t \upharpoonright A\}$

end of definition

In traces, occurrences of symbols are counted from the left to the right. As a consequence, the first occurrence of a symbol in a trace is the left most occurrence of this symbol in this trace. For trace t and symbol a we denote the number of occurrences of a in t by  $\#_a t$ .

definition 1.15 *number of occurrences*

We define the number of occurrences of a symbol a in a trace t by:

$$\#_a t \stackrel{\text{def}}{=} l(t | \{a\}).$$

end of definition

We define the notion bag.

definition 1.16 bag

A bag, say B, is a set of pairs such that

$B = \{a : a \in \Omega : (a, f(a))\}$  for some function  $f : \Omega \to \mathbb{N}$ .

### end of definition

In definition 1.16, "bag", for every symbol a, f(a) is the number of occurrences of a in the bag B. In order to avoid a cumbersome notation, we abbreviate the denotation of a bag, say B, to  $\{a, n : (a, n) \in B \land n > 0 : (a, n)\}$ .

We define the bag of a trace:

definition 1.17 bag of trace For trace t, bag t denotes the bag of t: bag  $t \stackrel{\text{def}}{=} \{a : a \in \Omega : (a, \#_a t)\}$ end of definition

# 1.4.1 Trace structures

A trace structure is an ordered pair  $\langle A, S \rangle$ , in which A denotes an alphabet and S denotes a trace set satisfying  $S \subseteq A^*$ . For trace structure T, aT denotes the alphabet of trace structure T, and tT denotes the trace set of trace structure T.

We define the partial order inclusion on trace structures.

## definition 1.18 trace structure inclusion

For trace structures T and U, we say that T is included in U, denoted by  $T \subseteq U$ , if and only if

$(\mathbf{a}T = \mathbf{a}U) \land (\mathbf{t}T \subseteq \mathbf{t}U)$

# end of definition

Of course, the proper inclusion  $T \subset U$  equals  $(aT = aU) \land (tT \subseteq tU) \land (tT \neq tU)$ . We extend the definition of prefix-closure to trace structures.

### definition 1.19 prefix-closure of trace structure

For trace structure T, pref T denotes the trace structure that is the prefixclosure of T:

pref  $T \stackrel{\text{def}}{=} < aT$ , pref(tT) >

# end of definition

We call a trace structure T prefix-closed if and only if T = pref T. We call a trace structure nonempty if and only if its trace set is nonempty.

### property 1.20

For prefix-closed trace structure T,

$(\varepsilon \in \mathbf{t}T) = (T \text{ is nonempty})$

end of property

We often refer to prefix-closed trace structures that contain  $\varepsilon$  in their trace set. Using property 1.20 we call such a trace structure a nonempty and prefix-closed trace structure.

For trace structures with equal alphabets we define their intersection.

definition 1.21 intersection of trace structures

For trace structures T and U such that aT = aU, the intersection of T and U, denoted by  $T \cap U$ , is defined by

$T \cap U \stackrel{\text{def}}{=} < \mathbf{a} T \cap \mathbf{a} U, \, \mathbf{t} T \cap \mathbf{t} U >$

end of definition

Analogously, for trace structures with equal alphabets we define their union.

definition 1.22 union of trace structures

For trace structures T and U such that aT = aU, the union of T and U, denoted by  $T \cup U$ , is defined by

$T \cup U \stackrel{\text{def}}{=} < \mathbf{a} T \cup \mathbf{a} U, \ \mathbf{t} T \cup \mathbf{t} U >$

end of definition

We extend the definition of projection to trace structures.

definition 1.23 projection of trace structure For trace structure T and alphabet A,

$T \downarrow A \stackrel{\text{def}}{=} < a T \cap A, t T \downarrow A >$

## end of definition

For trace structures T and U we denote their *weave* by TwU. TwU is a trace structure. We consider traces t,  $t \in tT$ , and u,  $u \in tU$ , that are equal w.r.t. the common symbols, i.e.  $t \mid (aT \cap aU) = u \mid (aT \cap aU)$ . Traces t and u are 'merged' into one or more traces of t(TwU); the common symbols are not duplicated by this 'merging'. All pairs of traces t and u that satisfy  $t \mid (aT \cap aU) = u \mid (aT \cap aU)$  are 'merged' in this way.

definition 1.24 weave

For trace structures T and U,

$T \mathbf{w} U \stackrel{\text{def}}{=} \langle \mathbf{a} T \cup \mathbf{a} U, \{ s : s \in (\mathbf{a} T \cup \mathbf{a} U)^* \land s \mid \mathbf{a} T \in \mathbf{t} T \land s \mid \mathbf{a} U \in \mathbf{t} U : s \} \rangle$

end of definition

In example 1.25 we give examples of the weave of trace structures.

example 1.25

- (i)  $\langle \{a,b\}, \{\varepsilon,a,ab,aba\} \rangle w \langle \{b,c\}, \{\varepsilon,b,bc\} \rangle$ =  $\langle \{a,b,c\}, \{\varepsilon,a,ab,aba,abc,abac,abca\} \rangle$

- (ii)  $\langle \{a, b, d\}, \{\varepsilon, b, d, ba\} \rangle w \langle \{b, c, d\}, \{\varepsilon, b, d, dc\} \rangle$ =  $\langle \{a, b, c, d\}, \{\varepsilon, b, d, ba, dc\} \rangle$

end of example

property 1.26 weaving is symmetric For trace structures T and U,

$T\mathbf{w}U = U\mathbf{w}T$

end of property

For trace structures T and U such that  $aT \cap aU = \emptyset$ , the trace set of TwU consists of all traces that are interleavings of a trace of tT and a trace of tU. Property 1.27 shows that weaving is equal to intersection if the alphabets of the trace structures are equal.

# property 1.27

For trace structures T and U such that  $\mathbf{a}T = \mathbf{a}U$ ,

$T \mathbf{w} U = T \cap U$

# end of property

The weave of nonempty prefix-closed trace structures is a nonempty prefix-closed trace structure :

## property 1.28

For nonempty prefix-closed trace structures T and U,

$T \mathbf{w} U$  is nonempty and prefix-closed.

# end of property

For trace structures T and U we denote their *blend* by TbU. TbU is a trace structure, viz. the projection of TwU on the non-common symbols.

definition 1.29 blend For trace structures T and U,  $T\mathbf{b}U \stackrel{\text{def}}{=} (T\mathbf{w}U)|(\mathbf{a}T \div \mathbf{a}U)$ end of definition

In example 1.25 we considered the weave of some trace structures. Examples of the blend of these same trace structures are given in example 1.30.

### example 1.30

end of example

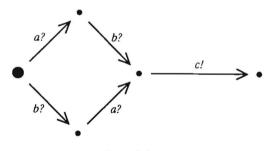

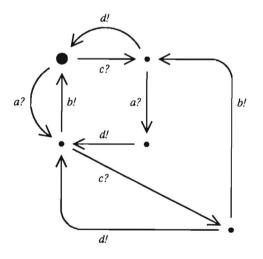

# 1.4.2 State graphs

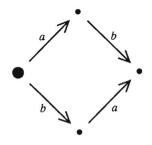

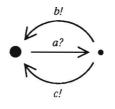

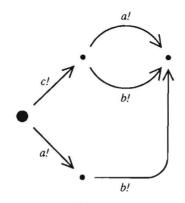

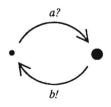

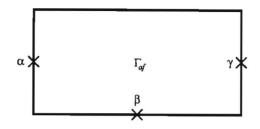

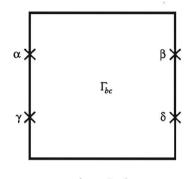

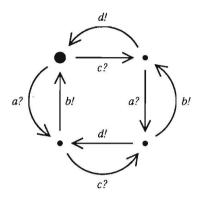

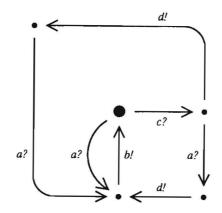

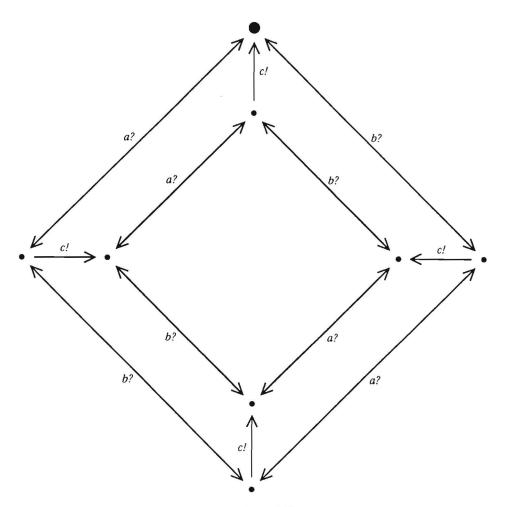

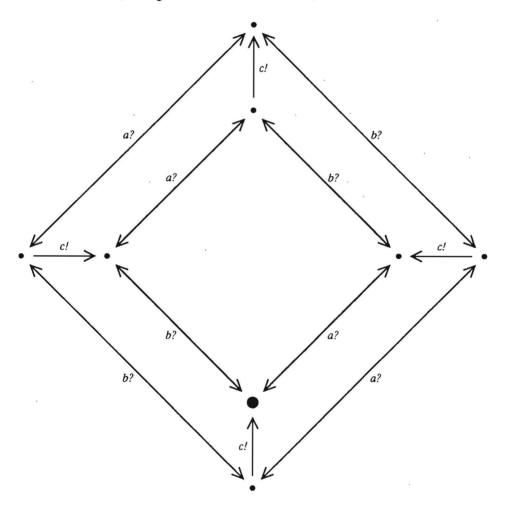

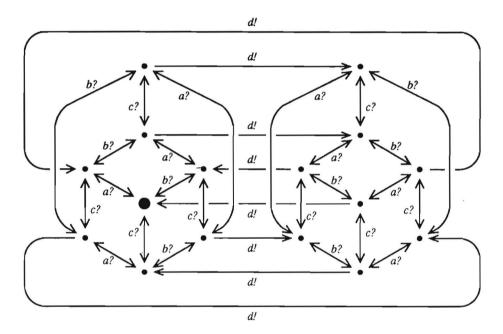

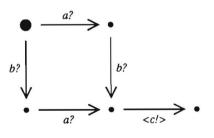

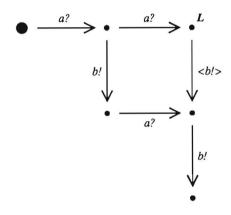

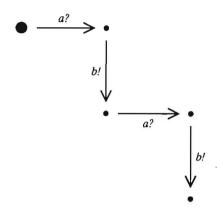

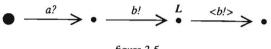

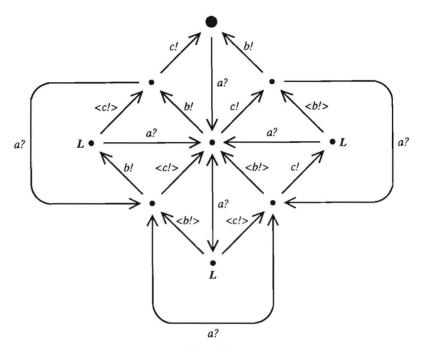

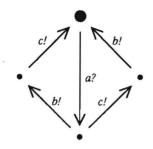

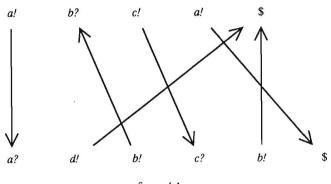

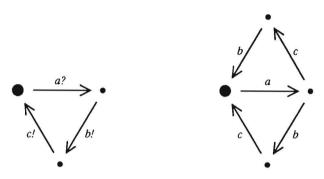

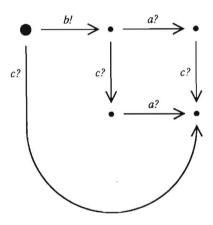

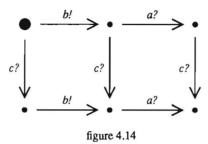

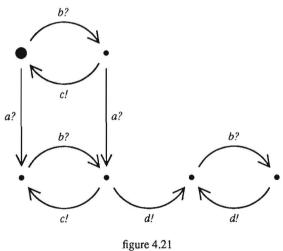

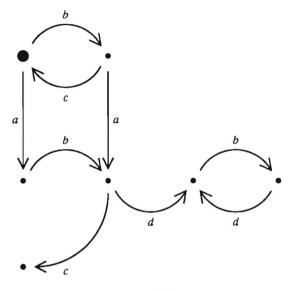

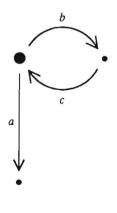

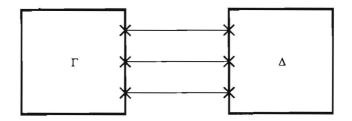

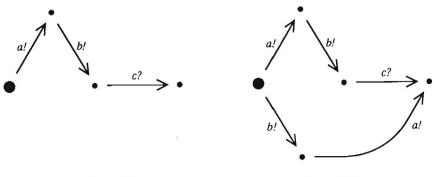

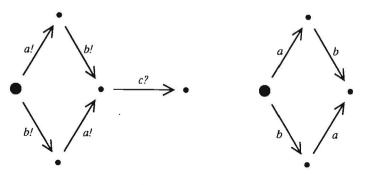

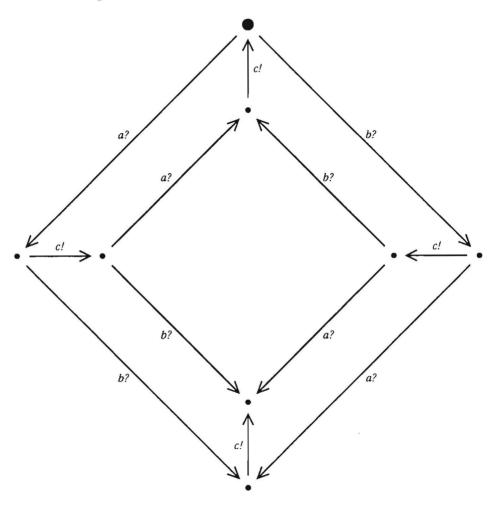

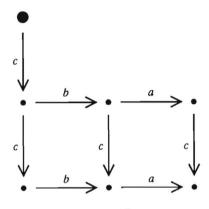

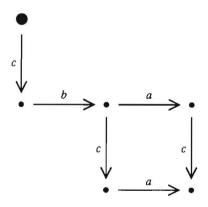

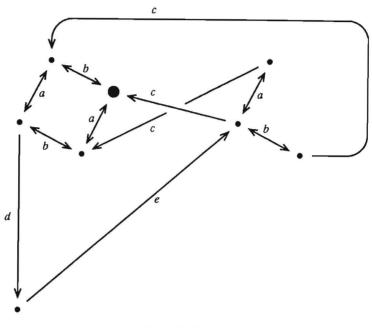

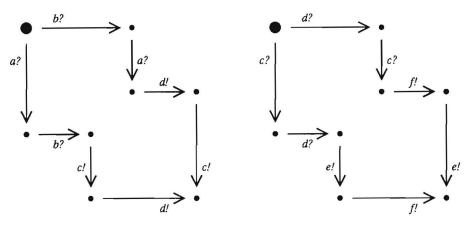

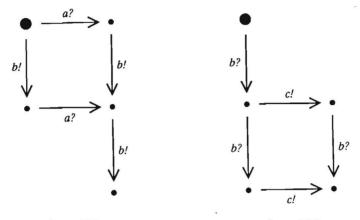

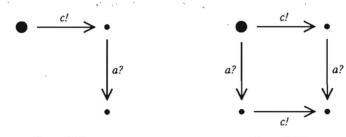

We often denote a nonempty prefix-closed trace set by a *state graph* (i.e. a simple, arc-labeled, directed graph) that is deterministic and minimal, cf. [Kaldewaij86]. The nodes of the graph are the *states*; the arcs of the graph are the *transitions*. The state, to which trace *t* corresponds, is denoted by [t]. As a consequence,  $[\varepsilon]$  denotes the *initial state*. Each path starting in  $[\varepsilon]$  yields a trace by catenating the labels of the arcs on that path as they are traversed. If a state graph has a finite number of states, it is called *regular*. In a diagram of a regular state graph the initial state is indicated by a fat dot, see figure 1.1.

figure 1.1 State graph of trace set { $\varepsilon$ , a, b, ab, ba }.

A state graph can also denote a nonempty prefix-closed trace structure, say T, if every symbol of  $\mathbf{a}T$  occurs in at least one of the traces of  $\mathbf{t}T$ . In that case the alphabet of the trace structure consists of all symbols that occur as a label of some arc in the state graph. If the state graph in figure 1.1 is used to denote a trace structure, it denotes  $\langle \{a, b\}, \{\varepsilon, a, b, ab, ba\} \rangle$ .

#### 1.4 Trace theory

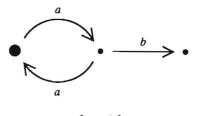

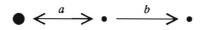

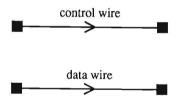

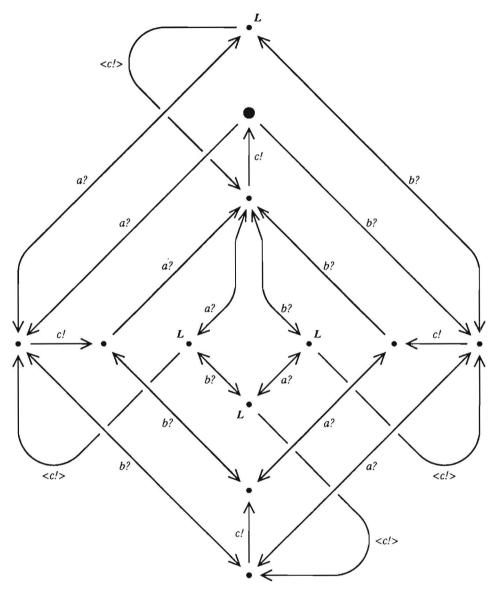

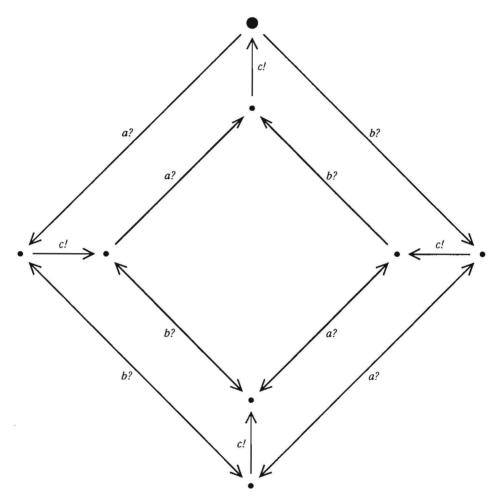

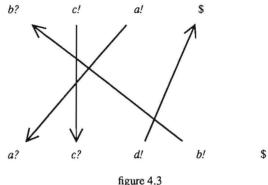

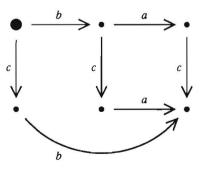

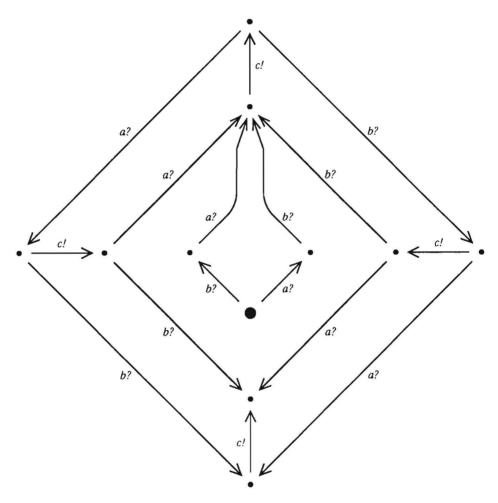

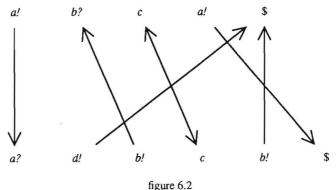

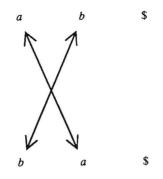

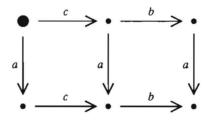

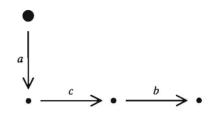

Often we present state graphs in which two states are connected by two arcs that point in opposite directions and have the same label, see figure 1.2.

figure 1.2 A state graph.

We abbreviate such a pair of arcs by replacing these two arcs by one bidirectional arc with the same label, see figure 1.3.

figure 1.3 Abbreviated diagram of the state graph of figure 1.2.

As a consequence, the diagrams in figure 1.2 and figure 1.3 are diagrams of the same state graph.

# 1.4.3 Extensions of trace theory

In this subsection we introduce two extensions of trace theory that are used in this monograph.

## 1.4.3.0 The bipartitions alphbip and iobip

We introduce the notion *alphbip*. An alphbip is an unordered pair of disjoint sets of symbols. The union of these sets is called the *alphabet of the alphbip*; an alphbip is a bipartition of its alphabet. Given alphbip D, the alphabet of D is denoted by aD. Given two disjoint sets of symbols, say A and B, the alphbip of which A and B are the parts is denoted by  $A \oplus B$ .

For two disjoint sets, A and B, of symbols,

$A \oplus B = B \oplus A$

end of property

definition 1.32 intersection of alphbip and alphabet

For two disjoint sets, A and B, of symbols, and alphabet C, the intersection of alphbip  $A \oplus B$  with C is defined by:

$(A \oplus B) \cap C \stackrel{\text{def}}{=} (A \cap C) \oplus (B \cap C)$

end of definition

For symbol a and alphbip D such that  $a \in aD$ , we denote the alphabet of symbols in aD that are in the same part of alphbip D as a by spa(a, D); we denote the alphabet of symbols in aD that are in the other part of alphbip D than a by opa(a, D).

property 1.33

For alphbip D,

$(\mathbf{A}a: a \in \mathbf{a}D: D = \mathbf{spa}(a, D) \oplus \mathbf{opa}(a, D)).$

## end of property

We also introduce the notion *iobip*. An iobip is a pair of disjoint sets of symbols, viz. the *input alphabet of the iobip* and the *output alphabet of the iobip*. The union of these sets is called the *alphabet of the iobip*; an iobip is an ordered bipartition of its alphabet. Given iobip F, the alphabet of F is denoted by  $\mathbf{a}F$ . The input alphabet of F is denoted by  $\mathbf{i}F$ ; the output alphabet of F is denoted by  $\mathbf{o}F$ . For iobip F we define its *reflection*, which is denoted by  $\overline{F}$ :  $\mathbf{i}\overline{F} \stackrel{\text{def}}{=} \mathbf{o}F$  and  $\mathbf{o}\overline{F} \stackrel{\text{def}}{=} \mathbf{i}F$ . The reflection of an iobip is an iobip.

# 1.4.3.1 Reduction operator

We introduce the function redts; this function reduces the trace set of a trace structure by removing certain traces. The motivation for the introduction of this operator redts can only be provided in the context of the following chapters. Until there, the reader may not fully appreciate it.

## definition 1.34 redts

For trace structure T, alphabet A, and trace set S, we define trace structure redts(T, A, S) by:

redts $(T, A, S) \stackrel{\text{def}}{=}$ <**a**T, **t**T \ {x, y, w : x \in (**a**T)<sup>\*</sup>  $\land$  y \in (**a**T \ A)<sup>\*</sup>  $\land$  xy  $\in$  (**t**T  $\cap$  S)  $\land$  w  $\in$  (**a**T)<sup>\*</sup> : xw } >

end of definition

In definition 1.34, "redts", not only every trace (xy) in  $tT \cap S$  is removed from tT, but also all prefixes (x) of such a trace (xy) that differ from it (xy) by a sequence (y) of symbols that are not in A; to ensure the prefix-closedness of t(redts(T, A, S)), all traces (xw) of which a prefix (x) is removed are removed, too. For the necessity of the intersection with tT in definition 1.34, "redts", we refer to example 1.43. The role of alphabet A is illuminated by property 1.35: every trace in  $tT \cap S$  causes the elimination from tT of a trace that contains a symbol in A.

## property 1.35

For prefix-closed trace structure T, alphabet A, and trace set S such that  $\varepsilon \in t(redts(T, A, S))$ ,

```

(As: s \in (tT \cap S): (Ex, a: x \in (aT)^* \land a \in A \land xa \text{ prefix } s: x \in t(\text{redts}(T, A, S)) \land xa \notin t(\text{redts}(T, A, S))))

```

end of property

In property 1.36 we present a generalization of property 1.35.

## property 1.36

For prefix-closed trace structure T, alphabet A, and trace sets S and R such that  $\varepsilon \in t(\operatorname{redts}(T, A, S))$  and  $R = (tT \setminus t(\operatorname{redts}(T, A, S)))$ ,

$$(\mathbf{A}r : r \in \mathbb{R} : (\mathbf{E}x, a : x \in (aT)^* \land a \in A \land xa \text{ prefix} r$$

$$: x \in t(\text{redts}(T, A, S)) \land xa \notin t(\text{redts}(T, A, S))$$

))

end of property

#### remark 1.37

Trace x and symbol a in the existential quantification in properties 1.35 and 1.36 do not only exist: they are also unique.

## end of remark

In order to distinguish between statements about formal objects in definitions, properties, lemmas, and theorems and statements about specific instantiations of such objects in examples, we index the instantiations in examples with natural numbers. We refer to the indexed instantiations locally: in the chapter in which they occur.

#### example 1.38

We consider prefix-closed trace structure  $T_0$ , alphabet  $A_0$ , and trace sets  $R_0$  and  $S_0$ ; they are defined by:

$T_{0} \stackrel{\text{def}}{=} \{a, b\}, \{\varepsilon, a, ab\} >,$   $A_{0} \stackrel{\text{def}}{=} \{a\},$   $R_{0} \stackrel{\text{def}}{=} \{a\},$   $S_{0} \stackrel{\text{def}}{=} \{ab\}.$

From definition 1.34, "redts", follows redts $(T_0, A_0, R_0) = \langle \{a, b\}, \{\epsilon\} \rangle$ . We also see that redts $(T_0, A_0, S_0) = \langle \{a, b\}, \{\epsilon\} \rangle$ , since trace *a* is eliminated from  $tT_0$  because  $b \in (aT_0 \setminus A_0)^*$  and  $ab \in (tT_0 \cap S_0)$ .

## end of example

The following properties follow from definition 1.34, "redts".

#### property 1.39 redts preserves prefix-closedness

For prefix-closed trace structure T, alphabet A, and trace set S,

redts(T, A, S) is prefix-closed.

#### end of property

#### property 1.40

For nonempty, prefix-closed trace structure T, alphabet A, and trace set S,

$(\mathbf{A}s: s \in (\mathbf{t}T \cap S): l(s|A) > 0) = (\varepsilon \in \mathbf{t}(\mathbf{redts}(T, A, S)))$

end of property

#### property 1.41

For trace structure T, alphabet A, and trace sets R and S,

$\operatorname{redts}(T, A, R \cup S) = \operatorname{redts}(\operatorname{redts}(T, A, R), A, S)$

end of property

24

## property 1.42

For trace structure T, alphabet A, and trace set S such that  $tT \cap S = \emptyset$ ,

redts(T, A, S) = T

#### end of property

In example 1.43 we illustrate the necessity of the intersection with tT in definition 1.34, "redts".

## example 1.43

We consider prefix-closed trace structure  $T_i$ , alphabet  $A_i$ , and trace set  $S_i$ ; they are defined by:

$T_{I} \stackrel{\text{def}}{=} \{ a, b \}, \{ \varepsilon, a \} >,$  $A_{I} \stackrel{\text{def}}{=} \{ a \},$  $S_{I} \stackrel{\text{def}}{=} \{ a \}.$

We are interested in redts $(T_I, A_I, S_I)$ . If the intersection with  $tT_I$  in definition 1.34, "redts", is not present, then trace *a* would be removed when reducing the trace set of  $T_I$ , since  $ab \in S_I$  and  $b \in (aT_I \setminus A_I)^*$ . We see, however, that there is no need to remove trace *a* from  $tT_I$ , since  $ab \notin tT_I$  anyway.

end of example

# 1.4.4 Notational convention

Lower case letters near the beginning of the Latin alphabet are symbols; when they are used as variables, they denote symbols. Lower case letters near the end of the Latin alphabet denote traces. Capital letters are used to denote alphabets, alphbips, trace sets, and trace structures.

Boldface lower case operators are used in the trace theory formalism; this does allow them to range over objects in the Communication Model. Boldface upper case operators are used in the Communication Model; this does allow them to range over objects in the trace theory formalism.

Formalism and notation

# **Communication Model**

In this chapter we introduce the *Communication Model*. By introducing this model we achieve a separation of concerns between the interpretation of the underlying physics and the use of the trace theory formalism. We do <u>not</u> interpret any notions of trace theory in the underlying physics directly: we interpret them in our Communication Model. The importance of establishing the separation of concerns between the interpretation of the physical model and the formalism has been recognized previously by others. Van de Snepscheut, see [ van de Snepscheut 85 ], and Udding, see [ Udding 84 ], carefully distinguished trace theory from its mechanistic appreciation. We make this separation of concerns even more explicit by the introduction of our Communication Model.

When one addresses communication in a formal way, one introduces an abstraction from the underlying physics; the latter is either some physical model, that is considered to constitute a good model for some physical phenomena, or it is one's private notion of 'physical reality'. In this chapter we will set down the postulates for our Communication Model. These postulates have been chosen so as to be consistent with at least one class of "physical models" that is used for the design of computing machinery. In this monograph we will not present rigorous arguments for this consistency: we rather discuss the 'reasonableness' of the postulates in one interpretational example, which we will address as "the physical model" in the remainder of this monograph.

The Communication Model is introduced formally in section 2.0. We discuss the relation between our Communication Model and the physical model in section 2.1. In section 2.2 we introduce the trace theory formalism. In section 2.3 we present some examples and in section 2.4 we motivate why we have chosen to make our Communication Model an event-based model.

# 2.0 Definition of Communication Model

In this section we present the definitions and postulates that form the foundation of our Communication Model. The motivation for choosing these definitions and postulates is provided in section 2.1.

# 2.0.0 Commports

We assume the existence of a finite set  $\Psi$ . The elements of  $\Psi$  are called *commports*.  $\Psi$  is partitioned into two parts:  $\Psi^o$ , the set of *output commports*, and  $\Psi^i$ , the set of *input commports*. Of course, the set of commports is disjunct with the set  $\Omega$  of symbols, which has been introduced in subsection 1.4.0.

postulate 2.0

(i)

$$\Psi = \Psi^o \cup \Psi^i$$

(ii)  $\Psi^o \cap \Psi^i = \emptyset$

(iii)  $\Psi \cap \Omega = \emptyset$

end of postulate

For output commport  $\alpha$  and input commport  $\beta$ , we introduce the predicate " $\alpha$  matches  $\beta$ ", which is denoted by  $\alpha$ MATCH $\beta$ . We postulate that a commport matches exactly one commport. Matching commports are either "connected directly" or "connected indirectly".

#### postulate 2.1

(i) For input commport  $\gamma$ ,

$(\mathbf{E}\alpha:\alpha\in\Psi^o:\alpha MATCH\gamma)$

(ii) for output commports  $\alpha$  and  $\beta$ , and input commport  $\gamma$ ,

$(\alpha MATCH\gamma \land \beta MATCH\gamma) \Rightarrow (\alpha = \beta)$

(iii) for output commport  $\alpha$ ,

$(\mathbf{E}\gamma:\gamma\in\Psi^{i}:\alpha MATCH\gamma)$

(iv) for output commport  $\alpha,$  and input commports  $\gamma$  and  $\delta,$

$(\alpha MATCH\gamma \land \alpha MATCH\delta) \Rightarrow (\gamma = \delta)$

(v) for commports  $\alpha$  and  $\beta$  such that  $\alpha MATCH\beta$ , either  $\alpha$  and  $\beta$  are "connected directly" or  $\alpha$  and  $\beta$  are "connected indirectly".

end of postulate

From postulate 2.1 we infer that  $\Psi^o$  and  $\Psi^i$  have the same number of elements. From the definition of matching commports we infer property 2.2.

property 2.2

For commports  $\alpha$  and  $\beta$ ,

$\alpha MATCH\beta \Rightarrow (\alpha \in \Psi^o \land \beta \in \Psi^i)$

end of property

# 2.0.1 Comminsts and commsigs

The elements of the Cartesian product of  $\Psi$  and  $\mathbb{N}^+$  are called *comminsts*. The comminst with commport  $\alpha$  and positive natural number *n* is denoted by  $\alpha_n$ . If  $\alpha$  is an output commport, we call  $\alpha_n$  an *output comminst*; if  $\alpha$  is an input commport, we call  $\alpha_n$  an *input comminst*. A set of comminsts, say  $\Lambda$ , is called an *initial set* of comminsts if, for every comminst in  $\Lambda$ ,  $\Lambda$  contains all comminsts with the same commport and a smaller number, see definition 2.3.

definition 2.3 initial set of comminsts A set of comminsts Λ is called an *initial set of comminsts* if and only if

$(\mathbf{A}\alpha, m, n: \alpha_n \in \Lambda \land m \in \mathbb{N}^+ \land m < n: \alpha_m \in \Lambda)$ end of definition The elements of the Cartesian product of  $\Psi^o$ ,  $\mathbb{N}^+$ , and  $\Psi^i$ , for which the output commport matches the input commport, are called *commsigs*, see definition 2.4:

definition 2.4

For  $\alpha$ ,  $\beta$ , and *n* such that  $\alpha \in \Psi^o$ ,  $\beta \in \Psi^i$ ,  $n \in \mathbb{N}^+$ , and  $\alpha MATCH\beta$ , the triple  $(\alpha, n, \beta)$  is a commsig.

end of definition

Analogously to "initial set of comminsts", we define the predicate "initial" for sets of commsigs. A set of commsigs, say  $\Lambda$ , is called an *initial set of commsigs* if, for every commsig in  $\Lambda$ ,  $\Lambda$  contains all commsigs with the same pair of matching commports and a smaller number, see definition 2.5.

definition 2.5initial set of commsigsA set of commsigs  $\Lambda$  is called an initial set of commsigs if and only if

$(\mathbf{A}\alpha,\beta,m,n:(\alpha,n,\beta)\in\Lambda \land m\in\mathbb{N}^+ \land m< n:(\alpha,m,\beta)\in\Lambda)$ end of definition

# 2.0.2 Comminstorders and commsigorders

In order to define comminstorders and commsigorders we need the notion *strict partial order*. A strict partial order is an antireflexive and transitive relation; as a consequence, it is antisymmetric. It is also referred to as an "antireflexive partial order" in literature.

A comministorder is a pair  $\langle \Lambda, \Box \rangle$ , in which  $\Lambda$  denotes a finite <u>initial</u> set of comminists and " $\Box$ " is a strict partial order on  $\Lambda$ . For comministorder  $\phi$ ,  $\Lambda_{\phi}$  denotes the set of comminists of comministorder  $\phi$ , and  $\Box_{\phi}$  denotes the strict partial order of comministorder  $\phi$ .

In the strict partial order of a comminstorder, a comminst is preceded by every comminst with the same commport and a smaller number.

postulate 2.6 For comminitorder  $\phi$ ,

$(\mathbf{A}\alpha, m, n: \alpha_n \in \Lambda_{\phi} \land m \in \mathbb{N}^+ \land m < n: \alpha_m \sqsubset_{\phi} \alpha_n)$

end of postulate

For comminstorders we define the *restriction* to an initial set of comminsts:

definition 2.7 restriction of comminstorder

For comminstorder  $\phi$  and initial set of comminsts  $\Lambda$ , we denote the comminstorder that is *the restriction of*  $\phi$  *to*  $\Lambda$  by  $\phi^{\dagger}\Lambda$ ; it is defined by:

$\phi^{\uparrow} \Lambda \stackrel{\text{def}}{=} < \Lambda_{I}, \sqsubset_{I} >$

where  $\Lambda_I = \Lambda_{\phi} \cap \Lambda$  and  $\sqsubset_I$  is given by:

$$(\mathbf{A}\lambda,\mu::(\lambda\in\Lambda_{I}\wedge\mu\in\Lambda_{I}\wedge\lambda\sqsubset_{\phi}\mu)=(\lambda\sqsubset_{I}\mu))$$

#### end of definition

Notice that  $\Lambda_i$  in definition 2.7, "restriction of comminstorder", is an <u>initial</u> set of comminsts.

Analogously to comministorders, we define commisgorders. A commisgorder is a pair  $\langle \Lambda, \Box \rangle$ , in which  $\Lambda$  denotes a finite <u>initial</u> set of commisgs and " $\Box$ " is a strict partial order on  $\Lambda$ . For commisgorder  $\phi$ ,  $\Lambda_{\phi}$  denotes the set of commisgs of commisgorder  $\phi$ , and  $\Box_{\phi}$  denotes the strict partial order of commisgorder  $\phi$ .

In the strict partial order of a commsigorder, a commsig is preceeded by every commsig with the same output commport and a smaller number; notice that commsigs with the same output commport also have the same input commport.

#### postulate 2.8

For commsigorder  $\phi$ ,

$(\mathbf{A}\alpha,\beta,m,n:(\alpha,n,\beta)\in\Lambda_{\phi}\wedge m\in\mathbb{N}^{+}\wedge m< n:(\alpha,m,\beta)\sqsubset_{\phi}(\alpha,n,\beta))$

#### end of postulate

For commsigorders we define the restriction to an initial set of commsigs:

#### definition 2.9 restriction of commsigorder

For commsigorder  $\phi$  and initial set of commsigs  $\Lambda$ , we denote the commsigorder that is *the restriction of*  $\phi$  *to*  $\Lambda$  by  $\phi^{\dagger}\Lambda$ ; it is defined by:

$$\phi \mid \Lambda \stackrel{\text{def}}{=} < \Lambda_{I}, \sqsubset_{I} >$$

where  $\Lambda_i = \Lambda_{\phi} \cap \Lambda$  and  $\Box_i$  is given by:

$(\mathbf{A}\lambda,\mu::(\lambda\in\Lambda_{I}\wedge\mu\in\Lambda_{I}\wedge\lambda\sqsubset_{\phi}\mu)=(\lambda\sqsubset_{I}\mu))$

## end of definition

Notice that  $\Lambda_i$  in definition 2.9, "restriction of commsigorder", is an <u>initial</u> set of commsigs.

# 2.0.3 Iodirs and modules

An *iodir*, say  $\Phi$ , is a pair  $\langle \Phi^o, \Phi^i \rangle$ , in which  $\Phi^o$  is a set of output commports and  $\Phi^i$  is a set of input commports.

## postulate 2.10

For iodir  $\Phi$ ,

- (i)  $\Phi^o \subseteq \Psi^o$

- (ii)  $\Phi^i \subseteq \Psi^i$

## end of postulate

We define the *reflection* of an iodir. The reflection of an iodir is an iodir.

# definition 2.11 reflection of iodir For an iodir $\Phi$ , the reflection of $\Phi$ , which is denoted by $\overline{\Phi}$ , is defined by $\overline{\Phi}^o \stackrel{\text{def}}{=} \Phi^i$ $\overline{\Phi}^i \stackrel{\text{def}}{=} \Phi^o$

end of definition

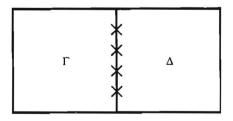

A module, say  $\Delta$ , is a pair <IO $\Delta$ , CB $\Delta$ >, in which IO $\Delta$  is an iodir and CB $\Delta$  is a set of comministorders; IO $\Delta$  is called the *iodir of module*  $\Delta$ , and CB $\Delta$  is called the *communication behavior of module*  $\Delta$ .  $\Psi^o_{\Delta}$  is called the set of output commports of module  $\Delta$ ,  $\Psi^i_{\Delta}$  is called the set of input commports of module  $\Delta$ . Of course, IO $\Delta = \langle \Psi^o_{\Delta}, \Psi^i_{\Delta} \rangle$ . We postulate that no two commports of  $\Delta$  match, that the empty comministorder, i.e.  $\langle \emptyset, \emptyset \rangle$ , is in CB $\Delta$ , and that CB $\Delta$  is closed with respect to restriction.

## postulate 2.12

For module  $\Delta$ ,

(i) for every output commport  $\alpha \in \Psi_{\Delta}^{o}$  and input commport  $\beta \in \Psi_{\Delta}^{i}$ ,

$\neg$  ( $\alpha$  MATCH  $\beta$ )

(ii) for every comminstorder  $\phi \in CB\Delta$ ,

$\Lambda_{\phi} \subseteq \{\Psi^{o}_{\Delta} \cup \Psi^{i}_{\Delta}\} \times \mathbb{N}^{+}$

- (iii)  $\langle \emptyset, \emptyset \rangle \in CB\Delta$ ,