### Handshake circuits: an intermediary between communicating processes and VLSI

Citation for published version (APA):

Berkel, van, C. H. (1992). Handshake circuits: an intermediary between communicating processes and VLSI. [Phd Thesis 2 (Research NOT TU/e / Graduation TU/e), Mathematics and Computer Science]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR372904

DOI:

10.6100/IR372904

Document status and date:

Published: 01/01/1992

Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 04. Oct. 2023

# Handshake circuits: an intermediary between communicating processes and VLSI

### Kees van Berkel

# Handshake circuits: an intermediary between communicating processes and VLSI

# Handshake circuits: an intermediary between communicating processes and VLSI

#### **Proefschrift**

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof. dr. J.H. van Lint, voor een commissie aangewezen door het College van Dekanen in het openbaar te verdedigen op woensdag 6 mei 1992 om 16.00 uur

door

Cornelis Hermanus van Berkel

geboren te Leimuiden

#### Acknowledgements

The work presented here grew out of the project "VLSI programming and silicon compilation" being conducted at Philips Research Laboratories Eindhoven since 1986. This project combines the research efforts of Ronan Burgess, Joep Kessels, Marly Roncken, Ronald Saeijs, Frits Schalij and myself. Together we defined the VLSI-programming language Tangram, built a silicon compiler, developed interesting demonstrators, and tested functional silicon. This thesis could only be written on the fertile ground of this inspiring and pleasant cooperation.

I am grateful to the management of Philips Research Laboratories, in particular to Theo Claasen and Eric van Utteren, for their support of the project, the provision of a very stimulating working environment, and their encouraging me to write this thesis.

Special thanks go to Cees Niessen. Numerous illuminating, critical, stimulating, and curious discussions with him helped me in choosing directions and setting priorities.

I am indebted to Martin Rem who supervised the work on this thesis. He also helped me in focusing this thesis on handshake circuits and separating essential issues from side issues. Also, his active interest in the topic provided a constant source of inspiration and motivation.

A number of people have given me substantial constructive criticism on all or parts of a draft version of this thesis. For their help I would like to thank Jos Baeten, Ronan Burgess, Ton Kalker, Joep Kessels, Frans Kruseman Aretz, Ad Peeters, Marly Roncken, Frits Schalij, and Kees Vissers.

Finally, this thesis could not have been built without TeX and LeTeX, for which I thank Donald Knuth and Leslie Lamport.

# Contents

| 0 | Intr | oduction                                            | 1   |

|---|------|-----------------------------------------------------|-----|

|   | 0.0  | VLSI systems                                        | 3   |

|   | 0.1  | VLSI circuits                                       | 6   |

|   | 0.2  | Overview of this thesis                             | 12  |

| 1 | Intr | oduction to Tangram and handshake circuits          | 15  |

|   | 1.0  | Introduction                                        | 15  |

|   | 1.1  | Some simple Tangram programs                        | 18  |

|   | 1.2  | Some simple handshake circuits                      | 20  |

|   | 1.3  | Cost-performance trade-offs                         | 25  |

|   | 1.4  | More examples                                       | 31  |

|   | 1.5  | Epilogue                                            | 39  |

| 2 | Han  | dshake processes                                    | 41  |

|   | 2.0  | Introduction                                        | 41  |

|   | 2.1  | Notational conventions                              | 42  |

|   | 2.2  | Handshake structures                                | 46  |

|   | 2.3  | Handshake processes                                 | 51  |

|   | 2.4  | The complete partial order $(\prod A, \sqsubseteq)$ | 67  |

|   | 2.5  | Nondeterminism                                      | 73  |

| 3 | Han  | dshake circuits                                     | 77  |

|   | 3.0  | Introduction                                        | 77  |

|   | 3.1  | Parallel composition                                | 78  |

|   | 3.2  | Handshake circuits                                  | 92  |

| 4 | Seq  | uential handshake processes                         | 97  |

|   | 4.0  | Introduction                                        | 97  |

|   | 4.1  | Sequential handshake processes                      | 97  |

|   | 4.2  | Process calculus                                    | 103 |

|   | 4.3  | Examples                                            | 114 |

|   | 4.4  | Directed communications                             |     |

| 5                | Tang  | gram                                  |  |   |      |  |   | 123 |

|------------------|-------|---------------------------------------|--|---|------|--|---|-----|

|                  | 5.0   | Introduction                          |  |   | <br> |  |   | 123 |

|                  | 5.1   | Tangram                               |  |   | <br> |  |   | 123 |

|                  | 5.2   | Tangram semantics                     |  |   | <br> |  |   | 130 |

|                  | 5.3   | Core Tangram                          |  |   |      |  |   | 132 |

| 6                | Tang  | gram → handshake circuits             |  |   |      |  |   | 137 |

|                  | 6.0   | Introduction                          |  |   | <br> |  |   | 137 |

|                  | 6.1   | Compilation function                  |  |   |      |  |   | 139 |

|                  | 6.2   | Compilation theorem                   |  |   | <br> |  | • | 156 |

| 7                |       | dshake circuits → VLSI circuits       |  |   |      |  |   | 165 |

|                  | 7.0   | Introduction                          |  |   |      |  |   | 165 |

|                  | 7.1   | Peephole optimization                 |  |   |      |  |   | 166 |

|                  | 7.2   | Non-receptive handshake components    |  |   |      |  |   | 169 |

|                  | 7.3   | Handshake refinement                  |  |   |      |  |   |     |

|                  | 7.4   | Message encoding                      |  |   |      |  |   | 178 |

|                  | 7.5   | Handshake components → VLSI circuits  |  |   |      |  |   | 180 |

|                  | 7.6   | Initialization                        |  |   |      |  |   |     |

|                  | 7.7   | Testing                               |  |   | <br> |  |   | 191 |

| 8                | In p  | ractice                               |  |   |      |  |   | 199 |

|                  | 8.0   | VLSI programming and compilation      |  |   |      |  |   | 200 |

|                  | 8.1   | An appraisal of asynchronous circuits |  | ٠ |      |  | • | 211 |

| A                | Dela  | y insensitivity                       |  |   |      |  |   | 217 |

| В                | Fail  | ure semantics                         |  |   |      |  |   | 225 |

| Bibliography     |       |                                       |  |   |      |  |   | 235 |

| Gl               | ossar | y of symbols                          |  |   |      |  |   | 243 |

| Index            |       |                                       |  |   |      |  |   | 248 |

| Samenvatting     |       |                                       |  |   |      |  |   | 251 |

| Curriculum vitae |       |                                       |  |   |      |  |   | 253 |

# Chapter 0

### Introduction

This thesis is about the design of digital VLSI circuits. Whereas LSI circuits perform basic functions such as multiplication, control, storage and digital-to-analog conversion, VLSI circuits contain complex compositions of these basic functions. In many cases all data and signal processing in a professional or consumer system can be integrated on a few  $cm^2$  of silicon. Examples of such "systems on silicon" can be found in

- Compact Disc (CD) players,

- Compact Disc Interactive (CDI) players,

- Digital Compact Cassette (DCC) players,

- Digital Audio Broadcast (DAB) receivers,

- cellular radios and mobile telephones,

- High-Definition TeleVision (HDTV) sets,

- digital video recorders,

- display processors,

- car-navigation systems,

- image processors, and

- digital test and measurement systems.

2 Introduction

These systems generally process analog as well as digital signals, but the digital circuits dominate the surface of an IC. The memory needed for storing intermediate results often covers a significant fraction of the silicon area.

Systems on silicon tend to become more complex and tend to increase in number. The increase in complexity follows from advancements in VLSI technology, and the rapid growth of the number of transistors integrated on a single IC. The constant reduction of the costs of integration makes integration economically attractive for an increasing number of systems. Also, the rapid succession of generations of a single product increases the pressure on design time. The ability to integrate systems on silicon effectively, efficiently, and quickly has thus become a key factor in the global competition in both consumer and professional electronic products. This recognition has lead to a quest for design methods and tools that increase design productivity and reduce design times.

At Philips Research a number of approaches to this goal are being investigated [WD89,NvBRS88,LvMvdW\*91]. One of these, viz. "VLSI programming and compilation to asynchronous circuits" forms the background of the research reported in this thesis. The central idea is that of viewing VLSI design as a programming activity, and thereby capitalizing on the achievements in computing science with regard to complexity bridling [Sei80,Rem81,vdS85,Mar89].

VLSI programming assumes a VLSI-programming language that provides the programmer with a suitable abstraction from the VLSI technology and circuit techniques. This abstraction allows systems on silicon to be designed by system (e.g. digital audio) specialists without detailed involvement of IC specialists. Ideally, this avoids the costly, time-consuming and error prone transfer of design data from system specialists to VLSI-circuit specialists. The degree of abstraction is constrained by the required cost and performance of the resulting IC. A VLSI programming language is thus a compromise between programming convenience and silicon efficiency.

The automatic translation of VLSI programs into VLSI circuits is often called *silicon compilation*. This thesis proposes a compilation scheme that results in asynchronous circuits. This relatively uncommon circuit style has specific advantages with regard to system modularity and IC power consumption.

The central contribution of this thesis is that of *handshake circuits*: an intermediary between VLSI programs and VLSI circuits. A handshake circuit is a network of asynchronous components connected by point-to-point channels along which components interact by means of handshake signaling. The role of an intermediary is generally that of separation of – more or less orthogonal – concerns. This introductory chapter continues with taking stock of these concerns and ends with an overview of this thesis.

VLSI systems 3

First we shall have a closer look at a particular system on silicon: a Compact Disc Decoder IC. This example shows the variety in interfaces, protocols and data types involved in system design.

The next section examines the VLSI medium by means of the mainstream VLSI technology CMOS. A computation will be viewed in terms of voltage transitions on wires. Differences between synchronous and asynchronous circuits are explained by discussing how to deal with the phenomenon called *interference*.

The final section contains a roadmap to this thesis and positions the handshake circuits as an intermediate form between VLSI programs and VLSI circuits.

#### 0.0 VLSI systems

One of the key modules of the Compact Disc (CD) player is its chip set. Other key modules are: a laser-optical pick-up, a turn table, and a user interface consisting of a key-board and a display. Typically, the chip set consists of a servo controller, a decoder, a digital filter, a digital-to-analog converter, a DRAM, and a micro processor [Phi90]. There is a tendency towards single-chip solutions. The decoder has been selected to illustrate a number of issues relevant to VLSI programming.

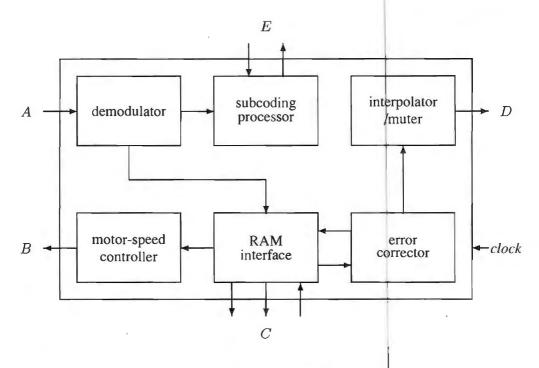

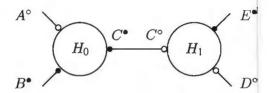

The main function of the decoder is to convert the digital signal from the optical disc into a digital (stereo) audio signal. The block diagram of the decoder in Figure 0.0 has been adapted from [Phi90]. The main parts of the interface of the decoder are:

- clock: crystal oscillator input (11.2896 MHz),

- A: bit stream from the optical pick-up (average bit frequency: 4.32 MHz),

- B: disc-motor control signal, pulse-width modulated (88.2 kHz, duty factor ranges from 1.6 % 98.4 %),

- C: interface to external DRAM of 16k × 4 bit (12 *clock* cycles for a single read or write access),

- D: bit serial output of stereo samples (2  $\times$  16 bit) with an error flag per sample in parallel (rate:  $clock/4 \approx 2.82$  MHz),

- E: subcode signal to external microprocessor (bit-serial, in bursts of 10 bit at 2.82 MHz; one handshake per burst).

4 Introduction

Figure 0.0: Simplified block diagram of the Compact Disc Decoder SAA7310.

The above overview indicates a variety in data rates and clock frequencies. Most frequencies are derived from clock by division. The incoming bit stream A, however, contains an implicit clock that must be recovered through frequency and phase detection. This clock frequency varies with the rotation speed of the disc. A feed back mechanism guarantees that on the average the incoming data rate matches the outgoing data rate.

There is also a considerable variety of data types involved. The incoming data are a formated stream of bits. Frames of 32 symbols of 8 bit are extracted internally. The arithmetic applied to these symbols, as required for error correction, is in the Galois Field  $GF(2^8)$ . The interfacing to the RAM requires address computations in natural numbers in the range  $[0..2^{16})$ . Audio samples are pairs of integers in the range  $[-2^{15}..2^{15})$ . A general-purpose VLSI-programming language must be able to deal with this variety in data rates and data types.

The behavior of VLSI programs is restricted to discrete events and discrete values. Conversion to and from time-continuous and/or continuous values requires adapter circuits such as digital-to-analog converters.

VLSI systems 5

The main submodules of the decoder are (with reference to Figure 0.0):

• Demodulator: extracts a clean digital signal and a clock signal from the disc signal. This digital signal is then demodulated and converted into frames of 32 symbols of 8 bit, error flags and subcode information. The rate of the extracted clock signal follows the rotation speed of the disc. This clock is local to the Demodulator.

- Subcoding processor: accumulates subcode words of 96 bit, performs a cyclic redundancy check (CRC), and sends the corrected word (80 bit) to an external microprocessor on an external clock.

- RAM interface: controls the traffic "Demodulator → RAM → Error corrector → RAM → Error corrector". The external RAM is used for two distinct purposes: that of a first-in first-out queue (FIFO) to buffer the irregularly produced data from disc, and that of a store for de-interleaving the symbol stream.

- *Motor-speed controller*: controls the speed of the disc motor based on the degree of occupancy of the FIFO.

- *Error corrector*: corrects the code words according to Cross Interleaved Reed-Solomon Code (CIRC) with a maximum of 2 × 2 errors per frame of 32 symbols.

- *Interpolator/Muter*: converts symbols in stereo audio samples, interpolates single errors and mutes in the presence of two or more successive erroneous samples.

These submodules operate in parallel. It is therefore hard to describe the behavior of the decoder in a traditional imperative programming language (such as Pascal, C or Fortran). The behavior of each submodule, however, can be conveniently described in such a language extended with appropriate primitives for input and output.

This describes exactly the idea of Communicating Sequential Processes (CSP) as proposed by Hoare in [Hoa78], and forms the basis of the VLSI-programming language Tangram <sup>0</sup> developed at Philips Research.

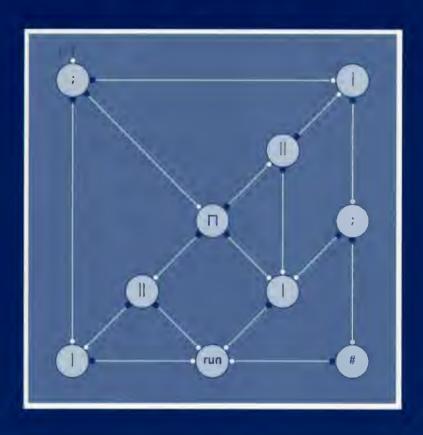

<sup>&</sup>lt;sup>0</sup>Tangram is the name of an ancient Chinese puzzle [Elf76]. It consists of a few, simple forms (five triangles of three different sizes, one square and one parallelogram), a simple composition rule (forms may not overlap), and allows the construction of a large variety of intricate and fascinating shapes. This view on design also shaped our VLSI-programming language Tangram.

6 Introduction

#### 0.1 VLSI circuits

A typical 1991 VLSI circuit is almost  $1 cm^2$  in size and consists of about 100,000 transistors, 100 meter wiring and 100 bonding pads. During its operation, when connected to a power supply, more than a  $10^{11}$  events (voltage transitions) may occur each second, of which often less than one percent are observable at the bonding pads. An event consumes about a picojoule of energy; the power consumption of a chip is usually less than one Watt.

These rounded numbers apply to digital VLSI circuits manufactured in CMOS, the dominant VLSI technology of today. For state-of-the-art chips the above numbers may be multiplied by an order of magnitude. The yearly world production of integrated transistors is in the order of 10<sup>15</sup>, or about a thousand transistors per world citizen per day<sup>1</sup>.

#### **Transitions**

The voltage transitions observable at the bonding pads are the only evidence of a computation going on inside a VLSI chip, apart from indirect evidence such as power consumption. We shall therefore first concentrate on such events, in particular on their occurrences on wires.

Wires are metal conductors usually connecting two or more (distant) transistors. Electrically they can be regarded as capacitors to the IC substrate. Except for the very long wires, the metal area may be considered *equipotential*: differences in potential along the wire tend to equalize in a time period shorter than the switching time of a transistor <sup>2</sup>. For long wires and wires made of material with a high sheet resistance such as polysilicon this approximation is not valid. Then the transmission delays caused by wire resistance and the speed of light may no longer be neglected.

A wire may be charged ("pulled up") through a path of transistors connected to the power-supply rail. Such a pull-up path usually consists of pMOS transistors, a type of transistor that conducts when its gate potential is low, i.e. connected to an uncharged wire. Similarly, wires may be discharged ("pulled down") by a path of nMOS transistors connected to ground. An nMOS transistor conducts when its gate potential is high. Often such paths may be merged, i.e.

<sup>&</sup>lt;sup>1</sup>A similar type of estimate was presented during an invited lecture delivered by G. Moore at the Decennial Caltech Conf. on VLSI, 1989.

<sup>&</sup>lt;sup>2</sup>For equipotential wires the image of a voltage transition propagating along a wire is false; when applied with care, the metaphor (as e.g. applied in the foam-rubber wrapper principle [Udd84]) may be useful.

VLSI circuits 7

individual transistors or combinations of transistors may be part of more than one path.

Generally, the situation in which both a pull-up path and a pull-down path compete in charging and discharging a wire is avoided, or at least restricted to a very short duration. For longer durations this form of short-circuit dissipation may form a considerable power drain.

When a wire is neither pulled up nor pulled down (it "floats"), its potential may not be constant due to charge leakage. A circuit is *static* if it has the property that its wires never float. If the floating of wires is essential for the operation of a circuit, the circuit is called *dynamic*.

#### Interference

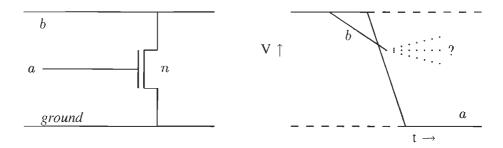

So far, it was tacitly assumed that voltage transitions are complete, i.e. they proceed all the way from the ground to the supply voltage or vice versa. But what if the (dis-)charging of a wire is interrupted? Figure 0.1 depicts two wires a and b and an nMOS transistor n.

Figure 0.1: Interference occurs e.g. when wire a is discharged during the discharging of b.

When wire a has a high potential, the nMOS transistor forms a conducting path between wire b and ground. Assume that b is being discharged through a, and the potential on a drops to the ground level: the discharging of b is interrupted. Wire b is discharged partially and its potential is somewhere between the ground and the supply voltage. In such a situation, the transition on a is said to *interfere* with the transition on a. The transistors controlled by a may or may not have changed their state of conductance, and may or may not be involved in (dis-)charging other wires, et cetera. If a is subsequently recharged, the effect of this "runt" pulse on other wires critically depends on sizes of currents, capacitors,

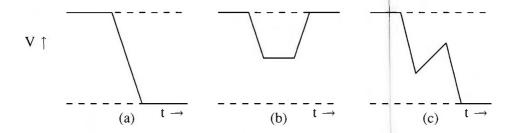

threshold voltages of transistors and the time interval between the two events. The runt pulse may have caused a multitude of partial or complete transitions on other wires, or not. Similar complications occur when the discharging of b is interrupted by a short period of charging. Figure 0.2 gives examples of a proper transition (monotonic and complete), a runt pulse and a non-monotonic transition.

Figure 0.2: A proper transition (a), a runt pulse (b), and a non-monotonic transition (c).

There are two ways of dealing with interference:

- Accept the possibility of interference, but insist that at specific moments the mess has cleared, i.e. the circuit is in a quiescent state and all wires are stable at well-defined potentials. Synchronous timing disciplines are based on this principle: an externally supplied clock defines the moments at which the circuit *must* be quiescent.

- Avoid interference: guarantee that all transitions are monotonic and complete. Many *asynchronous* timing disciplines are based on this principle, *self-timed* and *delay-insensitive* being two of them.

The overwhelming majority of today's digital VLSI circuits are synchronous.

#### **Proper transitions**

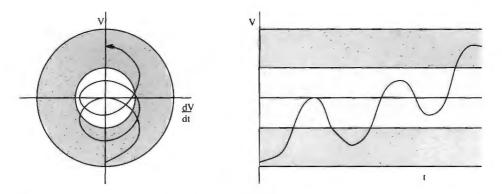

Our interest in asynchronous circuits justifies some elaboration on the notion of proper transition. A nice and effective way to capture all requirements on proper transitions is by means of a phase diagram as proposed in [Bro89]. The evolution of the voltage of a wire in time is then recordered by a so-called trajectory in the space  $(V, \, dV/dt)$ . The values of V and dV/dt are bounded by a doughnut shape as in Figure 0.3. With this choice of axis orientations, changes in V result in

VLSI circuits 9

Figure 0.3: Phase and time diagram for a runt pulse followed by a non-monotonic transition.

counter-clockwise trajectories. Lower bounds on (V, dV/dt) exclude runt pulses and non-monotonic transitions as illustrated in Figure 0.3.

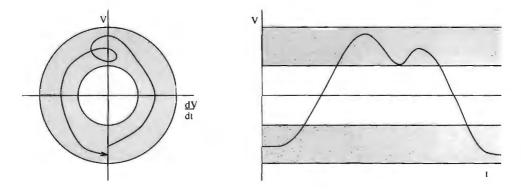

The thickness of the doughnut determines amongst others the margins in the voltage to count as logical false or true. Within these margins runt pulses may occur, as illustrated in Figure 0.4. The doughnut also bounds the slope of a transition. This is significant, because different transistors may change their state of conductance at different voltage levels of the controlling gate. Transistors controlled by the same wire may then "observe" the same transition at different moments. Bounds on the slope of a transition therefore effectively limit these time differences (cf. isochronic forks in Section 7.5).

Figure 0.4: Phase and time diagram for two proper transitions in succession.

10 Introduction

#### **Asynchronous circuits**

The method addressed in this thesis aims at the design of asynchronous VLSI circuits. The key question is then how to guarantee absence of interference. How to control the timing and dependencies of billions of transitions in such a way that the integrity of every single transition is assured?

The central idea is to construct the circuit from elementary circuits that indicate by means of transitions on output wires that transitions on specific input wires will not cause interference<sup>3</sup>. Circuits organized according to this principle are said to be *self-timed* [Sei80]

Delay-insensitive circuits are a restricted form of self-timed circuits. A circuit is delay-insensitive if the absence of interference does not depend on any assumption about delays of these elementary circuits and wires [vdS85]. In delay-insensitive circuits only point-to-point wires between elementary circuits are allowed, i.e. wires that connect one output to one input. A major advantage of delay-insensitive circuits is their modularity: a delay-insensitive composition of subcircuits will operate correctly, regardless of the response times of the subcircuits and regardless of the delays introduced by the connecting wires. An appraisal of delay-insensitive circuits is given in Section 8.1.

The constituent elementary circuits of self-timed and delay-insensitive circuits may be of arbitrary size, ranging from an inverter to an embedded self-timed RAM. It is attractive to have a finite set of elementary circuits from which delay-insensitive circuits can be constructed for any specification. Such a universal basis of elementary circuits has been proposed in [Ebe89]. Unfortunately, circuits constructed from this basis exclusively tend to be unpractically large.

A more practical set of elementary circuits has been proposed by Martin [Mar85b]. These elementary circuits are called *VLSI operators* and form a generalization of the traditional gates. Unfortunately, the class of delayinsensitive circuits that can be constructed from VLSI operators is severely restricted [BE90]. With the so-called *isochronic fork* as only concession to delay insensitivity [Mar90] reasonably efficient circuits can be constructed (cf. Section 7.5).

<sup>&</sup>lt;sup>3</sup>The requirement of absence of interference restricts the behavior of the environment as well. In some cases this may be too restrictive. For instance, the handling of concurrent requests for a single resource requires a circuit that assures mutual exclusion. Inside such a mutual-exclusion circuit interference cannot be avoided. It is a good idea to localize the interfering transitions inside elementary circuits such as arbiters.

VLSI circuits 11

#### Cost and performance issues

A 1991 CMOS transistor is less than  $10~\mu m^2$  in area. This would allow for a packing density of over 100,000 transistors per  $mm^2$ . The densest practical circuits are embedded memories with about 10,000 transistors per  $mm^2$ . The average density in other VLSI circuits is almost an order of magnitude below this number. The almost two orders of magnitude difference between possible and practical transistor density is caused by wires. A quick glance at any VLSI circuit layout shows that wires dominate the circuit area and therefore production costs. The area of an IC is still a most critical resource: 20 % area overhead in a competitive market is considered a serious handicap, and 50 % area overhead is usually acceptable only for prototype circuits, or for small series.

The time it takes to (dis-)charge a wire is proportional to its capacitance, and, for a given width, this is proportional to its length. For average wires this is about 1 nanosecond. For longer wires this may exceed 10 nanoseconds. The switching time of a transistor is well below 1 nanosecond. Clearly, the wires determine the operating speed of a VLSI circuit.

For a given power-supply voltage, the energy consumed by a single event is proportional to the capacitance of the wire on which it occurs. Consequently, the energy required for a computation depends on the number of events and the lengths of the wires involved. For a given set of events the wires determine the energy consumption of a circuit. More and more often these systems on silicon end up in portable products such as walkmans and notebooks. Efficient usage of battery power is then an important design consideration. Asynchronous circuits potentially consume less energy, because there is no energy used for clock distribution and no energy is wasted in interference.

In summary: wires dominate concerns for cost and performance in every respect. The wires determine the area, the computation time and the energy consumption [SM77,Sei84]. Every VLSI design method, existing or novel, must acknowledge this fact.

#### **Testing**

The VLSI fabrication process is extremely complicated. For moderately sized circuits the yield is about 50 %, i.e. 50 % of the manufactured circuits function correctly. For complex circuits in an advanced technology the yield may well be below 10 %. To make things worse, for larger circuits the yield decreases exponentially with the circuit area. This has two important consequences: circuit area is a most critical resource and there is a *test problem*.

12 Introduction

The problem of testing is how to discriminate between a correct circuit and a faulty circuit. This bears no relation with software testing. It is assumed that the circuit design is correct and that a possible malfunctioning is caused by a defect introduced during the fabrication of the circuit. For advanced production technologies such defects cannot be avoided: their density is about 1 per  $cm^2$ .

The problem of testing consists of two parts:

- bring the circuit into a state where an assumed fault makes a difference in the subsequent computation;

- detect this possible difference.

Given the exorbitant number of possible faults and circuit states on the one hand and the limited number of pads to control and observe the circuit behavior on the other hand, it is clear that the test problem is a hard one, in every respect. Testing of circuits is also costly: provisions for enhancing the testability of a circuit and executing tests may well account for 10 to 30 % of the price of an IC.

Given the complexity of testing, the user of an IC is not in a position to test an IC effectively. It is the joint responsibility of the circuit designer and the manufacturer. A novel VLSI-circuit design method without a systematic, effective and affordable test method simply is not viable.

#### 0.2 Overview of this thesis

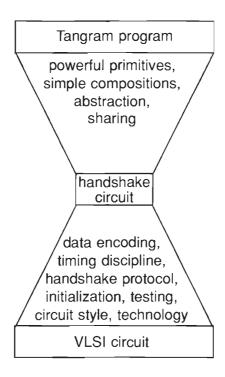

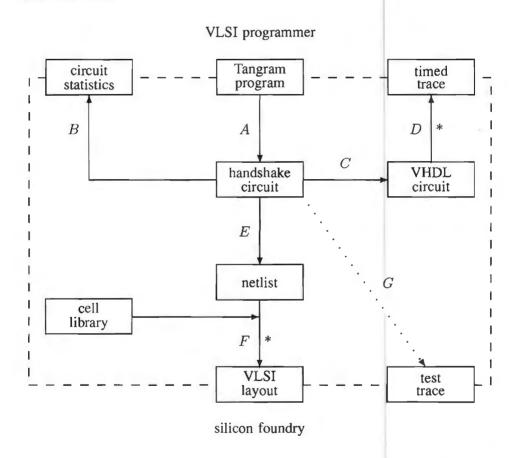

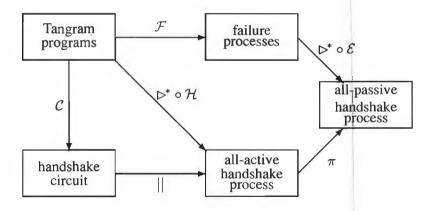

Handshake circuits are intended as an intermediary between VLSI programs and VLSI circuits. It thus separates concerns for systematic and efficient VLSI-programming from concerns at the VLSI-circuit level, such as absence of interference, data encoding, initialization, and testing (cf. Figure 0.5). The narrow waist of the "hourglass" is intended to reflect the clear separation realized by handshake circuits.

Handshake circuits can also be considered as a VLSI architecture. According to Webster's Ninth New Collegiate Dictionary [Mis87] one of the meanings of architecture is "a unifying or coherent form or structure". Handshake circuits unite control, storage, communication, logic and arithmetic in a single structure, supported by a single form of interaction: that of handshake signaling.

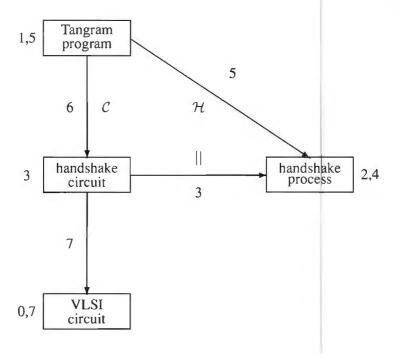

An overview of this thesis is presented with reference to Figure 0.6. By means of a variety of examples Chapter 1 presents an informal introduction to Tangram and handshake circuits. Concerns for cost and performance get special

Figure 0.5: Handshake circuits: a separation of VLSI programming and VLSI circuits concerns.

attention, as they make VLSI programming different from (and also more difficult than) traditional computer programming.

The body of this thesis is a theory for handshake circuits. The key notion is that of *handshake process*. A handshake process is a mathematical object that describes a handshake-communication *behavior*. This handshake behavior may be that of the components of a handshake circuit (Chapter 2).

A handshake circuit is a set of handshake processes that satisfy a simple composition rule (Chapter 3). The behavior of the handshake circuit is defined through parallel composition '||' of its constituent components, and is, again, a handshake process. In Appendix A the delay insensitivity of handshake circuits is related to the theory reported in the literature.

Chapter 4 develops a calculus for handshake processes. This calculus allows concise descriptions of behaviors of handshake components.

In Chapter 5 a precise definition of Tangram is given. For a subset of Tan-

14 Introduction

Figure 0.6: An overview of this thesis (numbers denote chapters).

gram, which we call  $Core\ Tangram$ , a formal denotation ' $\mathcal{H}$ ' is given in terms of handshake processes. Here we use the calculus of Chapter 4. In Appendix B a link to the well-known failure semantics of CSP is established.

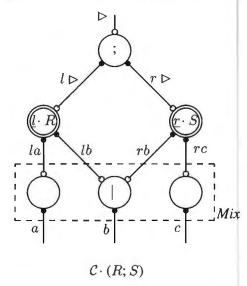

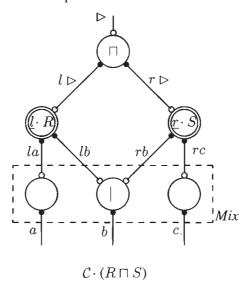

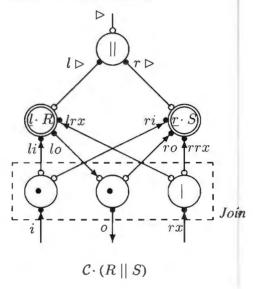

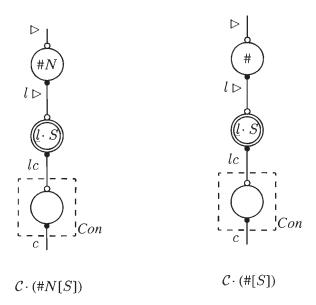

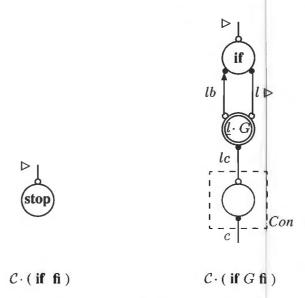

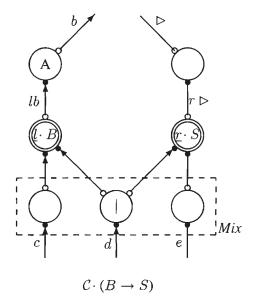

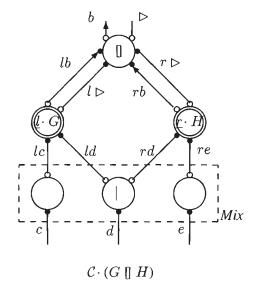

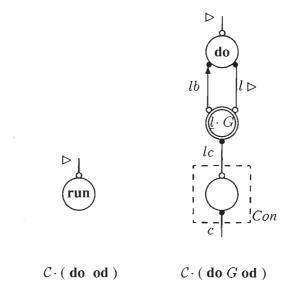

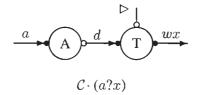

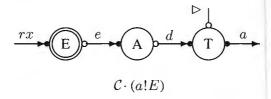

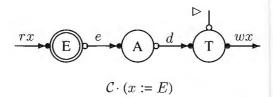

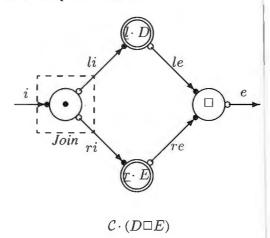

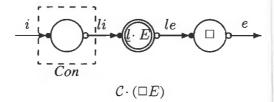

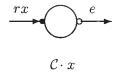

Chapter 6 describes the translation of Tangram programs into handshake circuits by means of the mathematical function ' $\mathcal{C}$ '. For Core Tangram it is proven that the behavior of the compiled handshake circuit is equivalent to that of the original program in a well-defined sense.

The realization of handshake circuits in VLSI is the subject of Chapter 7. Due to the variety of issues and the large number of choices involved we have not pursued completeness here. Issues such as peephole optimization, handshake refinement, data encoding, decompositions into VLSI-operator networks, initialization and testing are discussed in varying degrees of depth and completeness.

Chapter 8 discusses some practical experiences with VLSI programming and silicon compilation at Philips Research.

## Chapter 1

# Introduction to Tangram and handshake circuits

#### 1.0 Introduction

This thesis pursues a programming approach to the design of digital VLSI circuits. In such an approach the VLSI-system designer constructs a program in a suitable high-level programming language. When he is satisfied with his program the designer invokes a so-called *silicon compiler* which translates this program into a VLSI-circuit layout.

The choice of the programming language is a crucial one, for it largely determines the application area, the convenience of design, and the efficiency of the compiled circuits. A good VLSI-programming language

- 0. is general purpose in that it allows the description of all digital functions;

- 1. encourages the *systematic* and *efficient* design of programs by abstracting from circuit, geometry and technology details;

- 2. allows the *automatic* translation into *efficient* VLSI circuits and test patterns.

Below follows a motivation for these requirements.

- 0. A wide range of applications is required to justify the investment in tools and training.

- 1. A major gain in design productivity can be expected by designing in a powerful high-level language. Furthermore, system designers do not need to

resort to VLSI specialists. Systematic design methods, supported by mathematical reasoning, are required to deal with the overwhelming complexity involved in the design of VLSI systems.

2. Automatic translation to VLSI circuits avoids the introduction of errors at the lower abstraction levels. It also becomes attractive to design alternative programs and compare the translated circuits in costs and performance.

Any such language is of necessity a compromise between convenience of design and efficiency of the result.

Traditional programming languages such as Pascal and C can be considered for this purpose. However, these languages were conceived for the sequential execution on a specific architecture. It is not at all clear how to benefit from the parallelism so abundantly available in VLSI, when the program describes a total order of all elementary computation steps. On the other hand, these so-called *imperative* programming languages are successful in that they are general purpose and offer a good compromise between convenience of design and efficiency of the compiled machine code.

In an effort to add parallelism to the traditional sequential programming languages, Hoare developed Communication Sequential Processes [Hoa78]. CSP soon became an important vehicle for the (theoretical) study of *concurrency* in computing science. It also was the basis for OCCAM [INM89], a language suitable for programming networks of microprocessors. The suitability of CSP-based languages for VLSI programming has been addressed in [Mar85a,vBRS88].

In terms of CSP a VLSI circuit can be described as a fixed network of processes connected by channels. These processes are simultaneously active and co-operate by synchronization and the exchange of messages along channels. The behavior of each process can be described in a C or Pascal-like language to which proper primitives for synchronization and communication have been added.

If one considers the translation of such programs into circuits, it is attractive to preserve the parallelism of the program by translating each process into a subcircuit, and by translating each channel into a set of wires. This "transparent" way of translating programs into circuits has the advantage that the programmer has control over the efficiency and performance of his circuits.

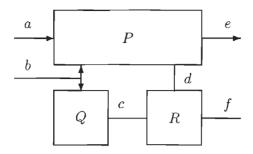

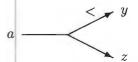

Figure 1.0 depicts an example of a network of three communicating processes P, Q and R. The arrows indicate the directions of data transport along the channels. Channel a is an input to P, b is an input channel that forks to two processes, and e is an output channel. Channels c, d and f do not convey data: they are used for synchronization only.

Figure 1.0: Communicating Sequential Processes.

One of the attractions of CSP is that it allows arbitrary numbers of processes of arbitrary complexity. The table below gives an impression of what can be realized in a single 100,000 transistor IC in terms of communicating processes. For a single IC the product of the degree of parallelism and the grain size (size of each process, measured e.g. in number of transistors) is more or less constant.

| degree of      | # processes | # transistors | example            |

|----------------|-------------|---------------|--------------------|

| parallelism    |             | / process     |                    |

| sequential     | 1           | 100k          | microprocessors    |

| coarse-grained | 10          | 10k           | digital audio (CD) |

| fine-grained   | 100         | 1 k           | systolic arrays    |

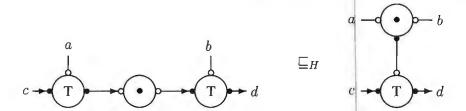

So far the notion "process" has been used rather loosely. In the sequel it is used to denote the set of observable communication behaviors of an object, irrespective of how the object is organized internally. The behavior of a network of processes can also be described as a single process. A program is an alternative way to define a process.

This thesis uses Tangram as a VLSI programming language. Tangram has been developed at Philips Research. It is based on Hoare's CSP [Hoa85] and includes Dijkstra's guarded-command language [Dij75].

The translation of Tangram programs into VLSI circuits has so-called *hand-shake circuits* as an intermediary. Handshake circuits are networks of elementary asynchronous processes that communicate according to a handshake protocol. These elementary processes are called handshake components. The translation of Tangram programs into handshake circuits requires a modest set of different handshake components. The translation method is highly transparent, which allows the VLSI programmer to infer cost and performance of the compiled circuit

fairly directly from his Tangram program.

This chapter gives an informal introduction to Tangram by means of a series of small programs. For many of the programs or program fragments the corresponding handshake circuits are presented. The examples have been chosen so as to cover most of Tangram, and to give a flavor of VLSI programming and the translation of Tangram programs into handshake circuits.

#### 1.1 Some simple Tangram programs

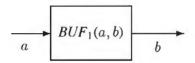

One of the simplest Tangram programs is  $BUF_1(a, b)$ , a one-place buffer:

$$(a?W \& b!W) \cdot |[x : \mathbf{var} \ W \ | \ \#[a?x; b!x]]|$$

where W is an arbitrary type, e.g. **bool** or the integer range [0..256). The opening pair of parenthesis contains the declarations of the external ports of  $BUF_1(a,b)$ . Port a is an input port of type W and port b is an output port of the same type.

The segment of Tangram text following the dot defines the behavior of the program. This behavior is described by a so-called *command* (statement). Here the behavior is described by a *block* command, in which the local variable x of type W is introduced. The brackets '[[' and ']]' delineate the scope of x. The bar ']' separates the local declarations from the command.

Command #[a?x;b!x] defines an infinite repetition of input action a?x followed by output action b!x. Execution of command a?x amounts to the reception of an incoming value through a and the storage of that value in variable x. Command b!x denotes the sending of the value of x through b.

In summary,  $BUF_1(a,b)$  repeatedly receives a value through a and sends that value through b. The variable x is merely a container to store the incoming value between the two communication actions. The identity of x and its role in the operation of the buffer cannot be observed externally, since x is effectively concealed by the scope brackets. Only the external communications through a and b can be observed. If type W is the range [0..10), a possible observation of  $BUF_1(a,b)$  is:

where a:v denotes the communication of value v through port a. Such a finite sequence of communications is called a trace.

A slightly more interesting program is that of two-place buffer  $BUF_2(a, c)$ :

$$(a?W \& c!W) \cdot |[b: \mathbf{chan} \ W \mid (BUF_1(a,b) \mid |BUF_1(b,c))]|$$

This two-place buffer is a cascade of two instances of  $BUF_1$ . The output of the first instance is connected to the input of the second. Both instances operate in parallel, as denoted by '||'. Cascades of instances of  $BUF_1$  are called "ripple buffers".

The internal communication along channel b has two aspects. Firstly, it requires simultaneous participation of sender and receiver. In other words, the output action of the left  $BUF_1$  and the input action of the right  $BUF_1$  form a single communication action. Secondly, a communication has the effect of the assignment action xr := xl, where xl and xr are aliases for the variable x in the left and right buffer instance respectively.

Communications along b are concealed by the scope brackets around the declaration of channel b. The communication behavior of  $BUF_2(a,c)$  is more interesting than that of  $BUF_1(a,c)$ . In addition to all the traces of the one-place buffer (with their output port renamed), a trace such as:

$$a:3$$

$a:9$   $c:3$   $c:9$   $a:0$   $c:0$

may be observed. True to its name, the two-place buffer allows the number of input communications to exceed the number of output communications by two.

A quite different program is TEE(a, b, c):

$$(a?W \& b!W \& c!W) \cdot (BUF_1(a,b) \mid\mid BUF_1(b,c))$$

It is a two-place buffer where the intermediate channel b is not concealed, but declared as an output port:

A communication along a channel that connects a single sender to multiple receivers is sometimes called a broadcast. A broadcast requires simultaneous participation of the sender and all receivers. A possible observation of TEE(a,b,c) is:

$$a:3 \ b:3 \ a:9 \ c:3 \ b:9 \ c:9 \ a:0 \ b:0 \ c:0$$

The external behavior of the program below is identical to that of  $BUF_2(a, c)$ . The program is named WAG(a, c) [vBRS88], because it behaves in a wagging fashion internally:

$$(a?W \& c!W) \cdot |[x, y : \mathbf{var} W \mid a?x; \#[(a?y \mid c!x); (a?x \mid c!y)]]|$$

Inputs are alternatingly written into variables x and y. Similarly, the outputs are alternatingly read from the same variables. After the first input WAG(a,c) may proceed with a second input ("buffer full") or with an output ("buffer empty"). A second input must then be followed by an output or vice versa. Etcetera.

WAG(a,c) is interesting, because its behavior cannot be distinguished from that of  $BUF_2(a,c)$ . Still, the compiled circuits differ considerably, as do their cost and performance. This will be shown in the next sections.

#### 1.2 Some simple handshake circuits

This section presents the handshake circuits for the various buffer programs of the previous section. Its main purpose is to develop an intuitive understanding of the operation of handshake circuits and the way they are generated from Tangram programs. The formal definition of handshake circuits is presented in Chapter 3. The translation method is described in depth in Chapter 6.

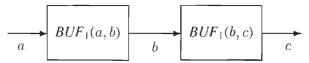

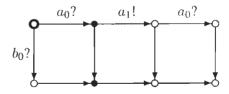

#### Handshake circuit for $BUF_1(a, b)$

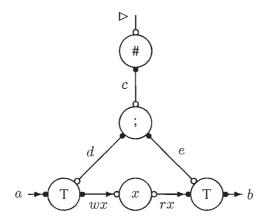

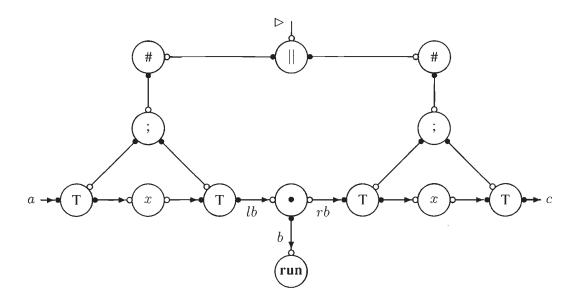

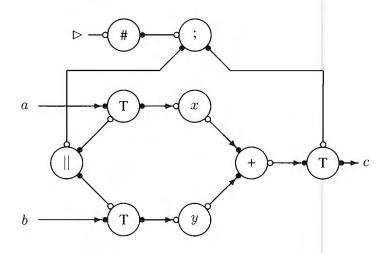

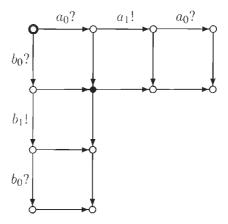

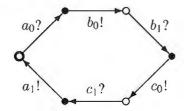

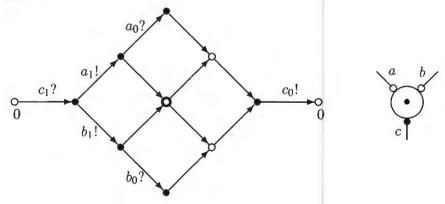

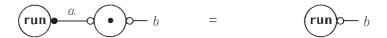

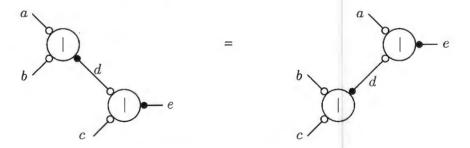

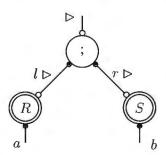

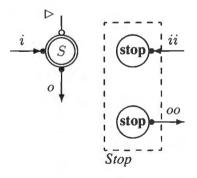

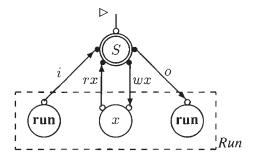

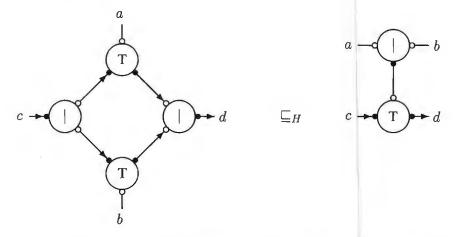

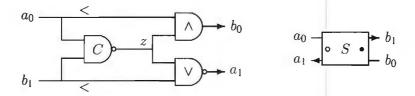

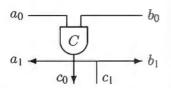

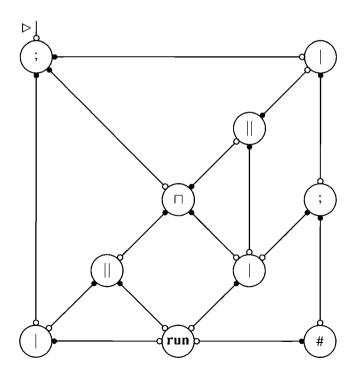

Figure 1.1 shows a handshake circuit for  $BUF_1(a, b)$ . It consists of 5 handshake components (depicted by circles), 5 channels (labeled c, d, e, wx and rx) and 3 ports (labeled  $\triangleright$ , a and b). Handshake components communicate through (handshake) ports. A channel connects one passive port (depicted by an open circle) to one active port (depicted by a fat dot). The communication along these channels is by means of a simple two-phase handshake protocol, in which the active side requests for a communication and the passive side responds by returning an acknowledgement.

In the handshake circuit for  $BUF_1(a, b)$  the active ports a and b correspond to the Tangram ports with these names. The passive port  $\triangleright$  (pronounced as "go")

Figure 1.1: Handshake circuit for  $BUF_1(a, b)$ .

is the activation port of the handshake circuit. The environment activates the buffer by a request along  $\triangleright$ . Only in the case of a terminating program, which  $BUF_1(a,b)$  is not, does the handshake circuit acknowledge termination through the same port.

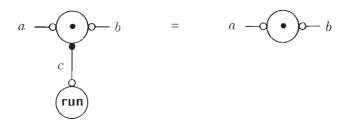

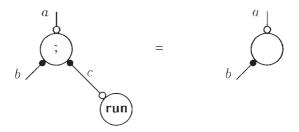

The handshake component labeled with a semicolon is a *sequencer*. Once activated along c it sequentially performs handshakes along d and e, before it returns an acknowledgement along c. It implements the semicolon that separates the input and output commands in the Tangram program. Unless explicitly indicated otherwise, the activation of the two active ports is counter-clockwise.

The component labeled with a '#' implements infinite repetition and is therefore called a *repeater*. Once activated along  $\triangleright$  it repeatedly executes handshakes along c, causing the repeated activation of the sequencer. The repeater never returns an acknowledgement along  $\triangleright$ .

Component x is a *variable*. A value can be written into x by sending it along channel wx. The acknowledgement along wx signals completion of the write action. Similarly, reading the variable starts by sending a request along rx (against the direction of the arrow). Component x responds by sending the most recently written value.

The two components labeled with a T are so-called *transferrers*. A request along d results in an active fetch of a value along a; this value is subsequently passed actively along wx. The left transferrer implements a?x and the right transferrer implements b!x.

Observe that the structure of the handshake circuit of  $BUF_1(a, b)$  clearly

reflects the syntactic structure of the Tangram program.

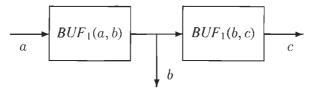

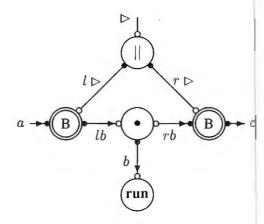

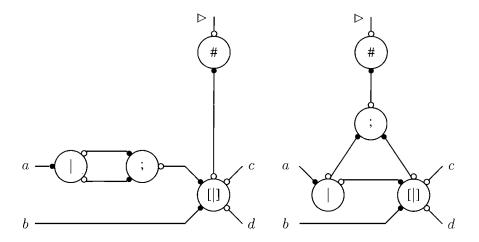

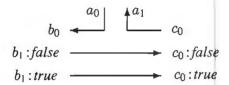

#### Handshake circuits for $BUF_2(a, c)$

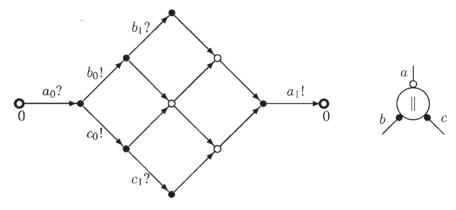

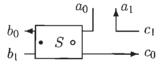

Figure 1.2: Handshake circuit for  $BUF_2(a, c)$ .

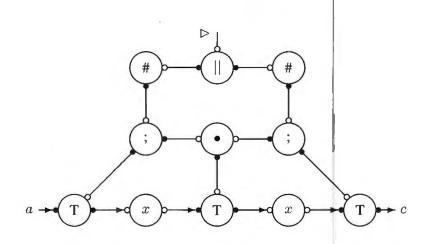

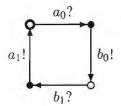

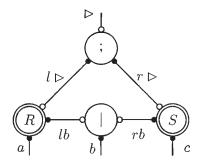

A handshake circuit for  $BUF_2(a,c)$  is shown in Figure 1.2. It introduces three handshake components. The two concentric circles enclosing a B represent instances of the handshake circuit of the one-place buffer. The two one-place buffers are activated along  $l \triangleright$  and  $r \triangleright$  at the same time by the parallel component after a request on  $\triangleright$ . Only when the parallel component receives an acknowledgement through both its active ports it will acknowledge through  $\triangleright$ .

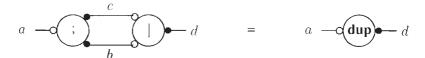

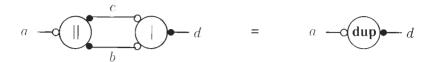

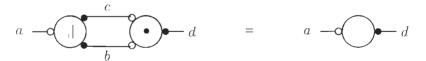

The handshake component labeled with a bullet is a *synchronizer*. It implements the concept of "communication and synchronization" of Tangram. If a request for communication arrives along both lb and rb the message arriving along lb is actively output along b. A subsequent acknowledgement along b results in a concurrent acknowledgements along lb and an output along rb.

The concealment of the Tangram channel b is realized by connecting a **run** component to handshake channel b. This component simply acknowledges each message it receives. Removing component **run** results in a handshake circuit for program TEE(a, b, c), with output ports a and b.

By expanding the two one-place buffers in the circuit of Figure 1.2 the handshake circuit of Figure 1.3 is obtained. The circuit clearly reflects the syntactic structure of the original program. The applied translation method is *syntax di*rected in that it closely follows the syntactic composition of the program in

Figure 1.3: Expanded handshake circuit for  $BUF_2(a, c)$ .

constructing the corresponding handshake circuit.

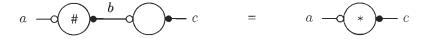

Such a syntax-directed translation may incur inefficiencies where subcircuits are combined in a way that only depends on their syntactic relation. Such inefficiencies can be removed by replacing small subcircuits by equivalent but cheaper subcircuits. This form of substitution is known as peephole optimization. One form of peephole optimization can be applied to the buffer of Figure 1.3: the result is shown in Figure 1.4. The component labeled '•' is again a synchronizer.

The handshake components introduced so far all implement Tangram primitives. Given the relatively small number of such primitives, the set of handshake components is modest in size. By providing an "equivalent" VLSI circuit for each handshake component and by wiring them according to the structure of the handshake circuit a VLSI circuit can be obtained. The circuits for many handshake components are simple and fixed. For handshake components such as variables and transferrers the circuit structure depends on the number of bits required to encode the relevant data types.

Handshake circuits are clockless. All synchronization is explicit by means of handshake actions between neighboring components. The scheduling problem of assigning a time slot to every primitive action is thus avoided. Furthermore,

Figure 1.4: Optimized handshake circuit for  $BUF_2(a, c)$ .

the absence of global synchronization avoids the timing overhead of aligning all primitive actions to clock transitions. Clockless operation combined with the locality of data and control make handshake circuits potentially faster than synchronous circuits.

Although the buffers are about the simplest Tangram programs one can think of, the design of *synchronous* "elastic" buffers offers considerable challenges. In particular, the synchronization of clocked input and output actions with an asynchronous environment involves complex circuitry and fundamental reliability problems [Ano73,Sei80].

#### Handshake circuit for WAG(a, c)

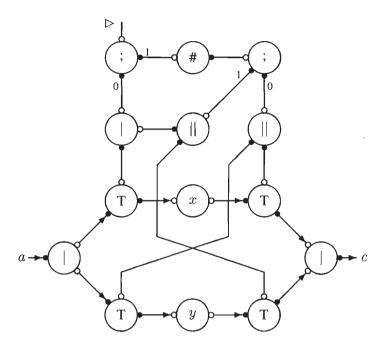

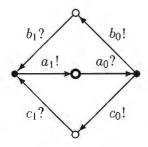

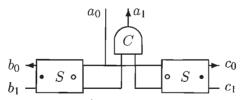

A handshake circuit for WAG(a,c) is presented in Figure 1.5. The three components labeled '|' are so-called *mixers*. They have in common that handshakes through their passive ports are passed to their active ports.

The component connected to a behaves like a demultiplexer. A request from either passive port is passed along a. The incoming message is passed to the side of the request.

The mixer connected to c passes the incoming message from one of its two passive input ports to the active output. The acknowledgement along b is passed to the side of the last incoming message (cf. multiplexer).

The third mixer is a multiplexer for synchronizing handshakes only. It allows

the transferrer connected to its active side to be activated by either of the two handshake components connected to its active ports.

These mixers make the wagging implementation of the two-place buffer more expensive in area than the ripple implementation.

Figure 1.5: Optimized handshake circuit for WAG(a, c). The numbers near the sequencers indicate the order of activation.

#### 1.3 Cost-performance trade-offs

The programs for  $BUF_2(a,c)$  and WAG(a,c) in Section 1.1 are functionally identical. The corresponding handshake circuits of Figures 1.4 and 1.5, however, differ considerably. In general, a range of Tangram programs can be designed that satisfy a single functional specification. The corresponding compiled circuits will differ in cost and performance. The best Tangram program is then the one that results in the smallest compiled circuit that satisfies the specified performance requirements.

With this view on VLSI programming it is important that for a given functional specification a range of Tangram programs can be constructed, covering a wide part of the cost-performance spectrum. An N-place shift register serves as a vehicle to demonstrate the idea.

#### Specification

An N-place shift register,  $N \ge 1$ , is a component with an input port, a, and an output port, b, of the same data type, with the following behavior:

- communications along a and b strictly alternate, starting with an output along b;

- the sequence of values along b consists of N unspecified values, followed by the sequence of input values.

This shift register will be denoted by  $SR_N(a, b)$ . Shift registers are common building blocks in VLSI systems, e.g. in various types of digital filters in signal-processing applications. The processed messages are usually called samples.

Note that in both aspects the behavior of a shift register differs from that of an N-place buffer. For an N-place buffer the difference in the number of a and b communications may vary in time over the range [0..N]. Also, the sequence of output values is a plain copy of the input sequence.

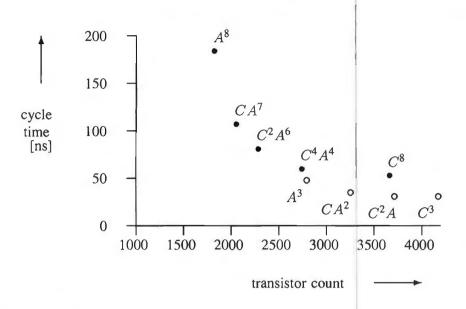

Implementations of shift registers will be compared in cost and performance. Cost ultimately denotes silicon area and performance refers to the sample rate, i.e. the number of processed samples per second. In a final comparison nine different VLSI programs of an 8-place 8-bit shift register will be compared in terms of transistor count and average cycle time of the corresponding VLSI circuits. The transistor count is a reasonable measure for the silicon area, by which we ignore the variation observed in wiring area. The cycle time is the time between two successive inputs (or outputs) and is the inverse of the sample rate.

#### A cheap realization

The simplest realization of  $SR_1(a, b)$  is denoted by SRA(a, b) and is defined by the Tangram program

$$(a?W \And b!W) \cdot |[x: \mathbf{var} \ W \ | \ \#[b!x;a?x]]|$$

where W denotes the data type of the samples. Note that the repetition command closely resembles that of a 1-place buffer. The only difference is in the order of the input and output command.

Figure 1.6:  $SR_{(M+N)}(a, c)$  composed of two shift registers with a smaller capacity.

For the construction of an N-place shift register a well-known cascade property of shift registers is used (see Figure 1.6):

$$|[b: \mathbf{chan} \ W \ | \ SR_M(a,b) \ || \ SR_N(b,c)]| = SR_{(M+N)}(a,c)$$

A realization for  $SR_N(a, b)$  can now be obtained by cascading N instances of SRA. This solution will be denoted by  $A^N$ .

Note that  $A^N$  is capable of producing N outputs before doing its first input. Moreover, after these initial N outputs the behavior is that of an N-place buffer. On closer inspection, is  $A^N$  really an implementation of  $SR_N(a,b)$ ?

It depends. If the environment relies on the alternation of b and a communications then definitely not. If the environment enforces this alternation,  $A^N$  is an acceptable realization. In order to avoid further confusion, the first requirement of the specification of  $SR_N(a,b)$  is redefined as: the following composition must not deadlock:

$$SR_N(a,b) \mid | |[x,y: \mathbf{var} \ W \mid \#[b?x \mid | \ a!y] ]|$$

Note that the specification is relaxed to the extent that the *i*th input and the *i*th output may occur concurrently.

What can be said about the performance of  $A^N$ ? After its first output, the last cell in the cascade is ready to do an input: "it is vacant". This vacancy then propagates backwards to the input of  $A^N$  and it takes N-1 successive internal assignments before an input action can occur. The cycle time is therefore proportional to N. The time an 8-bit assignment takes will be chosen as a time unit. A reasonable value for this time unit in current VLSI CMOS technologies is 25 nanoseconds. For an 8-place 8-bit shift register the cycle time is then 8 time units, or 200 nanoseconds. It depends on the performance requirements whether 200 nanoseconds are acceptable or not.

The cost of  $A^N$  is modest. It takes only N variables, which is obviously a lower bound for  $SR_N(a,b)$ .

#### Fast realizations

An alternative realization of  $SR_1(a, b)$  is SRB(a, b). It consists of an instance of SRA and a 1-place buffer:

$$(a?W \& b!W) \cdot |[x,y: \mathbf{var} \ W \& c: \mathbf{chan} \ W \ | \ \#[c!x;a?x] \ || \ \ \#[c?y;b!y]]|$$

SRB resembles a traditional synchronous shift register composed of master-slave flipflops. The SRA part assumes the role of the master, the 1-place buffer that of the slave. Input and output actions may overlap in time. In contrast to a synchronous shift register (and with SRA for that matter) SRB may start with an input. Shift register SRB(a,b) can be rewritten into SRC(a,b):

$$(a?W \& b!W) \cdot |[x, y : \mathbf{var} \ W \mid \#[(b!y \mid | a?x); y := x]]|$$

SRB and SRC are very close in terms cost and performance (SRC is slightly cheaper, because of its simpler control structure).

By cascading N instances of SRC we obtain a second realization of  $SR_N(a,b)$ . This realization will be denoted by  $C^N$ . Because each SRC section has its own vacancy, the behavior of  $C^N$  is markedly different from that of  $A^N$ . For the analysis it is assumed that when the environment is ready to participate in an input or output action, it does so without delay. Then the input and output actions of each individual SRC occur simultaneously, and all N stages operate in harmony. As a result the sample rate is independent of N, and the cycle time amounts to only two time units (50 nanoseconds). The price for this nice performance is substantial:  $C^N$  requires 2N variables, twice that of  $A^N$ .

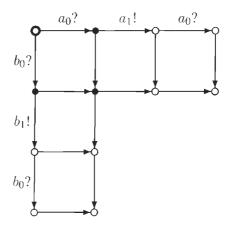

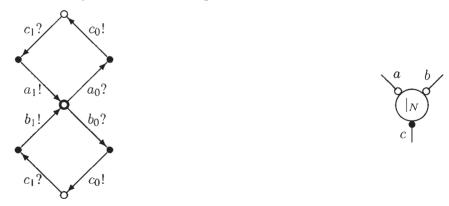

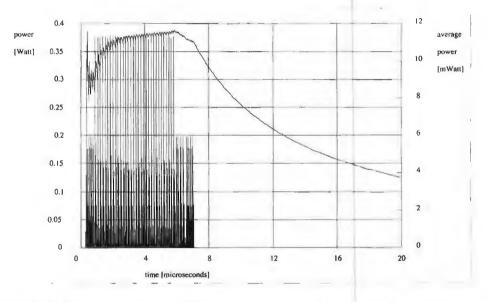

Given the substantial difference in cost and performance between  $A^N$  and  $C^N$  one may wonder if intermediate solutions exist. Indeed, by introducing one or more SRC cells in a sequence of SRA cells, intermediate solutions can be obtained of the form  $C^KA^{N-K}$ , with  $0 \le K < N$ . The solid circles in Figure 1.8 indicate the average cycle time and transistor counts for five shift registers of this kind, with K equal to 0, 1, 2, 4 and 8 respectively. The cycle times were obtained by simulation of the compiled handshake circuits. The timing models of the handshake components have been calculated from the timing characteristics of their constituent VLSI operators.

The realizations described so far have in common that the messages ripple through a cascade of N cells. Hence, they will be referred to as ripple shift registers.

#### Still faster realizations

One may wonder whether  $C^N$  is the fastest possible shift register. Equivalently, is two time units the minimum cycle time? By putting two shift registers in parallel, and by serving them alternatingly, faster shift registers can be constructed (see Figure 1.7). Shift registers based on this structure will be referred to as wagging shift registers. In order to keep matters simple, N is restricted to even values.

SRD(a, c, e) de-interleaves the incoming sequence by sending the incoming values alternatingly along c and e:

$$(a?W \& c!W \& e!W) \cdot |[x, y : \mathbf{var} \ W \mid \#[(c!x \mid | a?y); (e!y \mid | a?x)]]|$$

SRE(d, f, b) interleaves the incoming sequences by receiving inputs alternatingly along d and f:

$$(d?W \& f?W \& b!W) \cdot |[x, y : \mathbf{var} \ W \mid \#[(b!x \mid | d?y); (b!y \mid | f?x)]]|$$

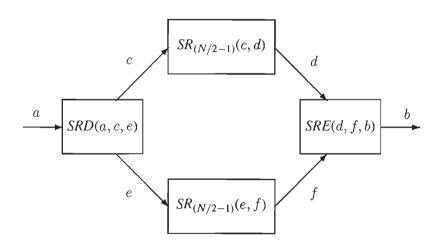

Figure 1.7: The wagging shift register.

Both *SRD* and *SRE* have a cycle time of one unit, measured at the input and output respectively. Unfortunately, due to some additional overhead in control and data routing, the real cycle time is somewhat larger. For 8-bit messages 30 nanoseconds is realistic.

For the two parallel shift registers ripple implementations can be used, e.g. composed of SRA and SRC cells. A regular communication behavior is obtained by taking identical cell sequences for  $SR_{(N/2-1)}(c,d)$  and  $SR_{(N/2-1)}(e,f)$ .

Figure 1.8: Cycle time versus transistor count for nine different 8-place 8-bit shift registers. Solid circles represent ripple solutions, open circles wagging solutions.

In Figure 1.8 the compilation and simulation results for four triplets for  $SR_3(c,d)$  and  $SR_3(e,f)$  (from slow/small to fast/large):  $A^3$ ,  $CA^2$ ,  $C^2A$  and  $C^3$ . Due to the aforementioned overhead,  $C^2A$  is barely an improvement over  $CA^2$ . For the same reason  $C^3$  offers no advantages over  $C^2A$ .

#### Discussion

One type of realization has not been considered: array-based solutions. Such an array can be mapped on a Random Access Memory (RAM). Array-based realizations are attractive for large N, because of the very small area/bit of a RAM. For small N, array-based solutions are less attractive due to an area overhead of circuitry for timing, control and addressing.

Despite the simplicity of the specification of  $SR_N(a,b)$  an interesting range of implementations has been realized. If we ignore the wagging solution with cell sequence  $C^3$ , all implementations have different cycle times and different costs. Among these eight solutions there is *no* best solution. Depending on throughput requirements, each of these eight implementations may be the best, except  $C^8$ .

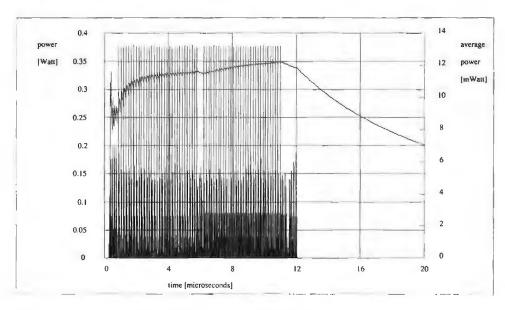

Even totally different considerations may part of the cost/performance tradeoff, for example energy consumption. An 8-bit assignment consumes approxiMore examples 31

mately a quarter of a nanoJoule. A reasonable measure for the energy consumption of a ripple buffer is then the number of moves made by a single message from input to output, viz. K+N. The *power* consumption of  $A^8$  running close to its maximum speed (5 Mhz sample rate) will then be approximately 10 mWatt. For  $C^8$  at 20 Mhz this amounts to 80 mWatt. Wagging solutions, on the other hand, are markedly economic in their energy consumption, because the path traversed by a message is only half in length compared to that of ripple solutions. For instance, a message takes five moves to ripple through  $A^3$ . At 20 Mhz this results in a power consumption of 25 mWatt. Of course, more accurate estimates for size, timing and power need to be provided by the silicon compiler and simulation tools.

These concerns for cost and performance make VLSI programming different from and also more difficult than conventional programming. Especially high-performance systems (e.g. digital video systems) may require detailed performance analysis. But also for low-performance systems (e.g. digital audio systems) with critical requirements on silicon area, balancing the performance of subsystems is important.

From a VLSI-circuit perspective, these asynchronous shift registers also provide an interesting insight.  $A^N$  requires one latch per section per bit whereas a master-slave flipflop requires two. In principle, no solution based on master-slave flipflops can beat  $A^N$  in circuit size. Mimicking the behavior of  $A^N$  with synchronous circuits requires complex timing/control circuitry.

Although the sample rate of  $A^N$  is low, the vacancy travels at maximal speed from output to input. With a few SRC cells, the internal timing behavior becomes highly irregular. This form of irregularity is hard to capture in clocked circuits.

In complex VLSI systems the different input and output ports often have different sample rates. Sometimes the samples are offered or consumed irregularly in time. Even if these rates are constant and identical, this need not be so for internal channels. Certain subcomputations have data-dependent processing times, or are invoked at irregular intervals, e.g. for handling exceptional situations. In such situations the absence of a clock opens new architectural possibilities and trade-offs.

# 1.4 More examples

Buffers and shift registers are not very interesting from a data-processing point of view: the sequence of output message is basically a copy of the sequence of input messages. This section introduces Tangram constructs by which more interesting

programs can be described. Various small programs are used as illustrations. Where appropriate, the corresponding handshake circuits are given.

#### An adder

ADD(a, b, c) is a simple process that repeatedly accepts two values of type W along its two inputs a and b and outputs their sum along c:

$$ADD(a, b, c) = (a?W \& b?W \& c!W) \cdot |[x, y : \mathbf{var} \ W \mid \#[(a?x \mid |b?y); c!(x+y)]]|$$

Expressions such as x+y may occur in assignments, outputs commands and guards (see later in this chapter). It will be assumed that the evaluation of an expression always terminates. However, if the result value does not "fit" its destination, the consequent behavior is not specified: the program may deadlock, or may proceed in some erratic way. ADD continues properly as long as the value of x+y is of type W.

Figure 1.9: Handshake circuit for ADD(a, b, c).

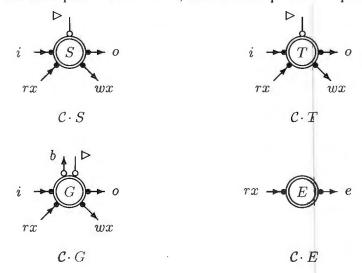

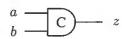

The handshake circuit for ADD is presented in Figure 1.9. The handshake component labeled '+' is an *adder*. The expression x + y is evaluated in a demand-driven fashion:

0. a request for a sum is passed to the passive output of the adder;

More examples 33

- 1. the adder forks this request to its active inputs;

- 2. the input values arrive at the inputs of the adder;

- 3. their sum is output along the output.

## A simple FIR filter

A Finite Impulse Response (FIR) filter is a process with a single input and a single output. The input and output communications strictly alternate, starting with an input. For a FIR filter of order N the output values are specified as follows. The value of the ith output,  $i \geq N$ , is generally a weighted sum of the N most recent input values. The N weights are generally referred to as the filter coefficients. The first N output values are left unspecified.

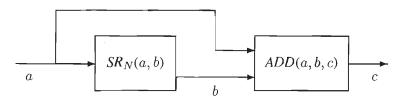

A very simple FIR filter of order N can now be constructed by connecting ADD with a shift register:

$$(a?W \& b!W) \cdot |[b : \mathbf{chan} \ W \mid ADD(a, b, c) \mid] SR_N(a, b)]|$$

The *i*th output,  $i \geq N$ , is the sum of the *i*th input and the input with index i-N. This composition is depicted in Figure 1.10. Clearly, the input channel a is connected to both ADD and SR. In general, any number of receivers may be connected to a channel. The connected receivers must all participate in each communication along that channel. This is another example of broadcast. There may be at most one sender.

Figure 1.10: A simple FIR filter constructed from  $SR_N(a, b)$  and ADD(a, b, c).

A more general FIR filter program is discussed in [vBRS88], in which the degree of parallelism is parameterized. The program is a linear systolic array of N div M cells, where M is a measure of the grain size of the parallelism. If M = N the program is sequential and requires a single multiplier. The other extreme solution is M = 1: an array of N cells guarantees maximum throughput, but requires N multipliers.

#### A median filter

A median filter repeatedly outputs the median value of the three most recent inputs. (Similar to the FIR filter, the sequence of output messages starts with a few unspecified values.) A Tangram program for the median filter is given by:

```

\begin{array}{l} (a?W \ \& \ b!W). \\ |[x,y,z: \ \mathbf{var} \ W \ \& \ xy,yz,zx: \ \mathbf{var} \ \mathbf{bool} \\ | \ \#[ \ (z:=y;y:=x;a?x \ || \ yz:=xy) \\ ; xy:=x \le y \ || \ zx:=z \le x \\ ; \ \mathbf{if} \ \ zx=xy \ \to \ b!x \\ |[\ \ xy=yz \ \to \ b!y \\ |[\ \ \ yz=zx \ \to \ b!z \\ \mathbf{fi} \end{array} ]

```

The program segment if .. fi is a selection command [Dij75]. The if fi bracket pair encloses three so-called guarded commands. Guarded commands have the form  $B \to S$ , where B is a Boolean expression and S a command. The execution of the selection command starts with the evaluation of the guards. If all guards are false the henceforth behavior program is left unspecified. If at least one guard evaluates to true the command corresponding to a true guard is executed. If more than one guard is true, the choice which of command to execute is not specified. This nondeterminism can be resolved at compile time, or even at run time. Of course, for purposes of efficiency the programmer may strengthen the guards to make them non-overlapping.

The following may help to understand the Tangram description of the median filter. Just prior to the execution of the selection command, the variables x, y and z contain the three most recent input values, in increasing age. At that point the three Boolean variables xy, yz and zx have the values  $x \le y$ ,  $y \le z$  and  $z \le x$ . The expression zx = xy is then equivalent to "x is the median value". The two other guards can be read similarly.

Note that if x = y = z all three guards evaluate to *true*. The corresponding nondeterministic selection of one of the three output commands cannot be observed externally. However, the internal operation does depend on how the nondeterminism is resolved.

The median filter nicely demonstrates an advantage of this form of command selection. The symmetry among the three guards can only be captured in a language with explicit and overlapping guards for the three alternatives. The

More examples 35

reader may try for instance an if-then-else command to replace the above selection command to convince himself.

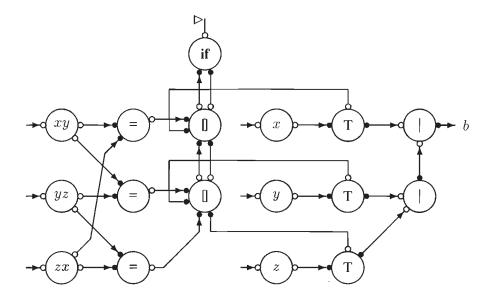

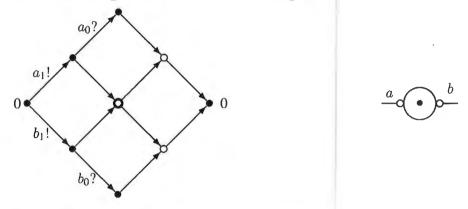

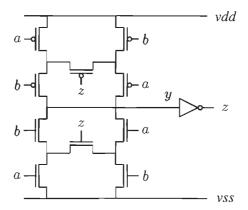

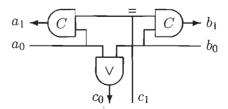

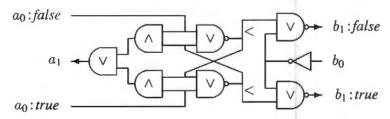

The handshake circuit for the **if**  $\mathbf{fi}$  section of the median filter program is depicted in Figure 1.11. The write ports of the variables are left unconnected. After an activation along  $\triangleright$  the selection command is executed in two phases.

Figure 1.11: Handshake circuit for the if fi section of the median filter.

In the first phase the **if** component actively collects the disjunction of the guards. The component labeled '[]' passes on a request on its output to both its Boolean inputs; upon the reception of these Booleans their disjunction is transmitted along its output. Note that the guards are evaluated in parallel.

The effect of the second phase depends on the collected disjunction of the guards. If this value equals *false*, the **if** component remains passive and the circuit deadlocks. If the value equals *true*, as is always the case for the median filter, component **if** activates the topmost [] component. This component activates the circuit corresponding to an input from which it received the value *true*. In this solution the nondeterminism is resolved in the [] component.

This implementation scheme works for an arbitrary number of guards. When the [] components are organized according to a binary tree, the computation of

the disjunction of the guards and the selection of the appropriate command can be done in  $O(\log N)$  time, where N denotes the number of guards.

The handshake component labeled '=' is another example of a binary operator. The variables xy, yz and zx have two read ports, from which concurrent read actions are allowed.

The median filter is an instance of a so-called rank-order filter. After each input value the rank-order filter outputs the value with rank K among the last N inputs  $(0 \le K < N)$ . A value has rank k among N values if it has position k in the ascendingly ordered list of these N values. The median filter is a rank-order filter with N=3 and K=1. [KR89,KU91] present programs for rank-order filters. Both solutions are linear systolic arrays of N cells. Except for the two end cells, all cells are identical. The cells communicate with neighboring cells in a regular, systolic manner.

## The greatest common divisor

Program GCD repeatedly computes and outputs the greatest common divisor of the two most recent inputs:

The algorithm goes back to Euclid; this particularly elegant version is based on [Dij76]. The program segment **do** .. **od** is a *guarded repetitton*, a generalization of the well-known **while** command. As long as at least one guard evaluates to *true* one of the *true* guards is selected and the corresponding command is executed. If all guards fail, the repetition command terminates. If one of the inputs equals 0 the guarded iteration will not terminate.

In [Dij76] a similar algorithm is given for computing the least common multiple. The Tangram program for a sequential multiplier [vBS88] also resembles *GCD*. The number of cycles required to compute the greatest common divisor strongly depends on the two input values. The computation time and energy are proportional to this number.

More examples 37

Note that the communication behavior of *GCD* is identical to that of *ADD*. The handshake circuits have the same external ports, viz. an activation port, two input ports and one output port. The fact that *GCD* contains an iterative algorithm is completely hidden for the user of the circuits. The proposed method of compiling Tangram programs into handshake circuits leads to a form of distributed control. Information is kept local, with the associated advantages of shorter wires and minimum timing overhead.

#### **Modulo-**N counters

The modulo-N counter is presented to introduce the choice command. There are two ways in Tangram by which the environment can influence the future course of action of a program. Firstly, the environment may select the value to send through an input port. The incoming value is stored in a variable and may subsequently occur in the guards of a guarded command. The input value may thus determine the future pattern of communications and computations.

Secondly, the environment may have the *choice* among a set of ports through which it may synchronize or communicate. The binary form of this choice is exemplified by the program CE(a, b, c, d) (CE is an acronym for Count Even, as will become clear later):

$$(a \& b \& c \& d) \cdot \#[[c; a; a \mid d; b]]$$

Operator ';' binds more strongly than '|'. The environment is repeatedly offered the choice between a synchronization on c or on d. These two commands act as guards in the choice command. For each c, process CE performs two synchronizations on a; for each d, it performs only one synchronization on b.

Using the choice command, a program for a modulo-N counter will be constructed  $(N \geq 1)$ . The program has two external synchronization ports, a and b. A modulo-N counter repeatedly performs N synchronizations on a followed by a single on b. Let this behavior be denoted by

$$\#[\#N[a];b]$$

The simplest counter is a modulo-1 counter C1:

$$\#[a;b]$$

For even values of N the modulo-N counter can be written as

$$\#[\#M[a;a];b]$$

where  $M = N \operatorname{div} 2$ . By introducing a modulo-M counter this can decomposed into

$$|[c,d: \mathbf{chan} \mid (CE(a,b,c,d) \mid | \#[\#M[c];d])]|$$

In words, the modulo-M counter performs M synchronizations on c, which are effectively doubled by CE and passed through a. A closing d is simply passed by CE as b.