## Timing recovery techniques for digital recording systems

#### Citation for published version (APA):

Wang, J. J. (2002). Timing recovery techniques for digital recording systems. [Phd Thesis 1 (Research TU/e / Graduation TU/e), National University of Singapore]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR559505

DOI: 10.6100/IR559505

#### Document status and date:

Published: 01/01/2002

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# Timing Recovery Techniques for Digital Recording Systems

## Timing Recovery Techniques for Digital Recording Systems

JIANJIANG WANG (B. Eng. & M. Eng., Tsinghua University)

A THESIS SUBMITTED FOR THE DEGREE OF DOCTOR OF PHILOSOPHY OF THE ELECTRICAL AND COMPUTR ENGINEERING DEPARTMENT OF THE NATIONAL UNIVERSITY OF SINGAPORE

2002

## Timing Recovery Techniques for Digital Recording Systems

PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr. R.A. van Santen, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op donderdag 5 december 2002 om 14.00 uur

door

### JIANJIANG WANG

geboren te Korla, China

Dit proefschrift is goedgekeurd door de promotoren:

prof.dr.ir. J.W.M. Bergmans en prof. D.S.H. Chan

Copromotor:

prof. T.C. Chong

©Copyright 2002 Jianjiang Wang

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without the prior written permission from the copyright owner.

### CIP-DATA LIBRARY TECHNISCHE UNIVERSITEIT EINDHOVEN

Wang, Jianjiang

Timing recovery techniques for digital recording systems / by Jianjiang Wang. - Eindhoven : Technische Universiteit Eindhoven, 2002. Proefschrift. – ISBN 90-386-1950-2 NUR 959 Trefw.: tijdmeting / signaalverwerking / dataopslag / magnetische registratie / datarecorders. Subject headings: synchronization / signal processing / data recording / magnetic storage.

Printed by: University printing office, Eindhoven, The Netherlands

promotiecommissie:

prof. dr. ir. J.W.M. Bergmans

prof. dr. ir. W.M.G. van Bokhoven

prof. dr. P.P.J. van den Bosch

prof. dr. ir. A.C. Brombacher

prof. dr. D.S.H. Chan

prof. dr. T.C. Chong

dr. W.M.J. Coene

dr. G. Mathew

dr. ir. F.M.J. Willems

to my parents and my family

## ACKNOWLEDGEMENTS

First, I want to acknowledge my dissertation advisors Prof. Jan W. M. Bergmans, Prof. Chong Tow Chong and Dr. George Mathew. They provided sustained guidance and indispensable advice by setting aside large amounts of their time for discussions and review. Completion of my Ph.D. would not have been possible without their support.

I want to thank Prof. Jan W. M. Bergmans from Electrical Engineering Department, the Eindhoven University of Technology, The Netherlands. I owe a lot to him for the tremendous source of knowledge and inspiration that he has been to me. He has freely shared his time and insights with me and provided excellent guidance and continual support throughout the course of this work. I have benefited much from his constructive criticism, invaluable advice and many enlightening discussions with him. His enthusiastic support and high quality guidance during my Ph.D. study will never be forgotten. His systematic and rigorous approach to research has been a constant source of challenge to achieve greater heights.

I want to thank Prof. Chong Tow Chong from Electrical and Computer Engineering Department, the National University of Singapore, for introducing me into this wonderful and challenging area of data storage technology. I feel extremely fortunate to have had him as my advisor. I really cannot thank him enough for his constant support and encouragement during my work and study.

I want to thank Dr. George Mathew from the Data Storage Institute (DSI), Singapore, for his counseling and expertise. It is difficult to imagine reaching this point without his help. He dedicated large amounts of his time and expertise in reviewing my work, offering advice and giving direction to my efforts. His positive attitude led me constantly to look for solutions to problems that appeared to have none. He also provided me with a tremendous amount of support, especially in the area of numerical analysis and computer simulation resources.

Second, I want to thank Prof. Daniel S.H. Chan from the National University of Singapore, Prof. W.M.G. van Bokhoven, Prof. P.P.J. van den Bosch, Prof. Aarnout C. Brombacher and Associate Prof. F.M.J. Willems from the Eindhoven University of Technology, The Netherlands, and Dr. Wim M.J. Coene, principal scientist from the Digital Signal Processing group of the Philips Research, Eindhoven, The Netherlands, for serving on my committee and providing valuable comments.

I am also grateful to Dr. Y.X. Lee, IBM, San Jose, CA, who was one of the dissertation advisors during the initial period of my research. He introduced me to the subject of timing recovery, and helped me in the formulation and execution of the initial part of my research work.

I am thankful to DSI for providing all the necessary support and an excellent research environment for my thesis work. There are several persons in the Coding and Signal Processing group of DSI who deserve to be acknowledged here. They are Dr. Y.X. Lee, Dr. Victor Y. Krachkovsky, Dr. George Mathew, Mr. W.C. Ye, Dr. K.C. Indukumar, Dr. S. Gopalaswamy, Dr. Q.W. Jia, Mr. L. Bi, Mr. Q. Li, Mr. B. Liu and Ms. M.Y. Lin. They have been a source of constant moral and technical support to me during my time at DSI. While we each had a different research focus, we successfully worked as a team in solving problems related to signal processing techniques for data storage, enhancing the value of each other's work. I would also like to thank Mr. Lim Beng Wah for his dependable and cheerful technical assistance.

I owe a debt of thanks to numerous people who helped me make the thesis work a reality. These people include Dr. Roger W. Wood and Mr. John Hong from the IBM, San Jose, CA. USA, Mr. Hiroshi Mutoh and Mr. Hiroaki Ueno from the Fujitsu, Japan, Mr. M. Umemoto from the Hitachi, Japan, and Dr. Haralampos Pozidis, formerly from the Philips Research, The Netherlands. I am also thankful to the management of Philips Research Labs for providing the necessary support for my research work in Eindhoven, The Netherlands. Even though I cannot list here all of the people who helped me accomplish this work, nevertheless I am indebted to all of them.

Finally, I must thank my wife and my son, for their unfailing encouragement, love, support, patience and sacrifice. I also owe a great deal of gratitude to my parents in China; they have been behind me all the time, and their primary concern is always my well being. I would like to dedicate this dissertation to them for encouraging me to pursue higher education.

Wang, Jianjiang

Fremont, California, USA December 2002

*abstract* — This thesis is devoted to the development of timing recovery techniques for digital recording systems. The thesis begins with a detailed review and discussion of timing recovery structures, requirements, performance measures, timing error detector (TED) algorithms, and timing acquisition issues. The main contributions include five parts. The first part examines the timing sensitivity of read channel detectors, and develops a new analytical approach for evaluating the performance under static and random timing errors. The second part examines the TED efficiencies, develops an improved TED for jitter minimization, and studies optimality issues for timing acquisition. The third part investigates false lock and hang up problems, and develops two novel acquisition techniques. The fourth part presents the timing recovery loop design and implementation for an experimental read channel detector. The fifth part develops a new asynchronous equalizer adaptation structure with fully digital interpolative timing recovery (ITR) for digital optical recording systems.

## SUMMARY

A critical part of data storage systems is the read-write channel, which consists of the electronic circuits needed for writing the user-supplied data into the storage medium and for reliably recovering the written data. A properly designed read-write channel has the potential to enhance the recording density and data rate capabilities of a given head-medium combination. Equalizer, data-detector and timing recovery circuitry are among the most important blocks of a read-write channel. Usually, the tasks of equalization and detection receive considerable attention from researchers. As recording channels become more efficient in terms of modulation code, bandwidth and storage density, the task of timing recovery becomes more difficult and, at the same time, increasingly critical for reliable data recovery. The problem of timing recovery is concerned with the determination of the optimum sampling instants for the readback signal. The research work that has been undertaken in the thesis deals with the timing recovery issues in read-write channels.

This thesis is devoted to the study and development of timing recovery techniques for digital recording systems. It investigates the structure and performance of timing recovery schemes, and develops new timing recovery schemes for magnetic and optical recording applications. The thesis contains eight chapters. Chapter 1 gives a brief introduction to digital recording technology and a review of read-write channel techniques. It concludes with the motivation, contributions and organization of the thesis. Chapter 2 gives a detailed review of timing recovery, highlighting the different possible structures, requirements, and performance measures. It also discusses the generic timing error detector (TED) algorithms and the main issues that arise during timing acquisition. Analyses and simulation results support the discussions, wherever possible. Chapters 3 to 7 describe the main new research contributions made during the course of this Ph.D. work. Chapter 8 concludes the thesis with some remarks on directions for further work.

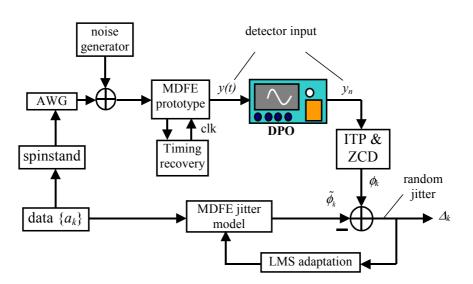

Chapter 3 investigates the timing sensitivity of partial response (PR) Viterbi detectors and decision feedback equalization (DFE) detectors, and develops an analytical approach to evaluate the performance in the presence of static and random timing errors. Chapter 4 examines the efficiencies of existing and proposed TED algorithms for partial response and DFE recording systems. It also develops a marginal detection based TED for minimizing jitter in the multi-level DFE (MDFE) detector and analyzes its phase noise performance. Further, it examines the optimality of the preamble and TED used for timing acquisition in MDFE. Chapter 5 investigates the problem of timing acquisition in DFE detectors. It develops two novel fast acquisition techniques that do not suffer from hang up and false lock problems, even in the presence of large initial errors in timing, gain and DC offset. Chapter 6 describes the design and implementation of a practical timing recovery system, which is designed and prototyped in ECL (emitter-coupled logic) discrete-components, for a 100 Mb/s experimental MDFE read channel (channel data rate is 150 Mb/s). Performance evaluations of the system based on bench and spinstand tests are also presented.

The focus of the development of the algorithms and systems presented in Chapters 3 to 6 is on magnetic recording, even though these are also applicable with minor modifications to optical recording. In contrast, the focus of Chapter 7 is on optical recording. In Chapter 7, a new and attractive architecture for fully digital zero-forcing based equalizer adaptation and interpolative timing recovery (ITR) is developed. The development of algorithms and systems in Chapters 3 to 7 is supplemented with computer simulation results. These simulation results are used for demonstrating the effectiveness of the proposed algorithms and for corroborating the analytical developments.

# CONTENTS

| Acknowledgements                                                                     |    |

|--------------------------------------------------------------------------------------|----|

| Abstract                                                                             |    |

| Summary                                                                              | X  |

| Contents                                                                             |    |

| Glossary                                                                             | XV |

| Abbreviations                                                                        |    |

| Often Used Symbols                                                                   |    |

| Notational Conventions                                                               |    |

| List of Tables                                                                       |    |

| List of Figures                                                                      | XX |

| CHAPTER 1                                                                            |    |

| INTRODUCTION                                                                         | 1  |

| 1.1 Introduction to Digital Recording Technology                                     |    |

| 1.2 Overview of Read-Write Channel Techniques for Digital Magnetic Recording Systems |    |

| 1.3 Motivation for the Present Study                                                 |    |

| 1.4 Contributions and Organization of the Thesis                                     |    |

| References:                                                                          |    |

|                                                                                      |    |

| CHAPTER 2                                                                            |    |

| REVIEW OF TIMING RECOVERY                                                            | 17 |

| 2.1 Introduction to Timing Recovery                                                  |    |

| 2.2 Structures, Requirements and Performance Measures                                |    |

| 2.3 Timing Recovery Schemes and TED Algorithms                                       |    |

| 2.4 Timing Acquisition                                                               |    |

| 2.5 Summary                                                                          |    |

| References:                                                                          |    |

|                                                                                      |    |

| CHAPTER 3                                                                            |    |

| TIMING SENSITIVITY ANALYSIS FOR MAGNETIC RECORDING                                   | 51 |

| 3.1 Introduction                                                                     |    |

| 3.2 Channel Model with MDFE and PR4-VD Detectors                                     |    |

| 3.3 Timing Sensitivity of MDFE Detector                                              |    |

| 3.4 Timing Sensitivity of PR4-VD.                                                    |    |

| 3.5 Conclusions                                                                      |    |

| Appendix 3.A : PDF of ISI with Correlated Data                                       |    |

| References:                                                                          |    |

|                                                                                      |    |

| CHAPTER 4                                                                            |    |

| ANALYSIS OF TIMING ERROR DETECTORS                                                   | 67 |

| 4.1 Introduction                                                                     | 67 |

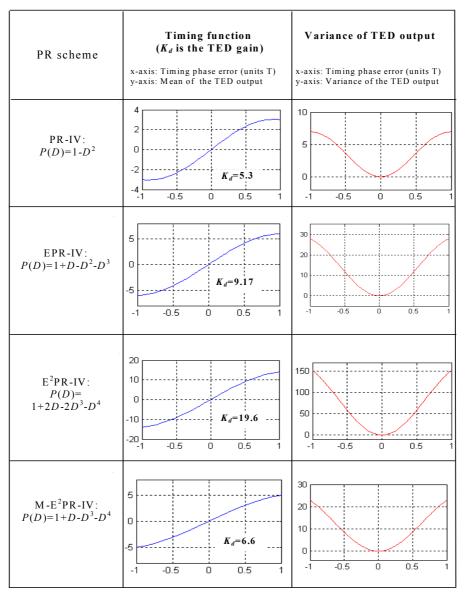

| 4.2 TED Analysis for PR Recording Systems                                            | 68 |

| 4.3 TED Analysis for DFE Recording Systems                                           |    |

| 4.4 Marginal Detection-Based TED.                                                    |    |

| 4.5 Optimality of MDFE Acquisition Performance                                       |    |

| 4.6 Conclusions                                                                      |    |

| References:                                                                          |    |

|                                                                                      |    |

| CHAPTER 5<br>FAST TIMING ACQUISITION FOR DECISION FEEDBACK EQUALIZATION<br>RECEIVERS IN MAGNETIC RECORDING  |     |

|-------------------------------------------------------------------------------------------------------------|-----|

| 5.1 Introduction                                                                                            |     |

| 5.2 Fast Acquisition for DFE with Modified Equalization                                                     | 90  |

| 5.3 Modified Threshold-based Timing Acquisition Scheme for DFE                                              |     |

| 5.4 Summary                                                                                                 |     |

| References:                                                                                                 | 103 |

| CHAPTER 6                                                                                                   |     |

| IMPLEMENTATION OF MULTI-LEVEL DECISION FEEDBACK EQUALIZAT                                                   | ION |

| TIMING RECOVERY SYSTEM                                                                                      | 105 |

| 6.1 Introduction to MDFE Read Channel Prototype                                                             |     |

| 6.2 Implementation of MDFE Timing Recovery System                                                           |     |

| 6.3 Evaluation of MDFE Prototype                                                                            | 119 |

| 6.4 Considerations of Hardware Implementation                                                               | 123 |

| 6.5 Conclusions                                                                                             | 124 |

| References:                                                                                                 | 125 |

| ASYNCHRONOUS EQUALIZER ADAPTATION AND INTERPOLATIVE TIMI<br>RECOVERY FOR A DIGITAL OPTICAL RECORDING SYSTEM | 127 |

| 7.1 Introduction                                                                                            |     |

| 7.2 Overview of Interpolation Techniques                                                                    |     |

| <ul><li>7.3 Advantages of Using ITR for DVR.</li><li>7.4 Novel Asynchronous Adaptation Structure.</li></ul> |     |

| <ul> <li>7.4 Novel Asynchronous Adaptation Structure</li></ul>                                              |     |

| <ul><li>7.5 DVR System Model</li><li>7.6 Realization of SRC and ITR for DVR</li></ul>                       |     |

| 7.7 Simulations of Asynchronous Equalizer Adaptation and ITR Loops for DVR                                  |     |

| <ul><li>7.8 Summary and Further Discussions.</li></ul>                                                      | 152 |

| References:                                                                                                 |     |

| CHAPTER 8                                                                                                   |     |

| SUMMARY AND CONCLUSIONS                                                                                     | 157 |

| 8.1 Further Work                                                                                            | -   |

|                                                                                                             |     |

| Samenvatting                                                                                                | 161 |

| Publications by the author                                                                                  |     |

| Curriculum Vitae                                                                                            | 165 |

# GLOSSARY

## Abbreviations

| A/D :      | Analog-to-Digital converter.                    |

|------------|-------------------------------------------------|

| AGC :      | Automatic Gain Control.                         |

| AWG :      | Arbitrary Waveform Generator.                   |

| AWGN :     | Additive White Gaussian Noise.                  |

| BECM :     | Band-Edge Component Maximization.               |

| BER :      | Bit Error Rate.                                 |

| CAD :      | Computer Aided Design.                          |

| CD :       | Compact Disc.                                   |

| D/A :      | Digital-to-Analog Converter.                    |

| DA :       | Data-Aided.                                     |

| DC :       | Direct Current.                                 |

| DD :       | Decision-Directed.                              |

| DDFE:      | Dual Decision Feedback Equalization.            |

| DFE :      | Decision Feedback Equalization.                 |

| DFT :      | Discrete-time Fourier Transform.                |

| DPO :      | Digital Phosphor Oscilloscope.                  |

| DVR:       | Digital Video Recording                         |

| DSP :      | Digital Signal Processor.                       |

| DVD :      | Digital Versatile Disc.                         |

| ECC :      | Error Control Coding.                           |

| ECL :      | Emitter-Coupled Logic.                          |

| EER :      | Error Event Rate.                               |

| EPR4 :     | Extended class IV Partial Response.             |

| $E^2PR4$ : | Extended order-2 class IV Partial Response.     |

| FBF :      | Feedback Filter.                                |

| FDTS/DF :  | Fixed Delay Tree Search with Decision Feedback. |

| FEQ :      | Forward Equalizer.                              |

| FIR :      | Finite Impulse Response.                        |

| HDD :      | Hard Disk Drive.                                |

| IC :       | Integrated Circuit.                             |

| IIR :      | Infinite Impulse Response.                      |

| ISI :      | Intersymbol Interference.                       |

| ITP :      | Interpolation                                   |

ITR : Interpolation. ITR : Interpolative Timing Recovery.

| IT.           | Loop Eilter                                       |

|---------------|---------------------------------------------------|

| LF:           | Loop Filter.<br>Low-Pass Filter.                  |

| LPF:          |                                                   |

| LMS :         | Least-Mean-Square.                                |

| MAP :         | Maximum A Posteriori.                             |

| MDFE :        | Multi-level Decision Feedback Equalization.       |

| MLSD :        | Maximum Likelihood Sequence Detector.             |

| ML :          | Maximum-Likelihood.                               |

| MMSE :        | Minimum Mean-Square Error.                        |

| MR:           | Magneto-Resistive.                                |

| MSE :         | Mean-Square Error.                                |

| MSB :         | Most Significant Bit.                             |

| MT :          | Modified Threshold.                               |

| NCO :         | Numerically Controlled Oscillator.                |

| NDA :         | Non-Data-Aided.                                   |

| NDD :         | Non-Decision-Directed.                            |

| NRZ :         | Non-Return to Zero.                               |

| NRZI :        | Non-Return to Zero Inverse.                       |

| PAM :         | Pulse-Amplitude modulation.                       |

| PCB :         | Printed Circuit Board.                            |

| PDF :         | Probability Density Function.                     |

| PLL :         | Phase-Locked Loop.                                |

| PR :          | Partial Response.                                 |

| PR4 :         | class IV Partial Response.                        |

| PR4-VD :      | class-IV Partial-Response with Viterbi Detection. |

| PRML :        | Partial Response with Maximum Likelihood.         |

| PSD :         | Power Spectral Density.                           |

| RC :          | Resistor-Capacitor.                               |

| RF :          | Radio Frequency.                                  |

| RLL :         | Run-Length-Limited.                               |

| RMS :         | Root-Mean-Square.                                 |

| SNR :         | Signal-to-Noise Ratio.                            |

| SRC :         | Sample Rate Conversion.                           |

| STI :         | Spatio-Temporal Interpolation.                    |

| TA :          | Thermal Asperity.                                 |

| TED :         | Timing Error Detector.                            |

| VCO :         | Voltage Controlled Oscillator.                    |

| VCO :<br>VD : | Viterbi Detector.                                 |

| ۷D.           |                                                   |

- VGA :

- Variable Gain Amplifier. Zero-Crossing Detection. Zero-Forcing. ZCD :

- ZF:

## Often Used Symbols

$a_k$ : RLL coded data bit sequence in alphabet  $a_k \in \{-1, 1\}$ .

$A(e^{j2\pi\Omega})$ : PSD of data  $a_k$ .

$b_k$ : RLL encoder output in alphabet  $b_k \in \{0, 1\}$ .

$B_1$ : PLL equivalent noise bandwidth.

(d, k): two constraint-parameters of RLL codes.

$d_k$ : desired (reference) sequence.

$D_{ch}$ : channel bit density.

$D_u$ : user bit density.

$e_k$ : error sequence.

f: frequency variable in units Hz.

h(t): channel bit response.

$\hat{h}(t)$ : isolated transition response.

k: discrete-time index in units T.

$K_d$ : TED gain, i.e., slope of  $\rho(\tau)$  at the origin  $\tau = 0$ .

n(t): channel additive noise.

$N_o/2$ : PSD of two-sided 'white' noise.

$pw_{50}$  : pulse width (in seconds) at 50% base-to-peak amplitude of  $\tilde{h}(t)$  .

r(t): readback (replay) signal at the channel output.

*R* : RLL modulation encoder rate,  $0 < R \le 1$ .

*SNR*<sub>loop</sub>: PLL loop signal-to-noise ratio.

$SNR_m$ : signal-to-noise ratio in the matched filter bound sense.

$S_u(e^{j2\pi\Omega})$ : PSD of noise component  $u_k$  at the TED output.

*t* : continuous-time index in seconds.

$t_k$ :  $k^{\text{th}}$  sampling instant in seconds.

T: duration of one bit in seconds.

$u_k$ : noise component at the TED output.

$y_k$ : discrete-time detector input.

$y'_k$ : sampled derivative of signal y(t) with respect to t at instants  $t_k$ .

$\gamma$  : TED efficiency.

$\Gamma$ : time-constant of the first-order PLL in units T.

$\rho(\tau)$ : timing function, i.e. TED characteristics.

$\varsigma$ : damping factor of the continuous-time second-order PLL.

$\zeta^{d}$ : damping factor of the discrete-time second-order PLL.

$\theta_k$ : input-referred phase noise of the PLL.

$\sigma_{\theta}^2$ : variance of  $\theta_k$ .

au : timing phase error in units *T*.

$\phi$ : unknown channel delay in units T.

$\chi_k$ : TED output.

$\psi$ : sampling phase in units *T*.

$\omega_n$ : natural frequency of the continuous-time second-order PLL.

$\omega_n^d$ : natural frequency of the discrete-time second-order PLL.

$\Omega$ : normalized frequency variable in units 1/*T*, i.e.  $\Omega = fT$ .

## Notational Conventions

D: one-bit interval delay operator. E[x]: expected value of x. Im[x]: imaginary part of a complex number x. **P** : matrices or vectors are boldfaced. **P**<sup>-1</sup>: matrix inverse.  $\mathbf{P}^{\mathrm{T}}$ : matrix or vector transpose. Q(x): Q-function, i.e.,  $Q(x) = \left(\sqrt{2\pi}\right)^{-1} \int_{x}^{\infty} \exp\left(-u^2/2\right) du$ .  $r_{x}(l)$ : autocorrelation function of x for lag l.  $\operatorname{Re}[x]$ : real part of a complex number x.  $s_k$ : sample element of sequence  $\{s_k\}$  at instant k.  $\{s_k\}$ : discrete-time sequence. |x|: absolute value (magnitude) of x. |x|: biggest integer not exceeding x.  $x^*$ : conjugate of a complex number x.  $\otimes$  : convolution operator.  $\oplus$ : modulo-2 addition operator.  $\delta(t)$ : Dirac's delta function.  $\delta_k$ : discrete-time delta function.

# LIST OF TABLES

| Table 4-1: PR TARGETS FOR MAGNETIC RECORDING SYSTEMS.                         | 69 |

|-------------------------------------------------------------------------------|----|

| Table 4-2: MEAN AND VARIANCE OF THE TED OUTPUT FOR PR MAGNETIC                |    |

| RECORDING SYSTEMS.                                                            | 71 |

| Table 4-3: RMS VALUES OF THE TIMING LOOP JITTER AND SUPPRESSION GAIN $\kappa$ |    |

| (USER DENSITY 3.0)                                                            | 80 |

| Table 4-4: TED EFFICIENCY LOSS OF THE MDFE TED RELATIVE TO THE ML TED.        |    |

| Table 5-1: INITIAL CONDITIONS OF MONTE-CARLO SIMULATIONS FOR MDFE TIMING      |    |

| ACQUISITION                                                                   | 93 |

# **LIST OF FIGURES**

| Fig.1-1: Block schematic of a magnetic recording system. The blocks enclosed by the dashed boxes                                                                                                     |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| constitute the read-write channel of the recording system.                                                                                                                                           |    |

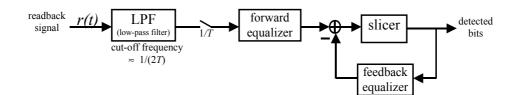

| Fig.1-2: Read channel with PR equalizer and Viterbi detector.                                                                                                                                        |    |

| Fig.1-3: Read channel with DFE detector.                                                                                                                                                             |    |

| Fig.1-4: Example of timing recovery system.                                                                                                                                                          |    |

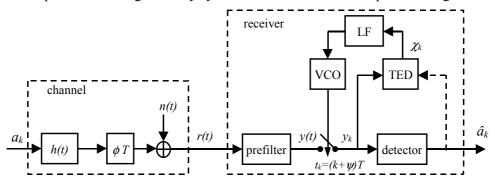

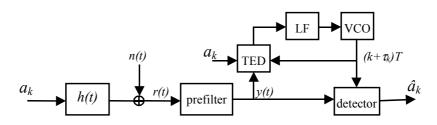

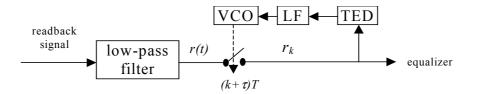

| Fig. 2-1: Schematic of a read-write channel with timing recovery.                                                                                                                                    |    |

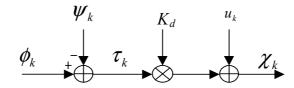

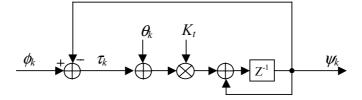

| Fig. 2-2: Linearized discrete-time phase-domain TED model.                                                                                                                                           | 19 |

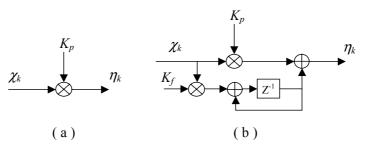

| Fig. 2-3: Structures of discrete-time loop filters: (a) proportional type, (b) proportional-plus-<br>integral type.                                                                                  | 10 |

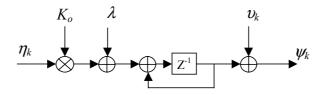

| Fig. 2-4: Discrete-time phase-domain model of VCO.                                                                                                                                                   |    |

| Fig. 2-4. Discrete-time phase-domain model of VCO.                                                                                                                                                   | 20 |

| frequency error.                                                                                                                                                                                     | 20 |

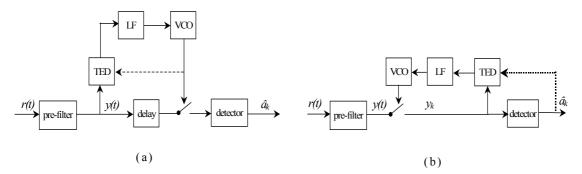

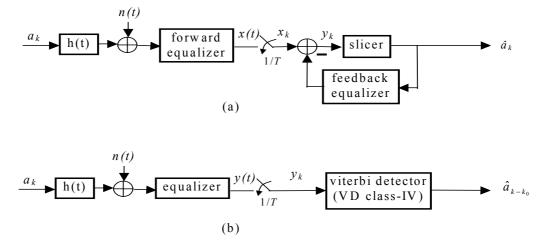

| Fig. 2-6: Receivers incorporating (a) deductive and (b) inductive timing recovery schemes                                                                                                            |    |

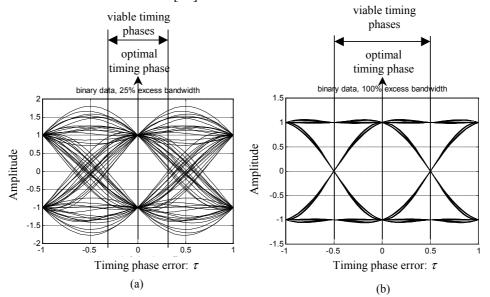

| Fig. 2-7: Eye patterns for a raised-cosine channel with (a) 25% and (b) 100% excess bandwidth                                                                                                        |    |

| Fig. 2-7: Eye patterns for a raised-cosine channel with (a) $25\%$ and (b) 100% excess bandwidth<br>Fig. 2-8: Eye patterns of (a) PR4 and (b) $E^2PR4$ partial response channels that have no excess | 23 |

| bandwidth                                                                                                                                                                                            |    |

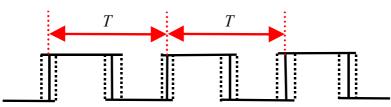

| Fig. 2-9: Recovered clock with phase jitter.                                                                                                                                                         | 24 |

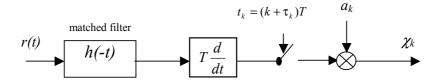

| Fig. 2-10: Data-aided ML TED scheme based on the matched filter                                                                                                                                      | 28 |

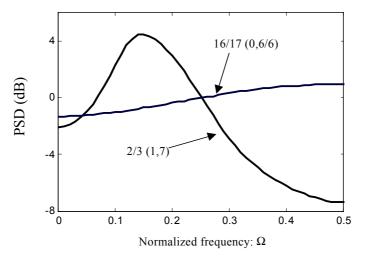

| Fig. 2-11: Power spectral densities of 2/3 (1, 7) and 16/17 (0, 6/6) RLL coded data.                                                                                                                 |    |

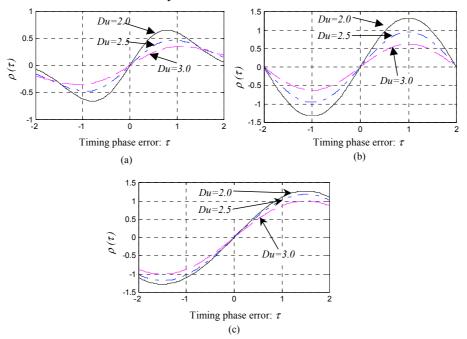

| Fig. 2-12: ML TED timing functions for the Lorentzian channel at different user densities $D_u$ with                                                                                                 |    |

| (a) uncorrelated data, (b) 4T-training data, and (c) 6T-training data                                                                                                                                | 30 |

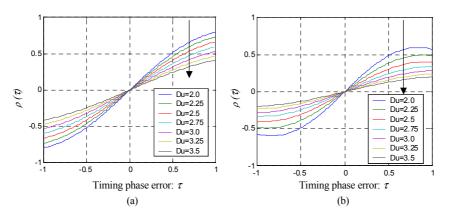

| Fig. 2-13: ML TED timing functions for the RLL coded Lorentzian channel at different user                                                                                                            |    |

| densities $D_u$ with (a) $2/3$ (1,7) coded data and (b) $16/17$ (0, $6/6$ ) coded data.                                                                                                              | 30 |

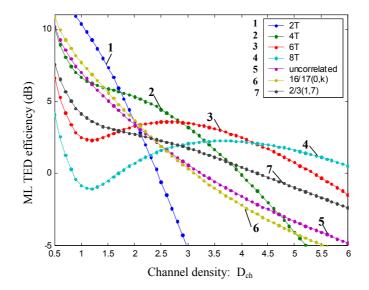

| Fig. 2-14: ML TED efficiency for the Lorentzian recording channel with various data patterns                                                                                                         |    |

| versus the channel density                                                                                                                                                                           | 31 |

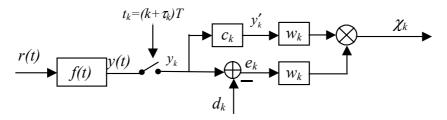

| Fig. 2-15: TED structure of MMSE timing recovery scheme.                                                                                                                                             | 32 |

| Fig. 2-16: Simplified TED structure of MMSE timing recovery scheme.                                                                                                                                  |    |

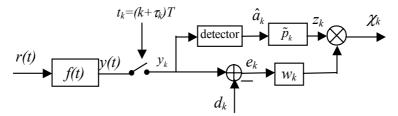

| Fig. 2-17: TED structure of a ZF timing recovery scheme.                                                                                                                                             |    |

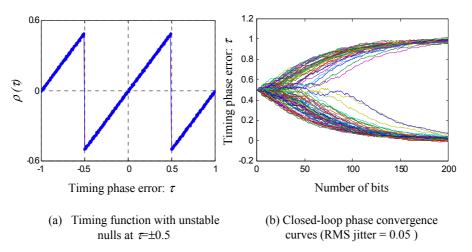

| Fig. 2-18: Demonstration of hang up problem when the unstable nulls in the timing function arise                                                                                                     |    |

| from discontinuities.                                                                                                                                                                                | 36 |

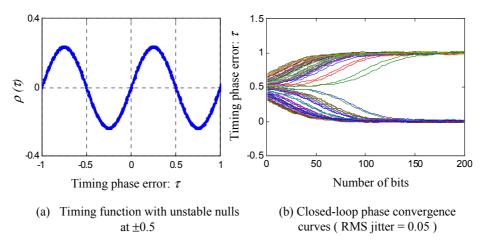

| Fig. 2-19: Demonstration of hang up problem when the timing function has undesired nulls with                                                                                                        | 27 |

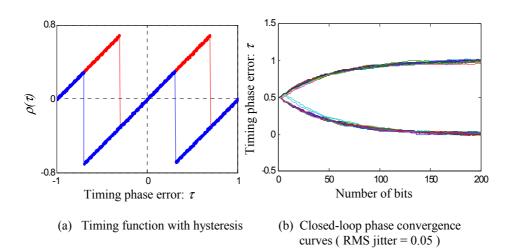

| wrong slopes.<br>Fig. 2-20: Demonstration of how hang up can be avoided by incorporating hysteresis in the timing                                                                                    |    |

|                                                                                                                                                                                                      | 20 |

| function.                                                                                                                                                                                            |    |

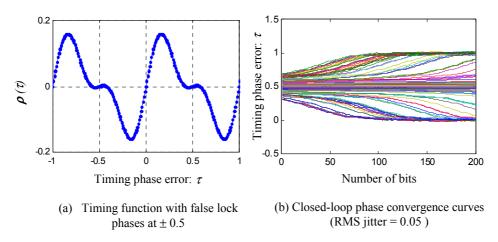

| Fig. 2-21: Demonstration of false lock phenomenon arising from undesired zero-crossings of the                                                                                                       | •  |

| timing function.                                                                                                                                                                                     |    |

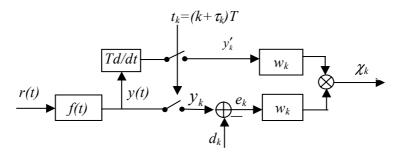

| Fig. 2-22: Non-decision-directed TED for timing acquisition in recording systems.                                                                                                                    | 40 |

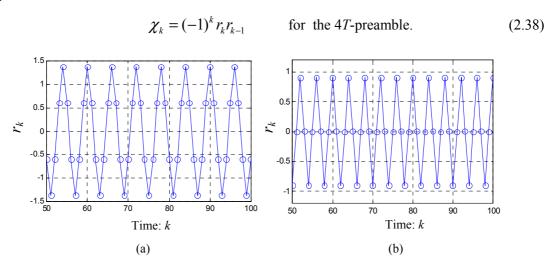

| Fig. 2-23: Symbol-rate samples (marked by 'o' at the ideal sampling phase) of replay signal of the                                                                                                   |    |

| Lorentzian recording channel corresponding to (a) 6T pattern and (b) 4T pattern preamble                                                                                                             |    |

| sequences.                                                                                                                                                                                           | 41 |

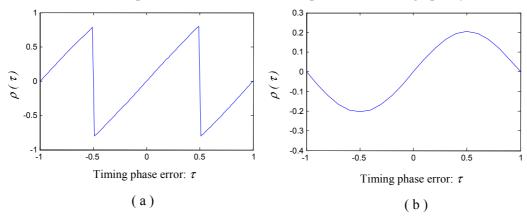

| Fig. 2-24: Timing functions corresponding to the NDD TEDs for using (a) $6T$ pattern and (b) $4T$                                                                                                    |    |

| pattern preamble sequences.                                                                                                                                                                          | 41 |

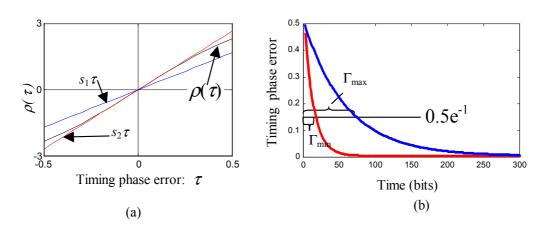

| Fig. 2-25: Illustration of (a) a timing function and (b) its corresponding phase convergence with                                                                                                    |    |

| maximum and minimum time constants.                                                                                                                                                                  | 45 |

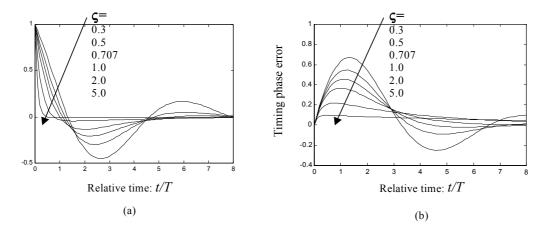

| Fig. | 2-26: Second-order continuous-time PLL transient responses with (a) timing phase error due to a unit phase step and (b) timing phase error due to a unit frequency step. The damping                |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | factor $\varsigma$ is used as a parameter                                                                                                                                                           | 46  |

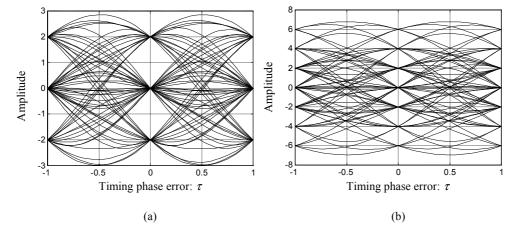

|      | 3-1: Magnetic recording system model incorporating (a) MDFE and (b) PR4-VD detector                                                                                                                 | 52  |

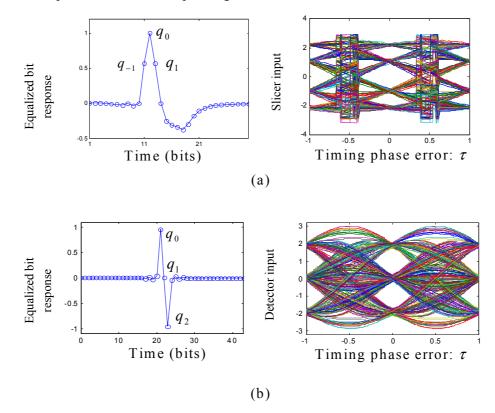

| Fig. | 3-2: Equalized bit response $q_k$ and the noiseless detector inputs $y_k$ for different timing phase                                                                                                |     |

|      | errors $\tau$ for (a) MDFE and (b) PR4-VD detectors at user density 2.5                                                                                                                             | 54  |

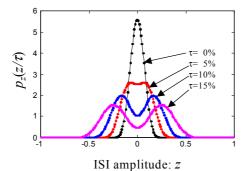

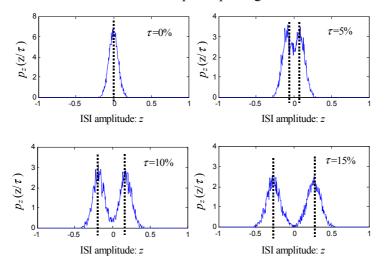

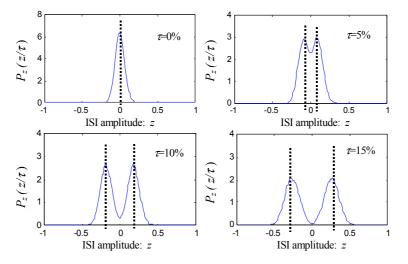

| Fig. | 3-3: PDF of inner level residual ISI in the presence of timing phase errors (obtained by                                                                                                            |     |

|      | computation).                                                                                                                                                                                       | 57  |

| Fig. | 3-4: PDF of inner-level residual ISI in the presence of timing phase errors (obtained by                                                                                                            |     |

|      | simulation).                                                                                                                                                                                        | 57  |

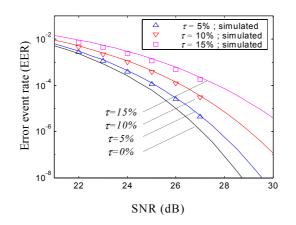

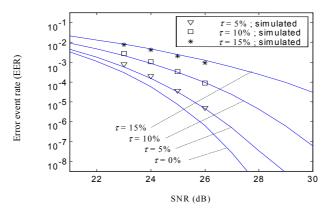

| Fig. | 3-5: Error event rate of MDFE in the presence of timing phase error $\tau$ (solid curves: EER                                                                                                       |     |

| -    | obtained by calculation).                                                                                                                                                                           | 58  |

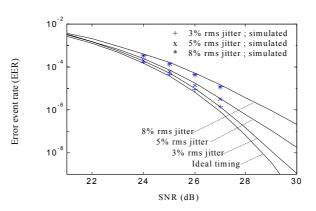

| Fig. | 3-6: Error event rate of MDFE in the presence of random phase jitter (solid curves: EER                                                                                                             |     |

|      | obtained by calculation).                                                                                                                                                                           | 59  |

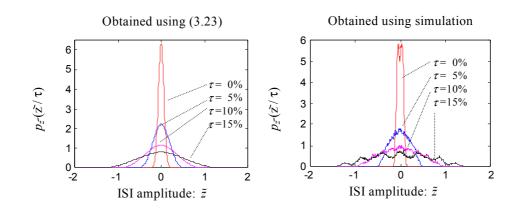

| Fig. | 3-7: PDF of residual ISI $\tilde{z}_{k}(\tau)$ obtained using analytical and simulation approaches.                                                                                                 | 61  |

| -    | 3-8: Error event rate of PR4-VD in the presence of timing phase error (solid curves:                                                                                                                |     |

| гıg. | obtained using calculation based on Eq. (3.23)).                                                                                                                                                    | 61  |

| Fig  | 3-9: PDF of inner-level ISI in the presence of timing phase errors (obtained using                                                                                                                  | 01  |

| гıg. |                                                                                                                                                                                                     | 62  |

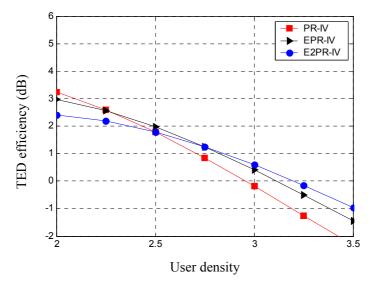

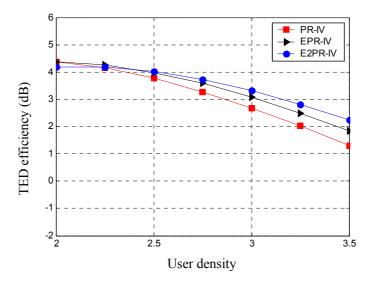

| Fie  | calculation)<br>4-1: TED efficiency for Lorentzian recording channel and rate 16/17 (0,6/6) code                                                                                                    |     |

|      |                                                                                                                                                                                                     |     |

|      | 4-2: TED efficiency for Lorentzian recording channel and rate 2/3 (1,7) code                                                                                                                        |     |

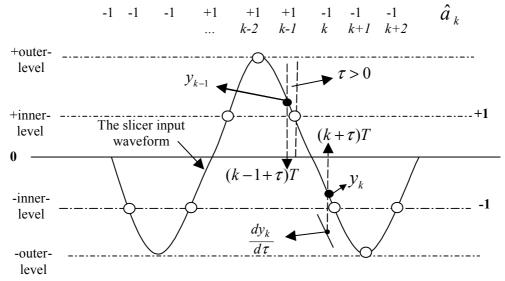

|      | 4-3: Illustration of the existing transition-based MDFE TED algorithm.                                                                                                                              |     |

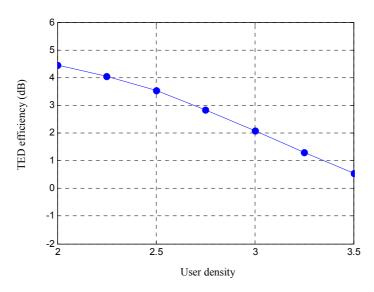

|      | 4-4: TED efficiency for the MDFE transition-based TED.                                                                                                                                              |     |

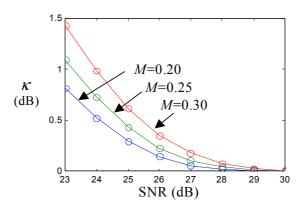

|      | 4-5: TED output noise variance suppression factor $\kappa$ at user density 3.0                                                                                                                      | 80  |

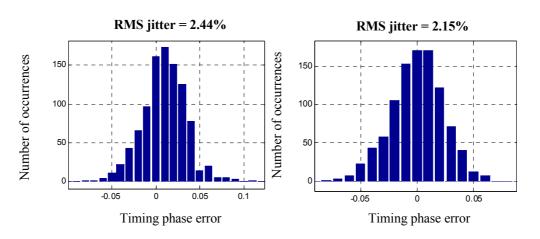

| Fig. | 4-6: Distribution histogram of timing phase error for the TEDs with (right) and without                                                                                                             | 01  |

| Ein  | (left) the marginal detection scheme.                                                                                                                                                               |     |

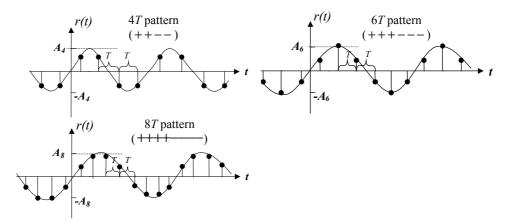

|      | 4-7: Replay waveforms at the output of Lorentzian channel.                                                                                                                                          |     |

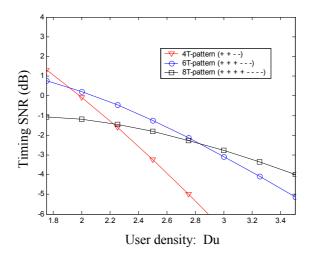

| Fig. | 4-8: Timing SNR for the 4 <i>T</i> , 6 <i>T</i> and 8 <i>T</i> preamble patterns, on a rate 2/3 (1,7) coded                                                                                         | 01  |

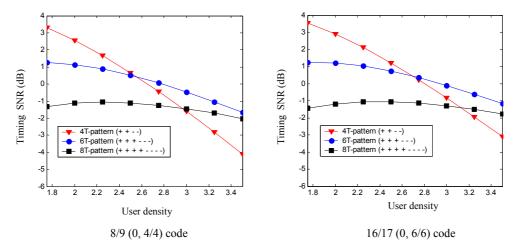

| Fie  | Lorentzian channel.                                                                                                                                                                                 |     |

|      | 4-9: Timing SNR for the 4 <i>T</i> , 6 <i>T</i> and 8 <i>T</i> patterns in a $(0,k)$ coded Lorentzian channel                                                                                       | 83  |

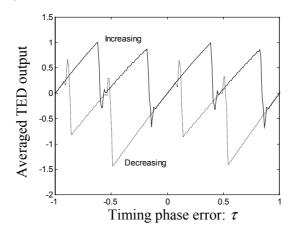

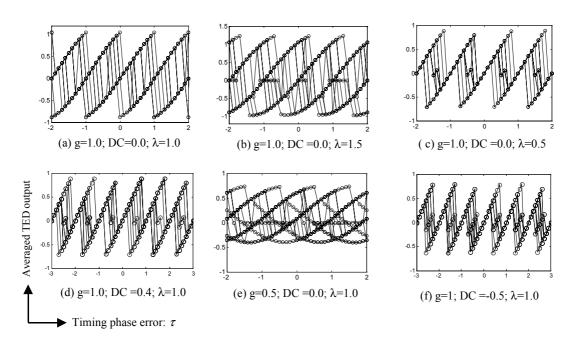

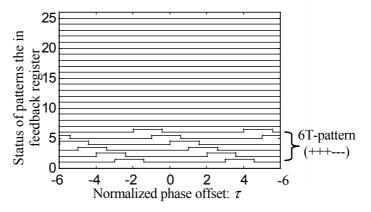

| гıg. | 5-1: The averaged TED output when the normalized sampling phase offset is changed                                                                                                                   | 90  |

| Fie  | dynamically from -1 to 1 and from 1 to $-1$ .                                                                                                                                                       | 90  |

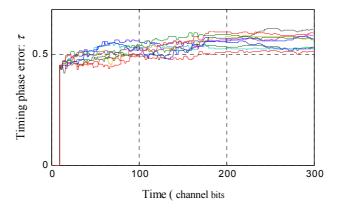

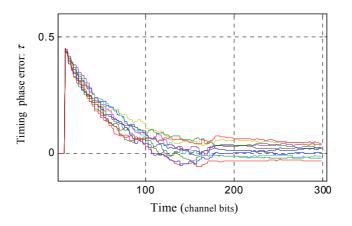

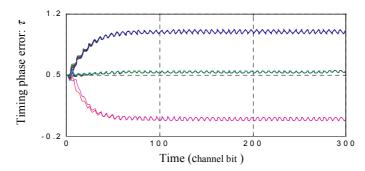

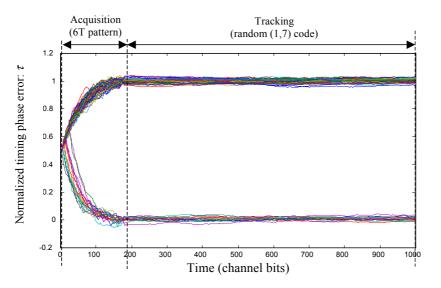

| гıg. | 5-2: Phase convergence curves at $D_u = 3.0$ and $SNR = 27$ dB with the MDFE TED (10 simulation runs).                                                                                              | 91  |

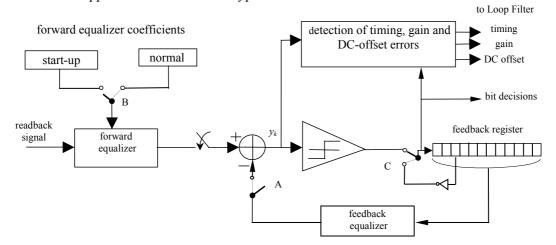

| Fig  | 5-3: Modified forward equalizer based MDFE timing acquisition scheme.                                                                                                                               |     |

|      | 5-4: Timing function of MDFE using the 4-step acquisition scheme.                                                                                                                                   |     |

|      | 5-4. Thing function of MDFE using the 4-step acquisition scheme.<br>5-5: Phase convergence curves at $D_u = 3.0$ and SNR = 27 dB (with the 4-step acquisition                                       |     |

| гıg. | scheme).                                                                                                                                                                                            | 92  |

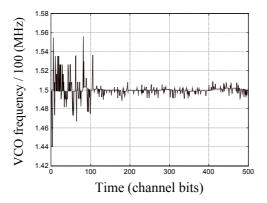

| Fig  | 5-6: Convergence of VCO frequency (data rate in the channel is 150 Mb/s)                                                                                                                            |     |

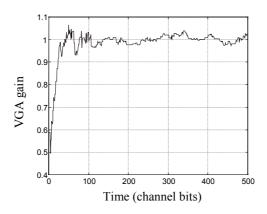

|      | 5-7: Convergence of VGA gain (ideal value of VGA gain is 1.0)                                                                                                                                       |     |

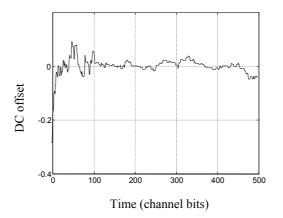

|      | 5-8: Convergence of DC offset (ideal value of DC offset is 0).                                                                                                                                      |     |

|      |                                                                                                                                                                                                     |     |

| гıg. | 5-9: Timing functions based on the variable threshold $c_k = \lambda \hat{a}_{k-3}$ for MDFE acquisition                                                                                            |     |

|      | scheme using the $6T('+++)$ preamble (Horizontal axis: normalized phase offset,                                                                                                                     | 0(  |

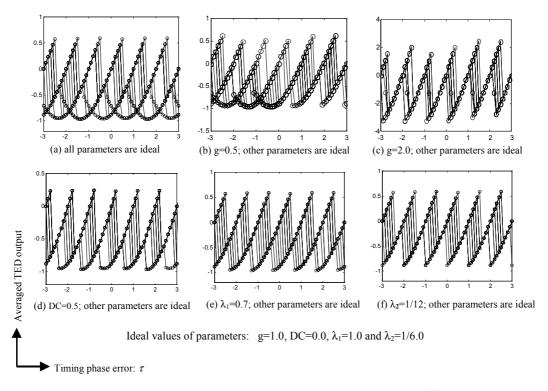

| Ein  | τ, Vertical axis: averaged TED output).                                                                                                                                                             | 96  |

| Fig. | 5-10: Closed-loop phase convergence in the presence of a fixed DC offset 0.5 with $medified threehold = \frac{1}{2}$ in a prejudent should be the set of the presence of a fixed DC offset 0.5 with | 06  |

| г:.  | modified threshold $c_k = \hat{a}_{k-3}$ in a noiseless channel.                                                                                                                                    | 96  |

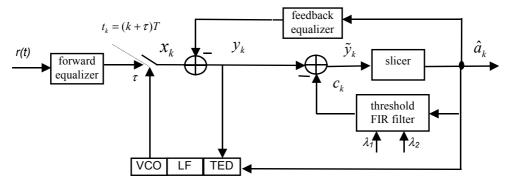

|      | 5-11: Modified threshold timing-acquisition scheme for DFE detector.                                                                                                                                |     |

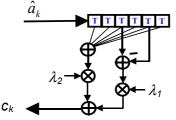

|      | 5-12: Structure of modified threshold filter.                                                                                                                                                       | 97  |

| гıg. | 5-13: Illustration of the role of MT sequence $c_k$ to shift the decision sequence from one phase of the <i>CT</i> pattern to enother                                                               | 0.0 |

| E:   | phase of the 6 <i>T</i> pattern to another.                                                                                                                                                         |     |

| гıg. | 5-14: Results indicating which of the first 25 tagged patterns are presented in the feedback                                                                                                        | 00  |

| г:   | register at the time of the 25 <sup>th</sup> bit instant from the start of acquisition                                                                                                              |     |

| гıg. | 5-15: Timing functions based on the MT scheme $c_k = \lambda_1(\hat{a}_{k-3} - \hat{a}_{k-3}) + \lambda_2 \sum_{i=1 \to 6} \hat{a}_{k-i}$ . (Horizontal                                             | 100 |

|      | <u>axis</u> : normalized phase offset, $\tau$ ; <u>Vertical axis</u> : averaged TED output).                                                                                                        | 100 |

-

| Fig.      | 5-16: Closed-loop phase convergence in the presence of a fixed DC offset 0.5 with the MT                                    | 100 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|-----|

| г.        | scheme $c_k = \lambda_1(\hat{a}_{k-3} - \hat{a}_{k-3}) + \lambda_2 \sum_{i=1 \to 6} \hat{a}_{k-i}$ for a noiseless channel. | 100 |

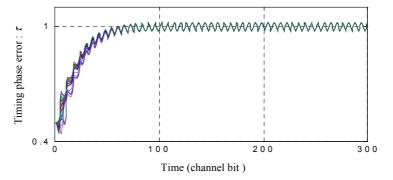

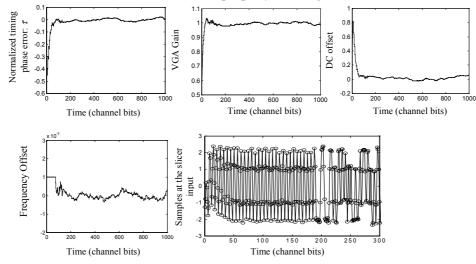

| Fig.      | 5-17: Convergence of parameters with closed timing, gain and DC loops (horizontal axis:                                     | 101 |

| г:.       | time in channel bits).                                                                                                      | 101 |

| Fig.      | 5-18: Phase convergence curves for 5000 acquisition trials at user density 3.0 and 23 dB                                    | 101 |

| г.        | SNR                                                                                                                         |     |

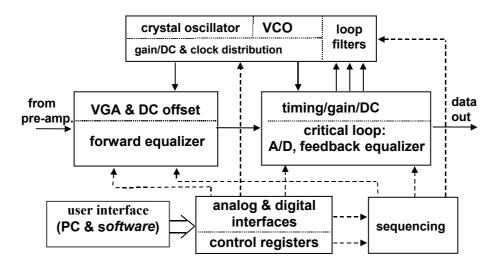

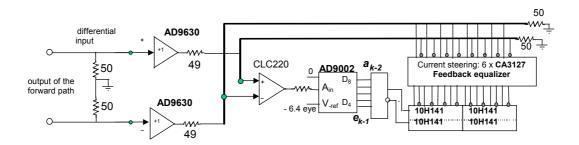

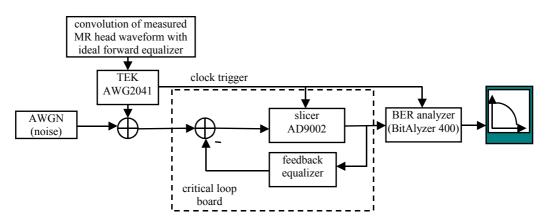

|           | 6-1: Structure of MDFE prototype                                                                                            | 106 |

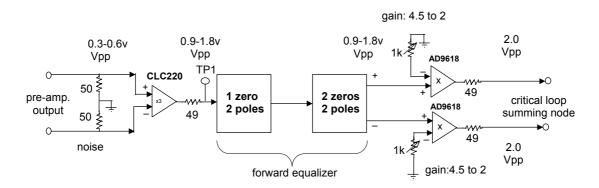

| F1g.      | 6-2: Implementation of the forward path from the preamplifier output to the critical loop                                   | 105 |

| <b></b> . | input, consisting of a 4-pole/3-zero forward equalizer                                                                      |     |

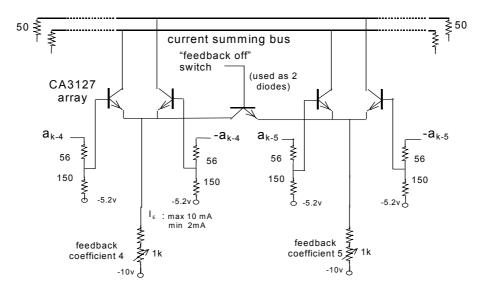

|           | 6-3: Implementation of the feedback equalizer using current steering switches.                                              |     |

|           | 6-4: Implementation of the critical-loop.                                                                                   |     |

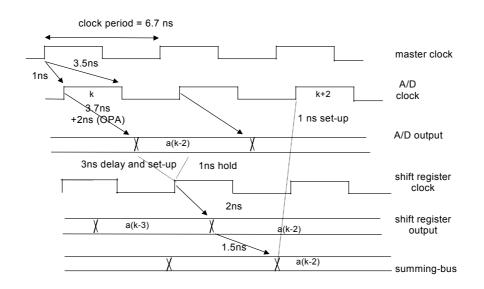

|           | 6-5: MDFE critical loop timing diagram.                                                                                     | 109 |

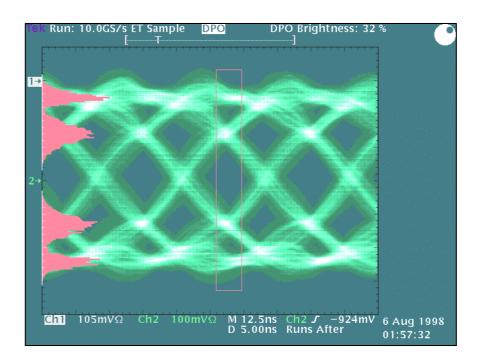

| Fig.      | 6-6: Eye pattern measured at the analog summing bus showing the four levels at ideal                                        | 100 |

| <b></b> . | sampling instants (the block marks the desired sampling instant).                                                           | 109 |

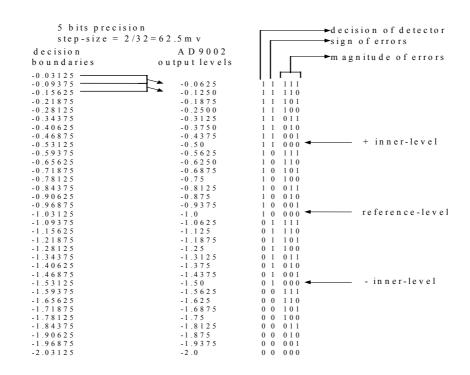

| Fig.      | 6-7: Mappings of input to 5-bit output of the 8-bit AD9002 A/D converter with error pattern                                 |     |

| <b></b> . | assignment.                                                                                                                 | 110 |

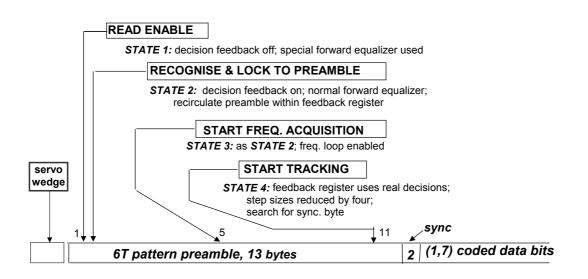

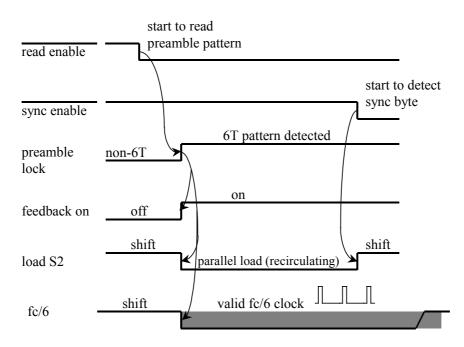

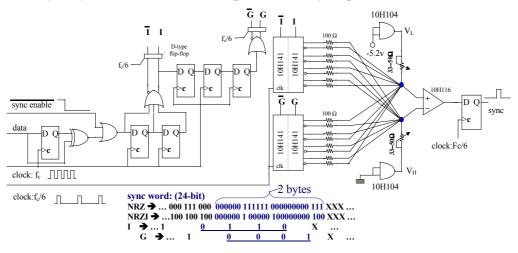

| Fig.      | 6-8: Data format of one sector of magnetic disk for MDFE timing acquisition, sync byte                                      |     |

|           | detection and clock tracking.                                                                                               |     |

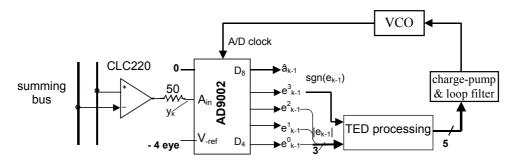

| Fig.      | 6-9: Block schematic of the overall timing loop which uses the A/D output for generating the                                | 110 |

|           | error signal for TED                                                                                                        |     |

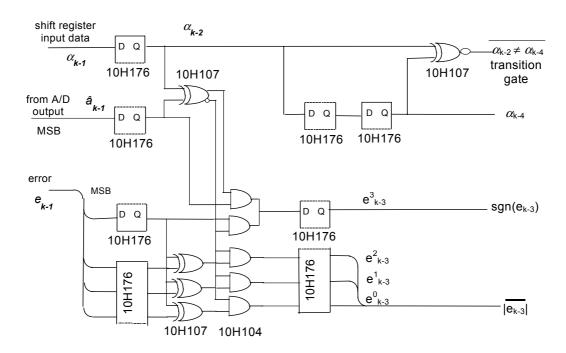

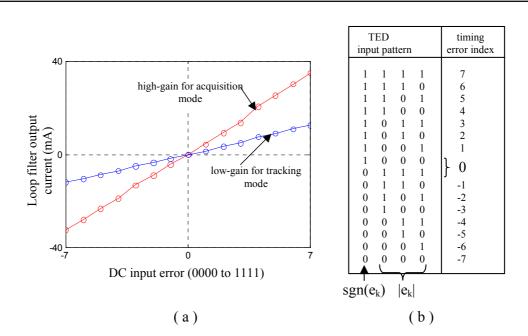

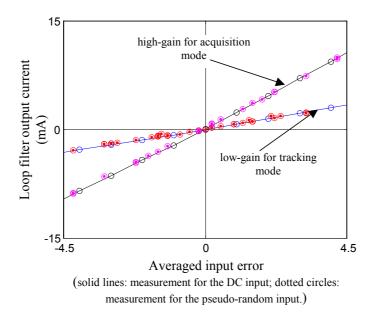

|           | 6-10: Digital error generation for TED implementation.                                                                      |     |

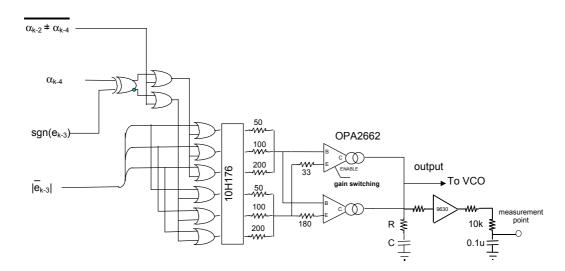

|           | 6-11: Circuit for implementing the charge-pump and loop filter                                                              | 114 |

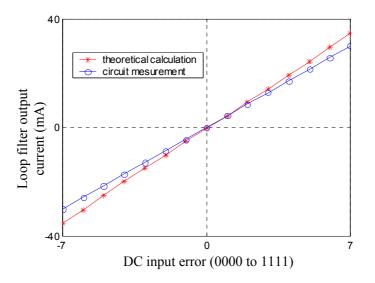

| Fig.      | 6-12: (a) Measured static transfer function from the digital TED input to the output of RC                                  |     |

|           | loop filter; (b) Table that shows the relation between the input patterns and timing errors                                 |     |

|           | 6-13: Measured transfer function of the charge-pump circuit for waveform input                                              | 115 |

| Fig.      | 6-14: Comparison of measured and simulated transfer functions from TED input to the loop                                    |     |

|           | filter output under high-gain conditions                                                                                    |     |

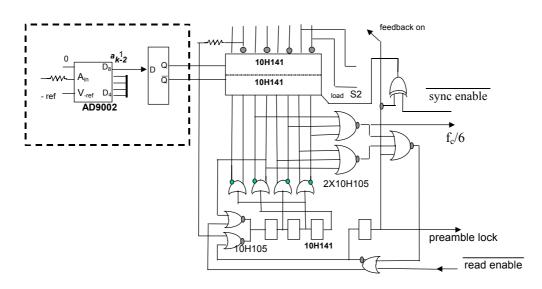

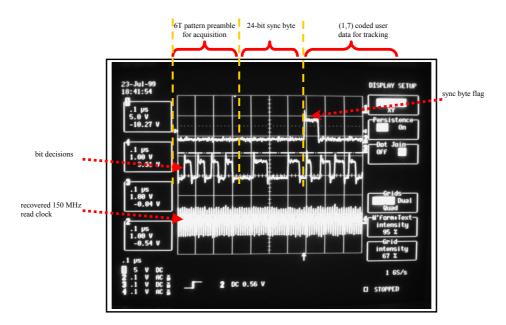

|           | 6-15: Lock-to-Preamble circuit for preloading the 6T pattern.                                                               |     |

|           | 6-16: Timing diagram of the lock-to-preamble circuit.                                                                       |     |

|           | 6-17: Sync-byte detection circuit.                                                                                          |     |

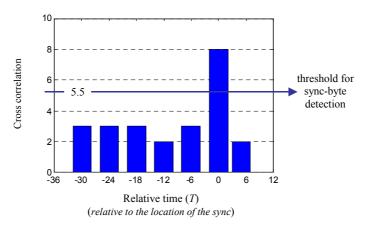

|           | 6-18: Cross-correlation of the data in the shift-registers and the word '01100001'.                                         |     |

|           | 6-19: Measured waveforms from the sync-byte detection circuit                                                               | 119 |

| Fig.      | 6-20: Bench test setup for measuring the BER performance of the critical loop board (the                                    |     |

|           | portion in the dashed block) of the MDFE prototype.                                                                         |     |

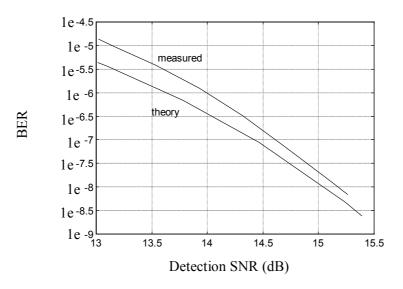

|           | 6-21: Measured and theoretical BER performance of the critical loop board                                                   |     |

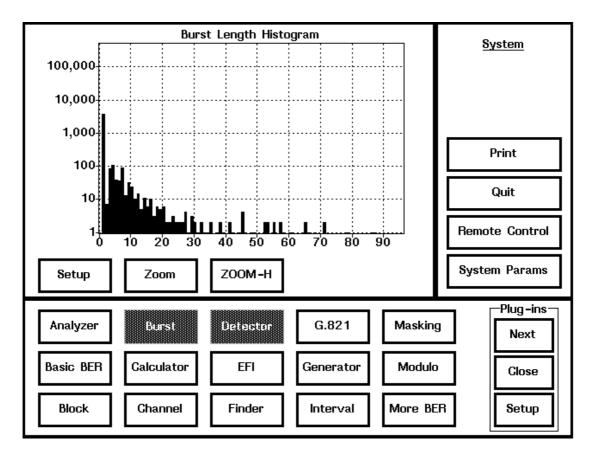

| Fig.      | 6-22: Histogram of MDFE burst errors measured using BitAlyzer400.                                                           | 121 |

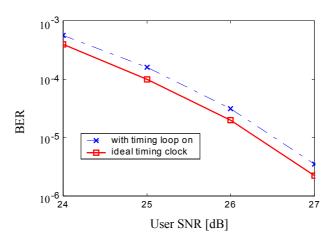

| Fig.      | 6-23: Measurement of the BER performance of the MDFE board at user density of 2.5, with                                     |     |

|           | and without active timing recovery loop                                                                                     |     |

| Fig.      | 6-24: Test setup for measuring random jitter in the recovered clock of the MDFE prototype                                   | 123 |

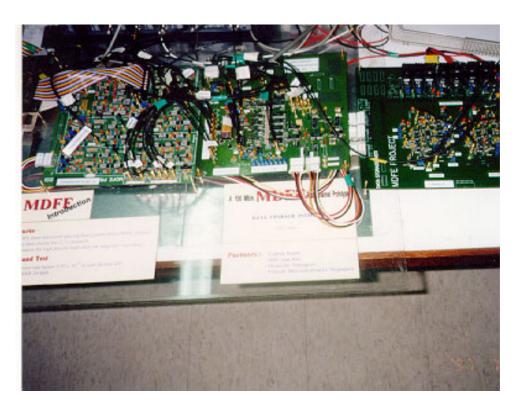

| Fig.      | 6-25: MDFE prototype circuits and timing board                                                                              | 124 |

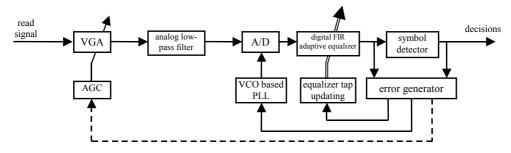

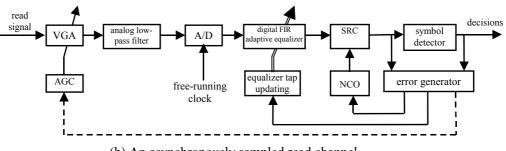

| Fig.      | 7-1: Synchronously sampled versus asynchronously sampled read channels                                                      | 129 |

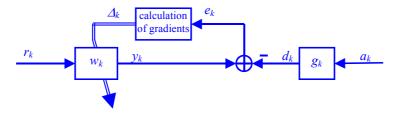

| Fig.      | 7-2: System model for studying synchronous equalizer adaptation algorithms                                                  | 131 |

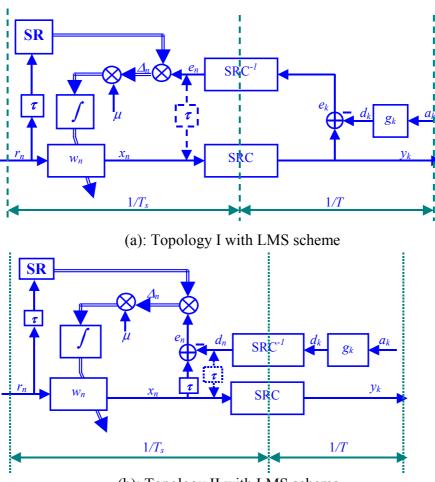

| Fig.      | 7-3: Existing topologies for asynchronous equalizer adaptation with LMS algorithm                                           | 134 |

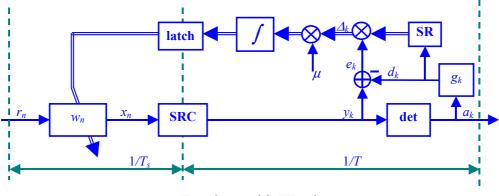

| Fig.      | 7-4: Novel structure for asynchronous equalizer adaptation with the ZF algorithm                                            | 135 |

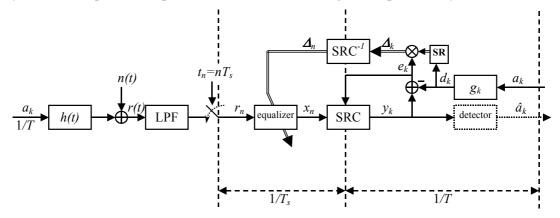

| Fig.      | 7-5: DVR system model.                                                                                                      | 136 |

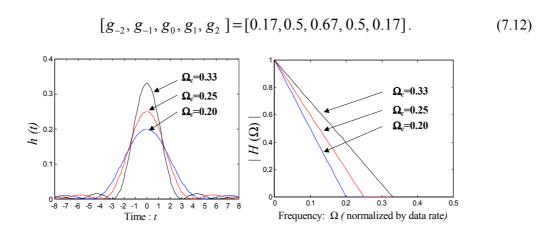

| Fig.      | 7-6: DVR channel bit response $h(t)$ and its magnitude response for $\Omega_c=0.20, 0.25$ and 0.33                          | 137 |

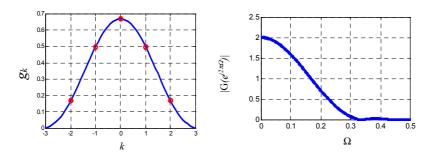

|           | 7-7: Target response g <sub>k</sub> and its magnitude response.                                                             |     |

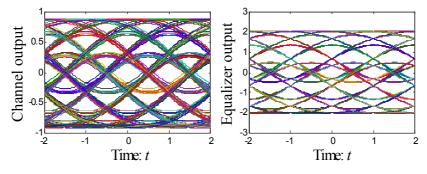

| Fig.      | 7-8: Eye patterns at the channel output and the equalizer output in the absence of noise for                                | -   |

| U         | $\Omega_{c}=0.33$                                                                                                           | 138 |

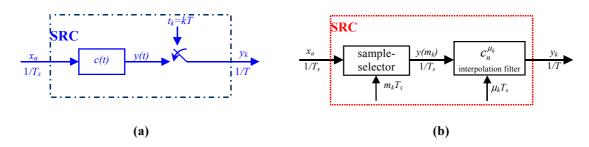

| Fig       | 7-9: Block diagram of SRC. (a): principle of resampling after reconstruction; (b) digital                                   |     |

| - 18.     | realization of SRC.                                                                                                         |     |

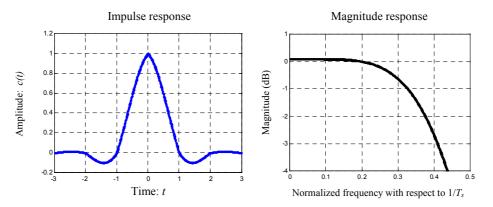

| Fig       | 7-10: Impulse response and frequency response of the six-point Lagrange interpolator                                        |     |

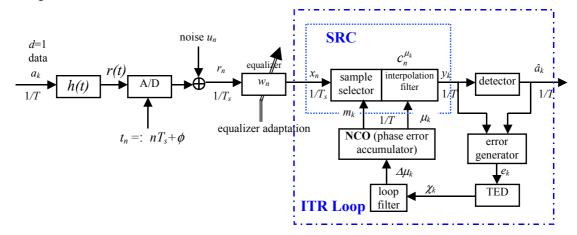

| -         | 7-11: Asynchronously sampled DVR system with ITR loop.                                                                      |     |

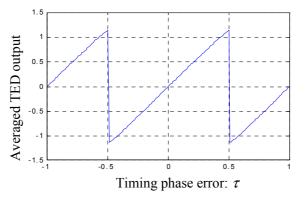

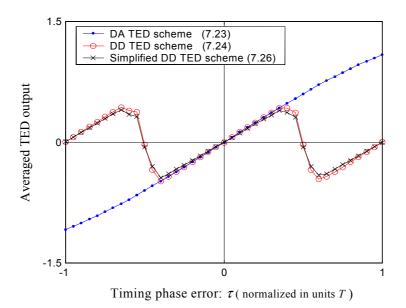

|           | 7-12: Timing functions for the DVR with $\Omega_c=0.33$ TED, no noise, and $d=1$ data                                       |     |

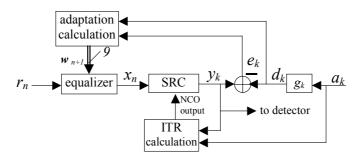

|           | 7-13: Block diagram with the equalizer adaptation and ITR loops.                                                            |     |

| 0-        | · ····································                                                                                      |     |

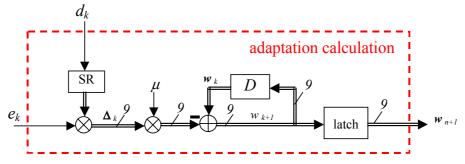

| Fig. | 7-14: Block diagram of equalizer adaptation calculation in the adaptation loop based on the                  |     |

|------|--------------------------------------------------------------------------------------------------------------|-----|

|      | latch-based asynchronous ZF adaptation structure.                                                            | 144 |

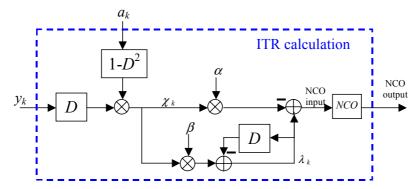

| Fig. | 7-15: Block diagram of ITR calculation for the NCO adjustment in the ITR loop.                               | 144 |

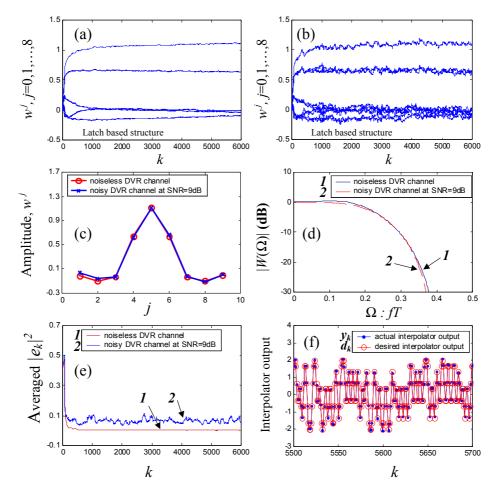

| Fig. | 7-16: Simulation results of synchronous adaptation at $T_s = T$ for a 9-tap equalizer. (a)                   |     |

| -    | coefficient convergence for the noiseless channel; (b) for the 9 dB SNR channel; (c) steady-                 |     |

|      | state equalizer coefficients; (d) corresponding equalizer magnitude response; (e) time-                      |     |

|      | averaged squared error convergence; (f) detector inputs.                                                     | 145 |

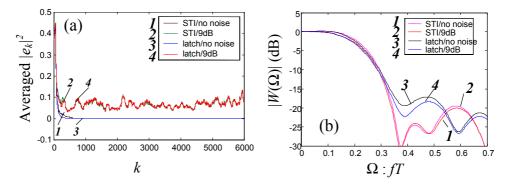

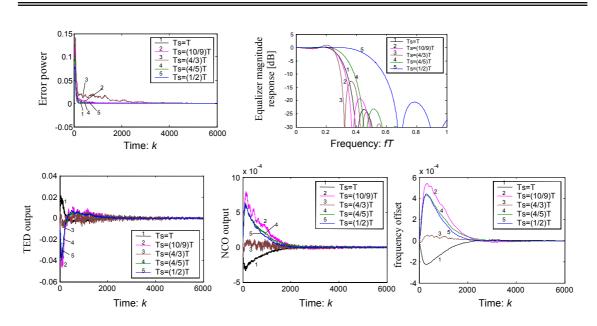

| Fig. | 7-17: Simulation results of undersampled asynchronous adaptation $(T_s = (4/3)T)$ : (a) time-                |     |

| -    | averaged error power convergence, (b) steady-state equalizer magnitude response                              | 146 |

| Fig. | 7-18: Simulation results of oversampled asynchronous adaptation $(T_s = (3/4)T)$ : (a) time-                 |     |

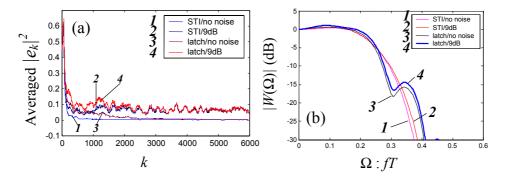

| -    | averaged error power convergence, (b) steady-state equalizer magnitude response                              | 146 |

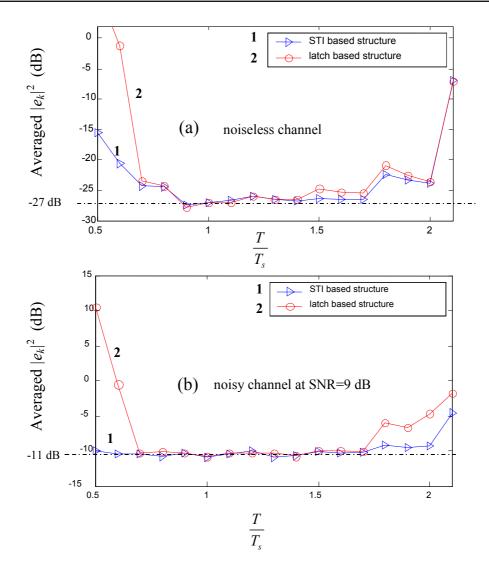

| Fig. | 7-19: Equalizer adaptation performance of the latch-based and STI-based structure for                        |     |

| -    | various sampling rates with (a) no noise; (b) 9 dB SNR                                                       | 148 |

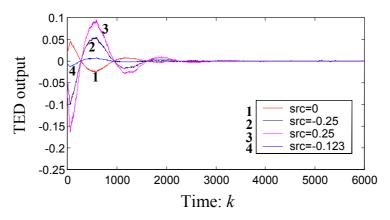

| Fig. | 7-20: TED output for various sampling rates for the noiseless DVR channel with a fixed                       |     |

|      | equalizer                                                                                                    | 149 |

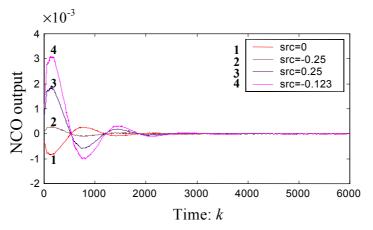

| Fig. | 7-21: NCO output for various sampling rates for the noiseless DVR channel with a fixed                       |     |

| -    | equalizer                                                                                                    | 149 |

| Fig. | 7-22: Frequency offset for various sampling rates for the noiseless DVR channel with a fixed                 |     |

|      | equalizer                                                                                                    | 150 |

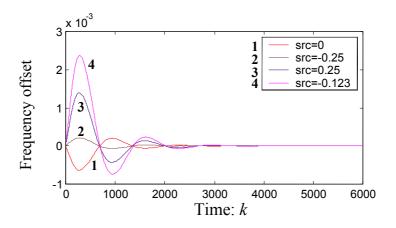

| Fig. | 7-23: Simulation results of the latch-based equalizer adaptation and ITR loops for the                       |     |

|      | noiseless DVR channel for $T_s = T$ , $T_s = (10/9)T$ , $T_s = (4/3)T$ , $T_s = (4/5)T$ and $T_s = (1/2)T$ . | 151 |

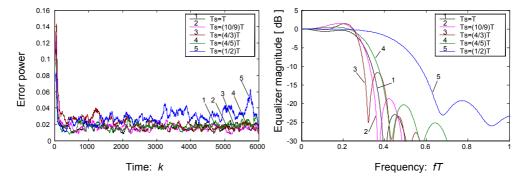

| Fig. | 7-24: Error power convergence of equalizer output and steady-state equalizer magnitude                       |     |

|      | response with latch-based equalizer adaptation and ITR loops at 9 dB SNR for $T_s = T_s$                     |     |

|      | $T_s = (10/9)T$ , $T_s = (4/3)T$ , $T_s = (4/5)T$ and $T_s = (1/2)T$ .                                       | 151 |

# **CHAPTER 1**

## INTRODUCTION

In this chapter, we first give a brief introduction to digital recording systems such as magnetic and optical systems. Following this, we present an overview of the key techniques used for data recovery in magnetic recording systems<sup>1</sup>. Our emphasis in this overview is on the role of coding and signal processing techniques in digital recording systems. Thereafter, we present the motivation for the work reported in this thesis. The chapter concludes with a brief description of the contributions in each chapter of the thesis.

## 1.1 Introduction to Digital Recording Technology

The advent of the information era and the fast growth of information technology have resulted in an enormous demand for the storage of digital data, along with demands for processing and transmission in huge volumes and/or at high speeds. The recording density and transfer rate of storage devices have had to increase at dramatically fast rates to accommodate this growing demand. For instance, the areal density and transfer rate of magnetic hard disk drives were about 20 Mb/in<sup>2</sup> and 24 Mb/s, respectively, in 1986 [1]. By the beginning of 2001, these had become 50 Gb/in<sup>2</sup> and 700 Mb/s, respectively [2] [3]. Although this explosive growth has been mainly due to the technological improvements made in the design of heads and diskmedia, sophisticated coding and signal processing techniques, as well as accurate servo control algorithms, have also played a significant role [4] [5]. The potential of coding and signal processing techniques to significantly enhance the storage capacity has been proved repeatedly in the past. For a given head-medium combination, the use of better coding and signal processing techniques allows more bits to be packed into a given area in the medium, resulting in an increase in storage density from the improved reliability. A classic example of this is the increase in density that resulted from substituting partial response detection for peak detection in hard disk drives in the early 1990s [6] [4] [5]. As the developments in integrated circuits (IC) technology allow ever more complex functions to be implemented at affordable costs, signal processing techniques are going to play an increasingly important role in data storage systems.

<sup>&</sup>lt;sup>1</sup> The review in Chapters 1 and 2 is aimed at magnetic recording systems. This is because the developments in Chapters 3 to 6, which constitute the bulk of the thesis, assume magnetic recording systems. Chapter 7, which deals with optical systems, will also include the required review on optical recording.

A digital recording system very much resembles a synchronous digital baseband communication system. Whereas communication systems transport information from one location to another, recording systems do it from one time to another. The common goal of both systems is to eventually retrieve the transmitted or stored information as accurately as possible [7]. The information is in the form of binary data. In baseband systems, no carrier modulation is used for matching the channel and data characteristics. Instead, these systems typically use modulation codes to adapt the data to the channel characteristics [8]. The received signal is processed using equalization, detection and timing recovery techniques for recovering the original digital data. Because of the operational and system level similarities between digital storage systems and digital baseband communication systems, the techniques developed for transmission and reception in communications have been widely exploited in storage systems.

The principles of digital magnetic recording and digital optical recording form the basis of most of the data storage systems that are in use currently. Magnetic recording systems, in particular hard disk drives (HDD), prevail for high volume and high-speed storage applications. On the other hand, optical recording systems, such as compact disc (CD), digital versatile disc (DVD), and their advanced generations, prevail for removable storage applications. Because of the continuous demand from customers for storage systems capable of high densities and/or high data rates, the research efforts in the last decade on improving the storage technology have been very aggressive. As a result, for example, areal densities of 100 Gb/in<sup>2</sup> and data rates of more than 1 Gb/s will be realized very soon in magnetic recording [9] [10]. In fact, researchers are being forced to make revolutionary changes in technology to sustain the advancements in storage capabilities, since the existing technologies are fast approaching their physical limits [11].

A critical part of data storage systems is the read-write channel, which consists of the circuits and techniques needed for writing the user-supplied data into the storage medium and for reliable recovery of the written data. A properly designed read-write channel has the potential to enhance the recording density and data rate capabilities. The research work that has been undertaken in this thesis deals with timing recovery issues in read-write channels. To motivate the work, we first present a system-level overview of the read-write channel and the various key techniques developed for implementing each of its subsystems. For the sake of convenience, we present this review in the context of digital magnetic recording systems.

## 1.2 Overview of Read-Write Channel Techniques for Digital Magnetic Recording Systems

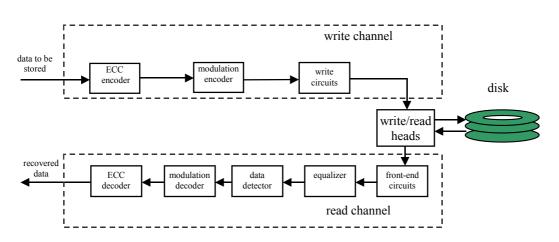

Fig.1-1 shows the block schematic of a magnetic recording system, highlighting the readwrite channel part of the whole system. As shown, the read-write channel involves a write channel and read channel. These are similar in functionality to the transmitter and receiver, respectively, in a communication system. The write channel accepts the input binary data and converts it into a form suitable for writing into the storage medium. The read channel recovers the original data by processing the output of the read head in accordance with certain algorithms. Throughout the thesis, the phrase 'recording channel' refers to the cascade of write circuits, write head, storage medium, and the read head.

Fig.1-1: Block schematic of a magnetic recording system. The blocks enclosed by the dashed boxes constitute the read-write channel of the recording system.

We now briefly describe the functions of each block shown in Fig.1-1. The ECC (error control coding) encoder uses special coding schemes to introduce error detection and correction capability into the input binary data. The ECC decoder uses this capability for detection and correction of errors during data recovery [12] [13]. The modulation encoder, on the other hand, is used for matching the data to the recording channel characteristics, and to help in the operation of the various control-loops (e.g. timing/gain recovery) in the read-channel [14] [15] [16]. The write circuits convert the binary output data of the modulation encoder to a write-current waveform. Each current pulse is properly shaped and positioned (through pulse shaping and write precompensation) to counteract the nonlinear distortions in the recording process. These distortions arise from the bandwidth limitations of the write path and the demagnetization fields in the medium [17] [8] [18]. The write-current waveform causes the write-head to produce magnetic flux which magnetizes the storage medium in one of the two directions, thereby recording the data.

The electrical signal generated by the read-head, in response to the magnetization pattern in the medium, is processed by the frond-end circuits which condition the replay signal (e.g., amplify, limit noise bandwidth, regulate dynamic range, etc) prior to equalization [19]. The equalizer shapes the signal according to certain pre-chosen criteria [20] [21] [22] [23] [8] so that the data detector is able to recover the binary data from the equalized signal with as few errors as possible [24] [6] [25] [26]. The modulation and ECC decoders operate on the output bits of the data detector to give the estimate of the original data that was input to the storage system. Not shown explicitly in Fig.1-1 are the control loops required for doing timing recovery [27] [28], gain control [19] [29], DC offset cancellation and adaptive equalization [30] [26].

In the rest of this section, we further elaborate on selected parts of the read-write channel, namely, modulation codes, equalization, and detection, since these will be used extensively in this thesis. The problem of timing recovery, which is the main subject of the thesis, is briefly introduced in Section 1.3. A detailed review on timing recovery will be given in Chapter 2.

#### 1.2.1 Modulation codes

As mentioned above, modulation codes are used for matching the characteristics of the data to those of the recording channel [8] [31]. Run-length-limited (RLL) codes are the most popularly used modulation codes in digital magnetic and optical recording systems [32].

In this thesis, the output sequence  $\{b_k\}$ ,  $b_k \in \{0,1\}$ , of the RLL (modulation) encoder is assumed to be in the NRZI (non-return to zero inverse) representation [33]. That is,  $b_k = 1$ implies a transition in the medium magnetization at the  $k^{\text{th}}$  bit instant, whereas  $b_k = 0$  implies no transition. To generate the write current from the transition sequence  $\{b_k\}$ , a precoder is used to convert the NRZI bits  $\{b_k\}$  into NRZ (non-return to zero) representation  $\{b'_k\}$ , where  $b'_k = 1$  and  $b'_k = 0$  imply the two directions of magnetization (i.e., write current polarities) instead of the presence and absence of transitions [33] [15]. This precoding is done as

$$b_k' = b_{k-1}' \oplus b_k \tag{1.1}$$

where '  $\oplus$  ' indicates modulo-2 addition. The write current polarity is given by

(

$$a_k = 2b'_k - 1 \tag{1.2}$$

so that  $a_k \in \{-1, 1\}$ .

RLL codes are also known as (d, k) codes. The parameters d and k specify the constraints on the minimum and maximum runs of consecutive zeros between two ones in the coded sequence  $b_k$ . The *d*-constraint, when d > 0, helps to increase the minimum spacing between transitions in the medium. This, in turn, helps to reduce the linear as well as nonlinear interactions (called intersymbol interference) among the data bits recorded in the medium [34]. The k-constraint limits the maximum transition spacing and ensures that the control loops (e.g. timing, gain and equalization) are updated frequently enough to maintain the loops in good condition. The k-constraint also helps to reduce the path memory requirement as well as to avoid certain catastrophic error events in Viterbi-algorithm-based data detectors [24] [25]. The benefits provided by the d and k constraints carry a price tag in the form of redundancy added to the coded data stream. This redundancy is characterized by a parameter called code-rate that is defined as R = p/q, 0 < R < 1, specifying that groups of p data bits at the encoder input are coded into groups of q bits at its output. Clearly, the code-rate decreases with increase in d or decrease in k. An important disadvantage of coding is that it decreases the signal-to-noise ratio (SNR) in the readback signal. The lower the code-rate is, the greater will be the reduction in SNR [35] [36]. Hence, it is important to design the data detector to minimize any further reduction of SNR.

In practical recording systems, the *d*-constraint is restricted to 0, 1 or 2, and the *k*-constraint ranges between 2 and 10. The most popular RLL codes are the rate 1/2 (1, 3) code used in floppy disk drives [15], rate 8/17 (2, 10) code used in CD [32], rate 8/16 (2, 10) code used in DVD [37], rate 1/2 (2, 7) and 2/3 (1, 7) codes used in earlier hard disk drives [15] [32], and several d=0 codes such as rate 8/9 (0,4/4) [25], 16/17 (0, 6/6) [38], and 8/9 (0,11) codes [39] used in hard disk drives. The rate 16/17 (0, 6/6) and 8/9 (0, 4/4) codes belong to the class of RLL codes whose constraints are specified as (d, G/I), where d and G have the same meaning as d and k discussed above. The *I*-parameter describes an additional constraint on the maximum run-length of zeros in the odd and even interleaved sequences [16]. More recently, high-rate codes combined with parity bits in conjunction with parity-based post-processing schemes have been widely used for improving error performance and densities [40] [41] [42]. These codes have the advantage of minimizing performance degradation due to rate loss and error propagation at the modulation decoder. For example, in the disk-drive industry, to enhance density and performance, the rates of d=0 modulation codes have steadily been increasing over the years, from initially, rate 8/9 and 16/17 codes to currently 19/20 [43], 32/33, 64/65 [42], and

96/100 [42]. These codes keep the *d*-constraint to zero and allow the *k*-constraint to vary between 4 and 8, thus providing the benefits of (d, k) codes while largely reducing the code redundancy.

#### 1.2.2 Equalization and detection techniques

A mathematical model for the readback signal at the read head output can be given as [44] [6]

$$r(t) = \sum_{k=-\infty}^{\infty} a_k h(t - kT) + n(t)$$

(1.3)