# Towards efficient development of complete CAD frameworks

#### Citation for published version (APA):

Rovers, W. M. H. M. (1998). *Towards efficient development of complete CAD frameworks*. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR514353

DOI: 10.6100/IR514353

#### Document status and date:

Published: 01/01/1998

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# Towards Efficient Development of Complete CAD Frameworks

# Towards Efficient Development of Complete CAD Frameworks

PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr. M. Rem, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op dinsdag 29 september 1998 om 16.00 uur

DOOR

### Wilhelmus Martinus Henricus Maria Rovers

geboren te Gemert

Dit proefschrift is goedgekeurd door de promotoren:

prof.dr.ir. C.J. Koomen en prof.ir. M.P.J. Stevens

Copromotor: dr.ir. J.W.G. Fleurkens

Cover: The DABchic IC. Courtesy of the DAB-team from Philips Research

© Copyright 1998 by W.M.H.M. Rovers

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission from the copyright owner.

Druk: Universiteitsdrukkerij Technische Universiteit Eindhoven

CIP-DATA LIBRARY TECHNISCHE UNIVERSITEIT EINDHOVEN

Rovers, Wilhelmus M.H.M.

Towards efficient development of complete CAD frameworks / by Wilhelmus M.H.M. Rovers. - Eindhoven : Technische Universiteit Eindhoven, 1998. Proefschrift. - ISBN 90-386-0470-X NUGI 832 Trefw.: grote geintegreerde schakelingen ; CAD / datamanagement / Petri-netwerken. Subject headings: integrated circuit design / circuit CAD / Petri nets.

# Summary

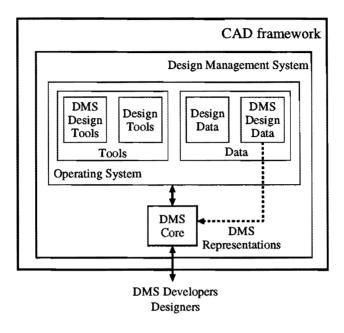

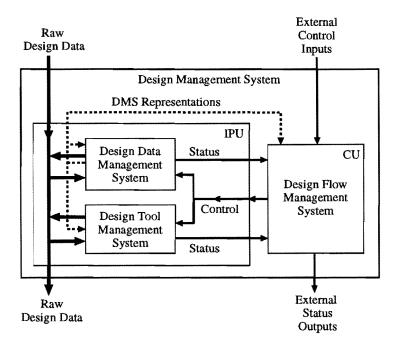

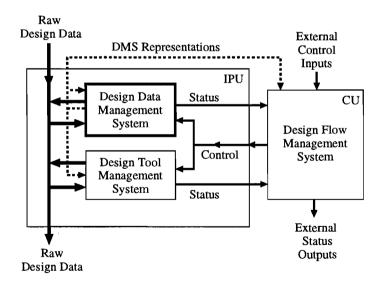

In this thesis we are concerned with the development of *complete Computer Aided Design frameworks*. CAD frameworks enable designers to create complex systems by managing their design processes. These processes are managed by the design management system component of a CAD framework. In order for a CAD framework to be considered complete it has to provide support for all three design management sub-activities, so for design data, design tool, and design flow management. The design management component of a CAD framework is a dynamic system which is updated regularly, for instance by the addition of new tools or design flows. The persons creating and updating the design management system are referred to as *design management system developers*. Besides supporting the designers, a complete CAD framework should also assist the design management system developers in performing their job. This thesis proposes a method to *efficiently* develop such complete CAD frameworks.

For a long time there has been a lot of confusion regarding what design management is. As a result, it was even less apparent what the structure of CAD frameworks providing this service had to be. Notwithstanding this, a number of systems were made. Most of these systems however, provided only a part of the CAD framework functionality, usually some form of design data management. Some of these systems were extended later on to provide support for the other design management activities as well. Since these systems were originally created with the first activity in mind, this often resulted in non-uniform systems which are difficult to use. In order to design a complete CAD framework it is essential to have a good picture of the complete system. Therefore, this thesis presents a detailed CAD framework model. This model can be used to reason about CAD frameworks and can also serve as a guideline for the implementation of such a system.

The existing CAD frameworks provide hardly any support to the design management system developers. In this thesis the CAD framework model is used to show how this aspect of framework completeness can be implemented. This model points out that their exists an analogy between IC designers and design management system developers, namely that all these people are designers. The only difference between these designers is what they design, namely ICs and design management systems, respectively. Like IC designers, DMS developers produce lots of data and use a variety of tools while creating their DMS descriptions. Therefore, the support provided by the framework to DMS developers should include management of their data, tools and flows. A CAD framework can realise this by making the support facilities it provides to the IC designers available to the DMS

#### developers.

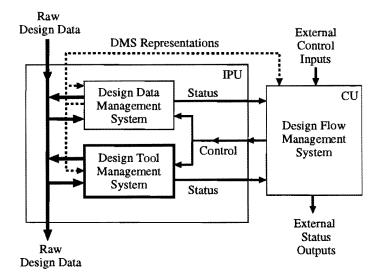

Besides assisting all participants, complete CAD frameworks feature a design management system which provides support for all design management sub-activities. Despite this, the design management systems of most of the existing CAD frameworks do either not support all three activities or lack a good integration of these. The main reason for this is that these systems were directly implemented based on an often incomplete and informal notion about what design management is, how the different design management activities have to be integrated and how to construct a system providing support for these. To avoid these problems, the CAD framework model presented in this thesis features a mathematical description of its design management system. The model is based on an analogy between design management systems and digital systems. This abstract design management system model describes both the behaviour of the system's three main components, i.e., the design data, the design tool and the design flow management systems and their interaction. This model can be used as a guideline for the construction of complete design management systems featuring a seamless integration of design data, design tool and design flow management. The feasibility of this model is demonstrated by using it to represent a design management system for the LOCAM logic synthesis system developed by Philips.

The time required for the development of a CAD framework is almost entirely consumed by the construction and maintenance of its central component, i.e., the design management system. Therefore, the efficiency of CAD framework development can be greatly improved by providing better assistance to the design management system developers. Currently these developers implement their design management systems using a general purpose programming language. Since such a language does not feature special constructs for CAD framework construction, the creation of a design management system will be very time consuming task. Moreover, the resulting system will be difficult to maintain and extend with new functionality. Therefore, the CAD framework development time can be greatly reduced if it is programmed using a dedicated design management system description language. Using such a language, the system under development can be represented at a higher level of abstraction. As far as we know, there are currently no suitable design management system description languages available. In this thesis it is demonstrated how such a language can be defined. Using the presented CAD framework model as a guideline, first the requirements for a design management system description language are formulated. Subsequently interactive hierarchical coloured Petri nets are introduced. Furthermore it is demonstrated that languages based on this extension of the hierarchical coloured Petri net concept satisfy the presented requirements. The suitability of such a language is demonstrated by showing how it can be used to create executable design management system representations.

# Samenvatting

In dit proefschrift behandelen we de ontwikkeling van *complete Computer Ondersteund Ontwerp (COO) framewerken*. COO-framewerken beheren de ontwerpprocessen van ontwerpers en stellen hen daardoor in staat om complexe systemen te maken. Deze service wordt verleend door de OntwerpBeheerSysteem (OBS) component van een COOframewerk. Het OBS van een compleet COO-framewerk verleent drie soorten services, namelijk ontwerpdata-, ontwerpprogramma- en ontwerpmethodologiebeheer. Een OBS is een dynamisch systeem dat regelmatig gewijzigd wordt, bijvoorbeeld door de toevoeging van nieuwe ontwerpprogramma's of methodologieën. De personen die ontwerpbeheersystemen maken en/of wijzigen worden *ontwerpbeheersysteemontwikkelaars* genoemd. Naast het assisteren van ontwerpers moet een compleet COO-framewerk ook de werkzaamheden van deze OBS-ontwikkelaars ondersteunen. In dit proefschrift zal een methode geïntroduceerd worden welke gebruikt kan worden om op een efficiënte manier complete COO-framewerken te ontwikkelen.

Er is gedurende een lange periode veel verwarring geweest over wat ontwerpbeheer nu eigenlijk inhoudt. Het gevolg was dat er nog minder duidelijkheid bestond over de structuur van de bijbehorende COO-framewerken. Ondanks dit zijn er toch een aantal van deze systemen gemaakt. De meeste van deze framewerken verleenden echter maar een gedeelte van de gewenste COO-framewerk functionaliteit, veelal een bepaalde vorm van ontwerpdatabeheer. Sommige van deze systemen zijn later uitgebreid met ontwerpprogrammaen/of ontwerpmethodologiebeheer. Doordat deze systemen echter oorspronkelijk ontworpen waren voor ontwerpdatabeheer, zijn de meeste niet-uniform en moeilijk te gebruiken. Om een compleet COO-framewerk te kunnen ontwerpen is het absoluut noodzakelijk om een goed beeld te hebben van het complete systeem. Dit is de reden waarom we in dit proefschrift een gedetailleerd COO-framewerkmodel presenteren. Dit model kan niet alleen gebruikt worden om over COO-framewerken te redeneren, maar geeft ook richtlijnen voor de realisatie van zo'n systeem.

De bestaande COO-framewerken verlenen erg weinig ondersteuning aan de ontwerpbeheersysteemontwikkelaars. In dit proefschrift gebruiken we het COO-framewerkmodel om te laten zien hoe dit aspect van framewerkcompleetheid gerealiseerd kan worden. Het model laat zien dat er een analogie bestaat tussen IC-ontwerpers en OBS-ontwikkelaars, namelijk dat beiden te beschouwen zijn als ontwerpers. Het enige verschil tussen beide typen ontwerpers is wat zij ontwerpen, namelijk respectievelijk IC's en ontwerpbeheersystemen. Net zoals IC-ontwerpers, produceren OBS-ontwikkelaars grote hoeveelheden data en gebruiken ze allerlei programma's om hun OBS-beschrijvingen te creëren. De ondersteuning welke door het framewerk verleend wordt aan de OBS-ontwikkelaars zou daarom ook het beheer van hun data, programma's en methodologieën moeten inhouden. Dit kan gerealiseerd worden door de ondersteuningsfaciliteiten welk een framewerk aanbiedt aan de IC-ontwerpers ook beschikbaar te maken voor de OBS-ontwikkelaars.

De meeste bestaande COO-framewerken zijn incompleet in de zin dat ze niet alle drie de ontwerpbeheerservices verlenen. Bovendien zijn deze services vaak niet goed geïntegreerd. De belangrijkste oorzaak hiervan is dat deze systemen geïmplementeerd zijn gebaseerd op een vaak incompleet en informeel idee over wat ontwerpbeheer is en hoe het bijbehorende ontwerpbeheersysteem gemaakt zou moeten worden. Om deze problemen te vermijden maakt het in dit proefschrift gepresenteerde COO-framewerkmodel gebruik van een wiskundige beschrijving van het bijbehorende ontwerpbeheersysteem. Deze beschrijving is gebaseerd op een analogie tussen ontwerpbeheersystemen en digitale systemen. Dit leidt tot een abstract ontwerpbeheersysteemmodel welk een beschrijving geeft van zowel het gedrag van de drie OBS componenten, dus van het ontwerpdata-, het ontwerpprogramma-, en het ontwerpmethodologiebeheersysteem, als van hun interactie. Dit model kan dienen als een richtlijn voor de constructie van complete ontwerpbeheersystemen welke de drie ontwerpbeheerservices op een naadloze manier integreren. De bruikbaarheid van dit model wordt gedemonstreerd door het te gebruiken tijdens de beschrijving van een ontwerpbeheersysteem voor het LOCAM logische-synthese systeem ontwikkeld door Philips.

De ontwikkeltijd van een COO-framewerk wordt bijna geheel gebruikt voor de constructie en het onderhoud van het bijbehorende ontwerpbeheersysteem. De efficiëntie van COOframewerkontwikkeling kan daarom sterk verbeterd worden door de OBS-ontwikkelaars beter te ondersteunen. De huidige ontwerpbeheersystemen zijn geprogrammeerd in een universele programmeertaal. Aangezien dergelijke talen geen speciale constructies voor OBS-ontwikkeling bevatten, zal het programmeren van een ontwerpbeheersysteem in een dergelijke taal een tijdrovend karwei zijn. Een ander nadeel is dat het resulterende systeem zowel moeilijk te onderhouden als uit te breiden zal zijn. De ontwikkeltijd van een COOframewerk kan daarom sterk gereduceerd worden door het bijbehorende OBS te programmeren in een speciaal ontworpen ontwerpbeheersysteembeschrijvingstaal. In een dergelijke taal kan het te ontwikkelen systeem beschreven worden op een hoger niveau van abstractie. Zover we weten zijn er op het moment echter geen geschikte ontwerpbeheersysteembeschrijvingstalen beschikbaar. In dit proefschrift laten we daarom zien hoe een dergelijke taal gedefinieerd kan worden. Gebruik makend van de richtlijnen verkregen uit het COOframewerkmodel, definiëren we eerst de eisen waaraan de OBS-beschrijvingstaal moet voldoen. Vervolgens worden interactieve hiërarchische gekleurde Petri-netten geïntroduceerd. Daarna laten we zien dat talen gebaseerd op deze uitbreiding van het hiërarchische gekleurde Petri-net concept voldoen aan de gestelde eisen. De bruikbaarheid van een dergelijke taal wordt gedemonstreerd door te laten zien hoe deze gebruikt kan worden om executeerbare ontwerpbeheersysteembeschrijvingen te creëren.

# Acknowledgements

I would like to thank prof. dr. ir. C.J. Koomen and prof. ir. M.P.J. Stevens for their support and for given me the opportunity to perform my Ph.D. research. Doing this research enabled me to switch from theoretical physics to electrical engineering and computer science.

I would also like to thank Emile Aarts, Hans Fleurkens, Willem Reijntjes, and Jeroen Voeten for their invaluable comments which helped me to improve the quality of this thesis.

Furthermore I would like to thank Rudi Bloks, Frank Budzelaar, Ton van Doorn, Yun Chao Hu, Robert Huis in 't Veld, Sherif El Kassas, Ardo van Rangelrooij, and Ad Verschueren for their contributions ranging from drinking coffee together to discussions about my research. I'm also grateful to my other colleagues from the ICS group at the Eindhoven University of Technology for making my stay there a very agreeable one. In addition I would like to thank Rian van Gaalen for her excellent assistance.

I'm also grateful to my colleagues at Philips Research in Eindhoven, especially Marc Verra, because he motivated me to finish my thesis by constantly reminding me that it was not finished yet.

Finally, I want to express my gratitude to my parents and my wife. Without their support writing this thesis would not have been possible.

viii

# Abbreviations

| ALU   | Arithmetic Logic Unit                |

|-------|--------------------------------------|

| BD    | Bus Definition set                   |

| CAD   | Computer Aided Design                |

| CB    | Copying Bus                          |

| CD    | Compact Disk                         |

| CI    | Control Interpreter                  |

| CPN   | Coloured Petri Net                   |

| CS    | Current State                        |

| СТКО  | CAD Tool Knowledge Object            |

| CU    | Control Unit                         |

| DDMS  | Design Data Management System        |

| DDS   | Design Data Store                    |

| DDSIS | DDS Input Sequence                   |

| DDSOS | DDS Output Sequence                  |

| DF    | Delete Function                      |

| DFMS  | Design Flow Management System        |

| DFS   | Design Flow Store                    |

| DMS   | Design Management System             |

| DTMS  | Design Tool Management System        |

| DTMSO | DTMS Output                          |

| DTS   | Design Tool Store                    |

| DTSIS | DTS Input Sequence                   |

| DTSO  | DTS Output                           |

| DTSOS | DTS Output Sequence                  |

| EDIF  | Electronic Design Interchange Format |

| ELLA  | Electronic Logic Language            |

| FEE   | Flow Execution Engine                |

| FId   | Flow Identifier                      |

| FIFO  | First In First Out                   |

| HDL   | High-level Design Language           |

|       |                                      |

|     | IC              | Integrated Circuit                             |  |  |

|-----|-----------------|------------------------------------------------|--|--|

| IGF |                 | Input Generation Function                      |  |  |

| IPU |                 | Information Processing Unit                    |  |  |

|     | NDL             | Network Description Language                   |  |  |

|     | NSF             | Next State Function                            |  |  |

|     | OF              | Output Function                                |  |  |

|     | OGF             | Output Generation Function                     |  |  |

|     | OMA             | Optimizer and MAtcher tool                     |  |  |

|     | OPB             | One Place Buffer                               |  |  |

|     | OTC             | Overspecified Timing Constraints               |  |  |

|     | OTDM            | OMA Timing Driven Matching                     |  |  |

|     | OTO-D           | Object Type Oriented Data                      |  |  |

|     | PHACO           | Philips HArdware COmpiler                      |  |  |

|     | PLANETS         | Philips Logic And NETwork Specification format |  |  |

|     | PTN             | Place/Transition Net                           |  |  |

|     | $\mathbf{RC}$   | Random Colour                                  |  |  |

|     | $\mathbf{RF}$   | Read Function                                  |  |  |

|     | RS              | Random Selection                               |  |  |

|     | RTC             | Realistic Timing Constraints                   |  |  |

|     | RTL             | Register Transfer Level                        |  |  |

|     | TE              | Transition Expression                          |  |  |

|     | TEE             | Tool Execution Engine                          |  |  |

|     | TEEI            | TEE Input                                      |  |  |

|     | TEEO            | TEE Output                                     |  |  |

|     | TES             | Tool Encapsulation Specification               |  |  |

|     | $\mathbf{TIGF}$ | TEE Input Generation Function                  |  |  |

|     | VHDL            | VHSIC Hardware Description Language            |  |  |

|     | WF              | Write Function                                 |  |  |

|     | WS              | WorkSpace                                      |  |  |

|     |                 |                                                |  |  |

# Contents

| Su | mma        | ary i                              | ii |

|----|------------|------------------------------------|----|

| Sa | men        | vatting                            | v  |

| A  | cknov      | wledgements v                      | ii |

| A  | brev       | viations i                         | x  |

| 1  | Intr       | oduction                           | 1  |

|    | 1.1        | The design of complex systems      | 2  |

|    |            | 1.1.1 Abstraction                  | 2  |

|    |            | 1.1.2 Decomposition                | 4  |

|    |            | 1.1.3 Design reuse                 | 5  |

|    |            | 1.1.4 Teamwork                     | 6  |

|    |            | 1.1.5 Automation                   | 6  |

|    | 1.2        | Design management                  | 7  |

|    | 1.3        | Problem definition                 | 8  |

|    | 1.4        | Towards a solution                 | 8  |

|    | 1.5        | Thesis organisation                | 9  |

| 2  | CAI        | D frameworks: State of the art 1   | 1  |

|    | 2.1        | CAD framework definition           | 1  |

|    | 2.2        | CAD framework participants 1       | 2  |

|    | 2.3        | The design management activities 1 | 3  |

|    |            | 2.3.1 Design data management       | 3  |

|    |            | 2.3.2 Design tool management       | 8  |

|    |            | 2.3.3 Design flow management       | 0  |

|    | <b>2.4</b> | Existing CAD frameworks            | 1  |

|    |            | 2.4.1 Nelsis                       | 1  |

|    |            | 2.4.2 Cadweld                      | 4  |

|    | 2.5        | The architecture of CAD frameworks | 6  |

|    | 2.6        |                                    | 9  |

.

| 3 | A C        | AD framework model                             | 31       |

|---|------------|------------------------------------------------|----------|

|   | 3.1        | The LOCAM logic synthesis system               | 32       |

|   | 3.2        | The designer - DMS developer analogy           | 33       |

|   | 3.3        | The digital system analogy                     | 35       |

|   |            | 3.3.1 Digital systems                          | 36       |

|   |            | 3.3.2 A design management system model         | 40       |

|   |            | 3.3.3 Busses                                   | 43       |

|   | 3.4        | Summary                                        | 46       |

| 4 | The        | design data management system                  | 49       |

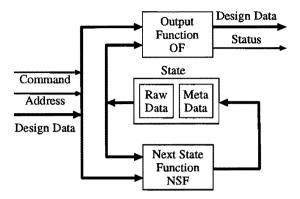

|   | 4.1        | The design data store                          | 51       |

|   |            | 4.1.1 Raw data                                 | 53       |

|   |            | 4.1.2 Raw data identifiers                     | 55       |

|   |            | 4.1.3 Attributes                               | 57       |

|   |            | 4.1.4 Relations                                | 58       |

|   |            | 4.1.4.1 Relation representation                | 58       |

|   |            | 4.1.4.2 Relation types                         | 59       |

|   |            | 4.1.4.3 Relation definitions                   | 60       |

|   |            | 4.1.4.4 Relations and data characterisation    | 61       |

|   |            | 4.1.4.5 Relations and the DDS organisation     | 64       |

|   |            | 4.1.5 The design data store state              | 68       |

|   |            | 4.1.6 Commands                                 | 70       |

|   |            | 4.1.7 Addresses                                | 71       |

|   |            | 4.1.8 Status information                       | 76       |

|   |            | 4.1.9 The behaviour of the design data store   | 76       |

|   |            | 4.1.10 Concurrency control                     | 79       |

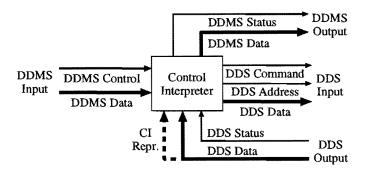

|   | 4.2        | The control interpreter                        | 80       |

|   | ±          | 4.2.1 Control inputs                           | 81       |

|   |            | 4.2.2 The behaviour of the control interpreter | 86       |

|   |            | 4.2.3 Concurrency control                      | 86       |

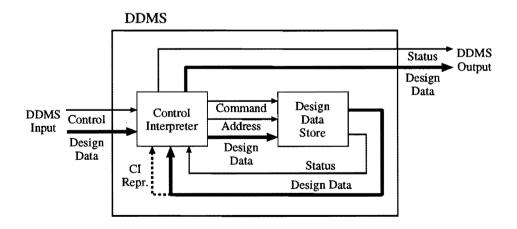

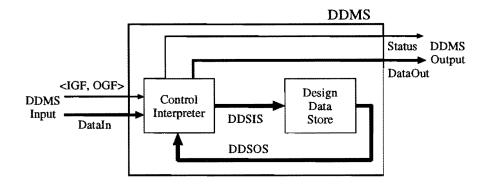

|   | 4.3        | The behaviour of the DDMS                      | 87       |

|   | 4.4        | Summary                                        | 87       |

| 5 | The        | design tool management system                  | 89       |

| Ŭ | 5.1        | The design tool store                          | 91       |

|   | 0.1        | 5.1.1 Tool abstractions                        | 92       |

|   |            | 5.1.2 Tool characterisation                    | 92<br>93 |

|   |            | 5.1.2         Tool selection                   | 93<br>95 |

|   | 5.2        | The tool execution engine                      | 95<br>96 |

|   | 5.2<br>5.3 | s                                              | 90<br>97 |

|   |            | The control interpreter                        |          |

|   | 5.4        | Summary                                        | 98       |

#### CONTENTS

| 6  |                      |         | flow management system                                      | 101 |

|----|----------------------|---------|-------------------------------------------------------------|-----|

|    | 6.1                  | ~       | flows                                                       | 102 |

|    | 6.2                  |         | sign flow execution engine                                  | 109 |

|    | 6.3                  | Summa   | ary                                                         | 110 |

| 7  | A de                 | esign n | nanagement system description language                      | 111 |

|    | 7.1                  | Langua  | age requirements                                            | 112 |

|    | 7.2                  | Interac | tive hierarchical coloured Petri nets                       | 114 |

|    |                      | 7.2.1   | Place/transition nets                                       | 114 |

|    |                      | 7.2.2   | Net inscriptions                                            | 116 |

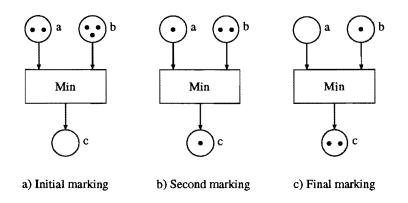

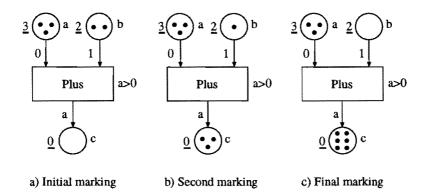

|    |                      | 7.2.3   | Coloured Petri nets                                         | 120 |

|    |                      |         | 7.2.3.1 Execution of coloured Petri nets                    | 123 |

|    |                      |         | 7.2.3.2 Coloured Petri net behaviour                        | 126 |

|    |                      | 7.2.4   | Hierarchical Petri nets                                     | 130 |

|    |                      | 7.2.5   | Interactive Petri nets                                      | 132 |

|    |                      |         | 7.2.5.1 Interactive CPNs and the simple execution mechanism | 133 |

|    |                      |         | 7.2.5.2 The interactive Petri net execution method          | 137 |

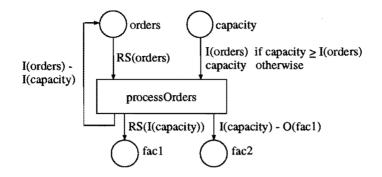

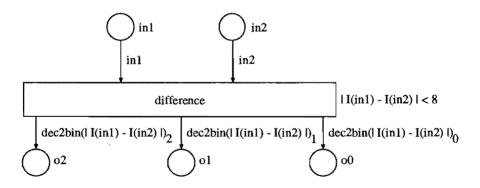

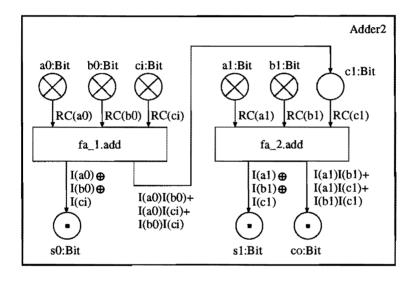

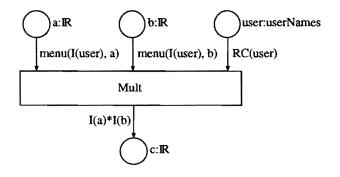

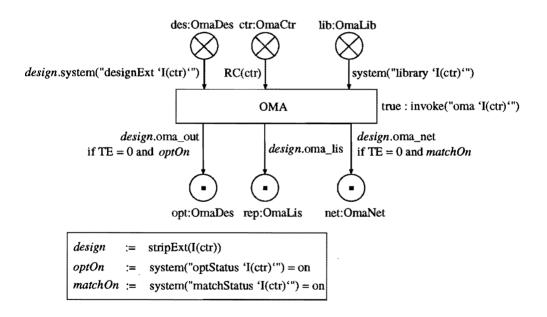

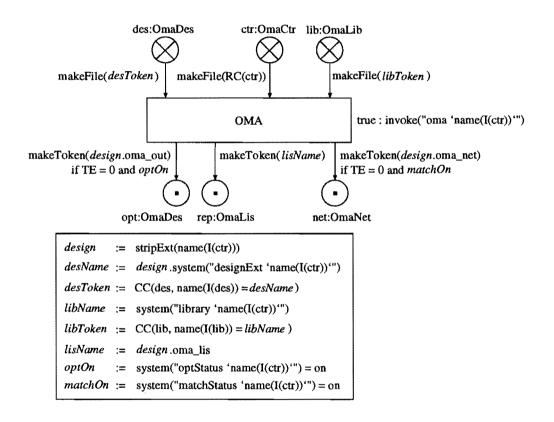

|    | 7.3                  | Design  | management system representation                            | 140 |

|    |                      | 7.3.1   | Raw data representation                                     | 141 |

|    |                      | 7.3.2   | Tool representation                                         | 143 |

|    |                      | 7.3.3   | Representation of busses                                    | 145 |

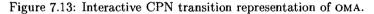

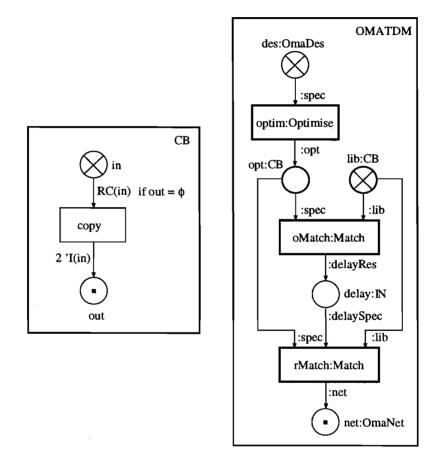

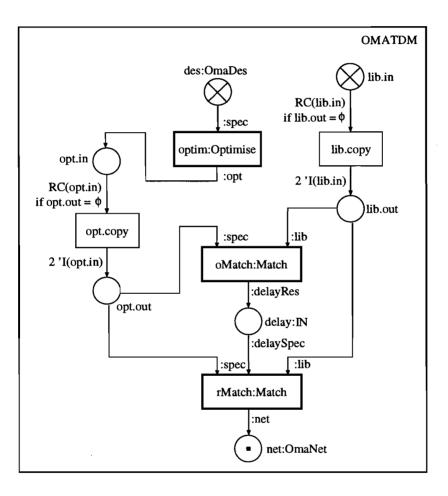

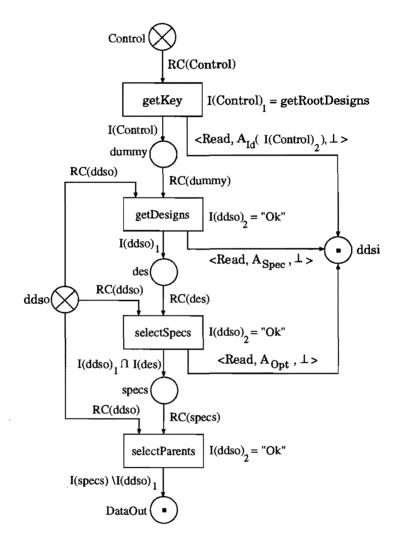

|    |                      | 7.3.4   | Representation of flows                                     | 148 |

|    |                      | 7.3.5   | Representation of control inputs                            | 148 |

|    | 7.4                  | Summa   | ary                                                         | 151 |

| 8  | Con                  | clusior | as and future research                                      | 153 |

| A  | Raw                  | data    | distinguishability                                          | 155 |

| в  | The                  | relatio | on operators                                                | 163 |

| Bi | bliog                | raphy   |                                                             | 166 |

| Cı | Curriculum Vitae 173 |         |                                                             |     |

. \_\_\_\_\_

# Chapter 1 Introduction

In this thesis we are concerned with the development of Computer Aided Design (CAD) frameworks. In literature [tBBvW91], [RW95], [HNSB90], [KGMB94], [vW93], [vW94], [ZG96], there is still a lot of confusion about the nature of CAD frameworks. Despite this, the following facts are agreed upon. A CAD framework should assist designers in managing their design processes. We refer to the CAD framework component which is responsible for this as the *Design Management System* (DMS). This design management system is not a static system, but is updated regularly, for instance by the addition of new tools or design flows. The persons updating the design management system are referred to as *design management system developers*. Besides supporting the designers, a CAD framework should also assist the design management system developers in performing their job.

CAD frameworks enable designers to design complex systems. The creation of complex designs is a complicated and time-consuming task. Designers are still able to do this by making use of the following complexity handling methods: Abstraction and decomposition. The time required for creating complex designs can be kept within realistic boundaries by making use of the following design-time reduction methods: Design reuse, teamwork, and automation. In Section 1.1 these complexity handling and time reduction methods are illustrated.

The use of the previously mentioned complexity management methods comes at a price; designers only benefit from these methods if they are applied correctly. The activity of supporting the designer in making proper use of these methods is referred to as *design management*. Design management is the topic discussed in Section 1.2.

The development of CAD frameworks is an active area of research. Currently, there are no commercially available CAD frameworks that can handle all the aspects of design management. In Section 1.3 the problems associated with currently available CAD frameworks are discussed. Section 1.4 gives an overview of the approach presented in this thesis to solve these problems and of the main results. Finally Section 1.5 gives an outline of the organisation of the remainder of this thesis.

## 1.1 The design of complex systems

Before we can start to discuss about how CAD frameworks should assist designers in managing their design processes, we first have to know what a design process is. For general models of the IC design process we refer to [All90], [Koo91], and [Sie91]. In [Yos81] and [TY86] the design process is considered from a mechanical engineering viewpoint. [Das89] presents the structure of design processes in general. However, for our discussions about design management, the detailed models presented in these articles are not required; it is sufficient to know how the previously presented complexity management methods enable designers to create complex designs. In this section these methods are introduced. Although these methods can be used for the design of complex systems in general, they will be illustrated using examples taken from the area of Integrated Circuit (IC) design.

### 1.1.1 Abstraction

ICs are characterised by their behaviour and by properties such as speed, power dissipation and size. Before the manufacturing process of an IC can start, a description of its layout must be created. Due to the complexity of state of the art ICs, it is nearly impossible to design them starting at the layout level. The layout description simply contains too much detail, whilst not explicitly representing the IC behaviour. Therefore, other, more abstract, representations of the IC are used. These descriptions provide a more explicit representation of some aspects of either the IC's behaviour and/or structure.

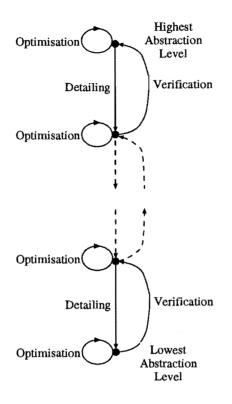

Figure 1.1 depicts how a multiple abstraction level design process is performed. A design process starts by formulating the requirements, which are a number of statements about the properties the system is required to have. After the requirements have been formulated, a first representation of the system is created, which describes the system at the highest level of abstraction. The properties of the system that are explicitly represented at this level of abstraction are optimised at that level. When, after a number of optimisation steps, these properties satisfy the requirements, the optimised description is transformed using a detailing step to a more detailed description at the next level of abstraction. This description forms the starting point for the optimisation of the properties specific for this lower abstraction level. This process repeats itself until a description at the lowest level of abstraction is obtained. The multiple abstraction level design process will only produce correct designs if the design representations at the different levels of abstraction are consistent. Detailing and the subsequent optimisations should not invalidate the optimisations made at the higher abstraction levels. Therefore, the optimisations are usually followed by a verification step during which it is verified that an optimised design representation is consistent with the more abstract representation it was derived from.

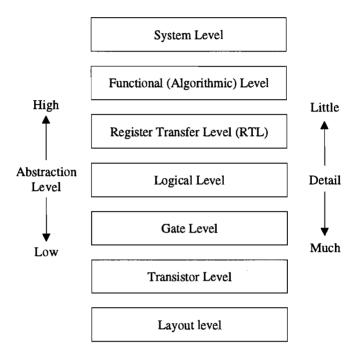

Figure 1.2 shows the abstraction levels that are most frequently used during the design of digital ICs ([MPC90]). The first two levels are not specific for IC design, but can be used to represent information processing systems in general. The system level is the top level of abstraction. At this level the general structure of the system is described. Typically the

Figure 1.1: A multiple abstraction level design process.

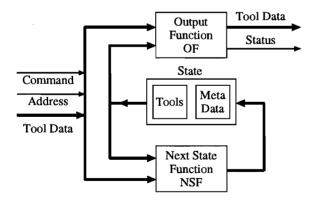

system is described as a composition of a number of related sub-systems, which are either implemented in hardware or in software. At the functional level, an algorithmic description of the behaviour of these sub-systems is given. For the sub-systems implemented in an IC, the next abstraction level will be the Register Transfer Level. At this level the system is described in terms of a number of *registers*, an *output function* and a *next state function*. The registers determine the state of the system. Given the system's current state and input, the output and next state functions determine what the system's output and next state are, respectively. At the logical level, these functions are described in terms of a number of logical expressions. During the detailing step, which transforms a logical level to a gate level description, these expressions are mapped to a collection of interconnected gates, such as AND, OR, NOT, NAND and NOR gates. At the transistor level the interconnected registers and gates are described in terms of a transistor netlist. During the last detailing step, this transistor netlist is transformed into a layout, which implements it in silicon. The layout describes the IC in terms of a number of layers, each representing the areas where a certain type of material should be deposited or removed. The layout description is used to produce the masks employed during the IC fabrication process.

Figure 1.2: Abstraction levels used during IC design.

#### 1.1.2 Decomposition

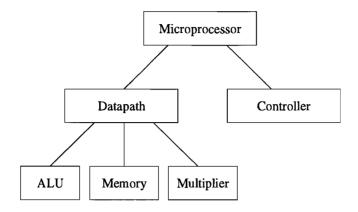

Another way to handle complex designs is by making use of decomposition [Nie86]. Decomposition reduces the complexity of the design process by splitting up the original design into a number of components, which can then be designed separately. Often these design components are still very complex. Therefore, some of these will again be decomposed. This process of decomposition continues until each component is small enough to be handled conveniently as a single unit. The result of the decomposition process is a hierarchy of design components. In Figure 1.3 the decomposition hierarchy of a microprocessor is shown. The design of this microprocessor has been split into two parts, namely a datapath and a controller. The datapath has again been decomposed into an arithmetic logic unit (ALU), a memory and a multiplier.

Figure 1.3: A design hierarchy.

#### 1.1.3 Design reuse

An obvious method for reducing the time required to create a design is by reusing other designs. The following three modes of reuse can be distinguished [AOS94]: Reuse by adaptation, reuse by instantiation, and reuse by generation. In the case of reuse by adaptation an existing design is adapted such that it satisfies a given requirements specification. For example, if a 15-bit multiplier is required, it can very quickly be obtained by stripping the most significant output from a 16-bit multiplier. RTL synthesis [BRSVW87] [BHMSV84] is a good example of a design process that makes use of reuse by instantiation. During RTL synthesis the objects to be reused are pre-designed logic gates and registers stored in a library. Starting from a RTL level design description, the synthesis system will create a functionally equivalent netlist of interconnected library element instantiations. This netlist is converted to a layout by using a placement and a routing program. The placement program determines where the pre-designed pieces of layout representing the instantiated library elements will be put on the layout. The routing program completes the layout by generating the required interconnections. The concept of reuse by generation can be illustrated using architecture synthesis [MPC90] [Sto91] as an example. For architecture synthesis the designs to be reused are not simple blocks like gates and registers, but parameterised blocks such as memories or arithmetic logic units. The designer selects which blocks he or she requires in his or her design and determines the desired parameters for these blocks. In contrast to RTL synthesis, the layout of the employed blocks is not taken from a library, but generated using a module generator. In this case, the module generator implicitly represents a complete class of reusable blocks, namely one block for each possible parameter setting.

#### 1.1.4 Teamwork

Teamwork will only result in a reduction of the required design time if the design process can be split up into a number of relatively independent sub-processes, each of which can be performed by one of the team members. When teamwork is combined with the previously introduced complexity and design time reduction methods, this results in a natural division of the total design task.

The use of multiple abstraction levels splits the total design process into a number of subprocesses, namely one for each employed abstraction level. For example, the transistor netlist and the layout implementing this netlist are sometimes created by different people. This means that designers do not have to know all the details of the complete design process, but can become experts on some of the design subtasks.

Decomposition splits a design into a number of smaller design components, which can be developed separately. Except for the interfaces to their own component, designers do not participate in the development of the other design parts.

Design reuse also results in a natural division of the total design task. The first task is the creation of the basic building blocks to be reused, e.g. the libraries and module generators used in RTL and architectural synthesis, respectively. The second task is the maintenance of these basic building blocks. The last task is designing by making use of these building blocks. All these tasks can be performed by different people.

### 1.1.5 Automation

For certain steps of the design process an algorithm can be found describing how it is performed. These design steps are candidates for being automated. Design process automation means that the design step is performed by a piece of software rather than by the designer. The programs automating such a design step are commonly referred to as *synthesis tools*. Design automation not only reduces the design time, but also enables the designer to carry out a design step without the need to have much knowledge about how it is done. The drawback of design automation is that (partly) automatically generated designs are, in general, less efficient than custom made designs. For many applications however, the performance of the generated designs suffices.

Automation is very common for software design, where programs are written using a high level programming language. For execution of the program, however, a machine language representation is required. These low-level representations are automatically generated from the high level program using a tool referred to as a compiler.

Examples of highly automated design processes in the IC design domain are RTL and architectural synthesis. In the case of RTL synthesis the designer will first create a register transfer level representation of his design. After the behaviour described by this design representation is validated using simulation, the rest of the design process is completely automated. In the first step of this process the RTL description is converted into a more

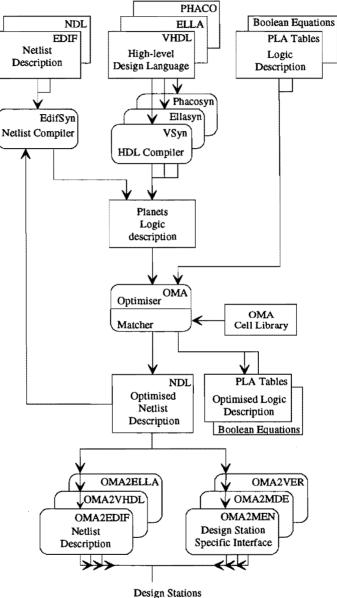

#### 1.2 Design management

detailed logical level design representation. Subsequently the number of expressions in this design representation is reduced using a tool referred to as a logic optimise. The resulting description is mapped by a matcher tool onto a network of interconnected gate level elements, i.e. gates and registers. The corresponding layout is created by a placement and routing tool. In the placement step, the pre-designed pieces of layout of the employed gate level elements are put at a certain location in the layout. In the routing step the layout is completed by adding new pieces of layout, which implement the connections of the gate level network.

### 1.2 Design management

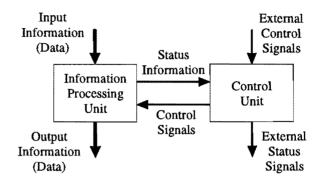

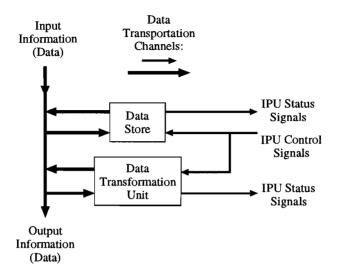

Design management is a combination of three sub-activities, namely design data, design tool, and design flow management [SD96]. These three activities are the topic of the remainder of this section.

Design data management is the activity of keeping track of all the design data and their relations and the use of these relations for controlling the access to data by multiple designers. The need for design data management is directly related to the use of the complexity handling and time reduction methods introduced above. These methods not only enable designers to create complex designs within a reasonable amount of time, but also give rise to substantial overhead. Instead of one description of the IC, there is a collection of design components, each represented at multiple levels of abstraction. The situation is worsened by the fact that during the design process many different versions of these design parts are created. Unless the designer is able to keep track of the relations between all these pieces of data, abstraction and decomposition will be useless. Libraries are only useful if the designers are able to find the desired library elements. When a team of designers is working on a design the situation becomes even more complex. In this case a data access control mechanism is required, preventing designers from making mistakes such as overwriting other designers' data or using the wrong version of another person's design part in a simulation.

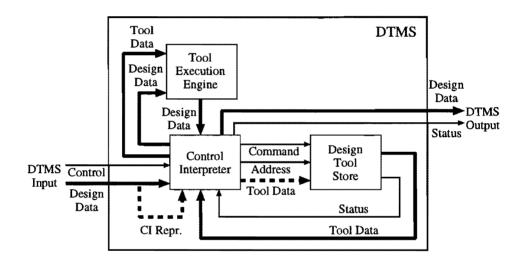

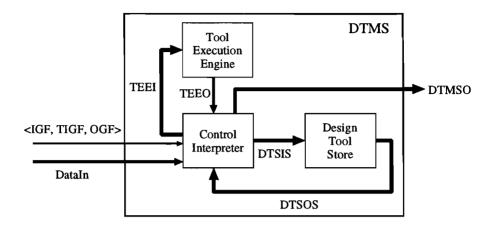

Design tool management is the activity of assisting the designer in making proper use of the available tools. Although design automation tools potentially reduce the design time, a real reduction is only achieved if the designers know how to use these tools. For instance, the designers have to know what a certain tool can be used for, how the tool is invoked and how to fine-tune the tool for their specific application. A design tool management system will typically abstract from tool invocation related information and will provide its users with tool characterisation information to be used for tool selection.

If the designer's data and tools are managed, the only task remaining for the designer is to decide how the required design can be obtained using these tools and data. This involves selection of the tools to invoke, determination of the order of these invocations and selection of the data to which these tools are applied. Although the terms design methodology management [HNSB90] [KGMB94] and design process management [JD92] [SD96] are frequently encountered in literature, we refer to the activity of assisting the designer in making these decisions as *design flow management* [tB95] [vW93] [vW94].

### **1.3** Problem definition

Development of a CAD framework is not a trivial task; it usually takes a lot of painstaking work to create such a system. This is especially true when, like in the case of most of the currently available CAD frameworks, such a system has to be build from scratch using a general purpose programming language, which does not feature special constructs for CAD framework construction. In addition to the fact that their construction requires a lot of effort, the resulting systems will often be difficult to maintain and/or to extend with new functionality. Therefore it would be very useful to have a method enabling us to develop CAD frameworks more efficiently.

Another problem associated with the currently available CAD frameworks is that most of these are not complete; they either do not provide support for all three design management sub-activities and/or they provide little or no assistance to the design management system developers. Typically, CAD frameworks originated as a design data management system [vW93] [vW94]. Despite the difficulties encountered, some of these systems were then extended to provide support for the design tool and design flow management activities as well. However, due to the fact that these systems were originally designed with design data management in mind, it was not always possible to achieve a good integration of the different design management system components. So even though some CAD frameworks in principle support all three activities, these systems will often be non-uniform and difficult to use. The main reason why CAD frameworks are created is to improve the efficiency of designers. Realisation of a framework doing this is already a very difficult task. Therefore, less urgent features such as design management system developer support received little or no attention during the development of the currently available CAD frameworks. As a consequence most of these systems are very designer oriented and provide only poor assistance to the design management system developers.

### 1.4 Towards a solution

In thesis we propose a method to solve the problems described above, i.e., a method enabling us to *efficiently* develop *complete* CAD frameworks.

One of the characteristics of a complete CAD framework is that it provides support and uniform interfaces to all participants, so to both the designers and design management system developers. In this thesis we will show how this aspect of framework completeness can be implemented. Our approach is based on an analogy between IC designers and design management system developers, which stresses that all these people are designers, who only differ in what they design, namely ICs and design management systems, respectively. Like IC designers, DMS developers produce lots of data and use a variety of tools while creating their DMS descriptions. Therefore, the support provided by the framework to DMS developers should include management of their data, tools and flows. A CAD framework can realise this by making the support facilities it provides to the IC designers available to the DMS developers. These facilities are provided by the design management system component of the CAD framework, so design management system developers will be assisted by the same system they are helping to develop.

When the CAD framework's design management system provides support to all participants, it becomes the central component of the CAD framework. In the past there has been only little consensus about what the structure of such a system should be. Therefore, the design management systems of most of the existing CAD frameworks were directly implemented based on some informal and often incomplete description of this system. This is the main reason for the incompleteness and lack of uniformity of these systems. To avoid these problems we will create a mathematical description of the design management system. This abstract design management system model shows how a good integration of design data, design tool and design flow management can be achieved. This model is based on the analogy existing between design management systems and digital systems.

The time required for the development of a CAD framework is mainly consumed by the construction of its central component; the design management system. The design time of this system can be greatly reduced if it is not programmed in a general purpose language, but instead, is implemented using a dedicated design management system description language, which features special constructs for CAD framework construction. Using such a language, a design management system can be represented at a higher level of abstraction. As a result, it not only becomes easier to create design management system descriptions, but also to maintain and extend these and will therefore lead to a big improvement of the CAD framework development efficiency. However, currently there is no suitable design management system description language available. Therefore, in this thesis we will demonstrate how such a language can be defined.

# 1.5 Thesis organisation

In Chapter 2 we present an overview of the state of the art for CAD frameworks. This chapter introduces the current ideas about what a CAD framework is, presents some of the techniques developed for design management and shows how these techniques have been integrated in the existing CAD frameworks.

In Chapter 3 up to and including Chapter 6 a CAD framework model is presented, which clearly demonstrates how a CAD framework can be constructed which not only achieves a good integration of design data, design tool and design flow management, but also provides support to all participants.

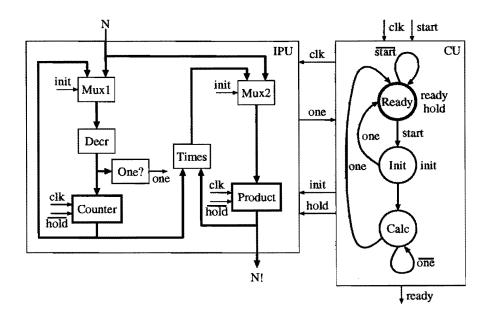

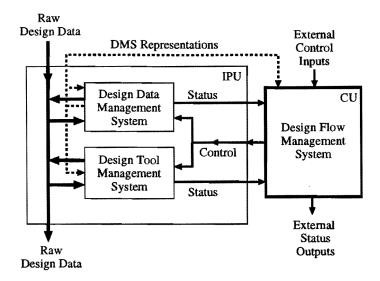

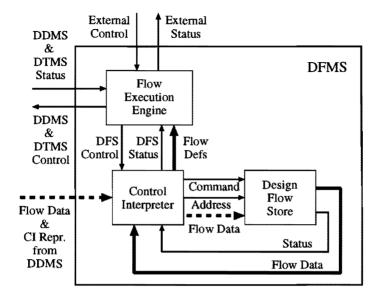

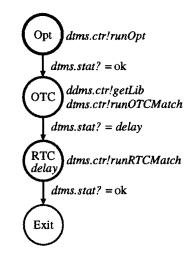

Chapter 3 introduces the IC designer - DMS developer analogy and shows how this analogy leads to a CAD framework in which the design management system is the central component. In addition it features a model of the design management system based on an

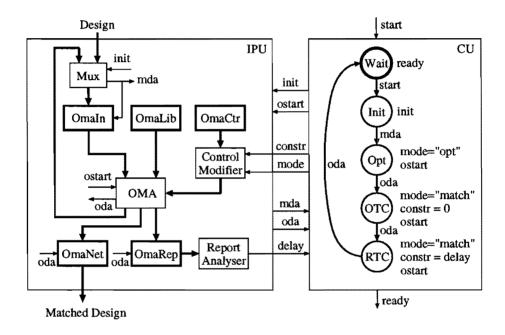

analogy with digital systems. This model is illustrated using a design management system for the LOCAM logic synthesis system. The LOCAM system is described in this chapter and will be used throughout this thesis to illustrate the concepts we introduce.

In Chapter 3 the design management system is described in terms of three interacting subsystems. In the following three chapters, more detailed models of these three sub-systems will be presented, where Chapter 4 covers the design data management system, Chapter 5 the design tool management system and Chapter 6 the design flow management system.

Chapter 7 demonstrates how to define a suitable design management system description language. First the requirements for such a language are formulated. To do this it is essential to have very good picture of what a design management system is. Fortunately, we have already presented a detailed design management model in the previous chapters, which can be used as a guideline. Finally we introduce a class of languages based on an extension of hierarchical coloured Petri nets and demonstrate that these satisfy the formulated requirements.

Finally in Chapter 8 we present our conclusions and we discuss the topics to be addressed by future research.

# Chapter 2 CAD frameworks: State of the art

In this chapter an overview of the state of the art for CAD frameworks is given. Besides for giving information about the completeness of the currently available CAD frameworks, this overview will also be used to informally introduce the concepts involved.

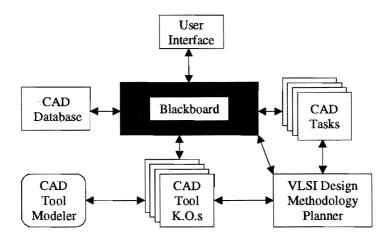

Section 2.1 presents the current ideas about what a CAD framework is and about what it is supposed to do. In order to be able to discuss the kind of support a CAD framework has to provide, we have to know what people are involved. Section 2.2 introduces these CAD framework participants. Likewise, discussions about how to integrate the different design management activities only make sense if we know what design data, design tool and design flow management are. Section 2.3 presents the current ideas about these three design management activities. In Section 2.4 we demonstrate how these ideas have been implemented in some of the existing CAD frameworks. Section 2.5 discusses the current ideas regarding the architecture of CAD frameworks. The architectures presented in this section describe a CAD framework in terms of a number of interconnected components, which either assist designers by performing one of the three design management activities or provide support to the other participants. Therefore, Section 2.5 will also present some of the ideas regarding the integration of the three design management activities and the kind of support which should be provided to the CAD framework participants.

### 2.1 CAD framework definition

Like stated in [KGMB94], defining the term CAD framework is a difficult task. Although the term CAD framework is not exactly defined, the following definitions roughly cover the contents. In [CFI90] the following definition is encountered: "A CAD framework is a software infrastructure that provides a common operating environment for CAD tools." In [tBBvW91] a CAD framework is defined as: "A CAD framework serves as a basis for CAD tool integration and provides the designer with assistance for data organisation and design management." In [HNSB90] the following alternative definition is found: "The term CAD framework has come to mean all of the underlying facilities provided to the CAD tool developer, the CAD system integrator, and the end-user (IC or system designer) necessary to facilitate their tasks." Finally in [KGMB94] the following statement is encountered: "Typically, CAD frameworks include some form of design data management, a consistent user interface, and inter tool communication, in addition to design methodology management."

Despite the confusion regarding the definition of what a CAD framework is, the following things are clear. Firstly, a CAD framework should provide the designer with support for all three design management activities, so for design data, design tool and design flow management. Secondly, besides supporting the designer, the CAD framework should also assist the design management system developers, such as the tool developers and the CAD system integrators mentioned above, in performing their jobs. Therefore, we adopt the following definition: "A CAD framework is a software infrastructure which assists designers by managing their design data, design tools and design flows and which provides support to the design management system developers maintaining it."

Providing support to the Design Management System (DMS) developers is an essential characteristic of CAD frameworks. Many CAD frameworks provide only little assistance to these DMS developers. An extreme example of this is the type of design support system referred to as a *design environment*. Design environments consist of a number of tightly integrated tools operating on a common design data representation. Addition of new tools or alteration of the built in design flow is nearly impossible in these systems. Although a design environment provides design management support, it is usually not considered to be a CAD framework [Dan89], because it completely lacks DMS developer support.

# 2.2 CAD framework participants

In addition to the confusion about what a CAD framework is, there is also little agreement about how to classify the participants involved. In [HNSB90] the CAD tool developer, the CAD system integrator, and the end-user (IC or system designer) are introduced as the CAD framework participants. In [KGMB94] design tool and flow management are referred to as activities involving the following groups of users:

- Designers the ultimate end-users, people who produce design data by executing CAD tools in a design flow,

- Tool Developers people who write CAD programs,

- Tool Integrators people who combine tools and hide the dependencies between tools. They also customise vendor tools to tailor them to the needs of a specific site,

- Flow Developers design experts who describe the design methodology to be used, and

- Managers those who supervise all of the above.

To make the situation even more complex, [LJ92] introduces framework administrators, design methodology managers, project managers and design engineers as the CAD framework participants.

We introduce two types of participants: Designers and design management system developers. The DMS developers can again be divided into five groups: Tool developers, flow developers, design data management system developers, integrators, and CAD framework managers. As their names suggest, tool developers and flow developers create the design management system's tools and flows, respectively. Design data management system developers structure the design data management system by defining a useful organisation for the design data managed by this system. Normally tool developers create tools independent from the CAD frameworks in which these will potentially be used. Therefore, in order for a tool to be used in a CAD framework, the tool will have to be integrated with it. This is the task of the *integrators*. In contrast to tools, flows will usually be developed using the flow description language provided by the CAD framework. In this case no integration is required. A CAD framework stores its data in its local database and/or in external databases. In the last case these external databases will have to be integrated with the CAD framework by the integrators. The last participants we introduce are the CAD framework managers. It is the task of these managers to ensure that the framework created by the other DMS developers functions correctly. One of their tasks is to add new users to the CAD framework and to grant them with the privileges required for performing their tasks.

### 2.3 The design management activities

Discussions about how to integrate the different design management activities only make sense if we know what these activities encompass. In the following three sub-sections we introduce the current ideas about design data, design tool and design flow management, respectively.

### 2.3.1 Design data management

Design data management is concerned with two types of design data, i.e.,

- 1. raw data, and

- 2. meta data.

Raw data are the design descriptions and the auxiliary data, such as simulation and analysis results, used and/or produced during the design process. These often large amounts of data are stored in files residing at some location on a computer network. A design data management system should provide the designer with logical rather than physical access to these data. This means that the system should abstract from information about the actual location of the data on the network and of the operating system specific methods used to store and retrieve these data.

Meta data is information about the design representations and the design activities. A design data management system uses meta data to represent raw data properties and to keep track of the relations existing between the different pieces of raw data. A design data management system collects the meta data by monitoring the design process and uses these data to perform its services.

In [RRvHK93] [vHL96] design data management is described as a multi-dimensional problem. In Table 2.1 the six dimensions presented in [RRvHK93] are listed.

| Dimension  | Representation of:         | Why?                  | Example                 |

|------------|----------------------------|-----------------------|-------------------------|

| Versions   | Modifications              | Keep history          | Optimisation            |

| Hierarchy  | (De)composition            | Divide and Conquer    | Subcircuits             |

| Views      | Other representation       | Abstraction           | Layout, schematic       |

| Derivation | Input $\rightarrow$ Output | Tool flow             | Simulation results      |

| Workspaces | Team-work                  | Access control        | Library                 |

| Variants   | Product options            | Parallel developments | Mains or battery supply |

Table 2.1: Design data management dimensions.

During the design process many different versions of a design representation are created. The reason is that design representations are almost never "first time right". They either contain functional errors or do not satisfy the formulated requirements. A correct design representation is usually obtained after a number of modifications of the original description, each time resulting in a new version. A hierarchy represents how the different components of a decomposed design are related. During the design process a number of different views of the design are created, each uniquely characterised by the abstraction level at which the design is described and/or by the representation language employed. Derivation is concerned with the management of tool invocation results. This is done by association of the resulting outputs with the inputs they were derived from. For example, derivation relates the results of a simulation run to the corresponding design representation and input vectors. For managing team-work, design data management systems employ workspaces, which provide a means to control access to data. A product may have different variants, which, although they provide almost identical functionality, have different implementations, because they have to operate under different circumstances. For example, CD-players are produced in three variants, namely a home, a car, and a portable version. Because the portable version has to run on a battery supply, the ICs used in this variant have to be optimised with respect to power consumption. However, because the remaining functionality is almost identical for all three applications, the design processes of all three variants will have a large part in common. The design data management system has to keep track of to which variant a piece of data belongs.

It is not difficult to build a design data management system which handles one or more dimensions separately. However, creation of a system which is able to deal with more dimensions simultaneously, without causing data inconsistencies, is not a trivial task. Most of the existing systems only support a few dimensions and have difficulties taking the interaction between these dimensions into account. For a summary of how some of the existing design data management systems handle multiple dimensions we again refer to [RRvHK93].

Most of the existing design data management systems are based on an approach similar to the one introduced by Randy Katz [KBC<sup>+</sup>87], who proposes an organisation of the design data space based on design objects. He introduces the following two classes of design objects.

Representation objects are associated with raw data representing a design part at some level of abstraction. These objects are uniquely identified by their name, version number and type. For example the second version of a layout representation of a datapath is referred to as "Datapath[2].Layout". Representation objects are either composite or primitive. Primitive objects are associated with a complete representation of a design part. Composite objects on the other hand, correspond to representations describing a design part in terms of how it connects the subsystems it is composed of. Since such a representation does not contain the descriptions of these subsystems, a composite object only provides an incomplete description of the corresponding design part.

Structural objects are system maintained objects introduced with the purpose of introducing a useful structure on the design database. Structural objects can be used to create an explicit representation of design data management dimension related information. Having such an explicit representation is essential for each design data management system.

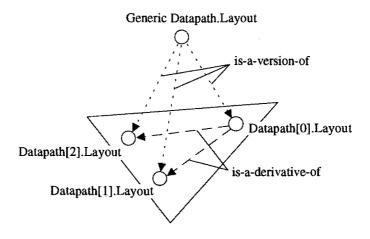

Katz represents objects and their relations using directed graphs. Nodes represent objects and the labelled edges the relations between these objects. As an example consider the datapath layout version history graph shown in Figure 2.1. Such a graph can be used to represent information about versions, derivations and variants. The top node of this graph represent the "Datapath.Layout" structural object. This object, referred to as a version object, groups all the versions of the layout level datapath representation produced during the design process and can be used to represent information which all these versions have in common. The version history graph associates the datapath layout versions to the corresponding version object "Datapath Layout" using the is-a-version-of relationship. The version history is represented using the *is-a-derivative-of* relationship, which relates a version to the design representation it was derived from. Design variants are often functionally equivalent and only differ by the way they are optimised. For example, the ICs used in a portable product will usually be optimised for power, whereas products which are not powered by a battery are most likely to be optimised for speed and/or area. This results in situations like that for the "Datapath Layout" versions "1" and "2", which are derived from the same ancestor object, possibly by the same tool but using different settings.

Figure 2.1: Datapath layout version history.

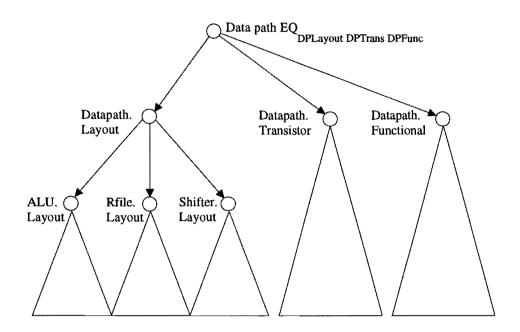

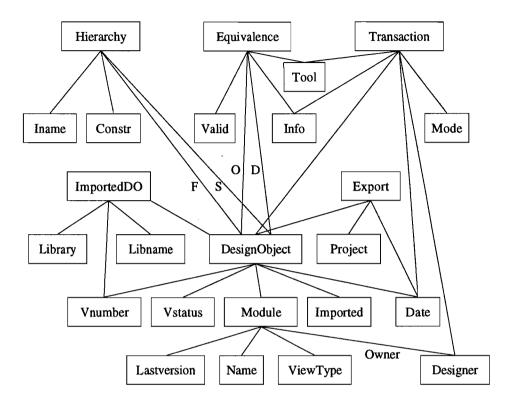

Katz represents information about hierarchy and views using declaration graphs like the one shown in Figure 2.2. The top node of this graph represents an equivalence object, which is a structural object combining all the different views of the Datapath design. The equivalence object combines sub-graphs, referred to as representation hierarchies, which represent the structure of the design representations at a certain level of abstraction. For example, the layout representation hierarchy declares the layout level datapath representation objects as being composite objects defined in terms of an "ALU", "Rfile" (register file) and a "Shifter" subsystem.

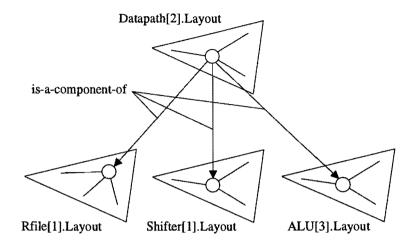

To manage the interaction between hierarchy and versions Katz introduces configuration graphs. Using the different versions of the design part representations created during a design process, many versions of the total design representation can be created. Such combinations are called configurations and are created by relating a version of a composite representation object to versions of its components. An example of a graph representing a configuration is presented in Figure 2.3, which combines version "2" of the composite "Datapath.Layout" object with version "1", "1" and "3" of the primitive objects "Rfile.Layout", "Shifter.Layout" and "ALU.Layout", respectively.

For managing team-work Katz uses the workspace concept. He defines a workspace as a named collection of design objects. There are several types of workspaces, characterised by their access rights (check-out/export privileges) and how severe objects are verified before they can be placed into a workspace (check-in/import restrictions). Examples of the different kinds of workspaces employed are the archive, group, and private workspaces. Archive workspaces, also referred to as library workspaces, contain information which is frequently used by lots of designers. Therefore, this information has to be correct and

Figure 2.2: A hierarchy and view declaration graph.

accessible to all designers. This is achieved by nearly unrestricted check-outs and very restrictive check-ins. Private workspaces are owned by only one designer. Objects can only be checked out by the designer who owns such a workspace. Of the three types of workspaces presented here, private workspaces have the most restrictive check-outs and the most liberal check-ins. Group workspaces are owned by the members of a design group. In a group workspace the design part representations made by the group members are combined to form the complete design representation. The check-in and check-out restrictions of such a group fall somewhere between those of archive and private workspaces.

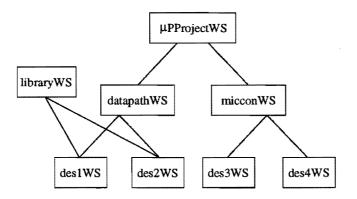

Workspaces can be organised in the form of a *workspace hierarchy*. A workspace hierarchy describes the communication structure of its workspaces, i.e., workspaces can only export to and import from workspaces they are related to by the workspace hierarchy.

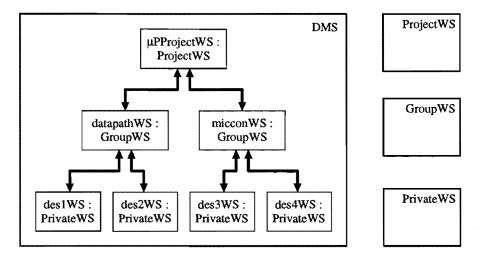

Figure 2.4 shows a workspace hierarchy employed during the design of the microprocessor of Figure 1.3. It represents that the microprocessor is created by a team consisting of the designers "des1", "des2", "des3" and "des4". The design of the datapath is a joint activity of "des1" and "des2". These designers make their datapath representations in their private workspaces "des1WS" and "des2WS". Their work is co-ordinated using the group workspace "datapathWS", which contains data shared by both designers. The datapath is designed using the information stored in the library workspace "li-

Figure 2.3: Datapath layout configuration.

braryWS". Designers "des3" and "des4" are responsible for the design of the controller and the top-level microprocessor description. Their co-operation is co-ordinated using group workspace "micconWS". The work performed in the datapath and the microprocessor/controller workspaces is co-ordinated using the project workspace " $\mu$ PProjectWS". A project workspace [RRvHK93] is a higher-level group workspace which co-ordinates the work performed in a number of group workspaces.

Usually the workspace hierarchy reflects how the total design task is split into a number of smaller design sub-tasks. In our example the decomposition of the microprocessor design task into a datapath design task and a controller design task formed the basis for the workspace hierarchy. However, the workspace hierarchy can also be based on any of the other ways to divide the design task, e.g., according to abstraction level or, in the case of design reuse, the type of work performed.

#### 2.3.2 Design tool management

As the name suggests, a *design tool management system* manages the tools of a CAD framework. A *tool* is an executable program used to support the designer in his design tasks [LJ92] [vW93] [vW94]. Design tool management can be divided into three sub-activities: Tool integration, tool characterisation, and tool invocation.

Tool integration [CFI90] [FBM94] [HWS92] [Sim93] deals with the addition of new tools to the CAD framework. Design tools are usually developed as stand-alone programs, which are independent from the CAD frameworks in which they are used. Therefore, for most of the tools it will not be possible to directly interface them to the CAD framework. Some

Figure 2.4: A workspace hierarchy.

tools are integrated by modification of the source code, allowing these tools, referred to as *integrated tools*, to directly access the services provided by the CAD framework. However, the source code of a tool is not always available. In this case, the tool is integrated using *encapsulation* [Sch94] [Sch95], i.e., a special program is written, referred to as a *wrapper*, which interfaces the *encapsulated tool* to the CAD framework. To facilitate encapsulation the Tool Encapsulation Specification language TES [CFI91] was developed. This language enables tool developers to the specify tool encapsulation information required by tool integrators for writing a tool wrapper. To support the integration of tools, a CAD framework should feature a *tool interface*, consisting of a number of functions via which the tools can access the services provided by the framework. In [vW93] and [HWS92] two proposals for such a tool interface are presented.

As stated in [DD89], a designer should be able to query the design tool management system about the existence of tools suitable for a given task. This is only possible if the tools are able to accurately represent their general abilities to their potential users. The activity of charting the abilities of a tool is referred to as *tool characterisation*. Except for [DD89], there is not much literature about this topic, probably because it strongly depends on the type of tool being characterised.

Once a designer has selected a tool, he should not be bothered with details about how to invoke the tool. This means that the system should abstract from *tool invocation* related information such as:

- The location of the corresponding executable,

- the parameters to be supplied to this program during invocation, and

- the location of the inputs and outputs of the program.

Like for tool characterisation, [DD89] is about the only article addressing this problem. The reason is probably that tool invocation deals with low level operating system specific issues.

Tool integration, tool characterisation and representation of tool invocation related information are activities performed by the DMS integrator referred to as a *tool integrator*. Sometimes the tool integrator is assisted by the developer of the tool.

### 2.3.3 Design flow management

Besides managing their data and tools, a CAD framework should also assist designers in applying the tools to the data in such a way that the desired design is obtained. This involves selection of the tools to invoke, determination of the order of these invocations and selection of the data to which these tools are applied. A description of how to make these decisions is referred to as a *flow*. The activity of assisting the designer in making these decisions is referred to as *design flow management*. For a good overview of the existing approaches for design flow management we refer to [tB95] and [KGMB94].

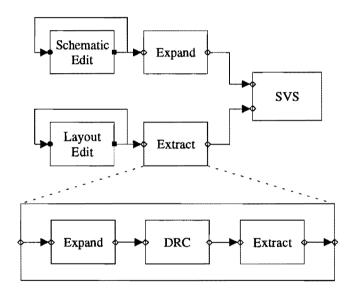

A design flow management system should provide a language to represent flows. Using this language, design flow developers either create an explicit flow representation [vHT90][vW93] [vW94] [tB95] or a description of a flow generator [BC94] [BC95] [SBD93], which can be used to dynamically define flows. The knowledge required for constructing such a flow is obtained by consulting design experts. The resulting flow representations can be used to document design processes. However, if the flow description language is executable, then these representations can be used to automate the part of he design process the flow describes. In fact, such a flow acts as a higher level tool, to be used by a designer instead of the tools invoked by the flow. This enables managers to enforce a design policy simply by selecting the tools and flows which a designer is allowed to use.

[KGMB94] uses *directed graphs* as a intuitive metaphor to discuss flows. A directed graph is composed of a set of vertices or nodes, a set of edges or arcs, and a mapping of every edge onto an ordered pair of vertices. A design flow can now be represented by a graph, where each node represents a design activity, such as the application of a CAD tool, and each arc describes a dependency, temporal, data or control, the destination node has on the source node.

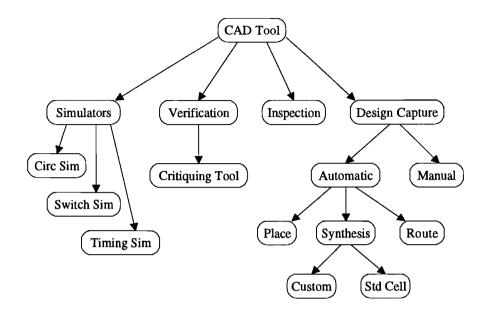

Flows describe decisions regarding which tools are to be invoked on what data. If a flow directly refers to the tools to be executed, changes to the set of available tools will require some of the flows to be updated. This makes the flows descriptions very volatile. A possible solution is to have the flow refer to tool abstractions like *tasks* [BD91] [HD96] [KGMB94] or *activities* [LJ92] [BtBvW92] instead. These tool abstractions correspond to abstract design functions and abstract from information about how these are implemented in terms of tool invocations. When flows are defined in terms of tool abstractions, then changes to the collection of available tools will only affect the tool abstraction definitions and will leave the flows unchanged.

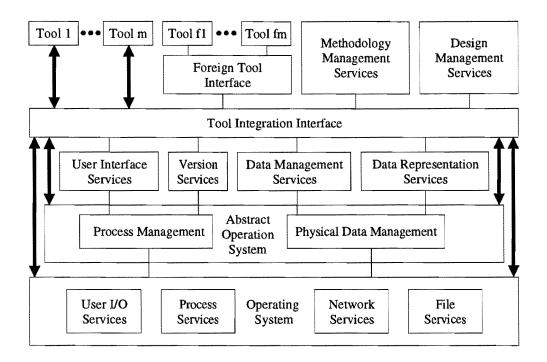

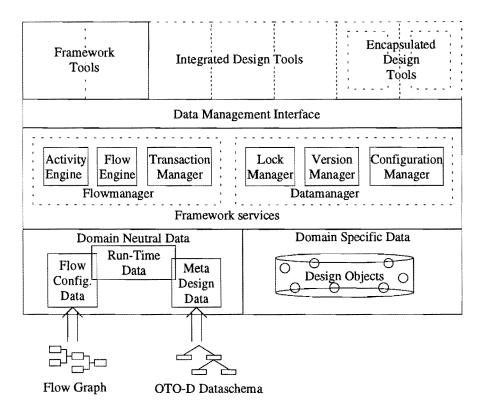

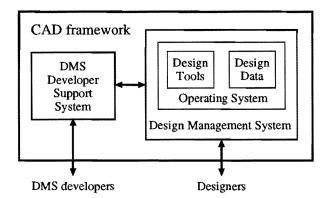

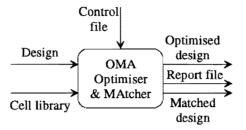

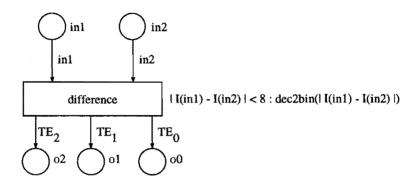

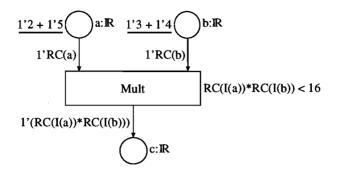

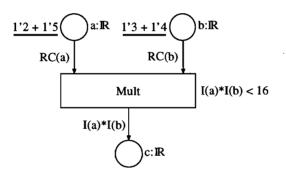

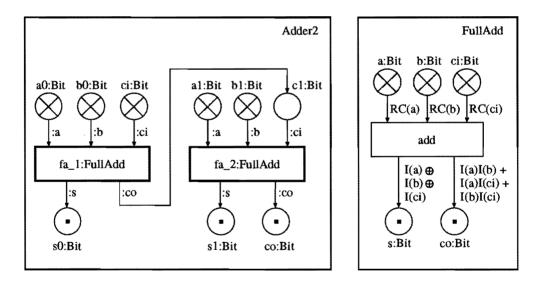

# 2.4 Existing CAD frameworks