## Interactive modelling and simulation of heterogeneous systems

### Citation for published version (APA):

Fleurkens, J. W. G. (1996). Interactive modelling and simulation of heterogeneous systems. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR456563

DOI: 10.6100/IR456563

### Document status and date:

Published: 01/01/1996

### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

## Interactive Modelling and Simulation of Heterogeneous Systems

## **Hans Fleurkens**

## Interactive Modelling and Simulation of Heterogeneous Systems

## Interactive Modelling and Simulation of Heterogeneous Systems

### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr. J.H. van Lint, voor een commissie aangewezen door het College van Dekanen in het openbaar te verdedigen op dinsdag 26 maart 1996 om 16.00 uur.

door

Johannes Wilhelmus Gerardus Fleurkens

geboren te Venray

Dit proefschrift is goedgekeurd door de promotoren:

prof.Dr.–Ing. J.A.G. Jess prof.ir. M.P.J. Stevens

en de copromotor:

dr.ir. J.T.J. van Eijndhoven

© Copyright 1996 J.W.G. Fleurkens

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without prior written permission from the copyright owner.

Druk: Wibro dissertatiedrukkerij, Helmond

CIP-GEGEVENS KONINKLIJKE BIBLIOTHEEK, DEN HAAG

Fleurkens, Johannes Wilhelmus Gerardus

Interactive modelling and simulation of heterogeneous systems / Johannes Wilhelmus Gerardus Fleurkens. – Eindhoven : Eindhoven University of Technology. – III. Proefschrift Technische Universiteit Eindhoven. – Met lit. opg. – Met samenvatting in het Nederlands. ISBN 90-386-0377-0 Trefw.: elektronische schakelingen / simulatie.

## Contents

| Abstract v   |                                              |           |   |

|--------------|----------------------------------------------|-----------|---|

| Samenvatting |                                              |           |   |

|              |                                              |           | 1 |

|              | 1.1 Background                               | 1         |   |

|              | 1.2 Design and simulation in ESCAPE          | 4         |   |

|              | 1.3 Examples                                 | 9         |   |

|              | 1.4 Related work                             | 12        |   |

|              | 1.5 Outline of this thesis                   | 16        |   |

| 2            | Event driven simulation                      | 17        |   |

|              | 2.1 Introduction                             | 17        |   |

|              | 2.2 Simulation models                        | 19        |   |

|              | 2.3 Discrete event simulation                | <b>21</b> |   |

|              | 2.3.1 Simulation approaches                  | 21        |   |

|              | 2.3.2 Time advance mechanisms                | 24        |   |

|              | 2.4 Event driven simulation                  | 25        |   |

|              | 2.4.1 The simulation state of the system     | 25        |   |

|              | 2.4.2 Event types                            | 27        |   |

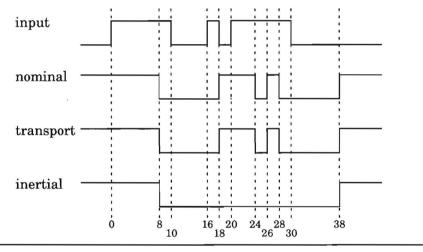

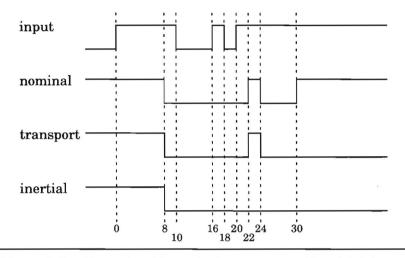

|              | 2.4.3 Examples using various delay models    | 31        |   |

|              | 2.4.4 Delta delay events                     | 32        |   |

|              | 2.5 Event processing and management          | 33        |   |

|              | 2.6 Interaction between simulator and editor | 36        |   |

|              | 2.7 Animation                                | 42        |   |

|              | 2.8 Discrete event monitors                  | 43        |   |

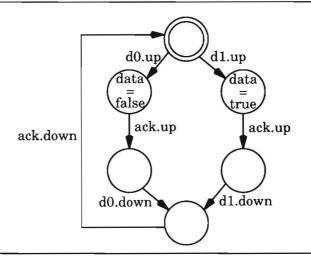

|              | 2.8.1 Discrete event automata                | 47<br>50  |   |

|              | 2.8.2 Examples and results                   | 50<br>51  |   |

|              | 2.9 Hierarchy<br>2.9.1 Related work          | 53        |   |

|              | 2.9.1 Kelated work                           | 53        |   |

|              | 2.9.2 Managing merarchy                      | 55<br>57  |   |

| 3            | Multi-model simulation                       | 59        |   |

| -            | 3.1 Introduction                             | 59        |   |

|              |                                              |           |   |

|                  | 3.2 Foreign language models                                   | 61         |  |  |

|------------------|---------------------------------------------------------------|------------|--|--|

|                  | 3.2.1 The foreign language interface                          | 62         |  |  |

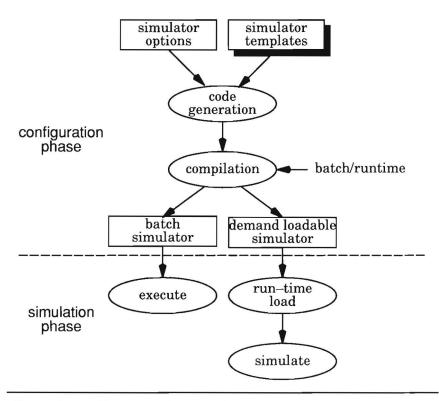

|                  | 3.2.2 Compiled simulation                                     | 65         |  |  |

|                  | 3.2.3 Experimental results                                    | 67         |  |  |

|                  | 3.3 External simulator interface                              | 68         |  |  |

|                  | 3.3.1 Synchronization of simulation time                      | 76         |  |  |

|                  | 3.3.2 Example: The PLATO piecewise linear simulator           | 79         |  |  |

|                  | 3.3.3 Simulation examples and results                         | 82         |  |  |

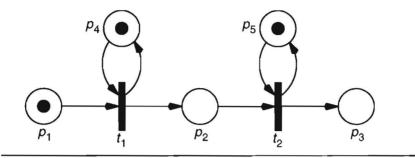

|                  | 3.4 Token flow models                                         | 83         |  |  |

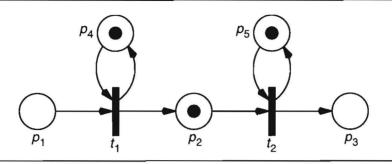

|                  | 3.4.1 Petri nets                                              | 85         |  |  |

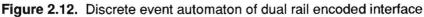

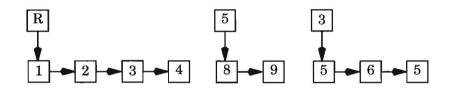

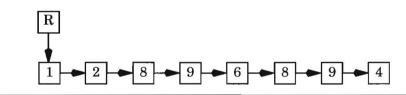

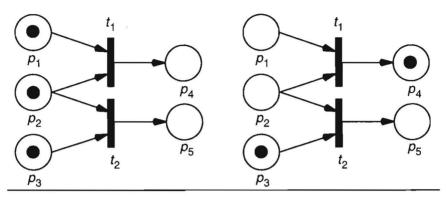

|                  | 3.4.2 Data flow graphs                                        | 89         |  |  |

|                  | 3.4.3 Simulation of data flow graphs                          | 92         |  |  |

|                  | 3.5 Run-time configuration of the simulator                   | 96         |  |  |

|                  |                                                               |            |  |  |

| 4                | Simulation examples                                           | 99         |  |  |

|                  | 4.1 Introduction                                              | 99         |  |  |

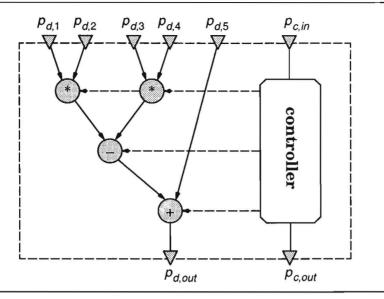

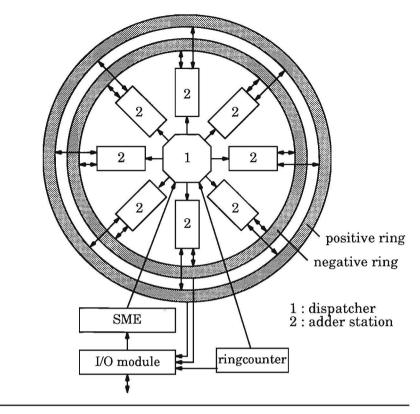

|                  | 4.2 The inner product calculation chip                        | 99         |  |  |

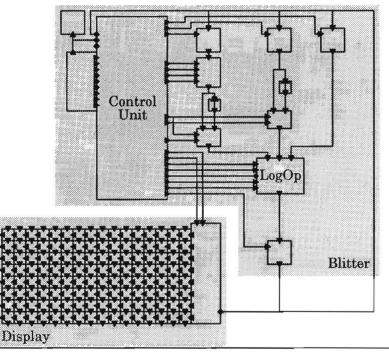

|                  | 4.3 The bit blitter                                           | 102        |  |  |

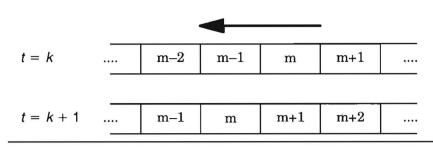

|                  | 4.4 Simulation of traffic on a road                           | 103        |  |  |

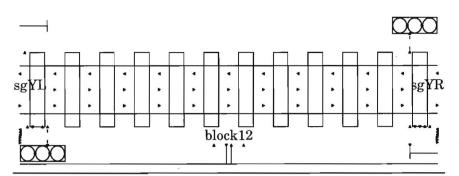

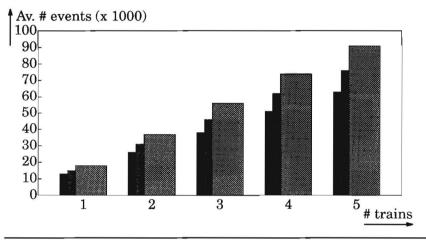

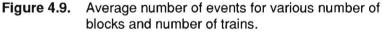

|                  | 4.5 Model of a railroad and block control system              | 106        |  |  |

| 5                | Design process integration                                    | 113        |  |  |

|                  | 5.1 Introduction                                              | 113        |  |  |

|                  | 5.2 A programmable graph view                                 | 114        |  |  |

|                  | 5.3 Inter process communication and the inter tool protocol . | 117        |  |  |

|                  | 5.4 Configuration of the user interface                       | 119        |  |  |

|                  | 5.5 The interactive data access language                      | 121        |  |  |

|                  | 5.6 An example: the integration of NEAT and ESCAPE            | 121<br>122 |  |  |

|                  |                                                               | 144        |  |  |

| 6                | Concluding remarks                                            | 125        |  |  |

| A                | The LISP-like HDL                                             | 141        |  |  |

|                  | A.1. Introduction                                             | 141        |  |  |

|                  | A.2. The language                                             | 141        |  |  |

|                  | A.3. Summary of functions                                     | 141        |  |  |

|                  |                                                               |            |  |  |

| B                | Simulating the bit blitter                                    | 147        |  |  |

| С                | The inter tool protocol                                       | 151        |  |  |

| -<br>Notation 15 |                                                               |            |  |  |

| Notation         |                                                               |            |  |  |

| Biography 1      |                                                               |            |  |  |

|                  |                                                               |            |  |  |

## Abstract

Simulation is used intensively to validate the functional behaviour of electronic systems. It may be used to make estimations on timing, performance and power issues. Simulation is also of great value during the prototyping and debugging of system descriptions in the specification phase. Both the increasing size and complexity of systems to be designed , the migration of the initial specification to higher abstraction levels as well as a reduction of the time to market put new demands on simulation tools.

Simulation performance and the ability to simulate different types of models are important parameters in developing a simulator that satisfies current and future needs. The key issue is to provide the flexibility to simulate a large variety of models without sacrificing simulation performance. Besides raw simulation performance, the design time itself should be reduced as much as possible.

This thesis describes the concepts and techniques that can be used to develop an event driven simulator that

- reduces the design cycle time to facilitate the prototyping and debugging of systems, and that allows to explore the design space;

- allows to simulate multiple types of models homogeneously.

All these concepts and techniques have been implemented in a tool called ES-CAPE.

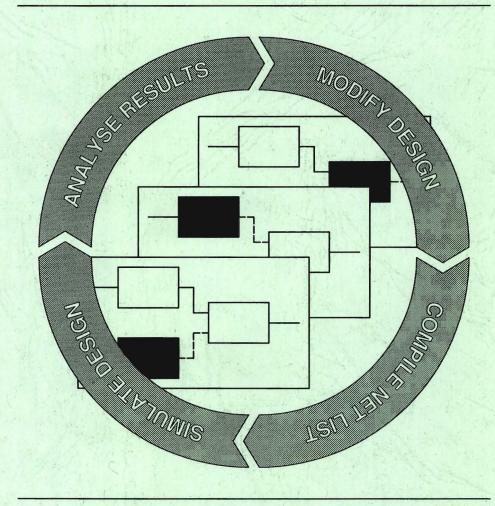

A reduction of the design cycle time has been achieved by embedding a graphics editor and discrete event simulator into a single tool. This allows a tight integration of the various phases of the design cycle, which reduces the overall design time significantly. The time consuming net list compilation phase is avoided by *incrementally* updating the simulation model with each modification of the underlying descriptions it is composed of. As opposed to other simulation tools, in which the compilation or elaboration of the simulation model consumes a large part of the designer's time, the simulation model can be re-simulated without perceivable delay to the designer. It is even possible to modify parts of the model during simulation, for instance to investigate the influence of errors on various aspects of the model. The simulator also features various facilities to support the designer in analysing simulation results: the behaviour of the system may be animated or visualized during simulation. Furthermore, erroneous behaviour may be detected at a higher level of abstraction. This is achieved by hierarchically defining monitors that process sequences of events and replacing such sequences by events at a higher level of abstraction. These events do not influence the progress of the simulator itself.

This thesis also describes the problems and that are associated with multimodel simulations as well as some solutions. Since it is very hard to anticipate which models need to be supported in near future, the simulation kernel should be flexible enough

- to deal with multiple types of models at the same time;

- to be able to support relatively easy a new type of simulation model.

Performance and flexibility have been the dominating issues in the research of integration techniques that allow homogeneous simulation of multiple types of models.

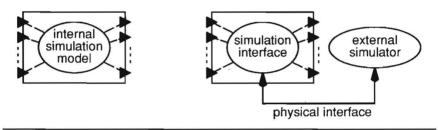

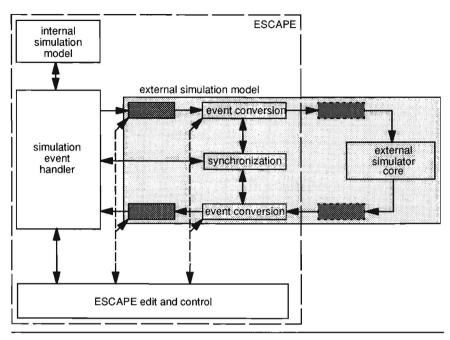

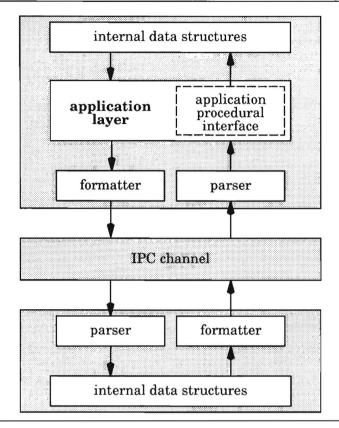

The basic approach that has been taken here is that different types of simulation algorithms and different types of simulators are mapped onto the event driven paradigm: one event driven simulation kernel can handle different timing representations and different delay models. This kernel also orchestrates the execution of all models in a unified and proper way. Different types of events are used to accomplish this. To facilitate the integration of external simulators, both a simulation interface and a model encapsulation technique have been developed that deal with event conversion, value conversion and synchronization between the various models.

Finally, this thesis describes which techniques have been used to be able to customize the design and simulation tool and how it may be interfaced with other design tools. As a result, it can easily be incorporated into an existing design flow. When used in master mode, the tool may be used as a generic frontend, or as a simulation and visualization tool of other design tools, when used in slave mode. A very successful example is the integration with an architectural synthesis system.

The solutions presented in this thesis are substantiated by practical implementations and validated by a large variety of examples. They may be applied to various application areas, even in other disciplines.

## Samenvatting

Simulatie is een intensief gebruikt middel om het funktionele gedrag van elektronische systemen te controleren. Het wordt gebruikt om schattingen te maken op het gebied van tijdsgedrag, prestatie en vermogensgebruik. Simulatie is eveneens een waardevol hulpmiddel bij het ontwikkelen van prototypes en het elimineren van fouten in systeembeschrijvingen tijdens de specifikatie van het gewenste gedrag. Omdat de grootte en de complexiteit van systemen toeneemt, systemen op een steeds hoger abstractieniveau beschreven worden en omdat tegelijkertijd systemen steeds sneller op de markt moeten komen, worden steeds hogere en nieuwe eisen aan simulatieprogrammatuur gesteld.

De snelheid waarmee gesimuleerd kan worden en de mogelijkheid om verschillende types van modellen te kunnen simuleren zijn belangrijke eisen die gesteld worden bij de ontwikkeling van een simulator die zowel aan de huidige als aan toekomstige behoeftes moet voldoen. Het is erg belangrijk om een groot scala van modellen te kunnen simuleren zonder de snelheid van de simulatie daaraan op te offeren. Behalve de invloed van de snelheid van de simulatie zelf moet ook de ontwerptijd zoveel mogelijk bekort worden.

In dit proefschrift worden een aantal concepten en technieken beschreven voor een *event* gestuurde simulator zodanig dat

- de iteraties tijdens het ontwerpen zo kort mogelijk worden en ook het aantal iteraties zo klein mogelijk is; dit bevordert de ontwikkeling van prototypes en maakt het gemakkelijker om fouten in beschrijvingen op te sporen en te verwijderen. Verder is het mogelijk om verschillende alternatieven af te wegen;

- verschillende soorten modellen tegelijkertijd op een homogene wijze gesimuleerd kunnen worden.

Al deze concepten en technieken zijn geïmplementeerd in een programma ES-CAPE geheten.

De vermindering van de tijd om een ontwerpcyclus te doorlopen is mogelijk gemaakt door een grafische editor en een diskrete event simulator in één programma onder te brengen. Dit maakt het mogelijk om de verschillende fases van de ontwerpcyclus te integreren, waardoor de ontwerptijd aanzienlijk gereduceerd kan worden. De veel tijd kostende netlijst compilatie wordt vermeden door het simulatiemodel *incrementeel* aan te passen, als één van de beschrijvingen waaruit het model is opgebouwd veranderd wordt. In tegenstelling tot andere simulatoren, waar het compileren of het uitwerken van het simulatiemodel een groot gedeelte van de tijd van de ontwerper kost, kan het simulatiemodel zonder enige merkbare vertraging opnieuw gesimuleerd worden. Het is zelfs mogelijk om tijdens de simulatie delen van het model te veranderen, bijvoorbeeld om de invloed van fouten op verschillende aspecten van het model te onderzoeken.

De simulator bevat eveneens een aantal eigenschappen die de ontwerper helpen bij de analyse van de simulatieresultaten. Het gedrag van het systeem kan nl. grafisch weergegeven worden tijdens de simulatie. Eveneens kan foutief gedrag ontdekt worden op een hoger abstractieniveau. Dit wordt bereikt door monitoren hierarchisch te definiëren die sequenties van events kunnen verwerken en deze vervangen door events op een hoger abstractieniveau. Deze events beïnvloeden het gedrag van het te simuleren systeem verder niet.

Daarnaast beschrijft dit proefschrift de problemen met betrekking tot, en een aantal oplossingen voor simulaties van een aantal verschillende soorten modellen. Omdat het erg lastig is om rekening te houden met de modellen die gebruikt gaan worden in de nabije toekomst, moet de kern van de simulator flexibel genoeg zijn om

- tegelijkertijd verschillende types simulatiemodellen aan te kunnen;

- relatief gemakkelijk een nieuw type simulatiemodel te kunnen toevoegen.

De efficiëntie en de flexibiliteit zijn de belangrijkste aspecten geweest bij het onderzoek naar integratietechnieken voor het op uniforme wijze simuleren van verschillende types modellen.

De basistechniek is dat verschillende algoritmes en simulatoren op hetzelfde event gestuurde model zijn afgebeeld: de kern van het simulatieprogramma kan omgaan met verschillende representaties van de tijd, verschillende vertragingsmodellen en controleert de uitvoering van alle modellen op een uniforme en correcte wijze. Dit is gerealiseerd door het gebruik van verschillende soorten events. Om de integratie van andere simulatoren te ondersteunen zijn een simulatie-interface en een encapsulatietechniek ontwikkeld. Deze zorgen voor de conversie van de events, de conversie van de signaalwaardes en de synchronizatie tussen de verschillende modellen en simulatoren.

Tenslotte beschrijft dit proefschrift een aantal technieken zodat het programma gemakkelijk aan de wisselende eisen van gebruikers kan worden aangepast en zodat dit programma kan samenwerken met andere ontwerptools. Deze technieken maken het mogelijk om het programma te gebruiken in een bestaand ontwerptraject. Het programma kan met name gebruikt worden om andere programma's aan te sturen of voor het simuleren en het grafisch weergeven van gegevens van andere ontwerptools. Een goed voorbeeld is de succesvolle integratie met een architectuursynthesesysteem.

De oplossingen die aangedragen zijn in dit proefschrift zijn geïmplementeerd en gecontroleerd met een grote verscheidenheid aan voorbeelden. Ze kunnen gebruikt worden voor een groot aantal toepassingsgebieden, zelfs in andere vakgebieden.

## Preface

This thesis is based on the research that has been performed in the Design Automation Section of the Department of Electrical Engineering of Eindhoven University of Technology in the Netherlands. In this period, an interactive flexible design and simulation tool called ESCAPE has been developed, in which a discrete event simulator and a graphics editor have tightly been integrated. The concepts and techniques that have been applied in this tool are described in this thesis.

### Acknowledgements

I would like to thank Jochen Jess for giving me the opportunity to work in his research group and the Dutch Foundation on Fundamental Matter (FOM) and STW for sponsoring the research project under contract EEL 88.1427.

I would like to thank the following people for their contributions to my research work: Ronald Tangelder [Fle91], Pim Buurman [Fle93a] and Koen van Eijk [Fle95], and the students who helped me. Furthermore, I would like to thank the people who have provided some of the examples: Arnold Niessen who developed the basic components of the railroad model, Wim Philipsen who developed the model of the bit blitter, but in particular Geert Janssen.

I also would like to thank all other members of the Design Automation Section for providing a stimulating environment and a good atmosphere.

I am very grateful to Gjalt de Jong for thoroughly proofreading the draft version of my thesis and for the many discussions I have had with him.

And last but not least, I would like to thank my parents and my sister for giving me support throughout my study.

# Chapter I Introduction

### 1.1 Background

Today's market, in which electronic products have a short life time, requires that new products are put on the market as soon as possible, while the production costs are minimized. The total costs of manufacturing electronic products are greatly reduced, if the number of components of these products are decreased. This can be achieved by integrating more components on a single chip. Although the progress in technology makes it possible to integrate more and more components on a single chip every year, the design process itself is becoming more and more a limiting factor for manufacturing ICs with complex designs.

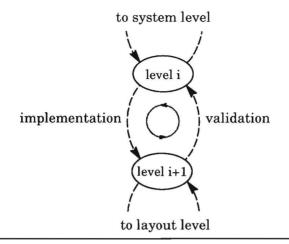

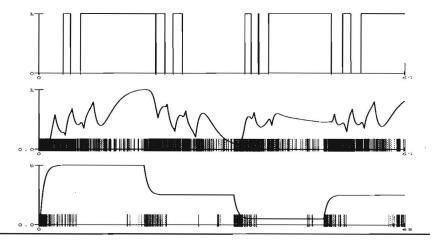

To design an IC, which performs exactly as specified, is an extremely difficult task. Therefore, this task is usually divided into a number of implementation steps. A sequence of implementation steps transforms an initial specification of a system into a mask description of the layout of the chip, which can be processed in a foundry. Every implementation step has to be validated intensively. If the result of this validation does not satisfy, the implementation step has to be repeated. If the validation phase does not detect erroneous behaviour, the resulting design can serve as the specification of the next implementation step. In this thesis, an iteration of implementation and validation activities between two levels is referred to as the *design cycle* (see figure 1.1). To facilitate the design task, design automation tools have been developed in the last decades for implementing and validating designs.

The implementation steps have been automated to a large extent by developing synthesis tools for different abstraction levels. As a result, the level of initial specification is moved from the layout level to the system level. Currently, most research in this area is focussed on architectural synthesis, hardware software co-design, and system level synthesis tasks like specification, partitioning and interface synthesis. This thesis deals with the other phase of design activity: the validation part of the design cycle. The thesis especially focusses on validation at the highest levels of abstraction. Design validation is extremely important, because undetected errors may result in expensive redesigns and long delays before the resulting product can be put on the market. Besides for validation purposes, simulation may also be used to make estimations on timing, performance and power issues.

Figure 1.1. A step in the design trajectory

Simulation has been and currently is the most important technique to validate the functional behaviour of a system. Implementation steps are validated by comparing the simulation results at two different abstraction levels. Synthesis tools should make the validation process easier: in principle, they should produce results that are correct by construction. However, in practice the results of each synthesis tool have to be validated as intensively as the results of other approaches, because of bugs and deficiencies in those tools. Therefore, validation remains an important (and the most time consuming) design activity.

Simulation can not guarantee the correctness of a design in all circumstances, because the number of cycles required to get full coverage of errors is too large to perform this task in reasonable time. Despite this fact, simulation is fully accepted in the design community. Formal verification techniques are a promising alternative to simulation as a validation technique and their application often guarantees full coverage of errors [McM94]. Although much progress has been made in this area, these tools often fail to handle real–life designs and definitely can not handle full system specifications. Therefore, both simulation and verification tools should supplement each other to perform system validation. A simulator may also assist verification tools in locating and correcting design errors, e.g. by feeding the simulator with output traces of verification tools that lead to erroneous behaviour. But the most important application area of simulation will be its use during the prototyping, validation and debugging phases of an initial specification of a system. A number of problems are associated with the simulation of large systems. The increasing complexity of systems makes simulation a difficult and timeconsuming task. Even worse, the computational time increases exponentially with a decreasing level of abstraction, which is often required to accurately simulate a system. For instance, simulating a complete system at the circuit level is nowadays (almost) infeasible, because it may require several days or even weeks. A number of solutions exist for this problem: mixed-level simulators handle the problem by simulating various parts of the model at different levels of abstraction. This solution reduces the computational costs of the simulation task significantly. Other techniques like parallel or distributed simulation, or improvements on the simulation algorithm itself, only give minor (i.e. linear) performance improvements.

Not only much computational time is required to validate a system description, but the time spent by the designer to iterate through the design cycle is increasing rapidly as well. This is caused by both the complexity of interpreting simulation results, and the separation of synthesis and validation tools. The latter problem often causes expensive re-simulations for small design changes. Simulation time is also reduced by incremental simulation tools [Cho88], which restrict re-simulation to those regions of the system, that are affected by design modifications. This approach takes a large amount of memory to store simulation histories and is only useful in the debugging phase, when only small modifications are made to the design. Most work in this area still focusses on the lower levels of the design trajectory, in particular logic and switch-level simulation.

Validation at the system level introduces another problem: systems often contain subsystems of different nature and the design of each subsystem may involve a different design trajectory. Often, each subsystem is best modelled using the most natural and appropriate description language or, from simulation point of view, the most appropriate model of computation. The choice of an appropriate description language may also depend on the backend design tools for that particular subsystem. Different descriptive means can also be used to model different properties or aspects of a system. For instance, a Petri net could model the communication behaviour between different components of a system: the operational semantics of a Petri net determine when a component needs to be evaluated. The (functional) behaviour of each component could be described using a hardware description language. In this case, the Petri net might be verified for properties like liveness and deadlock by dedicated analysis tools, while a simulator might be used to validate the overall system behaviour.

Validation of such heterogeneous systems can only be performed efficiently and accurately, if multiple models of computation are supported by the simulation tool. Since it is very hard to anticipate on the models of computation that are going to be used to describe systems, it has to be relatively straightforward to include support for new models of computation in the simulation tool.

In the next section, an overview is given of a design tool called ESCAPE, which tries to cope with the problems related to the validation of complex heterogeneous systems.

### 1.2 Design and simulation in ESCAPE

ESCAPE is a highly interactive and flexible design environment. It can be used to capture complex heterogeneous system descriptions and verify these descriptions through simulation. Its open architecture makes possible easy adaptation to different application areas and simulation needs. The environment provides an incremental design and validation strategy and animation techniques to visualize the activity and other properties of the system under design. This allows fast exploration of the design space and easy debugging of a system description.

ESCAPE has evolved from a simple schematics entry program called ESCHER [Lod86] that has been extended with a discrete event simulator [Jan89] towards a sophisticated design environment, which combines textual and graphical design entry and the validation of systems composed of these descriptions. The role of schematics entry in the CAD community has partly been replaced by popular hardware description languages (HDLs) like VHDL [IEE88] and Verilog [Tho91]. HDLs are used to describe both structure and functional behaviour of systems, but can be combined with graphics entry as well. Often, a graphical representation of a system gives a better perception of the system's overall structure. Especially, if these graphical representations are used for visualization purposes by other tools, they are preferred over textual descriptions. Graphical languages and graphical design capture have gained in popularity lately, because of standardization of graphics libraries and fast graphics workstations. Graphical languages or descriptions are used for various purposes:

- structural decomposition of a description, which is analogous to the use hierarchy in schematics capture programs;

- functional decomposition of either hardware or software descriptions;

- design methodologies which rely on a graphics formalism.

In ESCAPE, a combination of graphical and textual formats can be used to describe a system. Systems are described hierarchically and consist of composite and primitive modules. A composite module is described using another graphical description, that again consists of other composite or primitive modules. Primitive modules require a textual description to document their behaviour. Such a description is not necessarily a pure behavioural one: it might contain structural data as well, if that is supported by the hardware description language. In this thesis, a primitive module is related to a textual description, mostly describing its behaviour, whereas a composite module is related to a graphical description, mostly describing structure.

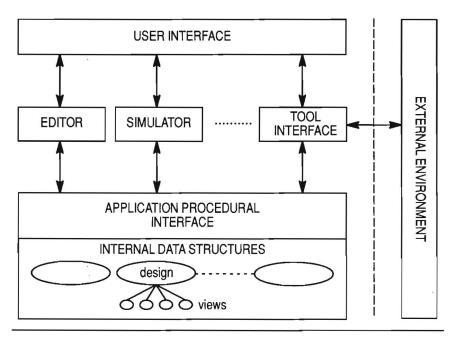

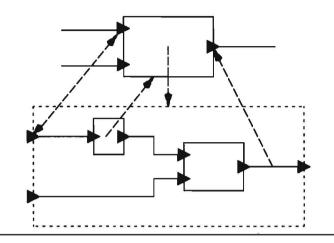

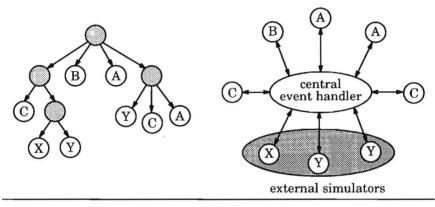

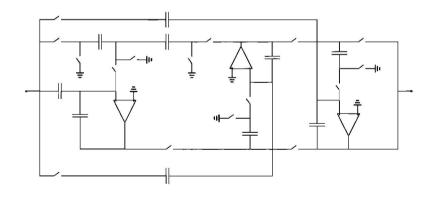

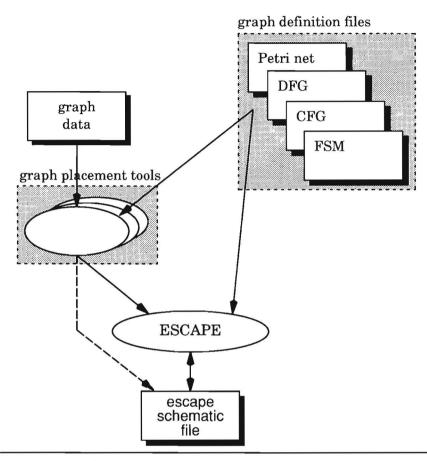

The internal organization of ESCAPE is depicted in figure 1.2. ESCAPE is composed of several functional components, which are controlled through the user interface and which access the same data structures through the application procedural interface (API). The organization of ESCAPE will be discussed in more detail starting with the internal data structures. This will also give more detailed information on the capabilities of this interactive design and simulation environment.

Figure 1.2. Schematic overview of ESCAPE.

The internal data structures store all data that is manipulated in a single session. In ESCAPE, a basic entity is called a *design*. Each design is a collection of different views, which represent various aspects and alternative implementations of a design. The following view types are defined:

- The *symbol* view which is used to define both the representation of a design and its interface.

- The *network* view which is used to capture structural descriptions of a design. Another design is instantiated in this view using its symbol view.

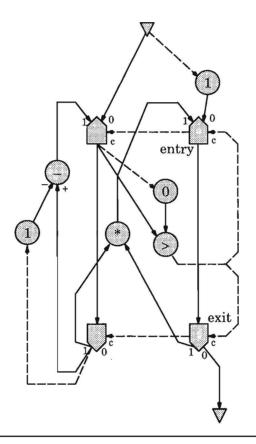

- The graph view which is used to capture graph models. Graph models are often used as an intermediate format in synthesis and verification tools. Many formalisms and representations in CAD applications are based on graphs. Examples are finite state machines, data flow graphs, Petri nets. A special definition language is developed to describe different classes of graphs: it allows to customize this view to be able to capture different types of graphs.

- The *text* view which is primarily used to capture behavioural descriptions of a design.

- The *link* view which is used to define a set of relations between different objects in views of one or more designs. In this thesis, such relations are referred to as *explicit* relations, i.e. explicitly defined by a user.

Besides explicit relations, some relations are directly modelled (hardcoded) in the underlying data structures: these relations are required by the built-in tools to correctly access and modify design data. They are referred to as *implicit* relations. This is opposed to the explicit relations which can be used without any restriction to model additional relations between various views. Multiple sets of explicit relations are used to capture different information. Each set is considered as a separate link view.

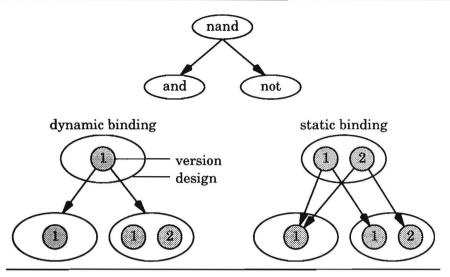

An example of an implicit relation is the link between a module in the network view and the symbol view of the design, of which this module is an instantiation. This relation is mandatory and models hierarchy. Explicit relations are for instance used to relate nodes in the three graph representations of the architectural synthesis system NEAT [Hei94]: ESCAPE is able to capture and visualize the design data used by this synthesis system by storing the relations between the various representations of synthesis data.

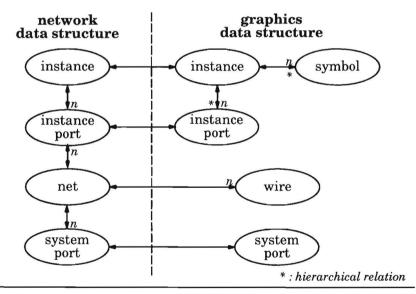

Each view consists of two data structures: the graphical data structure and the *network* data structure. Data in both of these data structures is strongly related. Data of particular objects (e.g. a module, a wire or some textual information) are represented in either data structure or both. The graphical data structure stores all data of an object related to its position, size and appearance on the screen. The graphical data structure is used to build and modify the network data structure in an incremental way. The network data structure always represents an up-to-date net list of the system that is directly accessable by other tools, like the built-in event-driven simulator.

All functionality to create, modify, delete and access the objects in the internal data structures is accessable through an application procedural interface. Tools or new functions can be built which are compiled and linked into a single program (executable). In ESCAPE, a graphics editor and a discrete event simulator have been integrated tightly in a single program. This reduces the overhead of transferring simulation data using files or other mechanisms provided by the operating system to a minimum. Using the same concepts, more tools could be integrated in the same tool as well: this would further reduce the overhead between two or more design steps, and allow incremental updates and validation of multiple implementation or synthesis steps.

One of the components of ESCAPE is the event driven simulator, which is fully embedded within the tool or environment: it executes in the same address space as the editor. The performance of this simulator is not affected by the integration itself: the network data structures are optimized for access by the embedded simulator. The close interaction between simulator and editor reduces the design time: for instance, excessive net list compilation times for large net lists are avoided, because each modification immediately updates all data structures. In ESCAPE, it is even allowed to modify a design during a simulation experiment, which gives the opportunity to explore the design space and to simulate exceptions without any overhead.

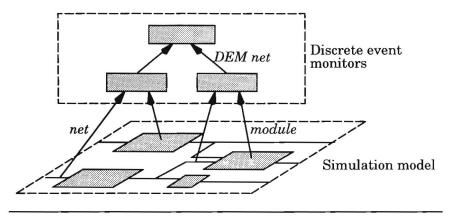

With ESCAPE, the operation of a system can be *animated*. The simulator provides the functionality to highlight objects on specific conditions and to annotate simulation data on the screen. Although animation reduces the performance of the simulator, it greatly improves the understanding of the operation of the system. It also improves the debugging capabilities of the tool, since the location of errors can be isolated easily. Furthermore, the concept of *discrete event monitors* is provided to better support the validation of complex systems: a discrete event monitor analyses the event trace of a simulation run and can abstract from unnecessary low level details.

ESCAPE deals with the specific demands for system level modelling and simulation: models of different domains can be combined in a single simulation model and the result is simulated in a homogeneous way. To accomplish this, various techniques are used:

• the use of different event types that manipulate the behaviour of the simulator;

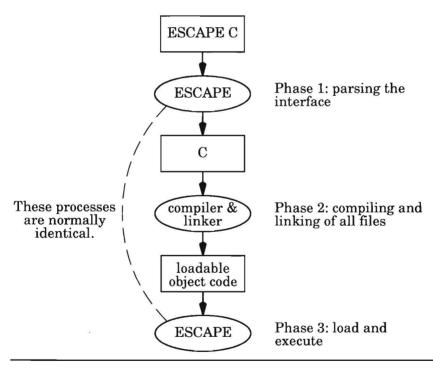

- the generation of code to embed models automatically into discrete event compatible models. The resulting model can contain a complete scheduler, which handles the event interface to the outside world;

- programmable simulation interfaces, through which an external simulator can be connected to the event driven simulator.

The same techniques are used to simulate partial implementations of a system: this may be required for analog subsystems and other critical parts of an electronic system. In principle, these techniques can be used for hardware software co-design as well (see section 1.4).

Currently, the behaviour of primitive modules can be described by

- a hardware description language based on the LISP [Ste84] language. Besides the statements found in other LISP languages, this language provides statements to define the animation of the system's components.

- programming languages like C and FORTRAN. A foreign language interface allows interactive and efficient simulation of compiled code models.

- a behavioural subset of VHDL as described in [Hou93].

- token flow models, in particular the ASCIS data flow graph.

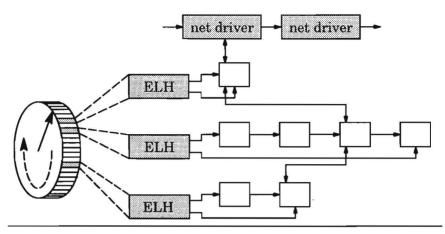

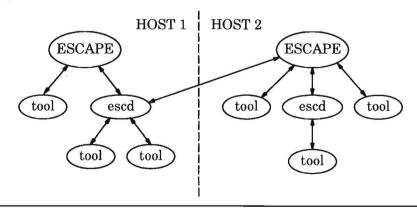

- models simulated by an external simulator. An external simulator interface provides the necessary means to use ESCAPE as a simulation backplane. Different models can possibly be executed on different machines in the network, but this only improves performance, if the overhead of communication costs is small with respect to the computational costs of executing the models.

The *tool interface* gives access to the API from the external environment. This interface can be used in both master and slave mode. In slave mode, ESCAPE is invoked by another tool, which sends a series of commands to ESCAPE to visualize output or to perform other tasks. In master mode, external programs or tasks are started through the user interface and the results are read back by ESCAPE. These results can again be visualized in one of its view windows. In master mode, different tasks can be scheduled simultaneously, either on the same workstation or on different workstations in the network. This interface can be used for various purposes and provides users with all the flexibility and customizability they need to integrate various tools with ESCAPE and to use the functionality of ESCAPE without additional programming effort.

### 1.3 Examples

In this section, two small examples are presented that give an impression of the capabilities of ESCAPE:

- a delay insensitive two-place one-bit ripple buffer;

- a 5 x 5 Conway's Game of Life board showing a glider pattern.

A delay insensitive circuit called RIPP2 [Ber92] is a two-place one-bit "ripple" buffer, which is composed of a number of basic components. The set of basic components has been defined in [Ber88] and can be used to compile any program written in Tangram into a delay-insensitive circuit. Tangram is a HDL based on Communicating Sequential Processes (CSP) [Hoa78].

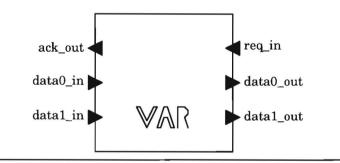

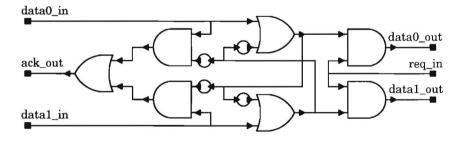

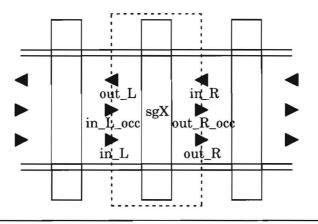

All basic components have been defined in ESCAPE as primitive modules. Defining a primitive module comprises of drawing a symbolic representation in the symbol view and editing a textual description representing the behaviour of the component. Some components have a more detailed implementation as well. For this example, the built—in LISP—like HDL has been used, which is described in more detail in appendix A. The basic component *variable* is depicted in figure 1.3 as an example.

Figure 1.3. Symbol view of variable.

The corresponding behaviour is:

```

(behaviour var

(term data0_in)

(term data1_in)

(term data0_out)

(term data1_out)

(term req_in)

(term ack_out)

(state value)

```

In this description, the statements, which are used to visualize the activity of the module during simulation, can easily be identified. The *color* statement will highlight the module, if one or more of the module's inputs are high. Otherwise, the module will have its default colour. The *write* statement draws the current value of the state variable *value* in the module.

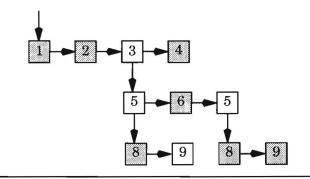

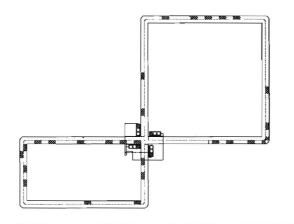

The implementation of this component can be modelled in the network view as well (see figure 1.4): the designer may choose to expand an instance of design variable and simulate its implementation instead of its behavioural description. For debugging purposes, a lower level implementation can be shown in a separate view window.

Figure 1.4. Implementation of basic component variable.

The next example is a network representing a world consisting of 25 cells of Conway's Game of Life [Gar70, Gar71]. This game is considered to be a cellular automaton: each cell of the automaton exchanges information with its 8

)

neighbours. Each cell has a state variable that indicates if this cell is alive or dead. The following rules are applied to each cell of the automaton:

- a cell will be alive in the next generation, if exactly three of its neighbours are alive in the current generation;

- a cell will stay alive in the next generation, if two or three of its neighbours are alive in the current generation;

- if none of the rules above applies to a cell, it will starve in the next generation.

Depending on the starting pattern of alive cells on the board, new generations will be generated from it. Some patterns are known to move itself along the board forever (e.g. gliders and fishes), other patterns oscillate with a specific period of generations before the orignal pattern is generated again. Large patterns have been developed for this type of cellular automaton. Examples are *blockpushers* and large *ships* having satellites. These patterns consist of numerous smaller patterns.

The behaviour of each life cell is described as follows:

```

(behaviour life_cell

"Conway's game of life. description of 1 cell."

(term nw_in) (term nw_out)

(term no in) (term no out)

(term ne in) (term ne out)

(term ea in) (term ea out)

(term se in) (term se out)

(term so_in) (term so_out)

(term sw in) (term sw out)

(term we in) (term we out)

(term init) ; used to set initial state

(term clk); global control

(state alive) ; holds state of cell: alive or death

(local count); counts number of living neighbours

(if (= (simtime) 0) ; initialize state

(setg alive init))

(color alive); color cell according state

(if clk

(progn ; determine new state of cell

(setq count (+ nw in no in ne in ea in se in so in sw in we in))

(setq alive (or (= count 3) (and alive (= count 2))))

;; else

;; inform neighbours of this cell's current state:

;; refrain events: clock triggers evaluation

```

```

(delay 0 nw_out alive 1)

(delay 0 no_out alive 1)

(delay 0 ne_out alive 1)

(delay 0 ea_out alive 1)

(delay 0 se_out alive 1)

(delay 0 so_out alive 1)

(delay 0 sw_out alive 1)

(delay 0 we_out alive 1)

```

In the declaration section, the ports for communicating the state, the clock that controls the execution of the cell and the port that sets the initial state of the cell, are easily identified, as well as the state variable, that indicates its lifeness, and a local variable for counting the neighbours alive. The algorithm itself is straightforward: if the value of the clock rises to *high*, the rules of the game are applied to the cell using the values on its input ports. The result is communicated to the other cells using refrain events: these events do not cause the cell to be evaluated. Instead, if the value of the clock falls to *low*, the evaluation of all life cells is triggered.

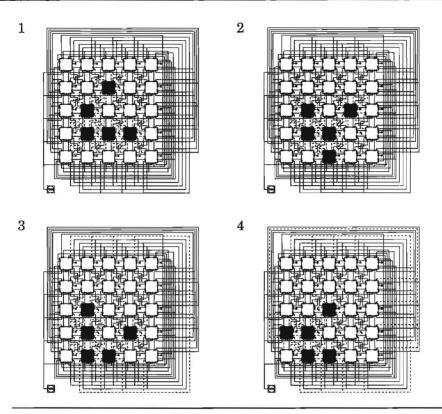

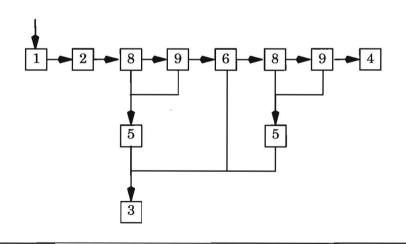

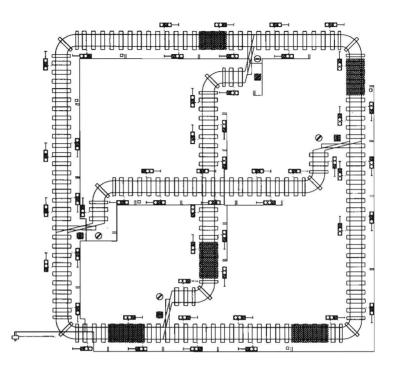

Using a small world consisting of  $5 \times 5$  cells, a glider pattern is initialized in the first generation. During simulation, the state of each cell is animated on the screen: the glider pattern starts to move from cell to cell, while it is rotating around. Some snapshots of this animation are presented in figure 1.5.

Larger worlds having more life cells have been developed as well. The underlying structural models for these examples have been generated using a special purpose program for placement and a routing program for schematics. Examples are:

- a 18 by 11 world starting with a oscillator as initial generation. This oscillator has a cycle of 16 generations;

- a 80 by 30 world starting with multiple glider patterns as initial generation.

The simulation speed for these examples is dependent on the number of cells, and it is not dependent on the total number of cells alive because in each cycle all cells are evaluated. The evaluation of a cell is triggered by the clock signal, which is an input of every cell. The behaviour of a model of which the speed mostly depends on the number of cells alive would be more complicated.

### 1.4 Related work

The functionality offered by ESCAPE has overlap with various kinds of systems. The most important one is Ptolemy. Simulation backplanes and mixed-level simulators are other types of simulators, which have some overlap. Another

)

Figure 1.5. Animated simulation of Conway's Game of Life.

category of systems are development systems for DSP applications, which are readily available on the market. These and some other types of tools are explained in more detail in this section.

Ptolemy [Buc94] is a framework to capture and validate heterogeneous systems. It is focussed towards designing signal processing and telecommunication systems, but is used in other application areas as well. Ptolemy is based on an object-oriented programming paradigm. It consists of a kernel on top of which different models of computation (called domains) can be used. Among others, the following domains can be used: synchronous data flow, dynamic data flow and discrete event. Ptolemy has also been used for hardware software co-design: a dedicated simulator for a DSP microprocessor has been coupled to the system [Kal92]. If such a simulator would be available in public, such a simulator could easily be coupled to ESCAPE as well.

In Ptolemy, there is one top-level view of a simulation model. It is called the Universe and has a domain associated with it. The Universe contains a number of computational blocks, which operate in the same domain. These blocks are called Stars. Stars are interconnected, which allows the transfer of data between them. In addition, the Universe contains a scheduler, which controls the execution order of these blocks. Models of other domains can be included in the Universe using a so called Wormhole, which behaves like a regular star. A Wormhole interfaces the foreign domain with the domain of the Universe using an interface called the EventHorizon. Each domain provides an interface to this EventHorizon.

In Ptolemy, different domains are hierarchically nested. Each foreign domain has its own scheduler, which controls the execution of the stars in this domain. During simulation, the current simulation time is known to all schedulers. Combined with a conservative scheduling approach, no deadlock can occur in the coordination of the various schedulers. However, this approach may restrict the feedback of inner domain particles to the outer domains or have a significant performance penalty.

The Simulator Coupling System (SiCS) [Nie92, Ocz91], is a simulation backplane, which can be used to simulate systems composed of different models of computation. SiCS consists of a coupling kernel and a user interface. Unlike ESCAPE, SiCS itself provides no support for simulating models of computation. SiCS contains a procedural interface for the interfacing between a simulator and the simulation kernel. This interface contains various functions for signal administration, signal manipulation and simulation control and enables the coupling of external simulators to the backplane. In [CFI94], a draft proposal for a standard on simulation backplane programming interfaces is described. In this document, much attention has been paid to the data types and the representation of values, the synchronization of the simulators, the user interface, and the resolution and conversion functions.

As opposed to a simulation backplane, other examples of multi-domain simulators are various mixed-mode simulators, which have been developed in the last decade. An overview of many mixed-mode simulators is given in [Sal90]. A mixed-mode simulator is oriented towards simulation at various well-defined levels of abstraction in order to reduce the computational complexity of simulating large systems. The main difference between these simulators and a simulation environment like ESCAPE, is that they do not provide the functionality to integrate new domains or levels of abstraction within the system, especially if the simulation paradigm is not event-based. This often implies that the integration of a new model of computation results in the development of a (partly) new simulator. An example of this are the various derivations of the ELDO simulator [Hen85], of which VHDL-ELDO is the latest one [Tah93]. STATEMATE<sup>™</sup> [Har90] is a design framework, which can be used to specify and validate reactive systems. The design methodology is based on three graphics formalisms: module charts, activity charts and statecharts. Module charts represent the structural view of the system; this is analogous with structural descriptions in other tools, like the network view in ESCAPE. Behaviour is described using both activity charts and statecharts. Activity charts are used to specify the functional behaviour of components used in the module charts. The interaction between these components or, in other words, the specification of the control activities is described by statecharts [Har87].

Statecharts are a graphics formalism that offer some extensions to the FSM formalism to facilitate the description of complicated control activities. To reduce the complexity of this task, hierarchy is allowed by repeated decomposition of states into substates. Another difference is that the thread of control of a statechart is not necessarily sequential. Furthermore, statecharts allow broadcasting of messages to apply actions to multiple states, e.g. a reset.

STATEMATE is a good example of the fact, that visual formalisms are getting more important and that they gain in popularity. This effect is reinforced by the development of workstations with powerful graphics capabilities and the standardisation of graphics libraries. Like with ESCAPE, it is possible to animate the operation of the system in STATEMATE. The specification of the system can be analysed interactively or in batch mode. Various debugging commands are provided to control the execution of the model.

Related to the work described above is the SpecCharts language [Vah91]. used for specific system level synthesis tasks like partitioning and interface synthesis. The language is based on hierarchical and concurrent state diagrams (comparable to statecharts) and is extended with VHDL based constructs.

In [Hoe92], a design system for the specification and implementation of digital signal processor arrays is described. In this system, different applications like a network editor and a simulator are sharing a common data structure. A communication mechanism is used to notify other (passive) applications of modifications in the state of the system (caused by the execution of an application).

Visual hardware description languages are another example of design capture systems, which rely heavily on graphics. In [Gol93], a visual language for VHDL is described consisting of a graphics editor and a compiler that translates the graphical descriptions into a textual VHDL description for analysis and simulation purposes. Visual HDLs are also available commercially and often consist of graphical design capture, simulation and code generation tools. The graphics formalisms are often derivatives of FSM, flowchart and block diagram approaches. The output of such systems is a description in a standard HDL like VHDL or Verilog, which serves as input for other simulation and synthesis tools. The HDL code generation offered by these tools is tailored for commercially available synthesis tools. In general, these systems lack the extendibility of a system like ESCAPE. A designer is restricted to use the graphical languages provided by the system and can't include other models of computation.

### 1.5 Outline of this thesis

In chapter 2, the capabilities of the discrete event simulator are discussed in detail. It is also explained how the design cycle (edit – elaborate – simulate – analyse) time is reduced by applying incremental techniques and run-time analysis techniques. In chapter 3, various approaches are discussed that allow simulation of multiple models of computation and models at various abstraction levels by the discrete event simulator.

Throughout chapters 2 and 3 examples and experimental results are used to illustrate the various concepts and approaches applied in the prototype ES-CAPE. In chapter 4, some additional examples are given that illustrate the flexibility, modelling capabilities and performance of the simulation environment.

In chapter 5, some additional features of ESCAPE are described. It shows how it is customized and integrated with other tools in the design flow. Finally, some concluding remarks are made on this research project and some suggestions are proposed to extend the prototype tool and to apply the techniques and concepts described in this thesis to other simulators.

### Chapter

## 2 Event driven simulation

### 2.1 Introduction

Simulation is widely being used to validate the functionality and the performance of a description of a system under design at various levels of abstraction. At each level, a simulator meets different requirements with respect to model size, level of detail of the models and computational costs. The following levels are distinguished:

- System level. At this level, a system is described as a number of interacting components, which are described by a model of computation or a behavioral description. Subsystems may be of different nature: digital hardware, analog hardware, firmware or software components.

- Architectural or functional level. The function of a (sub)system is described as an algorithm, which receives data from its environment and issues data to its environment after calculation. Descriptions at this abstraction level often serve as the input specifications for architectural synthesis tools.

- Register Transfer Level (RTL). The system is modelled as a datapath and a controller. The datapath consists of computational blocks, multiplexers and registers. Data is read from the registers and fed to the computational blocks. After calculating the resulting output values, these values are transferred back to the registers. The multiplexers are used to direct the flow of data through the system. The controller is a finite state machine (FSM), that specifies how the data is transferred in each state.

- Logical level (gate level). The following classification is used for models at this level: combinational logic, sequential logic and asynchronous logic. Sequential logic can be handled in a similar way as combinational logic by cutting the nets at the flip-flops creating new inputs and outputs. Much research has been conducted at this abstraction level to increase the performance of logic simulation: optimization of the simulation algorithm for specific delay models, parallel logic simulators [Mat92] and hardware accelerators [Sas83, Bla84]. Note that raw simulation speed is not always the most important aspect of a simulator. A software implementation may be indispensable for debugging the model and may complement the use of a hardware accelerator [Bee90]. Many of the simulation techniques that have been developed for this abstraction level are being applied to higher

levels of abstraction as well, for instance hardware acceleration at the RTL [Tak90] and distributed simulation at the behavioural level [Gho95].

- Switch level. This level is used to model digital circuits as a network of nodes and transistors. Each transistor represents both a switch and a attenuator. At this abstraction level, many aspects MOS circuits can be modelled quite accurately. However, the computational costs are small compared to simulation at the circuit level. Examples of switch level simulators are MOSSIM II [Bry84] and COSMOS [Bry87]. In [Gen86], the model is refined using a network of switches, capacitors and resistors. In this model, analog values instead of a set of discrete values are used to model the strengths of the components. This enables to simulate a model fairly detailed with respect to timing aspects.

- *Circuit level (electrical level)*. The model of a system is a set of differential equations, which are composed from the model equations of each component and from Kirchhoff's voltage and current laws. To simulate this model, the DC solution and the transient solutions have to be calculated from these equations. Simulation at this level produces the most detailed results. However, it is also most expensive with respect to computational costs. Spice [Nag75] and its numerous derivatives symbolize simulation at this abstraction level.

At various levels of abstraction, VHDL and Verilog are used as the standard hardware description languages. For these languages, many simulators are commercially available from various CAD tool vendors. Models written in these languages can be simulated together as well: this is referred to as *co-simulation*. There are also hardware accelerators available for VHDL simulation as well as techniques for parallel simulation [Vel92].

Simulation models at all abstraction levels can be divided in two classes: time discrete and time continuous models. The definitions are given below:

| <b>D</b> EFINITION 2.1: | A time discrete (simulation) model is a model of which the (simulation) state can only change at a <i>countable</i> number of time points.      |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| DEFINITION 2.2:         | A time continuous (simulation) model is a model of which<br>the (simulation) state changes continuously with respect<br>to the simulation time. |

Discrete and continuous models differ in the following ways:

The simulation time in a discrete simulation model is in general represented by an integer number, whereas the simulation time in a continuous simulation model is represented by a floating point number. In a continuous simulator, the simulation model is often described using differential equations; in a discrete simulator, the model is composed of executable components, that are invoked by a scheduler. Events are used to model activity in such models. In this thesis, the term *discrete event simulation* refers to models, that are simulated by an event driven or a similar simulation algorithm, (e.g. a compiled simulator, see section 2.3.1).

This thesis primarily focuses on simulation of models at the register transfer level and higher levels of abstraction. These models are mostly modelled using a time discrete model. Models without an explicit notion of time and models of partial implementations at lower level of abstractions can be combined with time discrete models as well. Therefore, we restrict ourselves to discrete event simulation.

### 2.2 Simulation models

Systems are composed of computational blocks. These blocks are connected with each other by nets. Nets are used to communicate values from one computational block to others. A system S is described with the 7-tuple:

$$S = (\mathcal{M}, \mathcal{N}, \mathcal{P}, \mathcal{B}, P_{\mathcal{M}}, P_{\mathcal{N}}, M_{\mathcal{B}})$$

(2.1)

where

- $\mathcal{M}$  is the set of modules or components.

- $\mathcal{N}$  is the set of nets or signals.

- $\mathfrak{P}$  is the set of ports. This set contains both primary input and output ports of the system, and the input and output ports of the modules.

- B is the set of behavioural descriptions.

- $-P_{\mathcal{M}}: \mathfrak{P} \to \mathcal{M} \cup \{ \emptyset \}$  is a function that maps each port to a module. In case  $p \in \mathfrak{P}$  is a primary port,  $P_{\mathcal{M}}(p)$  will return empty.

- $P_{\mathcal{N}}$  :  $\mathfrak{P} \to \mathcal{N}$  is a function that maps each port to a net.

- $M_{\mathfrak{B}}$  :  $\mathcal{M}$  →  $\mathfrak{B}$  is a function that assigns a behavioural description to each module.

The system model of S in (2.1) describes a structure. To complete this model, each module requires a behavioural description. The term *computational block* is used for a module, which has a behavioural description associated with it. A behaviour  $B \in \mathfrak{B}$  is described with the 5-tuple

(2.2)

B = (I, O, Q, init, exec)

where

- / is the set of input ports.

- O is the set of output ports.

- Q is the set of state variables (memory elements).

- init is a function that calculates the initial values of all state variables,

- exec is a function that calculates the values of the output ports for a time point greater or equal than the current time point from the values of the input ports and the values of the state variables. The new values of the state variables are calculated from the values of the input ports and the current values of the state variables as well. Time may also be used in the function to account for time-dependent behaviour.

The exec function calculates the new values of the output ports at future time points. Note that more than one value may result from this calculation. However, the number of values produced should be finite. Otherwise, the function exec will not terminate after activation of the behavioural model. This leads to an erroneous condition during simulation, if more components need to be activitated, which is usually the case.

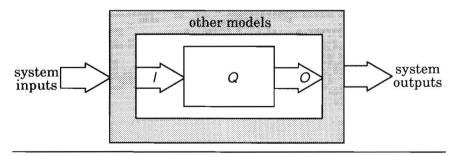

The behaviour of each module of (2.1) is described using (2.2). The inputs and outputs of behaviour *B* correspond with the ports of the module it is assigned to. An input gets its value from the net, that is connected to the corresponding port of the module. An output drives the net, that is connected to the corresponding port of the module. In figure 2.1, it is depicted how a module interacts with its environment. The behaviour of a module is executed or simulated, if activity occurs at one or more of the module's inputs.

Figure 2.1. The execution of a model in its environment

A behaviour described using (2.2) closely resembles the description of a finite state machine. However, there are some differences:

- The data types associated with *I*, *O* and *Q* are not necessarily finite. The type of an element of these sets may for instance be a boolean, a natural number, a floating point number or some abstract data type.

- The model may have internal non-determinism. Even if a model has internal non-determinism, still its overall behaviour may be deterministic: the relation between the values at the input and output ports may still be deterministic.

- The behaviour may be dependent on time. Although it is not explicitly represented in (2.2), the *exec* function takes time as an argument.

Finally it should be noted that notation (2.1) does not account for hierarchical descriptions. This is not necessary, since its purpose is to represent a valid simulation model. It does not describe how the model is composed from a hierarchy of structural and behavioural descriptions! This is part of the internal representation of the tools used. The model that is actually simulated is represented by this notation. In section 2.9, it is explained in detail, how hierarchy can be dealt with.

### 2.3 Discrete event simulation

Discrete event simulators can be classified with respect to their overall simulation approach and their time advance mechanism. Depending on the type of models to be simulated, they determine its accuracy and performance.

### 2.3.1 Simulation approaches

Various approaches can be used to simulate a discrete model:

- *Event driven simulation*. A component of the system is evaluated depending on the activity in the system. Activity is expressed by events, which denote value changes in the simulation model.

- Demand driven simulation. An alternative approach to event driven simulation is demand driven simulation [Smi87]. This approach may reduce the number of component evaluations compared to event driven simulation, because demand driven simulation propagates requests for simulation values backwards through the circuit and through time. Event driven simulation propagates simulation values forward through the circuit in response to input port events.

- Oblivious simulation. All components of the system are evaluated at every time point. The execution order of the components is determined statically

and can be used to compile the simulation model. Therefore, oblivious simulation is often referred to as *compiled simulation*.

- Process (interaction) oriented simulation. All components of the system are executed independently and communicate with each other using events. Events, which are local to a component, are isolated from events occurring in other components and can be executed in arbitrary order. Communication between components leads to synchronization.

- Cycle-based simulation. In a cycle-based simulator, all components are evaluated at clock boundaries and there is no notion of time. Cycle-based simulators are used because of their high simulation performance for functional validation of synchronous designs. Traditionally, they can not support all features as provided by a popular popular hardware description language like VHDL. Often, they are used in conjunction with an event driven simulator to be able to support all design methodologies and styles, for instance asynchronous designs.

### Event driven simulation versus oblivious simulation

The advantage of using event driven simulation instead of oblivious simulation is its flexibility:

- an event driven simulator handles both synchronous and asynchronous circuits or systems. In [Wan90], a technique is described that is able to compile asynchronous circuits by identifying strongly connected components in the circuit description;

- an event driven simulator handles multi-delay models, whereas most oblivious simulators can only simulate zero or unit delay models [Mau92];

- an event driven simulator handles different delay models. More specific, the possibility to cancel events scheduled for future time points, allows the simulation of more complex delay models;

- an event driven simulator reduces the number of component evaluations, which is dependent on the activity in the system under simulation.

Although an event driven simulator avoids unnecessary component evaluations, the overhead of managing and processing events reduces its efficiency. In general, compiled simulation is getting more efficient compared to event driven simulation with an increasing level of activity in a system. For logic simulation, activity levels of about 1% have been reported [Bar87]. In this case, the complexity of the behavioural descriptions of the components is very low and therefore the overhead of scheduling and processing events is relatively high. At higher levels of abstraction, event driven simulation is preferred because of its flexibility. The overhead of event scheduling and processing is reduced because of the complexity of the behavioural descriptions.

Computer hardware plays also a dominant role in the trade-off between event driven versus oblivious simulation. The performance of microprocessors is getting higher and higher every year. A compiled simulator can better exploit a cache in a computer architecture than an event driven simulator. Therefore, the use of a compiled simulator is getting more attractive with the progress in processor technology.

### Process oriented simulation and process modeling

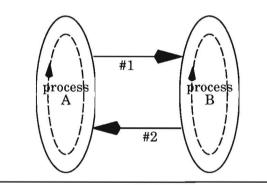

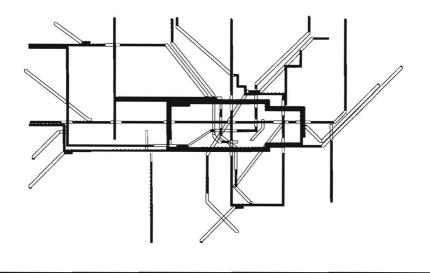

Process oriented simulation provides a higher conceptual view on the system and reduces the complexity of developing simulation models for large systems: each component in the model is considered as a separate process, which interacts with its environment. In figure 2.2, a process oriented simulation model is depicted with two processes, that are communicating with each other. Process A and B run independently. Each process executes its task: such a task is a repetition of a number of subtasks.

Figure 2.2. Process oriented simulation model

The behaviour of the processes is synchronized, if communication takes place between A and B. If process A is executing faster than process B, at some time point message #1 will be sent to B and A continues with its task. After a while, process A has to be suspended, because it requires a message from B. At some point in time, B requires a message from A, and detects its reception. B can immediately continue processing. After some time message #2 will be sent to A. After reception of this message, A can resume processing its own task.

Process oriented simulation can be emulated using an event driven simulator based on a scheduling technique. It is also possible to model various process

networks and communication channels, that can be simulated with an event driven model. An example of a process network with communication channels modelled in VHDL is described in [Sri92]. In [Rou89], VHDL is viewed as a process oriented simulation language. In general, a process oriented simulation model can be mapped onto an event driven simulation model, if each process cycle has at least one synchronization point, where it is suspended: this is the point, at which the process synchronizes with its outside environment. Otherwise, the process will not terminate after activation. This is not a requirement in a process oriented simulator: the simulator itself suspends and activates the processes of the model.

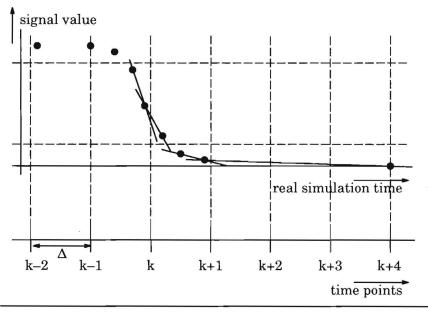

#### 2.3.2 Time advance mechanisms

Another important aspect of a discrete event simulator is the time advance strategy: two strategies can be used to advance the simulation time: fixed-increment time advance or next-event time advance. Using a fixed-increment time advance strategy, events are processed at equidistant points in time. Each event is scheduled at a time point, that is an integer multiple of some time constant  $\Delta$ . The length of the interval between two time points influences the accuracy and the performance of the simulator. With a next-event time advance, events can be scheduled and processed at arbitrary points in time. Especially for detailed models, this approach has to be used to guarantee accurate simulation results.

Note that a fixed-increment time advance strategy is a special case of the next-event time advance. If events are scheduled with delays, which are an integer multiple of some time interval, the performance of the simulator is increased using a fixed-increment time advance strategy: it reduces the time to insert a newly scheduled event in the event queue.

A fixed-increment time advance does not impose any restriction on the time interval that is associated with  $\Delta$ : this is an issue during the development of the simulation model. A proper choice of  $\Delta$  can increase the performance of the simulator. This will be explained later in this chapter.

# 2.4 Event driven simulation

An event driven simulation algorithm provides the flexibility required to control various types of computional models. Events also provide with an easy means for interaction between the simulator and its environment. In this thesis, the following definition is used:

**DEFINITION 2.3:** An *event* models a future change of a simulation variable.

An event E is described with the 6-tuple:

$$E = (time, insert, type, object, value, data)$$

(2.3)

where

- time : the time point an event is scheduled for.

- *insert*: the insertion time of the event. It is used to order all events that are scheduled for the same time point. The implementation normally ensures a proper order of events scheduled for the same time point: this attribute is only used to describe this order. In this thesis, it is assumed that all events scheduled for the same time point are ordered using this attribute.

- *type* : the type of the event, which determines, how the event will be processed.

- *object* : the object in the model of (2.1) the event is scheduled for. This object is either a net, a module or a port.

- value : the value the object will be set to, when the event is processed.

- data : an additional data field needed for particular types of events.

# 2.4.1 The simulation state of the system

Let  $Q_m$  be the set of state variables, that are associated with the behaviour of a module m in (2.1). Let N be the set of *variables* associated with the nets of (2.1). Then V represents the set of all state variables in the model:

$$V = N \cup \left( \bigcup_{m \in \mathcal{M}} Q_m \right)$$

(2.4)

Note that the subsets, that compose V are disjoint. Let  $L_V$  be a mapping from the state variables to a value domain D:

$$L_V: V \to D \tag{2.5}$$

In case of all simulation variables are of type integer, the range of  $L_V$  would be N. Because the simulation variables may be of different types, the range of  $L_V$  is not defined explicitly.

Let  $E_D$  be the set of all events, that are defined using tuple (2.3). The *powerset* of  $E_D$  is defined as

$$P(E_D) = \{ x \mid x \subseteq E_D \}$$

$$(2.6)$$

Let  $E_q$  be a set of events

$$E_q = \{ e_1, e_2, ..., e_n \} \in P(E_D)$$

(2.7)

$E_q$  represents the set of events that are scheduled at a particular simulation time point  $t_k$ . Thus  $\forall e \in E_q$ : time(e)  $\geq t_k$ . The time and insert attributes of the events in this set induce the ordering of the elements of  $E_q$ .

The simulation state of the system is then the tuple:

$$(L_V, E_q) \in (V \rightarrow D) \times P(E_D)$$

(2.8)

At the start of a simulation run, the state is initialized by executing the *init* functions of all behaviours and by setting the values of all nets. Note that this function merely sets the values of all state variables. Then, the *exec* functions of all modules is called: this schedules the events, which will be processed in the first simulation cycle.

Initialization results in the initial simulation state  $(L_0, E_0)$ .

After initialization, the simulation state is updated each simulation cycle. Let  $(L_k, E_k)$  be the simulation state after k simulation cycles. First, the events are selected from  $E_k$ , that must be processed in the current cycle. This is a partitioning of  $E_k$  into two disjoint sets  $E_{sel}$  and  $E_{next}$

$$E_{sel} = \{ e \in E_k \mid \forall e' \in E_k : (time(e) \le time(e')) \}$$

$$(2.9)$$

and

$$E_{next} = E_k \setminus E_{sel} \tag{2.10}$$

Then the events of  $E_{sel}$  are processed in order – the *insert* attribute is used to determine this order. This results in the generation of new events and a modification of a subset of V. The new simulation state is then  $(L_{k+1}, E_{k+1})$ .  $E_{k+1}$  contains the union of  $E_{next}$  and the newly created events.