# The proceedings of the first international symposium on Visual Formal Methods VFM'99, Eindhoven, August 23rd, 1989

Citation for published version (APA):

Bosnacki, D., Mauw, S., & Willemsé, T. A. C. (Eds.) (1999). The proceedings of the first international symposium on Visual Formal Methods VFM'99, Eindhoven, August 23rd, 1989. (Computing science reports; Vol. 9908). Technische Universiteit Eindhoven.

## Document status and date:

Published: 01/01/1999

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 04 Oct 2023

# **Preface**

These are the proceedings of the Visual Formal Methods – VFM'99 symposium, held on August 23rd 1999 in Eindhoven, The Netherlands.

The idea behind Formal Methods has always been to have methods allowing for unambiguous, mathematically precise descriptions of a system, supporting formal analysis. However, the appearance of a Formal Method is often based on its underlying mathematical theory, which, although intuitive to the people specialised in this particular Formal Method, is not particularly intuitive to outsiders. Although the use of Formal Methods in the industry has been prophesied since their very dawn, reality learns that their acceptance is still not very wide-spread.

On the other hand, an increasing interest is showing nowadays directed towards visual languages. A reason for this trend is the fact that visual languages are much closer to the way in which people think when developing a system; their appearance is intuitive and they allow for expressing the relation between objects spatially, thus easing the understanding of descriptions.

Combining the strengths of both approaches will result in a formal and still intuitive approach to system design. Examples of such combinations already exist; visual languages with a formal semantics which allows for formal validation (e.g. Message Sequence Charts) and Formal Methods with a graphical interface. It looks as if in the last few years, the research community is taking up this challenge, and the combined use of Formal Methods and Visual Languages is becoming a topic of interest.

Taking up on this trend, it was decided in the group of Formal Methods at the department of Computing Science at the Eindhoven University of Technology, that a symposium on this topic should be organised. This symposium, christened Visual Formal Methods – VFM'99, linked to Concur'99 aimed at bringing together leading researchers and practitioners from the intersecting area of Visual Languages and Formal Methods.

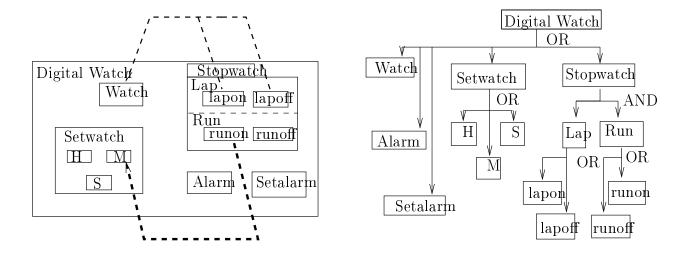

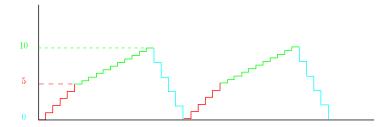

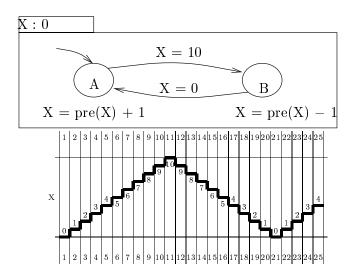

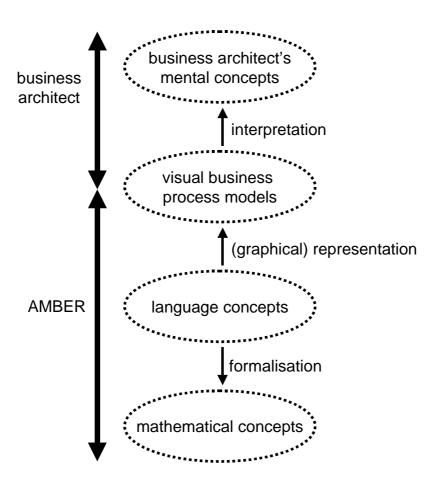

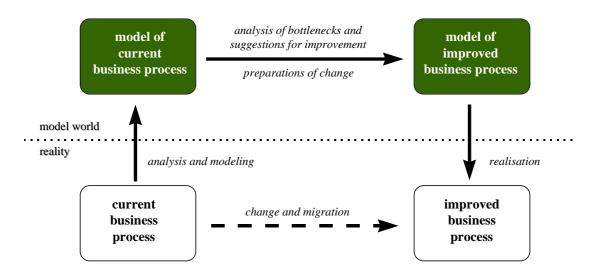

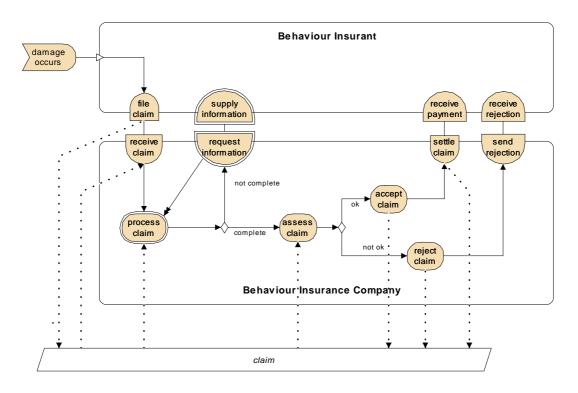

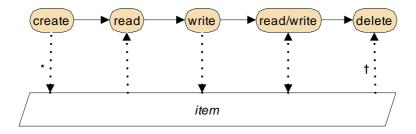

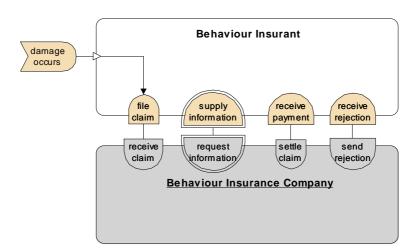

The area of Visual Formal Methods is rather broad but roughly it can be divided into two distinct areas. On the one hand, methods are being developed to deal with the architecture of systems. Often, the architecture, with the emphasis on software architecture, plays an important role in the development of software systems. Various methods for coping with the problems involved in systems' architecture are investigated, each emphasising different aspects of this area as is shown in "Formalization and Visualization of Software Architectures", which suggests how the module view of software architecture can be visualised and formalised. The presentation on "Object-Oriented Modelling and Specification using SHE" discusses a system level modelling language, POOSL, which is used to manage the intrinsic complexity of complex hardware and software systems. The use of a visual formal method is not limited to software architecture as is convincingly demonstrated in "Visualising business processes", which describes how the formal visual language AMBER is applied to business architectures.

On the other hand, research is directed towards the specification and analysis of the behaviour of complex software and hardware systems. First of all, languages itself are the subject of investigation, as is shown in "Composing Automata in Graphical Languages for Re-

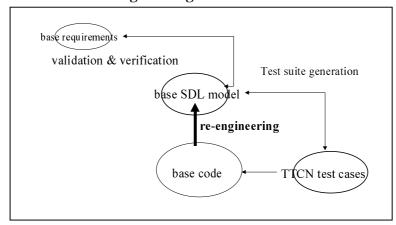

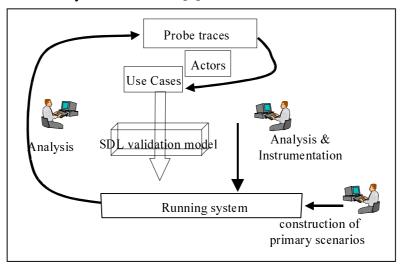

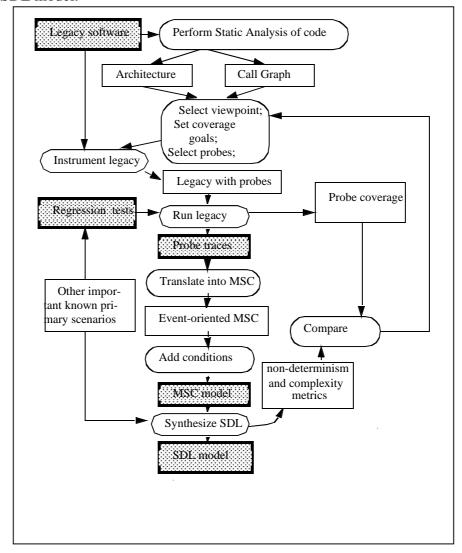

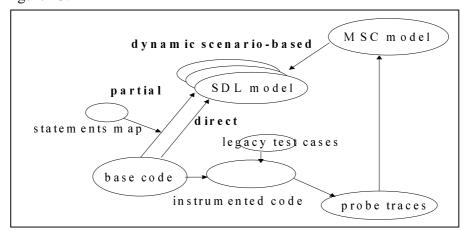

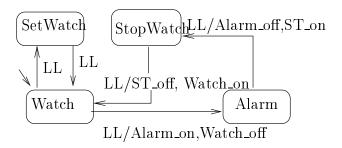

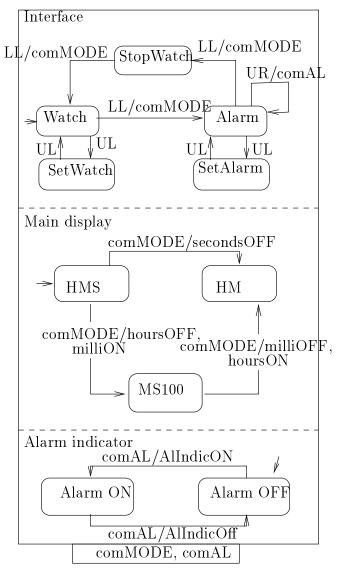

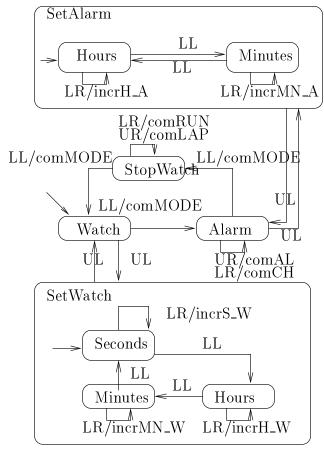

active Systems: from Argos to Mode-Automata". There, a graphical, synchronous approach to specifying reactive systems is explained. Secondly, development of tool support for the analysis and verification of systems is an important research area. In "Visual Temporal Logics as a Rapid Prototyping Tool" formal specifications in real-time symbolic timing diagrams are used for reliable and rapid prototyping. The presentations on "Automatic Synthesis of SDL from MSC in Forward and Reverse Engineering" and "uBET: Graphical Specification Support in an Industrial Environment" focus on the use of computer-aided software tools and the effects they have on the time-to-market.

We thank Desiree Meijers, Marcella de Rooij and Anne-Meta Oversteegen for their organisational assistance. For providing and setting up the required hardware and software support, BCF is thanked. Last but not least, we are grateful for the financial support by SOBU (the Co-operation Center of Tilburg and Eindhoven Universities) IPA (the Institute of Programming Research and Algorithmics, NL), and the Eindhoven University of Technology.

Dragan Bošnački Sjouke Mauw Tim Willemse August 1999 Eindhoven The Netherlands

# Table of contents

| Visual Temporal Logics as a Rapid Prototyping Tool                                                                   | 1   |

|----------------------------------------------------------------------------------------------------------------------|-----|

| Object-Oriented Modelling and Specification using SHE $\dots \dots \dots \dots \dots M.C.W.$ Geilen, $J.P.M.$ Voeten | 16  |

| uBET: Graphical Specification Support in an Industrial Environment $B.\ Knaack$                                      | 25  |

| Formalization and Visualization of Software Architectures $R.\ Krikhaar,\ L.\ Feijs,\ R.\ van\ Onnerink$             | 26  |

| Automatic Synthesis of SDL from MSC in Forward and Reverse Engineering $N.\ Mansurov$                                | 44  |

| Composing Automata in Graphical Languages for Reactive Systems: from Argos to Mode-Automata                          | 65  |

| Visualising Business Processes                                                                                       | 82  |

| P. Oude Luttighuis, M. Lankhorst, R. van de Wetering, R. Bal, H. van den B                                           | erg |

# Visual Temporal Logic as a Rapid Prototyping Tool\*

Martin Fränzle and Karsten Lüth

Carl von Ossietzky Universität Oldenburg

Department of Computer Science

P.O. Box 2503, D-26111 Oldenburg, Germany

{Martin.Fraenzle|Karsten.Lueth}@Informatik.Uni-Oldenburg.De

**Abstract.** As embedded systems become more and more complex, early availability of unambiguous specification of their intended behaviour has become an important factor for quality and timely delivery. Consequently, the quest for rapid prototyping methods for such specifications arises. Addressing these issues, the computer architecture group of Oldenburg University has devoted a major line of research towards automatic prototyping of embedded controllers from fully formal specifications given as real-time symbolic timing diagrams (RTSTDs, for short). RTSTDs are a graphical formalism for specifying behavioural requirements on hard real-time embedded systems. They are a full-fledged metric-time temporal logic, but with a graphical syntax reminiscent of the informal timing diagrams widely used in electrical engineering. Within this survey article, we will explain real-time symbolic timing diagrams as well as the ICOS tool-box supporting RTSTD-based requirements capture and rapid prototyping. ICOS integrates a variety of tools for RTSTDs, ranging from graphical specification editors over tautology checking and counterexample generation to code generators emitting C or VHDL, thus bridging the gap from specification to prototype generation.

#### 1 Introduction

Due to rapidly dropping cost and the increasing power and flexibility of embedded digital hardware, digital control is becoming ubiquitous in technical systems encountered in everyday life. Often, such embedded systems can hardly be altered once they have been shipped out due to extremely large quantities being shipped, or they even have to be right first time due to their crucial impact on safety of human life. For example, modern means of transport rely on digital hardware even in vital sub-systems like anti-locking brakes, fly-by-wire systems, or signaling hardware, as does medical equipment even in such critical applications as life-support systems or radiation treatment. As, furthermore, many

<sup>\*</sup> This article reflects work that has been partially funded by the German Research Council DFG under grant no. Da 205/5-1. A preliminary version of this article has been published as [6].

embedded systems are developed under tight time-to-market constraints, early availability of unambiguous specification of their intended behaviour has become an important factor for quality and timely delivery.

Such a specification is, however, always a compromise between various demands: ought it to be operational, in order to guide developers and programmers in the implementation phase, or ought it to be declarative in order to allow straightforward formulation of safety requirements, thus supporting safety analysis? Ought it to be formal, thus facilitating formal analysis and hence providing correctness guarantees that are not otherwise available, or may it be informal if this enhances comprehensibility, thus simplifying traditional approaches for ensuring quality of software, like testing and certification by code inspection?

Due to their prospects for reconciling some of these seemingly contradictory demands, graphical specifications have recently attracted much interest. Their prospects for gaining comprehensibility of even complex specification are deemed so high that it should be possible to simultaneously further the level of formality without sacrificing understandability. However, even with graphical specifications, the global interaction patterns of complex (for example, distributed) systems remain complex and, furthermore, it seems that graphical idioms also tend to hide some of the fine-grain semantics from the user, at least from the non-expert one. Thus, while being a big step ahead, graphical specification formalisms are not per se a means for ensuring that "what you specify is what you mean".

The problem of misconceptions in early development phases is, however, well-known in software engineering. A traditional remedy is rapid prototyping, where a partially developed product is brought into executable shape in order to assess its compliance with expectations. We suggest to take over the paradigm of "rapid prototyping" to the realm of formal, graphical, and declarative (i.e., essentially non-operational) specifications such that these become executable, thereby facilitating early evaluation of specifications on an operational model. If such a prototyping process is based on an unambiguous semantics of specifications and applies rigorous rules for deriving executables from specifications then it can, furthermore, be made sure that the prototype obtained is in strict correspondence with the specification such that the evaluation is faithful.

In this article, we propose a method of that kind: it builds upon a fully formal semantics of specifications and applies automata-theoretic constructions for fully automatically deriving operational systems that represent the specification in a "what you specify is what you get" way. The method has been developed and implemented by the computer architecture group of Oldenburg University, which has dedicated part of its rapid prototyping project 'EVENTS' [13] towards automatic prototyping of embedded control hardware from fully formal specifications given as real-time symbolic timing diagrams. Real-time symbolic timing diagrams (RTSTDs, for short), as introduced in [4], are a graphical formalism for specifying behavioural requirements on hard real-time embedded systems. They are a full-fledged metric-time temporal logic, but with a graphical syntax reminiscent of the informal timing diagrams widely used in electrical engineering.

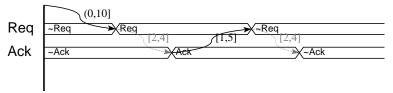

Fig. 1. An RTSTD specifying a simple handshaking protocol. The black arcs represent strong constraints, while weak constraints (i.e., assumptions on the environment) are printed in grey. The perpendicular line to the far left indicates the activation mode of the diagram, which here is the so-called invariant mode, meaning that the diagram has to apply whenever its activation condition fires. The activation condition is the state condition crossed by the perpendicular line, i.e.  $\neg \text{Req} \land \neg \text{Ack}$ .

In Sect. 2 and 3, we introduce real-time symbolic timing diagrams and give an overview over the ICOS tool-box supporting requirements capture and rapid prototyping using RTSTDs. As the ICOS approach to rapid prototyping is based on synthesis of embedded control hardware — in general, FPGAs — satisfying the specification, we then turn to game-theoretic methods of controller synthesis. Section 4 introduces the controller synthesis problem, and Sect. 4.1 outlines a classical controller synthesis framework based on the effective correspondence of propositional temporal logic to finite automata on infinite words and on the theory of  $\omega$ -regular games [18]. A compositional variant of this approach, which is more suitable for rapid prototyping purposes due to its reduced complexity, is shown in section 4.2. This is our current synthesis method, which has been fully implemented in the ICOS tools [10,12]. The results obtained using this method on e.g. the FZI production cell [11] indicate that the compositional extension yields a significant enhancement for reactive systems, yet a further compositional treatment of timing is necessary for real-time systems. Section 4.3 sketches the basic design decisions underlying such an extension which is currently being implemented for a new release of ICOS, while Sect. 5 compares this to the state of the art.

# 2 Real-time symbolic timing diagrams

The RTSTD language is a metric discrete-time temporal logic with an — as we hope — intuitive graphical syntax reminiscent of the informal timing diagrams widely used in electrical engineering, and with a declarative semantics which is formalized through a mapping to propositional temporal logic (PTL). In contrast to some other approaches using timing diagrams, e.g. those described in [1, 9], symbolic timing diagrams do not have any imperative control structure like iteration or sequencing. Instead, the recurrence structure of RTSTDs is expressed in terms of the modalities of linear-time temporal logic, thus providing a direct logical interpretation. In fact, RTSTDs provide a declarative rather than an operational specification style, even despite their intuitive syntax: an RTSTD is interpreted as a constraint on the admissible behaviours of a component, and

a typical specification consists of several small RTSTDs, with the individual constraints being conjoined. The main consequence is that RTSTDs are well-suited for incremental development of requirements specifications. However, they pose harder problems than more operational timing diagrams when used as source language for code generation. Fig. 1 shows an example RTSTD, specifying a simple handshaking protocol using two signals Ack and Req.

A basic<sup>1</sup> RTSTD consists of the following parts:

- An entity declaration defining the interface of the component (not shown in Fig. 1). It specifies the signals (e.g. Req, Ack), their data types (e.g. Bit) and access modes (in or out, i.e. being driven by the environment or the component, resp.).

- A set of waveforms (here Req, Ack). A waveform defines a sequence of Boolean expressions associated with a signal (e.g. ~Req, then Req, then ~Req in the upper waveform of Fig. 1). The point of change from validity of one expression to another is called an event. A distinguished activation event, which specifies a precondition for applicability of the diagram, is located to the left over the waveforms.

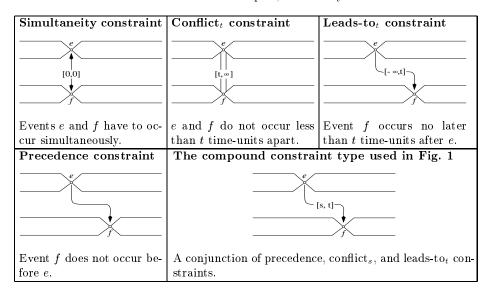

- A set of constraints, denoted by constraint arcs, which define a partial order on events. We distinguish between strong constraints and weak constraints. Strong constraints are those which have to be satisfied by the system under development, while weak constraints denote assumptions on the behaviour of the environment. Violation of a weak constraint implies that the remainder of the timing diagram poses no further design obligations. Table 1 summarizes the different kinds of constraints.

- An activation mode. Initial diagrams describe requirements on the initial system states whereas an invariant diagrams expresses requirements which must be satisfied at any time during system lifetime. Invariant mode corresponds to the 'always' modality of linear-time temporal logic, implying that

— in contrast to timing diagram formalisms employing iteration multiple incarnations of the diagram body may be simultaneously active if the activation condition fires again before the end of the body has been reached.

More details about syntax and semantics of RTSTDs are given in [4].

#### 3 The ICOS tool-box

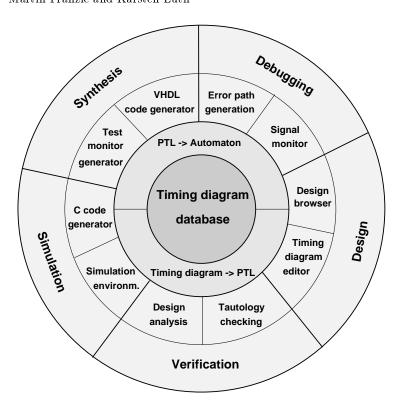

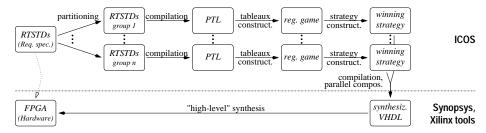

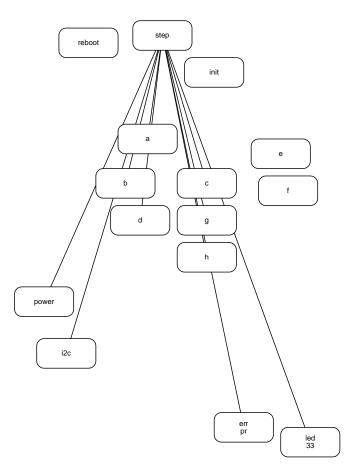

Despite the appealing graphical syntax of RTSTDs, specification of reactive systems using RTSTDs remains a challenging task. The ICOS tool-box, as shown in Fig. 2, is a comprehensive set of tools that supports this process [5, 10, 12]. ICOS is built around a timing diagram database that holds all specification clauses belonging to the current project. The database is augmented by a layer of procedures for compiling RTSTDs to other effective representations of reactive behaviour, like propositional temporal logic (PTL) [14] or Büchi automata

<sup>&</sup>lt;sup>1</sup> there is some syntactic sugar available for making large specifications more concise.

**Table 1.** Basic strong constraint types of symbolic timing diagrams and a compound constraint. Each of these has a weak counterpart, denoted by a shaded constraint arc.

[18]. These procedures, as well as the corresponding derived representations of reactive behaviour, are in general hidden from the user. Instead, they are invoked (resp., constructed) on the fly whenever a particular representation is needed for some user-selected task (e.g., for code generation).

User-selectable activities are concerned with design, verification, simulation, synthesis, and debugging. Design-related activities involve creating and editing RTSTDs with a graphical editor, as well as browsing the specification database. Verification entails static analysis, for checking whether interfaces are consistently used, and automatic tautology checking, for formally verifying that some refined specification satisfies the original commitments of the design task. Simulation is performed upon a keystroke by first generating a finite automaton faithfully reflecting the semantics of the specification, then encoding it in the C programming language, and finally linking it to a simulation environment, thus facilitating interactive simulation of specifications. The intermediate steps involved do, however, not require any user interaction.

Simulation shares most of the basic technology with synthesis. Synthesis goes however a bit further in that it actually yields an FPGA-based embedded control device that can be plugged into the application context rather than just an interactive simulation. The steps involved are, first, the generation of a set of interacting Moore automata satisfying the specification, second, their translation to synthesizable VHDL code, and third, synthesis of a corresponding FPGA. We will expand on the techniques underlying synthesis in the next section, as embedded controller synthesis forms the backbone of our rapid prototyping method.

Fig. 2. The ICOS system

Test monitor generation is a minor variant of this synthesis process which yields an FPGA that does not control its application context, but instead may be plugged into the application context as an online monitor, then monitoring the running system for violations of the specification.

Debugging, finally, yields error paths pinpointing the problem whenever synthesis fails due to a contradictory (and thus unimplementable) specification, or if tautology checking finds a non-tautology.

## 4 Synthesis

Automatic synthesis of FPGA-based controllers is the core of our rapid prototyping method for RTSTD specifications. The application scenario is that the user invokes an *fully automatic* synthesis procedure once the requirement set, being formalised through RTSTDs, is deemed sufficiently complete. The synthesis algorithm then tries to construct an FPGA-based embedded controller satisfying the specification — i.e., an operational prototype — or, if it detects unimplementability of the specification — delivers diagnostic information.

In fact, the synthesis method is a three-step procedure: first, the synthesis algorithm tries to construct a Moore automaton satisfying all stated requirements. However, no appropriate Moore automaton need exist due to a contradictory specification in which case the algorithm creates error paths to help the programmer refine the specification. Otherwise, the second step can commence, where the generated Moore automaton is automatically translated to VHDL code. The subset of VHDL used as target language is synthesizable by the Synopsys tools [7] such that the final step of actually implementing the automaton by a given target technology (e.g. FPGAs) can be done through so-called high-level synthesis by the Synopsys tools [7], and we have indeed integrated our tools with the Synopsys and some Xilinx tools to achieve this.

As high-level synthesis is by now an industrially available technology, we will in the remainder of this article concentrate on the first step and will sketch different specification-level synthesis procedures yielding sets of interacting Moore machines from RTSTD specifications. The procedures differ in the methods used for dealing with timing constraints and in the number and shapes of the interacting Moore machines generated, which affects the average-case complexity of the synthesis procedure and the size of the hardware devices delivered.

Given a specification  $\phi$ , the problem of constructing a Moore automaton satisfying the specification, called the *synthesis problem*, is to find a Moore automaton  $A_{\phi}$  which is

- 1. well-typed wrt.  $\phi$ , i.e. has the inputs and outputs that the entity declaration of  $\phi$  requires, and accepts any input at any time (i.e., only the outputs are constrained),

- 2. correct wrt.  $\phi$ , i.e. the possible behaviours of  $A_{\phi}$  are allowed by the specification  $\phi$ , formally  $\mathcal{L}_{A_{\phi}} \subseteq \mathcal{M}[\![\phi]\!]$ , where  $\mathcal{M}[\![\phi]\!]$  is the set of behaviours satisfying  $\phi$  and  $\mathcal{L}_{A_{\phi}}$  is the set of possible behaviours of  $A_{\phi}$ .

By adoption of logical standard terminology, an algorithm solving the synthesis problem is called sound iff, given any specification  $\phi$ , it either delivers an automaton that is well-typed and correct wrt. the specification  $\phi$ , or no automaton at all. It is called complete iff it delivers an automaton whenever a well-typed and correct automaton wrt. the specification exists.

#### 4.1 Classical controller synthesis and RTSTDs

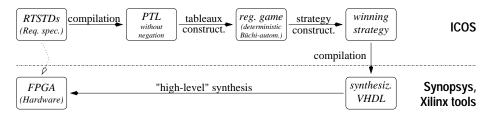

If the requirements specification language is a classical, non-graphical, discrete-time temporal logic, like propositional temporal logic (PTL) [14], then algorithms for solving the synthesis problem are well-known: there is an effective mapping of these logics to infinite regular games which, together with the firmly developed theory of strategy construction in infinite regular games yields a fully automatic procedure for generating finite-state winning strategies, i.e. finite-state controllers, from temporal logics specifications of the allowable behaviour [18].

As there is an effective mapping of RTSTDs to PTL, which is fully explored in [10], this approach can be extended to deal with RTSTDs also. Soundness

Fig. 3. The basic synthesis chain.

and completeness of the synthesis method then is directly inherited from the corresponding properties of winning strategy construction in regular games. In fact, this chain of algorithms, depicted in Fig. 3, forms the backbone of the ICOS tool set [5,12].

However, this basic synthesis chain suffers from complexity problems if the specification is large, i.e. is a conjunction of multiple timing diagrams, as the regular games constructed then tend to suffer from state explosion. With the basic method, game graphs grow exponentially in the number of timing diagrams due to the automaton product involved in dealing with conjunction. As this would render application for rapid prototyping impractical, the ICOS tools offer modified procedures which reduce the complexity of dealing with large specifications. Obviously, such extensions cannot deal efficiently with arbitrary RTSTD specifications, but they are, however, carefully designed to cover the typical specification patterns.

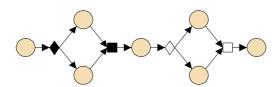

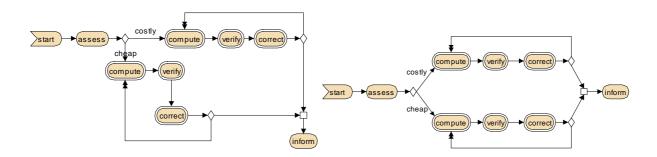

#### 4.2 Compositional synthesis

The first such variant is a compositional extension of the basic algorithm. Within this approach, which is sketched in Fig. 4, the specification is first partitioned into a maximal set of groups of formulae  $\mathcal{G}_1, ..., \mathcal{G}_n$  such that each output is constrained by the formulae of at most one group. Then synthesis down to a winning strategy is performed for each group individually, yielding for each group  $\mathcal{G}_i$  a Moore automaton  $A_i$  that has just the outputs constrained by  $\mathcal{G}_i$  as outputs, and all other ports as inputs. The individual Moore automata are then compiled to synthesizable VHDL and composed by parallel composition.

Fig. 4. Compositional synthesis.

With this compositional method, growth of the game graph is linear in the number of groups, and exponential growth is only encountered in the maximal size of the individual groups. Table 2 provides empiric results from [5], obtained by Feyerabend and Schlör when using both the non-compositional and the compositional synthesis procedure of ICOS for synthesizing a controller for the FZI production cell [11]. Overall, Feyerabend and Schlör have found the compositional approach to save over 99% of the transitions in the game graphs of the major components.

Soundness of the compositional synthesis technique is easily established:

**Theorem 1.** Let  $\mathcal{G}_1, \ldots, \mathcal{G}_n$  be groups of RTSTDs with  $O_i$ ,  $1 \leq i \leq n$ , being the outputs constrained by  $\mathcal{G}_i$ , and with  $O_i \cap O_j = \emptyset$  for  $i \neq j$ . Let  $A_i$  be the Moore automaton synthesized for  $\mathcal{G}_i$ . Then  $A_1 \parallel \ldots \parallel A_n$  is well-typed and correct wrt.  $\mathcal{G}_1 \wedge \ldots \wedge \mathcal{G}_n$ , where  $\parallel$  denotes parallel composition of Moore automata.

Proof. Correctness of  $A_1 \parallel \ldots \parallel A_n$  wrt.  $\mathcal{G}_1 \wedge \ldots \wedge \mathcal{G}_n$  is straightforward, as parallel composition of Moore automata with disjoint output alphabets semantically yields language intersection, as does conjunction of RTSTDs. Thus, soundness of the basic synthesis algorithm, which yields  $\mathcal{L}_{A_i} \subseteq \mathcal{M}[\mathcal{G}_i]$  for the individual groups, implies  $\mathcal{L}_{A_1 \parallel \ldots \parallel A_n} = \mathcal{L}_{A_1} \cap \ldots \cap \mathcal{L}_{A_n} \subseteq \mathcal{M}[\mathcal{G}_1] \cap \ldots \cap \mathcal{M}[\mathcal{G}_n] = \mathcal{M}[\mathcal{G}_1 \wedge \ldots \wedge \mathcal{G}_n]$ . Similarly, well-typedness of  $A_1 \parallel \ldots \parallel A_n$  wrt.  $\mathcal{G}_1 \wedge \ldots \wedge \mathcal{G}_n$  follows from soundness of the basic synthesis procedure since the composition rules for interfaces agree for Moore automata and RTSTDs if outputs occur at most once in a parallel composition.

Completeness is, however, lost using compositional synthesis. The problem is that a certain group may not be synthesizable without knowledge about the behaviour of another group. Such problems are regularly encountered within compositional methods, and we propose to solve them by just the same techniques that proved to be helpful in compositional verification: the necessary information on the other components can be formalized via assumptions (for example, through weak constraint arcs). It should be noted that ICOS helps in finding adequate assumptions, as an error path is supplied whenever synthesis of a component fails.

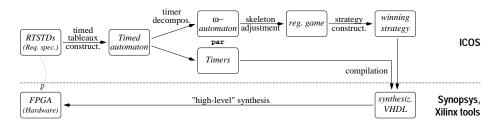

#### 4.3 Synthesizing hardware clocks

However, there still is some reason for dissatisfaction: as timing annotations have to be unwound to an according number of next-operators of PTL by the translation of RTSTDs to PTL, which introduces corresponding chains of unit-delay transitions in the game graphs, the modular synthesis method remains exponential in the number of potentially overlapping timing constraints. This makes dealing with timing constraints of more than a handful time units hardly affordable — realistic real-time system programming cannot be done with such code generation methods. Therefore, we are heading for an algorithm that is of linear complexity in the number of timing constraints, even though completeness is thereby necessarily sacrificed. What is thus needed is a synthesis method that separates generation of timers controlling the allowable passage of time from

**Table 2.** Experimental results obtained when applying non-compositional and compositional synthesis to the Karlsruhe production cell [11] (after [5]).

Non-compositional synthesis: System has 8 components. One controller per component is synthesized. The most complex components are:

| Component | STDs | Game graph |                    | Controller |                   | Time (s) |

|-----------|------|------------|--------------------|------------|-------------------|----------|

|           |      | states     | ${ m transitions}$ | states t   | ${ m ransitions}$ |          |

| Press     | 14   | 1703       | 115897             | 82         | 435               | 4483     |

| Crane     | 16   | 1574       | 76041              | 190        | 1303              | 1035     |

Compositional synthesis: System is automatically partitioned into 26 groups. One controller per group is synthesized. Most complex group deals with controlling vertical movement of the press:

|                            | STDs | Gan    | ne graph           | Cor      | troller    | Time (s) |

|----------------------------|------|--------|--------------------|----------|------------|----------|

|                            |      | states | ${ m transitions}$ | states t | ransitions |          |

| (Press, vertical movement) | 5    | 27     | 193                | 6        | 26         | 8        |

synthesis of an untimed control skeleton. In the remainder, we sketch a synthesis technique currently being integrated into ICOS, which offers the desired separation. In this hybrid approach, small — and thus harmless wrt. the state explosion problem — time constants are treated by purely  $\omega$ -automata-theoretic means, whereas large-scale timing constraints, if found to be sufficiently independent, are directly mapped to hardware timers.

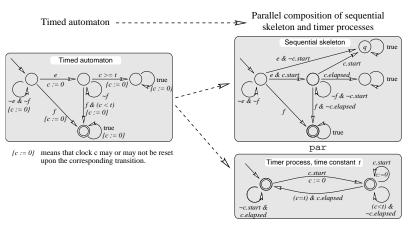

The new approach starts by using timed automata for representing the semantics of real-time symbolic timing diagrams: every RTSTD  $\phi$  is assigned a timed automaton  $A_{\phi}$  that accepts exactly the counterexamples of  $\phi$ , i.e. all those traces that are not models of  $\phi$ . An example of a timed automaton recognizing the counterexamples of an RTSTD can be seen on the left hand side of Fig. 6, where the conjunction of a precedence and a leads-to<sub>t</sub> constraint between events e and f is dealt with.

Once a timed automaton accepting counterexamples to the specification is constructed, synthesis of a controller satisfying the specification can commence: in a first step, all clocks implementing delays of more than a handful time units are removed from the timed automaton and replaced by external timer com-

Fig. 5. Synthesis chain employing timer decomposition.

Fig. 6. Converting clocks to timer components.

ponents acting in parallel, as shown in Fig. 6. Thereafter, the remaining clocks are removed by expanding their effect to an appropriate number of unit-delay transitions. This results in an untimed automaton, called sequential skeleton in the remainder, which communicates with the environment and with the timer components. The novelty of our approach is that from then on, synthesis will treat the timers similar to environment components, which means that the behaviour of these components is left untouched during synthesis. The advantages are twofold: first of all, the fixed behavioural description of timers allows for the use of pre-fabricated, optimized hardware components, and second, controller synthesis can concentrate on solving the control problem described by the small, untimed automaton that remains.

Note that the parallel composition (alas automaton product, thus yielding language intersection) of the sequential skeleton and the timer processes derived thus far recognizes the counterexamples to the specification. Now, we would like to implement the timers in hardware and to remove them from the synthesis problem, i.e. we want to synthesize wrt. the skeleton *only* without, however, risking erroneous behaviour of the synthesized controller. As the timer communications are only internal to the controller, the correctness criterion involved is

$$(\mathcal{L}_C \cap \mathcal{L}_{timer}) \setminus [t.start, t.elapsed] \subseteq \overline{(\mathcal{L} \cap \mathcal{L}_t) \setminus [t.start, t.elapsed]} , \qquad (1)$$

where  $\mathcal{L}_C$  and  $\mathcal{L}_{timer}$  are the trace sets of the controller and the timers, resp.,  $\mathcal{L}$  is the language accepted by the skeleton automaton, '\[[t.start, t.elapsed]]' denotes hiding of the timer communications, and the overbar denotes language complement.

It might seem that straightforward synthesis wrt. the complement of the skeleton, which yields a controller C satisfying the language inclusion property  $\mathcal{L}_C \subseteq \overline{\mathcal{L}}$ , suffices. Unfortunately,  $\mathcal{L}_C \subseteq \overline{\mathcal{L}}$  is in general not a sufficient condition

for (1) due to the existential quantification involved in hiding,<sup>2</sup> which changes to universal quantification under the complementation involved in (1).

However, this can be repaired by synthesizing wrt. an appropriately adjusted variant skel' of the skeleton automaton that enforces a certain usage of timers. The key issue is that the synthesized controller is forced to start a timer and not interfere its run whenever a violation of the corresponding timing constraint could possibly occur. The new skeleton skel' is generated by taking the same state set, same initial states, and same transition relation as in the original skeleton, yet expanding the set of accepting states by states like state q in Fig. 6, which is entered if the timer signaling the possible violation of the leads-to<sub>t</sub> constraint is not properly activated. The detailed construction, which we cannot provide due to lack of space, is s.t. if a timer action sequence ts exists with  $w \oplus ts \in \mathcal{L} \cap \mathcal{L}_{timer}$  then  $w \oplus ts' \in \mathcal{L}_{skel'}$  for each  $ts' \in \mathcal{L}_{timer}$ . Note that furthermore  $\mathcal{L}_{skel'} \supseteq \mathcal{L}$  by construction.

If we now synthesize a controller with inputs  $I \cup \{t.elapsed\}$ , outputs  $O \cup \{t.start\}$  (where I and O are the original in- and outputs) that is correct wrt. the adjusted control problem, i.e. satisfies  $\mathcal{L}_C \subseteq \overline{\mathcal{L}_{skel'}}$ , then we have obtained a correct solution:

**Lemma 1.** Correctness of C wrt.  $\overline{\mathcal{L}_{skel'}}$ , i.e.  $\mathcal{L}_C \subseteq \overline{\mathcal{L}_{skel'}}$ , implies (1).

*Proof.* Assume that  $\mathcal{L}_C \subseteq \overline{\mathcal{L}_{skel'}}$  holds and (1) is false, i.e. there exists some  $w \in (\mathcal{L}_C \cap \mathcal{L}_{timer}) \setminus [t.start, t.elapsed] \cap (\mathcal{L} \cap \mathcal{L}_{timer}) \setminus [t.start, t.elapsed]$ . By definition of hiding this implies that there are two timer action sequences  $ts_1, ts_2$  with

$$w \oplus ts_1 \in \mathcal{L}_C \cap \mathcal{L}_{timer} \land w \oplus ts_2 \in \mathcal{L} \cap \mathcal{L}_{timer}$$

.

Then, by construction of skel',  $w \oplus ts_1 \in \mathcal{L}_{skel'}$ . But on the other hand  $w \oplus ts_1 \in \mathcal{L}_C$  and  $\mathcal{L}_C \subseteq \overline{\mathcal{L}_{skel'}}$ , which yields a contradiction.

Consequently, synthesis wrt. the adjusted control problem is sound. Furthermore, by directly mapping all timing constraints of significant size to hardware timers, this method is linear in the number of timing constraints. If it is furthermore combined with modular synthesis then super-linear blow-up can only occur through individual timing diagrams containing unusually large numbers of events or through large groups of formulae controlling the same outputs. These situations are, however, atypical, rendering the new method a practical rapid-prototyping tool for real-time embedded controllers.

Similar methods are, btw., currently explored by the second author for dealing with data in an essentially uninterpreted way. The idea is that thus the traditional separation between control and data can be incorporated into gametheoretic synthesis methods. The net effect is that a large data path no longer yields a blow-up of the game-graph. The complexity of automatic synthesis then predominantly depends on the control part, making automatic synthesis applicable to much larger, control-dominated systems.

<sup>&</sup>lt;sup>2</sup> For a language  $\mathcal{L} \subseteq (\alpha \times (\{t.start, t.elapsed\} \to \mathbb{B}))^{\omega}$  and some string  $w \in \alpha^{\omega}$ ,  $w \in \mathcal{L} \setminus [t.start, t.elapsed]$  holds if some sequence  $ts \in (\{t.start, t.elapsed\} \to \mathbb{B})^{\omega}$  of timer actions exists with  $w \oplus ts \in \mathcal{L}$ .

#### 5 Discussion

We have presented a rapid-prototyping framework for requirements specifications that are formalised through real-time symbolic timing diagrams, a metric-time temporal logic with a graphical syntax akin to the informal timing diagrams used in electrical engineering [4]. The underlying core technology is fully automatic synthesis of embedded control hardware from requirements specifications. This involves two major steps: first, the generation of Moore automata satisfying the specification, and second, the actual implementation of these automata by embedded control hardware. For the latter step, we rely on industrially available tools from Synopsys and Xilinx that perform FPGA-based implementation of VHDL-coded Moore-automata [7]. In contrast, the former step is based on procedures that have been specifically implemented for the ICOS tool-box [5, 10, 12]. While the underlying algorithms have been derived from the well-established theory of winning-strategy construction in  $\omega$ -regular games, the overall approach is — being targeted towards rapid prototyping — mostly pragmatic, weighing efficiency higher than completeness. Two key issues have been identified in this respect: first, the necessity of compositional synthesis of parallel components and second, early decomposition of timing issues from the synthesis problem. The result is a synthesis method that is essentially linear in the size of the specification and thus suitable as a development tool in rapid prototyping contexts.

Within the ICOS tool-box, these algorithms are closely integrated with a graphical specification editor supporting the specification phase and all compilation and mapping algorithms necessary for mechanically translating down to automatically synthesizable VHDL code such that implementation is truly automatic from the specification level all the way down to actual hardware. ICOS furthermore comprises — under a common user interface — tools for browsing and manipulating a specification database, as well as for interactively simulating and for verifying specifications. It is thus a comprehensive environment for the incremental development of RTSTD-based requirements specifications. Furthermore, within the rapid-prototyping project "EVENTS" [13], ICOS is conjoined with Statemate-based code generation techniques such that rapid prototyping of hybridly specified systems, where some components have a declarative formulation through RTSTDs while others are operationally described by Statecharts [8], becomes feasible. While this involves integration of different rapidprototyping tools through automatic interface generation for the generated components, other extensions to the source language accepted can be accomplished within just the ICOS tool: ICOS is modularly built such that while the current version is dedicated towards RTSTD-based specification, an adaptation to other declarative specification formalisms is possible. A possible candidate formalism, for which front-end tools like graphical editors are already under development at our department, is that of Live Sequence Charts (LSCs), an extension of Message Sequence Charts (MSCs) recently proposed by Damm and Harel [3].

On the algorithmic side, we think that the main contribution of the ICOS tools to game-theoretic synthesis are methods for dealing with timing or with the data path in an uninterpreted way. Due to the obvious necessity of treating

timing mostly independent from algorithmic aspects within any reasonably efficient synthesis method for hard real-time controllers, quite a few other research groups work on this theme. However, most approaches are based on primarily operational rather than declarative specification styles (e.g. [19]). Closest to our approach is [15], where Dierks and Olderog detail a direct mechanism for deriving timer actions from specifications formalised through a very restrictive subset of Duration Calculus [20], the so-called DC-implementables [16]. Dierks' algorithm is extremely efficient, but at the price of a very restrictive specification format: the processable specifications are confined to be 'phased designs' in the sense of the ProCoS projects [2], which are akin to RTSTDs featuring just three events. While our formalism is more expressive in this respect, Dierks and Olderog do, on the other hand, go ahead by dealing with a dense-time logic and analyzing certain kinds of switching latency.

#### References

- G. Borriello. Formalized timing diagrams. In The European Conference on Design Automation, pages 372–377, Brussels, Belgium, Mar. 1992. IEEE Computer Society Press.

- 2. J. P. Bowen, M. Fränzle, E.-R. Olderog, and A. P. Ravn. Developing correct systems. In *Proc. 5th Euromicro Workshop on Real-Time Systems*, *Oulu, Finland*, pages 176–189. IEEE Computer Society Press, June 1993.

- 3. W. Damm and D. Harel. LSCs: Breathing Life into Message Sequence Charts. Technical Report CS98-09, Weizmann Institute, Apr. 1998.

- 4. K. Feyerabend and B. Josko. A visual formalism for real time requirement specification. In *Transformation-Based Reactive System Development*, number 1231 in LNCS, pages 156–168. Springer Verlag, 1997.

- 5. K. Feyerabend and R. Schlör. Hardware synthesis from requirement specifications. In *Proceedings of EURO-DAC'96 with EURO-VHDL'96*. IEEE Computer Society Press, September 1996.

- M. Fränzle and K. Lüth. Compiling graphical real-time specifications into silicon. In Ravn and Rischel [17], pages 272–281.

- S. Golsen. State Machine Design Techniques for Verilog and VHDL. Synopsys Journal of High Level Design, Sept. 1994.

- 8. D. Harel, H. Lachover, A. Naamad, A. Pnueli, M. Politi, R. Sherman, and A. Shtul-Trauring. STATEMATE; a working environment for the development of complex reactive systems. In *Proceedings of the 10th International Conference on Software Engineering*, pages 396–406, Singapore, Apr. 1988. IEEE Computer Society Press.

- 9. P. Khordoc, M. Dufresne, and E. Czerny. A Stimulus/Response System based on Hierarchical Timing Diagrams, Publication No.770. Technical report, Universite de Montreal, 1991.

- F. Korf. System-Level Synthesewerkzeuge: Von der Theorie zur Anwendung. Dissertation, Fachbereich Informatik, Carl von Ossietzky Universität Oldenburg, Germany, 1997.

- 11. C. Lewerentz and T. Lindner, editors. Formal Development of Reactive Systems: Case Study Production Cell, volume 891 of Lecture Notes in Computer Science. Springer-Verlag, Jan. 1995.

- K. Lüth. The ICOS synthesis environment. In Ravn and Rischel [17], pages 294– 297.

- K. Lüth, A. Metzner, T. Peikenkamp, and J. Risau. The EVENTS Approach to Rapid Prototyping for Embedded Control Systems. In Zielarchitekturen eingebetteter Systeme (ZES '97), 14. ITG/GI Fachtagung Architektur von Rechnersystemen (ARCS'97), Rostock, Germany, September 1997.

- Z. Manna and A. Pnueli. The Temporal Logic of Reactive and Concurrent Systems, volume 1. Springer-Verlag, 1992.

- E.-R. Olderog and H. Dierks. Decomposing real-time specifications. In H. Langmaack, W. de Roever, and A. Pnueli, editors, Compositionality: The Significant Difference, Lecture Notes in Computer Science. Springer-Verlag, to appear 1998.

- A. P. Ravn. Design of Embedded Real-Time Computing Systems. Doctoral dissertation, Department of Computer Science, Danish Technical University, Lyngby, DK, Oct. 1995. Available as technical report ID-TR: 1995-170.

- 17. A. P. Ravn and H. Rischel, editors. Formal Techniques in Real-Time and Fault-Tolerant Systems (FTRTFT'98), volume 1486 of Lecture Notes in Computer Science. Springer-Verlag, 1998.

- 18. W. Thomas. Automata on infinite objects. In J. v. Leeuwen, editor, *Handbook of Theoretical Computer Science*, volume B: Formal Models and Semantics, chapter 4, pages 133–191. North-Holland, 1990.

- P. Vanbekbergen, G. Gossens, and B. Lin. Modeling and synthesis of timed asynchronous circuits. In *Proceedings EURO-DAC with EURO-VHDL 94*. IEEE Comp. Soc. Press, 1994.

- Zhou Chaochen, C. A. R. Hoare, and A. P. Ravn. A calculus of durations. Information Processing Letters, 40(5):269-276, 1991.

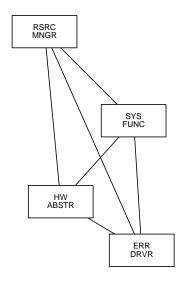

# Object-Oriented Modelling and Specification using SHE

M.C.W. Geilen, J.P.M. Voeten

Section of Information and Communication Systems

Faculty of Electrical Engineering

Eindhoven University of Technology

P.O. Box 513, 5600 MB Eindhoven, The Netherlands

#### Abstract

Industry is facing a crisis in the design of complex hardware/software systems. Due to the increasing complexity, the gap between the generation of a product idea and the realisation of a working system is expanding rapidly. To manage complexity and to shorten design cycles, industry is forced to look at system level languages towards specification and design. The (formal) system level modelling language called POOSL is very expressive and is able to model dynamic hard real-time behaviour as well as static (architecture and topology) structure in an object-oriented fashion. The language integrates a process part, based on the process algebra CCS, with a data part, based on the concepts of traditional object-oriented programming languages. Currently a number of automated software tools (model editing, simulator and compiler tools) are available in an environment which is called SHESim. These tools allow visual entry of structure and topology of the system, whereas the behaviour of individual processes is expressed in an imperative textual language.

#### 1 Introduction

Industry struggles with mastering the development process of complex hardware/software systems. Examples of these systems are data/telecommunication systems, multimedia systems, medical systems, industrial control systems and consumer electronics. Hardware/software systems are typically implemented using several types of hardware components and complex application software running on real-time operating systems. These systems perform very complex behaviour and have to satisfy architectural constraints that impose physical distribution and hardware/software partitioning. Currently, industry is facing a crisis in the design of these complex systems [5]. Due to their combination of requirements, modern hardware/software systems are inherently complex to design, implement, verify, validate, test and debug. Today's systems integrate more and more functionality that has to satisfy stringent requirements of quality, flexibility, reliability and reusability. Deciding on an appropriate implementation has become increasingly difficult due to the diversity of available technology components (microprocessors, digital signal processors, application specific instruction processors, application specific integrated circuits, field programmable gate arrays, real-time operating systems, etcetera). Industry is struggling with tight bounds on time-to-market, -quality and -volume, high innovation speed and high costs for failure.

Existing specification and design approaches are no longer keeping pace with the growth of system complexity. For hardware, traditional design approaches are well established for the lower levels (transistor, logic, register and algorithmic level) of the design trajectory. However, as systems become more complex, the descriptions on these abstraction levels grow so huge that they become incomprehensible for designers and unmanageable for design tools [2, 5]. For the development of software, methods supporting the higher levels of the design trajectory are available. These methods, however, are often unsuitable for system design, and they do not help in making design decisions regarding architecture structure, hardware/software partitioning and the technology components to be applied.

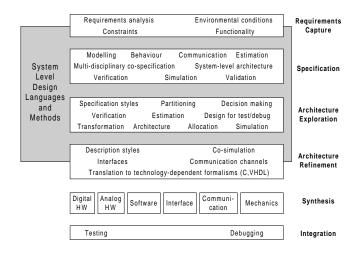

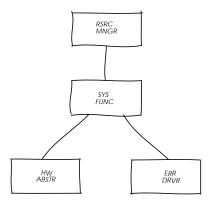

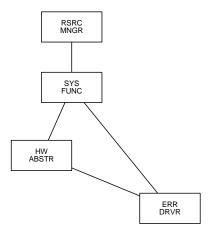

Figure 1. The role of system level languages

Due to the increasing system complexity, the gap between the generation of a product idea and the realisation of a working system is expanding rapidly. To manage complexity and to shorten design cycles, industry is forced to look at system level approaches towards specification and design [2, 5]. System level specification and design methods allow the creation of formal, executable models describing a system in the earliest stages of the design process. These models are expressed in powerful languages such that complex systems can be described with relatively few language constructs. System level models allow the properties of a system to be analysed, simulated, validated and verified before this system is actually being realised in terms of hardware and software components [2]. In this way design errors can be detected in a very early phase, thereby preventing expensive and time-consuming design iterations. The models further allow the systematic and rapid evaluation of different hardware/software architectures on a high level of abstraction, without having to spend a lot of time in creating low level implementations. This is an important advantage since it is at the higher levels of abstractions where the largest gains in designing 'optimal' hardware/software systems can be obtained [2].

In this paper we report on the system level modelling language called POOSL (Parallel Object-Oriented Specification Language). In Section 2 our requirements for a system level language are pointed out. Section 3 explains the basic concepts of POOSL and compares them to the concepts of the description languages SDL, Estelle, LOTOS and ROOM. In Section 4 we show how the language can be used to model a non-trivial part of a datalink protocol. Section 5 describes the software tools that are currently available. It will be shown how these tools allow the estimation of a performance parameter of this protocol. Finally in Section 6 we present our conclusions and directions for future research.

## 2 System Level Language Requirements

Figure 1 shows the role of system level languages and methods in the design trajectory for hardware/software systems [5]. It visualises the different design phases and indicates for each phase the relevant keywords and key activities. It should be clear that system level languages are especially useful in the early phases of design, where a system is being analysed and specified and where the system level architecture is being decided upon. They should help to bridge the gap between requirements capture and synthesis. Therefore they should be intuitive, applicable within multidisciplinary design and easy to understand. For this reason, a system level language should have an imperative nature, should be simple and built on a small collection of blending language primitives [1]. During the architecture exploration phase, the implementation technologies to be applied are decided upon. To make architecture exploration feasible, a system level specification should not be biased towards a particular choice of implementation and should be described in a language that abstracts from technology. To help designers bridge the gap between requirements capture and synthesis, adequate tool support is indispensable. Tools are required to edit, validate, verify, simulate and transform specifications, but are also needed for parameter estimation, automatic

test-suite generation and system level synthesis to compile specifications to technology-specific languages such as VHDL and C. To support the development of such tools, a system level language should be equipped with a mathematical semantics [1].

From the characteristics of complex hardware/software systems, a number of other language requirements can be deduced. The communication and functional behaviour of a hardware/software system is often so complicated that it is quite impossible to understand it or to model it in its entirety. Therefore behaviour should be distributed over modules whose behaviour can be understood without having to understand the environment they are placed in. This requires modules to be self-contained, autonomous, relatively independent, and weakly coupled entities. We will call these entities process objects, or processes in short. Processes exist in their own right, have their own responsibilities, and they have their own activities to perform. This is highly desirable because it enables processes to be reused in contexts other than the one for which they were originally devised. Reuse is achieved by organising objects into classes. A class is a template from which objects are instantiated.

A very important characteristic of hardware/software systems is structure. Physical or spatial distribution, physical topology, hardware/software partitioning and software layering are all examples of phenomena that impose structure. The modelling of topology requires processes to be structured in a network of channels. The other forms of structure require the possibility to group processes into higher-order entities, called clusters. A cluster acts as an hierarchical abstraction of its internals. Hierarchy is an important concept that helps to manage complexity. To enhance modularity and reuse, clusters should be organised into classes.

Processes (and clusters) are relatively independent and they can perform their activities concurrently and at their own speed. Despite of their autonomy, processes will frequently have to exchange information. To make the coupling between processes (and clusters) as weak as possible, information exchange should be based upon message passing. The essential feature of message passing is that information is exchanged by means of an intermediate artefact, called a message. The purpose of a message is to reduce the coupling between the message senders and the message receivers [12]. To exchange information, the sender and the receiver only have to share the format and the general semantics of a message. They do not have to know anything about each other's internals, i.e. about private data. The internals of a process are said to be encapsulated by a strong encapsulation boundary. The only way for other processes to access these internals is through a clear-cut message interface.

A process can exhibit very complex behaviour. It can perform several activities in parallel and is able to exchange messages in various ways (synchronous, asynchronous, interrupt-driven and by broadcast). Behaviour can depend on (hard) real-time concepts such as time-outs, watchdogs and deadlines. It must be possible to express all these forms of behaviour in a system level modelling language.

Processes in hardware/software systems are able to perform complex manipulations on their private data. Because private data can have complex structures of their own, they should be represented by objects too. We will call these objects data objects. Data objects can be exchanged as parameters of messages between processes. Within a single process, data objects are shared and several activities can be manipulating these data objects concurrently. Different processes cannot share any data objects. To make data objects reusable, they have to be organised into classes.

#### 3 Basic Concepts of POOSL

In [15, 1] we introduced the method Software/Hardware Engineering (SHE). SHE is an object-oriented modelling technique. Starting from informal graphical models, SHE produces rigorous behaviour and architecture models expressed in the formal specification language POOSL [1, 3]. The POOSL language has specifically been developed to be used as a system level modelling language.

The POOSL language combines a process part with a data part. The process part is based on the key ideas of the process algebra CCS [7]. The data part is based upon the concepts of traditional sequential object-oriented programming languages such as Smalltalk and C++. In POOSL very complex hard real-time behaviour is represented by a collection of asynchronous concurrent process objects that communicate synchronously or asynchronously by passing messages over static channels. Behaviour of process objects is described by

- synchronous (conditional) message (and data object) passing primitives;

- asynchronous (unbuffered) broadcast message passing primitives;

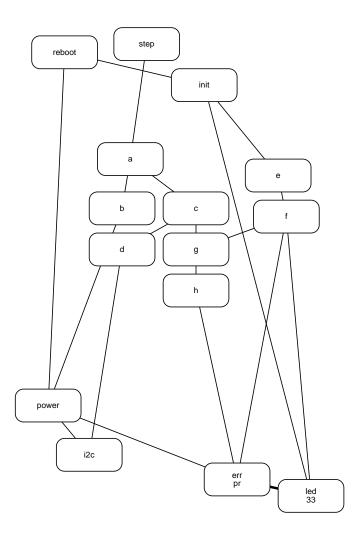

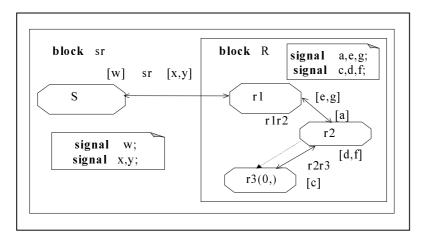

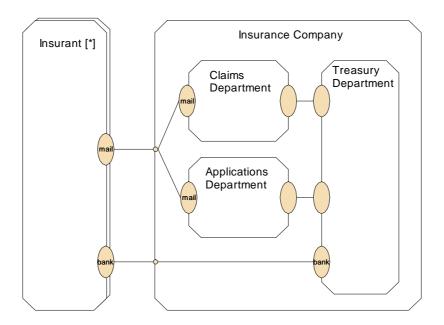

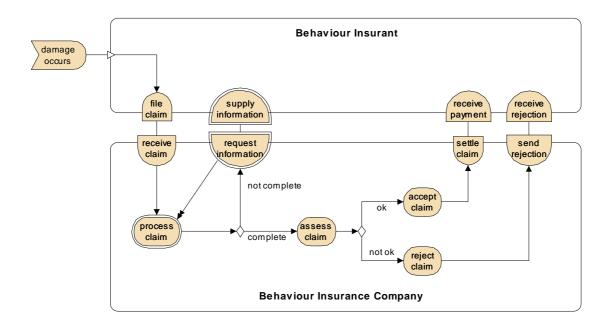

Figure 2. A Protocol Stack

- loop and select primitives, guarded commands, parallel and sequential composition, procedure (method) abstraction and (tail) recursion;

- interrupt and abort primitives;

- delay primitives.

Next to processes, POOSL supports the concept of cluster. A cluster is composed of processes and other clusters and acts as an abstraction of these. Clusters are used to create an hierarchical structure of modules that hide their internal structure. The constituents of a cluster are composed by parallel composition, channel hiding and channel renaming. These combinators are based upon similar combinators originally used in CCS [7]. Together, clusters and channels are suitable for describing architecture structure, topology and implementation boundaries [1].

To describe complex functional behaviour, POOSL supports data objects. Data objects have sequential behaviour and communicate by synchronous message passing. They are contained in processes and they model the private data of these processes. Data objects are also called travelling objects, since they can be passed between processes.

The POOSL language is equipped with a complete mathematical semantics. The semantics is based on a two phase execution model. The state of a system can either change by asynchronously executing atomic (communication or data processing) actions (taking no time) or by letting time pass (synchronously). The semantics of the non real-time part of POOSL is given in [1]. The formalisation of the real-time extension is described in [3, 4].

The key feature of POOSL is the expressive power to model very complex hard real-time (communication and functional) behaviour as well as static (architecture and topology) structure in an object-oriented fashion. POOSL can best be compared with the formal description languages LOTOS, SDL and Estelle [14] and the modelling language ROOM [12]. These languages all have a well-defined semantics<sup>1</sup> and are relatively simple<sup>2</sup>. They are further based on autonomous, encapsulated asynchronous concurrent entities that are connected in a static topology of channels and communicate using well-defined interaction primitives<sup>3</sup>. However, there are many concepts in which these languages differ from POOSL. Some important differences are:

<sup>&</sup>lt;sup>1</sup>The semantics of LOTOS and SDL are defined in a formal mathematical way. As far as we have been able to verify, this is not true for Estelle and ROOM.

<sup>&</sup>lt;sup>2</sup>This especially holds for Estelle. The other languages are a lot more complicated.

<sup>&</sup>lt;sup>3</sup>LOTOS supports concurrent processes. Processes in LOTOS are pieces of behaviour, but they are not objects that perform this behaviour. Nevertheless, objects can be modelled by processes [9].

Communication: Communication in SDL, Estelle and ROOM, is buffered asynchronously<sup>4</sup>. Buffered asynchronous message passing is certainly a useful concept and should be supported, but it is not sufficient for hardware/software systems. We have experienced that especially at higher levels of abstraction, the concept of synchronous communication<sup>5</sup> is indispensable. It should be noted that asynchronous interaction can easily be expressed in terms of synchronous interaction. This is not true in the other direction. Synchronous interaction is incorporated in the LOTOS language. Although it is based on undirected (multi-way) action synchronisation, and not message passing, it can be used to express directed message passing too [9], be it in a less natural way. None of the languages above support asynchronous broadcast primitives.

Interrupts and aborts: Interrupts and aborts are very important for describing complex behaviour. In case of an interrupt the current course of behaviour is temporarily suspended until the interrupting behaviour has terminated. In case of an abort the current course of behaviour is terminated and the aborting behaviour is started. The LOTOS language only supports aborts. In ROOM behaviour can both be aborted as well as interrupted. SDL and Estelle do not have interrupt or abort facilities.

**Data Objects:** For describing intricate dynamic data structures, the concept of data object is indispensable. Except for ROOM, none of the languages support data objects. LOTOS and SDL use abstract data types and Estelle uses Pascal types to model data. Abstract data types are attractive from a mathematical point of view, but they have appeared to be difficult to understand [10] and they are hard to simulate and implement efficiently. Pascal is a procedural language and has insufficient support for encapsulation and data modularisation.

Concurrency and Sharing: The combination of concurrency and shared data is often considered dangerous since it introduces a lot of non-determinism in models and can lead to synchronisation and mutual exclusion problems. We agree with this, but we think a restricted combination of concurrency and sharing is necessary to model real-life systems. Therefore, POOSL has a par-statement that allows concurrency inside processes. The restriction lies in the fact that operations on data objects are atomic and hence concurrency in processes is defined at a rather coarse grain. In this way mutual exclusion and synchronisation problems can be solved very naturally, without forbidding activities to operate on shared data entirely. The grain of concurrency in ROOM, SDL, Estelle and LOTOS is at the level of process objects<sup>6</sup>. These processes cannot share data and therefore it is not possible to model activities that operate on a piece of shared data concurrently.

Real-time: None of the above languages have sufficient support to model (hard) real-time behaviour. The LOTOS language does not have any facilities to express time at all<sup>7</sup>. Estelle supports a restricted timing mechanism in the form of time delays. However, the Estelle semantics restricts the interpretation of time in the weakest way possible, placing only those requirements that derive from assuming that time moves forward consistently for all modules in the same subsystem [14]. SDL has a built-in real-time mechanism, relying on an asynchronous timer mechanism that is able to access a global clock referring to the current moment in time. However the delay between the moment of timer expiration and the moment at which the SDL model reacts to this expiry is unbounded. Therefore SDL is not suitable for expressing hard-real time behaviour [6]. In fact, the concept of time is not an inherent property of a model in SDL but of the possibly underlying execution engine or operating system. The same holds for the ROOM language.

## 4 Example

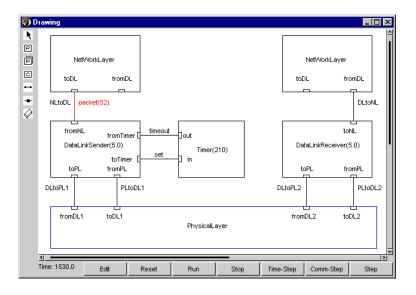

In [17] we have shown the suitability of the SHE method and POOSL language for the specification and design of an industrial distributed control system. In this section we will demonstrate how the POOSL language can be used to model a non-trivial part of a protocol stack [13]. The protocol stack is shown in the simulator window of Figure 2. The stack consists of two peer NetworkLayers, a DataLinkSender with a Timer, a DataLinkReceiver and a PhysicalLayer. These entities communicate by exchanging messages over channels. The NetworkLayer exchange Packets. The left NetworkLayer can send messages of the form packet(somePacket) to the corresponding DataLinkSender by executing toDL!packet(somePacket) statements<sup>8</sup>. toDL is a port of the NetworkLayer object

<sup>&</sup>lt;sup>4</sup>A sender can always send a message without knowing the readiness of the receiver. In general, messages are buffered until they are consumed by the receiver, but under some circumstances they can also be discarded.

<sup>&</sup>lt;sup>5</sup>A sender may only send a message if the receiver is ready and willing to receive it.

<sup>&</sup>lt;sup>6</sup>In ROOM these objects are called actors, in SDL process instances and in Estelle they are called modules.

Although many proposals have been written to extend LOTOS with a notion of time.

<sup>&</sup>lt;sup>8</sup>The behaviour descriptions of the NetworkLayers, DataLinkSender, Timer and DataLinkReceiver are not given in this paper.

Figure 3. PhysicalLayer cluster

and this port is connected to channel NLtoDL. The DataLinkSender can receive these packet(somePacket) messages by executing fromNL?packet(somePacket) statements. Here somePacket denotes a data object of data class Packet. Upon reception of a Packet the DataLinkSender wraps this Packet (together with some control information) in a data object of class Frame. This Frame is then sent to the PhysicalLayer which transports it to the DataLinkReceiver. Consequently, the Packet is retrieved from the Frame object, and is delivered to the peer NetworkLayer.

The *PhysicalLayer* is unreliable and can lose messages. To make sure that all *Packets* are delivered in the correct order, the *DatalinkSender* and *DataLinkReceiver* make use of a positive acknowledgement with retransmission protocol [13]. Therefore, they can send particular *Frames* several times and they can also send acknowledgement *Frames*. To this end the *DataLinkSender* makes use of a *Timer* process.

The specifications of the *DataLinkSender*, *Timer* and *DataLinkReceiver* are not further elaborated in this paper. Instead we will take a closer look at the specification of the *PhysicalLayer*.

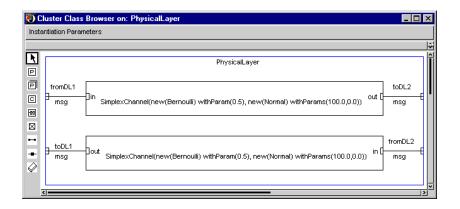

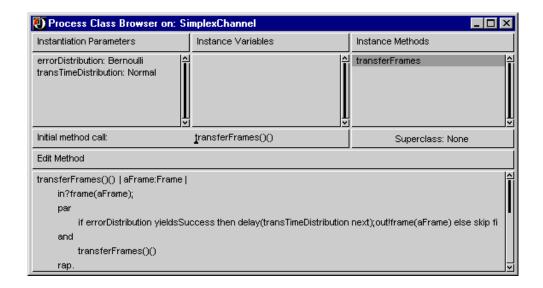

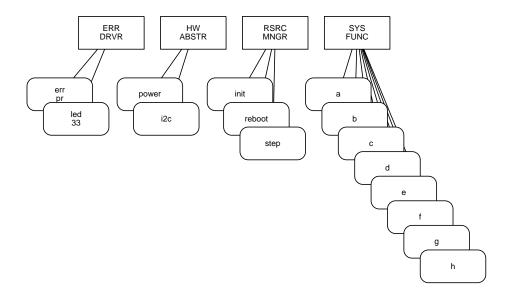

Physical Layer is a cluster consisting of two SimplexChannels, see Figure 3. A SimplexChannel has two ports in and out. From port in it receives frame (aFrame) messages and after some specified period of time it delivers these messages at port out. The specification of the behaviour of a SimplexChannel is shown in the Process Class Browser of Figure 4. Within the Instantiation Parameters pane, two instantiation parameters, error Distribution and transTimeDistribution, are specified. These parameters are bound at the moment a process of class SimplexChannel is instantiated. Parameter error Distribution is a data object of data class Bernoulli and it models the probability that a message in the channel is lost. The parameter is bound to expression new(Bernoulli) with-Param(0.5) which delivers a new Bernoulli distribution with success parameter 0.5 (half of the messages are lost), see Figure 3. The transTimeDistribution parameter models the transmission time of a message through the channel. This parameter is bound to a Normal distribution object with mean 100.0 and variance 0.0 (the transmission time is constant).

The behaviour of a process is specified in terms of instance methods. Methods can be compared to procedures of traditional imperative programming languages such as C or Pascal. Upon instantiation of a process, it calls its initial method. The initial method of class SimplexChannel is transferFrames()(). The definition of this method is given in the  $Edit\ Method\ (POOSL)$  pane of Figure 4. The definition starts with header transferFrames()(). The brackets indicate that methods can have input and output parameters. Clause |aFrame:Frame| declares a local method variable aFrame of data class Frame. The declaration of local variables is followed by the actual body of the method. Message-receive statement in?frame(aFrame) indicates that the process wants to receive (?) message frame with parameter aFrame from channel in. This statement is blocking; it is executed only if some other process executes a corresponding message-send (!) statement of the form in!frame(someFrame).

After the reception of message frame(aFrame) a SimplexChannel executes two statements in parallel. Parallel composition is indicated by the  $par \cdots and \cdots rap$  construct. The first statement of the parallel composition starts by drawing a sample from the Bernoulli distribution and by checking whether this sample denotes success. This operation is performed by sending the message yieldsSuccess to data object errorDistribution. If this data object replies with false the message is lost (statement skip is executed). Otherwise, the SimplexChannel draws a sample

Figure 4. SimplexChannel specification

from the Normal distribution transTimeDistribution by sending it the message next. Consequently, the channel starts to delay for the sample's amount of time units. After this delay, message-send statement out!\*frame(aFrame) is executed. The !\* symbol denotes that the message is sent asynchronously, i.e. the message is lost if no process is currently willing to receive it. The second statement transferFrames()() of the parallel composition is a method call. This statement starts the method, that is currently being executed again in parallel. In this way, the channel is able to transport an unbounded number of incoming messages.

The parallel activities in the *SimplexChannel* do not require any shared data. We could however introduce an instance variable *amountOfFrames* that stores the amount of *Frames*, currently being transported by the channel. Such a variable could be read or assigned a value by any concurrent activity at any instant in time. The modelling languages we discussed in Section 3 do not allow such behaviour to be expressed.

Notice that the behaviour of the *SimplexChannel* is far from trivial. Due to the expressive power of POOSL however, the behaviour can be expressed in only a few lines of easily readable code. This expressive power makes POOSL especially suitable for describing (the behaviour of) complex systems at a high level of abstraction without having to write detailed implementations in some hardware or software description languages such as VHDL or C (the reader is challenged to describe the behaviour of the channel in one of these languages).

#### 5 Tool Support

The drawings we used in the previous section are snapshots taken from an interactive model editing and simulation tool for the SHE method. The tool is used to incrementally specify and modify classes of data, processes and clusters. A specification does not have to be complete before it can be tested and simulated. Using the different buttons on the bottom of the *Drawing* window of Figure 2, the current (partial) model can be executed in different modes of simulation. The messages and parameters that are passed between the different processes and clusters are indicated on the appropriate channels. It is possible to open inspectors on each model part (data objects, process objects and clusters). The inspectors show the current state of each variable; for processes they show the code that is currently being executed as well.

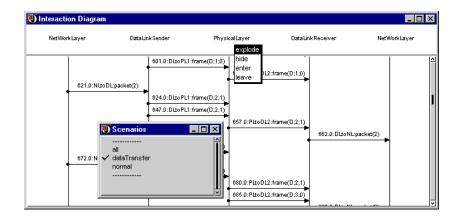

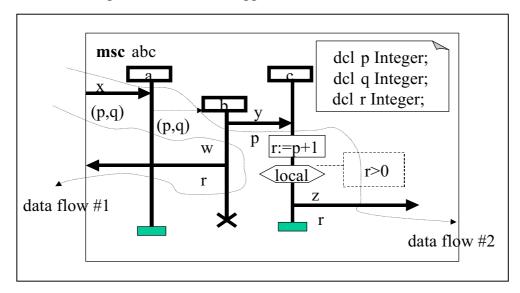

To inspect the history of all messages exchanged between the different entities, interaction diagrams (also called message sequence charts) can be generated automatically. An example of an interaction diagram is shown in Figure 5. The diagram shows the different model entities and the messages exchanged between these entities. For each message, the time, the channel and the parameters are indicated. For instance on time 621.0, message packet with parameter 2 (this is the sequence number of the corresponding Packet data object) is exchanged between the leftmost NetworkLayer and DataLinkSender. Notice that not every instance of message exchange is shown in Figure 5.

Figure 5. Interaction Diagram

The communications inside the *PhysicalLayer* are hidden. They can be made visible, however, by either exploding or entering the *PhysicalLayer*, see Figure 5. Another way to handle the complexity of behaviour is through the concept of *scenario* [1, 11]. A scenario defines a coherent piece of behaviour in terms of the entities (processes, clusters and channels) that are involved in this behaviour. The interaction diagram of Figure 5 visualises the behaviour corresponding to the *dataTransfer* scenario only. This scenario involves the two *NetworkLayers*, the *DataLinkReceiver* and the *PhysicalLayer* as well as channels *NLtoDL*, *DLtoPL1*, *PLtoDL2* and *DLtoNL*. The other entities are invisible.

Using the Interaction Diagrams we have been able to manually estimate the time-out time (of the *Timer*) that establishes an optimal (with respect to throughput) link between the *NetworkLayers*<sup>9</sup>. Counter-intuitively, this optimal time-out appeared to be lying around 27 time units and yields a throughput of 1 packet every 284 units of time. Of course, having to estimate performance figures manually is not desirable. Therefore an important topic of our research concerns the (statistical) estimation of model parameters (such as performance) automatically.

By using a formal verification tool for CCS, we have been able to verify the correctness of an abstract CCS version of the protocol. Even for the relatively simple positive acknowledgement with retransmission protocol we had to make severe abstractions (with respect to real-time and unbounded sequence numbers of packets) to make formal verification feasible. The truth is that the general problem of exhaustive formal verification is either theoretically or practically unsolvable. Therefore we are investigating methods to perform automatic, non-exhaustive verification on full models. In our opinion this is an important and challenging new research topic.

Research is also being carried out into system level synthesis of POOSL specifications. The first results into the mapping of POOSL onto hardware are presented in [8]. For the automatic mapping onto software (C++), promising results have been obtained. Further a system of behaviour-preserving transformations has been developed [1, 16]. Behaviour-preserving transformations allow the architecture of POOSL models to be modified, without changing the functional and communication behaviour.

### 6 Conclusions and Future Research