### Logics for digital circuit verification: theory, algorithms, and applications

Citation for published version (APA):

Janssen, G. L. J. M. (1999). *Logics for digital circuit verification : theory, algorithms, and applications*. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR520460

DOI:

10.6100/IR520460

Document status and date:

Published: 01/01/1999

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 04. Oct. 2023

# Logics for Digital Circuit Verification

Theory, Algorithms, and Applications

G.L.J.M. Janssen

# **Logics for Digital Circuit Verification Theory, Algorithms, and Applications**

## Logics for Digital Circuit Verification Theory, Algorithms, and Applications

#### **PROEFSCHRIFT**

Ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr. M. Rem, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op woensdag 24 februari 1999 om 16.00 uur

door

Gradus Leonardus Johannes Maria Janssen geboren te Oss Dit proefschrift is goedgekeurd door de promotoren

prof.Dr.-Ing. J.A.G. Jess, en prof.dr. J.C.M. Baeten

Copromotor:

dr.ir. C.A.J. van Eijk

#### © Copyright 1999, G.L.J.M. Janssen

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission from the copyright holder.

Druk: Universiteitsdrukkerij Technische Universiteit Eindhoven

#### CIP-DATA LIBRARY TECHNISCHE UNIVERSITEIT EINDHOVEN

Janssen, Gradus L.J.M.

Logics for digital circuit verification: theory, algorithms, and applications / by Gradus L.J.M. Janssen. - Eindhoven: Technische Universiteit Eindhoven, 1999. Proefschrift. - ISBN 90-386-1560-4

**NUGI 832**

Trefw.: digitale geintegreerde schakelingen / digitale systemen ; CAD / correctheidsbewijzen / temporele logica / hardwarebeschrijving / sequentiele machines.

Subject headings: digital integrated circuits / logic CAD / formal verification / temporal logic / sequential circuits.

voor mijn vader

## **Summary**

This thesis presents the results of investigating various logics with respect to their application to verification of digital hardware design. The approach highlights both the end-user aspects and the implementor's aspects.

The thesis is structured in 3 parts: part I discusses verification problems in the area of combinational circuits, part II focuses on sequential circuit verification, and part III presents the software tools that have been developed and discusses details of their implementations. Also, part III contains a number of test cases that exhibit the typical modelling of problems in terms of the investigated logics and shows how they are solved by the presented tools:

- bdd a boolean function manipulation package

- ptl a temporal logic satisfiability checker

- mu a propositional  $\mu$ -calculus tool

- bsn2veri a combinational circuit equivalence checker

- bsn2mc a Fair-CTL model checker

This thesis focuses on techniques for hardware verification. The approach is formal, i.e., mathematical theories will be presented that form the basis for modelling the hardware and reasoning about its behaviour. The work concentrates on decidable theories, for which algorithms exist that can be used to prove certain properties of the circuit. Central to this thesis are the application of the theory and the development of efficient algorithms.

.

## Samenvatting

Dit proefschrift presenteert de resultaten van een onderzoek naar de toepassing van diverse logica's met betrekking tot de verificatie van digitale hardware. De aanpak belicht zowel de eindgebruikeraspecten als ook de aspecten t.a.v. de implementator.

Deze thesis is onderverdeeld in 3 delen: deel I beschouwt verificatieproblemen op het gebied van combinatorische circuits, deel II focusseert op verificatie van sequentiële circuits en deel III presenteert de software pakketten die zijn ontwikkeld en gaat in op de details van hun implementatie. Daarnaast presenteert deel III een aantal voorbeelden die de typische modellering van problemen in termen van de onderzochte logica's duidelijk maken en laat zien hoe deze opgelost worden met de ontwikkelde programma's:

- bdd een pakket voor manipulatie van boolse functies

- ptl een satisfiability checker voor LTL temporele logica

- mu een programma voor propositionele  $\mu$ -calculus

- bsn2veri een equivalentie checker voor combinatorische circuits

- bsn2mc een *model checker* voor Fair-CTL

Deze thesis richt zich vooral op technieken voor hardware verificatie. De aanpak is formeel, d.w.z. mathematische theorieën worden behandeld die de basis vormen voor het modelleren van hardware en het redeneren over het gedrag ervan. We concentreren ons op beslisbare theorieën, waarvoor geldt dat er algoritmen bestaan die gebruikt kunnen worden om zekere eigenschappen van het circuit te bewijzen. Centraal staan de applicatie van de theorie en de ontwikkeling van efficiënte algoritmen.

## **Contents**

| Summary      |                                             | V11 |

|--------------|---------------------------------------------|-----|

| Samenvatt    | ing                                         | ix  |

| 1. Gener     | 1                                           |     |

| 1.1 In       | ntroduction and thesis overview             | 1   |

| 1.2 B        | ackground and acknowledgements              | 3   |

| Verification | n of Combinational Circuits                 | 7   |

| 2. Comb      | national Circuits                           | 9   |

| 2.1 I        | ntroduction                                 | 9   |

| 2.2 B        | oolean functions and combinational circuits | 9   |

| 2.3 B        | oolean network                              | 11  |

| 2.4 H        | ligher-Level descriptions                   | 14  |

| 2.5 C        | ther verification problems                  | 14  |

| 3. Propos    | sitional Logic                              | 19  |

| 3.1 I        | ntroduction                                 | 19  |

| 3.2 T        | he language of propositional logic          | 19  |

| 3.3 T        | ruth table method                           | 23  |

| 3.4 E        | risjunctive normal form                     | 23  |

| 3.5 C        | ontainment (or subsumption)                 | 25  |

| 3.6 In       | nplementation of DNF                        | 26  |

| 4. Binary    | Decision Diagrams                           | 29  |

|              | ntroduction                                 | 29  |

| 4.2 N        | lotation and terminology                    | 29  |

| 43 B         | DD construction                             | 33  |

xii Contents

| Ver | ificat | tion of Circuits with Memory                         | 37         |

|-----|--------|------------------------------------------------------|------------|

| 5.  | Segi   | uential Circuits                                     | 39         |

|     |        | Introduction                                         | 39         |

|     |        | Finite automata and sequential circuits              | 39         |

|     |        | Verification problem                                 | 42         |

|     | 5.4    |                                                      | 43         |

|     |        | Symbolic computation                                 | 46         |

|     |        | - · · · · · · · · · · · · · · · · · · ·              | 51         |

| 6.  | Tem    | nporal Logic                                         | 53         |

|     |        | Introduction                                         | 53         |

|     | 6.2    | A few words about time                               | 54         |

|     | 6.3    | Kripke structures                                    | 54         |

|     |        | Computation tree logic                               | 55         |

|     |        | 6.4.1 Semantics                                      | 56         |

|     |        | 6.4.2 CTL operators                                  | 58         |

|     | 6.5    | CTL model checking                                   | 59         |

|     |        | 6.5.1 Model checking algorithms                      | 61         |

|     | 6.6    | Linear-time temporal logic                           | 63         |

|     | 6.7    | An LTL satisfiability checker                        | 65         |

|     |        | 6.7.1 Parsing an LTL formula                         | 65         |

|     |        | 6.7.2 Normalization                                  | 66         |

|     |        | 6.7.3 Optimization                                   | 67         |

|     |        | 6.7.4 Model construction                             | 68         |

|     | 6.8    | Specification of finite state machines in LTL        | <i>7</i> 7 |

|     |        | 6.8.1 Notational preliminaries                       | 78         |

|     |        | 6.8.2 FSM to LTL transformation                      | 78         |

| 7.  | μ-C    | alculus                                              | 83         |

|     |        | Introduction                                         | . 83       |

|     |        | Syntax                                               | 84         |

|     |        | Semantics                                            | 86         |

|     | 7.4    | Boolean $\mu$ -calculus                              | 88         |

|     | 7.5    | Interpreter for $\mu$ -calculus                      | 97         |

| Pro | gran   | ns and Examples                                      | 101        |

| 8.  | The    | BDD Package                                          | 103        |

|     | 8.1    | Implementation issues                                | 103        |

|     | 8.2    | Dynamic variable ordering                            | 105        |

|     |        | 8.2.1 Principles                                     | 105        |

|     |        | 8.2.2 Implementation issues                          | 106        |

|     |        | 8.2.3 Examples and results                           | 109        |

| 9.  | Apr    | plication of BDDs in a Hardware Description Language | 111        |

| Contents | xiii |

|----------|------|

|----------|------|

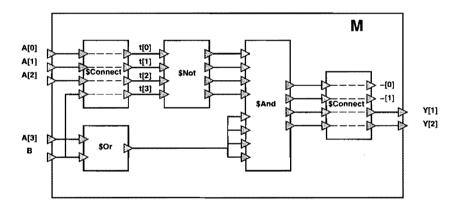

|     | 9.1   | Introduction                              | 111 |

|-----|-------|-------------------------------------------|-----|

|     | 9.2   | A sample HDL                              | 112 |

|     | 9.3   | Source-level transformations              | 117 |

|     | 9.4   | BDD interpretation of behavioural modules | 122 |

|     |       | The HDL verifier                          | 127 |

|     | 9.6   | Dealing with large circuits               | 129 |

|     |       | 9.6.1 Cutpoints and BDDs                  | 130 |

|     |       | 9.6.2 Hunting for correspondences         | 131 |

|     |       | 9.6.3 Cutpoint guessing                   | 131 |

|     |       | 9.6.4 Resolving false negatives           | 132 |

|     |       | 9.6.5 Experiments                         | 133 |

| 10. | The   | PTL Program                               | 137 |

|     | 10.1  | Introduction                              | 137 |

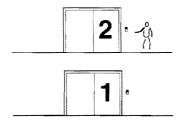

|     | 10.2  | A 2-story elevator                        | 137 |

|     |       | Chinese ring puzzle                       | 142 |

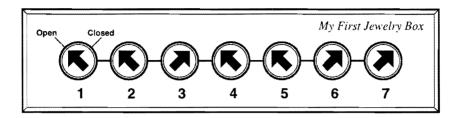

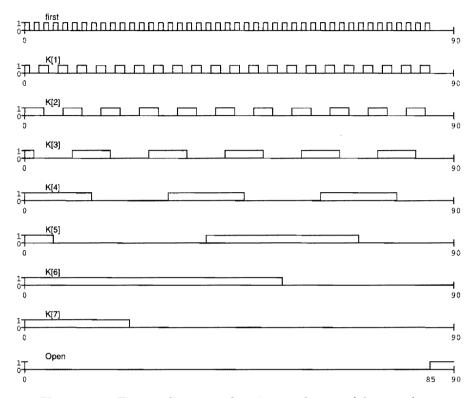

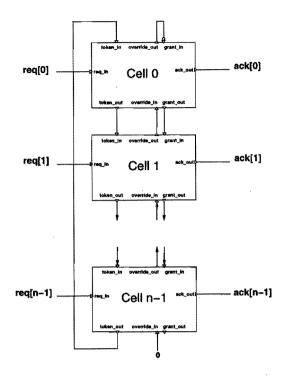

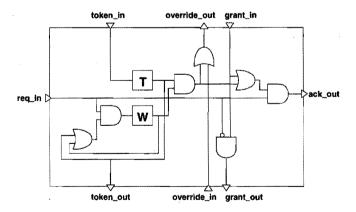

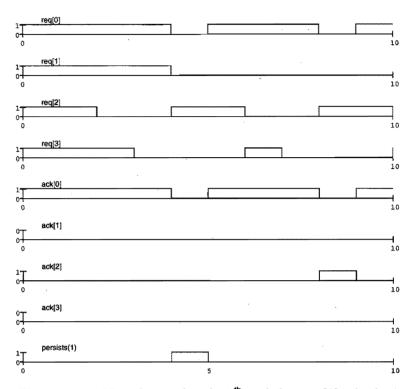

|     | 10.4  | Synchronous bus arbiter                   | 144 |

|     |       | 10.4.1 Reachability analysis              | 149 |

|     | 10.5  | Discussion                                | 150 |

| 11. | Con   | clusions                                  | 151 |

|     | 11.1  | Contributions and achievements            | 151 |

|     | 11.2  | Directions for future research            | 153 |

| Ref | erenc | res                                       | 157 |

| Bio | grapl | nv                                        | 161 |

|     | OI    | · ·                                       |     |

## **General Introduction**

#### 1.1 Introduction and thesis overview

This thesis is about verification. The purpose of this general introduction is to set the context for our meaning of the term 'verification' and to argue why verification is an important subject in the realm of digital circuit design. We also give an overview of the contents of the thesis. Lastly, my personal history of work in this field is narrated and acknowledgements to people that influenced me are made.

In many industrial production areas, quality is of utmost importance. And quality entails measurements and standards: the standards set the goals and by measurements it is verified whether these goals are met. In the design of complex electronic circuits it is no longer possible to ensure their correctness by mere visual inspection (the features on a chip are simply too small to see with the naked eye). But even the design data or blueprints, i.e., the schematics, hardware description language texts, and layouts, contain so much detail that inspection by a human designer becomes a truly Herculean job. It is not just the complexity, i.e., large scale of integration, that causes problems; also the intrinsic 'go-or-nogo' characteristic of the subject matter makes it hard to devise good and simple tests. The effect of a single wrong connection during design, or a tiny oversight (read: bug) by the programmer of a logic synthesis tool, may render a whole batch of wafers useless. The sooner the flaw is discovered the better, and the cheaper. Not to mention all the things that can go wrong during the actual chip fabrication process. However, that is not the subject of this thesis.

A first step towards a successful production of a chip is that its design is functionally correct. Correctness is not an absolute notion. One can only meaningfully talk about the correctness of a design with respect to a some predefined specification (the standard). By means of measurement or testing it is possible to assess the quality of a design. But, (non-exhaustive) testing can only indicate the presence of errors; it cannot guarantee their absence. This is a slightly rephrased quotation from Edsger Dijkstra [Dijks76] who was then talking about the correct construction of computer programs. In this dissertation we investigate the applicability of formal methods in verifying the functional correctness of designs for digital circuits. For that we need two things: a mathematical model for the behaviour of the circuit and a theory that allows 'mechanical' reasoning within that model. We use the word 'functional' to stress a certain narrowing of, or abstraction from, all possible issues involved; it is the behaviour that fits a certain model of the circuit that we are interested in, and it is with respect to the models that we tailor the correctness problems and their solutions.

A major part of this thesis is concerned with the practical issues that arise when implementing these formal methods as a computer program suitable for use by electronic circuit designers. Several computer-aided verification tools were developed as part of this thesis work:

- bdd a package for logic function manipulation

- ptl a propositional temporal logic satisfiability checker

- mu implements an extended propositional  $\mu$ -calculus

- bsn2veri a combinational circuit equivalence checker

- bsn2mc a Fair-CTL model checker

Undoubtedly, the design process of computer algorithms and their implementation in a certain programming language parallels the design of integrated circuits. Many mathematical concepts and techniques are similar, if not the same, at least when regarded at a certain level of abstraction. (There is no equivalent to a physical MOS transistor in a programming language; but when modelled as a switch, the ensuing logic circuit may well be simulated by if-then-else statements). In fact, computer sciencists recognized this and not surprisingly they were the ones that coined the phrase 'VLSI programming' [Niess88]. True, much of the earlier work on formal verification was initiated by mathematicians and computer scientists. Unfortunately, this has led to the situation where much of this work was not accepted by the electrical engineering community and the CAD tool makers. Also, the goals they set out do not always coincide with the needs of a hardware designer; there often exists a large gap between theoretical results and useful applications. We should not forget that the main purpose of computer aided design is to actually help a designer in getting his job done and not to put up yet another barrier for him to cross.

This thesis focuses on techniques for hardware verification. The approaches are formal, i.e., mathematical theories will be presented that form the basis for modelling the hardware and reasoning about its behaviour. Moreover, we concentrate

on decidable theories, this means that algorithms exist that can be used to prove certain properties of the circuit. Central to this thesis are the applications of the theory and the development of efficient algorithms.

This thesis consists of three parts: part I deals with combinational circuits, part II treats sequential circuits, and part III presents practical approaches to solving the problems raised in the preceding parts. It is valid to say that the first two parts mainly define a number of important verification problems and the necessary theory to describe them, and that in the last part of this thesis choices are made as to how to practically solve those problems in the form of computer programs. The last part also presents examples and quantitative data of experiments. The three parts are entitled:

Part I: Verification of Combinational Circuits.

In this part the relations between combinational circuits, propositional logic, and canonical representations of switching functions (DNF, BDD) are made explicit.

Part II: Verification of Circuits with Memory.

Here we extend the combinational circuit model to include time-dependent behaviour. This leads to the introduction of the propositional temporal logics LTL and CTL, and an even more powerful system:  $\mu$ -calculus.

Part III: Programs and Examples.

The theory presented in the first two parts culminated in the development of several verification tools: the ptl program for temporal logic, the mu program for  $\mu$ -calculus, the bsn2veri program for combinational circuit verification based on a hardware description language, and last but not least a BDD package that forms the core of all the aforementioned programs. Part III will discuss some of the more interesting implementational aspects of these programs, in sofar as they were not already covered in the preceding parts, and, more importantly, we will discuss how to effectively use those programs by studying a number of example problems.

#### 1.2 Background and acknowledgements

It has taken me quite some time to prepare this thesis. The best excuse I can offer is that the field of CAD for electronic circuits is so exciting that it is hard for me to tear myself loose from the daily work and sit back and reflect on my own specialized field of hardware verification, let alone to do nothing else but concentrate on writing a whole thesis. The 'trouble' is that my interests are rather diverse, and my character forces me to not be satisfied until a new idea or theory or algorithm is fully understood, which often results in writing my own program for the particular problem just to see what is involved and thereby creating a framework for exploring my own ideas and hopefully to be able to come up with

improvements. So, over the years I have developed quite a few programs on a variety of subjects. I once wrote some language development tools, like an LL(1) checker and a program that draws syntax diagrams. I was involved in the design of the Eindhoven Schematic Entry tool "Escher" under the NELSIS project; a program that was later enhanced by some of my students to mature as "Escher+" [Janss89], and that now is in the able hands of Hans Fleurkens who turned it into a very flexible and general graphic design entry and user-interface. Within the same project, I developed the hardware description language NDML to be used with the piece-wise linear simulator also developed in our group [Janss86]. My first contact with temporal logic was when I was working at Philips Telecommunications Industry in Hilversum where Ron Koymans was doing his master thesis work under the guidance of (now Prof.) Jan Vytopil. Their goal was to formalize the message passing semantics of the CCITT programming language CHILL. I was intrigued by the many obscure symbols and seemingly heavy mathematics they were using in their writings. When a few years later I was confronted with the work of Amir Pnueli and Zohar Manna [Manna81] on propositional temporal logic, I decided to write my own satisfiability checker for LTL and apply it to the verification of digital systems. Fortunately, this work became part of the ASCIS project, which gave me a willing audience to promote my ideas and results [Raner93, Janss92]. The initial driving force for my work on temporal logic was fueled by a challenge proposed by Prof. Lars Philipson of Lund University, Sweden [Phili89]. His skepticism towards the applicability of temporal logic to prove correctness of state machines culminated in a hectic E-mail conversation, ending in an invitation to hop over to Lund and explain it all in person. (Those were the good old days.)

I am obliged to thank many people that in one way or other have 'educated' me to become the person that I am now. First of all I want to thank Professor Jochen Jess who has been, and still is, a most fair boss, an inspiring tutor, and amiable colleague (and a good drummer). I praise myself lucky to have the opportunity to work with so many good-hearted, honest, hard working, and outstanding colleagues in the Design Automation Group: Lia, Frans, Jos, Michel, en Oege, thanks. My office mates over the years deserve special mention: Hans Zuidam, André Slenter, Ed Huijbregts, and Pieter, a.k.a. Tiggr, Schoenmakers. They never tired of having to listen to my ranting about bugs, troubles, errors, frustrations, et cetera. I thank all my students who have helped me with the implementations of some of the algorithms, and doing much of the testing and debugging. The most appreciated, but for them less obvious, side-effect was that they forced me to keep ahead of them and to acquire an intimate understanding of the subject at hand. They also kept me young, in spirit that is. I salute all the doctoral students that I saw arrive in our group, do their excellent work, and leave again (veni, vidi, vici). I cannot resist to single out Jose Pineda who is a dear, and now unfortunately distant, friend, and Gjalt de Jong who was my sparring partner in the verification arena from the start. He handed over the towel to a knowledgeable substitute in the person of Koen van Eijk. Special thanks go to the members of the

BSN group at IBM T.J. Watson Research Center and their manager Marshall Schor (who generously hosted me during the past five summers), and to Ton Kostelijk and Willem Rovers of Philips Research. I hope we can continue our cooperation in the future.

# Verification of Combinational Circuits

The first part of this thesis consists of three chapters. Chapter 2 defines combinational circuits and states the combinational circuit equivalence problem. A more general problem that arises when correspondences between circuit inputs and outputs are not known is briefly discussed. It presents an elegant formulation of a general-purpose permutator circuit. Chapter 3 introduces propositional logic and derives an important representation for its expressions: disjunctive normal form. This form will be used again in chapter 6 in the implementation of an LTL satisfiability checker. Chapter 4 concludes this part with an introduction to binary decision diagrams (BDDs). All programs presented in this thesis are based on these BDDs.

## **Combinational Circuits**

#### 2.1 Introduction

In this chapter we define the notion of a combinational circuit and introduce an important verification problem, namely combinational circuit equivalence. We show how boolean functions can be associated with the network graph representation of a combinational circuit. It is assumed that the correspondences between inputs and outputs of the circuits to be compared are known beforehand. In the last section we drop this restriction and consider a more general verification problem.

#### 2.2 Boolean functions and combinational circuits

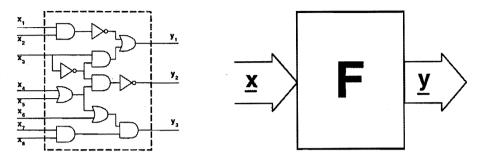

Let  $B = \{0, 1\}$  be the set of boolean truth values: 0 stands for false, and 1 stands for true. We consider functions  $f: B^n \longrightarrow B, n \ge 0$ , and more generally, m element vectors of such functions  $F: B^n \longrightarrow B^m, m > 0$ . Geometrically speaking we may say that F maps a point in boolean n space to a point in boolean m space. A reallife realization or implementation of F is called a combinational logic circuit. In a combinational circuit the 0 and 1 values are usually related to non-overlapping voltage intervals; the functions are realized by a network of primitive logic operator cells or gates. When the argument value  $\underline{x}$  to the function F is supplied to the inputs of the network, the function value  $\underline{y} = F(\underline{x})$  is observed at the outputs of the network. F is an abstract, mathematical model (black-box) for the behaviour of the combinational circuit. It does not necessarily tell us anything about its structure. Figure 2.1 illustrates the correspondence between a combinational circuit (left) and its black-box functional model (right). In fact, the logic

circuit itself is a model for a transistor level circuit.

Combinational Circuits

Figure 2.1. Schematic of combinational circuit and its black-box model.

A particular (vector component) function  $f: B^n \longrightarrow B$  may be defined in various ways. Usually one introduces place-holder symbols, say  $x_1, x_2, \cdots, x_n$ , to represent arbitrary argument values and then defines the result  $f(x_1, x_2, \cdots, x_n)$  of applying the function to those arguments by some logic expression involving the  $x_i$ 's. For our example circuit in figure 2.1 we could write:

```

\begin{split} f_1\left(\,x_1,x_2,x_3,x_4,x_5,x_6,x_7,x_8\,\right) &= \neg\,\left(\,x_1\,\wedge\,x_2\,\right) \vee \left(\,x_3\,\wedge\,\neg\,x_3\,\right), \\ f_2\left(\,x_1,x_2,x_3,x_4,x_5,x_6,x_7,x_8\,\right) &= \neg\,\left(\,\neg\,x_3\,\wedge\,\left(\,x_4\vee x_5\,\right)\,\right), \\ f_3\left(\,x_1,x_2,x_3,x_4,x_5,x_6,x_7,x_8\,\right) &= \left(\,x_4\vee x_5\vee x_6\,\right) \wedge \left(\,x_7\,\wedge\,x_8\,\right). \end{split}

```

Intuitively, the meaning of the logic expressions on the right-hand side should be clear. In a following chapter we will formally define a language of logic expressions.

It should be obvious that the position of a place-holder variable in the argument list is very crucial; above this has been indicated using subscripts. Generally,  $f(x_1, x_2) \neq f(x_2, x_1)$ , and in order to compare two functions, no matter in what way they are represented, the correspondence between their sets of place-holder variables has to be known in advance. With this in mind, the following definition makes sense:

#### **Definition 2.1** (Functional circuit equivalence).

Two combinational circuits  $C_1$  and  $C_2$  are said to be functionally equivalent if their corresponding black-box models  $F_1$  and  $F_2$  are identical (vector) functions.

In practice, this means that we assume the two circuits to have identical input and output labelling (symbols), and that the correspondence is simply defined as identity of these labels. We can now state the main problem that we will address in this chapter:

#### COMBINATIONAL CIRCUIT EQUIVALENCE

**INSTANCE:** Two combinational circuits  $C_1$  and  $C_2$  over the same sequence of inputs and outputs.

**QUESTION:** Are both circuits functionally equivalent? That is, do both circuits for all possible combinations of input values yield the same values at their corresponding outputs?

Note that the formulation of the above question already hints at a possible solution: exhaustive simulation. Once we have established a model for a combinational circuit suitable to automatic evaluation (= operational model), the equivalence problem can be solved by simulating both circuits for all possible combinations of input values, each time checking whether the corresponding output pairs evaluate to the same value. However, simulation is not the topic of this thesis; our goal is to develop verification algorithms that answer this question. Before we do so we first need to define a combinational circuit precisely, and show how we can attach a functional meaning to it. Then the equivalence problem can be rephrased in terms of the circuits' associated functions.

#### 2.3 Boolean network

We define a boolean network as a graph: the vertices of the graph represent the gates of the circuit; the edges represent the connections from a gate output to other gates' inputs. More formally,

**Definition 2.2** A boolean network is a vertex-labelled directed graph G(V, E). The set of vertices V consists of the three non-overlapping sets G ates, Inputs, and Outputs, with

- Gates: a finite set of gates. Each gate is labelled by a logical operator symbol chosen from the set {¬, ^, ∨}. Note that since the ^ and ∨ operators are commutative and associative it is not necessary to define an ordering on the incoming edges to such a vertex. ¬ gates have a single incoming edge; ^ and ∨ gates have 2 or more incoming edges.

- Inputs: a finite set of circuit inputs, also called the primary inputs. A primary input cannot have incoming edges.

- Outputs: a finite non-empty set of circuit outputs, also called the primary outputs. A primary output has a single incoming edge and no outgoing edges.

- The directed edges E ⊆ (Gates ∪ Inputs) × (Gates ∪ Outputs) represent the connections between gates, primary inputs, and primary outputs. Note that edges between inputs and edges between outputs are not allowed. It is tempting to impose the requirement that the graph be acyclic. However, this is not a necessary condition for a circuit to be combinational [Malik93]. However, for simplicity we do here assume acyclicness.

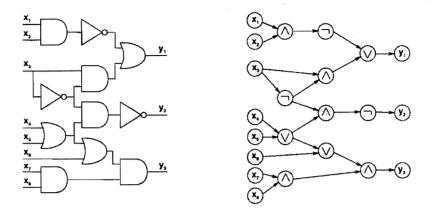

Figure 2.2 shows a circuit schematic and its associated boolean network graph.

Figure 2.2. Circuit schematic and its boolean network graph.

The following additional definitions for a boolean network will prove to be useful:

**Definition 2.3** The direct fanin of a vertex v is the set of its immediate predecessor vertices:

$$fanin(v) = \{u \mid (u, v) \in E\}.$$

Note that for a primary input  $x_i$ , fanin  $(x_i) = \emptyset$ .

**Definition 2.4** The direct fanout of a vertex v is the set of its immediate successor vertices:

fanout

$$(v) = \{w \mid (v, w) \in E\}.$$

Note that for a primary output  $y_k$ , fanout  $(y_k) = \emptyset$ .

We are now ready to define the meaning (semantics) of a combinational circuit. We do this by giving an inductive definition for its (black-box) boolean function vector F.

**Definition 2.5** With each combinational circuit, represented by an acyclic boolean network graph according definition 2.2, we associate a vector of boolean functions  $F = [f_1, f_2, \cdots, f_m]$ , with m = |Outputs|. We first impose a total ordering on the set of primary Inputs =  $\{x_1, x_2, \cdots, x_n\}$  and primary Outputs =  $\{y_1, y_2, \cdots, y_m\}$ , e.g. by the indices. All component functions  $f_k$  of F will have the same domain  $B^n$  and co-domain B; we abbreviate  $x_1, x_2, \cdots, x_n$  to X.

- Each primary input  $x_i$  is associated with a projection function  $f_{x_i} = \lambda X. x_i$ .

- Each gate g is associated with a function  $f_g = \lambda X$ .  $\Phi_{u \in fanin(g)} f_u(X)$ , where  $\Phi$  is the reduction operator corresponding to

the operator labelling the gate, e.g. if the label of g is  $\land$  then  $\Phi = \bigwedge$ .

- With each primary output  $y_j$  we associate a function  $f_{y_j} = f_{fanin(y_j)}$ .

- The boolean functions  $f_k$  associated with the circuit are the functions we associate with the primary outputs  $y_k$ , thus  $f_k = f_{v_k}$ .

**Example 2.1** Definition 2.5 applied to the circuit of figure 2.2 results in  $F = [f_1, f_2, f_3]$ , with

$$\begin{array}{l} f_1 = f_{y_1} = \lambda x_1, x_2, x_3, x_4, x_5, x_6, x_7, x_8. (\neg (x_1 \wedge x_2)) \vee (x_3 \wedge (\neg x_3)), \\ f_2 = f_{y_2} = \lambda x_1, x_2, x_3, x_4, x_5, x_6, x_7, x_8. \neg ((\neg x_3) \wedge (x_4 \vee x_5)), \text{ and} \\ f_3 = f_{y_3} = \lambda x_1, x_2, x_3, x_4, x_5, x_6, x_7, x_8. ((x_4 \vee x_5) \vee x_6) \wedge (x_7 \wedge x_8). \end{array}$$

□ example 2.1

We conclude this subsection with a restatement of the equivalence problem.

#### COMBINATIONAL CIRCUIT EQUIVALENCE

**INSTANCE:** Two combinational circuits  $C_1$  and  $C_2$  represented by their boolean network graphs  $G_1$  (Gates<sub>1</sub>  $\cup$  Inputs  $\cup$  Outputs,  $E_1$ ) and  $G_2$  (Gates<sub>2</sub>  $\cup$  Inputs  $\cup$  Outputs,  $E_2$ ) respectively.

**QUESTION:** Are both circuits functionally equivalent? That is, does  $F_1 = F_2$  hold for the associated vectors of boolean functions  $F_1$  and  $F_2$ ?

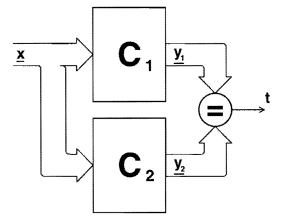

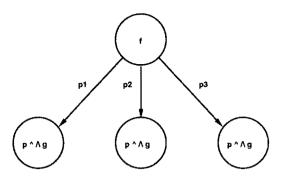

Figure 2.3 presents this problem in the form of a picture.

**Figure 2.3.** Combinational circuit equivalence:  $C_1 = C_2$ ?

The single bit output represents the function  $t = \lambda \underline{x}$ .  $(F_1(\underline{x}) = F_2(\underline{x}))$ . The circuits are equivalent if and only if this function is a tautology, i.e.,  $\forall_{\underline{x} \in B^n} t(\underline{x}) = 1$ .

#### 2.4 Higher-Level descriptions

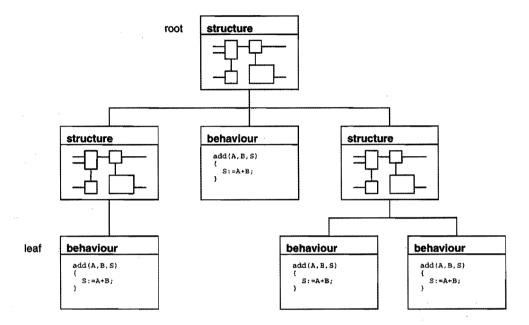

A representation of a combinational circuit by its boolean network graph is called a gate-level description. It is a convenient representation (encoding) for many problems relating to logic optimization and synthesis. The ratio of functionality to representation size at the gate level is quite small: to implement a simple arithmetic function over n-bit numbers requires a large number of gates. Thus we look for more efficient representations yielding a larger ratio. Basically, two approaches come to mind:

- Introduce hierarchy. This will allows us to exploit the fact that in many

designs the same subcircuits are used over and over again. In a hierarchical

description a subcircuit representing a certain function is defined only once,

and all its uses are references instead of copies. The effect is twofold:

descriptions become more compact and algorithms processing them are

faster (because of data sharing).

- 2. Introduce richer domains. Instead of having to express all functionality in terms of operations on boolean variables, we allow a designer to use enumerated types, arrays of booleans, various number types, records, et cetera. Each type comes with a convenient set of operations.

In many hardware description languages both approaches are combined. We will present such a language in chapter 10.

#### 2.5 Other verification problems

Figure 2.4. Phase and permutation independent comparison.

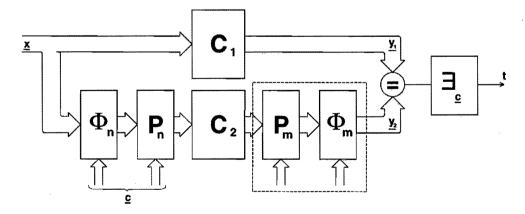

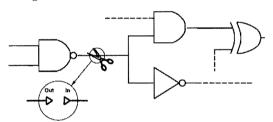

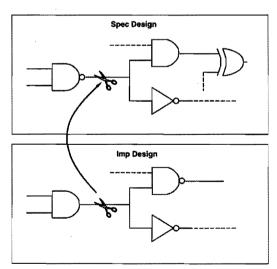

The problem of comparing two circuits for equivalence becomes much harder when the correspondences between their inputs and outputs are not known in advance. To make the equivalence question even more general, one could also drop the assumption that the phase (or polarity) of corresponding inputs and outputs is the same. By the latter we mean whether or not a certain signal is complemented with respect to a reference signal. In other words, we are considering equivalence modulo complementation: we might know that two inputs  $x_i$  and  $x_j$  correspond but they still might carry signal values that are each others complement, then  $x_i = \neg x_j$  holds. We are facing the problem of phase and permutation independent boolean comparison, see e.g. [Mohnk93]. The general setting of this problem is depicted in figure 2.4.

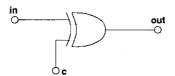

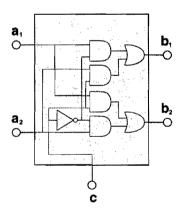

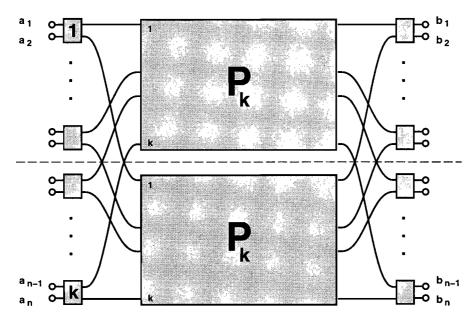

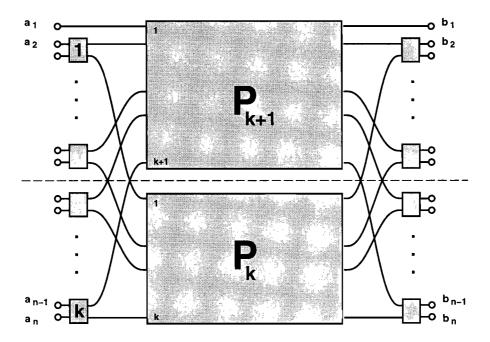

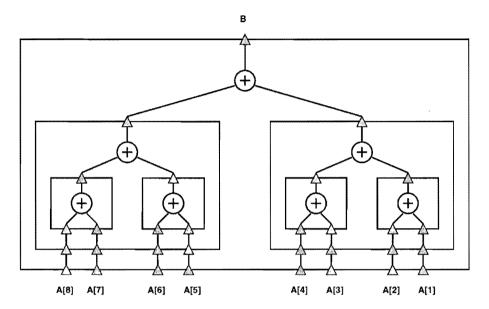

Often the output correspondence is known so the dashed part in figure 2.4 may be left out.  $\Phi_n$  stands for an n-bit phasor circuit;  $P_n$  is an n-bit permutator circuit. Both introduce a number of control inputs  $\underline{c}$  that are to be smoothened out by the  $\exists_{\underline{c}}$  block on the right. In fact what we are asking is whether an assignment to the control inputs  $\underline{c}$  exists that makes the corresponding outputs of  $C_1$  and  $C_2$  identical for all assignments to the primary inputs  $\underline{x}$ . The phasor circuit is easily realized by XOR gates (see figure 2.5). The output of a 1-bit phasor equals its input when the control input c is low (0); the output is the complement of the input when c is high (1). A number of c control variables will be needed to generate the c possible phase assignments to an c-bit input vector  $\underline{x}$ .

Figure 2.5. A 1-bit phasor circuit.

A permutator circuit causes its inputs to be connected to its outputs according to a certain permutation; in fact, it is a particular type of controlled switch. Its precise implementation will be explained shortly. Clearly, the permutator needs a minimum of  $\lceil 2\log(n!) \rceil$  control variables. In [Corme90] it is suggested to implement a permutator using the same structure as a sorting network by replacing the comparator nodes by 2-input, 2-output switches. It can then be shown that a number of  $c_n = n \cdot 2\log(n) - n/2$  control variables is required, with the restriction that n is a power of 2. Table 2.1 lists  $c_n$  for some practical values of n together with related quantities.

| n | $\lceil^2 \log(n)\rceil$ | n!  | $\lceil^2 \log(n!)\rceil$ | Cn |

|---|--------------------------|-----|---------------------------|----|

| 1 | 0                        | 1   | 0                         | 0  |

| 2 | 1                        | 2   | 1                         | 1  |

| 3 | 2                        | 6   | 3                         | 3  |

| 4 | 2                        | 24  | 5                         | 6  |

| 5 | 3                        | 120 | 7                         | 8  |

| 6 | 3                        | 720 | 10                        | 12 |

| n   | $\lceil 2\log(n) \rceil$ | n!                    | \[ \bigsize \frac{1}{2}\log(n!) \right] | c <sub>n</sub> |

|-----|--------------------------|-----------------------|-----------------------------------------|----------------|

| 8   | 3                        | 40320                 | 16                                      | 20             |

| 16  | 4                        | 2.1 10 <sup>13</sup>  | 45                                      | 56             |

| 32  | 5                        | 2.6 10 <sup>35</sup>  | 118                                     | 144            |

| 64  | 6                        | 1.3 10 <sup>89</sup>  | 296                                     | 352            |

| 128 | 7                        | 3.9 10 <sup>215</sup> | 717                                     | 832            |

| 256 | 8                        | 8.6 10 <sup>506</sup> | 1684                                    | 1920           |

**Table 2.1.** Number of control variables  $c_n$  in 'butterfly' permutator  $P_n$ .

The general n-bit permutator circuit  $P_n$  can be inductively defined as follows.

For the 1 bit case (n = 1) the identity is the only possible permutation and the

permutator circuit P<sub>1</sub> is a simple connection from input to output:

$$P_1 = a_1 b_1$$

• In case n = 2 two permutations exist: either the inputs are directly connected to the outputs, i.e.,  $b_1 = a_1$  and  $b_2 = a_2$ , or they are cross-connected, i.e.,  $b_1 = a_2$  and  $b_2 = a_1$ .

$$P_2 =$$

We see that  $P_2$  is realized by two multiplexors: if c = 0 then input  $a_1$  is passed on to output  $b_1$ , and  $a_2$  is passed on to  $b_2$ , else, i.e., c = 1,  $a_1$  appears at  $b_2$  and  $a_2$  at  $b_1$ .

• For  $n \ge 3$ ,  $P_n$  is a network consisting of a  $P_{\left\lfloor \frac{n+1}{2} \right\rfloor}$  circuit, a  $P_{\left\lfloor \frac{n}{2} \right\rfloor}$  circuit, and

$2 \cdot \left\lfloor \frac{n}{2} \right\rfloor$  basic  $P_2$  circuits. The number of control variables  $c_n$  equals the number of  $P_2$  nodes in  $P_n$ . This number can be found by solving the following recurrence equation:

$$c_n = c_{\left\lfloor \frac{n+1}{2} \right\rfloor} + c_{\left\lfloor \frac{n}{2} \right\rfloor} + 2 \cdot \left\lfloor \frac{n}{2} \right\rfloor$$

, with intial values  $c_1 = 0$  and  $c_2 = 1$ .

It is natural to treat odd and even n separately. For even  $n=4,6,\cdots$ ,  $P_n$  has the following structure, where  $n=2\cdot k$ :

For odd  $n=3,5,\cdots$ ,  $P_n$  has the following slightly different structure (now  $n=2\cdot k+1$ ):

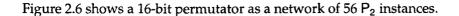

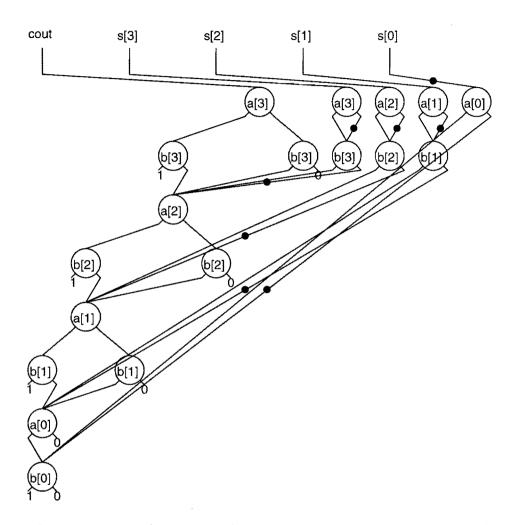

Figure 2.6.  $P_{16}$  permutator network.

It turns out that phasor and permutator circuits can be compactly represented by BDDs (to be discussed in chapter 4). The BDD size of  $\Phi_n$  is  $2 \cdot n$ . The size for a permutator  $P_n$  is  $c_n + n$  in case of an optimal variable ordering. Later it will be shown that existential quantification over all control variables can also be efficiently implemented as an operation on a BDD. However, in combination with a circuit  $C_2$  (figure 2.4) the BDD sizes tend to grow unacceptably. Table 2.2 convincingly indicates this when we choose  $C_2$  to be an adder. (The BDD sizes reported here do not count the constant nodes; both complemented edges and inverted-input edges are used.)

|   |    |                   | BDD size           |                |                            |

|---|----|-------------------|--------------------|----------------|----------------------------|

|   | n  | c <sub>n</sub> +n | add <sub>n/2</sub> | $\Phi_n + P_n$ | $\Phi_n + P_n + add_{n/2}$ |

|   | 2  | 3                 | 2                  | 5              | 5                          |

|   | 4  | 10                | 5                  | 14             | 79                         |

| - | 6  | 18                | 10                 | 24             | 1538                       |

|   | 8  | 28                | 15                 | 36             | 47876                      |

|   | 10 | 36                | 20                 | 46             | >200000                    |

**Table 2.2.** Adder circuit with phasor and permutator at its inputs.

## **Propositional Logic**

#### 3.1 Introduction

In this chapter we will look at the theory of propositional logic. It is by far the most commonly used mathematical framework in today's logic synthesis tools. It nicely fits the modelling of combinational circuits. Since our formalism constitutes a decidable theory, it is readily implemented in a computer program. We start with a brief overview of the theory and main results of propositional logic. We will hint at some practical applications and show some implementation details of the computer programs that were developed.

We will later see that many of the results need only slightly be adjusted and extended for the temporal case. Our aim is to provide enough of a mathematical basis to appreciate the engineering applications we have in mind. Therefore, theorems will often be stated in an informal way and their proofs are mostly only hinted upon. A rigorous treatment of the matter may be found in the many books on logic [Galli87]. Our goal is to explain what it means when we say that a proposition is satisfiable and show several approaches to implement such a satisfiability test.

#### 3.2 The language of propositional logic

We introduce Propositional Logic as a language PL over an alphabet AP of atomic propositions and we will assign a meaning to each string (proposition) of the language by means of a truth assignment.

**Definition 3.1** AP =  $\{p_0, p_1, p_2, \dots\}$  is a countably infinite set of atomic propositions.

To denote an arbitrary atomic proposition we will use the letters P, Q, R, ....

**Definition 3.2** PL is the language defined by the following grammar:

```

formula ::= P

i '¬' formula

i '(' formula ( '∧' i '∨' ) formula ')' .

where P is an atomic proposition taken from AP.

```

The symbols  $\neg$ ,  $\wedge$ , and  $\vee$  are called the logical operator symbols, sometimes called the logical connectives. In the sequel, the letters A, B, C,  $\cdots$  will be used to denote arbitrary formulas of PL.

**Definition 3.3** A function  $f: B^n \longrightarrow B$  is called an n-ary boolean function. The set  $B = \{0, 1\}$  is the set of truth values; 0 stands for false and 1 stands for true.

**Definition 3.4** A function  $v : AP \longrightarrow B$  that assigns to each atomic proposition a truth value is called a *valuation function* or *truth assignment*.

The semantics of formulas is defined by associating a function with each formula. This function is the extension  $\hat{\mathbf{v}}: PL \longrightarrow B$  of  $\mathbf{v}$  under the usual interpretation of the logical operator symbols. The interpretation of  $\neg$  is the function  $H_{\neg}: B \longrightarrow B$  defined in table 3.1.

| Р | H <sub>¬</sub> (P) |

|---|--------------------|

| 0 | 1                  |

| 1 | 0                  |

Table 3.1. Semantics of ¬.

The interpretation of the  $\land$  connective is the function  $H_{\land}: B \times B \longrightarrow B$ , and  $\lor$  is interpreted by the function  $H_{\lor}: B \times B \longrightarrow B$ . Both are defined in table 3.2. (It is easy to extend these functions to apply to more than two arguments:  $H_{\land}$  will be 1 only if all arguments are 1;  $H_{\lor}$  will be 1 if at least one argument is 1.)

| Р | Q | $H_{\wedge}(P,Q)$ | $H_{\vee}(P,Q)$ |

|---|---|-------------------|-----------------|

| 0 | 0 | 0                 | 0               |

| 0 | 1 | 0                 | 1               |

| 1 | 0 | 0                 | 1               |

| 1 | 1 | 1                 | 1               |

**Table 3.2.** Semantics of  $\wedge$  and  $\vee$ .

**Definition 3.5** Let v be a valuation function, then  $\hat{v}$  is inductively defined by:

$$\hat{\mathbf{v}}(P) = \mathbf{v}(P)$$

$$\hat{\mathbf{v}}(\neg A) = H_{\neg}(\hat{\mathbf{v}}(A))$$

$$\hat{\mathbf{v}}((A \land B)) = H_{\wedge}(\hat{\mathbf{v}}(A), \hat{\mathbf{v}}(B))$$

$$\hat{\mathbf{v}}((A \lor B)) = H_{\vee}(\hat{\mathbf{v}}(A), \hat{\mathbf{v}}(B))$$

**Definition 3.6** Let PROP(A) stand for the set of distinct atomic propositions occurring in the formula A. PROP:  $PL \longrightarrow 2^{AP}$  is inductively defined by:

$$PROP(P) = \{P\}$$

$$PROP(\neg A) = PROP(A)$$

$$PROP((A \land B)) = PROP(A) \cup PROP(B)$$

$$PROP((A \lor B)) = PROP(A) \cup PROP(B)$$

Since A is a finite string, PROP (A) is finite too.

**Definition 3.7** Given a formula A with PROP(A) = { $p_1, p_2, \dots, p_n$ }, its associated boolean function  $f: B^n \longrightarrow B$  is  $f = \lambda p_1, p_2, \dots, p_n$ .  $\hat{v}(A)$ .

With the semantics defined, we can now define satisfiability of a formula:

**Definition 3.8** A valuation v satisfies a formula A, denoted  $v \models A$ , if and only if  $\hat{v}(A) = 1$ .

**Definition 3.9** ⊨ A expresses that all valuations satisfy the formula A. Equivalently, A is called a tautological formula or tautology.

The satisfiability problem in PL asks whether a valuation exists that makes a given formula true. The tautology problem asks whether  $\models$  A holds for a particular formula A. This latter problem may be stated as a satisfiability problem: to check whether  $\models$  A holds it suffices to show that there is no valuation  $\lor$  such that  $\lor$   $\models$  ¬A holds. If one exists it follows that A is not a tautology. Be aware that both problems are not of the same complexity; satisfiability is NP-complete, whereas tautology is not even known to be in NP (in fact it is co-NP-complete).

**Definition 3.10** Two formulas A and B are said to be logically equivalent,

denoted A = B, iff  $\hat{v}(A) = \hat{v}(B)$  for all valuations v.

**Theorem 3.1** For all propositions A, B, C the following properties hold:

$$((A \lor B) \lor C) \simeq (A \lor (B \lor C))$$

$$((A \land B) \land C) \simeq (A \land (B \land C))$$

$$(A \lor B) \simeq (B \lor A)$$

$$(A \land B) \simeq (B \land A)$$

$$(A \lor (B \land C)) \simeq ((A \lor B) \land (A \lor C))$$

$$(A \land (B \lor C)) \simeq ((A \land B) \lor (A \land C))$$

$$\neg (A \lor B) \simeq (\neg A \land \neg B)$$

$$\neg (A \land B) \simeq (\neg A \lor \neg B)$$

$$(A \lor A) \simeq A$$

$$(A \land A) \simeq A$$

$$(A \land A) \simeq A$$

$$(A \land (A \lor B)) \simeq A$$

$$(A \land (A \lor B)) \simeq A$$

*Proof:* Use the properties of the underlying interpretation functions  $H_{\neg}, H_{\wedge}$  , and  $H_{\vee}.$

□ theorem 3.1

We see that the syntax for formulas is rather restrictive. We often define some rules of precendence for the operators and use their associativity to drop a number of parentheses. The grammar in EBNF of figure 3.1 incorporates these considerations.

Figure 3.1. Relaxed grammar for PL.

Of course, this does not violate any of our previous results; the semantics may still be defined in a similar way but now it seems easier to do this with respect to the parse tree of a formula.

#### 3.3 Truth table method

A straightforward algorithm to solve the satisfiability and tautology problems is provided by the truth table method. Given a formula A over a certain set of atomic propositions PROP (A), all we have to do is list all possible assignments  $\nu$  to these symbols and evaluate the formula for each of them, i.e., compute  $\hat{\nu}(A)$ . If in at least one case the evaluation leads to a true result the formula is satisfiable. If all cases evaluate to true the formula indeed expresses a tautology, and if none of the cases evaluate to true the formula is unsatisfiable or also called a contradiction. For satisfiability, the worst case complexity of this method is clearly of the order  $2^n$  where n is the number of distinct atomic propositions appearing in the formula. Since we know that the satisfiability problem is NP-complete there is not much hope of ever finding a method that beats the exponential time complexity. However, in many problem instances the truth table method must be considered too brute force.

A more ingenious way of determining tautology is based on a search for a falsifying assignment to the formula under test. If the search fails we must conclude that the formula is indeed a tautology else we have found a counter example (refutation), namely an assignment  $\nu$  that yields  $\hat{\nu}(A) = 0$ . More indirectly, one could investigate the satisfiability of the negated formula; if not satisfiable the original formula is a tautology. There are several methods based on the above principles. They have in common that they are purely based on syntactical transformations of the formula under test. Typically a number of axioms (or usually axiom schemata) is defined that comprise the terminating cases of the search, which on intermediate stages is guided by a set of rewrite or inference rules. Care has to be taken that the system of axioms and inference rules is sound and complete, i.e., only tautological formulas will be classified as such and none is missed. Fortunately, for propositional logic such systems do exist, see e.g. section 3.4 "Proof Theory of Propositional Logic" in [Galli87].

#### 3.4 Disjunctive normal form

A simple way to test for satisfiability is the disjunctive normal form (DNF) method. Here we will define a DNF as a set of sets of literals:

**Definition 3.11** A DNF is a finite set  $\{C_1, C_2, \cdots, C_n\}$  of clauses  $C_i$ , each  $C_i$  is a set of literals  $\{L_{i1}, L_{i2}, \cdots L_{i_m}\}$ . A literal is either an atomic proposition (also called positive literal) or its negation (negative literal). Negative literals will be denoted by a prime (') after the name of the atomic proposition. A clause  $C_i$  expresses a conjunction over its literals; a DNF set expresses a disjunction over its clauses.

**Definition 3.12** The transformation of a formula to a DNF set is inductively defined as follows:

$$DNF(P) = \{\{P\}\}$$

$$DNF(\neg P) = \{\{P'\}\}$$

$$DNF(\neg \neg A) = DNF(A)$$

$$DNF(\neg (A \land B)) = DNF(\neg A) \cup DNF(\neg B)$$

$$DNF(\neg (A \lor B)) = DNF(\neg A) \circ DNF(\neg B)$$

$$DNF((A \land B)) = DNF(A) \circ DNF(B)$$

$$DNF((A \lor B)) = DNF(A) \cup DNF(B)$$

with P an arbitrary atomic proposition, A and B arbitrary formulas, and  $S \circ T = \{s \cup t \mid s \in S, t \in T \text{ and } s^+ \cap t^- = s^- \cap t^+ = \emptyset\}$  for DNFs S and T and clauses s and t. We use  $s^+$  to denote the set of positive literals of a clause s; likewise,  $s^-$  denotes its set of negative literals. Clearly, the  $\circ$  operator on DNF sets selectively unites pairs of clauses, omitting pairs containing literals with opposite sign.

**Definition 3.13** The meaning of a DNF set is defined by the function  $h: DNF \longrightarrow (B^n \longrightarrow B)$  as follows: (here we already make use of the syntax of figure 3.1 and assume  $\hat{v}$  to be adjusted accordingly)

Bottom case: DNF set =  $\emptyset$ , h( $\emptyset$ ) = 0.

Inductive case: DNF set =  $\{C_1, C_2, \dots, C_n\}$ , then

$$h(\{C_1, C_2, \dots, C_n\}) = \hat{v}(h(\{C_1\}) \vee h(\{C_2\}) \vee \dots \vee h(\{C_n\})).$$

Where for each clause  $C_i = \{L_1, L_2, \dots, L_m\}$ ,

$$h\left(\left\{\left\{L_{1},L_{2},\cdots,L_{m}\right\}\right\}\right)=\hat{v}\left(g\left(L_{1}\right)\wedge g\left(L_{2}\right)\wedge\cdots\wedge g\left(L_{m}\right)\right),$$

in which for each positive literal  $L_i = P, g(P) = P$ ,

and for each negative literal  $L_i = P'$ ,  $g(P') = \neg P$ .

Now the definition of the o operator should be clear: having a atomic proposition and its negation appear in the same clause will be interpreted as false and since all clauses are "or"-ed together we might as well avoid false clauses in the first place. Notice that the definition of h has been chosen in a way such that:

**Theorem 3.2**  $\hat{\mathbf{v}}(\mathbf{A}) = \mathbf{h}(\mathsf{DNF}(\mathbf{A}))$  holds for every formula A.

*Proof:* Use the definitions of v and h and use the following identities of theorem 3.1:

$$(A \lor (B \land C)) \approx ((A \lor B) \land (A \lor C))$$

$$(A \lor B) \approx (B \lor A)$$

$$\neg (A \lor B) \approx (\neg A \land \neg B)$$

$$\neg (A \land B) \approx (\neg A \lor \neg B)$$

$$\neg \neg A \approx A$$

□ theorem 3.2

$= \{ \{ P, Q', R' \} \}$

**Corollary 3.1** The satisfiability problem — is there a v such that  $v \models A$ ? — can now be rephrased as "is the DNF set nonempty, i.e., DNF(A)  $\neq \emptyset$ ?" Similarly,  $\models A$  holds if and only if DNF ( $\neg A$ ) =  $\emptyset$ .

```

Example 3.1 Does \models ((P \land Q) \lor (\neg P \lor R)) \text{ hold?}

DNF(\neg ((P \land Q) \lor (\neg P \lor R)))

= DNF(\neg (P \land Q)) \circ DNF(\neg (\neg P \lor R))

= (DNF(\neg P) \cup DNF(\neg Q)) \circ (DNF(\neg \neg P) \circ DNF(\neg R))

= (\{\{P'\}\} \cup \{\{Q'\}\}) \circ (\{\{P\}\} \circ \{\{R'\}\})

= \{\{P'\}, \{Q'\}\} \circ \{\{P,R'\}\}

```

So we get a nonempty result, meaning the original formula is not a tautology.  $\Box$  example 3.1

#### 3.5 Containment (or subsumption)

As with formulas of PL, we can have many different DNF sets with the same meaning. For instance the sets  $\{\{P\}\}\$  and  $\{\{P\},\{P,Q',R\}\}\$  have the same meaning  $\lambda p$ , q, r. p. The clauses of a DNF set are partially ordered according the subset relation  $\subseteq$ . The following lemma is useful in minimizing the number of clauses:

**Lemma 3.1** Let DNF (A) = { $C_1$ ,  $C_2$ }. If  $C_1 \subseteq C_2$  then h({ $C_1$ ,  $C_2$ }) = h({ $C_1$ }). We will say, although this may sound counter-intuitive, that  $C_1$  contains  $C_2$ . (The term 'contains' stems from the fact that when a clause is interpreted as a set of points in B<sup>n</sup>, we have that whenever  $C_1 \subseteq C_2$  then the points of  $C_2$  are contained in the set of points of  $C_1$ .)

*Proof:* Clauses express a conjunction ( $\land$ ) of their elements. Each element (literal) in a clause must evaluate to 1 in order for the clause to be 1. For  $C_2$  to be 1 at least all elements in it that are also in  $C_1$  must thus be 1, so  $C_1$  will be 1 but then DNF (A) is already 1 independent of the remaining literals in  $C_2$ . Conversely, if  $C_1$  evaluates to 0 then also  $C_2$ .

□ lemma 3.1

Given a DNF set we may replace it with the set consisting of the minimal elements of that DNF set under the  $\subseteq$  relation. To find these minimal elements requires a quadratic number of  $\subseteq$  comparisons, viz. every element has to be compared with the rest.

#### 3.6 Implementation of DNF

In a program that tests satisfiability based on the DNF set approach we need to represent sets of sets of literals. Regarding the operations that are to be performed on this abstract data structure we derive that clauses are conveniently implemented by means of bitvectors and that a set of them can be represented by a singly-linked list. This way uniting DNF's requires appending (or concatenating) lists, and the o operation can be based on bitwise 'and' and 'or' operations on the bitvectors. Each clause will be represented by 2 bitvectors, one to express the inclusion of a positive literal and one to do the same for negative literals. A DNF set is then represented by a list of pairs of bitvectors.

```

list-of-pairs-of-bitvectors DNF(PL f)

switch (f) {

case P:

clause C:=pair (pos, neg) of all-0's bitvectors;

set bit in pos(C) corresponding with P;

return singleton list with C as element;

case ¬P:

clause C:=pair (pos, neg) of all-0's bitvectors;

set bit in neg(C) corresponding with P;

return singleton list with C as element;

case ¬¬A:

return DNF(A):

case \neg (A \land B):

return concat(DNF(\neg A), DNF(\neg B));

case \neg (A \lor B):

return \circ (DNF(\neg A), DNF(\neg B));

case (A \wedge B):

return o(DNF(A), DNF(B));

case (A \lor B):

return concat(DNF(A), DNF(B));

}

}

```

Algorithm 3.1. Implementation of DNF.

Algorithm 3.1 shows a straightforward implementation of the conversion of a PL formula to its DNF form as defined in definition 3.12. Details of the o operator are presented in algorithm 3.2.

Algorithm 3.2. Implementation of the o operator.

The worst-case performance of the above algorithm is exponential in the size of the formula, and, considering that satisfiability is an NP-complete problem, there is little hope to ever find a polynomial-time algorithm.

The resulting DNF list can often be simplified using containment. A good heuristic that we use in our implementation is to define a lexicographical ordering on the clauses (based on a linear ordering of the literals) and then while doing a mergesort on the clauses mark the ones that are subsumed (or contained) by others. The marked clauses may be deleted from the DNF list. This way only a total of n<sup>2</sup>log(n) containment tests is performed.

The DNF representation will be used in chapter 6 when we look at an algorithm for the satisfiability of propositional linear-time temporal logic.

# **Binary Decision Diagrams**

#### 4.1 Introduction

So far we have looked at two distinct representations of boolean functions: PL formulas and DNF sets. To solve the tautology problem we are basically asking whether the formula or DNF set denotes the 1 function, i.e., the function that is invariably true. The major drawback of the representations is that many formulas and many DNF sets denote the same function. So it is not always directly obvious that two different descriptions indeed describe the same circuit (i.e., have the same logic behaviour). Here we will introduce a representation for a boolean function that does not have this disadvantage: the Binary Decision Diagram (BDD) also known as Boolean Function Graph. Seminal work by [Bryan86, Karpl89] has shown that given a fixed ordering of the function's place-holder variables, binary decision diagrams are canonical: each distinct function may be represented by a unique binary decision diagram. Moreover, we will shortly see that in an implementation each function can be represented by a unique reference (pointer value), thus tautology checking reduces to testing whether two references are the same. However, constructing a binary decision diagram might in the worst case require an exponential number of operations. The success of binary decision diagrams lies in the fact that for many practical functions it is known that the diagram has a size which is only polynomially related to the number of variables.

# 4.2 Notation and terminology

We consider boolean functions all with the same arity, i.e., they all have the same,

fixed number of arguments  $n \ge 0$ . These functions can be denoted by propositional formulas  $\phi(X)$  over a set of atomic propositions  $X = \{x_1, x_2, \cdots, x_n\}$  as  $f = \lambda x_1, x_2, \cdots, x_n, \phi(X)$ . Here the  $x_i$ 's will be called boolean variables. The functions will be total or complete in the sense that they are defined for every element of the domain  $B^n$ . Two functions are considered identical when application of each to all  $2^n$  distinct argument values always gives the same result value.

Our presentation of BDD's follows the terminology used in [Brace90].

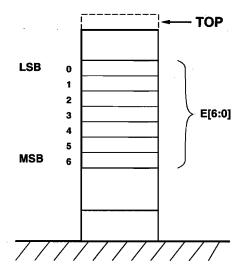

**Definition 4.1** A BDD is a labelled, possibly multi-rooted, directed acyclic graph (DAG) G (V, E). We distinguish two kinds of vertices: I-nodes and T-nodes. The edge set E is defined by a relation  $E \subseteq I$ -nodes  $\times$  (I-nodes  $\cup$  T-nodes). The details are as follows:

- I-nodes is a finite set of internal vertices, each having precisely 2 outgoing edges to (other) internal or terminal vertices. One is said to be the else-edge, the other is the then-edge. The successor vertex of an internal vertex v via its else-edge is denoted by else (v); the successor accessible via its then-edge is denoted by then (v). Each internal vertex v is labelled with a variable denoted by var (v). The set of variables is assumed to be totally ordered, i.e., we postulate the existence of a ranking function rank: X→{1,2,···,n}; rank(x) then denotes the rank number of variable x in the ordering. When no confusion can occur, we write rank(v) instead of rank(var(v)).

- T-nodes = {zero, one} is the set of terminal vertices. Terminal vertices have no outgoing edges. For uniformity we define the rank of a terminal vertex to be n + 1.

**Definition 4.2** An Ordered BDD (OBDD) is a BDD where for each internal vertex  $v \in I$ -nodes we have:

```

rank(v) < min(rank(else(v)), rank(then(v))).

```

**Definition 4.3** A Reduced Ordered BDD (ROBDD) is an OBDD such that for each internal vertex its two successors are distinct and the graph does not contain isomorphic subgraphs.

For any BDD (not necessarily reduced and ordered) we can define a meaning in the following way:

**Definition 4.4** Assume a fixed set of variables  $\{x_1, x_2, \cdots, x_n\}$ . With each vertex  $v \in V$  in the BDD we associate a boolean function I(v). The (higher-order) interpretation function  $I: V \longrightarrow (B^n \longrightarrow B)$  is inductively defined on the structure of the graph. We abbreviate  $x_1, x_2, \cdots, x_n$  to X, and assume that the indexing is such that  $rank(x_i) = i$ .

• For terminal vertices zero and one:

I (zero) = **0**, i.e., the function

$$\lambda X$$

. 0

I (one) = **1**, i.e., the function  $\lambda X$ . 1

• For every internal vertex v:

$$I(v) = ITE(\lambda X. var(v), I(then(v)), I(else(v)))$$

with ITE(F, G, H) =  $\lambda X$ . H<sub>ITE</sub>(F(X), G(X), H(X)). ITE is a higher-order function manipulating functions with signature B<sup>n</sup>  $\longrightarrow$  B, based on the 3-argument boolean function H<sub>ITE</sub>(P, Q, R) = H<sub>v</sub>(H<sub>v</sub>(P, Q), H<sub>v</sub>(H<sub>v</sub>(P), R)), see table 4.1. The name ITE is an acronym for If-Then-Else.

| Р | Q | R | $H_{ITE}(P,Q,R)$ |

|---|---|---|------------------|

| 0 | 0 | 0 | 0                |

| 0 | 0 | 1 | 1                |

| 0 | 1 | 0 | 0                |

| 0 | 1 | 1 | 1                |

| 1 | 0 | 0 | 0                |

| 1 | 0 | 1 | 0                |

| 1 | 1 | 0 | 1                |

| 1 | 1 | 1 | 1                |

**Table 4.1.** Semantics of the ITE operator.

The functions associated with the BDD are the functions associated with its root vertices.

It is customary to let the projection function associated with a variable be denoted by the name of that variable, thus if  $x_i$  is some variable then  $x_i$  stands for the function  $\lambda X$ .  $x_i$ . Also, often the same logical operator symbol is used to denote the corresponding higher-order operation, e.g. one often sees ITE (F, G, H) = (F  $\wedge$  G)  $\vee$  ( $\neg$  F  $\wedge$  H). Here, however, we will use the symbol  $\cdot$  to denote the higher-order "And" operation and the symbol + to denote the higher-order "Or" operation; higher-order "Not" is indicated by placing a bar  $^-$  above the function name.

From now on, we will simply write BDD when in fact we mean a Reduced Ordered BDD. We also assume some ranking function rank:  $X \longrightarrow \{1, 2, \dots, n\}$  to be defined for the variables (e.g. we may take rank  $(x_i) = i$ , however, this is only one of the n! possibilities).

Note that for each internal vertex v in a BDD with var(v) = x, T = I(then(v)), and E = I(else(v)), ITE(x, T, E) is by definition a unique function (within that BDD). We may therefore use the triple  $\langle x, T, E \rangle$  as a unique identification for the

internal vertex v, but also as an identification for the sub-BDD rooted at that vertex. For convenience we will denote the BDD by the function it represents, which is already done here for the BDDs T and E; in general, i.e., when they are not bottom cases, T and E themselves can be represented by such triples (they are the labels of the vertices then (v) and else (v) respectively). Bottom cases are the terminal vertices; they will be labeled by their respective functions 0 and 1. We refer to them as constant BDDs.

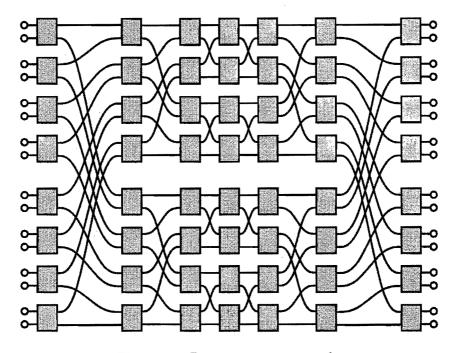

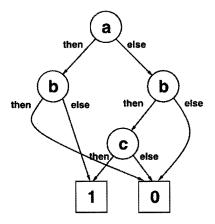

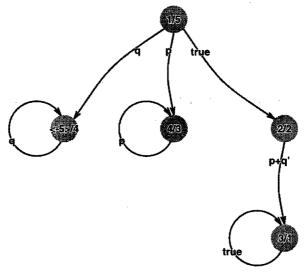

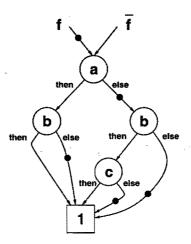

**Example 4.1** The BDD for the function  $\lambda a$ , b, c.  $a \land \neg b \lor \neg a \land b \land c$  and represented by  $\langle a, \langle b, 0, 1 \rangle, \langle b, \langle c, 1, 0 \rangle, 0 \rangle$  is depicted in figure 4.1.

Figure 4.1. Example BDD graph for  $f(a, b, c) = a \land \neg b \lor \neg a \land b \land c$ .

In drawing a BDD the following conventions will be adhered to:

- 1. A vertex is represented by a circle containing the name of its variable label.

- By letting incoming edges enter at the top of the circle and outgoing edges leave at the bottom of the circle there is no need to draw an arrow to indicate their direction.

- 3. Instead of labelling the edges with then and else we will use 1 and 0 respectively, or preferably even do without these labels and then it is understood that the edge exiting on the bottom left of a circle is the thenedge, and the edge exiting on the bottom right is the else-edge.

- 4. Terminal vertices are not explicitly drawn. We simply let the edge end in a 0 or a 1 symbol.

Figure 4.2 shows the example BDD drawn according the above rules.

Figure 4.2. Example BDD graph drawn in 'minimalistic' style.

□ example 4.1

#### 4.3 BDD construction

Now we investigate how BDDs can be put to practical use, i.e., manipulate them by means of logical operators. The following table 4.2 lists useful operations on functions F and G and shows how the same result may be achieved in terms of the higher-order ITE function. The objective of this section is to derive an algorithm for ITE operating on the BDD representation of the functions. We shall first formulate ITE in a recursive way.

| Name:   | Notation:            | ITE form:                 |

|---------|----------------------|---------------------------|

| not     | F                    | ITE (F, 0, 1)             |

| and     | F-G                  | ITE(F,G, <b>0</b> )       |

| xor     | F⊕G                  | $ITE(F, \overline{G}, G)$ |

| or      | F+G                  | ITE ( F, <b>1</b> , G )   |

| nor     | F+G                  | $ITE(F, 0, \overline{G})$ |

| equiv   | F↔G                  | $ITE(F,G,\overline{G})$   |

| implies | $F \to G$            | ITE (F, G, 1)             |

| nand    | $\overline{F\cdotG}$ | $ITE(F, \overline{G}, 1)$ |

**Table 4.2.** Operations on functions and equivalent ITE formulation.

**Definition 4.5** The Shannon expansion of a boolean function F with respect to a variable x is the decomposition of F in its cofactors  $F_x$  and  $F_{\bar{x}}$  according to  $F = x \cdot F_x + \bar{x} \cdot F_{\bar{x}}$ . The cofactor  $F_x$  is the restriction of F under x = 1, similarly  $F_{\bar{x}}$  is the restriction of F under x = 0. (Note that for any variable, a cofactor of a constant function is the function itself). The support of a function is the set  $\{x_i \mid F_{x_i} \neq F_{\bar{x}_i}\}$ . Constant functions have empty support.

Shannon expansion gives us a recursive procedure for BDD construction. Observe that the following derivation is valid:

$$\begin{split} ITE(F,G,H) &= x \cdot ITE(F,G,H)_x + \bar{x} \cdot ITE(F,G,H)_{\bar{x}} \\ &= x \cdot (F \cdot G + \overline{F} \cdot H)_x + \bar{x} \cdot (F \cdot G + \overline{F} \cdot H)_{\bar{x}} \\ &= x \cdot (F_x \cdot G_x + \overline{F}_x \cdot H_x) + \bar{x} \cdot (F_{\bar{x}} \cdot G_{\bar{x}} + \overline{F}_{\bar{x}} \cdot H_{\bar{x}}) \\ &= x \cdot (ITE(F_x,G_x,H_x)) + \bar{x} \cdot (ITE(F_{\bar{x}},G_{\bar{x}},H_{\bar{x}})) \\ &= ITE(x,ITE(F_x,G_x,H_x),ITE(F_{\bar{x}},G_{\bar{x}},H_{\bar{x}})) \end{split}$$

and the latter stands for the BDD:

$$\langle x, ITE(F_x, G_x, H_x), ITE(F_{\bar{x}}, G_{\bar{x}}, H_{\bar{x}}) \rangle$$

All that remains to be shown is how to compute the cofactors of a function and provide the bottom cases of the recursive expansion sketched above. Without violating the validity of the expansion, we may choose x to be the variable with the smallest rank among the variables labelling the root vertices of the BDDs for the functions F, G and G. Remember that the rank of a constant BDD is n+1 by definition. Assume the BDD for G non-constant, so let G is G Surely rank(G). If rank(G) < rank(G) then G is not in the support of G, hence G is G in the functions G and G is G in the same reasoning. Clearly, the bottom cases are determined by G being constant: ITE(G, G, G) = G and ITE(G, G, G) = G.

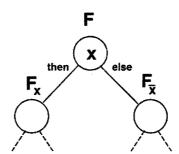

**Figure 4.3.** Function **F** and its cofactors w.r.t. the top variable **x**.

An implementation of the high-order ITE function operating on boolean functions represented by BDDs is outlined in algorithm 4.1. In an actual implementation, for instance in Pascal or C, it is convenient to define the type BDD to be a pointer to a vertex record (or struct). Then testing for equality of two BDDs can be done using the equality operation (=) on pointer values provided that BDD DAGs are uniquely stored, i.e., no isomorpic subgraphs exist. This uniqueness of subgraphs is achieved by keeping track of all the  $\langle x, T, E \rangle$  triples in a hash table. The BDDs for the projection functions  $\lambda X. x_i$  for the variables that are denoted by the triples  $\langle x_i, 1, 0 \rangle$  are also kept in this hash table. The information stored for each triple is the BDD pointer that points to the root vertex of the particular DAG for that BDD. In algorithm 4.1 the statement if  $\langle T = E \rangle$  then return  $T_i$

ensures the first condition mentioned in definition 4.3 (successors are distinct) to be met and returning the unique BDD for the triple  $\langle x, T, E \rangle$  ensures the second condition to be met, namely that no isomorphic subgraphs are constructed.

```

BDD ite(BDD F,G,H)

{

/* Bottom cases: */

if (F = 0) return H;

if (F = 1) return G;

/* Recursive case: */

x:=min(var(F),var(G),var(H));

T:=ite(F<sub>x</sub>,G<sub>x</sub>,H<sub>x</sub>);

E:=ite(F<sub>x</sub>,G<sub>x</sub>,H<sub>x</sub>);

if (T = E) return T;

return unique BDD for (x,T,E);

}

```

**Algorithm 4.1.** The basic BDD constructor function ite.

Many optimizations of the ite function may be considered, e.g. including more tests for special cases and supplying ite with a memory function that avoids recomputation. For the latter we keep a table of argument and result values that we consult upon entry (lookup) and update upon exit (remember). Some of these ideas are incorporated in algorithm 4.2.

```

BDD ite(BDD F,G,H)

if (F = 0) return H;

if (F = 1) return G;

/* Special case: */

if (G = 1 \&\& H = 0) return F;

/* Make use of memory function: */

R:=lookup(F,G,H);

if (R \neq \bot) return R; /* value \bot signals absence */

x:=\min(var(F), var(G), var(H));

T:=ite(F_X,G_X,H_X);

E:=ite(F_{\bar{x}},G_{\bar{x}},H_{\bar{x}});

if (T = E) R:=T; else R:=unique BDD for \langle x, T, E \rangle;

/* Supply memory function with new data: */

remember "ite(F,G,H)=R";

return R;

}

```

Algorithm 4.2. A more practical ite function.

More implementation issues are discussed in chapter 8.

.

\*

.

.

.

# Verification of Circuits with Memory

This part consists of three chapters. Its structure mimics the first part: first we introduce sequential circuits in chapter 5; then chapter 6 addresses two temporal logics, CTL and PTL, that are useful in reasoning about the behaviour of this type of circuit; lastly, chapter 7 presents a more general formalism that encompasses both temporal logics, namely  $\mu$ -calculus. For all three formalisms, basic implementations are presented.

# **Sequential Circuits**

#### 5.1 Introduction

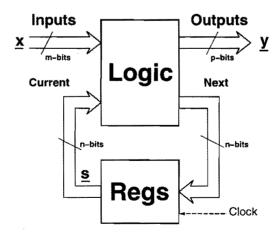

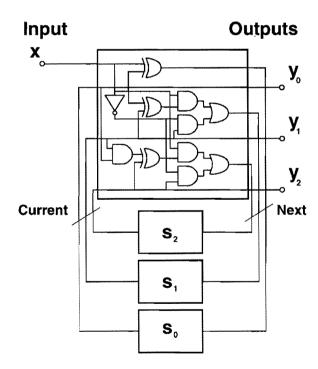

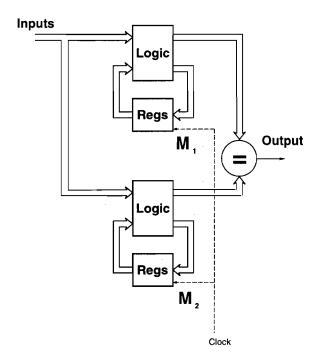

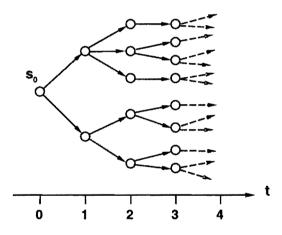

A sequential circuit can be defined as a logical circuit for which the values of the outputs not only depend on the present values on the inputs, but also on the history of the system. For that, the circuit needs some way of remembering what happened in the past: it needs memory. Time therefore becomes an explicit parameter in the logical functions that describe the outputs of a sequential circuit. We usually abstract from a real time value and use the notion of a clock instead. This means that we are only interested in observing the system at certain discrete points in time, e.g. the moment just after the clock signal has risen from 0 to 1. The mathematical model of such systems is the finite automaton. The system's memory is then replaced by the concept of state. The finiteness of the automaton implies that its behaviour is of an intrinsic repetitive nature. This directly translates to the decidability of the equivalence problem for automata.

# 5.2 Finite automata and sequential circuits

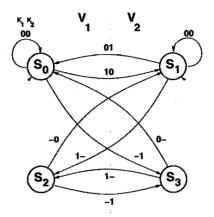

A finite automaton is usually defined by the quintuple (  $Q, \Sigma, \delta, q_0, F$  ), where

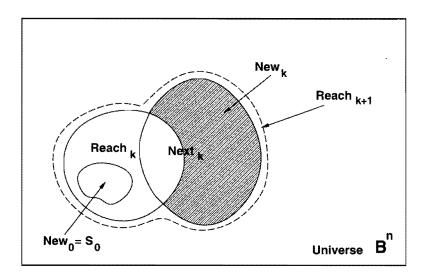

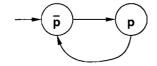

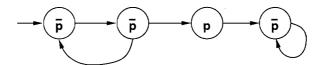

Q is a finite, non-empty, set of states;