## A bottom-up approach to multiple-level logic synthesis

*Citation for published version (APA):* Jozwiak, L., Chojnacki, A., Volf, F. A. M., & Perkowski, M. A. (1998). A bottom-up approach to multiple-level logic synthesis. In Proc. Second International Workshop on Design and Diagnostics of Electronic Circuits and Systems (pp. 39-45)

Document status and date: Published: 01/01/1998

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

### A bottom-up approach to multiple-level logic synthesis for look-up table based FPGAs

#### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr. M. Rem, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op maandag 29 september 1997

> door Franciscus Adrianus Maria Volf geboren te Eindhoven

Dit proefschrift is goedgekeurd door de promotoren:

prof.ir. M.P.J. Stevens en prof. Dr.-Ing. J.A.G. Jess

Copromotor: dr.ir. L. Jóźwiak

Druk: Universiteitsdrukkerij Eindhoven

#### CIP-DATA LIBRARY TECHNISCHE UNIVERSITEIT EINDHOVEN

Volf, Franciscus A.M.

A bottom-up approach to multiple-level logic synthesis for look-up table based FPGAs / by Franciscus A.M. Volf. - Eindhoven : Technische Universiteit Eindhoven, 1997. Proefschrift. - ISBN 90-386-0380-0 NUGI 832 Trefw.: logische schakelingen ; algoritmen /programmeerbare logische schakelingen /

combinatorische logica / digitale geintegreerde schakelingen. Subject headings: logic CAD / field programmable gate arrays / combinational circuits /

minimisation of switching nets.

### Abstract

Despite the fact that the automatic hardware synthesis of complex digital circuits and systems has been an important topic of research during the last two decades, many synthesis problems are still not solved in a satisfactory way. This thesis deals with one of these problems: the multiple-level synthesis of Boolean functions for implementations with look-up table based Field-Programmable Gate Arrays (FPGAs).

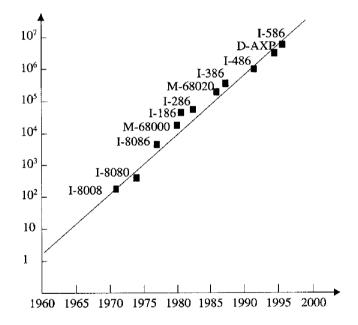

The topic addressed in this thesis is very important for many reasons. Perhaps, the two most important reasons are the following. Firstly, FPGAs have a number of important advantages compared to the other implementation techniques, and therefore the use of look-up table based FPGAs for the implementation of digital systems has increased dramatically over the last few years. Secondly, due to the internal structure of FPGAs, traditional logic synthesis methods cannot be applied to them without extensive modifications and additions, and even modified they have some fundamental shortcomings.

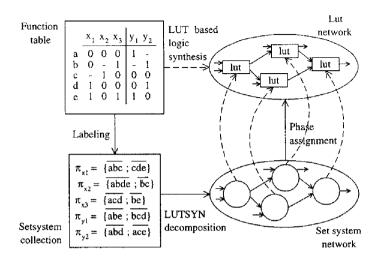

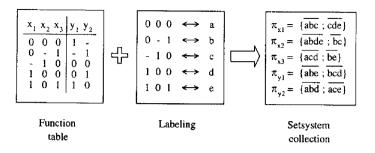

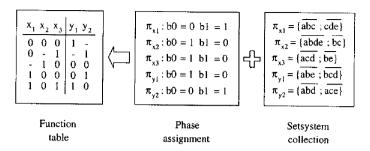

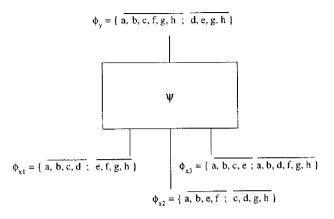

In this thesis, an original approach to the general (functional) decomposition of Boolean functions into multiple-level networks of look-up tables is proposed. The approach has four main characteristic features. The first of them is the use of set systems that provides a compact maximal functionally complete representation of logic blocks and Boolean functions, whereas traditional logic synthesis methods use minimal functionally complete representations. Secondly, a compositional bottom-up approach is used for the synthesis; this is different from all other known functional decomposition methods that use a top-down reduction approach. Thirdly, the proposed method searches explicitly for common subfunctions, whereas other methods find subfunctions only implicitly as the by-product of the synthesis process. Finally, the method does not use two-level minimization prior to the actual multiple-level synthesis what enables the exploitation of the whole design freedom during the actual multiple-level synthesis.

Because of the computational complexity of the considered logic synthesis problem, it was necessary to develop some heuristic algorithms to make the synthesis method effective and efficient.

For the research of general decompositions a software environment called LUTSYN (Look-Up Table SYNthesis) has been created. LUTSYN is specially designed to provide a lot of internal information, so the program can be experimentally used for research purposes, and especially for analysis and fine-tuning of all heuristic parts of the algorithms.

The primary goal of the synthesis process is to minimize the number of look-up tables that are used to implement a given Boolean function. Additional goals consist of minimizing the number of levels in the lookup table network (which is the main contribution to speed of the resulting circuit) and to minimize the number of long wires (what improves both the routability and speed of the FPGA). The implemented algorithm allows the trade-off between the quality of the synthesis results and the computer resources used to find an implementation.

Although LUTSYN is not yet a complete automated synthesis tool, it can be used as a prototype automatic logic synthesis tool. Preliminary results show that the algorithm performs well compared to other known methods. A more complete analysis of the results will be available in the nearest feature.

## Acknowledgement

I would like to thank prof.ir. M.P.J. Stevens and dr.ir. L. Jóźwiak for providing me the opportunity to perform this Ph.D. research and for their valuable advice and support while carrying out this work.

Furthermore I'm grateful to a number of people that have been involved in this research or provided assistance in a different way. In alphabetical order: Max Bonsel, Franck de Bruyn, Ad Chamboné, Artur Chojnacki, John van Houtert, Paweł Konieczny, Jan Kolsteren, Marcel Kolsteren, Wido Kruijtzer, Andy Ong, Rinus van Weert and Alex Wijffels.

A few people deserve extra credits: Wil Brant who single-handed created all the figures in this thesis, Jeroen Voeten for helping me to get all the mathematical details right and Rian van Gaalen for her continuous support and assistance.

Finally, I want to express my gratitude to my parents. Without their support writing this thesis would not have been possible.

......

## Contents

| Α  | bstra                                  | ct                                                                                                                                                                                                                                                                 | iii                                                 |

|----|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| A  | cknow                                  | wledgement                                                                                                                                                                                                                                                         | v                                                   |

| Li | st of                                  | Definitions                                                                                                                                                                                                                                                        | xi                                                  |

| Li | st of '                                | Theorems                                                                                                                                                                                                                                                           | xiii                                                |

| Li | st of I                                | Figures                                                                                                                                                                                                                                                            | xv                                                  |

| 1  | Intr<br>1.1<br>1.2<br>1.3<br>1.4       | oduction<br>Design of digital integrated circuits<br>Logic synthesis<br>General decomposition based logic synthesis<br>Organization of the thesis                                                                                                                  | 1<br>1<br>3<br>6<br>8                               |

| 2  | Dec<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5 | omposition theory<br>Basic definitions<br>Combinational machines<br>Partitions<br>General decomposition<br>Special cases of general decomposition                                                                                                                  | 9<br>9<br>12<br>16<br>23<br>31                      |

| 3  | <b>State</b><br>3.1<br>3.2             | e of the art in logic synthesisDivision based logic synthesis3.1.1Factorization algorithm3.1.2Example of division based synthesis3.1.3Technology mappingGraph based logic synthesis3.2.1Introduction3.2.2Classical binary decision diagrams3.2.3Extensions to BDDs | <b>35</b><br>35<br>41<br>44<br>48<br>48<br>48<br>53 |

|    | 3.3<br>3.4                             | 3.2.4 Logic synthesis using BDDs         Special cases of general decomposition         3.3.1 Input-bit parallel decomposition         3.3.2 Bit-parallel decomposition         Multiple valued logic and symbolic encoding                                        | 55<br>58<br>58<br>62<br>64                          |

| 4 | LUT |        | Framework and Concepts                   | 69  |  |  |  |

|---|-----|--------|------------------------------------------|-----|--|--|--|

|   | 4.1 | Proble | em definition                            | 69  |  |  |  |

|   |     | 4.1.1  | Choice of an FPGA architecture           | 69  |  |  |  |

|   |     | 4.1.2  | Optimization criteria                    | 72  |  |  |  |

|   |     | 4.1.3  | Problem formulation                      | 75  |  |  |  |

|   |     | 4.1.4  | Complexity considerations                | 77  |  |  |  |

|   | 4.2 | Mathe  | ematical framework                       | 79  |  |  |  |

|   |     | 4.2.1  | Network representation using set systems | 79  |  |  |  |

|   |     | 4.2.2  | Set system theory                        | 82  |  |  |  |

|   |     | 4.2.3  | Synthesis framework model                | 92  |  |  |  |

|   |     | 4.2.4  | From function table to set systems       | 93  |  |  |  |

|   |     | 4.2.5  | From set system networks to LUT network  | 94  |  |  |  |

|   |     | 4.2.6  | Comparison to other representations      | 98  |  |  |  |

|   | 4.3 | LUTS   | YN overview and concepts                 | 99  |  |  |  |

|   |     | 4.3.1  | Introduction                             | 99  |  |  |  |

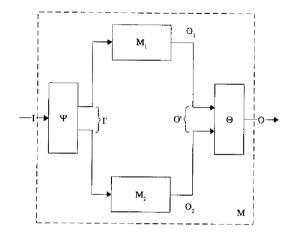

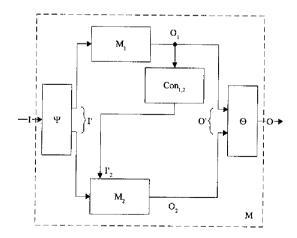

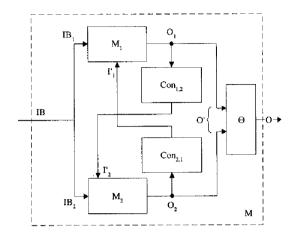

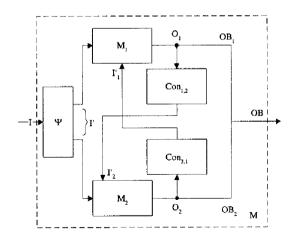

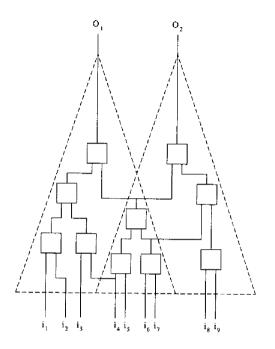

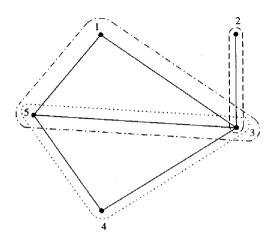

|   |     | 4.3.2  | Network construction approaches          | 100 |  |  |  |

|   |     | 4.3.3  | Calculation of set system similarities   | 103 |  |  |  |

|   |     |        | 4.3.3.1 Incompatibility relations        | 103 |  |  |  |

|   |     |        | 4.3.3.2 Similarity of set systems        | 105 |  |  |  |

|   |     | 4.3.4  | Input representation and don't cares     | 108 |  |  |  |

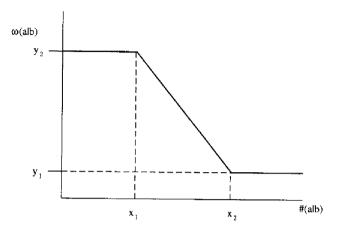

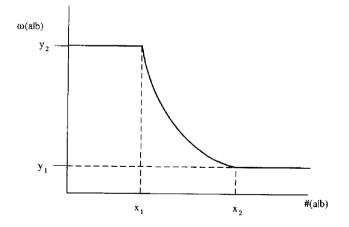

|   |     | 4.3.5  | Clustering process                       | 111 |  |  |  |

|   |     | 4.3.6  | Heuristic network construction process   | 112 |  |  |  |

| 5 | LUI | SYN -  | Algorithms                               | 115 |  |  |  |

| Ű | 5.1 |        | UTSYN environment                        | 115 |  |  |  |

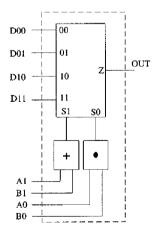

|   | 5.2 |        | B circuit                                | 117 |  |  |  |

|   | 5.3 |        |                                          |     |  |  |  |

|   | 5.4 | Prepro | ocess() : Preparation of the input data  | 121 |  |  |  |

|   |     | 5.4.1  | Introduction                             | 121 |  |  |  |

|   |     | 5.4.2  | Complete(): Calculate missing cover      | 123 |  |  |  |

|   |     | 5.4.3  | Split() : Split into output covers       | 125 |  |  |  |

|   |     | 5.4.4  | Optimize() : Optimize each output cover  | 125 |  |  |  |

|   |     | 5.4.5  | Combine() : Combine output covers        | 127 |  |  |  |

|   |     | 5.4.6  | Example                                  | 127 |  |  |  |

|   |     | 5.4.7  | Implementation                           | 127 |  |  |  |

|   |     | 5.4.8  | Preprocessing EB                         | 129 |  |  |  |

|   | 5.5 |        | er(): Cluster algorithm                  | 130 |  |  |  |

|   |     | 5.5.1  | The algorithm                            | 130 |  |  |  |

|   |     | 5.5.2  | Clustering EB                            | 132 |  |  |  |

|   | 5.6 | Build  | () : Network construction algorithm      | 134 |  |  |  |

|   | 2.0 | 5.6.1  | Introduction                             | 134 |  |  |  |

|   |     | 5.6.2  | The basic heuristic decision algorithm   | 135 |  |  |  |

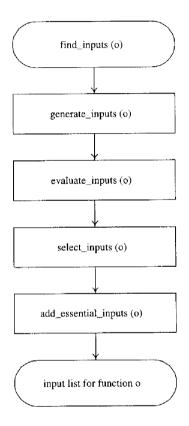

|   |     | 5.6.3  | Find_inputs(o)                           | 137 |  |  |  |

|   |     | 2.2.0  | 5.6.3.1 The algorithm                    | 137 |  |  |  |

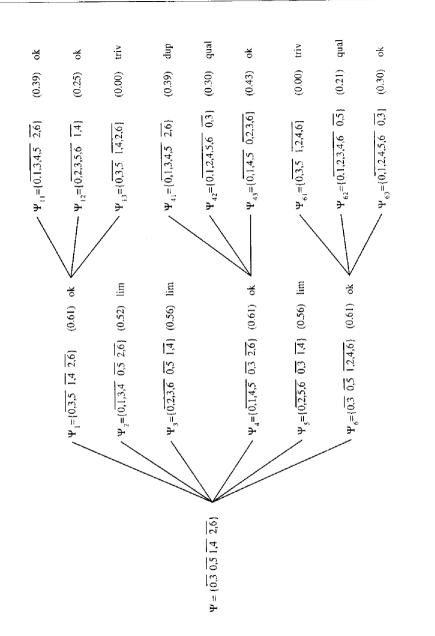

|   |     |        | 5.6.3.2 The EB example                   | 139 |  |  |  |

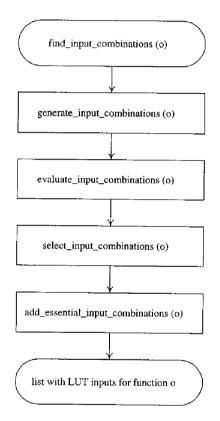

|   |     | 5.6.4  | Find_input_combinations(o)               | 142 |  |  |  |

|   |     | -      | L                                        |     |  |  |  |

|       | 5.6.4.1 The algorithm                                                              | 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 5.6.4.2 The EB example                                                             | 144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

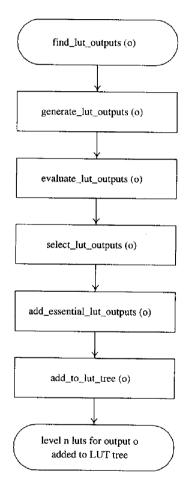

|       | 5.6.5 Find_lut_outputs( $o$ )                                                      | 146                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | 5.6.5.1 The algorithm                                                              | 146                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | 5.6.5.2 The EB example                                                             | 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

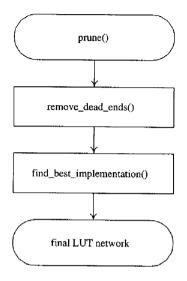

| 5.7   | Prune(): Find best of feasible realizations                                        | 151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | 5.7.1 The algorithm                                                                | 151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                    | 152                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Exp   | erimental results                                                                  | 153                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6.1   |                                                                                    | 153                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6.2   | Symmetric functions and LUTSYN                                                     | 158                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6.3   | Larger LUT blocks                                                                  | 158                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6.4   |                                                                                    | 159                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Con   | clusions and recommendations                                                       | 161                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                    | 161                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7.2   | Contributions of the work                                                          | 164                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7.3   |                                                                                    | 164<br>164                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| oliog | raphy                                                                              | 167                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Proc  | of af set system properties                                                        | 179                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A.1   | Properties of set system sets                                                      | 179                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | A.1.1 Introduction                                                                 | 179                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | A.1.2 Set systems form a lattice                                                   | 183                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | A.1.3 $M_{\rm ex}$ is the maximum of (Setsus( $\sim$ ) $\Box$ )                    | 186                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       | A.1.4 $m_{-}$ is the minimum of (Setsus( $\sim$ ) $\Box$ )                         | 188                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A.2   | $\leq \text{operator}$                                                             | 188                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A.3   | Closeness of set system product                                                    | 189                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       | Exp<br>6.1<br>6.2<br>6.3<br>6.4<br>Con<br>7.1<br>7.2<br>7.3<br>Dilog<br>A.1<br>A.2 | 5.6.5 Find_lut_outputs( $o$ )<br>5.6.5.1 The algorithm<br>5.6.5.2 The EB example<br>5.7 Prune(): Find best of feasible realizations<br>5.7.1 The algorithm<br>5.7.2 Pruning EB<br><b>Experimental results</b><br>6.1 Experimental results<br>6.2 Symmetric functions and LUTSYN<br>6.3 Larger LUT blocks<br>6.4 Improvements<br>Conclusions and recommendations<br>7.1 Characteristic features of LUTSYN<br>7.2 Contributions of the work<br>7.3 Future work<br>Proof of set system properties<br>A.1 Properties of set system sets<br>A.1.1 Introduction<br>A.1.2 Set systems form a lattice<br>A.1.3 $M_{\simeq}$ is the maximum of $(Setsys(\simeq), \Box)$<br>A.1.4 $m_{\simeq}$ is the minimum of $(Setsys(\simeq), \Box)$<br>A.2 $\leq$ operator |

## List of Definitions

| 2.1  | Power set                                                           | 10 |

|------|---------------------------------------------------------------------|----|

| 2.2  | Cartesian product                                                   | 10 |

| 2.3  | A binary relation                                                   | 10 |

| 2.4  | Single input/output complete function                               | 10 |

| 2.5  | Single input/output partial function                                | 11 |

| 2.6  | Multiple input/output (complete or partial) function                | 11 |

| 2.7  | An Onto (or surjective) function                                    | 11 |

| 2.8  | Equivalence relation                                                | 12 |

| 2.9  | Equivalence class                                                   | 12 |

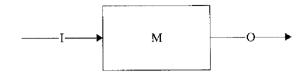

| 2.10 | Completely specified combinational machine                          | 12 |

| 2.11 | Completely specified combinational machine with multiple inputs and |    |

|      | outputs                                                             | 13 |

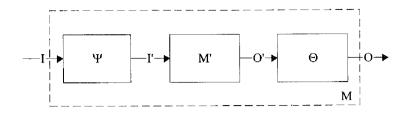

| 2.12 | Incompletely specified multiple input/output combinational machine  | 14 |

| 2.13 | Symbol covering                                                     | 14 |

| 2.14 | Realization of a machine                                            | 14 |

| 2.15 | Partition                                                           | 17 |

| 2.16 | Partition product                                                   | 17 |

| 2.17 | Partition sum                                                       | 17 |

| 2.18 | Partial ordering $\leq$ of partitions                               | 17 |

| 2.19 | I-O partition pair                                                  | 19 |

| 2.20 | M and m partitions of a partition pair                              | 19 |

| 2.21 | Mm partition pair                                                   | 19 |

| 2.22 | Input partition induced by an output partition                      | 20 |

| 2.23 | Bit partition                                                       | 21 |

| 2.24 | Symbol partition induced by a bit partition                         | 22 |

| 2.25 | The smallest symbol partition induced by a bit partition            | 22 |

| 2.26 | Bit partition induced by a symbol partition                         | 22 |

| 2.27 | General composition                                                 | 24 |

| 2.28 | "General" composition without loops                                 | 24 |

| 2.29 | General composition machine                                         | 25 |

| 2.30 | General decomposition                                               | 26 |

| 3.1  | Boolean divisor                                                     | 36 |

| 3.2  | Algebraic divisor                                                   | 37 |

| 3.3  | Primary divisors                                                    | 37 |

| 3.4  | Kernels                                                             | 38 |

| 3.5  | Binary Decision Diagram (BDD)                                       | 49 |

|      |                                                                     |    |

| 3.6  | Ordered Binary Decision Diagram (OBDD) 49                                                                                                                   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.7  | Reduced Ordered Binary Decision Diagram (ROBDD)                                                                                                             |

| 4.1  | Compatibility relation                                                                                                                                      |

| 4.2  | Compatible block                                                                                                                                            |

| 4.3  | Maximal compatible block 84                                                                                                                                 |

| 4.4  | Set system                                                                                                                                                  |

| 4.5  | Set system set $Setsys(\simeq)$                                                                                                                             |

| 4.6  | Canonical representative of $\simeq$                                                                                                                        |

| 4.7  | $\leq$ operator defined on set systems $\ldots \ldots $                                      |

| 4.8  | Set system product                                                                                                                                          |

| 4.9  | Symbol set system induced by a bit partition                                                                                                                |

| 4.10 | The smallest symbol set system induced by a bit partition                                                                                                   |

| 4.11 | Bit partition induced by a symbol set system                                                                                                                |

| 4.12 | Incompatibility relation                                                                                                                                    |

| 4.13 | Set system similarity                                                                                                                                       |

| A.1  | Compatibility relation                                                                                                                                      |

| A.2  | Compatible block                                                                                                                                            |

| A.3  | Maximal compatible block                                                                                                                                    |

| A.4  | Extendible block                                                                                                                                            |

| A.5  | Set system                                                                                                                                                  |

| A.6  | Set system set $Setsys(\simeq)$                                                                                                                             |

| A.7  | Block collection of a set system set 18                                                                                                                     |

| A.8  | Block intersection of a set system set                                                                                                                      |

| A.9  | $\leq$ operator defined on set systems $\ldots \ldots 18$ |

| A.10 | Set system product                                                                                                                                          |

|      |                                                                                                                                                             |

\_\_\_\_

## List of Theorems

| 2.1 Existence of general decomposition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2 Existence of general decomposition using two component machines 2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.1 Existence of multiple cube divisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.2 Input-bit parallel decomposition with two component machines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.3 Bit parallel decomposition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4.1 Satisfiability problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.2 Finding an optimal realization $r$ for $f$ is NP-hard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.3 For a given realization $r'$ , finding the distance $Q_f(r') - Q_f(r)$ , where $r$ is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| some optimal realization of $f$ , is NP-hard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.4 Checking whether $r$ is an optimal realization of some $f$ is NP-hard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.5 For a given realization $r'$ and natural number $n \in \mathbb{N}$ , checking whether                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| $Q_f(r') - Q_f(r) < n$ , where <i>r</i> is some optimal realization of <i>f</i> is NP-hard 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.6 $(Setsys(\simeq), \sqsubseteq)$ is a lattice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

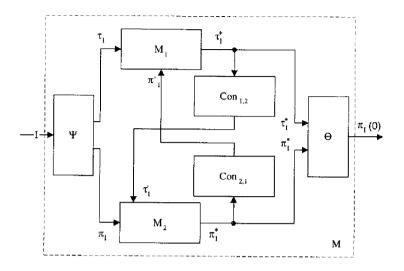

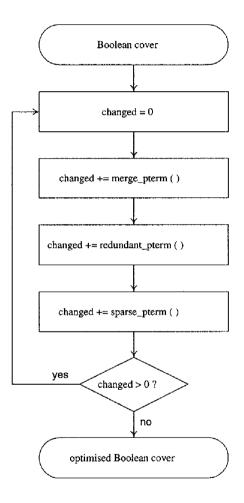

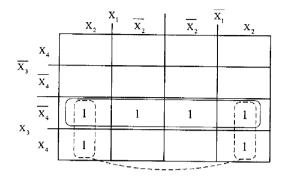

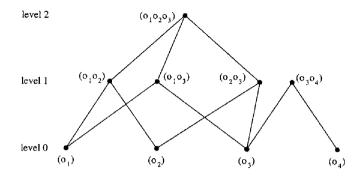

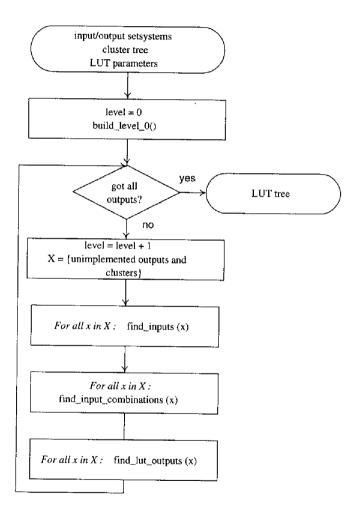

| $4.7 \leq \text{operator defined on canonical set systems}$ 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |