Citation for published version (APA):

Werf, van der, A. (1998). Processing unit design. [Phd Thesis 2 (Research NOT TU/e / Graduation TU/e), Frits Philips Inst. Quality Management]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR514711

DOI:

10.6100/IR514711

Document status and date:

Published: 01/01/1998

Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 04. Oct. 2023

Albert van der Werf

### Albert van der Werf

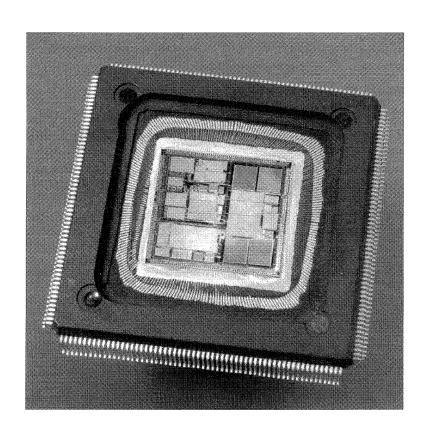

On the cover: I.McIC, a single-chip MPEG2 video encoder. This IC was designed in the period of 1994 to 1996 under the project leadership of the author. To make the circuit run at the required clock frequency, retiming techniques were applied as described in this thesis.

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr. M. Rem, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op woensdag 26 augustus 1998 om 16.00 uur

door

Albert van der Werf

geboren te Leeuwarden

Dit proefschrift is goedgekeurd door de promotoren:

prof.dr. E.H.L. Aarts en prof.dr.ir. Th. Krol

Copromotor: dr.ir. W.F.J. Verhaegh

#### CIP-DATA KONINKLIJKE BIBLIOTHEEK, DEN HAAG

van der Werf, Albert

Processing Unit Design/

Albert van der Werf. -

Eindhoven: Eindhoven University of Technology

Thesis Eindhoven. - With ref. - With summary in Dutch and English

ISBN 90-74445-41-1

Subject headings: scheduling, combinatorial optimization, IC design, high-level

synthesis, video signal processing

The work described in this thesis has been carried out at the Philips Research Laboratories in Eindhoven, the Netherlands, as part of the Philips Research programme.

© Philips Electronics N.V. 1998

All rights are reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

aan Marijn

#### **Preface**

In the summer of 1989, I became employed by Philips Research with the ambition to design state-of-the-art ICs. I had to wait for such work for five years and first became a member of a team that researched methods for the design of ICs for digital signal processing in video applications. The approach that this team set up resulted in the design methodology Phideo. My task was to develop a method for the design of the basic processing units in video ASICs.

The retiming algorithm, which had just been reported in the literature [Leiserson, Rose & Saxe, 1983], became the starting point of my work. The effect of the algorithm can be viewed as a shift of registers throughout a network of functional operations. The challenge was to make the retiming algorithm available in a practical form to IC designers. This involved writing software as well as improving the retiming algorithm in order to make run times acceptable. The software implementation of the newly developed algorithm, called RetLab (an anagram of Albert), is currently being utilized by a large IC-design community within Philips, even for ICs in other applications than digital video systems. In the early nineties a retiming tool called Optima, which is based on RetLab, was even marketed outside Philips, albeit temporarily [Sondervan, 1993; Sondervan, 1994].

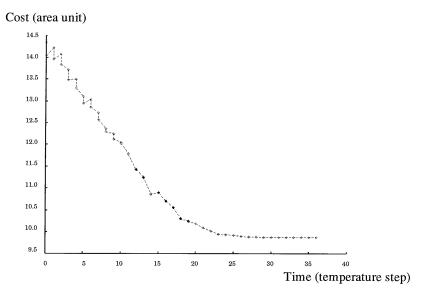

I found another challenge in developing algorithms for which the retiming technique is combined with resource sharing methods. A major part of this thesis is devoted to research on this subject. Unfortunately, it was much more difficult to make these algorithms easily accessible to the IC design community. Nevertheless, many valuable results were obtained, which give insight into algorithm development, especially in the application of simulated annealing. Moreover, its usefulness was clearly demonstrated in the design of a research vehicle [Lippens, Van Meerbergen, Verhaegh, Grant & Van der Werf, 1994].

At the end of 1994, I stopped with this work and devoted myself to the design of I.McIC, an IC for real-time MPEG2 encoding of digital video [Van der Werf, Brüls, Kleihorst, Waterlander, Verstraelen & Friedrich, 1997]. My involvement in design methods, especially the method I had developed myself, continued after this shift. Instead of being a developer, I became a user of my own design method. Although many designers within the Philips IC-design community were already enthusiastic users, it was very satisfactory that I could benefit from my own previous work as

well.

The shift in work did leave me with an unsatisfied feeling however. Although the success of the work was there, all the theory that had been built up during the years could not be easily and consistently presented. Many students had helped me with the research and had written reports in different styles. Furthermore, I had presented papers at conferences and workshops, in each case covering only a small part of the work. The task that was left was to convert a number of papers and to transform material from students into a thesis. This task comprised more than just stapling a number of papers together, which is reflected in the time it took me to write this thesis.

That I actually have written this thesis, I owe to Emile Aarts, who continued to encourage me to pursue a doctorate. I would like to thank him for that and also for the many philosophical discussions that we had and which I enjoyed.

I also want to express my gratitude to the former students whose results were undoubtedly crucial for the work presented here. I list their names here in alphabetical order: Babette de Fluiter, Eugene Heijnen, Richard Lukkassen, Marcel Peek, Christian Toma, and Arjen Vestjens.

Next I would like to thank Jef Van Meerbergen, Paul Lippens, and Wim Verhaegh, who were my fellow team members in the Phideo project. The discussions we had were very stimulating and often turned into a brainstorm producing enough ideas for a lifetime full of research. I am greatly indebted to Wim, who very carefully read drafts of this thesis.

I am very grateful to the people of Philips Electronic Design & Test, especially Rob Gerritsen, who has now left that organization. He was convinced of the strength of retiming from the very beginning of my work and showed great entrepreneurship in taking over the development of RetLab from me.

The work described in this thesis was carried out from 1989 through 1994 at the Philips Research Laboratories as part of the Philips Research programme. The research was supported by the European Commission in the ESPRIT 2260 project. I would like to thank the management of Philips Research, especially Engel Roza, for giving me the opportunity to use the research for this thesis.

Finally, I give my special thanks to my loving wife Anke for her understanding and support in numerous ways that I could never have done without.

### Contents

| 1 | Intr | roduction                                             | 1  |

|---|------|-------------------------------------------------------|----|

|   | 1.1  | Signal flow graphs and processing units               | 1  |

|   | 1.2  | Multiplexing, timefolding, and retiming               | 3  |

|   | 1.3  | Informal statement of the PU design problem           | 5  |

|   | 1.4  | Towards a solution approach                           | 11 |

|   | 1.5  | Context and related work                              | 12 |

|   | 1.6  | Organization of the thesis                            | 15 |

| 2 | For  | mal Model                                             | 17 |

|   | 2.1  | Signal flow graphs                                    | 17 |

|   | 2.2  | Timing model                                          | 19 |

|   |      | 2.2.1 The timing model of operations and signal edges | 19 |

|   |      | 2.2.2 Paths in SFGs and their timing model            | 20 |

|   | 2.3  | Mapping SFGs onto a target SFG                        | 21 |

|   |      | 2.3.1 Folding factor                                  | 21 |

|   |      | 2.3.2 Allocation                                      | 22 |

|   |      | 2.3.3 Assignment                                      | 22 |

|   |      | 2.3.4 Retiming                                        | 23 |

|   | 2.4  | False paths and loops in PUs                          | 24 |

|   | 2.5  | Mapping a target SFG onto a PU                        | 26 |

|   | 2.6  | Processing unit design problem                        | 28 |

|   | 2.7  | Special cases of PUDP                                 | 28 |

|   |      | 2.7.1 Multiplexing problem                            | 29 |

|   |      | 2.7.2 Timefolding problem                             | 29 |

|   |      | 2.7.3 Retiming problem                                | 30 |

| 3 | Con  | aplexity Analysis and Decomposition                   | 33 |

|   | 3.1  | Complexity of the processing unit design problem      | 33 |

|   | 3.2  | Decomposition of the processing unit design problem   | 37 |

|   |      | 3.2.1 Subproblem order                                | 37 |

|   |      | 3.2.2 Formal subproblem definitions                   | 40 |

|   | 3.3  | Complexity of subproblems                             | 47 |

|   |     | 3.3.1                                                      | Complexity of the operator allocation problem    | 48  |  |  |  |  |  |  |  |  |  |  |  |

|---|-----|------------------------------------------------------------|--------------------------------------------------|-----|--|--|--|--|--|--|--|--|--|--|--|

|   |     | 3.3.2                                                      | Complexity of the operator assignment problem    |     |  |  |  |  |  |  |  |  |  |  |  |

|   |     | 3.3.3                                                      | Complexity of the operator duplication problem   |     |  |  |  |  |  |  |  |  |  |  |  |

|   |     | 3.3.4                                                      | Complexity of the generalized retiming problem   | 54  |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.4 | 3.4 Overview of the complexity of PUDP and its subproblems |                                                  |     |  |  |  |  |  |  |  |  |  |  |  |

| 4 | Bas | ic Solut                                                   | tion Methods                                     | 65  |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.1 | Local                                                      | search                                           | 65  |  |  |  |  |  |  |  |  |  |  |  |

|   |     | 4.1.1                                                      | Iterative improvement                            | 66  |  |  |  |  |  |  |  |  |  |  |  |

|   |     | 4.1.2                                                      | Simulated annealing                              | 66  |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.2 | Netwo                                                      | ork flow                                         | 68  |  |  |  |  |  |  |  |  |  |  |  |

|   |     | 4.2.1                                                      | Network flow problems                            | 68  |  |  |  |  |  |  |  |  |  |  |  |

|   |     | 4.2.2                                                      | Shortest path algorithms                         | 70  |  |  |  |  |  |  |  |  |  |  |  |

|   |     | 4.2.3                                                      | Maximum-flow algorithms                          | 72  |  |  |  |  |  |  |  |  |  |  |  |

|   |     | 4.2.4                                                      | Minimum-cost flow algorithms                     | 74  |  |  |  |  |  |  |  |  |  |  |  |

|   |     | 4.2.5                                                      | Maximum-weight bipartite matching problem        | 79  |  |  |  |  |  |  |  |  |  |  |  |

| 5 | Оре | erator A                                                   | Assignment                                       | 81  |  |  |  |  |  |  |  |  |  |  |  |

|   | 5.1 |                                                            | search                                           | 82  |  |  |  |  |  |  |  |  |  |  |  |

|   |     | 5.1.1                                                      | Solution space, cost, and neighborhood structure | 82  |  |  |  |  |  |  |  |  |  |  |  |

|   |     | 5.1.2                                                      | Implementation                                   | 83  |  |  |  |  |  |  |  |  |  |  |  |

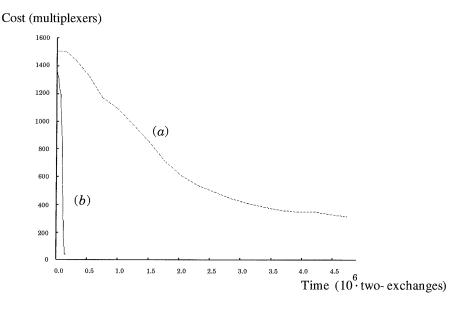

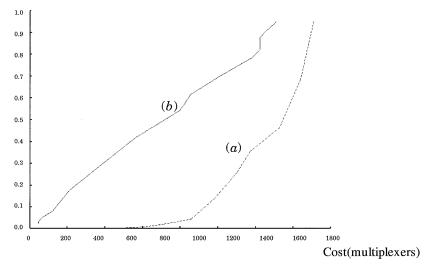

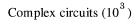

|   |     | 5.1.3                                                      | Experimental results                             | 86  |  |  |  |  |  |  |  |  |  |  |  |

|   | 5.2 | Large                                                      | SFGs                                             | 86  |  |  |  |  |  |  |  |  |  |  |  |

|   |     | 5.2.1                                                      | First experimental results                       | 88  |  |  |  |  |  |  |  |  |  |  |  |

|   |     | 5.2.2                                                      | Analysis                                         | 88  |  |  |  |  |  |  |  |  |  |  |  |

|   |     | 5.2.3                                                      | Neighborhood reductions                          | 89  |  |  |  |  |  |  |  |  |  |  |  |

|   |     | 5.2.4                                                      | Experimental results                             | 92  |  |  |  |  |  |  |  |  |  |  |  |

| 6 | Ope | rator D                                                    | <b>Duplication</b>                               | 95  |  |  |  |  |  |  |  |  |  |  |  |

|   | 6.1 | Reform                                                     | mulating the operator duplication problem        | 96  |  |  |  |  |  |  |  |  |  |  |  |

|   | 6.2 | Solution                                                   | on space, cost, and neighborhood structure       | 97  |  |  |  |  |  |  |  |  |  |  |  |

|   | 6.3 | Implei                                                     | mentation of local search                        | 99  |  |  |  |  |  |  |  |  |  |  |  |

|   | 6.4 | Experi                                                     | imental results                                  | 102 |  |  |  |  |  |  |  |  |  |  |  |

| 7 | Tim | ing Ana                                                    | alysis                                           | 107 |  |  |  |  |  |  |  |  |  |  |  |

|   | 7.1 |                                                            | timing properties                                | 108 |  |  |  |  |  |  |  |  |  |  |  |

|   | 7.2 | Redun                                                      | dancy                                            | 110 |  |  |  |  |  |  |  |  |  |  |  |

|   | 7.3 |                                                            | mentation of speed constraint derivation         | 116 |  |  |  |  |  |  |  |  |  |  |  |

|   |     | 7.3.1                                                      | Constraint generation                            | 117 |  |  |  |  |  |  |  |  |  |  |  |

|   |     | 7.3.2                                                      | Delay and weight labeling                        | 117 |  |  |  |  |  |  |  |  |  |  |  |

| Contents | X1 |

|----------|----|

| Contents | Ai |

|     | 7.4                  | 7.3.3 Efficient labeling             | 121<br>123 |  |  |  |  |  |  |  |  |  |  |

|-----|----------------------|--------------------------------------|------------|--|--|--|--|--|--|--|--|--|--|

| 8   | Reti                 | ming                                 | 127        |  |  |  |  |  |  |  |  |  |  |

|     | 8.1                  | Solution space                       | 128        |  |  |  |  |  |  |  |  |  |  |

|     |                      | 8.1.1 Timing constraint satisfaction | 129        |  |  |  |  |  |  |  |  |  |  |

|     |                      | 8.1.2 Phase constraint satisfaction  | 133        |  |  |  |  |  |  |  |  |  |  |

|     | 8.2                  | Cost                                 | 137        |  |  |  |  |  |  |  |  |  |  |

|     | 8.3                  | Neighborhood structure               | 138        |  |  |  |  |  |  |  |  |  |  |

|     | 8.4                  | Simulated annealing                  | 142        |  |  |  |  |  |  |  |  |  |  |

|     | 8.5                  | Experimental results                 | 144        |  |  |  |  |  |  |  |  |  |  |

| 9   | Con                  | clusions                             | 147        |  |  |  |  |  |  |  |  |  |  |

| Bil | Bibliography         |                                      |            |  |  |  |  |  |  |  |  |  |  |

| Au  | Author index Summary |                                      |            |  |  |  |  |  |  |  |  |  |  |

| Su  |                      |                                      |            |  |  |  |  |  |  |  |  |  |  |

| Sai | menva                | atting                               | 161        |  |  |  |  |  |  |  |  |  |  |

| Cu  | rricu                | lum Vitae                            | 163        |  |  |  |  |  |  |  |  |  |  |

# 1

#### Introduction

In this thesis we are concerned with the design of area-efficient *Processing Units* (PUs) that can execute one or more functions, specified as *Signal Flow Graphs* (SFGs), in one or more clock cycles and at a high clock frequency. The functions are part of a signal processing algorithm specifying the behaviour of a digital electronic system. The PUs are applied in video signal processors as part of an *Integrated Circuit* (IC) in silicon.

In this chapter we introduce the concepts of SFGs and PUs and we describe a number of techniques for designing PUs. The organization of this introductory chapter is as follows. SFGs and PUs are introduced in Section 1.1. Three basic techniques to design PUs, namely *multiplexing*, *timefolding*, and *retiming*, are discussed in Section 1.2. Section 1.3 discusses the relation between SFGs and PUs, and informally introduces the PU design problem. The solution strategy for the PU design problem that is described in this thesis is presented in Section 1.4. The context and related work of PU design is discussed in Section 1.5.

#### 1.1 Signal flow graphs and processing units

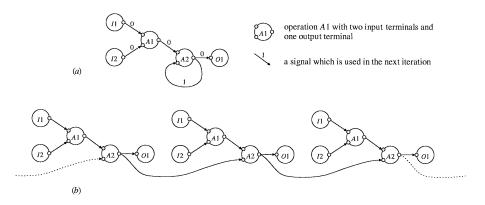

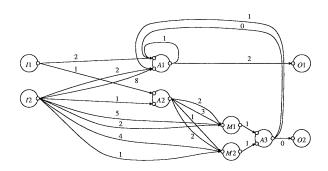

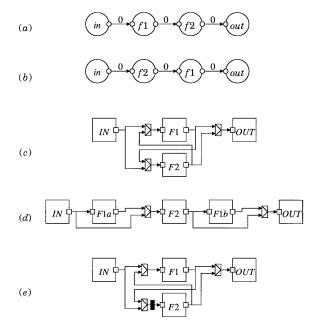

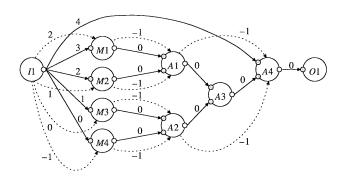

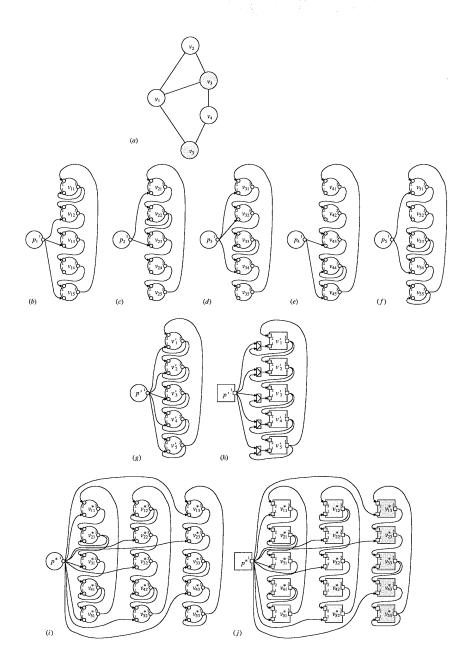

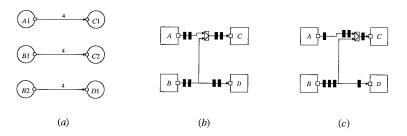

A signal flow graph represents a function that consists of *operations* of which the *input* and *output terminals* are connected by *edges*; see Figure 1.1a. Every operation in an SFG is executed repeatedly, for an indefinite period of time; see Fig-

ure 1.1b. An output terminal produces a *signal* on an edge, which is consumed at an input terminal. A signal may be used in a subsequent execution of the SFG. In that case, the edge represents a number of succeeding signal values concurrently. The *weight* on an edge refers to the number of values of previous iterations.

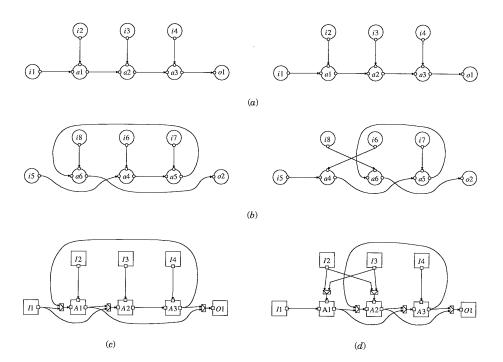

Figure 1.1. An example of a signal flow graph (a) with two input operations, I1 and I2, and one output operation O1. The operations A1 and A2 represent additions. An indefinite repetition of executions of the SFG is shown in (b).

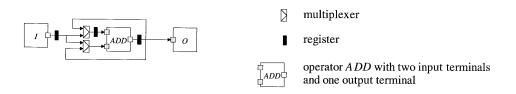

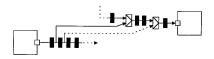

We consider PUs that consist of *operators*, *registers*, and *multiplexers* connected by point-to-point connections called *wires*; see Figure 1.2. A processing unit can execute one or more functions, specified as SFGs, in one or more clock cycles.

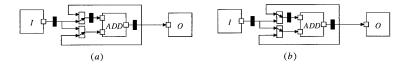

Figure 1.2. An example of a processing unit. It has one input operator, I, one output operator, O, and one adder, ADD. Furthermore, it has two multiplexers and three registers.

In this thesis we are concerned with the synchronous processing of digital signals, where a clock signal synchronizes the flow of data. A clock signal is a sequence of clock cycles that are repeated at a certain frequency. The transfer of data from one clock cycle to the next is performed by registers. At the end of a clock

cycle, which is marked by a rising edge of the clock signal, data at the input of a register is stored and available at its output during the next clock cycle.

The time it takes within a clock cycle for an operator to return a value at an output terminal after a change of value at one of its input terminals is called the *asynchronous delay*. A sequence of operators and multiplexers, connected by wires, comprises a path. The length of a path represents the total asynchronous delay of the operators and multiplexers on the path. The maximum clock frequency at which a PU can operate is determined by the so-called critical path, which is the longest path between any two subsequent registers and which must have a delay smaller than the clock period. Within the delay of the critical path all the signals of a PU will settle to a certain value. *Asynchronous feedback loops*, which are loops that contain no registers, are not allowed.

We speak of a pipelined execution of functions when more than one execution of a function is performed in parallel in the same clock cycle, but the executions are in different stages. In that case it takes a number of clock cycles before the result of a function's execution is available at the output operators. The number of clock cycles it takes to get a result is called the *synchronous delay* or the *latency*.

In a PU, data is routed from output terminals of operators to input terminals of operators by a switching network containing registers and multiplexers. A multiplexer has two input terminals, one output terminal, and a select input. The select input indicates from which input terminal the data must be routed to the output terminal.

Here, we assume that a global controller is present outside a PU that generates the select signals for the multiplexers. Furthermore, we assume that a clock signal is present for the registers. The clock terminals of registers and the select terminals of multiplexers are omitted in figures for the sake of clarity.

#### 1.2 Multiplexing, timefolding, and retiming

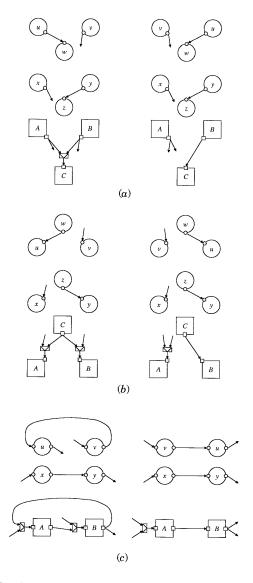

Below we consider three basic techniques that are jointly used in the design of processing units: multiplexing, timefolding, and retiming.

Multiplexing is a technique to construct a multi-functional PU that can perform more than one function. The goal with multiplexing is to save on hardware costs by reusing operators for the execution of more than one operation of different SFGs.

Depending on the function that is executed, the signals produced by operators must be routed to certain input terminals of other operators. To this end, a switching network between the operators is present that contains multiplexers. Although a multi-functional PU requires less area for operators than two or more single-functional PUs, it uses additional area for the switching network. Moreover, its

multiplexers introduce additional asynchronous delay in signal paths and therefore may decrease the maximum clock frequency at which a function can be executed.

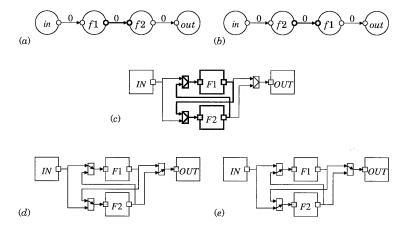

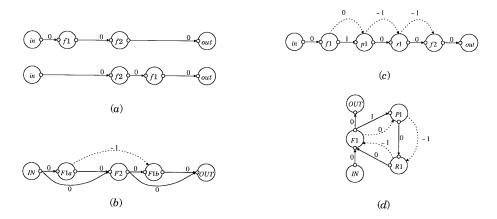

The multiplexing technique is explained with the following example. Given are the SFGs of a butterfly and a 5-tap filter, as shown in Figure 1.3. For more detailed descriptions we refer to Rabiner & Gold [1975], Oppenheim & Schafer [1975], and Roberts & Mullis [1987]. A PU that can perform either a butterfly or a 5-tap filter is shown in Figure 1.4.

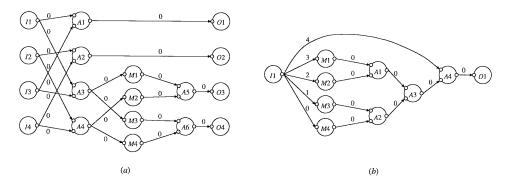

Figure 1.3. Two functions, namely a butterfly (a) and a 5-tap filter (b), specified as SFGs.

Figure 1.4. A PU that can either execute a butterfly or a 5-tap filter.

Timefolding is a technique to construct a multi-cycle PU that can execute a function in more than one clock cycle. The goal with timefolding is to save on hardware

costs by reusing operators for the execution of more than one operation of the same SFG. In the case of timefolding, the executions of operations are spread over more than one clock cycle.

Timefolding may delay operations for a number of clock cycles and consequently signals may need to be delayed one or more clock cycles. To this end, the switching network contains registers to store signals for one or more clock cycles. Furthermore, it contains multiplexers to route signals to their destinations. A multicycle PU requires less area for operators than a single-cycle PU, but additional area is used by the switching network. The multiplexers in the switching network may increase the longest path, but the registers in it may decrease it; therefore the effect on the maximum clock frequency at which the function can be executed is hard to predict.

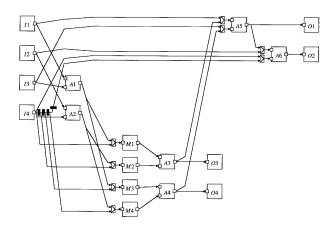

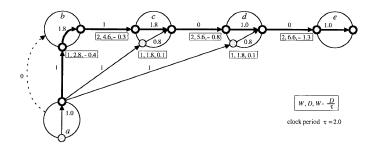

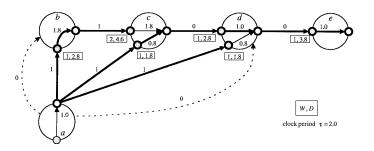

An example of a multi-cycle PU is shown in Figure 1.2. Every two clock cycles it can execute a function according to the SFG shown in Figure 1.1a. The time at which operations are executed is shown in Figure 1.5a. This can also be compactly represented in the SFG by (modified) weights on its edges; see Figure 1.5b. The multiplexer inputs that are selected are indicated in Figure 1.6.

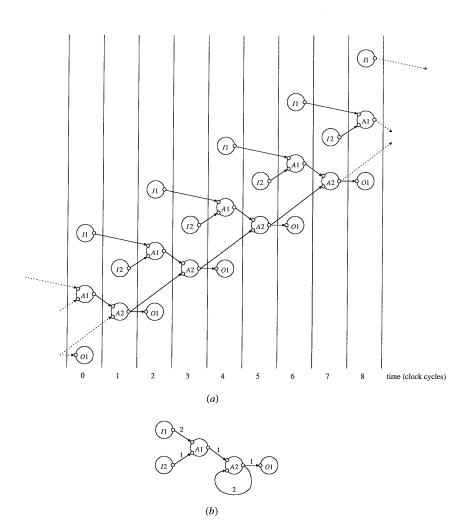

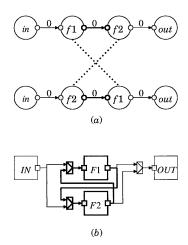

Retiming is a technique to construct a PU that executes a function at a required clock frequency. The technique is called retiming, because the position of registers in a PU is determined by a change of the times at which operations are executed. Since the placement of the registers determines the longest path between two registers in the PU, retiming affects the maximum clock frequency at which functions can be executed. Retiming may result in a change in the production and consumption times of output and input signals, respectively. Consequently, executions of functions may become overlapping in time, resulting in a pipelined implementation. Examples of PUs that are designed using retiming are shown in Figure 1.7.

The three design techniques *multiplexing*, *timefolding*, and *retiming* can be combined. A PU that can perform either a butterfly or a 5-tap filter every two clock cycles is shown in Figure 1.8.

#### 1.3 Informal statement of the PU design problem

The relationship between SFGs and a PU that can execute them can be defined in two steps. Firstly the SFGs are mapped onto a new target SFG, and secondly this SFG is implemented by a PU.

The first mapping, from one or more source SFGs to a target SFG, is defined by three sets of variables. These are the number of operations *allocated* in the target SFG, each of which corresponds to an operator in the PU, the operator to

Figure 1.5. (a) The time at which the operations of the SFG of Figure 1.1a are executed. Note that the SFG is executed in a timefolded and pipelined way. (b) The SFG of Figure 1.1a with its weights modified according to the times at which its operations are executed as shown in (a).

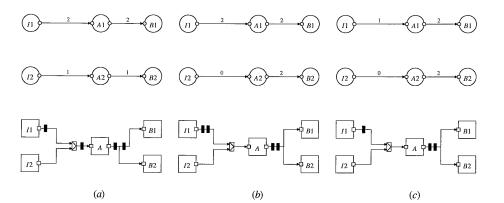

Figure 1.6. A multi-cycle PU that executes the SFG of Figure 1.1. The multiplexers indicate the input that is selected. The situation of (a) corresponds to the clock cycles in which operations I2 and A2 are executed. The situation of (b) corresponds to the clock cycles in which operations I1, A1, and O1 are executed.

Figure 1.7. PUs designed using the retiming technique for the butterfly (a) and the 5-tap filter (b), which are specified by the SFGs shown in Figure 1.3. We assumed that on a single path one multiplication or two additions can be performed in one clock cycle and that the delays of the input and output operators can be neglected.

Figure 1.8. A PU that every two clock cycles can perform either a butterfly or a 5-tap filter, which are specified by the SFGs shown in Figure 1.3. We assume that on a path one multiplication or two additions can be performed in one clock cycle and that the delays of the input and output operators can be neglected.

which each operation is *assigned*, and the time at which it is executed. The latter is indicated relative to an initial execution time and is called *retiming*. To design a PU we have to determine these variables; therefore we call them *decision variables*.

The variables must satisfy the following design constraints. There must be sufficient operators available to execute the operations. The time at which an operation is executed must be such that no path is longer than the clock period. Furthermore, two operations of one SFG must be executed at different clock cycles when they are mapped onto the same operator. No asynchronous feedback loops may be present in the PU designed.

The three sets of decision variables define a target SFG in which the edges are determined by the assignment of operations to operators. Every edge in the target SFG has a corresponding edge in one of the source SFGs. The weight of the edge in the target SFG is determined by the execution times of the producing and consuming operations and the original weight of the corresponding edge in one of the SFGs. The effect of retiming is that delaying the consuming operation increases the weight, while delaying the producing operation decreases it.

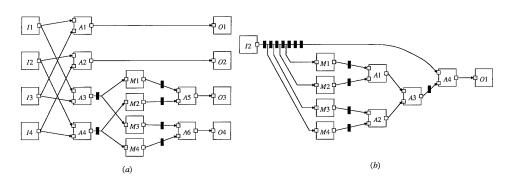

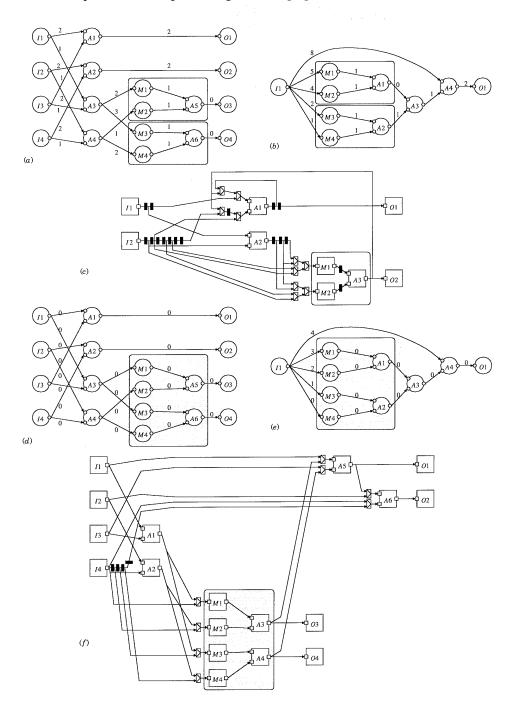

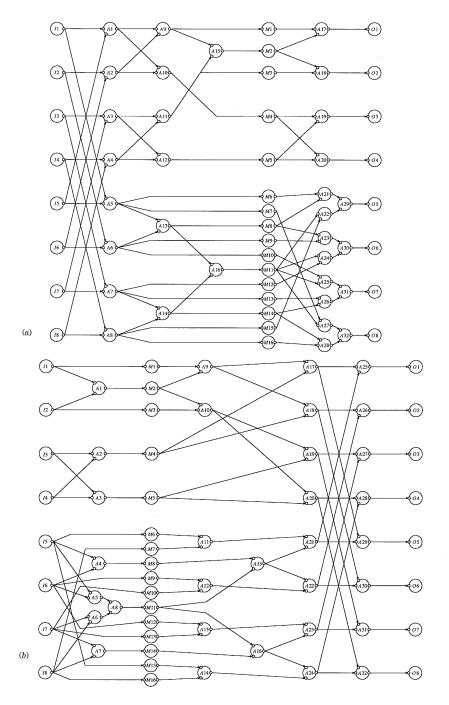

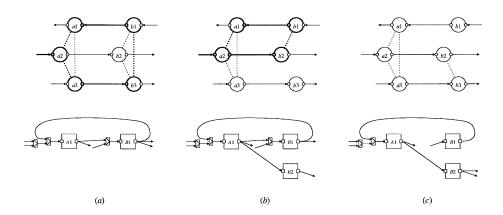

We take as an example the design of the PU that is shown in Figure 1.8, which every two clock cycles can execute either a butterfly or a 5-tap filter, which are specified by the SFGs shown in Figure 1.3. The allocation consists of two input operators, two output operators, two multipliers, and three adders. Table 1.1 gives the assignment. The retiming of the operations and its effect on the weights of the edges in the source SFG is shown in Figure 1.9. The target SFG constructed according to the allocation, assignment, and retiming is shown in Figure 1.10.

The second part of the mapping of SFGs onto a PU is the mapping of the

Table 1.1. The assignment of operations to operators for the example of mapping the SFGs of the butterfly and the 5-tap filter as shown in Figure 1.3 onto the PU of Figure 1.8.

|           |            |           |    |    |    |   |        |   |   |    |    | -  |    | (            | )per | atio | ns |    |    |    | - |    |    |    |    |    |    |    |    |

|-----------|------------|-----------|----|----|----|---|--------|---|---|----|----|----|----|--------------|------|------|----|----|----|----|---|----|----|----|----|----|----|----|----|

| H         |            | Butterfly |    |    |    |   |        |   |   |    |    |    |    | 5-tap filter |      |      |    |    |    |    |   |    |    |    |    |    |    |    |    |

|           |            | 11        | 12 | 13 | 14 | 0 | 00     | 8 | 8 | A1 | A2 | A3 | 44 | A5           | 4e   | M1   | M2 | M3 | M4 | 11 | 0 | A1 | A2 | A3 | 44 | M1 | M2 | МЗ | M4 |

| 1         | <i>I</i> 1 | •         | •  |    |    |   |        |   |   |    |    |    |    |              |      |      |    |    |    |    |   |    |    |    |    |    |    |    |    |

| ll        | <i>I</i> 2 | 1         |    | •  | •  |   | $\Box$ |   |   |    |    |    |    |              |      |      |    |    | П  | •  |   |    |    |    |    |    |    |    |    |

| ors       | 01         |           |    |    |    | • | •      |   |   |    |    |    |    |              |      |      |    |    |    |    | • |    |    |    |    |    |    |    |    |

| rate      | 02         |           |    |    |    |   |        | • | • |    | Г  |    |    |              |      |      |    |    |    |    |   |    |    |    |    |    |    |    |    |

| Operators | A1         | 1         |    |    |    |   |        |   |   | •  | •  |    |    |              |      |      |    |    |    |    |   |    |    | •  | •  |    |    |    |    |

| 110       | A2         |           |    |    |    |   |        |   |   |    |    | •  | •  |              |      |      |    |    |    |    |   |    |    |    |    |    |    |    |    |

|           | A3         |           |    |    |    |   |        |   |   |    |    |    |    | •            | •    |      |    |    |    |    |   | •  | •  |    |    |    |    |    |    |

|           | M1         |           |    |    |    |   |        |   |   |    |    |    |    |              |      | •    |    | •  |    |    |   |    |    |    |    | •  |    | •  |    |

|           | M2         |           |    |    |    |   |        |   |   |    |    |    |    |              |      |      | •  |    | •  |    |   |    |    |    |    |    | ٠  |    | •  |

Figure 1.9. The SFGs of the butterfly (a) and the 5-tap filter (b). The number in an operation denotes its retiming with respect to the SFGs shown in Figure 1.3. The weights on the edges are adjusted according to the retiming.

Figure 1.10. A target SFG constructed in the design process for a multi-functional multi-cycle PU that can execute either the butterfly or the 5-tap filter. The weights correspond to the SFGs shown in Figure 1.9 and the assignment is according to Table 1.1.

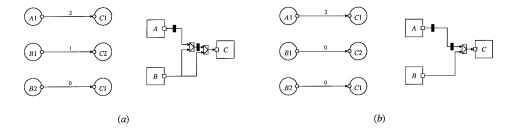

target SFG onto the PU. There, the sets of decision variables are associated with the *register allocation*, indicating for every terminal the number of registers that are placed there, and the *multiplexer allocation*, indicating for every input terminal the number of multiplexers placed there. To implement an edge, the total number of registers allocated to the corresponding input and output terminals should be at least the weight of the edge. Furthermore, the number of multiplexers allocated at an input terminal should be equal to one less than the number of edges connected to it with both different sources and with different weights. An example of a register and multiplexer allocation is shown in Figure 1.11. Note that we limit ourselves to the sharing of registers by edges in the target SFG that are incident to the same output or input terminal.

Figure 1.11. An example of a register and multiplexer allocation. At the output terminal four registers are allocated. At the input terminal four registers and two multiplexers are allocated. The connection indicated by a solid line between the input and output terminals corresponds with an edge with a weight equal to four.

The second part of the mapping can be considered as a sophisticated cost evaluation, i.e., main decisions are taken in the first part, but their costs are determined in the second part.

#### The objective of PU design

Our objective is to develop a method for designing a PU that occupies minimal silicon area and runs at the required clock frequency, using a combination of multiplexing, timefolding, and retiming techniques. We use an estimate of the area given by a weighted sum of the number of operators, multiplexers, registers, and wires.

The effect of each of the techniques, and certainly that of a combination of them, on the area of the PU and the clock frequency at which it can execute the SFGs cannot well be predicted in general. Since the area is a minimization goal, and the clock frequency is a constraint, the retiming technique is the most important one to obtain at least a feasible PU.

#### 1.4 Towards a solution approach

In this section we discuss an approach to developing a solution method for the efficient design of PUs of which the behaviour is specified by one or more SFGs.

First, a formal model is set up, which we use to formally define the processing unit design problem. The model contains the decision variables and formally defines SFGs, PUs, and their timing behaviour. The processing unit design problem is formulated as a combinatorial optimization problem. Next, the complexity of the processing unit design problem is analyzed to determine whether the problem can be solved easily using (existing) algorithms with acceptable run times, or if it is, formally spoken, difficult. The result of this analysis is that the problem is difficult to solve; this result is essential to the work that is described further in this thesis.

The processing unit design problem is decomposed such that the determination of a retiming follows the determination of an operator assignment. The main reason for this order is that we want to exploit regularity in the source SFGs, i.e., substructures of it may be identical. First we determine an operator assignment such that the identical substructures become present in the target SFG. For example, in the target SFG shown in Figure 1.10 the operators M1, M2, and A3 comprise a substructure that is also present in the source SFGs shown in Figure 1.3. Because this assignment is based on a minimal number of operators, asynchronous feedback loops may be introduced. These loops will never carry data around since the data routing will be according to one of the functions that can be executed, which is free of asynchronous feedback loops. Therefore they are called false loops. Since a PU may not contain asynchronous feedback loops, the false loops are removed in the following step that allocates additional operators to which some operations are reassigned. To ensure that the PU designed can run at the required clock frequency, a timing analysis is performed resulting in a set of linear constraints on retiming. Finally, a feasible retiming is determined such that corresponding operations in identical substructures are, if possible, equally retimed.

Restrictions on the instances of the processing unit design problem lead to the definition of three special cases of it, i.e., the multiplexing, timefolding, and retiming problem. Each of the special cases emphasizes one of the subproblems into which the PU design problem is decomposed. The complexity of each of the subproblems is analyzed, also in special cases.

The identified subproblems can be handled using algorithms belonging to the field of local search and network flow. Local search is applied for most of the subproblems, but first in a straightforward way. If the time performance of the local search algorithm is unacceptable for problem instances of a typical size, we search for ways to improve the application of local search. Although local search algorithms can be readily applied without the use of much detailed knowledge, we

12 Introduction

show that good solutions can only be obtained within acceptable run times by using problem-specific information.

Network flow algorithms can be applied to solve the retiming problem. Furthermore, a shortest path algorithm is used for timing analysis, and a bipartite-graph maximum-weighted matching algorithm is used to compute the register cost of a PU. Even when a problem is mathematically spoken easy and can be solved by, e.g., a network flow algorithm, the solution method deserves attention for its time performance.

#### 1.5 Context and related work

The work described in this thesis is in the field of Electronic Design Automation (EDA). In the past decades, EDA has received increasing attention and more participants. In 1980 the first International Conference on Circuits and Computers (ICCC) [Rabbat, 1980] was held, which three years later was renamed the International Conference on Computer-Aided Design. This was followed in 1982 with the publication of the first IEEE (Institute of Electrical and Electronics Engineers) Transactions on Computer-Aided Design (CAD) of Circuits and Systems [Rohrer, 1982]. A part of EDA concentrates on the translation of an abstract behavioral specification to a register-transfer level implementation, which is called *high-level synthesis* [McFarland, Parker & Camposano, 1990]. For an overview of problems and their solution methods belonging to the field of high-level synthesis, we refer the reader to McFarland, Parker & Camposano [1990], Borriello & Detjens [1988], Martin & Knight [1993], and Stok [1994].

In the eighties, research on high-level synthesis was started at the Philips Research Laboratories. The first result was a design method for audio signal processing called Piramid [Woudsma, Beenker, Van Meerbergen & Niessen, 1990]. This method was successfully applied to, e.g., the design of an ASIC for compact disc players [De Loore, Crombez, Delaruelle, Sheridan, Woudsma, Niessen, Biesterbos, Gubbels & Repko, 1992]. In the late eighties it became apparent that digital video signal processing had become feasible for consumer products and, consequently, that it was important for Philips. Therefore, new work was directed towards video applications and resulted in the design method Phideo [Van Meerbergen, Lippens, Verhaegh & Van der Werf, 1995]. For Piramid as well as for Phideo, processing units are designed that can execute functions specified as subgraphs of the total SFG specifying the function to be implemented. These subgraphs are treated as single operations during the scheduling, allocation, and assignment phases of Phideo and Piramid.

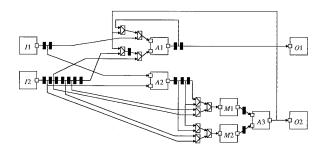

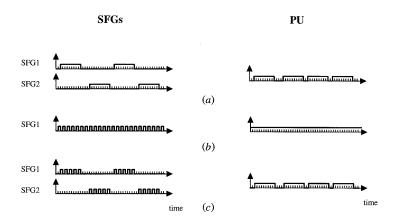

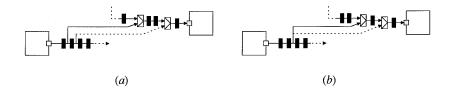

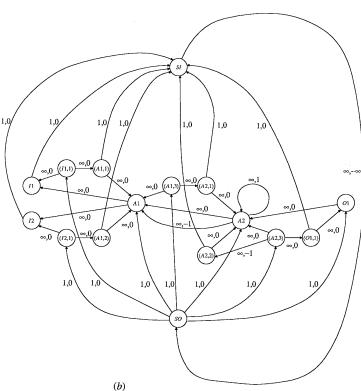

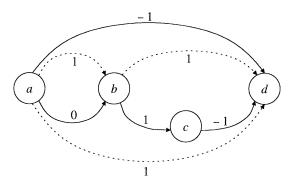

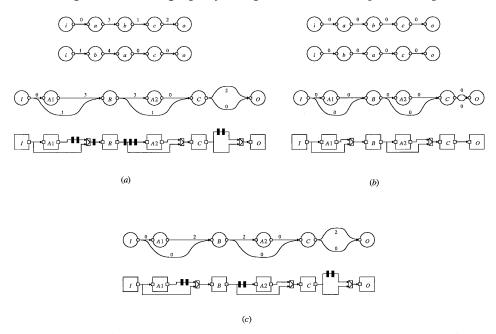

As a result of the scheduling of the subgraphs, they can be executed at nonoverlapping time intervals. Consequently, multiplexing techniques may be used to design processing units that can execute more than one SFG. As a result of scheduling, subgraphs can be executed repetitively with a period greater than one clock cycle. This is especially the case in Phideo, which is based on a model of multidimensional periodic operations [Verhaegh, 1995]. Consequently, timefolding techniques can be used to design processing units that can execute SFGs in more than one clock cycle. An overview of the possible design techniques that can be applied in certain situations is shown in Figure 1.12.

Figure 1.12. The activities of the source SFGs determine the design techniques that can be used. In (a) the activities of the source SFGs allow the application of the multiplexing technique. The activity of the PU on which the SFGs can be executed is shown as well, which results in well occupied hardware resources. In (b) the activity of one source SFGs is such that the timefolding technique can be applied. In (c) the activities of the source SFGs are such that both multiplexing and timefolding techniques can be applied.

To make the processing units run at a desired clock frequency, we apply retiming techniques. As a result of retiming, a processing unit can be pipelined, i.e., consumption and production times of input and output signals, respectively, can be changed with respect to the times specified by the corresponding SFG [Van der Werf, McSweeney, Van Meerbergen, Lippens & Verhaegh, 1991]. These changes can be accommodated by the scheduling and memory synthesis techniques of Piramid and Phideo.

The classical retiming technique was introduced by Leiserson, Rose & Saxe [1983]. Saxe [1985] described this work in his thesis and a refined version of the reported work appeared in 1991 [Leiserson & Saxe, 1991]. The first step in the classical retiming technique is the derivation of a number of speed constraint relations between pairs of operations. Together with causality constraints and a cost

14 Introduction

function they comprise a special case of an (integer) linear programming problem, which can be solved in polynomial time using network-flow algorithms [Ford & Fulkerson, 1962]. To derive the speed constraints in the first step an asynchronous-timing analysis, determining the length of paths between two registers is performed for all possible register allocations. The problem of speed constraint derivation can be solved with shortest path algorithms, which are also part of the field of network flows [Ford & Fulkerson, 1962].

When using the classical retiming technique for the design of processing units that run at high throughput frequencies and in a pipelined fashion, the timing analysis step may take a very long time. This was observed by Münzner & Hemme [1991], who developed a more efficient heuristic, which may find sub-optimal solutions. An important contribution of the work described in this thesis is a speed constraint derivation algorithm that is fast and gives optimal solutions. This work was first reported in [Van der Werf, Van Meerbergen, Aarts, Verhaegh & Lippens, 1994]. About half a year later, still in 1994, Shenoy & Rudell reported a similar, but less efficient method for speed constraint derivation.

Retiming in the context of resource sharing can be viewed as scheduling. Scheduling is an important area of interest in the field of combinatorial optimization [Papadimitriou & Steiglitz, 1982]. Baker [1974] defines scheduling as the problem of allocating scarce resources to activities in time. For an elaborate introduction to the theory of scheduling we refer to Conway, Maxwell & Miller [1967], Baker [1974], Coffman [1976], French [1982] and Pinedo [1995]. Scheduling for processing unit design is non-preemptive, which means that the execution of an operation cannot be interrupted. Several approaches have been presented to scheduling in the context of IC design, such as list scheduling [McFarland, 1986; Haupt, 1989; Parker, Pizarro & Mlinar, 1986; Park & Parker, 1988; Verhaegh, 1995], integer linear programming based scheduling [Gebotys & Elmasry, 1990; Hwang, Lee & Hsu, 1991], and approaches based on domain reduction, also called constraint satisfaction techniques [Paulin & Knight, 1989; Timmer & Jess, 1993; Verhaegh, Lippens, Aarts, Korst, Van Meerbergen & Van der Werf, 1995].

Scheduling and retiming both determine the time at which operations are executed. Whereas retiming is considered to deliver a circuit that meet asynchronous timing constraints, scheduling is used to meet both synchronous timing constraints and hardware resource constraints. In this thesis a combination of both objectives is considered, which is covered by the term retiming. Related work has been reported in which the combination is often referred to as "operator chaining during scheduling"; see, e.g., [Parker, Pizarro & Mlinar, 1986; Park & Parker, 1988; Park & Kyung, 1993].

In this thesis, we present a decomposition of the processing unit design problem

in which we determine a retiming after a number of operators are allocated and the operations are assigned to them. In most other applications of scheduling and operator assignment in the context of IC design the order is reversed; see, e.g., [Parker, Pizarro & Mlinar, 1986; Park & Parker, 1988; Park & Kurdahi, 1989; Park & Kyung, 1993; McFarland, 1986; Haupt, 1989; Paulin & Knight, 1989; Timmer & Jess, 1993].

The importance of an operator assignment has also been recognized by Note, Catthoor & De Man [1989], Geurts, Catthoor & De Man [1993a], and Geurts, Catthoor & De Man [1993b], who discuss the design of processing units that can perform more than one function for ICs designed with the Cathedral III method [Note, Geurts, Catthoor & De Man, 1991]. Geurts, Catthoor & De Man [1993b] avoid the existence of false loops by taking additional constraints into account in a quadratic 0-1 programming model. Other work on operator assignment in which the importance of false loops is considered is reported by Stok [1992].

Since many of the problems related to the design of digital ICs have a discrete nature, they can be formulated as combinatorial optimization problems. This opens the way to applying the elaborate theory of combinatorial optimization, as can be found in, e.g., Papadimitriou & Steiglitz [1982], Schrijver [1986], and Nemhauser & Wolsey [1988]. Furthermore, this allows us to study the computational complexity [Garey & Johnson, 1979] of the design problems.

#### 1.6 Organization of the thesis

The organization of this thesis in chapters and sections reflects the solution approach. Chapter 2 describes a formal model that we use to describe the processing unit design problem. Chapter 3 discusses the complexity of the processing unit design problem and its decomposition. Next we have Chapter 4, which is an intermediate chapter that summarizes the concepts of local search and network flow. Chapter 5 discusses a solution method for the first subproblem, which is to determine an operator assignment. Chapter 6 discusses the next subproblem, which is to find an allocation of additional operators to which some operations are reassigned. Chapter 7 discusses the subproblem concerned with the timing analysis of SFGs, which is to efficiently derive speed constraints. Chapter 8 discusses the final subproblem, which is to determine a retiming. We end this thesis with Chapter 9, which contains the conclusions of the presented work.

# 2

#### Formal Model

In this chapter we first give the formal model of an SFG in Section 2.1, followed by a discussion on its timing model in Section 2.2. In Section 2.3 the relation between a number of source SFGs and the target SFG on which they are mapped is discussed. This is followed by a discussion in Section 2.4 on the modelling of false loops that may be introduced by the mapping. The implementation of an SFG is called a PU and its cost is discussed in Section 2.5. In Section 2.6 a formal problem definition of PU design is given. We conclude this chapter with defining three special cases of PU design in Section 2.7.

#### 2.1 Signal flow graphs

An SFG consists of operations that are interrelated in some way. Here, we define the edges in an SFG not between the operations, as is done in most graph-based specifications, but between operation terminals. Therefore, an SFG can be represented as a directed graph in which the vertices are the operation terminals, either input or output, and the edges run from output terminals to input terminals. This leads to the following definition.

**Definition 2.1 (signal flow graph).** A *signal flow graph*  $\mathcal{G}$  is given by a three tuple (V,T,E) in which

V

is a set of operations, and

П

$T = O \cup I \subseteq V \times \mathbb{I}N$  is a set of operation terminals, where

O is a set of output terminals, I is a set of input terminals,

and  $O \cap I = \emptyset$ , and

$E \subseteq O \times I$  is a multi-set of *signal edges* representing the signal flow,

where IN is the set of non-negative integers.

Input operations of an SFG are modelled as operations without input terminals and output operations are modelled as operations without output terminals.

Since we discuss the mapping of possibly more than one source SFG onto a PU, different SFGs are identified by an index,  $\mathcal{G}_i = (V_i, T_i, E_i)$ , where i = 1, ..., N. The union of all these SFGs is indicated by  $\mathcal{G}$  and is called the *union SFG*. The union of all operations is indicated by V, i.e.,  $V = \bigcup_{i=1,...,N} V_i$ . Likewise, the unions of all terminals and edges are defined.

The design of a processing unit is partitioned into two steps. In the first step a number of source SFGs are mapped onto a target SFG and in the second step the target SFG is mapped onto a PU. The relationship between a target SFG and a PU is very direct. Consequently, we neglect the difference and also refer to a target SFG by the words *processing unit*. For the PU we use an apostrophe in the notation  $(\mathcal{G}' = (V', T', E'))$ , as well as for the variables pertaining to a PU. Furthermore, we call the operations of a PU *operators*.

To be able to formally define the relationship between SFGs and a PU, it is necessary to define the set of operation types. From a structural perspective, every operation type is characterized by its number of inputs and number of outputs. Furthermore, the cost of an operation type is important.

#### **Definition 2.2 (operation type).** $\mathcal{T}$ denotes a set of *operation types* where

$\mathcal{I}: \mathcal{T} \to IN$  returns the number of input terminals, and  $\mathcal{O}: \mathcal{T} \to IN$  returns the number of output terminals, and  $\mathcal{C}: \mathcal{T} \to Q$  returns the cost of an operator of this type.

We consider operations and operators that can perform only one type of operation. We define the following function, so that we can determine the type of an operation.

**Definition 2.3 (type function).** Given are an SFG  $\mathcal{G}$  and a type set  $\mathcal{T}$ . The *type function*  $l: V \to \mathcal{T}$  returns the type of an operation.

The number of terminals of each operation is determined by the corresponding operation type. Given an SFG  $\mathcal{G}$  and a type function  $\ell$ , the relationship between the

operation set and the terminal set is given as

$$I = \{(v, i) | v \in V \text{ and } i = 1, ..., \mathcal{I}(\ell(v))\}$$

$$O = \{(v, i) | v \in V \text{ and } i = \mathcal{I}(\ell(v)) + 1, ..., \mathcal{I}(\ell(v)) + \mathcal{O}(\ell(v))\}.$$

#### 2.2 Timing model

We discuss the synchronous processing of digital signals, where a processor clock synchronizes the flow of data. For synchronous circuitry, time is divided into an asynchronous component and a synchronous one. Synchronous timing is expressed in integer multiples of clock cycles, while asynchronous timing is expressed in real units, e.g., nanoseconds. We first discuss the timing model of operations and signal edges in Section 2.2.1. In Section 2.2.2 we introduce paths and discuss their timing properties.

#### 2.2.1 The timing model of operations and signal edges

The asynchronous timing model of an operation contains a delay for every pair consisting of an input terminal and an output terminal, which is defined as follows.

**Definition 2.4 (delay).** Given is an SFG  $\mathcal{G}$ . The *delay* is a function  $del: I \times O \rightarrow \mathbb{Q}^+ \cup \{\sim\}$  that returns the delay between an input terminal and an output terminal. The delay is only defined when there is a path from the input terminal to the output terminal inside one operation and without registers. Otherwise the delay is undefined, which is indicated by  $\sim$ .  $\mathbb{Q}^+$  denotes the set of non-negative elements of  $\mathbb{Q}$ .

To allow the timing model to be useful for sequential operations that take more than one clock cycle to execute, e.g., pipelined multiplications, it is extended with a number of functions. To this end, the timing model of an operation of an SFG contains information about the delay from an input terminal to an internal register and from an internal register to an output terminal. The former is called the *data* available time and the latter is called the *data* ready time. They are defined as follows.

**Definition 2.5 (data available time).** Given is an SFG  $\mathcal{G}$ . The *data available time* is a function  $dat: I \to \mathbb{Q}^+$  that returns the maximum delay of an internal path from an input terminal to either an internal register or an output terminal of the corresponding operation.

**Definition 2.6 (data ready time).** Given is an SFG  $\mathcal{G}$ . The *data ready time* is a function  $drt: O \to \mathbb{Q}^+$  that returns the maximum delay of an internal path from either an internal register or an input terminal of the corresponding operation to an output terminal.

If an operation v has a completely asynchronous behaviour, then the following holds for its input terminals (v, a) and its output terminals (v, b):

$$dat((v,a)) = \max_{o=(v,b)\in O} del((v,a),o), \text{ and}$$

$$drt((v,b)) = \max_{i=(v,a)\in I} del(i,(v,b)).$$

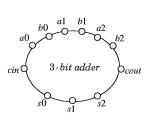

An example of a timing model of an operation is given in Figure 2.1.

| in         | puts |     | a0 | <i>a</i> 1 | a2 | <i>b</i> 0 | <i>b</i> 1 | <i>b</i> 2 | cin |

|------------|------|-----|----|------------|----|------------|------------|------------|-----|

| output     | dat  | 10  | 5  | 5          | 10 | 5          | 5          | 10         |     |

|            | drt  | del |    |            |    |            |            |            |     |

| s0         | 5    |     | 5  | ~          | ~  | 5          | ~          | ~          | 5   |

| s1         | 10   |     | 10 | 5          | ~  | 10         | 5          | ~          | 10  |

| <i>s</i> 2 | 5    |     | ~  | ~          | 5  | ~          | ~          | 5          | ~   |

| cout       | 5    |     | ~  | ~          | 5  | ~          | ~          | 5          | ~   |

Figure 2.1. An example of an operation (3-bit adder) and its timing model. The adder is internally pipelined.

Below we assume that for an SFG  $\mathcal{G}$ , a given clock period  $\tau$ , and timing functions drt, dat, and del, every operation in the SFG can be executed within one clock period, i.e.,

$$drt(o) < \tau$$

for each  $o \in O$ ,

$dat(i) < \tau$  for each  $i \in I$ , and, consequently,

$del(i, o) < \tau$  for each  $(i, o) \in I \times O$  with  $del(i, o) \neq \sim$ .

A signal in an SFG may be delayed a number of clock cycles between its production and consumption. To quantify this relation a weight on a signal edge, defined as follows, is applied.

**Definition 2.7 (weight).** Given is an SFG  $\mathcal{G}$ . The weight  $w: E \to \mathbb{Z}$  is defined as the number of clock cycles that a signal on an edge is delayed.

Here, we assume that both the data available times and data ready times of registers are equal to zero and that multiplexers have delays equal to zero. The timing model of operations is thus applicable for both sequential and combinational operations.

#### 2.2.2 Paths in SFGs and their timing model

In this section we discuss some basic theory on paths in SFGs.

**Definition 2.8 (path).** Given is an SFG  $\mathcal{G}$ . A path p is an alternating sequence of output and input terminals, starting with an output terminal and ending with an input terminal, of the following form:  $p = (o_1, i_2, o_2, ..., i_{n-1}, o_{n-1}, i_n)$ , where  $(o_k, i_{(k+1)}) \in E$  for each k = 1, ..., n-1 and  $del(i_k, o_k) \neq \sim$  for each k = 2, ..., n-1. Furthermore,  $o_k \neq o_l$ , and  $i_k \neq i_l$  for each k, l = 1, ..., n with  $k \neq l$ . Sometimes we only need to know on what operation output the path begins and on what operation input it ends. We then denote the path p by  $(o_1 \mapsto i_n)$ .  $P_{\mathcal{G}}$  denotes the set of all paths in  $\mathcal{G}$ .

The definition of a path is such that it cannot be a cycle or contain one, because it may visit an operation terminal only once. Moreover, all operations in a path belong to one source SFG.

The notion of timing functions in the timing model and weights on signal edges is extended to the domain of paths.

**Definition 2.9 (path delay).** Given are an SFG  $\mathcal{G}$  and timing functions dat, drt, and del. The path delay is a function  $D: P_{\mathcal{G}} \to \mathbb{Q}^+$  that returns the delay of a path, which is defined as follows. For each  $p = (o_1, i_2, o_2, ..., i_{n-1}, o_{n-1}, i_n) \in P_{\mathcal{G}}, D(p) = drt(o_1) + \sum_{k=2}^{n-1} del(i_k, o_k) + dat(i_n)$ .

Note that the delay of a path does not depend on the weights of the signal edges in the path. Consequently, the delay of a path can be greater than the clock period at which an SFG can be executed.

**Definition 2.10 (path weight).** Given are an SFG  $\mathcal{G}$  and a timing function w. The *path weight* is a function  $W: P_{\mathcal{G}} \to \mathbb{Z}$  that returns the weight of a path  $p = (o_1, i_2, o_2, ..., i_{n-1}, o_{n-1}, i_n) \in P_{\mathcal{G}}$  and is defined as  $W(p) = \sum_{k=1}^{n-1} w(o_k, i_{k+1})$ .

# 2.3 Mapping SFGs onto a target SFG

The mapping of a union of source SFGs onto a PU is done in two steps. First the source SFGs are mapped onto a target SFG, and then this target SFG is implemented by a PU. The first step is discussed in this section, the second step in one of the following sections, Section 2.5. First the folding factor is introduced in Section 2.3.1. This is followed by a discussion in Sections 2.3.2 to 2.3.4 on the three decision variables: allocation, assignment, and retiming.

#### 2.3.1 Folding factor

Timefolding implies that the synchronous timing behaviour of a source SFG is expressed using a processing clock that has more than one clock cycle for every execution of the SFG. The number of clock cycles used for one execution is called the folding factor and is defined as follows.

**Definition 2.11 (folding factor).** Given are a source SFG  $\mathcal{G}$  and a weight w. The *folding factor* of  $\mathcal{G}$  is defined by a positive integer f. Furthermore, the folding factor defines a folded weight  $w_f : E \to \mathbb{Z}$  as follows. For each  $e \in E$ ,  $w_f(e) = f * w(e)$ .

Below we do not consider explicitly the folded weight; we assume that it is already accounted for in the weight. The number of clock cycles that it takes to execute one iteration of a source SFG is expressed in *phases*. The notion of phase is formally defined in Section 2.3.4.

#### 2.3.2 Allocation

The operator allocation determines the operator set V' and the terminal set T' of a PU  $\mathcal{G}'$ .

**Definition 2.12 (operator allocation).** Given is a set of operation types  $\mathcal{T}$ . The *operator allocation* is a function  $al: \mathcal{T} \to \mathbb{I}\mathbb{N}$  that returns for each operation type the number of allocated operators.

In order to execute each of a union of source SFGs  $\mathcal{G}_i$ ,  $i=1,\ldots,N$ , by a PU  $\mathcal{G}'$ , it must have a sufficient number of operators, i.e., there is a lower bound on |V'|. Since we consider operators that can perform only one type of operation, this bound is determined by the bounds of each specific operation type. Therefore, the sets  $V_i$ ,  $i=1,\ldots,N$ , are partitioned into subsets of the same operation type, i.e.,  $V_i = \bigcup_{j \in \mathcal{T}} V_{i,j}$ , where  $V_{i,j} = \{v \in V_i \mid \ell(v) = j\}$ ,  $i=1,\ldots,N$ . A constraint on the allocation following from the instances is as follows.

(i)

$$al(j) \ge \max_{i=1,\dots,N} \lceil \frac{|V_{i,j}|}{f_i} \rceil$$

for each  $j \in \mathcal{T}$ .

#### 2.3.3 Assignment

The assignment of the operations of a source SFGs to the operations of a target SFG is defined as follows.

**Definition 2.13 (operator assignment).** Given are a union  $\mathcal{G}$  of source SFGs  $\mathcal{G}_i$ ,  $i=1,\ldots,N$ , a set of operators V', a type function  $\ell$ , and folding factors  $f_i$ . The *operator assignment* is a function  $as:V\to V'$  that returns for each operation in V the operator in V' on which it is executed.

An operator assignment must meet the constraints that each operation is assigned to an operator of the same type and that the number of operations in the same source SFG that are assigned to one operator cannot exceed the number of available phases, i.e.,

(ii)

$$\ell(v) = \ell(as(v))$$

for each  $v \in V$ ,

(iii)

$$|\{v \in V_i | as(v) = v'\}| \le f_i$$

for each  $v' \in V'$ , and for each  $i = 1, ..., N$ .

The edges and their weights in the PU are defined by the operator assignment as follows.

(iv)

$$e' = ((as(v), a), (as(u), b)) \in E'$$

and  $w(e') = w(e)$  for each  $e = ((v, a), (u, b)) \in E$ .

Thus each edge in the source SFGs is mapped onto only one edge in the target SFG and an edge in the target SFG has only one edge in one of the SFGs mapped onto it.

#### 2.3.4 Retiming

Changing the times at which operations are executed is defined as follows.

**Definition 2.14 (retiming).** Given are an SFG  $\mathcal{G}$  and a weight w. The *retiming* is a function  $r: V \to \mathbb{Z}$  that returns for each operation in V the number of clock cycles the operation is delayed. Furthermore, retiming defines a retimed weight  $w_r: E \to \mathbb{Z}$  as follows. For each  $e = ((u, a), (v, b)) \in E$ ,  $w_r(e) = w(e) + r(v) - r(u)$ .

As a result of retiming, the synchronous and asynchronous timing behaviour of an SFG are changed. We use the index r to identify the synchronous and asynchronous delay of paths in a retimed SFG.

In addition to retiming we also need a concept of phase, which is defined as follows.

**Definition 2.15 (phase).** Given are a source SFG  $\mathcal{G}$ , a retiming r and folding factor f. The *phase* is a function  $ph: V \to \mathbb{Z}$  that returns the phase of an operation. It is defined as follows. For each  $v \in V$ ,  $ph(v) = r(v) \mod f$ .

There are three reasons to retime operations, that each correspond with a type of constraint on the retiming. The first reason is that two or more operations of the same source SFG can be executed on one operator if they are executed in different phases according to the following requirement.

(v)

$$ph(u) \neq ph(v)$$

for each  $u, v \in V$  with  $as(u) = as(v)$  and  $u \neq v$ .

Note that these constraints make Constraints (*iii*) redundant, which state that the number of operations which can be assigned to one operator cannot exceed the number of phases that are available. Initially all operations are executed in the same phase. By changing the execution time of operations we can assign every operation that is assigned to the same operator to a different phase.

, ¬ 24 Formal Model

The second reason to retime operations is that the execution times of the operations determine the placements of registers in the PU. The minimum throughput frequency at which consecutive executions of an SFG must be performed is specified by a clock period  $\tau$ . It implies that a path between two registers in the retimed PU must have an asynchronous delay less than the clock period. A path between two registers is characterized by a path weight equal to zero, so we demand that

(vi)

$$D(p') < \tau$$

for each  $p' \in P_{\mathcal{G}'}$  with  $W_r(p') = 0$ .

By changing the execution times of operations in SFGs, the weights on paths are influenced and consequently the maximum achievable clock frequency can be controlled. Whether a path is executable or not is discussed in the next section, Section 2.4.

The third reason to retime operations is that the initial weights in the SFGs may be negative. Retiming changes the weights on signal edges and must make them all positive, i.e.,

(vii)

$$w_r(e') \ge 0$$

for each  $e' \in E'$ .

Another reason to retime operations is that the register cost of a PU can be minimized by doing it. The relationship between the retiming of operations and the cost is explained in Section 2.5.

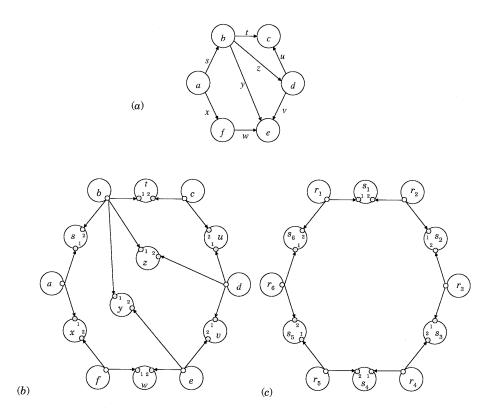

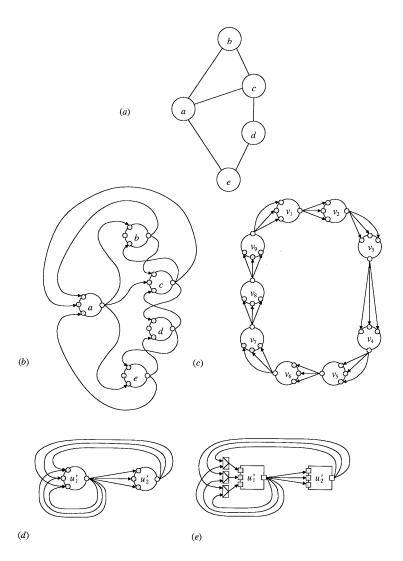

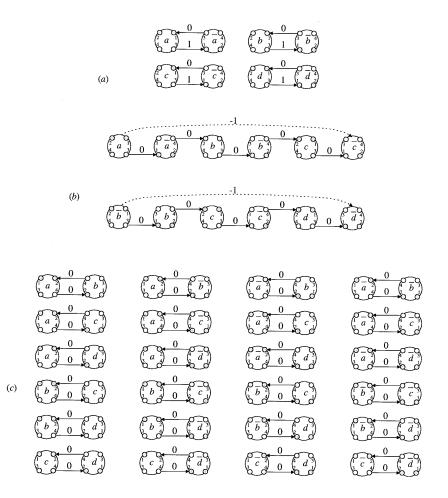

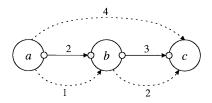

# 2.4 False paths and loops in PUs

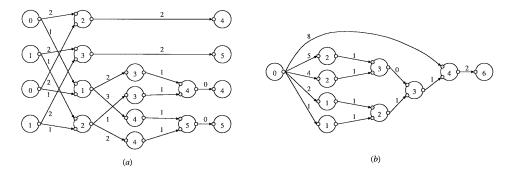

One of the constraints on the PU designed is that it cannot contain asynchronous feedback loops. These loops can be introduced by the mapping of source SFGs onto a target SFG; see Figure 2.2. However, these loops will never carry data around since the data routing will be according to one of the functions that can be executed, which is free of asynchronous feedback loops. Therefore, an asynchronous feedback loop in the target SFG is false. A false asynchronous feedback loop causes problems for timing verification, since most timing verification tools cannot handle PUs that contain false asynchronous feedback loops.

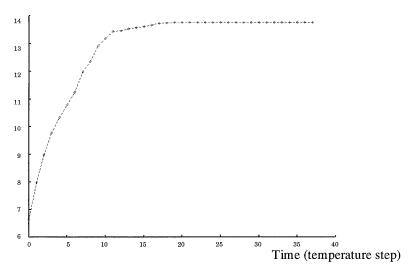

A path in a target SFG is false if not all its edges correspond to the same source SFG or if the operations of the source SFG that are assigned to the operators of the path are executed in different phases. A false path in a target SFG consists of a sequence of two or more paths, connected by operators with a defined delay, each of which corresponds to a path in one of the source SFGs. A false loop in a PU is a false path with the starting output terminal and the ending input terminal belonging to the same operator and a defined delay between these terminals. A false loop can be identified by a sequence of two or more paths in one or more source SFGs. Such a sequence is called a *complex circuit*.

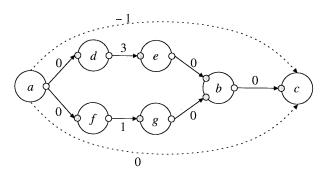

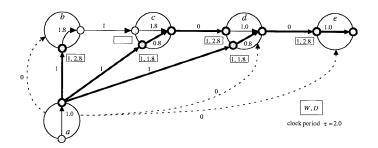

Figure 2.2. Two source SFGs, (a) and (b), and a PU, (c), that can execute one of the SFGs at a time. The PU contains a false loop, which is highlighted. The loop is false since one of the multiplexers in it is switched in such a way that the loop is broken. In (d) the selected inputs of the multiplexers are indicated corresponding with the execution of SFG (a). In (e) the selected inputs of the multiplexers are indicated corresponding with the execution of SFG (b). The paths of the SFGs that constitute a complex circuit are highlighted in (a) and (b).

**Definition 2.16 (complex circuit).** Given are a union  $\mathcal{G}$  of source SFGs  $\mathcal{G}_i = (V_i, T_i, E_i)$ , i = 1, ..., N, an operator allocation al, and an operator assignment as. A *complex circuit* is a sequence of paths  $(p_0, p_1, ..., p_{m-1})$ , with  $p_k = ((u_k, a_k) \mapsto (v_k, b_k)) \in P_{\mathcal{G}}$ , k = 0, ..., m-1, and  $m \ge 2$ , satisfying

$$as(v_k) = as(u_{(k+1) \mod m})$$

$k = 0, ..., m-1$ , and  $del((as(v_k), b_k), as(u_{(k+1) \mod m}), a_{(k+1) \mod m})) \neq \sim$   $k = 0, ..., m-1$ , and  $u \neq v$  for each  $(v, a) \in p_k$ , and  $(u, b) \in p_l$  with  $k, l = 0, ..., m-1, k \neq l$ .

We denote the set of all complex circuits in  $\mathcal G$  by  $C_{\mathcal G}$ . Furthermore, one of the paths p of a complex circuit  $c \in C_{\mathcal G}$  is considered to be an element of the complex circuit, which is denoted by  $p \in c$ .

Although a complex circuit visits an operation at most once, corresponding operators may be visited more than once because different operations may be assigned to the same operator. Note that a false loop may have more than one corresponding complex circuit.

We demand that on each complex circuit at least one register be present, i.e., (viii)  $\sum_{p \in c} W_r(p) \ge 1$  for each  $c \in C_G$ .

# 2.5 Mapping a target SFG onto a PU

The second step of the mapping of a union of source SFGs onto a PU consists of implementing the target SFG, which was designed in the first step, as a PU. In the second step the number of registers and the number of multiplexers are determined. The register allocation is defined as follows.

**Definition 2.17 (register allocation).** Given is an SFG  $\mathcal{G}$ . The *register allocation* is a function  $ra: T \to IN$  that returns for each terminal in T the number of registers allocated to the terminal.

According to the architecture of a PU, registers on different edges may be shared at operator inputs and operator outputs if edges have common terminals. The clocked delay of a signal edge must be smaller than or equal to the number of registers allocated to the terminals to which it is connected, i.e.,

(ix)

$$ra(o) + ra(i) \ge w_r(e)$$

for each  $e = (o, i) \in E$ .

An operator output can be connected to more than one operator input by a tapped delay line without the need for additional hardware; see Figure 1.11. If out of more than two sources must be selected at an operator input, a tree of two-input multiplexers is placed at the input. The number of two-input multiplexers placed at an operator input is determined by a multiplexer allocation.

**Definition 2.18 (multiplexer allocation).** Given are an SFG  $\mathcal{G}$  and a weight w. The *multiplexer allocation* is a function  $ma: I \to \mathbb{I}\mathbb{N}$  that returns for each operator input in I the number of two-input multiplexers located at the operator input, which is defined as follows. For each  $i \in I$ ,  $ma(i) = (|\{(o, w_r((o, i))) \in O \times \mathbb{I}\mathbb{N}|(o, i) \in E\}|-1)^+$ , where  $x^+ = \max\{x, 0\}$ .

The number of multiplexers can be reduced if two or more edges have identical sources and destinations and if they have the same weight. An operator assignment determines the sources and destinations. Retiming may affect the weight on an edge and, consequently, the multiplexer cost.

Having defined functions to indicate the number of operators, registers, and multiplexers, we next discuss the way they are connected. All the elements of a PU, i.e., the operators, registers, and multiplexers, are interconnected by point-to-point connections, also called wires. The number of wires is equal to the number of inputs of all the elements. Therefore we include the cost of wires by adding to each element an extra cost per input.

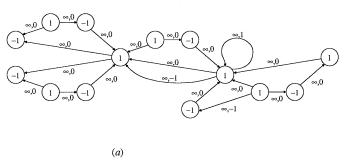

If a signal on an edge must be delayed a number of clock cycles that is smaller than the sum of the registers that are allocated to the output terminal and input terminal to which the edge is connected, more than one possibility exists to configure the multiplexers and registers. Since all the possible configurations have the same cost, we do not discuss this any further; see Figure 2.3.

Figure 2.3. Two configurations of a (part of a) PU, which have the same cost. At the output terminal four registers are allocated. At the input terminal four registers and two multiplexers are allocated. The connection indicated by a solid line between the input and output terminals corresponds with a signal edge with a weight equal to four.

Given an SFG  $\mathcal{G}$ , a type set  $\mathcal{T}$ , an operator allocation al, a register allocation ra, and a multiplexer allocation ma, the cost of the SFG is

$$\alpha \sum_{t \in T} ra(t) + \beta \sum_{i \in I} ma(i) + \sum_{j \in T} al(j) C(j),$$

where  $\alpha \in \mathbb{Q}^+$  denotes the cost of a register and  $\beta \in \mathbb{Q}^+$  the cost of a multiplexer.

The control signals to the multiplexers are defined by the mapping of source SFGs onto a PU and are not discussed any further.

# 2.6 Processing unit design problem

The central problem of this thesis is formulated as follows.

**Definition 2.19** (**processing unit design problem (PUDP)**). Given are a union  $\mathcal{G}$  of source SFGs  $\mathcal{G}_i$  with folding factors  $f_i$ ,  $i=1,\ldots,N$ , a type set  $\mathcal{T}$ , a type function  $\ell$ , timing functions dat, drt, del, and w, a clock period  $\tau$ , the cost of a register  $\alpha$ , and the cost of a multiplexer  $\beta$ . The problem is to find a PU  $\mathcal{G}'$  constructed by an operator allocation al, an operator assignment as, a retiming r, a register allocation ra, and a multiplexer allocation ma, for which

| ra, and a multiplexel anocation ma, for which                                                 |                                             |

|-----------------------------------------------------------------------------------------------|---------------------------------------------|

| (i) $al(j) \ge \max_{i=1,\dots,N} \lceil \frac{ V_{i,j} }{f_i} \rceil$                        | for each $j \in \mathcal{T}$ , and          |

| $(ii) \ \ell(v) = \ell(as(v))$                                                                | for each $v \in V$ , and                    |

| $(iii)  \{v \in V_i   as(v) = v'\}  \le f_i$                                                  | for each $v' \in V'$ , and                  |

|                                                                                               | for each $i = 1,, N$ , and                  |

| $(iv) \ e' = ((as(v), a)(as(u), b)) \in E'$ and                                               |                                             |

| $w_r(e') = w_r(e)$                                                                            | for each $e = ((v, a), (u, b)) \in E$ , and |

| $(v) ph(u) \neq ph(v)$                                                                        | for each $u, v \in V_i$ with                |

|                                                                                               | as(u) = as(v), and                          |

|                                                                                               | $u \neq v$ , and                            |

|                                                                                               | for each $i = 1,, N$ , and                  |

| $(vi) \ D(p') < \tau$                                                                         | for each $p' \in P_{\mathcal{G}'}$ with     |

|                                                                                               | $W_r(p')=0$ , and                           |

| $(vii) \ w_r(e') \ge 0$                                                                       | for each $e' \in E'$ , and                  |

| $(viii) \sum_{p \in c} W_r(p) \ge 1$                                                          | for each $c \in C_{\mathcal{G}}$ , and      |

| $(ix) ra(o') + ra(i') \ge w_r(e')$                                                            | for each $e' = (o', i') \in E'$ , and       |

| that minimizes                                                                                |                                             |

| $\alpha \sum_{t' \in T'} ra(t') + \beta \sum_{i' \in I'} ma(i') + \sum_{j \in T'} al(j) C(j)$ |                                             |

|                                                                                               |                                             |

# 2.7 Special cases of PUDP

In the introduction of this thesis we informally introduced PUDP as a generalization of the multiplexing, timefolding, and retiming problems. Here, we formally define these problems as special cases of PUDP. A special case of PUDP is defined by additional constraints that must hold for instances of PUDP.