# CCD imaging : concepts for low noise and high bandwidth

# Citation for published version (APA):

Centen, P. G. M. (1999). *CCD imaging : concepts for low noise and high bandwidth*. [Phd Thesis 2 (Research NOT TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR520658

DOI: 10.6100/IR520658

#### Document status and date:

Published: 01/01/1999

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# **CCD** Imaging

# Concepts for Low Noise and High Bandwidth

#### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr. M. Rem, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op maandag 29 maart 1999 om 16.00

door

# Petrus Gijsbertus Maria

Centen

geboren te Goirle

Dit proefschrift is goedgekeurd door de promotoren:

## prof.dr. F.M. Klaassen

en

# prof.dr. T.G.M Kleinpenning

Copromotor:

dr.ir. A.J.P Theuwissen

The work described in this thesis has been carried out at the Philips Research Laboratories in Eindhoven and Philips Digital Video Systems (Breda) B.V., The Netherlands.

Aan mijn vrouw Peti Aan mijn ouders Bertus en Lies

## CIP-DATA LIBRARY TECHNISCHE UNIVERSITEIT EINDHOVEN

Centen, Petrus G.M.

CCD Imaging : concepts for low noise and high bandwidth / by Petrus G.M.Centen. - Eindhoven : Technische Universiteit Eindhoven, 1999. Proefschrift. - ISBN 90-386-1570-1 NUGI 832 Trefw.: optische sensoren / optimale filters / elektronische beeldtechniek / beeldopname techniek / fotohalfgeleiders. Subject headings: CCD image sensors / semiconductor device noise / matched filters / optoelectronic devices / video signal processing.

Druk: Universiteitsdrukkerij, Technische Universiteit Eindhoven Coverdesign by Ben Mobach

Copyright (C) by P.G.M. Centen

All rights reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

# TABLE OF CONTENTS

| 1.2 CMOS imagers       10         1.3 Noise quantities in CCD imaging       11         1.4 Scope of this thesis       12         References       16         Chapter 2         ON-CHIP AMPLIFIER: Amplification and conversion         2.1 Introduction       19         2.2 Analysis of the first stage: a source follower       22         2.2.1 Small signal equivalent circuit.       22         2.2.2 Charge packet response: rise and fall time.       23         2.2.3 Bandwidth and $\Theta_n$ .       26         2.2.4 Noise in the Reset FET on- and off-state.       26         2.3 Procedure to determine $C_{tot}$ and $\Theta_n$ .       26         2.4 Equivalent Noise Electron Density (NED)       31         2.4.1 Equivalent noise electrons versus NED       31 | Chap | ter 1 |                                                     |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----------------------------------------------------|--|--|--|--|--|--|--|--|

| 1.2 CMOS imagers       10         1.3 Noise quantities in CCD imaging       11         1.4 Scope of this thesis       12         References       16         Chapter 2         ON-CHIP AMPLIFIER: Amplification and conversion         2.1 Introduction       19         2.2 Analysis of the first stage: a source follower       22         2.2.1 Small signal equivalent circuit       22         2.2.2 Charge packet response: rise and fall time.       23         2.2.3 Bandwidth and $\Theta_n$ .       26         2.2.4 Noise in the Reset FET on- and off-state.       26         2.3 Procedure to determine $C_{tot}$ and $\Theta_n$ .       26         2.4 Equivalent Noise Electron Density (NED)       31         2.4.1 Equivalent noise electrons versus NED       31  |      | -     |                                                     |  |  |  |  |  |  |  |  |

| 1.2 CMOS imagers       10         1.3 Noise quantities in CCD imaging       11         1.4 Scope of this thesis       12         References       16         Chapter 2         ON-CHIP AMPLIFIER: Amplification and conversion         2.1 Introduction       19         2.2 Analysis of the first stage: a source follower       22         2.2.1 Small signal equivalent circuit.       22         2.2.2 Charge packet response: rise and fall time.       23         2.2.3 Bandwidth and $\Theta_n$ .       26         2.2.4 Noise in the Reset FET on- and off-state.       26         2.3 Procedure to determine $C_{tot}$ and $\Theta_n$ .       26         2.4 Equivalent Noise Electron Density (NED)       31         2.4.1 Equivalent noise electrons versus NED       31 |      | 1.1   | CCD imagers                                         |  |  |  |  |  |  |  |  |

| 1.3 Noise quantities in CCD imaging       11         1.4 Scope of this thesis       12         References       16         Chapter 2         ON-CHIP AMPLIFIER: Amplification and conversion         2.1 Introduction       19         2.2 Analysis of the first stage: a source follower       22         2.2.1 Small signal equivalent circuit.       22         2.2.2 Charge packet response: rise and fall time.       22         2.2.3 Bandwidth and $\Theta_n$ .       26         2.2.4 Noise in the Reset FET on- and off-state.       27         2.3 Procedure to determine $C_{tot}$ and $\Theta_n$ .       28         2.4 Equivalent Noise Electron Density (NED)       31         2.4.1 Equivalent noise electrons versus NED       31                                   |      |       |                                                     |  |  |  |  |  |  |  |  |

| 1.4 Scope of this thesis       12         References       16         Chapter 2         ON-CHIP AMPLIFIER: Amplification and conversion         2.1 Introduction       19         2.2 Analysis of the first stage: a source follower       22         2.2.1 Small signal equivalent circuit.       22         2.2.2 Charge packet response: rise and fall time.       22         2.2.3 Bandwidth and $\Theta_n$ .       26         2.2.4 Noise in the Reset FET on- and off-state.       27         2.3 Procedure to determine $C_{tot}$ and $\Theta_n$ .       28         2.4 Equivalent Noise Electron Density (NED)       31         2.4.1 Equivalent noise electrons versus NED       31                                                                                        |      |       |                                                     |  |  |  |  |  |  |  |  |

| Chapter 2       ON-CHIP AMPLIFIER: Amplification and conversion       19         2.1 Introduction       19         2.2 Analysis of the first stage: a source follower       22         2.2.1 Small signal equivalent circuit.       22         2.2.2 Charge packet response: rise and fall time.       23         2.2.3 Bandwidth and $\Theta_n$ .       26         2.2.4 Noise in the Reset FET on- and off-state.       26         2.3 Procedure to determine $C_{tot}$ and $\Theta_n$ .       26         2.4 Equivalent Noise Electron Density (NED)       31         2.4.1 Equivalent noise electrons versus NED       31                                                                                                                                                       |      |       |                                                     |  |  |  |  |  |  |  |  |

| ON-CHIP AMPLIFIER: Amplification and conversion192.1 Introduction192.2 Analysis of the first stage: a source follower222.2.1 Small signal equivalent circuit.222.2.2 Charge packet response: rise and fall time.222.2.3 Bandwidth and $\Theta_n$ .262.2.4 Noise in the Reset FET on- and off-state.262.3 Procedure to determine $C_{tot}$ and $\Theta_n$ .262.4 Equivalent Noise Electron Density (NED)312.4.1 Equivalent noise electrons versus NED31                                                                                                                                                                                                                                                                                                                              |      | Refe  | rences                                              |  |  |  |  |  |  |  |  |

| 2.1Introduction192.2Analysis of the first stage: a source follower222.2.1Small signal equivalent circuit.222.2.2Charge packet response: rise and fall time.232.2.3Bandwidth and $\Theta_n$ .262.2.4Noise in the Reset FET on- and off-state.262.3Procedure to determine $C_{tot}$ and $\Theta_n$ .282.4Equivalent Noise Electron Density (NED)312.4.1Equivalent noise electrons versus NED31                                                                                                                                                                                                                                                                                                                                                                                        | Chap | ter 2 |                                                     |  |  |  |  |  |  |  |  |

| 2.1Introduction192.2Analysis of the first stage: a source follower222.2.1Small signal equivalent circuit.222.2.2Charge packet response: rise and fall time.232.2.3Bandwidth and $\Theta_n$ .262.2.4Noise in the Reset FET on- and off-state.272.3Procedure to determine $C_{tot}$ and $\Theta_n$ .282.4Equivalent Noise Electron Density (NED)312.4.1Equivalent noise electrons versus NED31                                                                                                                                                                                                                                                                                                                                                                                        | -    | •     |                                                     |  |  |  |  |  |  |  |  |

| 2.2.1Small signal equivalent circuit.222.2.2Charge packet response: rise and fall time.222.2.3Bandwidth and $\Theta_n$ .262.2.4Noise in the Reset FET on- and off-state.272.3Procedure to determine $C_{tot}$ and $\Theta_n$ .282.4Equivalent Noise Electron Density (NED)312.4.1Equivalent noise electrons versus NED31                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |       | -                                                   |  |  |  |  |  |  |  |  |

| 2.2.2Charge packet response: rise and fall time.222.2.3Bandwidth and $\Theta_n$ .262.2.4Noise in the Reset FET on- and off-state.272.3Procedure to determine $C_{tot}$ and $\Theta_n$ .282.4Equivalent Noise Electron Density (NED)312.4.1Equivalent noise electrons versus NED31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | 2.2   | Analysis of the first stage: a source follower      |  |  |  |  |  |  |  |  |

| 2.2.2Charge packet response: rise and fall time.232.2.3Bandwidth and $\Theta_n$ .262.2.4Noise in the Reset FET on- and off-state.272.3Procedure to determine $C_{tot}$ and $\Theta_n$ .282.4Equivalent Noise Electron Density (NED)312.4.1Equivalent noise electrons versus NED31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |       | 2.2.1 Small signal equivalent circuit               |  |  |  |  |  |  |  |  |

| 2.2.3Bandwidth and $\Theta_n$ .262.2.4Noise in the Reset FET on- and off-state.272.3Procedure to determine $C_{tot}$ and $\Theta_n$ .282.4Equivalent Noise Electron Density (NED)312.4.1Equivalent noise electrons versus NED31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |       |                                                     |  |  |  |  |  |  |  |  |

| 2.2.4Noise in the Reset FET on- and off-state.272.3Procedure to determine $C_{tot}$ and $\Theta_n$ .282.4Equivalent Noise Electron Density (NED)312.4.1Equivalent noise electrons versus NED31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |       |                                                     |  |  |  |  |  |  |  |  |

| 2.4 Equivalent Noise Electron Density (NED)       31         2.4.1 Equivalent noise electrons versus NED       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |       |                                                     |  |  |  |  |  |  |  |  |

| 2.4 Equivalent Noise Electron Density (NED)       31         2.4.1 Equivalent noise electrons versus NED       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | 2.3   | Procedure to determine $C_{tot}$ and $\Theta_{tot}$ |  |  |  |  |  |  |  |  |

| 2.4.1 Equivalent noise electrons versus NED 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |       |                                                     |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |       |                                                     |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |       |                                                     |  |  |  |  |  |  |  |  |

|      | 2.5    | Noise optimization                                              |   |  |  |  |  |  |

|------|--------|-----------------------------------------------------------------|---|--|--|--|--|--|

|      |        | 2.5.1 Equivalent Noise Electron Density for the case of         |   |  |  |  |  |  |

|      |        | thermal noise                                                   | 7 |  |  |  |  |  |

|      |        | 2.5.2 Total capacitance $C_{tot}$                               |   |  |  |  |  |  |

|      |        | 2.5.3 Minimum NED 39                                            |   |  |  |  |  |  |

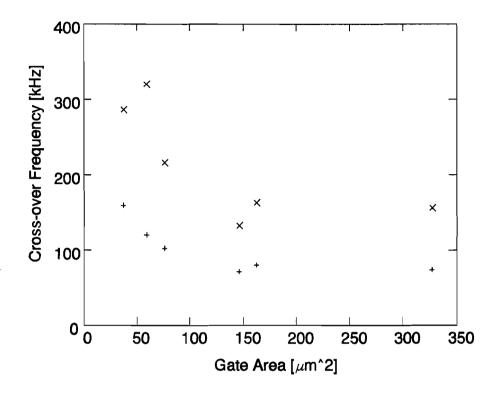

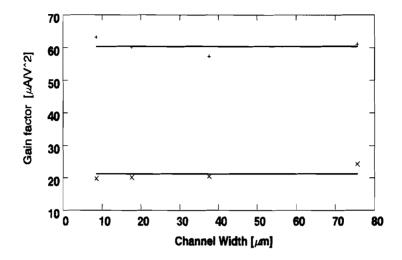

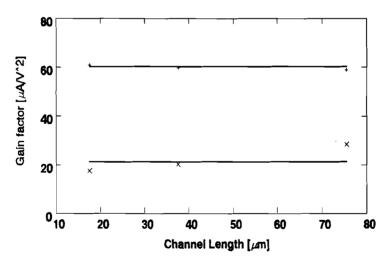

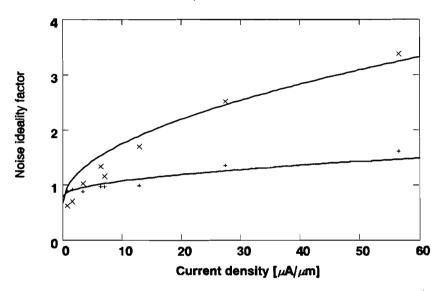

|      | 2.6    | Experimental results 42                                         |   |  |  |  |  |  |

|      |        | 2.6.1 Total capacitance of the detection node 44                | - |  |  |  |  |  |

|      |        | 2.6.2 The 3dB bandwidth and $\Theta_n$ 44                       |   |  |  |  |  |  |

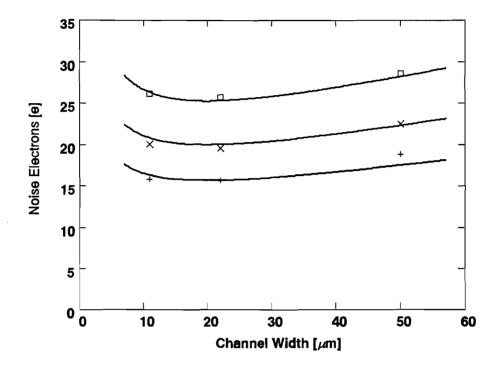

|      |        | 2.6.3 Optimum value of the channel width 4                      |   |  |  |  |  |  |

|      | 2.7    | Application of the model 50                                     |   |  |  |  |  |  |

|      |        | 2.7.1 Improvement of the FT5 on-chip amplifier                  |   |  |  |  |  |  |

|      |        | 2.7.2 The FT8 HDTV imager on-chip amplifier 52                  |   |  |  |  |  |  |

|      |        | Conclusions 5                                                   |   |  |  |  |  |  |

|      |        | endix A: Transfer function 50                                   |   |  |  |  |  |  |

|      |        | endix B: Procedure to determine $C_1$ and $C_2$                 |   |  |  |  |  |  |

|      | Refe   | erences                                                         | 9 |  |  |  |  |  |

|      |        |                                                                 |   |  |  |  |  |  |

| Chap |        |                                                                 | - |  |  |  |  |  |

|      |        | SING TRANSISTORS: Surface or buried channel type 6              |   |  |  |  |  |  |

|      | 3.1    | Introduction                                                    |   |  |  |  |  |  |

|      |        | 1/f noise                                                       |   |  |  |  |  |  |

|      | 3.3    | Thermal noise                                                   |   |  |  |  |  |  |

|      | 3.4    | Equivalent Noise Electron Density                               |   |  |  |  |  |  |

|      |        | Bandwidth                                                       |   |  |  |  |  |  |

|      |        | Conclusions                                                     |   |  |  |  |  |  |

|      |        | endix A: Determination of the transconductances                 |   |  |  |  |  |  |

|      | Rele   | erences                                                         | 9 |  |  |  |  |  |

| Chap | oter 4 | 1                                                               |   |  |  |  |  |  |

| Curr |        | D SIGNAL FILTERING: A figure of merit 8                         | 1 |  |  |  |  |  |

|      |        | Introduction                                                    |   |  |  |  |  |  |

|      |        | The CCD output signal decomposed                                |   |  |  |  |  |  |

|      |        | 4.2.1 Reset noise                                               | 6 |  |  |  |  |  |

|      |        | 4.2.2 The charge signal                                         |   |  |  |  |  |  |

|      |        | 4.2.3 Readout noise                                             |   |  |  |  |  |  |

|      | 4.3    | The optimal filter problem                                      |   |  |  |  |  |  |

|      |        | 4.3.1 Posing the variational problem                            |   |  |  |  |  |  |

|      |        | 4.3.2 The optimal filter in the presence of white noise only. 9 | 2 |  |  |  |  |  |

|      |        | 4.3.3 Two limiting cases 10                                     | 0 |  |  |  |  |  |

|      |        | 4.3.4 1/f noise and the optimal white noise filter 10           | 3 |  |  |  |  |  |

|      |        |                                                                 |   |  |  |  |  |  |

# Table of contents

|      |             | 4.3.5     | Discussion of the figure of merit for the white noise   |      |

|------|-------------|-----------|---------------------------------------------------------|------|

|      |             |           |                                                         | 105  |

|      |             | 4.3.6     | Multiple outputs and the figure of merit.               | 106  |

|      |             | 4.3.7     |                                                         | 107  |

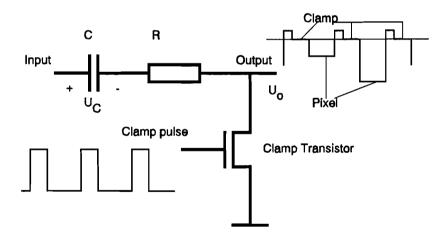

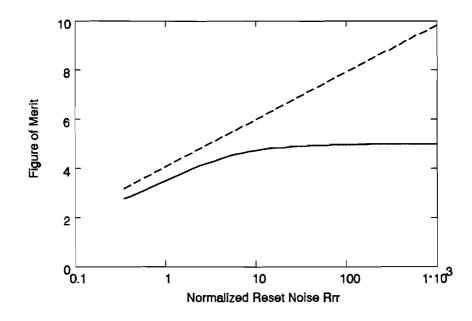

|      | 4.4         | A genera  |                                                         | 114  |

|      |             |           | 116                                                     |      |

|      |             | 4.5.1     |                                                         | 116  |

|      |             | 4.5.2     |                                                         | 117  |

|      |             | 4.5.3     | The reset noise residue                                 | 118  |

|      |             | 4.5.4     |                                                         | 119  |

|      |             | 4.5.5     | Determination of the clamp time constant.               | 120  |

|      |             | 4.5.6     | Experimental data of the soft clamp.                    | 124  |

|      | 4.6         | The pass  | sive integrator                                         | 125  |

|      |             | 4.6.1     | Transfer function of the passive integrator circuit     | 125  |

|      |             | 4.6.2     | The noise bandwidth of the passive integrator circuit   | 127  |

|      |             | 4.6.3     | Optimizing the passive integrator circuit               | 129  |

|      |             | 4.6.4     | Inter-Symbol Interference (ISI)                         | 130  |

|      |             | 4.6.5     | Conclusion                                              | 132  |

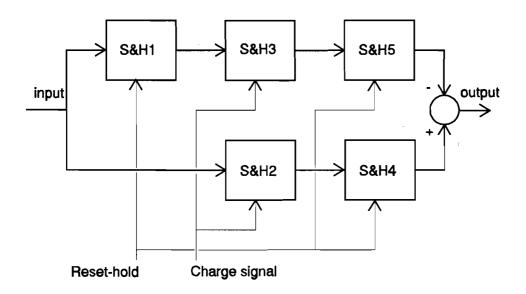

|      | 4.7         | Correlate | ed Double Sampler (CDS)                                 | 133  |

|      |             |           | ion                                                     | 135  |

|      |             |           | The noise spectral density after sampling               | 136  |

|      |             |           | The noise bandwidth of an integrator.                   | 139  |

|      |             |           | Some auxiliary functions.                               | 140  |

|      |             |           | Step response of the LCR-circuit.                       | 144  |

|      |             |           | • • • • • • • • • • • • • • • • • • • •                 | 147  |

|      |             |           |                                                         |      |

| Char | oter !      | 5         |                                                         |      |

| -    | <b>RE</b> A | ADOUT     | MODES: Reset noise-free readout mode for a floa         | ting |

|      |             | usion det |                                                         | 151  |

|      | 5.1         | Introduc  | tion                                                    | 151  |

|      |             |           | of the classical floating diffusion detector with reset | 153  |

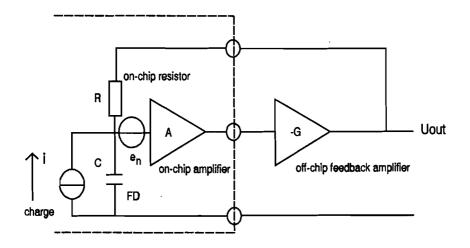

|      |             |           | tive charge readout using resistive feedback            | 159  |

|      |             |           | ison of both methods                                    | 165  |

|      |             | •         | f 1/f noise                                             | 169  |

|      | 5.6         | Numeric   | cal examples                                            | 170  |

|      | 5.7         |           | nental results                                          | 172  |

|      | 5.8         |           | on and conclusions                                      | 177  |

|      |             |           | Procedure to determine the transfer function            | 178  |

|      |             |           |                                                         | 180  |

| List of symbols      | 13 |

|----------------------|----|

| Summary 19           | 13 |

| Samenvatting         | 17 |

| Dankwoord            | )1 |

| Biography            | 13 |

| List of publications | )5 |

· \_\_\_\_\_

# **Chapter 1**

# INTRODUCTION

The first section of this introductory chapter provides some background on Charge Coupled Device imagers (CCDs). It starts by explaining the way a twodimensional imager is built, showing the on-chip amplifier and signal processor as part of the imaging signal chain. Next a CMOS imager is introduced. Then some quantities used in calculating the noise performance are discussed. Finally, a presentation of the scope of this thesis is given.

## 1.1 CCD imagers

A broadcast colour camera usually contains three CCD imagers. These CCDs are glued on a colour splitter, or prism, to obtain the optical red, green and blue signals (primary colours). The CCD converts the optical signal into an electrical signal, one for each colour channel. This electrical signal is further processed in a signal processor to obtain what is known as base band video. The CCDs used are of the two-dimensional type. Of the latter three architectures are used commercially: Interline Transfer (IT), Frame Interline Transfer (FIT) and Frame Transfer (FT). A lengthy discussion of these imager types has been given by Theuwissen [1].

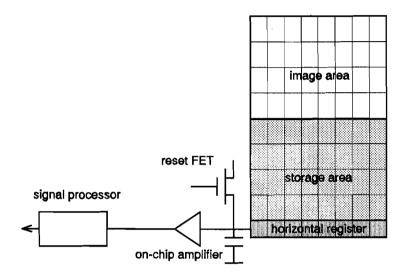

A two-dimensional FT imager or FIT imager consists of an image area, a

storage area, a horizontal register, and an on-chip amplifier (see Figure 1.1). In the image area a two-dimensional charge image is generated by a light pattern projected onto the array. In a PAL video camera it takes about 20 ms to generate the charge image. The whole charge image is transported quickly (typically some 100  $\mu$ s) to the storage area. The storage area is covered with a light shield to prevent false images being generated. After the fast vertical transport the image area is cleared and a new charge image is generated. The charge image, now present in the storage area, is shifted relatively slowly into a horizontal register one row at a time. This row is also called a TV line. A row is shifted from the storage area into the horizontal register in parallel and shifted serially towards the detection node with its on-chip amplifier. Transporting a row through the horizontal register takes about 64  $\mu$ s. The clock frequency for driving the horizontal register has increased over the years from about 4 MHz, Collet [2], to 54 MHz, Moelands et al. [3].

The charge image consists of individual charge packets, which are usually formed by electrons but sometimes by holes, Roks [4]. The number of image cells or charge packets in one charge image (frame) can be as low as  $3 \cdot 10^5$ , or as high as  $63.10^6$ , Kreider [5]. A charge packet arriving at the end of the horizontal register is dumped on a floating diffusion region, symbolized by a capacitor. This capacitor, together with the parasitic capacitances of the on-chip amplifier input, converts the charge packet into a voltage change. The on-chip amplifier buffers the voltage change and drives a signal processor. The latter processes the on-chip amplifier output signal to obtain base band video.

The floating diffusion region together with the input of the on-chip amplifier is called the detection node.

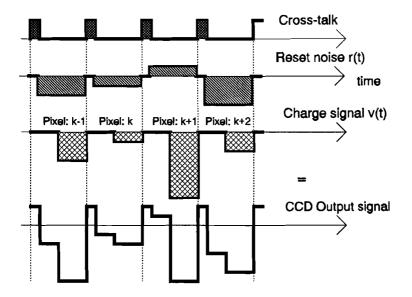

After the charge packet has been converted into a voltage pulse the reset FET clamps the detection node to a reference voltage. During the clamp action the charge is drained off and the detection node is prepared for the conversion of the next charge packet. During clamping the reset FET channel is conducting and together with the detection node capacitance forms a first order low pass filter for the thermal noise of the conducting reset FET channel. At the end of the clamping interval the reset FET is switched off and the momentary value of the noise voltage is sampled on the detection node capacitance. This is called reset noise, Carnes and Kosonocky [6].

Whether one focuses on IT, FIT, FT or CMOS imagers, all have in common that a charge packet is generated in an image cell which is converted into a voltage pulse on a detection node which is followed by an on-chip amplifier and a signal processor. Generally, the noise sources in the signal chain of Figure 1.1

# Introduction

are:

- photon generated shot noise in the image cell,

- shot noise arising from dark current in the image and storage cells (significant at high temperatures),

- reset noise generated when the reset FET is switched off,

- thermal noise and 1/f noise caused by the on-chip amplifier,

- the filtering effect of the signal processor.

Figure 1.1: An imager signal chain.

A broadcast colour camera generates 50 images per second in the PAL system and about 60 images per second in the NTSC system. The number of TV lines, cells in vertical direction, determined or image the is bv the imaging/transmission standard. For PAL this amounts to 575 image cells vertically in one frame and for NTSC 485. These standards are generally known as SDTV or standard television. In addition to SDTV there also exists HDTV, high definition television. The number of vertical image cells (TV lines) that make up one frame varies between 720, 960, 1035, 1080 and 1152. The number of image cells per TV line, or pixels per line, varies between 740 and 1440 for SDTV and between 1280 and 1920 for HDTV, Theuwissen et al. [7], Blankevoort [8] et al., Spitzer et al. [9].

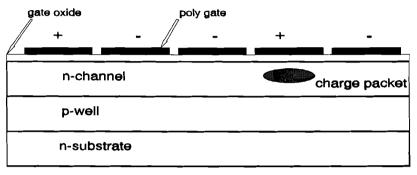

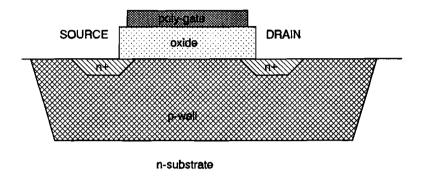

In Figure 1.2 a cross section of a CCD is given showing the transport of an electron charge packet. The voltages applied to the polysilicon gates are changed in such a way that the electron charge packet moves in a peristaltic way from right to left.

Figure 1.2: Cross section of a CCD, showing the transport of electron charge packets. The charge packet is transported from right to left.

# Introduction

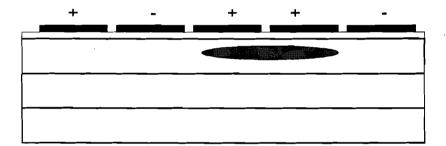

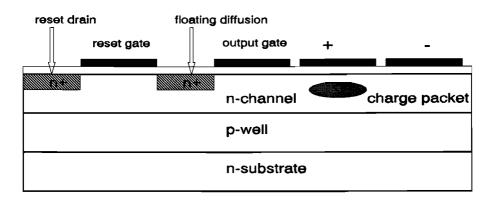

After the charge packet has been transported through the CCD register it will be dumped on the floating diffusion region (see Figure 1.3) where the charge is stored for about half a clock period. After that time the reset gate is positively biased to clamp the floating diffusion region to the drain potential. The floating diffusion region is connected to the input of an on-chip amplifier. An architecture where the floating diffusion region is the base of a pnp bipolar has been discussed by Roks et al. [10].

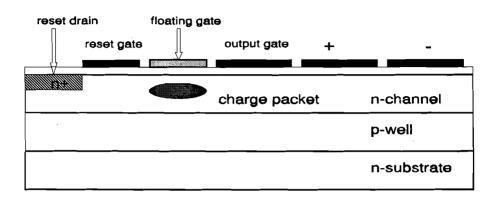

An alternative way to extract the charge packets from the CCD register makes use of a floating gate structure.

Figure 1.3: The charge packet prior to being dumped at the floating diffusion region.

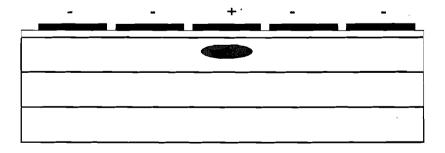

Figure 1.4 shows a floating gate structure where the charge packet is underneath, ready to be sensed by the on-chip amplifier.

The main difference between Figure 1.3 and Figure 1.4 is the lack of reset noise in the latter structure, Carnes and Kosonocky [6].

Figure 1.4: Cross section of a floating gate structure with the electron charge packet underneath a floating gate.

Several other architectures which are of the floating gate type have been reported: Brewer [11], Mutoh et al. [12], Matsunaga [13], and Roks et al. [14]-[15]

# 1.2 CMOS imagers

In contrast to CCD imagers described above the charge packets in a full CMOS imager (Wong [16], Fossum [17]) are not transported in a peristaltic CCD manner. In the image cell the electrons are collected in the same way as with CCDs. However, the charge of an image cell is transported through a wire as a current. Each image cell has an addressable output which is wired to a column amplifier. A common type of CMOS imager is one which has an amplifier in each image cell. This is known as active pixel readout, and every column has an integrating amplifier. During the horizontal retrace interval a row is read into the column amplifiers. A row (TV line) is read out by multiplexing the output of the column amplifiers one after another. In contrast to CCDs there is ample time for noise reduction due to the relatively long horizontal retrace interval (some µs), compared to a clock period of 55 ns. This is possible due to the huge amount of amplifiers, one for each column.

Presently no CMOS imagers are used in the professional broadcast video cameras. The reason for this is the high gain differences between pixels, column

#### Introduction

effects, and fixed pattern noise. Even though the CMOS imager can be produced more cheaply than a CCD imager and can have processing power on-chip, it does not reach the CCDs performance. Also the ever-decreasing dimensions of the CMOS process degrades optical performance, characterised by collection depth, and causes increased gain differences between pixels. A thorough discussion about the down scaling of CMOS processes and its effects on the CMOS imager has been given by Wong [16]. The CMOS imager will be an ideal vehicle for the low-end high-volume consumer market.

# 1.3 Noise quantities in CCD imaging

In the field of CCD imaging it is customary to convert a noise voltage in terms of an equivalent number of electrons, Carnes and Kosonocky [6], Barbe [18]. The reason for this is that almost all the important performance parameters of a CCD imager are related to the number of electrons a charge packet contains. Sometimes those numbers are countable electrons and sometimes they are an arithmetic number and should be called an equivalent number of electrons. The conversion of a noise voltage into a number of electrons is done by making use of the sensitivity S. The sensitivity is the change in output voltage of the on-chip amplifier  $\Delta V_{out}$  due to one electron being present at the detection node and is expressed as V/e.

$$\Delta V_{out} = A \ \Delta V_{in} = A \ \frac{\Delta Q}{C} = \frac{A}{C} \ q \ \Delta N = S \ \Delta N$$

In the above A is the amplifier gain,  $\Delta Q$  the amount of charge one charge packet contains, C the detection node capacitance and  $\Delta N$  the number of electrons one charge packet contains.

Assuming a noise voltage of 250  $\mu$ V and a sensitivity of S=10  $\mu$ V/e then the noise is equivalent to 25 electrons, abbreviated as 25 e. Strictly speaking this is not within the normal system for units but it is common practice in the field of CCD imaging for over 20 years now. Expressing the noise in 'electrons' is only meaningful after signal processing.

Elaborating on the above equation one can distinguish three quantities of fluctuations:

$S_V$  [V<sup>2</sup>/Hz] as the voltage noise spectral density of fluctuations  $\Delta V_{out}$

$S_N$  [e<sup>2</sup>/Hz] as the noise spectral density of fluctuations  $\Delta N$

$S_Q$  [C<sup>2</sup>/Hz] as the noise spectral density of fluctuations  $\Delta Q$ .

$$S_V = S^2 S_N = \left(\frac{S}{q}\right)^2 S_Q$$

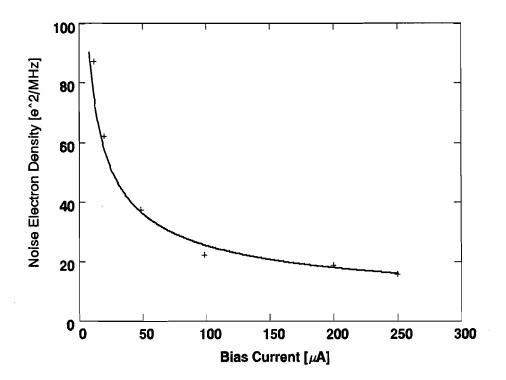

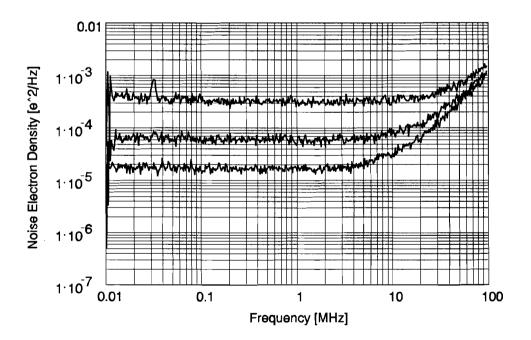

In general the noise voltage is expressed as  $V/\sqrt{Hz}$  and the voltage noise spectral density as  $V^2/Hz$ . The above units can also be converted with the use of the sensitivity S. Now the noise "number of electrons" becomes  $e/\sqrt{Hz}$  and the noise spectral density as  $e^2/Hz$ , Centen [19]. The latter will be used extensively throughout this thesis as the Noise Electron Density (NED).

$$NED = S_N$$

Another quantity that one can encounter is the ENC, which stands for: Equivalent Noise Charge, Sansen and Chang [20], Fasoli and Sampietro [21]. It is the noise spectral density of the fluctuations  $\Delta Q$  integrated over the whole bandwidth and expressed in 'Coulomb',

$$ENC = \int_{0}^{\infty} S_{Q}(f) df$$

or 'electrons',

$$ENC = \int_{0}^{\infty} S_{N}(f) df$$

as such it is a full bandwidth parameter. In the above the filtering which is usually applied to the imager output signal is not taken into account.

One also encounters the Noise Equivalent Signal or NES, White et al. [22], with dimensions  $J/m^2$ . This too is a full bandwidth expression for the noise.

# **1.4** Scope of this thesis

Since the work described in this thesis covers a relatively long period of time and therefore is interwoven with others results, we first discuss our work in relation to that of others. This is followed by a summary of the various chapters.

## Introduction

Noise and noise optimization have always been an important issue in CCD Imaging [6], [11]-[15], [18]-[28] and even recently, Fasoli and Sampietro [21], Centen and Roks [24]. From this work it has become clear that in practical imagers the noise performance of a camera is mainly determined by the on-chip amplifier and the signal processor. The focus in this thesis is on the on-chip amplifier and signal processor. Regarding the latter it does not matter whether one focuses on IT, FIT, FT or CMOS imagers.

In [11]-[15], different types of detection nodes have been presented and the noise performance has been determined experimentally. The newer detection node types show a better noise performance. But no experiment or model has been offered to show that after optimization the newer types still have a better performance. It is the aim of Chapter 2 through to Chapter 4 to give a systematic approach for optimizing the noise of the imaging chain. The method is based on the Noise Electron Density and the use of a figure of merit for the signal processor. It will be investigated whether the method can be applied to any type of capacitive detection node. In [19]-[22], [24] and [26]-[28] noise optimization models can also be found. In addition to these papers in Chapter 2 the weakness of that the noise optimum, which determines the dimensions of the detection node transistor, is investigated with respect to noise performance.

In addition to the models presented in the latter papers the validity of the noise optimization model for any type of on-chip amplifier topology (with capacitive detection node), such as source follower and common source configurations is studied in Chapter 2.

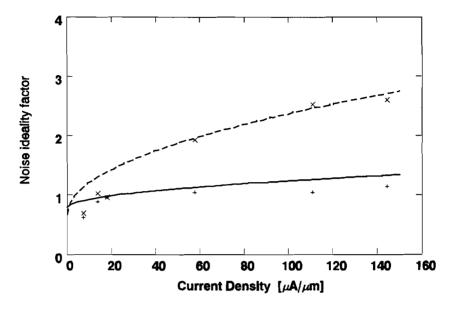

Another extension to the above papers is the inclusion of the noise ideality factor of the MOS transistor in the on-chip amplifier. This factor is 2/3 for an ideal MOS transistor. In Chapter 3 the effect of using a non ideal MOS transistor, surface and buried channel, in the on-chip amplifier is studied.

In [6,12,13,18,25,26] the on-chip amplifier noise voltage has been calculated by integrating the noise spectral density over the on-chip amplifier bandwidth to determine the performance. Following the latter papers, a low noise level and a huge bandwidth can produce a poorer noise performance than a high noise level in a small bandwidth. Yet, in a well designed imaging chain, the one with the low noise level will always be the better of the two.

The dimensions of the MOS transistor in the first stage of the on-chip amplifier determine both the bandwidth of the amplifier and its noise. Of course one can minimize the mean squared noise voltage over the bandwidth of the on-chip amplifier. But in this case, as explained above, the wrong parameters have been optimized and a sub-optimum result occurs.

Finally, in Chapter 3, the use of surface and buried channel transistors in the

detection node is studied for its effects on sensitivity, bandwidth and noise.

Considering the signal processor as a matched filter, it is shown in Chapter 4 that the noise performance of a well designed imaging chain is given by the product of the noise spectral density of the on-chip amplifier, the noise figure of the signal processor, and the clock frequency. Generally the noise bandwidth determining the noise voltage should be determined by the signal processor rather than by the on-chip amplifier.

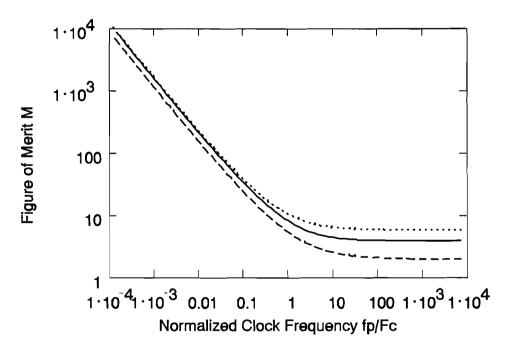

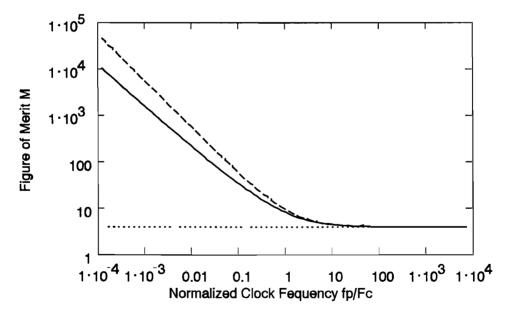

Although the performance of CCD signal processors has been studied extensively in [22], [23], [25] and [29]-[38], no one has derived a figure of merit as given in Chapter 4. This figure of merit has the powerful property that it has a theoretical lower bound. This figure of merit can be applied to any type of CCD signal processing irrespective of the CCD imager and type of detection node used, including CMOS imagers. In many cases this figure of merit is only determined by two ratios one between the pixel period time and the duration of the reset hold level and one between the pixel period time and the duration of the video in one pixel.

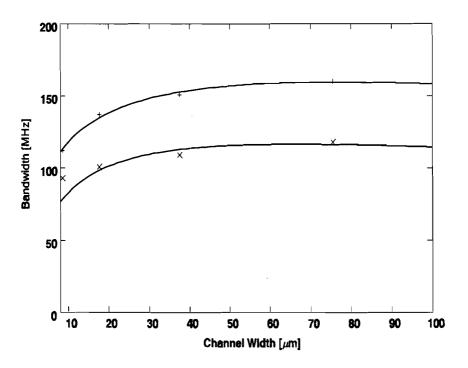

The bandwidth of the on-chip amplifier influences the shape of the output signal, determines the interference between pixels, and the ability to suppress the reset noise in the signal processor. For satisfactory operation of the imaging chain the bandwidth must be at least 3 times the clock frequency used to drive the horizontal register [23]. Above this value the noise behaviour of a well designed imaging chain does not change any more and its noise performance becomes independent of the bandwidth of the on-chip amplifier. On-chip amplifier bandwidth has become more and more important, in particular for HDTV, Theuwissen et al. [7], and high speed camera applications, Moelands et al. [3]. In the early days of CCD imaging the clock frequency was, for example, 5 MHz and the bandwidth during charge dump, at the detection node, 15 MHz. However, at present the clock frequency can be 36 MHz and the bandwidth can be as high as 158 MHz.

In [10]-[15], [18]-[21] and [24]-[28] different detection node topologies, such as floating diffusion, floating gate, junction FET, floating well, and floating surface, are described and their noise performance has been evaluated. None, except [19,24], give an analysis of the effect of the detection node on the bandwidth of the on-chip amplifier. Chapter 2 and Chapter 3 discuss the bandwidth of the on-chip amplifier and the way the distribution of capacitors at the input node (detection node plus parasitics) affect the bandwidth. These capacitors form a feedback path in the detection stage of the on-chip amplifier.

## Introduction

This feedback path causes the bandwidth to deteriorate. In addition the use of surface and buried channel transistors in the detection node and their effect on the bandwidth of the on-chip amplifier is studied.

Regarding the methods for experimental determination of design parameters, some novel and elegant methods are presented and discussed in Chapters 2-4. The aim is to determine important design parameters of the signal processor and on-chip amplifier.

In **Chapter 2** a model is derived to predict the noise and bandwidth behaviour of the on-chip amplifier. A parameter is introduced which is more suited for noise optimisation than the traditional ones. It is shown that this parameter is valid for any type of detection node architecture. Based on the model and the experiments conducted a second parameter is identified that has a large influence on the bandwidth of the on-chip amplifier. A special method is developed for the measurement of important design parameters.

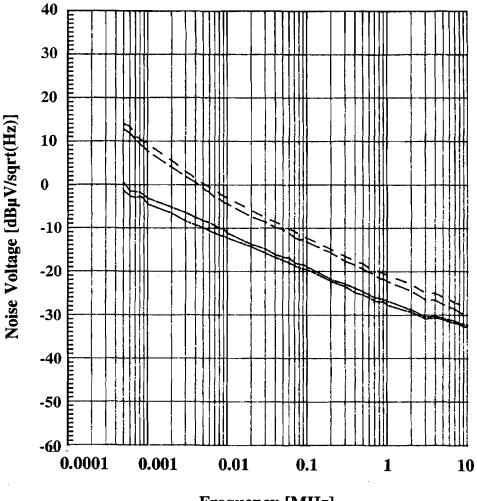

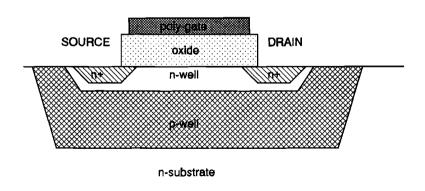

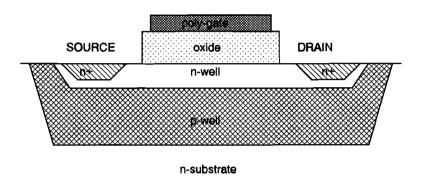

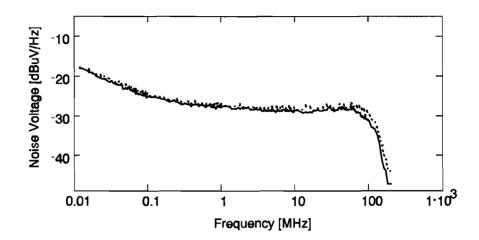

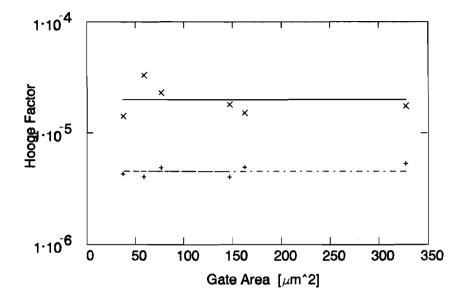

In **Chapter 3** the effects of sensitivity, 1/f noise, white noise, and bandwidth are studied for the case of using either a buried-channel or a surface-channel MOS transistor in the input stage of the on-chip amplifier.

In Chapter 4 the matched filter properties of the signal processor are derived with the aid of variational calculus. The derivation differs from the usual treatment given in the literature since it includes the effect of an important but often neglected noise contribution. Now a better solution for the matched filter can be found. The properties of the matched filter when excited with white noise and more generally with white and 1/f noise are studied. Based on this study a noise figure of merit for the signal processor is introduced and a lower bound is derived. For three types of signal processors the figure of merit is derived.

The basis of **Chapter 5** is an apparently academic question: "Is the noise performance of the current output of a CCD imager worse than the classical voltage output?" The discussion results in a novel way of using a floating diffusion detector. In fact we present a way of using a floating diffusion detector without generating reset noise. Criteria are established which determine the performance of the new readout scheme.

### References

- [1] A.Theuwissen. "Solid-State Imaging with Charge-Coupled Devices". Kluwer Academic Publishers 1995; ISBN 0-7923-3456-6.

- M.Collet, "Solid State Image Sensors". Proceedings SPIE Vol. 591, 1985, pp 82-93, 26-27 November 1985, Cannes, France.

- [3] T.Moelands, P.Centen, R. Voet. "A High Speed Sports Action Camera System". Technical Papers International Broadcast Convention, pp 86-92, Amsterdam, September 11-15, 1998.

- [4] E.Roks. "Advanced CCD Imaging by Opposite Carrier Interaction". Ph.D. Thesis Enschede, ISBN 90-74445-13-6, 1994

- [5] G.Kreider. "An mKxnK Modular Image Sensor Design". IEDM Technical Digest 1995, pp 155-158.

- [6] J.Carnes and W.Kosonocky, "Noise Sources in Charge-Coupled Devices". RCA Review, vol. 33, pp. 327-343, June 1972.

- [7] A.Theuwissen, H.Peek, P.Centen, R.Boesten, J.Cox, P.Hartog, A.Koskhoorn, H. van Kuijk, B.O'Dwyer, J.Oppers, F.Vledder. "A 2.2 Mpixel FT-CCD imager, according to the Eureka HDTV-standard". IEDM Tech. Dig. 1991 pp. 167-170.

- [8] J.Blankevoort, H.Blom, P.Brouwer, P.Centen, B. van de Herik, R.Koppe, A.Moelands, J. van Rooy, F.Stok and A.Theuwissen. "A High-Performance, Full Bandwidth HDTV Camera Applying the First 2.2 Million Pixel Frame Transfer CCD Sensor". SMPTE Journal, Vol. 103, No. 5, 1994, pp. 319-329.

- [9] S.Spitzer, J.Toker, A.Moelands, P.Centen, J. van Rooy, B.Gerovac. "Design and Implementation of a 3-CCD State of the Art, 750-line HDTV Progressive Scan Broadcast Camera". Proc. NAB 1996, pp. 171-178.

- [10] E.Roks, P.Centen, L.Sankaranarayanan, J.Slotboom, J.Bosiers, W.Huinink. "A Bipolar floating-base detector (FBD) for CCD Image Sensors". Technical Digest IEDM92, pp 109-112, San-Francisco, Dec 13-16, 1992.

- [11] R.Brewer, "A Low Noise CCD Output Amplifier", Technical Digest IEDM79, pp. 610-612, Washington DC, Dec 3-5, 1979.

- [12] N.Mutoh, M.Morimoto, M.Nishimura, N.Teranishi and E.Oda, "New Low Noise Output Amplifier for High Definition CCD Image Sensor", Technical Digest IEDM89, pp. 173-176, Washington DC, Dec 3-6, 1989.

- [13] Y.Matsunaga, "A High Sensitivity Output Amplifier For CCD Image Sensor", Technical Digest IEDM87, pp. 116-119, Washington DC, Dec 6-9, 1987.

#### Introduction

- [14] E.Roks, P.Centen, J.Bosiers, W.Huinink. "The Double-Sided Floating-Surface Detector: An Enhanced Charge-Detection Architecture for CCD image sensors". IEEE Trans. Electron Devices, vol. ED-43, No. 9, pp. 1583-1591, 1996.

- [15] E.Roks, J.Bisschop, P.Centen, L.Sankaranarayanan. "Theory and Modelling of the Floating-Surface Detector: An Enhanced CCD Output Structure". Philips Journal of Research, Vol. 48. No. 3, 1994, pp. 233-260.

- [16] H.S.Wong, "Technology and Device Scaling Considerations for CMOS Imagers". IEEE Trans. Electron Devices, vol. ED-43, no. 12, pp. 2131-2142, December 1996.

- [17] E.R.Fossum, "CMOS Image Sensors: Electronic Camera-On-A-Chip". IEEE Trans. Electron Devices, vol. ED-44, no. 10, pp. 1689-1698, October 1997.

- [18] D.Barbe, "Imaging Devices Using the Charge-Coupled Concept". Proceedings of the IEEE, pp. 38-67, Jan. 1975.

- [19] P.Centen, "CCD On-Chip Amplifiers: Noise Performance versus MOS Transistor Dimensions". IEEE Trans. Electron Devices, vol. ED-38, no. 5, pp. 1206-1216, May 1991.

- [20] W.Sansen, Z.Y.Chang, "Limits of Low Noise Performance of Detector Readout Front Ends in CMOS Technology", IEEE Trans. Circuits and Systems, vol. CAS-37, no. 11, pp. 1375-1382, November 1990.

- [21] L.Fasoli, M.Sampietro, "Criteria for setting the Width of CCD Front End Transistor to Reach Minimum Pixel Noise", IEEE Trans. Electron Devices, vol. ED-43, no. 7, pp. 1073-1076, July 1996.

- [22] M.White, D.Lampe, F.Blaha, I.Mack, "Characterization of Surface Channel CCD Image Arrays at Low Light Levels", IEEE Journal of Solid-State Circuits, vol. SC-9, No. 1, February 1974, pp 1-13.

- [23] P.Centen. "CCD signal processing for better signal-to-noise ratio". Philips Eindhoven, The Netherlands, TN 180-88, May 1988. Internal report.

- [24] P.Centen, E. Roks. "Characterization of Surface- and Buried-Channel Detection Transistors for On-Chip Amplifiers". Technical Digest IEDM97, pp.193-196, San Francisco, Dec 7-10, 1997.

- [25] J.Hynecek, "High-Resolution 8-mm CCD Image Sensor with Correlated Clamp Sample and Hold Charge Detection Circuit". IEEE Trans. Electron Devices, vol. ED-33, no. 6, pp. 850-862, June 1986.

- [26] J.Hynecek, "Design and Performance of a Low-Noise Charge Detection Amplifier for VPCCD Devices". IEEE Trans. Electron Devices, vol. ED-31, no. 12, pp. 1713-1719, Dec. 1984.

- [27] N.Teranishi, N.Mutoh, "Partition Noise in CCD Signal Detection". IEEE Trans. Electron Devices, vol. ED-33, no. 11, pp. 1696-1701, November 1986.

- [28] D.Heidtmann, F.Yang, "The effects of FET dimensions and bias on the noise performance of CCD output amplifier", Electronic Imaging 1987, pp. 248-253, Boston, Nov 2-5, 1987.

- [29] D.Hegyi and A.Burrows, "Optimal sampling of charge-coupled devices", Astronomical Journal, Vol.85, No. 10, pp 1421-1424, Oct. 1980

- [30] G.Hopkinson and D.Lumb, "Noise reduction techniques for CCD image sensors", J. Phys. E: Sci. Instrumm., Vol. 15, 1982, pp 1214-1222.

- [31] P.Levine, "Low-Noise CCD Signal Recovery". IEEE Trans. Electron Devices, vol. ED-32, no. 8, pp. 1534-1537, Aug. 1985.

- [32] W.Buttler, B.Hosticka and G.Lutz, "Noise Filtering for Readout Electronics", Nuclear Instruments and Methods in Physics Research, A288 (1990), pp 187-190

- [33] M.Ohbo, I.Akiyama, T.Tanaka, "A new suppression method for highdefinition CCD cameras". IEEE Trans. on Consumer Electronics, Vol. 35, No. 3, August 1989, pp. 368-374.

- [34] H.Wey and W.Guggenbühl, "An improved Correlated Double Sampling Circuit for low Noise Charge-Coupled Devices", IEEE Transactions on Circuits and Systems, Vol. 37, No. 12, december 1990, pp 1559-1565.

- [35] T.McCurnin, L.Schooley, G.Sims. "Charge-coupled device signal processing models and comparisons". Journal of Electronic Imaging, vol 2(2), pp. 100-107, April 1993.

- [36] C.Enz, "Analyses of low frequency noise reduction by auto-zero technique", Electronic Letters, Vol. 20, No. 23, pp 959-960, Nov 1984.

- [37] M.v.Buul and P.Centen, "Sampling Circuit", PCT application WO 96/01475, January 1996.

- [38] R.Kansy, "Response of a correlated double sampling circuit to 1/f noise", IEEE Journal of Solid-State Circuits, vol. SC-15, June 1980, pp 373-375.

# **Chapter 2**

# ON-CHIP AMPLIFIER Amplification and conversion<sup>1</sup>

# 2.1 Introduction

The main purpose of the on-chip amplifier in a CCD imager is the conversion of a charge packet into a voltage or a current. In addition to this conversion the on-chip amplifier must exhibit a good noise performance and it must be capable of driving an external load at the pixel frequency.

A popular way of detecting the charge of the CCD channel is to use a floating diffusion region [1,2] which, together with the input of the on-chip amplifier, forms a (capacitive) detection node. The change in the detection node voltage (V=Q/C) when a charge packet enters the node is sensed by the on-chip amplifier.

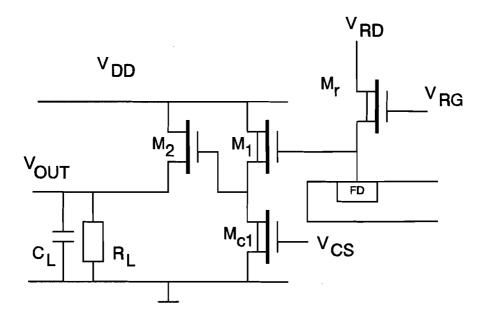

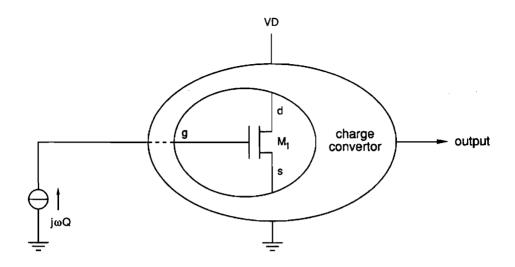

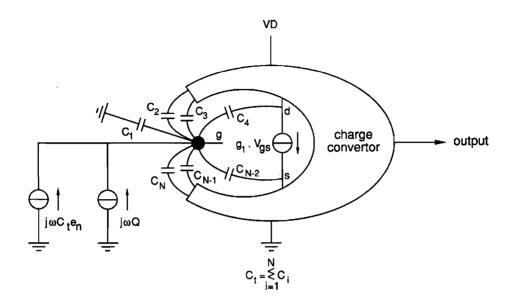

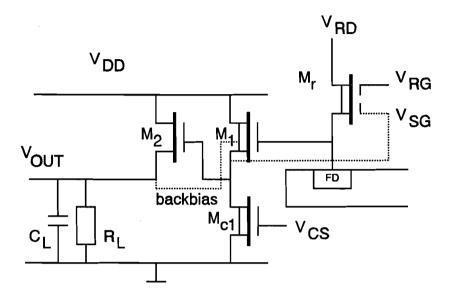

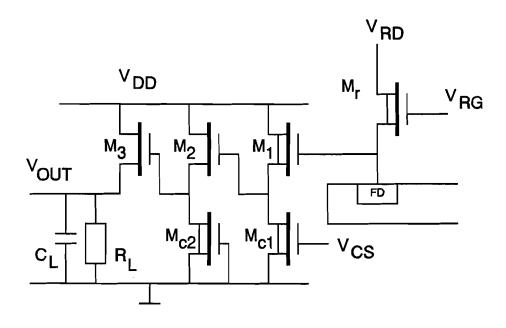

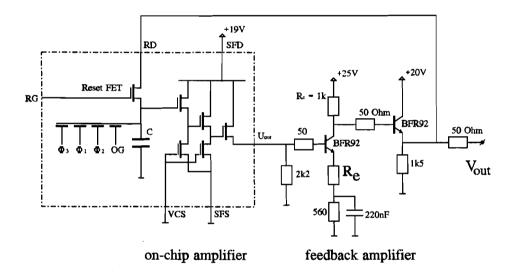

In order to achieve a large bandwidth one often encounters a two-stage source follower amplifier, the typical structure of which is shown in Figure 2.1. The first stage consists of a source follower  $(M_1)$  and a current sink  $(M_{c1})$  for biasing purposes. Both determine the noise performance. The second stage  $(M_2)$  drives

<sup>&</sup>lt;sup>1</sup> Based on the publication: P.Centen, "CCD-On-Chip Amplifiers: Noise Performance versus MOS transistor Dimensions". IEEE Trans. Electron Devices, vol. ED-38, no. 5, pp. 1206-1216, May 1991.

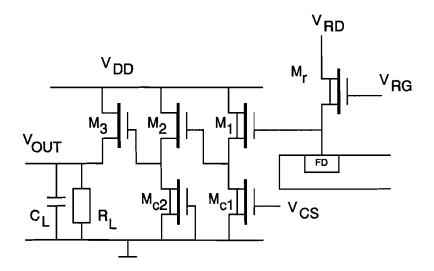

the load. For HDTV CCD imagers as many as three source follower stages can be needed [3].

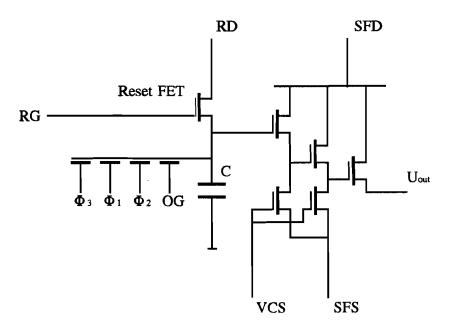

The reset FET  $(M_r)$  is connected to the floating diffusion region (FD) discussed above. In the off-state it can collect the next charge packet and in the on-state it resets the detection node to a reference voltage  $(V_{RD})$ . The drain of the reset FET is a current output (all signal charge appears here) but in general is not used as such (Chapter 5).

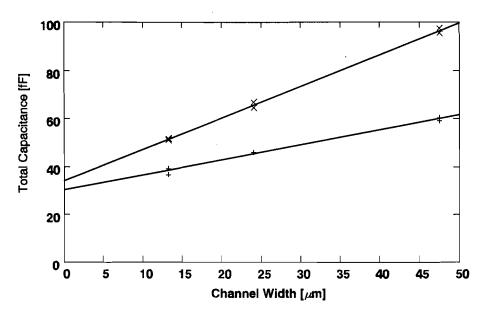

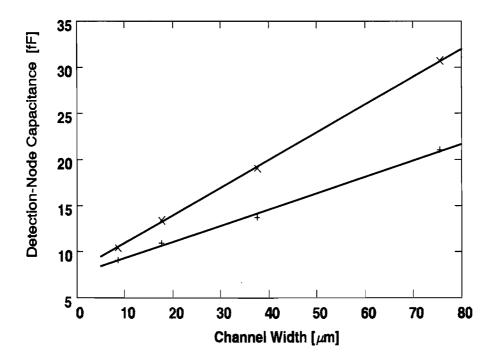

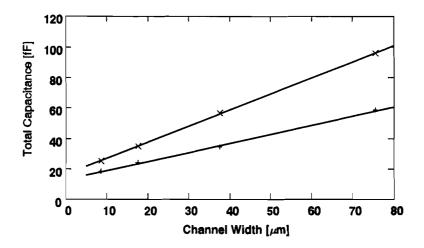

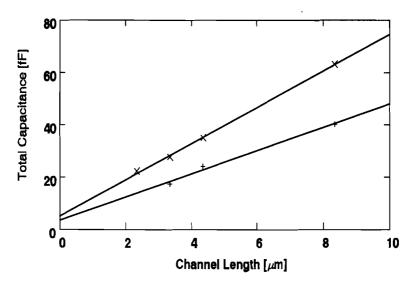

The bias voltage ( $V_{CS}$ ) at the gate of the current sink ( $M_{c1}$ ) determines the bias current (I) of the first stage. This gate can be used as a test signal injection point to measure both the ratio ( $\Theta_n$ ) between the total capacitance ( $C_{tot}$ ) and the detection node capacitance ( $C_{det}$ ) and the bandwidth in the reset FET off- and on-state. The total capacitance is defined as the capacitance between the gate of the detection node transistor and all the other nodes. The detection node capacitance is the effective capacitance of the detection node with the gain of the first stage taken into account.

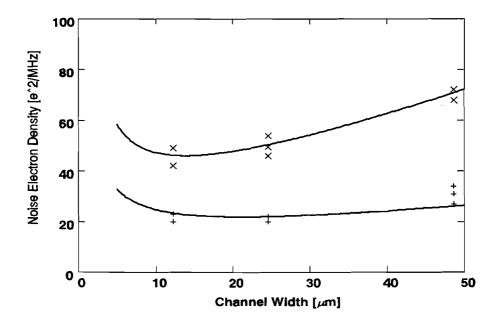

When the reset FET is off, as is the case when charge is dumped at the detection node, there is a large (capacitive) feedback from the source to the gate of  $M_1$ . Due to this phenomena the bandwidth is decreased during charge dumping. This decrease is controlled by the ratio between the total capacitance of the detection node  $C_{tot}$  and the detection node capacitance  $C_{det}$ . The latter capacitance ( $C_{det}$ ) consists for a small part of the floating diffusion region capacitance of the first MOS transistor. Nowadays much attention is paid to the design of low-capacitance detection nodes and scaling rules become important. Enlarging a structure on silicon not only increases the active MOS transistor capacitances but also the wiring and stray capacitance. It will be shown that the noise performance is proportional to the total capacitance  $C_{tot}$  of the detection node and the equivalent noise voltage of the first MOS transistor.

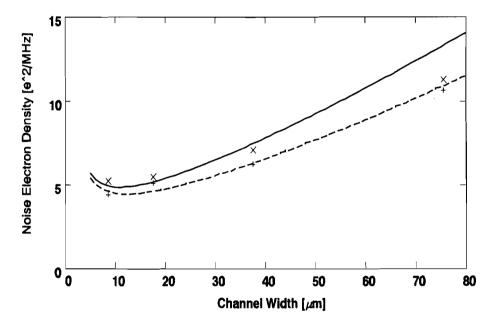

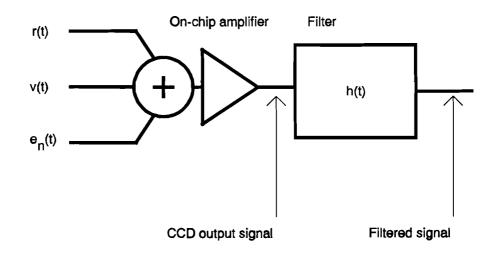

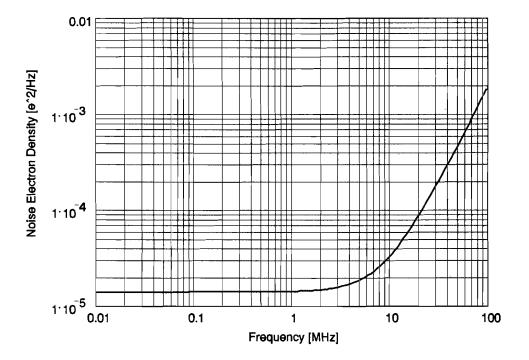

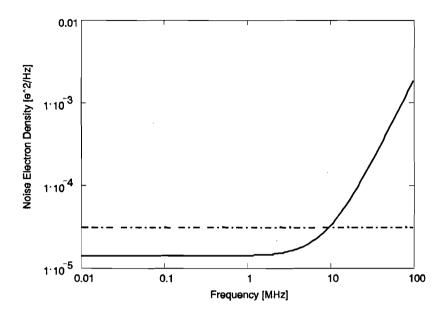

The designer of a signal processor generally uses its noise spectral density to determine the (noise) optimum filter. In the case of a CCD imager, where electrons are usually the signal, it is most natural to use the equivalent Noise Electron Density as a representation of the noise spectral density. The Noise Electron Density  $[e^2/Hz]$  is the ratio between the voltage noise spectral density  $[V^2/Hz]$  and the sensitivity squared  $[(V/e)^2]$ .

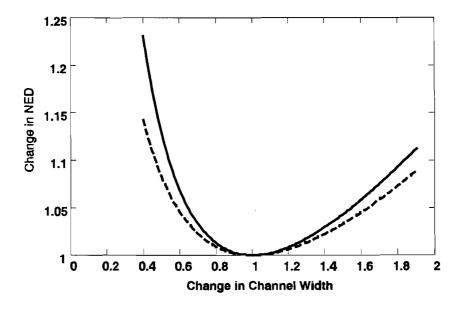

In contrast to earlier reports in literature [4,5] about noise optimization, the approach in this chapter is quite different: "the noise optimization is not based on minimizing the equivalent noise electrons but on minimizing the equivalent Noise Electron Density".

Figure 2.1: A typical on-chip amplifier for CCD imagers, with a floating diffusion detection node.

It will be shown that the optimum, with respect to signal-to-noise ratio, is valid for each type of signal processing.

Since the signal processors that are nowadays available [2,5,6,7,8,9], such as Correlated Double Samplers, suppress the reset noise sufficiently it is not taken into consideration.

In a well-designed on-chip amplifier the noise contribution of the first stage exceeds that of the second stage; therefore most attention will be paid to the first stage.

It is the goal of this chapter to establish both in theory and in practice the optimum values of the critical parameters of the detection node MOS transistor (the first source follower); namely, the bandwidth, the channel width and length, the bias current, the total capacitance, and the equivalent Noise Electron Density.

In Section 2.2 the first stage will be analyzed. First the charge dumping and

resetting of the floating diffusion region will be discussed, then the time response will be calculated, and then the 3 dB bandwidth in the reset FET onand off-state. Finally the noise in the on- and off- state will be discussed.

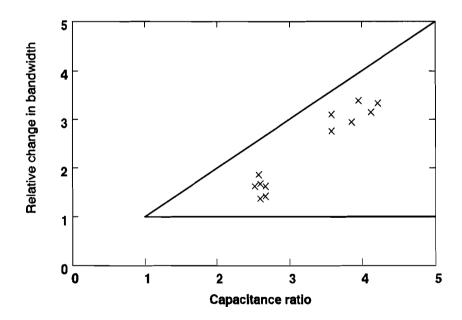

It will be shown that the ratio between total capacitance and detection node capacitance  $\Theta_n = C_{tot}/C_{det}$  is an important design parameter for the bandwidth. A method for measuring the latter ratio is discussed in **Section 2.3**. In **Section 2.4** a second important design parameter is introduced. It is the concept of equivalent Noise Electron Density. A general expression will be derived which is valid for both types of capacitive detection node, destructive and non-destructive [1,2,10,11,12,13,14].

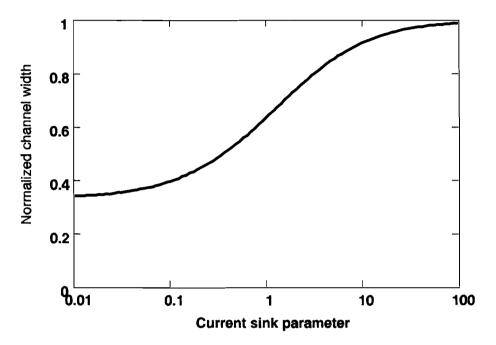

In Section 2.5 a calculation for noise optimization is presented based on the concept of the equivalent Noise Electron Density. The optimum dimensions and bias current of the detection node MOS transistor and current sink are derived for the case where thermal noise is dominant.

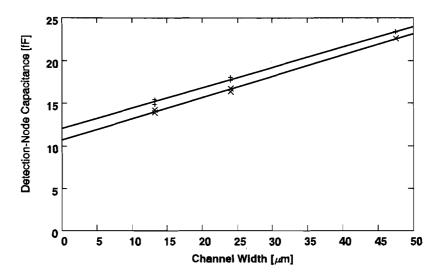

In Section 2.6 a comparison with some experimental results is presented.

Finally, the theory developed in the previous sections, together with the experimental results, is applied in Section 2.7. It describes an improvement in the design of the on-chip amplifier of the FT5 SDTV CCD imager [15] and discusses the design of the on-chip amplifier for the FT8 HDTV CCD imager [3].

# 2.2 Analysis of the first stage: a source follower

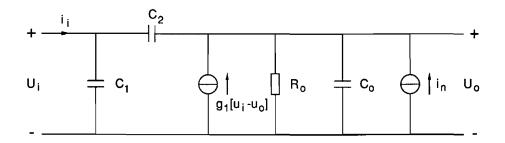

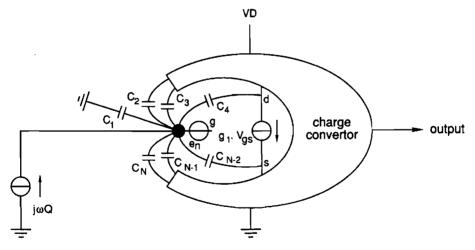

#### 2.2.1 Small signal equivalent circuit.

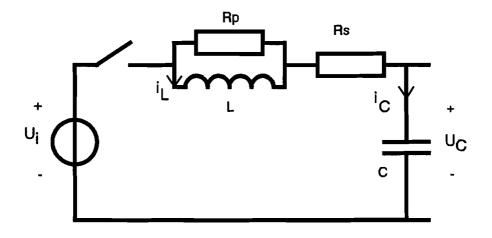

The small signal equivalent diagram of the first stage consisting of a source follower  $M_1$  and a current sink  $M_{c1}$  is given in Figure 2.2. The capacitance between the gate and ground  $(C_1)$  is made up of the floating diffusion capacitance (FD), the drain overlap capacitance  $(C_{gd,o})$  and some stray and wiring capacitances. The capacitance between the gate and the source  $(C_2)$  of  $M_1$  consists of the source overlap capacitance  $(C_{gs,o})$ , the active channel capacitance, and stray and wiring capacitances. At any biasing point the following small signal parameters are defined: the transconductance  $(g_1)$  of  $M_1$ , a load resistance  $(R_o)$  which includes the output resistance of  $M_1$  and  $M_{c1}$ , and a capacitive load  $(C_o)$  which also includes the input capacitance of the second stage. The current noise source  $(i_n)$  represents the noise of both the follower  $M_1$  and sink  $M_{c1}$ . Finally,  $i_i$  is the current flowing into the detection node. In the reset FET off-state charge is dumped onto the detection node. The reset FET is omitted

in the diagram. The loading effect of the second stage is represented by  $R_o$  and  $C_o$ .

Figure 2.2: The small signal equivalent diagram of the first stage of the on-chip amplifier.

#### 2.2.2 Charge packet response: rise and fall time.

There exists an asymmetry between the reset FET on- and off-state. In the onstate the detection node is almost short circuited. When it is placed in the offstate the detection node floats and is very high ohmic; from this moment on an effective feedback exists from the source to the gate of follower  $M_1$  due to  $C_2$ , which forms a capacitive divider with  $C_1$ .

In the frequency domain the node equations written in matrix form are:

$$\begin{bmatrix} I_i \\ I_n \end{bmatrix} = \begin{bmatrix} j\omega (C_1 + C_2) & -j\omega C_2 \\ -(j\omega C_2 + g_{ml}) & \frac{1}{R_o} + g_{ml} + j\omega (C_o + C_2) \end{bmatrix} \begin{bmatrix} U_i \\ U_o \end{bmatrix}$$

(2.1)

$I_i$  and  $I_n$  are the Fourier Transforms of  $i_i$  and  $i_n$ , respectively.

In practice the capacitive load  $C_0$  is much larger than the gate-to-source capacitance of  $M_1$  ( $C_0 >> C_2$ ). Furthermore, the 3 dB bandwidth ( $F_3$ ) caused by the load capacitance is well below the transit frequency ( $F_T=g_{m1}/(2 \pi C_2)$ ) of the detection node MOS transistor. Typically  $F_T$  has a value of 500 MHz - 1 GHz. A derivation of the transfer functions when using the above approximations is

given in Appendix A. The result will be used in the remainder of this section.

In the reset FET off-state charge is dumped on the floating diffusion region. The frequency response of the first stage is calculated by solving the matrix equation (2.1). By definition the input current is the time derivative of the charge. After Fourier transformation the relation between the input current  $I_i$  and the charge packet  $Q(\omega)$  is:

$$I_i = j \,\omega \, Q(\omega) \tag{2.2}$$

Assuming  $I_n(\omega)=0$ , the response at the source  $(U_0)$  becomes

$$U_o = \frac{A_{10}}{1 + j\omega\tau\theta_n} \cdot \frac{Q(\omega)}{C_{det}}$$

(2.3)

(see Appendix A)

In the above the following definitions have been used:

DC gain of the first source follower stage

$$A_{10} = \frac{g_{ml} R_o}{1 + g_{ml} R_o}$$

(2.4)

time constant of the output

$$\tau = \frac{C_o}{g_{ml}} A_{10}$$

(2.5)

and detection node capacitance

$$C_{\text{det}} = C_1 + (1 - A_{10})C_2$$

(2.6)

The ratio between the total capacitance  $C_{tot}=C_1+C_2$  and the detection node capacitance  $C_{det}$  is  $\Theta_n$  and determines the feedback between the source of  $M_1$  and the detection node in the reset FET off-state

$$\theta_n = \frac{C_{tot}}{C_{det}}$$

(2.7)

In the case of a source follower the ratio  $\Theta_n$  is always larger than one. With a

common source configuration it is possible to obtain values for  $\Theta_n$  smaller than one.

The charge packet in a CCD imager usually consists of electrons. Let us assume that one charge packet with a charge -qN is dumped on the floating diffusion region at t=0. Using the Dirac impulse function  $\delta(t)$  this is written as

$$i_i(t) = -qN\delta(t) \tag{2.8}$$

The effect of such a current impulse is a step-wise change in charge for which the Fourier transform equals

$$Q(\omega) = -qN\left(\pi\,\delta(\omega) + \frac{1}{j\,\omega}\right) \tag{2.9}$$

The source voltage  $U_o$  as a function of time is calculated making use of the inverse Fourier transformation of equation (2.3) after substituting equation (2.9).

Introducing the sensitivity

$$S = A_{10} \frac{q}{C_{\text{det}}}$$

(2.10)

the time response is given by

$$u_{o}(t) = V_{o} - S N \left[ 1 - e^{-\frac{t}{\tau \theta_{\pi}}} \right] \qquad t \ge 0$$

(2.11)

At t=0 the output voltage has the reference value  $V_o$ ; the stationary value (t =  $\infty$ ) is  $u_o(t=\infty) = V_o - S N$ . The output swing due to a charge packet of N electrons is therefore S N. This explains the reason for introducing the sensitivity through equation (2.10). The stationary value means that S equals the change in output voltage due to a charge packet of one electron. The sensitivity of the detection node is determined by the capacitance between the gate and the source of the detection node MOS transistor (C<sub>2</sub>), the capacitance between the gate and ground (C<sub>1</sub>), and the voltage gain of the detection node MOS transistor (A<sub>10</sub>). Because a source follower configuration is used only a fraction of the gate-to-source capacitance C<sub>2</sub> contributes to the detection node capacitance (equation (2.6)). The fall time of the output signal is  $\tau \Theta_n$ .

Before commenting on the fall time, the time response of the charge draining off in the reset FET on-state will first be calculated.

In the on-state the charge that has been dumped at the floating diffusion region is drained to the reset drain terminal ( $V_{RD}$  in Figure 2.1). The response for the on-state is arrived at by solving equation (2.1) under the condition of  $I_n(\omega) = 0$ (Appendix A)

$$U_o(\omega) = \frac{A_{10}}{1 + j\omega\tau} U_i(\omega)$$

(2.12)

Next we assume that at t=0 the output voltage has reached its stationary value  $V_o$ -S·N and that for t>0 the reset FET is switched on, clamping the floating diffusion region at the reset drain potential. The time response is then given by:

$$u_o(t) = V_o - S N e^{-\frac{t}{\tau}}$$

(2.13)

Note that the fall time  $\tau \Theta_n$  in equation (2.11) is a factor  $\Theta_n = C_{tot}/C_{det}$  larger than the rise time  $\tau$  of equation (2.13).

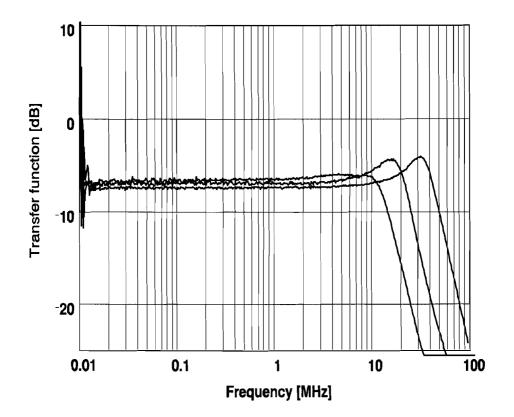

#### **2.2.3 Bandwidth and** $\Theta_n$ .

Instead of calculating the time response one can focus on the transfer function and determine the 3 dB bandwidth. In the reset FET on-state the transfer function is given by equation (2.12). Therefore the 3 dB bandwidth in the on-state has a value:

$$F_{3}(on) = \frac{1}{2\pi\tau}$$

(2.14)

On the other hand the 3 dB bandwidth in the reset FET off-state follows from equation (2.3)

$$F_3(off) = \frac{1}{2\pi\tau\theta_n}$$

(2.15)

and therefore is (much) smaller than in the on-state.

#### **On-chip** amplifier

The fact that the ratio  $\Theta_n = C_{tot}/C_{det}$  determines the loss of bandwidth is an important result. It is therefore one of the major design parameters for amplifiers on CCD imagers. In the design of high speed on-chip amplifiers one should focus on a low- $\Theta_n$  design. Practically  $\Theta_n$  ranges from 1.5 to 3.5. For example, when  $\Theta_n = 3.3$  and the bandwidth during charge dumping is

15 MHz than the bandwidth increases to 50 MHz when the floating diffusion region is clamped.

In order to measure the bandwidth and the DC gain of the on-chip amplifier the on-state is often used to apply a test signal at the reset drain. In this example the measured bandwidth of 50 MHz would be far too optimistic.

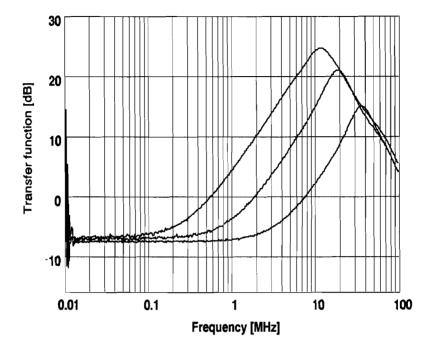

#### 2.2.4 Noise in the Reset FET on- and off-state.

The noise current  $i_n$  induces a voltage swing  $U_o$  at the source of  $M_1$  (Figure 2.2). With the substitution of an equivalent noise voltage  $e_n=i_n/g_{mc}$  equation (2.1) can be solved for the case  $C_o>>C_2$  under the condition that the reset FET in the onstate represents a short circuit ( $U_i=0$ ). The solution can be written as

$$U_o(\omega) = \frac{A_{10}}{1 + j\omega\tau} e_n$$

(2.16)

However, in the reset FET off-state with  $I_i=0$ , we have

$$U_o(\omega) = \frac{A_{10}}{1 + j\omega\tau\theta_n} \theta_n e_n \qquad (2.17)$$

Comparing equation (2.16) in equation (2.17), note that the output noise of the first stage has increased by the factor  $\Theta_n$  and that at the same time the bandwidth has decreased by the same factor.

The asymmetry between off-state and on-state has already been discussed for the charge handling (equations (2.11) and (2.13)).

This is a well-known result from feedback theory which states that for a given system the gain-bandwidth product is (almost) a constant.

The same conclusions apply for the situation in which the gate of the current source  $V_{cs}$  is used as an input to inject a test signal.

The noise of the source follower and the current sink. The noise current  $i_{nc}$  of sink  $M_{c1}$  and of the detection node MOS transistor  $M_1$ ,  $i_{n1}$ , together determine

the noise  $i_n$  of the first stage. That is,

$$\dot{i}_n^2 = \dot{i}_{n1}^2 + \dot{i}_{nc}^2 \tag{2.18}$$

Using the definition of the equivalent noise voltage for M<sub>1</sub>

$$e_{n1} = \frac{i_{n1}}{g_{ml}}$$

(2.19)

and M<sub>c1</sub>

$$\boldsymbol{e}_{nc} = \frac{\boldsymbol{i}_{nc}}{\boldsymbol{g}_{mc}} \tag{2.20}$$

one obtains for the total equivalent noise voltage  $e_n$

$$e_n^2 = e_{n1}^2 + \left[\frac{g_{mc}}{g_{ml}}\right]^2 e_{nc}^2$$

(2.21)

The ratio  $g_{mc}/g_{m1}$  is the voltage gain of the cascode section  $M_{c1}$  and  $M_1$ . In order to obtain a low noise level, it is trivial but very important to note that this gain must be small.

# **2.3** Procedure to determine $C_{tot}$ and $\Theta_n$ .

For measurement purposes a second input, other than the reset drain, is usually available: the gate of the current source ( $M_{c1}$  in Figure 2.1).

Given the following two constraints (equation (2.22))

- the reset FET  $(M_r)$  has a resistance R,

- and the current source  $M_{c1}$  has a transconductance  $g_{mc}$ ,

$$\frac{U_i}{I_i} = -R \tag{2.22}$$

$$I_n = -g_{mc} U_{cs}$$

and substituting the above in equation (A1) of Appendix A, the transfer function between the output  $(U_o)$  and the current source gate  $(U_{cs})$  is found to be

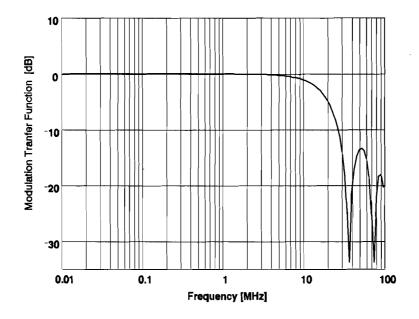

$$\frac{U_o}{U_{cs}} = \frac{g_{mc}}{g_{ml}} A_{10} \frac{1 + j\omega C_{tot}R}{1 + j\omega \left(\frac{A_{10}}{g_{ml}}(C_0 + C_2) + C_{det}R\right) - \omega^2 \frac{A_{10}}{g_{ml}}R(C_0 C_{tot} + C_2 C_1)}$$

(2.23)

The transfer function has one zero and two poles.

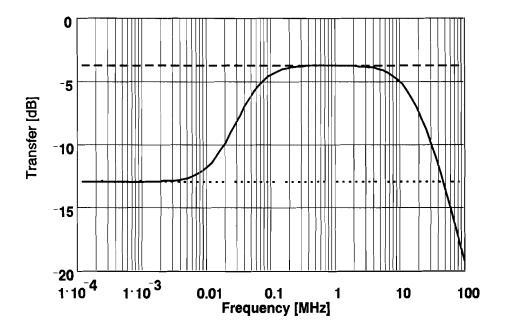

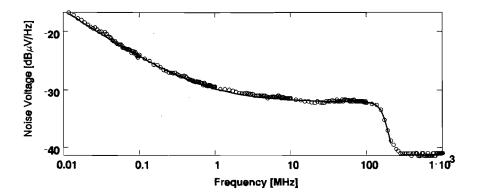

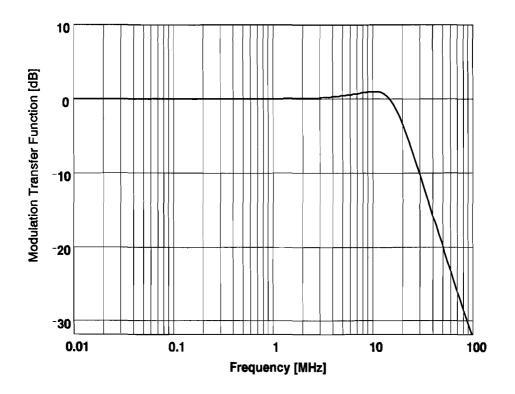

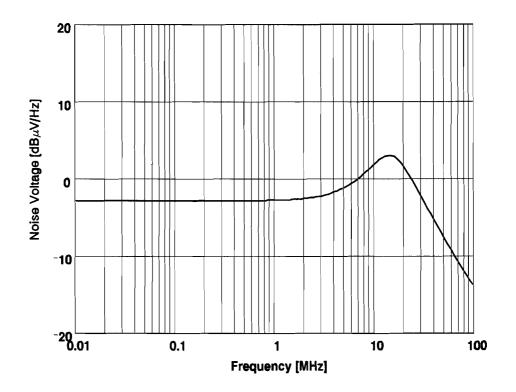

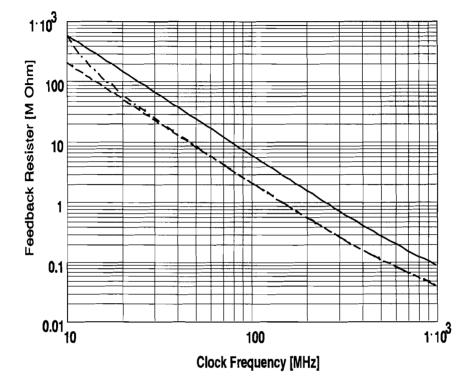

In Figure 2.3 the transfer function is calculated with the following parameter values substituted in equation (2.23):  $C_1=13$  fF,  $C_2=35$  fF,  $A_{10}=0.90$ ,  $C_0=350$  fF,  $g_{m1}=10^{-4} \Omega^{-1}$ ,  $g_{mc}=g_{m1}/4$  and R=300 M $\Omega$ . ( $C_{tot}=C_1+C_2=48$  fF,  $C_{det}=C_1+(1-A_{10}).C_2=16.5$  fF, and  $\Theta_n=C_{tot}/C_{det}=2.9$ )

For frequencies far below  $1/(2 \pi R C_{tot})$  the transfer function is approximately

$$\frac{U_o}{U_{cs}} = \frac{g_{mc}}{g_{ml}} A_{10} = 0.225$$

(2.24)

For frequencies between  $1/(2 \pi R C_{tot})$  and  $1/(2 \pi R C_{det})$  there is a transition region in which the gain increases and stabilizes at

$$\frac{U_o}{U_{cs}} = \frac{g_{mc}}{g_{ml}} A_{10} \theta_n = 0.654$$

(2.25)

For still higher frequencies bandwidth limiting occurs above  $g_{ml}/(2 \pi C_o \Theta_n A_{10})$ .

The value of the reset FET channel resistance, which is determined by the bias voltage ( $V_{RG}$ ), must be chosen so that the transition from equation (2.24) to equation (2.25) occurs well below the point where bandwidth limiting occurs. In the example 300 M $\Omega$  for the reset FET channel resistance was a suitable value. The exact value is not critical.

The importance of the above derivation lays in the fact that it is possible to determine the ratio  $\Theta_n = C_{tot}/C_{det}$  via a single measurement in which the bias conditions of the on-chip amplifier are not changed.

Since  $C_{det}$  and  $\Theta_n$  are measurable, the total capacitance  $C_{tot}$ , which controls the noise performance and bandwidth, can be measured and the optimum layout can be established.

**Figure 2.3:** The transfer function between the current source gate and the output for a reset FET channel resistance of 300 MQ. The dotted and the dashed lines are the asymptotic values and their difference is the value of  $\Theta_n = C_{to}/C_{der}$

For cases in which no network analyzer is available a second measurement technique is to determine the DC gain from the current source gate  $V_{CS}$  to the output in the reset FET off-state and on-state.

The reset FET channel resistance is determined by the value of the reset gate voltage. In equation (2.23) the following values for the reset FET channel resistance can be substituted: R=0 and R= $\infty$ . These are respectively obtained by setting a high and low value for V<sub>RG</sub>.

After substituting R=0, the gain in the reset FET on-state is

$$\frac{U_o}{U_{cs}} = \frac{g_{mc}}{g_{ml}} A_{10} \frac{1}{1 + j\omega \frac{A_{10}}{g_1} (C_0 + C_2)}$$

(2.26)

and in the reset FET off-state  $(R=\infty)$

$$\frac{U_o}{U_{cs}} = \frac{g_{mc}}{g_{ml}} A_{10} \theta_n \frac{1}{1 + j\omega \frac{A_{10}}{g_1} \theta_n \left(C_0 + \frac{C_2 C_1}{C_1 + C_2}\right)}$$

(2.27)

Therefore the ratio between the gain in the on- and off-states for low frequencies is  $Gain(off)/Gain(on)=\Theta_n=C_{tot}/C_{det}$ .

# 2.4 Equivalent Noise Electron Density (NED)

#### 2.4.1 Equivalent noise electrons versus NED

In CCD imagers it is common practice to express the noise performance as the number of equivalent noise electrons. This figure of merit is determined by the product of the square root of a noise level (spectral density) and an equivalent noise bandwidth. A low figure can be obtained in two ways: a low noise level or a small equivalent noise bandwidth. In optimizing the design it is better to separate the two effects and to use the Noise Electron Density as a figure of merit which is determined by the image sensor. The equivalent noise bandwidth is determined by off-chip signal processing.

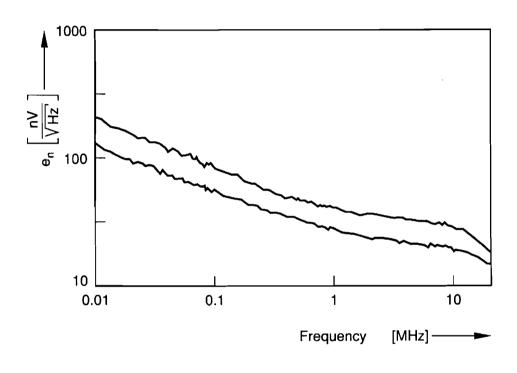

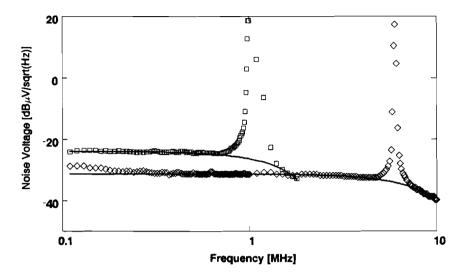

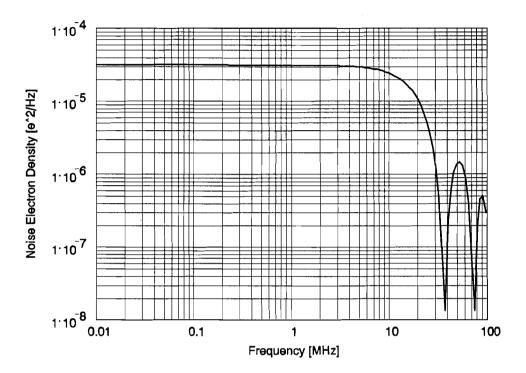

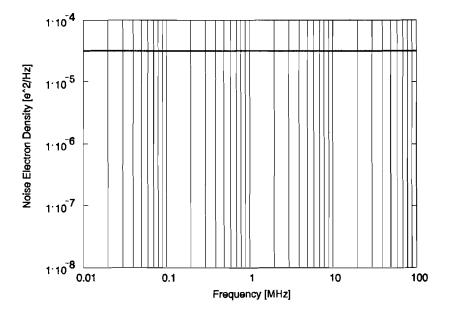

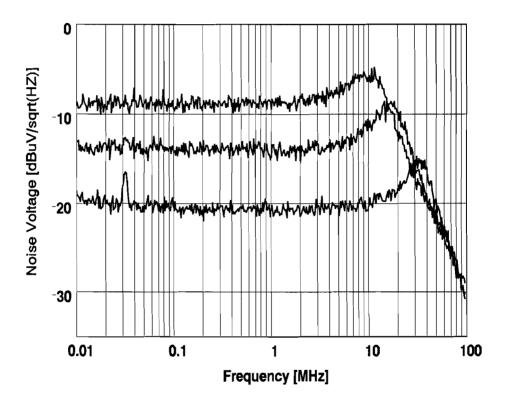

One usually expresses the noise level as an equivalent noise voltage in  $V/\sqrt{Hz}$  or as a noise current in  $A/\sqrt{Hz}$ . These units squared are called the voltage spectral density  $V^2/Hz$  and the current spectral density  $A^2/Hz$ . In the case of a CCD imager with its electrons (charge) as the signal it is more appropriate to express the noise in [electrons<sup>2</sup>/Hz] for which we propose the name equivalent Noise Electron Density (NED). This value can be given in two states, with the reset FET on or off. Of course the value in the off-state is more important because this is the state in which charge is dumped on the detection node. This is also the state in which the signal processor suppresses reset noise and 1/f noise [2,5,6,7,8,9] and amplifies the charge signal.

Dividing equation (2.17) by equation (2.3), where the charge Q is taken to be the unit charge q, and using equation (2.7), the expression for the NED becomes

$$NED(f) = \left[\frac{e_n(f)C_{tot}}{q}\right]^2$$

(2.28)

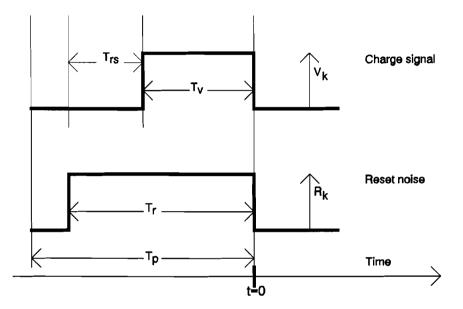

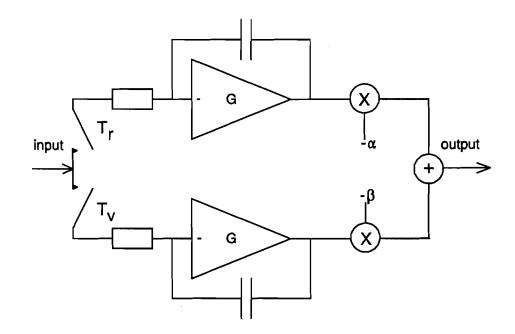

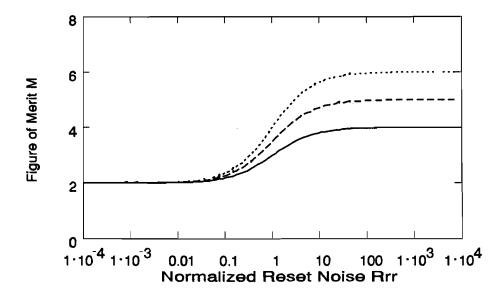

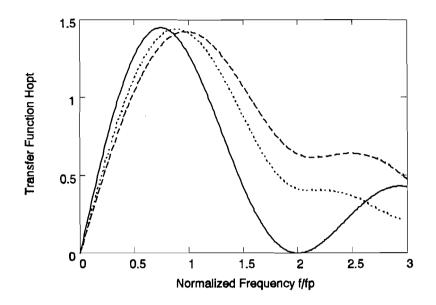

This equation, because it is valid for each frequency, also includes 1/f noise.