# The physics and technology of submicron MOS devices

#### Citation for published version (APA):

Walker, A. J. (1994). *The physics and technology of submicron MOS devices*. [Phd Thesis 2 (Research NOT TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR412165

DOI: 10.6100/IR412165

#### Document status and date:

Published: 01/01/1994

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# The Physics and Technology of Submicron Mos Devices

A.J. Walker

# THE PHYSICS AND TECHNOLOGY OF SUBMICRON MOS DEVICES

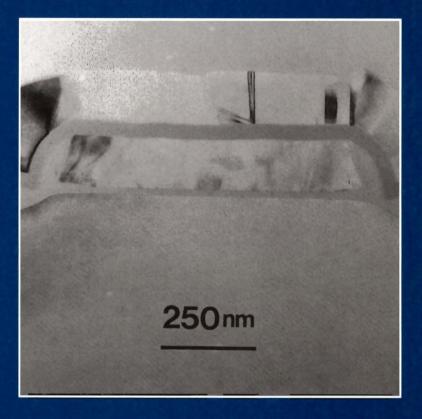

The figure on the front cover shows a TEM cross section of an Electrically Programmable Read Only Memory cell obtained using a focussed ion beam to slice through the sample.

CIP gegeven: ISBN: 90–74445\_08–X

> © Philips Electronics N.V. 1993 All rights are reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

# THE PHYSICS AND TECHNOLOGY OF SUBMICRON MOS DEVICES

PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr. J.H. van Lint, voor een commissie aangewezen door het College van Dekanen, in het openbaar te verdedigen op dinsdag 8 februari 1994 te 16.00 uur

door

#### Andrew Jan Walker

geboren te Sialkot, Pakistan

Dit proefschrift is goedgekeurd door de promotoren: prof.dr. F.M. Klaassen en prof.dr. P.H. Woerlee

The work described in this thesis has been carried out under supervision of prof.dr. F.M. Klaassen at the Philips Research Laboratories in Eindhoven, The Netherlands, as part of the Philips Research programme.

To my cousin Gerda

# Contents

| General Introduction |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1.1                  | Introduction                                                                                                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                      | 1.1.1 Scaling                                                                                                                                                                             | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                      | 1.1.2 Process Technology                                                                                                                                                                  | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 1.2                  | Thesis Summary                                                                                                                                                                            | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 1.3                  | References                                                                                                                                                                                | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| Inve                 | ersion Layer Mobility                                                                                                                                                                     | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 2.1                  | Introduction                                                                                                                                                                              | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 2.2                  | MOSFET: Qualitative Approach                                                                                                                                                              | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 2.3                  |                                                                                                                                                                                           | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 2.4                  |                                                                                                                                                                                           | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                      | 2.4.1 Model                                                                                                                                                                               | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                      |                                                                                                                                                                                           | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                      |                                                                                                                                                                                           | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 2.5                  |                                                                                                                                                                                           | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 2.6                  | References                                                                                                                                                                                | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| Sha                  | llow Implanted Boron Junctions                                                                                                                                                            | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 3.1                  | Introduction                                                                                                                                                                              | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 3.2                  |                                                                                                                                                                                           | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                      |                                                                                                                                                                                           | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                      |                                                                                                                                                                                           | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                      |                                                                                                                                                                                           | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 3.3                  |                                                                                                                                                                                           | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                      | 3.3.1 Introduction                                                                                                                                                                        | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                      | <ol> <li>1.1</li> <li>1.2</li> <li>1.3</li> <li>Inversion</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>Sha</li> <li>3.1</li> <li>3.2</li> </ol> | 1.1       Introduction         1.1.1       Scaling         1.1.2       Process Technology         1.2       Thesis Summary         1.3       References         1.3       References         1.4       Introduction         1.5       MOSFET: Qualitative Approach         2.4       Inversion Layer Mobility         2.4       Inversion Layer Mobility         2.4.1       Model         2.4.2       Mobility Measurement         2.4.3       Results         2.5       Discussion and Conclusions         2.6       References         3.1       Introduction         3.2       Preamorphization         3.2.1       Sample Preparation         3.2.2       Results and Discussion         3.2.3       Conclusions |  |  |  |

|   |                     | 3.3.2 Sample Preparation                      | 47 |  |  |  |

|---|---------------------|-----------------------------------------------|----|--|--|--|

|   |                     | 3.3.3 Results and Discussion                  | 47 |  |  |  |

|   |                     | 3.3.4 Conclusions and Summary                 | 49 |  |  |  |

|   | 3.4                 | General Conclusions                           | 49 |  |  |  |

|   | 3.5                 | References                                    | 55 |  |  |  |

| 4 | Gat                 | te Work Function Engineering                  | 59 |  |  |  |

|   | 4.1                 | Introduction                                  | 59 |  |  |  |

|   | 4.2                 | Experimental                                  | 62 |  |  |  |

|   | 4.3                 | Results and Discussion                        | 63 |  |  |  |

|   | 4.4                 | Conclusions                                   | 66 |  |  |  |

|   | 4.5                 | References                                    | 70 |  |  |  |

| 5 | Sili                | con/Silicon Dioxide Barrier Height Adjustment | 73 |  |  |  |

|   | 5.1                 | Introduction                                  | 73 |  |  |  |

|   | 5.2                 | Fowler-Nordheim Tunneling                     | 76 |  |  |  |

|   | 5.3                 | Experiment                                    | 79 |  |  |  |

|   | 5.4                 | Results and Discussion                        | 80 |  |  |  |

|   | 5.5                 | Summary                                       | 87 |  |  |  |

|   | 5.6                 | References                                    | 89 |  |  |  |

|   | Sun                 | nmary                                         | 91 |  |  |  |

|   | San                 | nenvatting                                    | 95 |  |  |  |

|   | Nav                 | woord                                         | 99 |  |  |  |

|   | Curriculum Vitae 10 |                                               |    |  |  |  |

| а |                     |                                               |    |  |  |  |

|   |                     |                                               |    |  |  |  |

# Chapter 1

# **General Introduction**

"It seems as if a great deal were attainable in a world where there are so many marriages and decisive battles, and where we all, at certain hours of the day, and with great gusto and despatch, stow a portion of victuals finally and irretrievably into the bag which contains us." R.L. Stevenson

## 1.1 Introduction

J.E. Lilienfeld could not have known what he was starting when he filed the first patents on amplifying devices using the field effect in 1926 and 1928 [1]. Leipzig of the 1920s, where he was professor, seems as far removed from the present day as the first MOSFETs (metaloxide-semiconductor field-effect transistor) are from the devices now on offer. The first successful MOSFET was reported in 1960 by D. Kahng and M.M. Atalla [2] who made use of thermally grown silicon dioxide as gate insulation. As in most fields of human endeavour, one parameter is taken to differentiate the various players in the game. In this case, it is minimum feature size, that ubiquitous measure of technological prowess which has gone from above  $20\mu m$  in 1960 to around  $0.5\mu m$  at the present time. Such is the power and importance of the semiconductor industry that a Japanese company is willing to spend 770 million American dollars in 1992 to prepare one of its factories to make 64Mbit DRAM (dynamic random access memories) chips [3]. These chips are regarded as the drivers of the industry resulting in an annual decrease of minimum feature size of 13% since the early 1960s. Such is the inexorable march to smaller dimensions that there is already talk of a 1Gbit SRAM (static random access memory) in a  $0.12 \mu$ m manufacturing process by the year 2000.

Why this ceaseless march, grudging ourselves the time for rest? The answer lies, of course, with money. By reducing the minimum feature size, the area of a transistor decreases with the result that more functionality can be packed onto a given area of silicon. Less silicon per switching element means reduced costs and therefore higher profit margins. However, there are other advantages from microminiaturisation which may be obscured by the cost analysis alone. For instance, in most cases the resultant switching element dissipates less power producing less heat. Furthermore, reliability and switching time improve. These simple facts have led to the relentless pursuit of smaller dimensions in the area of ULSI (ultra large scale integration).

#### 1.1.1 Scaling

| Quantity                        | Scaling factor   |

|---------------------------------|------------------|

| Device dimensions               | $1/\kappa$       |

| Area                            | $1/\kappa^2$     |

| Packing density                 | $\kappa^2$       |

| Doping concentration            | $\kappa$         |

| Voltages and threshold          | $1/\kappa$       |

| Currents                        | $1/\kappa$       |

| Power dissipation per unit area | 1                |

| Capacitance per unit area       | $\kappa$         |

| Charge per unit area            | 1 .              |

| Electric field                  | 1                |

| Body effect coefficient         | $1/\kappa^{0.5}$ |

| Transistor transit time         | $1/\kappa$       |

| Power delay product             | $1/\kappa^3$     |

TABLE 1.1 : Constant Field Scaling

Reducing the gatelength of a MOSFET is the first action in the downscaling of the device. A consequence is that depletion region widths must also be reduced to prevent the source and drain depletion regions from meeting and punching through. This can be attained by increasing

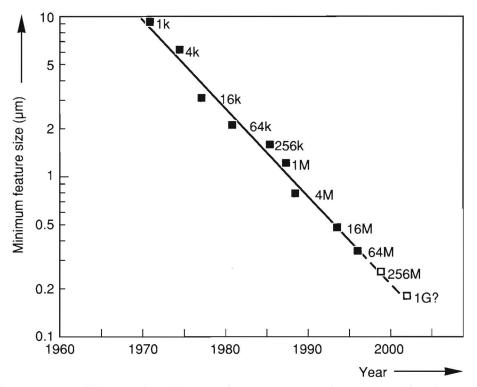

Figure 1.1. Historical evolution of the minimum feature size for dynamic random access memories at their introduction in production.

the substrate doping and decreasing the power supply voltage. The increase in doping results in threshold voltages being too high requiring, in turn, that the gate oxide thickness also be reduced. In other words, the process architecture must be changed to suppress short channel effects.

The incessant march to smaller dimensions can be seen in Fig. 1.1 which shows the historical evolution of the minimum feature size (the MOS gate length) for dynamic random access memories (DRAM) at their introduction in production [4].

The first set of rules proposed for the scaling of the MOSFET was introduced in 1974 [5] and is called *constant field scaling*. In this approach, the maximum electric field and the internal electric field profile are unaltered going from the original large device to the small scaled version. Using this method, the MOSFET is reduced by a factor  $1/\kappa$  ( $\kappa$  larger than 1) in all three dimensions (length, width, junction depth, gate oxide thickness). The effect of this is summarised in Table 1.1.

The problems with voltage losses along interconnections and in contact holes along with the fact that the slope of  $\log I_{ds}$  versus  $V_{qs}$  ( $I_{ds}$ - source drain current;  $V_{qs}$  - gate source voltage) does not change [6] mean that a larger fraction of the available voltage is lost in resistances and voltage swings to turn transistors on. This has led to the development of constant voltage scaling in which the voltage is kept constant as the device is scaled by a factor  $1/\kappa$  ( $\kappa > 1$ ). The main differences between this approach and that of the constant field scaling is that the supply and threshold voltages remain constant and the gate oxide thickness is reduced by a smaller amount than other dimensions to avoid problems with high fields. This approach has a more practical foundation than others in that standard supply voltages have remained largely constant while transistor dimensions have shrunk. It also deals with the practical problem that the threshold voltage does not scale downwards as dimensions shrink. With a reduced supply voltage, this would mean that less voltage over and above the threshold voltage (the "gate drive") would be available to invert the channel resulting in smaller currents.

Other approaches to scaling have been suggested such as *quasi*constant voltage scaling in which dimensions and dope levels are scaled as in the constant field approach but voltages are reduced by a smaller amount [7]. This means that depletion regions do not scale by the same amount as transistor dimensions. To achieve this, substrate doping is scaled by another factor resulting in the generalised scaling rules [8].

All the above approaches can be found in Table 1.2.

| Quantity       | Constant   | Constant         | Quasi-constant       | Generalised      |

|----------------|------------|------------------|----------------------|------------------|

|                | Field      | Voltage          | Voltage              |                  |

|                |            | $1<\beta<\kappa$ | $1 < \beta < \kappa$ | $1<\beta<\kappa$ |

| Length, Width  | $1/\kappa$ | $1/\kappa$       | $1/\kappa$           | $1/\kappa$       |

| Gate oxide     | $1/\kappa$ | $1/\beta$        | $1/\kappa$           | $1/\kappa$       |

| Substrate dope | $\kappa$   | $\kappa$         | $\kappa$             | $\kappa^2/eta$ . |

| Voltages       | $1/\kappa$ | 1                | $1/\kappa^{0.5}$     | 1/eta            |

TABLE 1.2 : Different Scaling Rules

Another scaling procedure takes advantage of the empirical result that devices exhibit long channel behaviour (i.e. short channel effects are absent) if their channel lengths are longer than some minimum amount given as

$$L_{min} = (constant)[x_j t_{ox} (d_s + d_d)^2]^{1/3}$$

where  $x_j$  is the source/drain junction depth,  $t_{ox}$  is the gate oxide thickness, and  $d_s$  and  $d_d$  are the source and drain depletion region widths [9].

#### 1.1.2 Process Technology

The key to miniaturisation is the huge advancements made in process technology. Billions of dollars are spent in the areas of lithography, deposition and etching to enable finer dimensions to be made on silicon wafers. Optical lithography is the workhorse of the semiconductor industry with dimensions down to  $0.5\mu$ m possible using the i-line of a mercury-arc light source to expose the resist on the wafer. The use of excimer laser light sources is expected to allow features down to  $0.25\mu m$  [10]. Beyond that, X-ray and electron-beam lithography are possible candidates for future processes. The fabrication of semiconductor circuits requires the deposition of various materials including dielectrics, semiconductors and metals. These processes demand the deposition of ultra clean layers, from a few nanometers to over 1 micron in thickness, on large silicon wafers of 8 inches ( $\approx 20$  cm) in diameter with a thickness variation across the wafer of less than 5%. The patterns defined in the resist by lithography are transferred to the wafer by etching. As devices shrink, the requirement is for anisotropic etches that remove material much faster in the vertical than in the horizontal dimension. In this way, the pattern in the resist is faithfully transferred to the underlying material without much loss in the linewidth. These anisotropic processes are achieved with the use of plasmas where reactive species are made to bombard the wafer surface. The fabrication of a ULSI circuit requires the use of hundreds of process steps involving lithography, deposition, etching, oxidation, implantation, high temperature annealing and cleaning. All for the sake of smaller devices and larger returns on investments.

## 1.2 Thesis Summary

The research to be described concerns topics related to the lateral and vertical scaling of devices for ULSI. In this case, the devices are metal-oxide-semiconductor (MOS) transistors and are fabricated in silicon.

In the scaling of the MOS transistor to smaller dimensions, the gate oxide thickness reduces while the substrate doping concentration increases. These steps lead to an increase in the vertical electric fields in the channel region of the device resulting in the reduction of the mobility of the charge carriers. The modeling of this mobility reduction is important to be able to simulate circuits containing submicron devices. The first main topic describes the modeling of the electron and hole inversion layer mobility as a function of the effective normal field,  $E_{eff}$  [11].

Scaling MOS transistors to smaller dimensions also involves the reduction in the source and drain junction depth. While shallow junctions are required in both NMOS and PMOS devices, the latter provide the greater challenge because of the high diffusivity of boron [12] and boron's tendency to channel during implantation [13]. In the second main topic, work will be described where the surface of silicon is made amorphous prior to boron implantation which reduces the channeling and affects the diffusivity. With the use of cross sectional Transmission Electron Microscopy (XTEM), Rutherford Backscattering (RBS) and Secondary Ion Mass Spectroscopy (SIMS), a complete description of this technique will be presented.

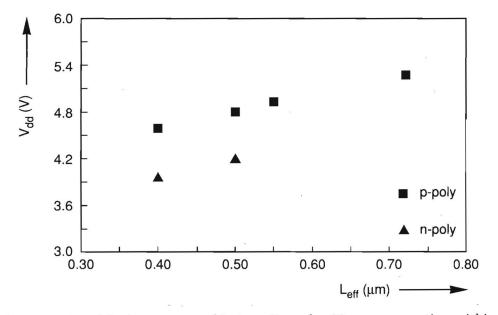

In the scaling of PMOS transistors, it is known that the use of the standard n-type polycrystalline silicon as gate material leads to problems. This involves the workfunction of the gate being too low and the magnitude of the threshold voltage too high, which can be circumvented by a p-type implant in the channel region of the device. The resulting vertical p-n junction in the channel makes it very difficult to shrink this device any further [14]. Increasing the gate's workfunction would help to solve this problem. This can be done using boron to dope the gate. The problems and limitations of this approach will be described in the third main topic.

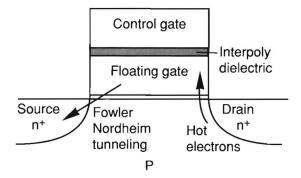

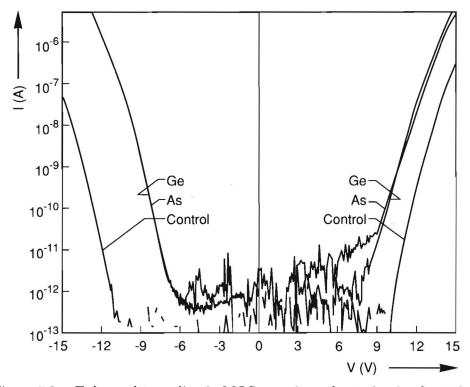

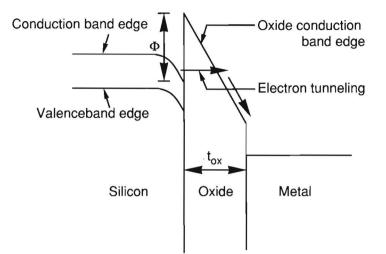

In integrated circuits containing scaled devices, the voltage which can be applied safely to any part of the circuit reduces due to thinner oxides and shallower junctions. In applications where devices are integrated that require large voltages for operation, problems can arise. This is especially the case for Electrically Erasable and Programmable Read Only Memories (EEPROM) and Flash EEPROM cells. These normally require voltages above 12 volts. If these are embedded in submicron circuits, special process steps have to be carried out to enable such large voltages to be used. The fourth main topic deals with a new techique to reduce the barrier height which limits electron tunneling through a thin oxide. Therefore, voltages can be reduced to program and erase EEPROM and Flash cells treated using this technique. In this way, such devices could be integrated with scaled MOS transistors.

In summary, the thesis deals with the practical problems of scaling MOS transistors to smaller dimensions. It is divided into four main topics and is based on several publications as follows:

- 1 Electron and Hole Inversion Layer Mobility [15], [16].

- 2 Shallow Junctions [17], [18].

- 3 Gate Work Function Engineering [19]

- 4 Silicon/Silicon Dioxide Barrier Height Adjustment [20].

## 1.3 References

- J.E. Lilienfeld, U.S. Patents 1,745,175 (filed in 1926, issued in 1930), 1,877,140 (filed in 1928, issued in 1932), and 1,900,018 (filed in 1928, issued in 1933).

- [2] D. Kahng and M.M. Atalla, IRE-AIEE Solid State Device Res. Conference, Carnegie Institute of Technology, Pittsburgh, PA 1960.

- [3] "Falling off the learning curve", The Economist Year Book, 1992 Edition, p182, 1992.

- [4] D. Bois, "The ultimate evolution of CMOS technology," Commission of the European Communities, Directorate-General III, DG III-A-5, 1993.

- [5] R.H. Dennard, F.H. Gaensslen, H.N. Yu, V.L. Rideout, E. Bassous and A.R. LeBlanc, IEEE J. of Solid-State Circuits, vol. SC-9, pp. 256-268, 1974.

- [6] "Operation and Modeling of the MOS Transistor," by Y. Tsividis, p204, McGraw-Hill, 1987.

- [7] P.K. Chatterjee, W.R. Hunter, T.C. Holloway and Y.T. Lin, IEEE Elec. Dev. Lett., vol. EDL-1, pp. 220-223, 1980.

- [8] G. Baccarani, M.R. Wordeman and R.H. Dennard, IEEE Trans. Elect. Dev., vol. ED-31, pp. 452-462, 1984.

- [9] J.R. Brews, W. Fichtner, E.H. Nicolian and S.M. Sze, IEEE Elect. Dev. Lett., vol. EDL-1, pp. 2-3, 1980.

- [10] E.H. Kung, M. Cheng, O. Nalamasu, A.G. Timko, C.B. Case and V. Pol, Jap. J. of Appl. Phys., vol.30, no. 11B, pp. 3030-3036, Nov. 1991.

- [11] A.G. Sabnis and J.T. Clemens, IEDM Tech. Dig., pp. 18-21, Dec. 1979.

- [12] T.M. Liu and W.G. Oldham, IEEE Electron Device Lett., vol. EDL-4, p.59 1983.

- [13] T.O. Sedgwick, A.E. Michel, V.R. Deline, S.A. Cohen and J.B. Lasky, J. Appl. Phys. 63 (5) pp. 1452-1463, March 1987.

- [14] G.J. Hu and R.H. Bruce, IEEE Trans. Elec. Dev., ED-32, pp. 584-588, March 1985.

- [15] A.J. Walker and P.H. Woerlee, European Solid State Device Research Conference, Tech. Dig. pp. 667 - 670 Sept. 1987.

- [16] A.J. Walker and P.H. Woerlee, J. Phys.Coll., vol. C4, pp. 265-268, Sept. 1988.

- [17] A.J. Walker, J. Appl. Phys. 71 (4) pp. 2033-2035, February 1992.

- [18] A.J. Walker, P.H. Woerlee, H.G. Pomp and N.E.B. Cowern, J. Appl. Phys. 73 (8) pp. 4048-4053, April 1993.

- [19] A.J. Walker and P.H. Woerlee, pp.29-32, Proc. 19<sup>th</sup> European Solid State Device Research Conference, Berlin, 1989.

- [20] A.J. Walker and J. Politiek, Appl. Phys. Lett., vol.63, pp.758-760, 1993.

# Chapter 2

# Inversion Layer Mobility

"And it would seem also, on a hasty view, that the attainment of as much as possible was the one goal of man's contentious life. And yet, as regards the spirit, this is but a semblance." R.L. Stevenson

### 2.1 Introduction

The mobility of charge carriers in MOS inversion layers is one of the most fundamental parameters for MOSFET device modeling. All the most important device characteristics such as source - drain current and switching time include the mobility in their expressions. For a full analysis of the MOSFET, the reader is referred to the literature [1]. In this chapter, a simple qualitative approach is given on MOSFET operation. In addition, the scattering mechanisms that affect charge carriers in the MOS inversion layer are described. Finally, the new MOSFET inversion layer mobility model based on effective normal field,  $E_{eff}$ , is presented.

## 2.2 MOSFET: Qualitative Approach

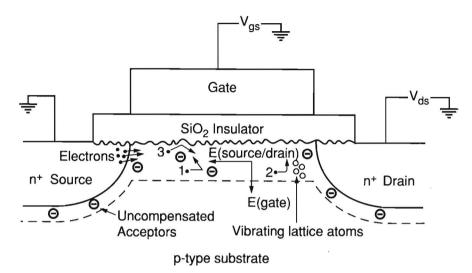

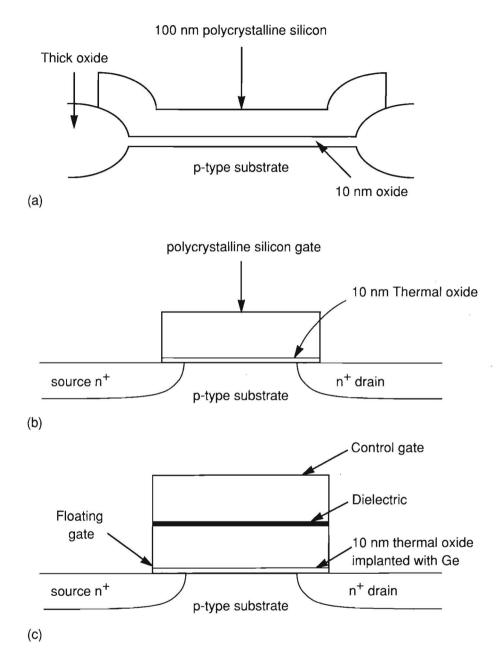

The structure of the silicon MOSFET has essentially remained the same since its inception with dimensions being reduced with time. A schematic cross section of an n-type MOSFET can be seen in figure 2.1

Figure 2.1. Schematic cross section of n-type MOSFET showing fields and scattering mechanisms acting on the mobile electrons in the inversion layer.

In this device, a silicon dioxide insulator separates the gate electrode from the n-type source and drain and the p-type substrate. In present day devices, the gate electrode is fabricated from polycrystalline silicon which is degenerately doped. The source and drain are selfaligned to this gate in the sense that the gate acts as a mask for source and drain implantation thus resulting in minimal gate to drain and gate to source capacitance. Also given in figure 2.1 are the fields affecting the movement of the electrons along with the scattering mechanisms that the electrons experience in the inversion layer. More information on these points is given later.

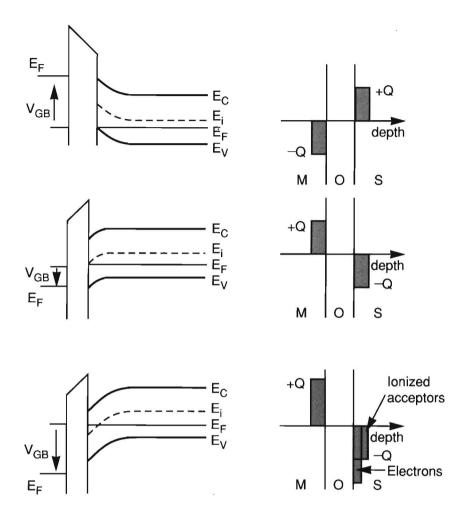

To change the band bending at the silicon - silicon dioxide  $(Si/SiO_2)$ interface, a voltage  $V_{GB}$  is applied between the gate and substrate electrodes. In this simple case, the source and substrate are both at ground potential. As  $V_{GB}$  is swept from negative values, through zero to positive values, the band bending at the  $Si/SiO_2$  interface changes from accumulation through depletion to inversion. These three cases are given in figure 2.2. This shows the band bending at the surface of the silicon as a function of depth in the channel region of a MOS transistor. The positions of the source and drain are therefore out of the plane of the paper. With a negative voltage on the gate with respect to the source and substrate, holes in the substrate are attracted to the surface forming an

Figure 2.2. Band bending at the surface of the silicon due to the application of a voltage on the gate electrode.

accumulation layer. As  $V_{GB}$  becomes less negative, the holes are driven from this layer with the band bending becoming less as shown in figure 2.2. At the flat band voltage condition between gate and substrate, the bands are literally flat with no net charge in the substrate.

As  $V_{GB}$  sweeps through zero to positive values, the band bending is in the opposite direction to the accumulation case. In the first instance, holes are pushed from the surface layer resulting in negatively charged uncompensated acceptors being present in the depletion layer. At still larger positive  $V_{GB}$  values, electrons are attracted to the surface coming primarily from the source electrode. The resulting inversion layer is a negatively charged conducting layer with mobile charge,  $Q_{inv}$ , due to these electrons. Since  $Q_{inv}$  is an exponential function of band bending at the silicon surface, band bending saturates as gate voltage increases. Effectively, the depletion region reaches a maximum depth into the silicon.

By applying a voltage,  $V_{DS}$ , now between source and drain, a current of electrons can be made to flow.

These are the essentials of the MOSFET.

## 2.3 Scattering Mechanisms

Charge carriers travelling from source to drain in a silicon inversion layer experience scattering of their motion due to various causes as is shown in figure 2.1. First, the uncompensated acceptors (for nMOS devices) or the uncompensated donors (for pMOS devices) are of the same charge type as the mobile inversion charge leading to Coulomb repulsion. This results in scattering. As the gate voltage increases leading to increased inversion, more mobile charge carriers are attracted into the channel region. This in turn leads to screening of the effect of the immobile donors or acceptors. Therefore, Coulomb scattering is important at low gate voltages and at high channel doping levels. Another more important source of Coulomb scattering is charges in interface states and in the gate oxide.

Second, bulk phonons and surface phonons (surfons) from the quantum vibrations of the crystal lattice scatter the mobile charge carriers.

Third, the interface between the crystal silicon and the gate oxide is not atomically smooth. This interface roughness scatters the mobile charge carriers. This effect becomes more important as the charge carriers are forced closer to this interface by increasing the gate voltage to increase the mobile inversion charge.

The net effect of all this scattering is seen in the effective mobility of the charge carriers moving from source to drain in the MOS inversion layer.

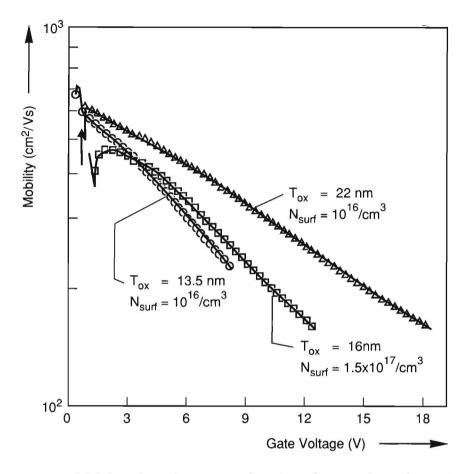

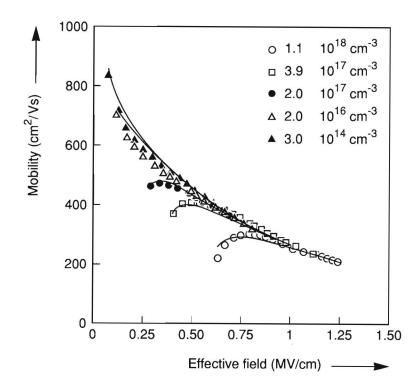

## 2.4 Inversion Layer Mobility

The scaling of MOS transistors towards the requisite submicron dimensions involves the use of thinner gate oxides, higher substrate doping and/or lower operating voltages. The goal of these changes is to increase the performance of the individual devices, but such changes may compromise the very performance they seek to enhance. Performance degradation can be seen by analysing the mobility of the charge carriers in the silicon inversion layer and how this is affected by gate oxide thickness, surface doping density and gate voltage. Figure 2.3 shows mobility degradation with gate voltage for scaled NMOS transistors with different gate oxide thicknesses and surface doping densities. The ability to model such effects is of great importance for device simulations which are necessary to direct actual experiments in silicon and thus reduce expenditure on these experiments.

As carriers travel from source to drain in an MOS transistor, they experience an electric field made up of two components. Firstly, a lateral contribultion due to the source - drain voltage and, secondly, a perpendicular component due to the gate voltage. Each component affects the carrier mobility in different ways. These electric fields are indicated for an NMOS in figure 2.1 in schematic detail.

This chapter presents a physically - based model for the perpendicular effective field dependence of the electron and hole mobilities in silicon inversion layers at low lateral fields. Recent results of an investigation into the application of this model to measurements carried out on MOS devices with gate oxide thicknesses and surface doping densities scaled for process generations down to  $0.5\mu$ m are given. Furthermore, for the first time such a model was incorporated in a two - dimensional device simulation program and comparisons between predictions from this program and measurements on submicron transistors are presented.

#### 2.4.1 Model

The modeling of the inversion layer mobility for applications in device simulation seems well established as evidenced by models from Yamaguchi [2] and Hiroki et al. [3]. Generally the local normal electric field is used to evaluate the influence of the normal field on the mobility. Such an approach is very attractive for applications in a device simulator. However, from a physical point of view it has several

Figure 2.3. Mobility degradation as a function of gate voltage for various n-type MOSFETs with different gate oxide thicknesses and surface doping densities. The source/drain voltage was 100 mV.

drawbacks. Firstly, since the normal field can vary strongly over the inversion layer thickness, appreciable variations of the mobility can occur over distances significantly smaller than the electron mean free path. More importantly, it has been shown elsewhere that the electron [4] and hole [5] mobilities follow universal curves when plotted as functions of an effective normal field,  $E_{eff}$ , given by

$$E_{eff} = \frac{1}{\epsilon_{si}} (Q_{dep} + \eta Q_{inv}) \tag{2.1}$$

with  $\eta = 1/2$  for electrons and 1/3 for holes and where  $Q_{dep}$  and  $Q_{inv}$  are the depletion and inversion layer charges per unit surface area respectively. This effective normal field can be regarded as the average normal field over the depth of the inversion layer.

In this new model a semi - empirical approach was taken to model the mobility -  $E_{eff}$  curves. It was assumed that the room temperature inversion layer mobility is dominated by three scattering mechanisms [6]:

- 1 Coulomb scattering

- 2 Carrier phonon scattering

- 3 Surface roughness scattering

Each has its own contribution to the net mobility. These contributions are designated by  $\mu_c$ ,  $\mu_{cp}$  and  $\mu_{sr}$  respectively. Actual modelling of scattering processes in inversion layers is very complex due to the quantum mechanical nature of these processes and the fact that at temperatures above absolute zero more than one sub - band is filled. Therefore, a simplified semi - empirical approach was adopted as a pragmatic step towards obtaining a fitting model. The three scattering processes are schematically shown in figure 2.1.

To obtain a simple first order expression for carrier mobility due to screened Coulomb scattering, the Brooks - Herring formula was adopted [7]:

$$\mu_c = \frac{CT^{1.5}}{\ln(1+b) - b/(1+b)} \cdot \frac{1}{N_I}$$

(2.2)

where  $b = (24m^*\epsilon_{Si}k^2T^2)/(\hbar^2q^2N_o)$ ,  $N_I$  is the charged impurity density,  $N_o$  is the mobile carrier density, C is a constant,  $\epsilon_{Si}$  is the dielectric constant of silicon and the other symbols have their usual meanings.

However, the following modifications were made for the inversion layer :

$$N_o = n_{inv} / \langle z \rangle \tag{2.3}$$

CHAPTER 2

$$N_I = N_I^1 + N_{ox} / \langle z \rangle$$

(2.4)

where  $n_{inv}$  is the number of mobile carriers per unit surface area,  $\langle z \rangle$  is the average distance of mobile carriers from the  $Si/SiO_2$ interface,  $N_{ox}$  is the fixed oxide charge per unit surface area and  $N_I^1$  is the actual charged impurity density due to uncompensated donors or acceptors.

As a result of numerical calculations [8],  $\langle z \rangle$  can be given as a function of the mobile inversion charge number density per unit surface area,  $n_{inv}$ , and therefore as a function of  $E_{eff}$ .

For carrier - phonon scattering, the prediction from theory (see [9] and references therein) is

$$\mu_{cp} \approx a T^{-1} (Q_{inv}/3 + Q_{dep})^{-\frac{1}{3}}$$

(2.5)

Surface roughness scattering, according to theory (see references in [9]), obeys the following relation :

$$\mu_{sr} = b(Q_{inv}/2 + Q_{dep})^{-2} \tag{2.6}$$

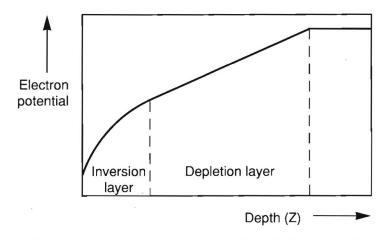

These two equations for  $\mu_{cp}$  and  $\mu_{sr}$  can be reformulated as functions of the effective perpendicular field,  $E_{eff}$  by considering Gauss's Law in one dimension. Reference is made to figure 2.4 which shows electron potential plotted as a function of depth into the silicon. Using Gauss's Law at the surface of the inversion layer, it can be seen that the field at the surface is

$$E_{surf} = \frac{1}{\epsilon_s} (Q_{inv} + Q_{dep}) \tag{2.7}$$

while at the inversion layer/depletion layer interface, it is

$$E_{dep} = \frac{Q_{dep}}{\epsilon_s} \tag{2.8}$$

These are of course the gradients of the curve in figure 2.4 at the respective depths. Therefore, the average of these two fields is defined as the effective normal field,  $E_{eff}$ , and is given as

$$E_{eff} = \frac{1}{\epsilon_s} \left( \frac{Q_{inv}}{2} + Q_{dep} \right) \tag{2.9}$$

Figure 2.4. Electron potential as a function of depth from the silicon/silicon dioxide interface through the inversion and depletion layers.

Therefore, we have

$$\mu_{cp} = k_{cp} T^{-1} E_{eff}^{-1/3} \tag{2.10}$$

and

$$\mu_{sr} = k_{sr} E_{eff}^{-2} \tag{2.11}$$

where  $k_{cp}$  and  $k_{sr}$  are constants.

The net mobility  $\mu$  is calculated using Matthiesen's rule. i.e.

$$\frac{1}{\mu} = \frac{1}{\mu_c} + \frac{1}{\mu_{cp}} + \frac{1}{\mu_{sr}}$$

(2.12)

with  $\mu_c$ ,  $\mu_{cp}$  and  $\mu_{sr}$  given in equations 2, 5 and 6 respectively with the constants C,  $k_{cp}$  and  $k_{sr}$  as adjustable parameters.

The above equations were incorporated into a two - dimensional device simulation program, CURRY [10], in which the effective field at any point from source to drain was calculated by averaging the normal field in the depth direction over the inversion layer or surface accumulation layer at that point. In other words, the following approximation is used for the calculation of the effective field :

$$E_{eff}(x) = \int_0^d n(x, y) E_y(x, y) dy / Q_{inv}(x)$$

(2.13)

where d is the thickness of the inversion layer and x is the lateral coordinate from source to drain. The model is therefore a non - local one with the mobility at any point dependent on the values of the normal electric field at other points. This contrasts with the approach used in some device simulators where the effective mobility at the point (x,y) is determined by the value of the normal electric field,  $E_y(x,y)$ , at that point.

#### 2.4.2 Mobility Measurement

In order to exclude possible two- dimensional effects playing an important role, the mobility at small lateral source - drain fields was extracted from measurements on large MOS transistors. If a small source - drain voltage,  $V_{ds}$ , is applied to such a device and the gate - source voltage,  $V_{gs}$ , is varied (the substrate is shorted to the source), then a certain source - drain current,  $I_{ds}$  will flow. In this case, the low lateral field mobility is given as

$$\mu = \frac{I_{ds}}{\frac{W}{L}V_{ds}Q_{inv}} \tag{2.14}$$

where  $I_{ds}$  is the current from source to drain, W and L are the width and length of the transistor respectively,  $V_{ds}$  is the source - drain voltage, and  $Q_{inv}$  is the mobile inversion charge per unit surface area.

In most approaches, the mobile inversion charge,  $Q_{inv}$ , is approximated by

$$Q_{inv} = C_{ox}(V_{gs} - V_T) \tag{2.15}$$

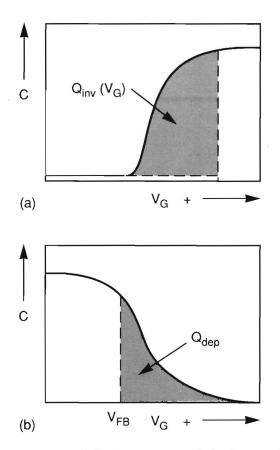

where  $C_{ox}$  is the transistor's oxide capacitance per unit surface area,  $V_{gs}$  is as above and  $V_T$  is the transistor's threshold voltage [11]. This expression is fairly accurate at gate - source voltages much larger than the threshold voltage. However, at gate - source voltages near threshold, uncertainty arises. This is due to the fact that this expression assumes, in contrast to reality, that there are no mobile charges at the surface at voltages below threshold. This approximation can be removed by actually measuring  $Q_{inv}$  on capacitor structures [12]. In addition, the measurement of the immobile depletion charge per unit surface area,  $Q_{dep}$ , can also be determined using capacitor structures. Since  $Q_{inv}$  and  $Q_{dep}$  are crucial to the model, a short description of how these are measured follows.

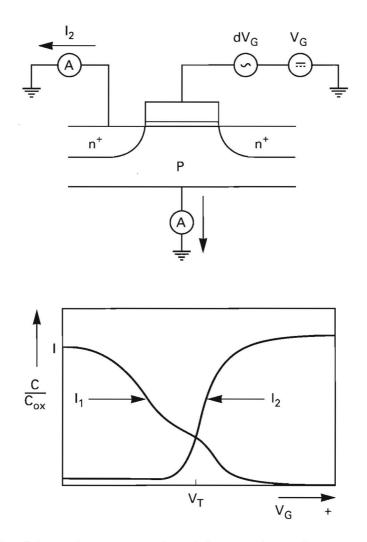

$Q_{inv}$  and  $Q_{dep}$  are determined using the so-called "split" capacitance - voltage method [13]. A schematic representation of the experimental set-up for this measurement in the case of electron mobility is given in figure 2.5. The main point to note is that separate measurements are made of the source-drain and bulk contributions to the gate capacitance as a function of gate voltage. The d.c. gate voltage,  $V_G$ , is ramped from a negative value through threshold to a positive value so that the silicon surface changes from being strongly accumulated with holes to being strongly inverted with electrons having passed through depletion on the way.

Superimposed on the d.c. gate voltage is a small a.c. signal,  $dV_G$ , which produces the displacement currents,  $I_1$  and  $I_2$  shown in figure 2.5. When the silicon surface is in strong accumulation, the density of holes at and near the  $Si/SiO_2$  interface is very large and any small signal variation in this density due to the small gate signal,  $dV_G$ , is recorded as a change in  $I_1$ . That is, the holes are considered to come exclusively from the substrate,  $I_1$  being the hole current. In strong inversion, electrons are the majority carriers at the surface and any variation in their density due to  $dV_G$  is recorded as a change in  $I_2$ . That is, the electrons are considered to come exclusively from the  $n^+$  regions bounding the channel. By making the assumption that, throughout the gate voltage sweep, electrons are supplied to the interface region exclusively by the  $n^+$  regions, and holes by the substrate, these separate contributions to the gate capacitance can be independently monitored, as can be seen in the graph in figure 2.5.

$$I_1 = rac{dQ_{dep}}{dt}$$

and  $I_2 = rac{dQ_{inv}}{dt}$

which, of course, means:

$$I_1 = \frac{dQ_{dep}}{dV_G} \frac{dV_G}{dt} \quad and \quad I_2 = \frac{dQ_{inv}}{dV_G} \frac{dV_G}{dt}$$

Since  $I_1$  and  $I_2$  are measurable quantities and  $dV_G/dt$  is known, the quantities  $dQ_{dep}/dV_G$  and  $dQ_{inv}/dV_G$  can be calculated. The latter two quantities are, in effect, the hole and electron contributions respectively to the small-signal capacitance of the gate-earth system. As can be seen

Figure 2.5. Schematic representation of the experimental set-up to measure electron mobility.

from the graph in figure 2.5,  $I_2$  has a constant non-zero value, even in the accumulation region. This is due to the fact that the  $n^+$  regions overlap the gate due to diffusion. This produces a parasitic capacitance since the electrons in these regions can faithfully follow a gate signal even when the channel is in accumulation, thus giving rise to a non-zero  $I_2$ .

Figure 2.6. Measurement of the inversion and depletion charges from the measured capacitance-voltage curves.

Figure 2.6 shows how  $Q_{inv}$  is found as a function of  $V_G$ . From monitoring  $I_2$ , the capacitance due to the electron contribution can be plotted as a function of  $V_G$ . The background parasitic capacitance, mentioned above, is then subtracted and the resulting curve can be integrated to give  $Q_{inv}(V_G)$ .

After the silicon surface has reached strong inversion, the depletion charge per unit surface area,  $Q_{dep}$ , can be considered to have reached its maximum value which remains constant in inversion. As indicated in figure 2.6, the hole contribution to the total capacitance per unit surface area is integrated from the flat-band voltage,  $V_{FB}$ , to large positive  $V_G$ to give  $Q_{dep}$ .

Figure 2.7. Electron mobility as a function of effective field for various surface doping concentrations with the gate oxide thickness at 14 nm for all samples.

Using the above techniques, the mobility can be directly measured as a function of gate voltage on the MOSFET. However,  $Q_{inv}$  and  $Q_{dep}$ are also known as functions of gate voltage from the capacitance measurements. Therefore, the mobility can be expressed as a function of these charges and as a function of the effective normal field,  $E_{eff}$  as required.

#### 2.4.3 Results

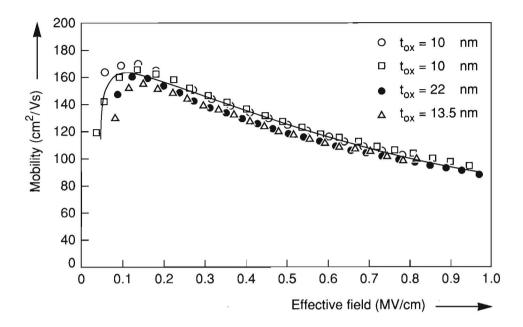

The results from mobility measurements on the large n- and p-MOS devices are given in figures 2.7 and 2.8 respectively in which mobility is plotted as a function of normal effective field.

The surface doping density,  $N_s$ , and gate oxide thickness,  $t_{ox}$  are also shown in the figures. The points are the experimental data with the solid lines being the fits of the model to these data. Figure 2.7 shows

Figure 2.8. Hole mobility as a function of effective field for various gate oxide thicknesses.

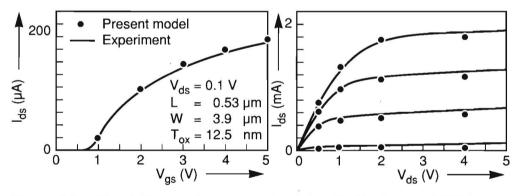

Figure 2.9. Simulations and experimental data of half-micron n-MOS transistors.

that the electron mobility in the inversion channel is almost independent of surface doping density at high effective fields but depends strongly on the doping at lower fields. In the case of the pMOS devices, different boron implants had been introduced into the originally n-type substrate but it was not clear as to what the actual density of charged impurities would be since the impurities are not completely ionized.

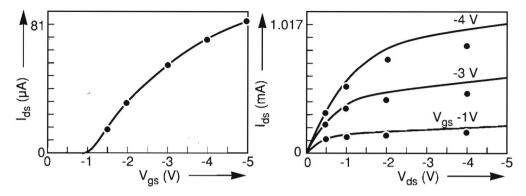

Figure 2.10. Simulations and experimental data of half-micron p-MOS transistors.

It was apparent in the model for electrons that the same values for C (equ.2),  $k_{cp}$  (equ.10) and  $k_{sr}$  (equ.11) could be used for all samples provided that the surface doping density,  $N_I$ , and the oxide fixed charge,  $N_{ox}$ , were known. The values used in figure 2.7 were  $C = 2.63 \times 10^{17}$ ,  $k_{cp} = 1.35 \times 10^7$  and  $k_{sr} = 7.0 \times 10^{14}$  all expressed in cgs units.

In the model for holes, the value of  $N_I$  was unknown. Therefore a fit was carried out to find the optimum value of  $C/(N_I + N_{ox}/\langle z \rangle)$  using fixed values of  $k_{cp}$  and  $k_{sr}$ . This was 0.225 for  $k_{cp} = 3 \times 10^6$  and  $k_{sr} = 2.22 \times 10^{14}$  all in cgs units. This is the solid line in figure 2.8

The mobility model as described was tested by modeling transistor charcateristics. Figure 2.9 shows simulations of a half-micron n-MOS transistor together with experimental data.

Good agreement between the calculated and experimental data is observed. Similar data for a buried channel p-MOS transistor are shown in figure 2.10. The  $I_{ds} - V_{gs}$  characteristics at low  $V_{ds}$  are modelled well but systematic deviations in the  $I_{ds} - V_{ds}$  characteristics at high drain bias suggest that the lateral - field model for holes is not sufficiently accurate at high lateral fields. The mobility model presented above is based on measurements on very large transistors. Clearly, application of the model to submicron devices leads to deviations which are not taken into account in the model itself.

## 2.5 Discussion and Conclusions

With the simple three parameter mobility model presented above, a large amount of experimental data can be modeled. It's incorporation in a device simulator has led to predictions of  $0.5\mu$ m MOS transistor behaviour in reasonable agreement with experiment. As was seen, the modelling of hole mobility and its subsequent use in simulating PMOS current-voltage curves were less accurate than for the electron mobility and NMOS case. Future work should concentrate on hole mobility and, in particular, on the "surface channel device" where the gate polysilicon has been doped p-type by incorporation of boron. This will become the device of choice for PMOS transistors in the deep submicron regime due to the ease in making low threshold devices for low power applications (see Chapter 4). The model should be tested against the newest devices in the laboratory which have gate lengths below  $0.25\mu$ m.

In the time between the appearance of the original articles [14], [15], and this dissertation, many articles have appeared along similar lines as proposed here. [16], [17], [18], [19], [20], [21], [22].

The newest most comprehensive approach can be found in [23] where an identical approach was taken regarding the effective inversion layer mobility as a Matthiesen's summation of three component mobilities due to screened Coulomb scattering, carrier-phonon scattering and surface roughness scattering. Reference was also made by the authors to the original articles by Walker and Woerlee. This confirms the approach taken here. A paper examining the effects of high substrate doping on threshold voltage and inversion layer mobility of deep-submicron MOS-FETs using the original approach in [15] was published recently [24].

### 2.6 References

- "Physics of Semiconductor Devices", by S.M. Sze, 2nd ed., Wiley-Interscience, New York 1981.

- [2] K. Yamaguchi, IEEE Trans. Electron Devices, vol.ED-26, pp. 1068-1074, Jul. 1979.

- [3] A. Hiroki, S. Odanaka, K. Ohe and H. Esaki, IEEE Electron Device Lett., Vol.EDL-8, pp. 231-233, May 1987.

- [4] A.G. Sabnis and J.T. Clemens, IEDM Tech. Dig., pp. 18-21, Dec.1979.

- [5] J.T. Watt and J.D. Plummer, Symp. on VLSI tech., pp. 81-82, 1987.

- [6] Y.C. Cheng and E.A. Sullivan, J. Appl.Phys., Vol.44, No.8, pp.3619

3625, Aug. 1973.

- [7] T. Sugano, K. Hoh, H. Sakaki, T. Iizuka, K. Hirai, K. Kuroiwa and K. Kakemoto, in J. of Faculty of Engineering, Univ. of Tokyo (B) XXXII, 155, Appendix F, pp. 362-363 1973.

- [8] J.A. Pals, Ph.D Thesis, Technical Univ. of Eindhoven, Dec. 1972.

- [9] T. Ando, A.B. Fowler and F. Stern, Rev. of Modern Physics, 54, p.437 1982.

- [10] S.J.Polak, C. den Heijer, W.H.A. Schilders and P. Markowich, in Int. J. for Num. Meth. in Eng., Vol.24, pp. 763-838, April 1987.

- [11] "Device Electronics for Integrated Circuits", by R.S. Muller and T.I. Kamins, John Wiley and Sons, 1977.

- [12] C.G. Sodini, T.W. Ekstedt and J.L. Moll, Solid-State Electronics, vol.25, pp. 833-841, Sept. 1982.

- [13] J. Koomen, Solid State Electronics, 16, p.801, 1973.

- [14] A.J. Walker and P.H. Woerlee, ESSDERC Tech. Dig. pp. 667 670 Sept. 1987.

- [15] A.J. Walker and P.H. Woerlee, J. Phys.Coll., vol. C4, pp. 265-268, Sept. 1988.

- [16] W. Hansch, R. Kircher, T. Vogelsang and M. Orlowski, Solid-State Elect., vol.32, pp.839-849, Oct. 1989.

- [17] A. Hairapetian, C.R. Viswanathan and D. Gitlin, IEEE Trans. Elect. Dev., ED-36, pp.1448-1455, Aug. 1989.

- [18] S. Selberherr, W. Hansch, M. Seavey and J. Slotboom, Solid-State Elect., vol.33, pp.1425-1436, Nov. 1990.

- [19] M. Schubert, B. Hofflinger and R.P. Zingg, IEEE Elect. Dev. Lett., EDL-12, pp.489-491, Sept. 1991.

- [20] V.M. Agostinelli, G.M. Yeric and A.F. Tasch, IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems, vol.12, pp.439-445, March 1993.

- [21] C.A. Dimitriadis, J. Stoemenos, P.A. Coxon, S. Friligkos, J. Antonopoulos and N.A. Economou, J. Appl. Phys., vol.73, pp. 8402-8411, 1993.

- [22] H.S. Wong, Solid-State Elect., vol.36, pp. 179-188, Feb. 1993.

- [23] V.M. Agostinelli, H. Shin and A.F. Tasch, IEEE Trans. Elec. Dev., vol.ED-38, pp. 151-159, Jan. 1991.

- [24] M.J. van Dort, P.H. Woerlee, A.J. Walker, C.A.H. Juffermans and H. Lifka, IEEE Trans. Elec. Dev., vol.ED-39, pp. 932-938, April 1992.

30

.

## Chapter 3

## Shallow Implanted Boron Junctions

"There is always a new horizon for onward-looking men, and although we dwell on a small planet, immersed in petty business and not enduring beyond a brief period of years, we are so constituted that our hopes are inaccessible, like stars, and the term of hoping is prolonged until the term of life."

$R.L.\ Stevenson$

## 3.1 Introduction

Ion implantation has replaced solid-state diffusion as the preferred method of introducing dopants into silicon. A very accurately controlled amount of dopant can be introduced in this way. Since the implantation is carried out at crystal temperatures where dopant diffusion is negligible, very shallow profiles close to the crystal surface are possible. With the continued miniaturisation of silicon devices and the demand for tight control in electrical parameters, ion implantation has become an indispensable tool in very large scale integrated circuit manufacture.

The depth penetration of the ions is determined by the energy of the ions and the rate at which they lose energy to the crystal lattice. This loss is caused by electronic and nuclear scattering. At high ion velocities, electronic interactions are predominant with very few nuclear - ion interactions. As the ions slow down, nuclear scattering takes over as the main mechanism. This results in displacements of silicon atoms from their lattice sites. In other words, most silicon displacement takes place at the ion's end of range. This illustrates one of the problems of ion implantation. The method introduces defects into the silicon crytal since as little as 30 eV is sufficient to displace a silicon atom from its lattice site. These resultant silicon "self-interstitials" are a problem on two counts. First, they can coalesce to form extended defects which may lead to large parasitic leakage currents if they are situated in charge depletion layers. Second, they can interact with implanted dopant atoms leading to enhanced dopant diffusion. A third problem encountered with light ion implantation is known as "channeling" in which the ion is guided into various crystal directions and experiences far fewer retarding interactions thus leading to deeper profiles than desired. This chapter is concerned primarily with an investigation of these three effects.

The first section deals with the fabrication of shallow boron junctions using a technique known as "preamorphization" where the surface of the silicon crystal is intentionally made amorphous using a relatively heavy ion prior to the implantation of the boron. This suppresses the channeling of the boron. The heavy ion implantation however leads to silicon displacement which in turn can form large extended defects and can cause enhanced boron diffusion. The requirements for shallow, low leakage junctions using preamorphization will be presented.

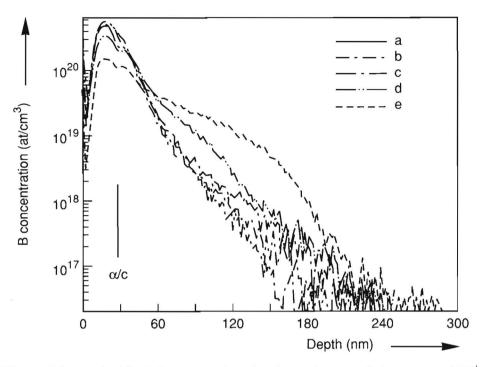

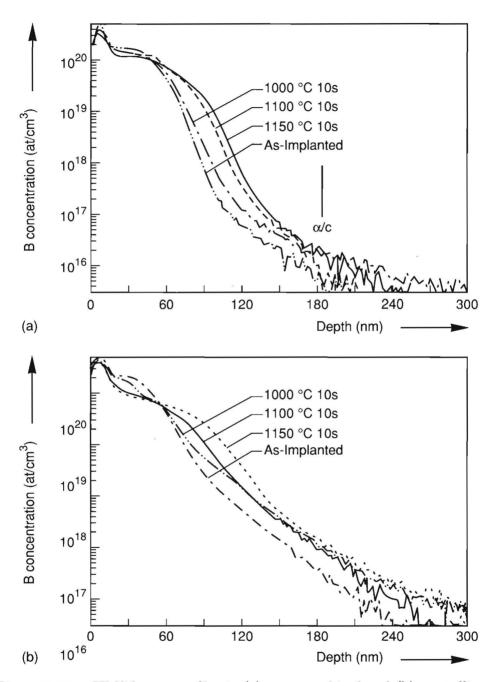

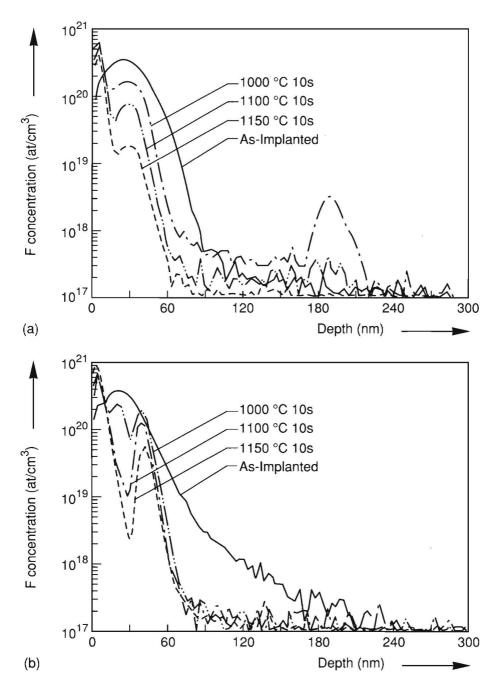

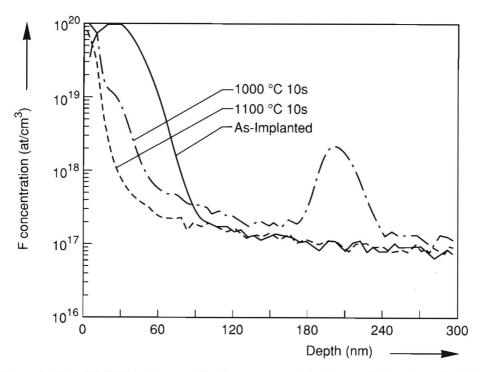

The second section concentrates on the diffusion of boron in this amorphous layer. In particular, the boron was introduced by implantation of boron diffuoride and the effect of the fluorine on the boron diffusion is shown during high temperature rapid thermal annealing.

## 3.2 Preamorphization

The lateral and vertical scaling of metal-oxide-semiconductor fieldeffect transistor devices for very large scale integrated circuits requires the fabrication of very shallow junctions to avoid short-channel effects. The greatest challenge arises in the fabrication of shallow  $p^+$ -n junctions, since these require the use of B which tends to channel during low energy implantation and has too low an atomic mass to amorphize the silicon at doses of practical interest. Channeling results in relatively deep penetration of the implanted B in the silicon substrate [1], [2]. The non-amorphous nature of the silicon substrate after B implantation requires the use of higher annealing temperatures to activate the dopant and remove the implantation damage [3] which, in turn, leads to considerable boron diffusion into the depth of the silicon substrate. Further problems, leading to a deepening of the  $p^+$ -n junction, arise due to anomalous enhanced diffusion of B during implant damage repair [4], [5], [6], [7] in which dopant diffusivities can be enhanced by several orders of magnitude during the initial stages of the thermal anneal.

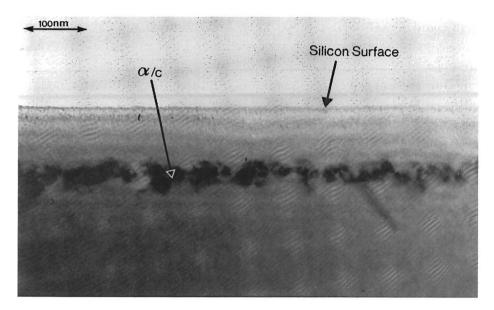

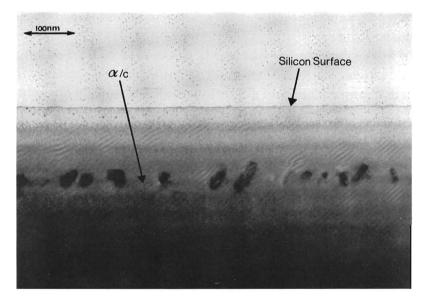

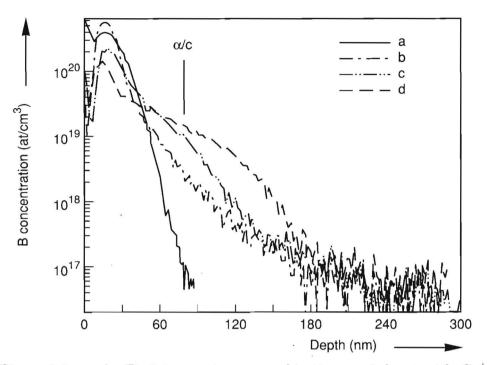

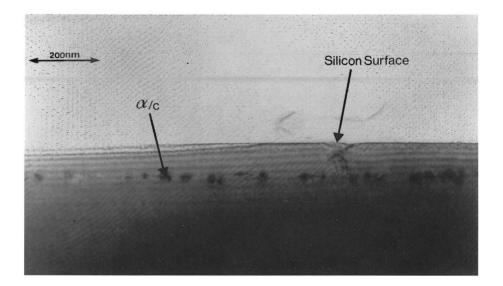

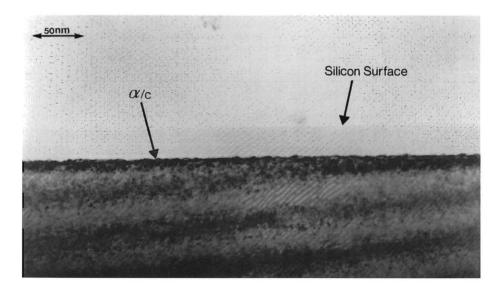

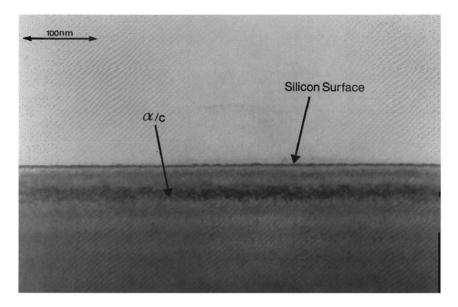

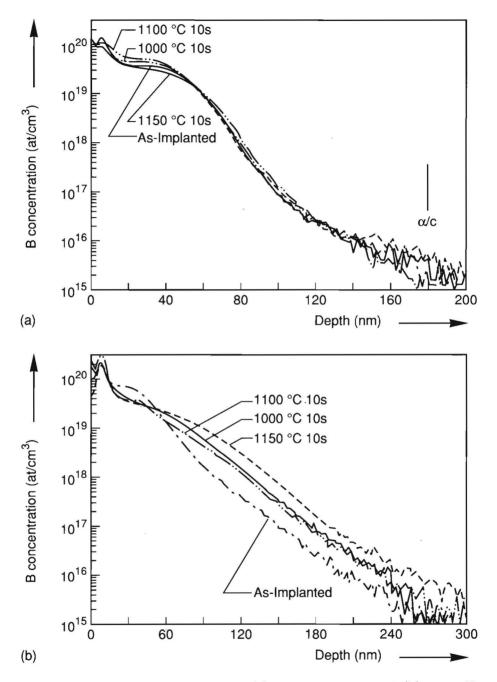

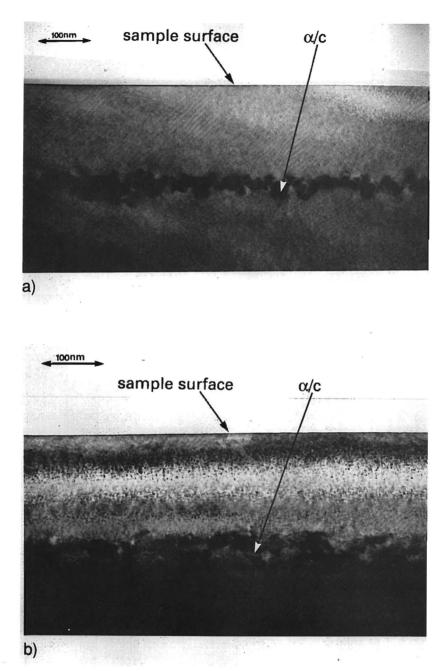

These difficulties have led to the study of shallow  $p^+-n$  junction fabrication using preamorphization by heavy ion implantation. Numerous studies have been carried out using different heavy ions such as Si<sup>+</sup>  $[10], [11], Sn^+ [12], Ar^+ [13], Ga^+ [14] [15] In^+ [16], Ge^+ [17],$ [18], [19], [20] and Sb<sup>+</sup> [21]. The resulting amorphous layer close to the silicon surface suppresses the channeling of the implanted B ions. The layer can be regrown by solid phase epitaxy at temperatures as low as 550°C resulting in very little B diffusion and high electrical activity. Unfortunately, however, the regrowth generates extended defects located at the position of the previous amorphous-crystalline  $(\alpha/c)$  interface which can result in very high junction leakage [19], [22]. The position of the junction depletion layer in relation to this defect band is therefore critical. As the reverse bias is increased, the depletion layer extends further into the lightly doped substrate than into the heavily doped  $p^+$  region, and it is therefore advantageous to position the defects within the  $p^+$  region. However, B diffusion in the region beyond the defect band has been seen to be enhanced [19] due to the supersaturation of silicon interstitials in this region, while diffusion between the defect band and the silicon surface is relatively little affected [7], [8]. Therefore, to satisfy leakage requirements, one of two approaches can be taken: (i) the B has to be implanted within the preamorphized silicon layer and diffused through the defect band, with minimal transient enhanced diffusion because the interstitial supersaturation in the region beyond the defect band only occurs at short times, before the dopant has entered this region; or (ii) the thermal annealing during the fabrication process must completely remove the implantation-induced defects.

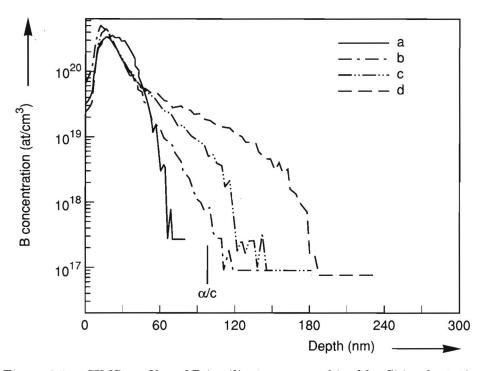

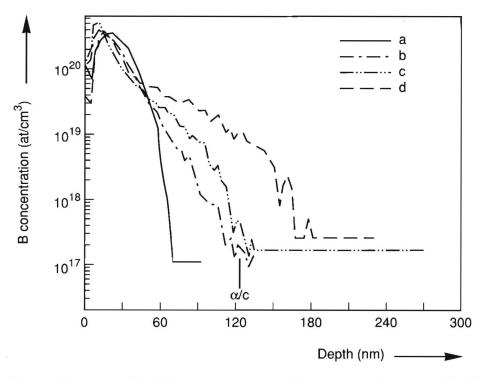

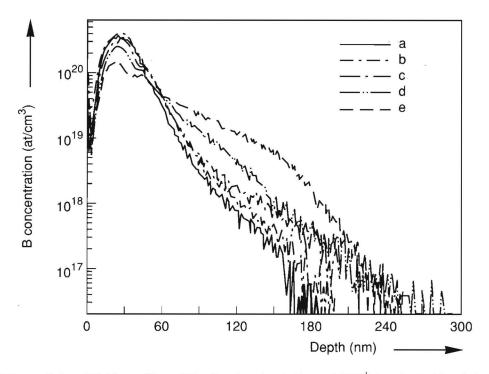

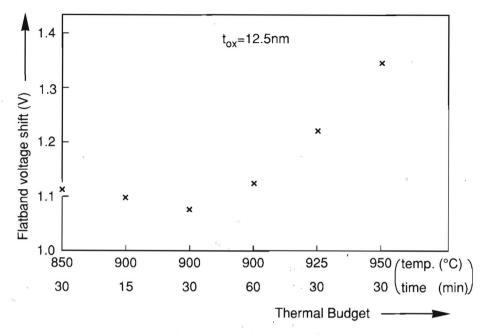

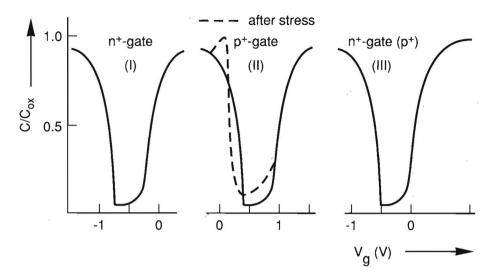

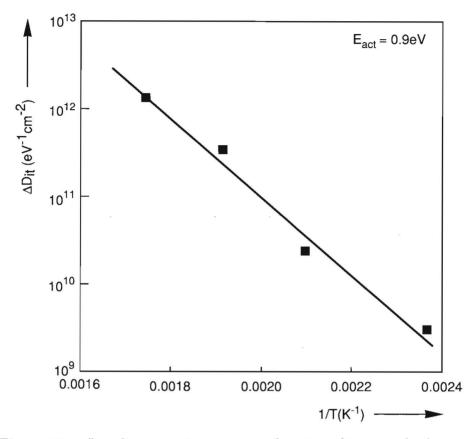

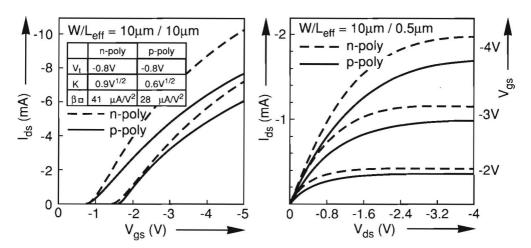

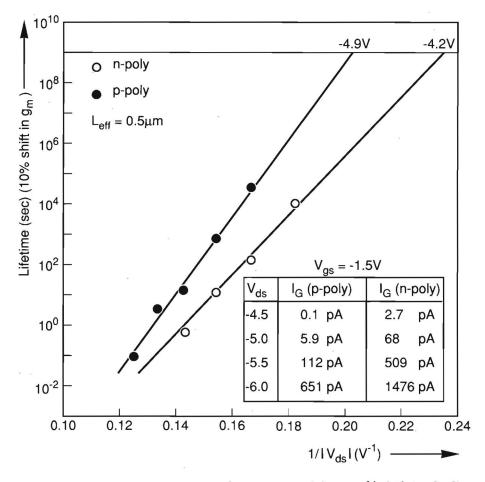

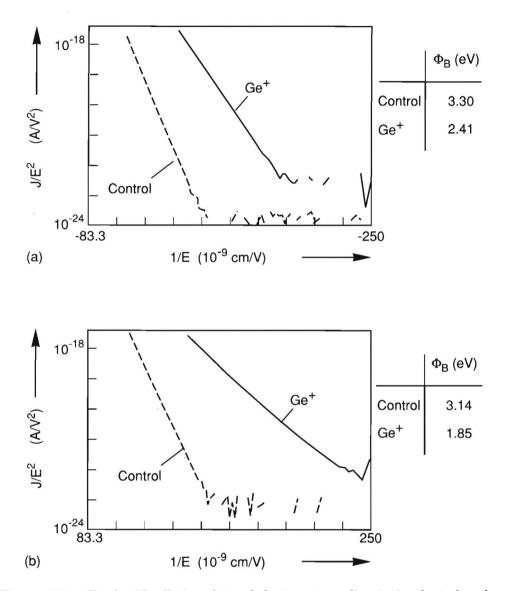

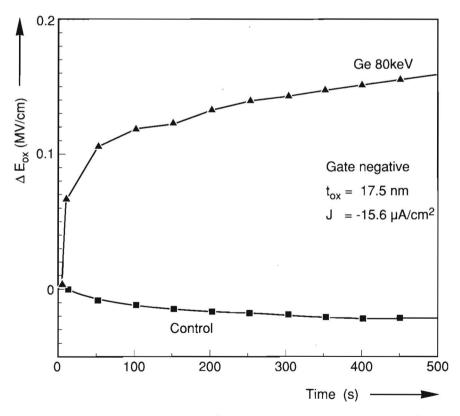

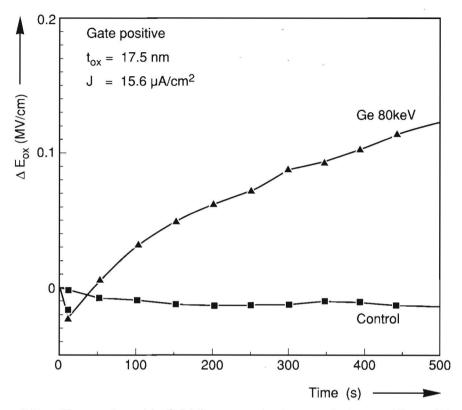

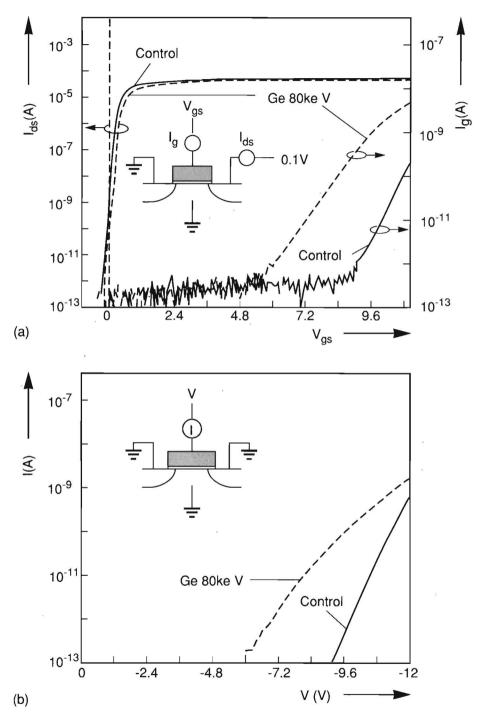

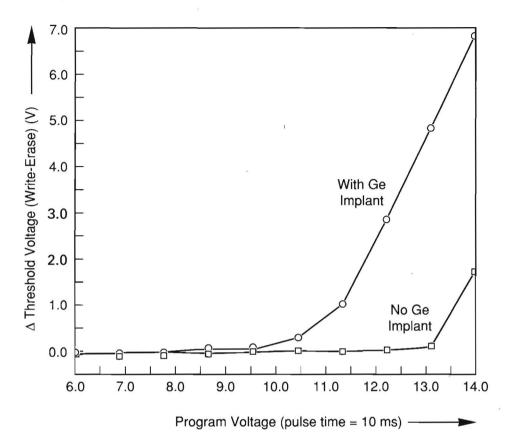

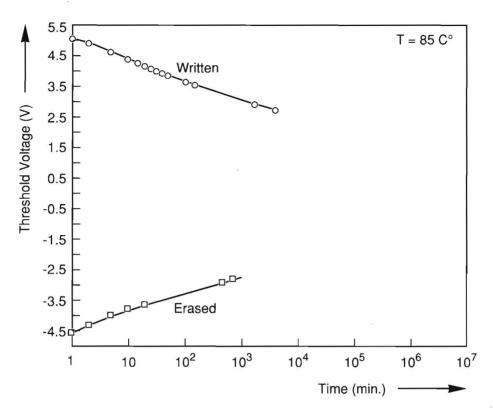

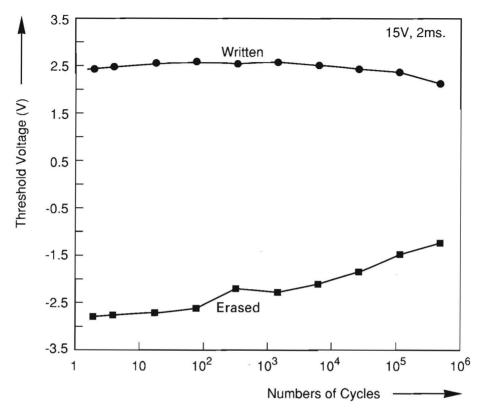

Since thermal budgets are decreasing as transistors decrease in size, the latter approach is becoming difficult to maintain. Therefore, the former approach has been studied here to investigate conditions for ideal junction behaviour. Structural and electrical properties of shallow junctions formed by implanting  $BF_2^+$  into crystal silicon or into silicon preamorphized by either Si<sup>+</sup> or Ge<sup>+</sup> have been investigated [9]. The position of the junction has been varied by furnace annealing at 850°C for different times with the resultant leakage currents and forward bias ideality factors being measured.