# Verification of electronic designs by reconstruction of the hierarchy

#### Citation for published version (APA):

Kostelijk, A. P. (1994). Verification of electronic designs by reconstruction of the hierarchy. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR421686

DOI: 10.6100/IR421686

#### Document status and date:

Published: 01/01/1994

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

• A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

• The final author version and the galley proof are versions of the publication after peer review.

• The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

#### Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

# Verification of electronic designs by reconstruction of the hierarchy

A.P. Kostelijk

# Verification of electronic designs by reconstruction of the hierarchy

A.P. Kostelijk

The work described in this thesis has been carried out at the PHILIPS RESEARCH LABORATORIES at Eindhoven, the Netherlands, as part of the Philips Research programme.

CIP-gegevens Koninklijke Bibliotheek, Den Haag

Kostelijk, A.P.

Verification of electronic designs by

reconstruction of the hierarchy

Proefschrift Technische Universiteit Eindhoven,-Met lit. opg.,

-Met samenvatting in het Nederlands.

ISBN 90-74445-14-4

Trefw.: IC-ontwerp, verificatie, patroonherkenning, algorithme

©Philips Electronics N.V. 1994 All rights are reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

# Verification of electronic designs by reconstruction of the hierarchy

### Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr. J.H. van Lint, voor een commissie aangewezen door het College van Dekanen, in het openbaar te verdedigen op woensdag 28 september 1994 te 16.00 uur

$\operatorname{door}$

# Anton Pieter Kostelijk

Geboren te Grootschermer

Dit proefschrift is goedgekeurd door de promotoren prof.dr.Ing. J.A.G. Jess en prof.dr.ir. W.M.G. van Bokhoven.

## Acknowledgements

This work was performed at the IC-design Centre, Philips Research Laboratories Eindhoven, since 1985. Many people have contributed to this work. In particular I owe a lot to the following persons.

The management of the IC-design Centre, especially groupleader Gerard Beenker, his predecessor Leo Nederlof, and former director Theo Claasen, for giving me the opportunity and support to perform this work.

Guido Schrooten for being the co-initiator of Vera, and for major contributions to the initial Vera setup.

Brian Lynch and Paul Kuppen († 1992) for sharing their talents with me for many years, and creating major parts, manuals and applications.

Bart De Loore, our "super user", for his questions, discussion, enthousiasm, innovative Vera usage, and joint publications.

Johan Jonkheid for his initiative and endurance power to set up the Vera support team.

Andries van der Veen, René Segers and Marc Verra for their contributions.

Furthermore, I thank all users for their interest in my work and their criticism.

I thank all current and former members of the IC-design Centre and the excellent system support team for a pleasant and cooperative atmosphere.

The following people have given substantial feedback on drafts of this thesis: Prof. J.A.G. Jess, Prof. E.H.L. Aarts, Prof. W.M.G. van Bokhoven, Prof. P.M. Dewilde, Gerard Beenker, André Slenter, Simon Thorn.

Finally, I am grateful to my wife, Elly Vogelzang, for her support and encouragement.

# Contents

| 1 | Introduction                         |                                                     |    |  |  |  |  |

|---|--------------------------------------|-----------------------------------------------------|----|--|--|--|--|

|   | 1.1                                  | IC-design, synthesis and verification               | 1  |  |  |  |  |

|   | 1.2                                  | Trends in IC-design                                 |    |  |  |  |  |

|   | 1.3                                  | High level design and layout design                 | 4  |  |  |  |  |

|   | 1.4                                  | Hierarchy reconstruction                            | 7  |  |  |  |  |

| 2 | Literature on structure verification |                                                     |    |  |  |  |  |

|   | 2.1                                  | Structure verification methods                      | 11 |  |  |  |  |

|   |                                      | 2.1.1 Simulation                                    | 11 |  |  |  |  |

|   |                                      | 2.1.2 Functional abstraction                        | 13 |  |  |  |  |

|   |                                      | 2.1.3 Netlist comparison                            | 14 |  |  |  |  |

|   | 2.2                                  | Literature on structure recognition                 | 18 |  |  |  |  |

|   |                                      | 2.2.1 Rule-based systems                            | 19 |  |  |  |  |

|   |                                      | 2.2.2 Other systems                                 | 20 |  |  |  |  |

|   | 2.3                                  | Conclusion                                          | 22 |  |  |  |  |

| 3 | The hierarchy reconstruction method  |                                                     |    |  |  |  |  |

|   | 3.1                                  | Introduction                                        | 23 |  |  |  |  |

|   | 3.2                                  | Hierarchy and structure parameters                  | 24 |  |  |  |  |

|   | 3.3                                  | The operational model                               | 29 |  |  |  |  |

| 4 | The                                  | sub-circuit recognizer                              | 33 |  |  |  |  |

|   | 4.1                                  | Introduction                                        | 33 |  |  |  |  |

|   | 4.2                                  | Definitions                                         | 34 |  |  |  |  |

|   |                                      | 4.2.1 General notions and notation                  | 34 |  |  |  |  |

|   |                                      | 4.2.2 The circuit definition                        | 36 |  |  |  |  |

|   |                                      | 4.2.3 The sub-circuit recognition problem           | 40 |  |  |  |  |

|   |                                      | 4.2.4 The internal data representation of a circuit | 45 |  |  |  |  |

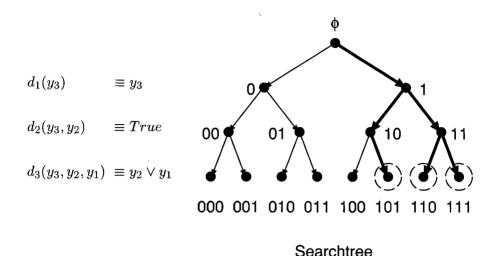

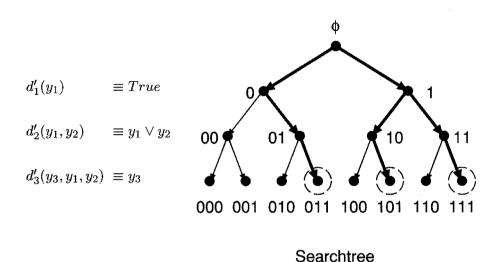

|                 | 4.3  | The pr  | mary algorithm: backtracking                                 | 47         |  |  |

|-----------------|------|---------|--------------------------------------------------------------|------------|--|--|

|                 |      | 4.3.1   | The brute-force approach                                     | 47         |  |  |

|                 |      | 4.3.2   | Backtracking in general                                      | 48         |  |  |

|                 |      | 4.3.3   | Backtracking and sub-circuit recognition                     | 54         |  |  |

|                 |      | 4.3.4   | The decomposition of the sub-circuit recognition prob-       |            |  |  |

|                 |      |         | lem                                                          | 57         |  |  |

|                 |      | 4.3.5   | Search tree traversal                                        | 63         |  |  |

|                 |      | 4.3.6   | Finding a candidate set for a demand                         | 65         |  |  |

|                 |      | 4.3.7   | The ordering of a search list                                | 71         |  |  |

|                 |      | 4.3.8   | The first search list element                                | 74         |  |  |

|                 |      | 4.3.9   | Ordering the rest of the search list                         | 79         |  |  |

|                 |      | 4.3.10  | The iterative search list generation algorithm               | $8\dot{4}$ |  |  |

|                 |      | 4.3.11  | The primary algorithm, an overview                           | 90         |  |  |

|                 | 4.4  | Post-p  | rocessing                                                    | 92         |  |  |

|                 |      | 4.4.1   | Automorphisms                                                | 93         |  |  |

|                 |      | 4.4.2   | Partially overlapping matches                                | 94         |  |  |

|                 | 4.5  | Extens  | sions to the primary algorithm                               | 96         |  |  |

|                 |      | 4.5.1   | Partially prescribed matches                                 | 96         |  |  |

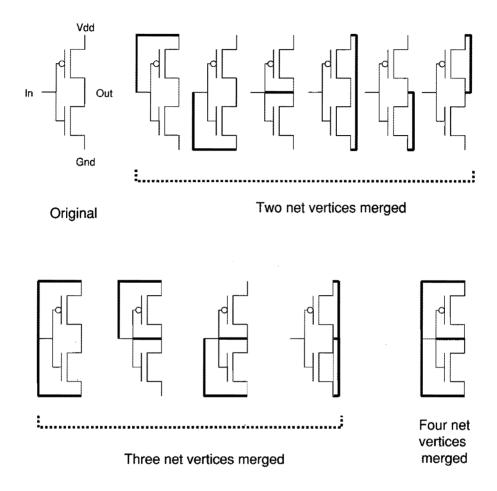

|                 |      | 4.5.2   | External net merging                                         | 97         |  |  |

|                 |      | 4.5.3   | Exchangeable terminal groups                                 | 100        |  |  |

|                 | 4.6  | Diagno  | osis feedback                                                | 105        |  |  |

|                 | 4.7  | Results | S                                                            | 109        |  |  |

|                 | 4.8  | Conclu  | usions                                                       | 113        |  |  |

| 5               | The  | hierar  | chy reconstruction implementation                            | 115        |  |  |

|                 | 5.1  | The R   | ECOGNIZE primitive                                           | 117        |  |  |

|                 | 5.2  | Hierare | chy reconstruction for various hierarchy categories          | 118        |  |  |

|                 | 5.3  |         | ample of a parameterized type description                    | 124        |  |  |

| ĸ               | 5.4  | Recons  | struction order and hidden hierarchy $\ldots \ldots \ldots$  | 125        |  |  |

|                 | 5.5  | Layout  | positions and very large designs                             | 129        |  |  |

| 6               | Res  | ults of | the hierarchy reconstruction method                          | 133        |  |  |

|                 | 6.1  | The hi  | erarchy reconstruction process for the TDA-1307 $\therefore$ | 133        |  |  |

|                 | 6.2  |         | ocation                                                      | 141        |  |  |

|                 | 6.3  | Proper  | ties of the hierarchy reconstruction method $\ldots$ .       | 142        |  |  |

| 7               | Fina | d conc  | lusions and future work                                      | 145        |  |  |

| Bibliography 14 |      |         |                                                              |            |  |  |

| A            | Summary                  | 155 |

|--------------|--------------------------|-----|

| в            | Nederlandse samenvatting | 157 |

| С            | Biography                | 159 |

| D            | List of symbols          | 161 |

| $\mathbf{E}$ | Layouts                  | 165 |

$\mathbf{i}\mathbf{x}$

# Chapter 1

# Introduction

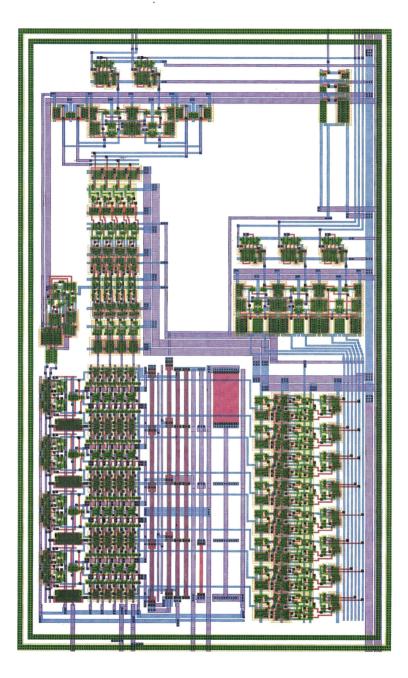

This chapter introduces and provides a motivation for the subject of this thesis. The subject is the verification of electronic designs by hierarchy reconstruction, and in particular the structure verification of the layout design of an IC (Integrated Circuit). The first section introduces briefly the notions of IC-design, synthesis and verification. The second section describes the main trends in IC-design. In the third section, the IC-design process is subdivided into two steps, high level design and layout design, to indicate the position of the thesis' subject in this process. Both steps are described in some detail. The last section describes the aim, subject and structure of the thesis.

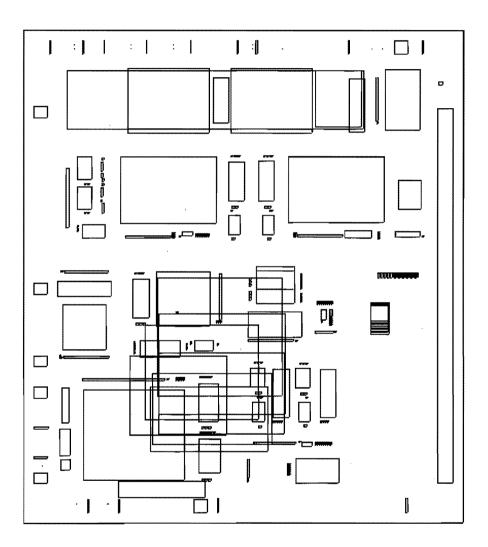

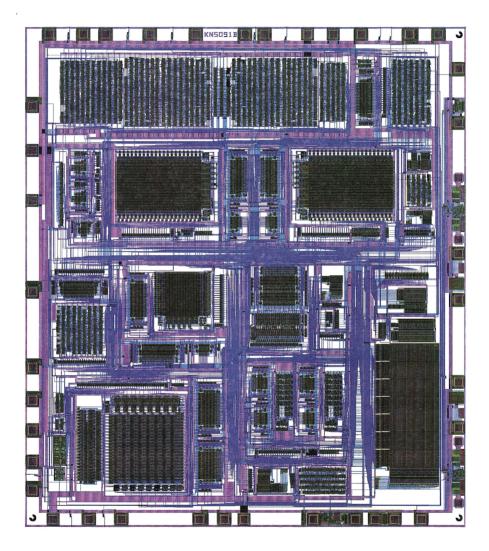

### 1.1 IC-design, synthesis and verification

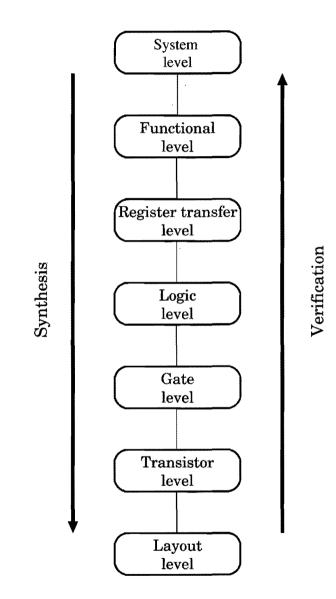

This section introduces the notions of IC-design, synthesis and verification. IC-design is the implementation of an initial IC-specification into a layout, which after processing results in an IC that meets the initial ICspecification. An initial IC-specification describes the required behavior of the IC, and constraints of the IC, such as timing, layout size, package demands, power consumption, etc. A layout describes the geometrical positions of different materials in an IC, thus forming the basic components, such as transistors, resistors and capacitances, and the wiring network connecting the basic components that determine the IC's behavior and properties. An example of a layout is shown in Figure E.2 of Appendix E. The implementation is performed in a number of design steps as indicated in Figure 1.1 to keep overview of the large number of details. A design step

Figure 1.1: Example of a design trajectory.

#### 1.2 Trends in IC-design

consists of a synthesis phase and a verification phase. In the synthesis phase of a design step, a description which is the result of the previous steps, called the specification of the current step, is transformed into a new description, that brings the aim, a layout, closer by. The new description is called the implementation of the current step. Since synthesis is a complicated activity, the implementation may be incorrect with respect to the specification. In the verification phase of a design step, it is established that the implementation of the current step is consistent with the specification of the current step. When the verification is successful, the implementation of the current step is accepted as the specification of the next step. When the verification is not successful, the errors must be corrected.

The description of the IC-design process so far is an example of a divideand-conquer top-down method. This method is applicable only when the consequences at the lower levels of high-level choices can be estimated accurately. However, when details of an IC-design are not yet filled in, for example the size of the design remains hard to predict from the initial IC-specification. In addition, details at a lower level may dramatically influence the higher levels. Therefore, a strict divide-and-conquer design method is impracticable. In current design practice, several complete design iterations from initial specification to layout are necessary, to map out the consequences of the choices made during the synthesis phases. Figure 1.1 shows the hierarchy levels and steps for one example of a design style [Veend92.1]. Each level is indicated by a rounded box. A complete iteration consists of the traversal of a top-down synthesis trajectory and a bottom-up verification trajectory. On a smaller scale, e.g., between two levels, many top-down bottom-up iterations are usually made.

# 1.2 Trends in IC-design

This section briefly analyzes the trends in IC-design. Even after four decades of IC-design, the main trend remains unaltered: the complexity of an IC, i.e., the number of details involved for designing the IC, is larger than the complexity of the previous IC. As a consequence, the amount of specialization keeps on growing, and the CAD-design environments become larger and larger. The relative design effort spent on verification, compared to the effort spent on synthesis, grows due to the growing number of details. In addition, the permanent flow of newly created synthesis tools shifts the design bottleneck even further towards verification.

Silicon technology nowadays allows the integration of many millions of transistors. However, the number of transistors of an IC is only an indirect indicator for the complexity of a design. For instance, a memory IC may contain many millions of transistors, but most of them are designed by repeating the same pattern millions of times. Because memory ICs require little design effort per transistor, the ICs having the largest transistor count are usually memories. The main design challenge is not to increase the transistor count that can be handled, but to design complex systems with as little effort as possible. Complex systems consist of many different functions and parts, resulting in a design containing millions of transistors without global repetition.

An additional phenomenon that comes with the complexity growth is that todays ICs are no longer designed with a single design method or a single design style only. A design is the result of a mixture of design methods and styles, each mastered by a team of specialists. An IC may contain parts consisting of standard cells, ROM modules, PLA modules, embedded memories, analog parts, macro-cells, and library blocks. Different parts may be designed by logic synthesis, manually, by application specific synthesis tools, or be copied from another design etc. All parts are integrated into one layout. This involves the placement and connection of many thousands of terminals. Whether the right parts are present, whether they are implemented correctly, and whether the parts are connected correctly to each other, has become a major verification question and is therefore the main subject of this thesis.

### 1.3 High level design and layout design

Two major steps can be identified in a design process, i.e.,

- high level design and

- layout design.

In the following, both steps are briefly described, with emphasis on the verification phases.

#### High level design

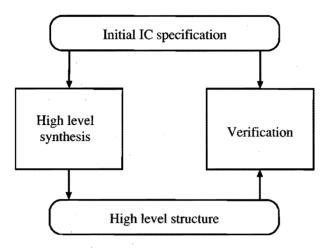

The aim of high level design (see also Figure 1.2) is to take the initial IC specification that describes input output behavior and a set of constraints, to find a high level structure that implements the specification

Figure 1.2: High level design.

correctly. A structure refers to a set of interconnected components that make up the design. In general, a structure or network can be given at various levels of abstraction, relating to various levels of detail. Since high level design deals with the properties as present at the levels close to the initial IC-specification, the outcome is a high level structure that contains no lower level details. The high level structure description may consist of macro-cells, standard-cells, analog cells, etc. Different parts of the initial IC specification may be synthesized by different design methods and styles. Like all design steps, high level design consists of a synthesis phase and a verification phase. In the high level synthesis phase, the top-down step is performed. In the high level verification phase one establishes the consistency between the initial IC specification and the high level network. This is mainly done by simulation, although for specific steps, better alternatives exist [Malik88], [Koste93], [Genoe92]. Much of research is done in this area [AFMC89], [TPCD92], [CHAR93], but many methods have not been as successful in the design practice as their creators hoped.

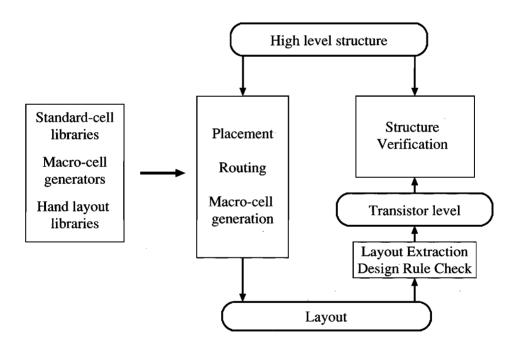

#### Layout design

Figure 1.3 shows the layout design phase. In this part of the design trajectory, the high level structure resulting from high level synthesis is transformed into a layout. A layout describes the geographical position of different materials in an IC. The different materials represented in the layout are usually referred to as the "layers" of a design. By using floor planning, placement and routing tools, various libraries, macro-cell generators and usually some manual editing, etc., a complete layout is generated. During this process, not only many different libraries and complicated CAD tools are used, but also the different design parts are brought together and usually some manual modifications are made. Verification is therefore an essential part of this design step, taking a major part of the layout design effort. These facts have motivated the subject described in this thesis, i.e., the improvement of verification in the layout design. The aim of the layout

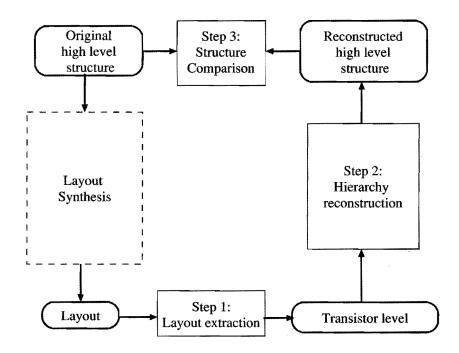

Figure 1.3: Layout design.

verification phase is to check whether the high level structure description has been implemented appropriately in the layout. In the following section, this process is described bottom-up, starting with the layout. The verification is subdivided into three steps.

In order to produce operational basic components such as transistors, resistors and capacitors, the layout must obey technology dependent de-

#### 1.4 Hierarchy reconstruction

sign rules [Veend92.2] that prescribe geometrical constraints on the layers. Therefore, the first verification step is to verify the layout design rules. Commercial layout extraction tools such as DRACULA, or Philips' LO-CAL45, are well capable of verifying the absence of layout design rule violations. Since this verification step is common and widely used, it will not be described in further detail here.

A second step consists of the extraction of basic components (transistors, capacitors, resistors) from layout, as shown in Figure 1.3. The tools for design rule checking are able to perform this task as well and it is done simultaneously with the design rule checking. Most of the components are transistors at this level, only for some analog parts may capacitors and resistors be extracted as well. The effect of *parasitic* capacitors and resistors, e.g., resulting from long wires in the layout, are usually checked by timing verifiers or by circuit simulation. Neither timing verification nor parasitics are subjects of this thesis.

The third verification step, called structure verification, consists of checking whether a high level structure description has been implemented correctly at the transistor level. The focus of this thesis is on an effective method of performing structure verification. This method, called "hierarchy reconstruction", is introduced in the next section.

### 1.4 Hierarchy reconstruction

This section describes the subject, motivation, relevance and structure of this thesis. The subject is an effective method of performing structure verification, called "hierarchy reconstruction". The first paragraph describes the need for structure verification. The second paragraph derives the properties that a structure verification method should have. The third paragraph explains briefly the verification method including the relevance of the method compared with other approaches. The final paragraph describes the structure of the thesis.

#### The need for structure verification

As indicated in Section 1.2 and elaborated in Section 1.3, a modern IC design consists of many parts coming from many different sources, put together during the layout design phase. Not only is the design of each part a complicated task that needs verification, but also putting the parts together appropriately involves many CAD tools and libraries, and often error-prone

Introduction

manual work. Furthermore, every non-trivial computer program contains bugs, and since many computer programs are involved during layout design, one cannot rely on the result without checking afterwards whether the right components have been connected correctly.

#### Structure verification requirements

Any structure verification method must check whether the transistor level structure is connected correctly according to the high level structure. To get a reliable verification method, it should not rely on information added during the synthesis phase, but start from the final result, i.e., the layout. The aim of IC-design is a correct layout where a processed IC will meet the initial IC-specifications. This implies that both synthesis and verification by itself are not aims of IC-design, but inevitable steps, performed to get a reliable layout. A structure verification tool should therefore require little designer effort and few computer resources. The tool should also be able to handle current industrial designs, i.e., a design composed of a million transistors. A structure verification tool should not only signal the presence of an error, but it should indicate the cause of errors, to diminish the extra design effort in correcting the errors. With the growing number of components and connections in IC-designs, the importance of error indication grows as well. The common practice of combining different (perhaps slightly modified) parts coming from different sources in one layout, indicates that connectivity errors at the high structure level are likely to occur, so especially errors at different structure levels should be indicated appropriately.

#### **Hierarchy reconstruction**

Existing structure verification methods are simulation, functional abstraction, netlist comparison at the transistor level and rule-based recognition. As will be shown in Chapter 2, these methods fail to combine complete verification, reasonable run times and appropriate error indication. The hierarchy reconstruction method as described in this thesis however succeeds in combining complete verification, reasonable run times and appropriate error indication.

Hierarchy reconstruction is a method that starts with a transistor level netlist that has been extracted from a layout. By identifying clusters of basic components forming a higher level unit, one can reduce the size of the netlist, and obtain a netlist consisting of higher level components. By per-

#### 1.4 Hierarchy reconstruction

forming this recognition process repeatedly, and on subsequent levels, one can obtain a netlist at the top level, allowing a high level netlist comparison to verify the correctness of the high level structure with the actual layout. When successful, the original high level structure has been reconstructed by the method. An advantage of the method is that any hierarchy that leads to the same top-level structure can be used, i.e., the verification hierarchy can be chosen independently to the one used in the layout synthesis phase.

The aim of this thesis is to describe the hierarchy reconstruction method, and to show that the method works in practice. Basically, the hierarchy reconstruction method is implemented as a sequence of different sub-circuit recognition operations. The core of the thesis describes the recognition algorithm in detail, to explain why the method works. The algorithm will be shown to combine high run time efficiency, flexibility and effective error indication.

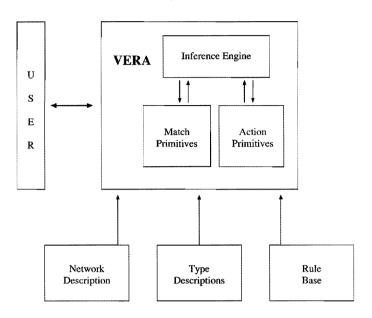

Based on this work, an environment called Vera [Koste89], [Koste88], [Deloor90], [Koste91], [Koste92.2], [Koste92.3] has been developed that supports the hierarchy reconstruction method. Vera is an acronym for VERification Assistant.

#### **Overview**

The thesis is subdivided as follows. Chapter 2 describes existing structure verification methods found in literature. Chapter 3 describes the hierarchy reconstruction method, and the tools needed to make the method operational are inventorized. The main part of thesis is found in Chapter 4, where the recognition algorithm is described. Chapter 5 describes other tools, in addition to the sub-circuit recognition, needed to make the hierarchy reconstruction method work. In this chapter especially the verification of parameterized macro-cells such as a Random Access Memory layout part will be described. Chapter 6 shows some results of the method. The conclusions and suggestions for future work are given in Chapter 7.

# Chapter 2

# Literature on structure verification

The literature on structure verification is partitioned into a section describing different methods on structure verification, and a section on structure recognition algorithms. Structure recognition is the core of the hierarchy reconstruction method. The strong and weak points of the methods and algorithms are summarized and compared with the structure verification requirements of Section 1.4. A conclusion finishes this chapter.

# 2.1 Structure verification methods

Existing methods to verify a high level structure description versus the transistor level structure are simulation, functional abstraction and netlist comparison.

### 2.1.1 Simulation

The classic verification method, simulation, aims at predicting the behavior of a circuit for a given set of input patterns. After simulating the structure at high level and at the transistor level, the resulting behaviors should be the same. When every input pattern leads to similar behavior for both levels, the structures are proven correct. The prediction of behavior is based on models for component interconnection, and an algorithm that combines the models and input patterns. Therefore many distinct simulators exist, supporting various kind of models [Graaf89] and using

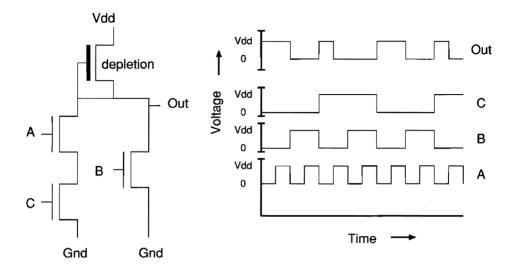

Figure 2.1: Simulation.

different algorithms [Jones94], [VHDL93], [Chua75], [Nagel75], [Feldm92]. At the transistor level, a switch-level simulator is used for digital designs, and a circuit simulator is used for analog designs. At high level, a VHDL simulator [VHDL93] is often used. Figure 2.1 shows a simulation example in which the Out signal is computed for given input signals A, B and C, for the transistor structure as drawn on the left hand side. A simplified switch-level model is used for this example. The depletion transistor is modeled as a finite resistance, and the NMOS transistors are modeled as ideal switches. A modern switch-level level simulator is described in [Jones94]. The predictive value of the computation depends on the models used and the numerical simulation algorithm. Except for several analog circuits, existing models and simulation algorithms in general lead to reliable predictions of circuit behavior. However, for verifying all possible input patterns the run time grows exponentially with the number of inputs and memory-cells, so even for small designs, simulation leads to excessive run times when used for structure verification. Also, the interpretation of simulation results, tracing back the origin of faulty behavior, is usually hard and time-consuming. Furthermore, a side effect of the specialization in IC-design mentioned in Section 1.2 is that the designer who combines all

#### 2.1 Structure verification methods

parts into a complete IC has little knowledge of the details that are needed when searching for errors.

We conclude that simulation is an expensive and ineffective method for structure verification.

#### 2.1.2 Functional abstraction

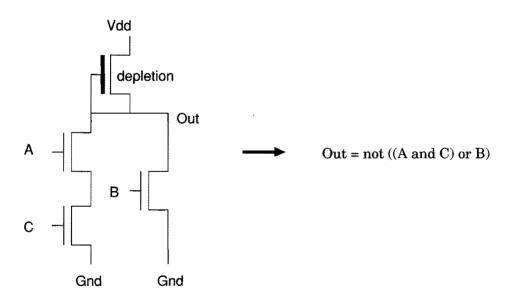

The functional abstraction method as described in [Apte82], [Boehn88], [Bryant87] computes the behavior of a transistor network by transforming the network into a set of Boolean operations. The advantage of this method with respect to simulation is that the complete behavior of a transistor level structure is derived in one step. Input patterns are not needed. The functional abstraction method is based on path-tracing. For each net, the paths leading to the ground or supply nets are analyzed. The rules to derive the Boolean function differ per technology. For instance (Figure

Figure 2.2: Functional abstraction.

2.2), in NMOS circuits [Apte82], a depletion transistor connects the supply net called Vdd with the intended Boolean output net called Out. Assume that the Gnd net has a constant potential of 0 Volt, and is also associated with the Boolean False value, and the Vdd net has a constant potential of 5 Volt, associated with the Boolean True value. The pull-down function of the output net defines when the output has zero potential, i.e, when the Boolean output value is False. The pull-down function is found by interpreting parallel branches to Gnd as an OR function, and serial paths to Gnd as an AND function. The actual Boolean function of the Out net is now given by the Boolean negation of the pull-down function. For full CMOS, both a pull-down function and pull-up function are identified, which must be the Boolean negation of each other. As described in [Ramme92], [Bolse89], the functional extraction method has recently been elaborated for CMOS, in which special attention was paid to timing and clockingstrategies.

The functional abstraction method has been popular for some time now. The premise of the method is that the mapping of electronic functions into layout can be formalized by a simple set of mathematical rules. Although for a limited set of functions this is indeed the case, such as for some combinatorial gates in pure CMOS, this is certainly not the case for all implementations. For digital design parts, one needs additional manual hints for memory-cells. Also, pass gate logic, such as wired-ORs, are a problem [Veend92.3]. The modelling of sized transistors as Boolean networks remains an issue [Verli92]. In [Dever92], a mixed approach of functional abstraction and structure recognition is presented. Functional abstraction so far is limited to Boolean gate level. For instance, no general functional abstraction method exists that abstracts any set of Boolean gates forming an n-bit adder. Also, no automatic functional abstraction method is known for analog designs, at present.

Summarizing we conclude that the maturity of known functional abstraction methods is insufficient for structure verification, especially when different design styles are combined in one layout.

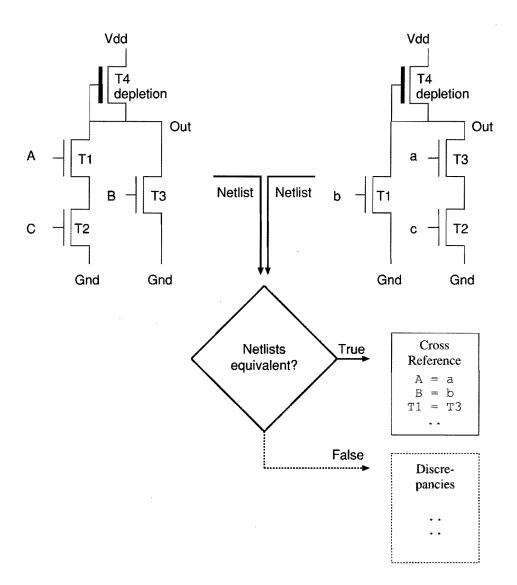

#### 2.1.3 Netlist comparison

The netlist comparison method such as in [Ebeli83], [Waten83], [Spick83], [Ebeli88], compares the transistor level netlist extracted from layout with a reference netlist, by proving or disproving graph isomorphism between the netlists. Figure 2.3 shows how netlist comparison is used. The result of netlist comparison is either a cross-reference list or a discrepancy list. For this particular example, the result is a cross reference list. The crossreference list indicates which elements are isomorphic to one another, as

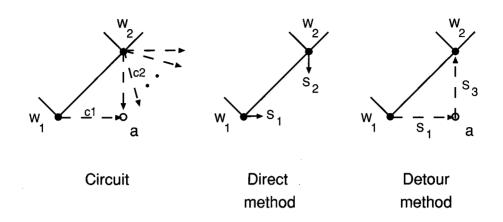

Figure 2.3: Netlist comparison.

indicated by Figure 2.3. A discrepancy list indicates the elements that contradict isomorphism between the netlists.

Existing algorithms for proving graph isomorphism are based either on depth-first search [Spick83], or on refinement [Ebeli83]. The aim of both approaches is to derive an isomorphism function  $\phi$ , i.e., a bi-jective mapping from the elements (nets and components) of the reference netlist, to the transistor level netlist, which preserves adjacency and other properties of every element.

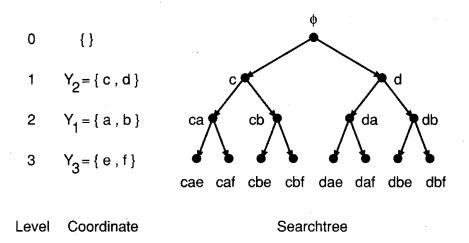

#### Depth-first search

The depth-first search algorithm for sub-graph isomorphisms will be explained extensively in Chapter 4. This paragraph describes briefly the depth-first search version of a graph isomorphism algorithm. The algorithm first defines a search tree that represents the set of all mappings between the netlists. Each path from the root to a leaf of the search tree represents one particular mapping. Next, the depth-first search algorithm constructs an isomorphism function  $\phi$ , by traversing the search tree starting from the root, to determine a path that corresponds to an isomorphism function. The traversal downwards continues until the partial function associated with the current path is inconsistent with preservation of adjacency or other properties of every netlist element. In that case, backtracking occurs to find alternative paths.

Proving graph isomorphism by depth-first search, works appropriately for small netlists. For medium and large netlists, this approach leads to unacceptable run times. Therefore, all modern algorithms for proving graph isomorphism are based on refinement.

#### Refinement

The principle of refinement (see also [Read77]) is informally explained as follows. First it is established that the number of components and number of elements are equal in both netlists. Next, the elements, i.e., components and nets, in the two netlists are iteratively partitioned into sets of elements having equal properties. The initial partitioning is based on initial properties. The initial properties are defined by local features of the elements, such as the type of a component and the number of connections of a net. In every iteration that follows the initialization, the property of every element is reassigned to a value computed by combining (see [Ebeli83]) the current property and the current properties of the neighbors. In this way charac-

#### 2.1 Structure verification methods

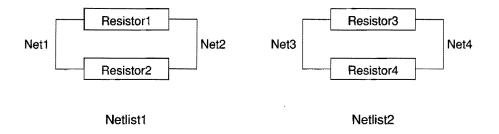

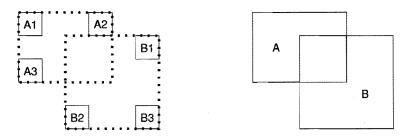

teristics of the neighborhood around every element, at a distance equal to the iteration step number, are combined. The partition can now be refined based on the updated element properties. When both netlists are partitioned into sets of one element (singleton sets), the pair of elements having equal properties in both netlists are assumed to be isomorphic. Unfortunately, it is not always possible to reach a partition consisting of singletons. When a netlist is symmetrical (or to state it exactly: when the number of automorphisms [Harar72.1] is larger than one), refinement into a partition of singletons is not possible. For the example in Figure 2.4, refinement can-

Figure 2.4: Example for which netlist comparison by refinement fails.

not be used to determine isomorphism. After initialization, the nets and resistor components of the netlists have exactly the same role, also when the neighborhood is taken into account, so refinement until a partition of singletons is reached is not possible. The refinement algorithm will conclude that netlist1 is not isomorphic to netlist2. This means that when errors are given by the method, based on not reaching two partitions of singletons, the netlist may still be isomorphic. In other words, this method may result in false negatives.

Despite this disadvantage, netlist comparison based on a refinement algorithm is widely used because it is available, and the run times are acceptable. Netlist comparison is often referred to as LVS (Layout Versus Schematics), since the method is often embedded in a graphical CADenvironment. Obviously, next to the extracted transistor netlist, one requires a reference transistor netlist for comparison. This leads us to another weak point of the method, the need for a reference netlist. Often, a complete netlist is not available, or it is copied from the corresponding transistor level in the synthesis trajectory. In the latter case only errors occurring between transistor level and layout are noticed, the synthesis

#### Literature on structure verification

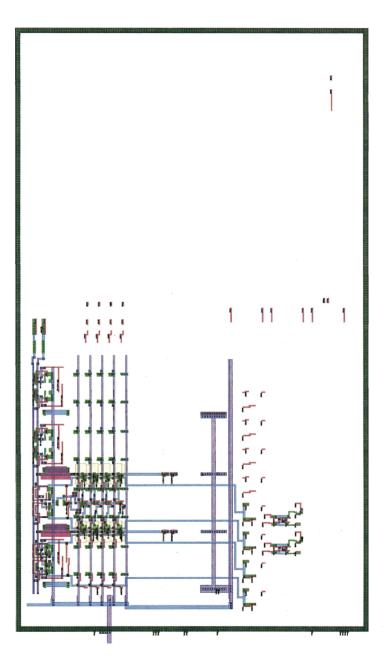

steps between transistor level and high level netlist remain unverified. As a method to check the transistor level versus the layout however, netlist comparison is very efficient when no errors are found. When a discrepancy is signalled by netlist comparison, the cause of discrepancy may be indicated poorly, as was shown in a recent study [Rovers93]. For example, in a small design of 780 components (see color figures E.1 and E.1a in Appendix E) two wires were accidently interchanged. Instead of reporting that two wires were interchanged, a massive and unstructured error report of 43 pages resulted. Figure E.1 (Appendix E) shows the nets and components mentioned in the report. The figure shows that for a single exchange of wires, in a small layout, errors are indicated at many places in the design. For VLSI designs, this is even worse, due to the size of the netlists at the transistor level.

In [Batra92], a hierarchical netlist comparison program is described. The program uses extra hierarchy information that is manually added in virtual layout layers, to indicate the intended hierarchy. In this way expansion of all structure levels down to the transistor level is partly omitted. The disadvantage of this method, as mentioned by the authors as well, is that the addition of hierarchy information is cumbersome. Additionally, it adds a new source of errors to the design trajectory.

We conclude that the netlist comparison method for structure verification is too restricted, because it needs a reliable reference netlist. Furthermore, the error indication is ineffective, and false negatives are inherent to the main algorithm.

### 2.2 Literature on structure recognition

This section describes the state of art with respect to sub-circuit recognition. In the 1960s and early 1970s, structure recognition was studied by discrete mathematicians focussing on graph theory. They referred to it as the problem of identifying sub-graph isomorphisms. They showed that the problem of identifying sub-graph isomorphisms is NP-hard [Read77], which lead to very pessimistic views on the possibility of applying sub-graph recognition algorithms [Berzt73]. The exponential growth of computer power in the last decades made worst case computation feasible for small problems. Furthermore, the usefulness of sub-circuit recognition was recognized in various other sciences, including electronics. Especially for rule-based systems, several recognition programs have been developed. However, the effort in

#### 2.2 Literature on structure recognition

this area was mainly spent on the possible applications. Developing an effective sub-circuit recognition algorithm was usually not the main focus. On the other hand, other work has been published, whose intention is similar to our work, but whose efficiency is limited. The rest of this section describes first some rule-based systems, followed by several other systems.

#### 2.2.1 Rule-based systems

Rule-based systems as described in [Dever92], [Ramme92], [Bolse89],

[Rubic84], [Spick88], use structure recognition in addition to functional abstraction (see Section 2.1.2), mainly to check electrical design rules. Although only the structure recognition aspect of these systems is considered here, the intended functionality is more general. The employed recognition methods are all rule-based. consisting of a user-defined set of clauses (goals), and a depth-first search algorithm that tries to find solutions that satisfy these goals. The set of clauses specifies a pattern that represents a sub-circuit. For these methods, sub-circuit recognition is not considered as a single problem, but recognition is directly subdivided into a set of sub-problems, the clauses. This immediate subdivision of the recognition problem fixes the search order of depth-first search algorithms, and the efficiency of the search process strongly depends on the incidental ordering of the clauses. Since the problem is not analyzed before applying depthfirst search, the order usually results in a bad performance. Other speed improving techniques as will be described in Chapter 4 are absent as well. Therefore, these methods are usually inefficient, and the execution time is very sensitive to the actual definition of a rule, leaving a large responsibility to the user. The results with respect to efficiency are poor, and they are only given for small designs. Regarding another important issue, error indication, little is known, as it is not mentioned in the papers.

We conclude that the efficiency of these systems with respect to structure recognition is insufficient. The merits of these systems are the exploration of applicability of rule-based techniques. We have described structure verification by hierarchy reconstruction as a possible application for the Vera environment in [Koste88], [Koste89]. The method includes both standard-cell structure recognition and macro-cell structure recognition. We have published more results and details in [Deloor90], [Koste91], and showed a complicated design containing 140 000 transistors that was verified in reasonable time on a common workstation. However, we did not explain any details of the structure recognition algorithm, because a patent was pending at that time [Koste92.4]. Part of this thesis is therefore devoted to the information missing in these articles.

#### 2.2.2 Other systems

The method for verifying a layout versus a top level structure by means of layout extraction followed by hierarchy reconstruction is nicely described in [Nebel86]. However, the structure recognition algorithm is not very clear. According to the conclusions, the speed of the structure recognition algorithm needs to be improved, and the error indication needs refinement. A corresponding paper [Nebel87] indeed shows that the performance of the structure recognition algorithm is poor. The computational efficiency behaves experimentally as  $O(n^2)$ , where n denotes the number of transistors in a design.

A standard-cell structure recognition algorithm, to be used for hierarchy reconstruction, is briefly described in [Pelz91]. It is based on a depth-first search algorithm, in which the search order is determined from the signal flow through a MOS-circuit [Jouppi87], and some limited heuristics. In addition, the problem of ambiguity when matching a library (see Section 5.4) is briefly explained. The problem of partly overlapping matches, that may lead to ambiguity, is not mentioned (see also Section 4.51). The work does not include macro-cell recognition and the size of the structures that are recognized seems rather small. Unfortunately, run times are only given for 7 small designs. Five designs contained less than 2 500 transistors, and the largest two contained about 33 000 and 61 000 transistors. Explicit error indication was not mentioned.

Article [Pelz94] is an elaborated version of the previous paper, [Pelz91]. After explaining the hierarchy construction method, the article claims to have proven the following theorem:

The expected run time complexity of the hierarchy construction method is O(n.p.j), where n is the number of components and nets of the transistor level netlist, p is the average number of components and nets of the sub-structures used for recognition, and j is the number of sub-structures that is being recognized.

The proof given for this claim first reduces the efficiency computation to a formula depending on several characteristics of the sub-structures. Next, 12 designs of the ISCAS '89 benchmark [ISCAS89] are selected and the characteristics are evaluated. Based on the trend of these 12 designs it

#### 2.2 Literature on structure recognition

is concluded that the claim holds. In my opinion, giving 12 examples for which the theorem holds is not a general proof. Further, the article advocates a hybrid structure verification approach, by combining hierarchy construction, limited high level cell expansion, and netlist comparison, as indicated schematically in Figure 2.5. The expansion is limited down to

Figure 2.5: Hybrid approach for structure verification.

some intermediate level, the hierarchy construction is limited up to the same intermediate level, followed by a comparison of the top-down and bottomup structures. The author claims to combine the benefits of both methods, i.e., hierarchical error location, the use of different hierarchies for synthesis and verification, and limited run times. The brief results of [Pelz91] are repeated. In addition, the results when applying the hybrid approach for the same designs is given. The hybrid approach is up to 33 % faster. The motivation for a hybrid approach indicates that the author is not satisfied with the performance of the structure recognizer. In my view, a gain of 33 % in run time efficiency is too little to justify the use of such a complicated method. Perhaps an unmentioned argument for introducing the method is the inability to handle macro-cell recognition. It also remains unclear what level should be selected as the intermediate level at which expansion and hierarchy construction should meet. The error indication becomes very complicated, because the error indication of netlist comparison is weak by itself (Section 2.1.3), and has to be translated back to the original top level structure for interpretation as well. Another disadvantage of the hybrid approach is that one relies on a part of the synthesis phase, the expander, to be correct without checking.

### 2.3 Conclusion

Several attempts in the past have aimed at tackling the structure verification problem. So far none of the methods in Section 2.1 meet the requirements as stated in Section 1.4. Not only do run time performance and error indication still present problems, but also several methodological questions remain unsolved.

With respect to the structure recognition algorithms for applying a structure reconstruction method (Section 2.2), the performance of the systems is either insufficient, or unknown. Explicit error indication has not been described.

For the structure recognition based systems, the best results have been reported by the author in [Deloor90], [Koste91], but the recognition algorithm was not described. Of the other papers, [Pelz91] and [Pelz94] are the most interesting, although only results for small designs are given, macro-cell hierarchy reconstruction was not included, and no explicit error indication was mentioned.

# Chapter 3

# The hierarchy reconstruction method

This chapter describes the hierarchy reconstruction method. After giving a global introduction, the required information and the tools needed to make the method operational are derived from existing hierarchy constructs. The requirements are summarized and ordered into an operational model. The model shows that in addition to a sub-circuit recognizer, other tools are also needed. The remaining chapters of this thesis focus on the implementation of the operational model and on the results obtained with the implementation.

# 3.1 Introduction

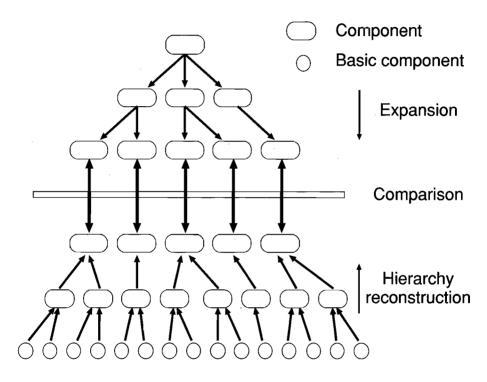

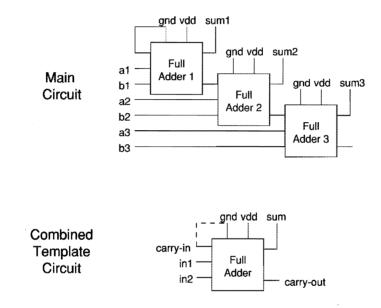

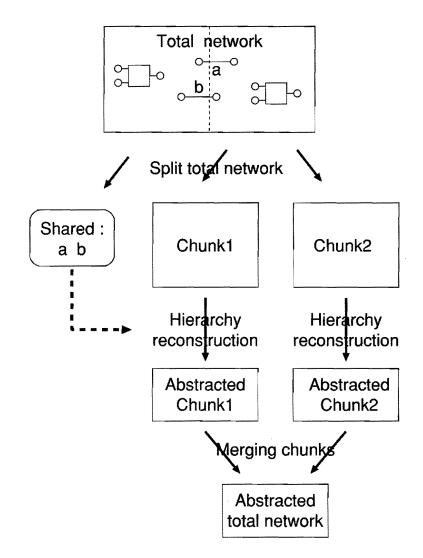

Hierarchy reconstruction aims at verifying consistency between the transistor level structure and a high level structure. The transistor level structure has been extracted from a layout, as described in Section 1.3. The high level structure consists of standard cells and macro-cells. In order to simplify terminology, we also call a fixed analog block a standard cell. Macro-cells are instances of parameterized modules. For example, an *n*-bits adder is a module with parameter n, and a 7-bits adder is a macro-cell, generated by the adder's module generator instantiated with n=7. Standard cells are not parameterized with respect to their structure. The hierarchy reconstruction method is based on stepwise bottom-up abstraction. By using a sub-circuit recognizer, the simplest sub-structures in the transistor netlist, such as inverters, nands, etc., are identified first. Next, the higher level sub-structures, such as memory-cells, etc., are found, as indicated in Figure 3.1. Recognition and abstraction of increasingly complex structures takes place, until no further abstraction is possible, and the highest level structure has been reached. By using netlist comparison at the top level, the constructed high level structure description can now be compared (see Figure 1.3) with the initial top level structure, to establish consistency.

The following information is needed for the construction process:

- a non-parameterized component library describing higher level components as a network of connected lower level components, and

- a parameterized module library, describing how a module instance (a macro-cell) is composed of interconnected lower level components, for given parameter instances.

In these libraries, layout related information is not included. The following tools are needed as well to be able to perform the construction process:

- a fast sub-circuit recognizer for performing structure recognition,

- a netlist comparison tool, and

- a tool, called the controller, that supervises the reconstruction process.

The latter should interpret the library information, and order the sequence of structures to be recognized.

Since there is no layout information required for hierarchy reconstruction, the effort to set up the library is limited. Compared to the effort spent on making (writing) a module generator and a standard cell library, our library effort is negligible. Since the information is set up differently and independently from the top-down library and synthesis tools, the probability of errors slipping through unnoticed is very small. In the remaining sections of this chapter, the method is elaborated into an operational model, that shows the prerequisites and their relations that must be implemented.

### **3.2** Hierarchy and structure parameters

This section describes the hierarchy reconstruction method in more detail by considering the role of structure parameters in a design hierarchy. Depending on the role of structure parameters, hierarchy is partitioned into

#### 3.2 Hierarchy and structure parameters

four categories. The requirements for constructing hierarchy are derived for each category. As indicated in the introduction of this chapter, the main distinction is between macro-cells that are instances of parameterized modules, and standard cells that are not parameterized. In theory, little can be said about the semantics of the structure parameters of a module. However, for a module to be usable, the semantics of a structure parameter should not be complicated. Therefore, our partitioning is based on actual semantics of parameters that are used in IC-design [Wouds90]. In all cases, parameters indicate either repetition of some structure, or a function, represented by a table.

#### **Category 0: Non-parameterized modules**

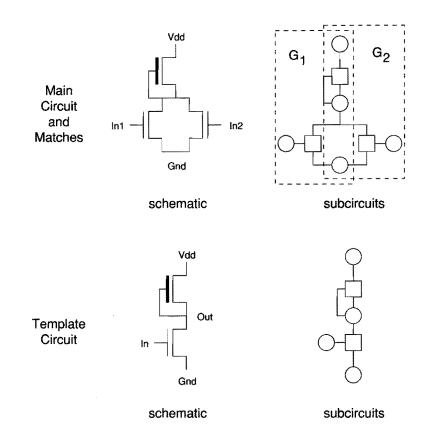

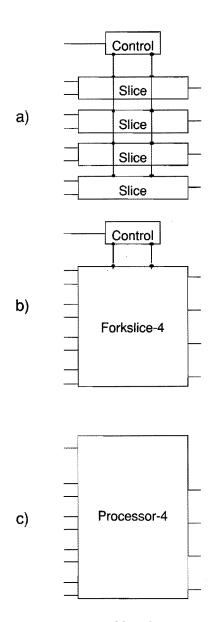

A non-parameterized module is a module that has a fixed structure. The reconstruction of non-parameterized modules such as standard cells is the first, and most important, step in reducing the complexity of a large circuit. For example replacing all transistor pairs forming an inverter circuit, by an inverter component can be performed as follows:

- 1. retrieve the inverter structure, to act as the template,

- 2. identify all transistor pairs matching the template,

- 3. replace the identified transistor pairs by inverter components.

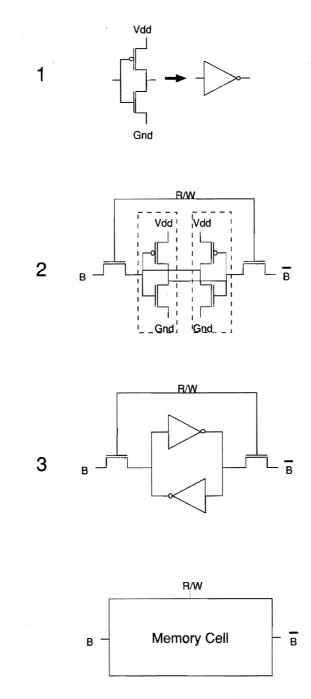

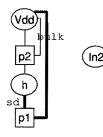

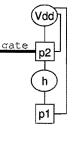

After the matched inverter transistors have been abstracted, other or higher level components can be constructed in the same way. Figure 3.1 illustrates the hierarchy construction steps of an inverter structure, followed by the construction of a memory cell.

In summary, hierarchy construction for Category 0 modules requires

- (a) a library, containing the structures of all non-parameterized (sub-)modules,

- (b) a pattern-matcher, capable of finding matches of a given library template in a large network, and

- (c) an "abstractor", to replace found matches by the corresponding higher level component.

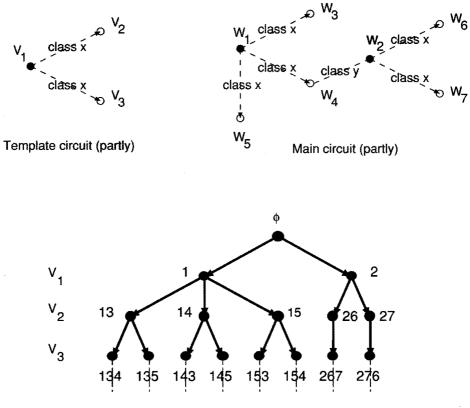

Figure 3.1: Non-parameterized hierarchy reconstruction

#### 3.2 Hierarchy and structure parameters

#### **Category 1: Singly parameterized modules**

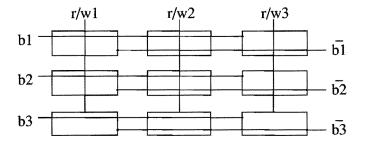

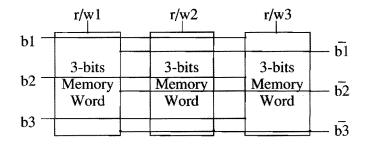

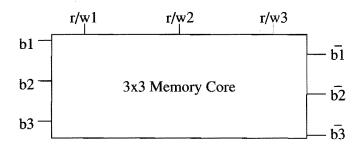

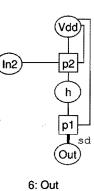

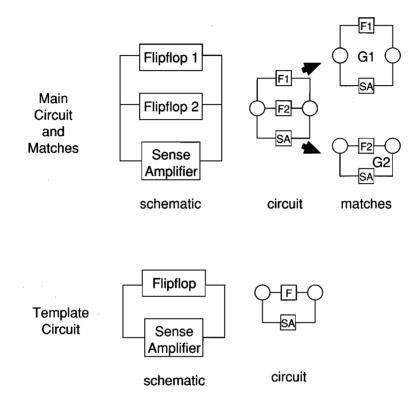

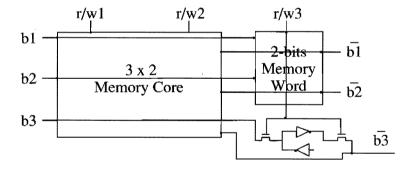

A singly parameterized module is a module of which the structure of a corresponding macro-cell is determined by the value of one structure parameter, k, that indicates structure repetition. The parameter value is a number of a limited integer domain. When two values are allowed only, the parameter indicates the absence or presence of some part of the structure. When the parameter has more than two acceptable values, it indicates serial or parallel repetition of some part of the structure. Obviously, when the parameter has one possible value, the parameter has no meaning for the structure of the module. The parameter may be associated with the number of bits in a data or control word. The hierarchy construction process of this category is explained for the abstraction of all memory words in a memory core (first step in Figure 3.2). After the reconstruction of the memory cells (see Category 0), the following is performed:

- 1. the value k, i.e., the number of memory cells connected in parallel to the same r/w select line, is derived from the network,

- 2. a parameterized module generator produces a structure template for the k-bit memory word instance,

- 3. the circuit components, matching this template, are replaced by a k-bit memory word.

Compared to Category 0 modules, Category 1 modules require:

- (d) a structure-repetition detector, capable of recovering parameter values from the repetition in a network,

- (e) a library of parameterized structure template generators.

# Category 2: Multiple parameterized modules

A multiple parameterized module is a module of which the structure of a macro-cell is determined by multiple parameter values. A RAM module is an example having multiple parameters. The structure of a RAM macro-cell may be a function of four parameters: x-decoder depth, y-decoder depth, z-decoder depth and word-length. Hierarchy reconstruction of these modules is performed by repeating singly parameterized hierarchy reconstruction. Figure 3.2 illustrates the reconstruction process of the core of a RAM. The number of bits in a word is determined first from the number of memory cells connected to the r/w select lines. All memory words can now be

Figure 3.2: Parameterized hierarchy reconstruction

#### 3.3 The operational model

abstracted, as described for Category 1 modules. Secondly, the memory core depth, i.e., the number of memory words, is determined by the number of parallel connections to both bit line {b1, b2, ...} and inverse bit line { $\overline{b1}, \overline{b2}, \ldots$ } signals. The complete memory core can now be abstracted. Compared to Category 1 modules, Category 2 modules have no additional requirements.

#### Category 3: Modules having a table parameter

This category is defined by modules that have a table parameter. Typical examples of this category are ROM and PLA modules. Their functionality is determined by a (truth) table. As an example, the reconstruction of ROM modules is briefly described. The ROM module is implemented as a row decoder, a column decoder and a core. The data contents in the core of the ROM are represented by the presence or absence of a transistor at the crosspoint of a word and a bit line. The row decoders and column decoders can be reconstructed in the same way as Category 2 modules. In addition to Category 2 modules, Category 3 modules require:

(f) a table-extractor, to retrieve the function of the macro-cell.

# 3.3 The operational model

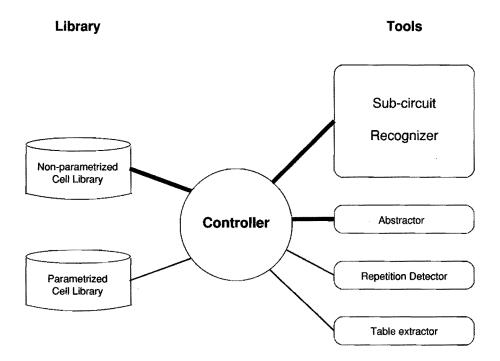

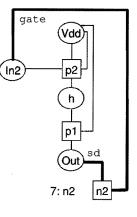

In Figure 3.3 the requirements derived in the previous section are summarized in the operational model of Figure 3.3. The operational model indicates the tools, libraries and relations between them to transform the transistor level structure, or circuit, into a top level structure. The cell library, at the left-hand side of Figure 3.3, stores component definitions as a non-parameterized or a parameterized structure of connected lower level components. The tools that operate on the circuit, shown at the right-hand side of Figure 3.3, are a sub-circuit recognizer, an abstractor, a structure-repetition detector and a table extractor. The sub-circuit recognizer identifies occurrences of a circuit pattern, called a template, the abstracter replaces a match of a template by the corresponding higher level template component, the structure repetition detector identifies iterative structure parameter values, and finally the table extractor derives the function related to table parameter of a module.

The controller organizes the interaction between the tools, the library and the circuit. For hierarchy reconstruction of non-parameterized modules, only the objects connected by bold lines are needed. The order of

Figure 3.3: Operational model for hierarchy reconstruction

#### 3.3 The operational model

abstraction is determined by the controller. For parameterized modules, the other objects are needed as well. For every module generator, a verification controller is created, which describes how a macro-cell can be reconstructed. By activating the associated controller, the user starts the reconstruction process of all instances of that specific module generator in the design. The controller determines the order in which the tools operate on the network, and gathers and provides the necessary information.

Control and libraries are set up separately and independently from the module generator, since they require a different view, namely bottom-up instead of top-down. By separating the information used in the top-down and bottom-up path, the probability of the same error occurring in both descriptions, thus escaping detection, is very small.

In the following chapters, the model of Figure 3.3 is elaborated. Some interesting tools are elaborated in more detail than other, less interesting tools. The sub-circuit recognizer is the most important tool to make hierarchy reconstruction operational. As described in Chapter 2, a suitable sub-circuit recognition tool has not yet been presented. The next chapter describes our sub-circuit recognition tool. Since the subject is subtle but crucial for the applicability of hierarchy reconstruction, it is described thoroughly, starting from formal definitions, and explaining the algorithm in detail, including the crucial efficiency enhancements. Chapter 5 describes the implementation of the remainder of the operational model, followed by Chapter 6, showing the results of the method for a typical design.

.

# Chapter 4

# The sub-circuit recognizer

# 4.1 Introduction

In the previous chapter, it has been shown that a sub-circuit recognizer is the main tool needed for making the hierarchy reconstruction method operational. This chapter discusses the sub-circuit recognizer in detail. When the casual reader is interested in the hierarchy reconstruction method, but not that much in the algorithms supporting it, this chapter can be omitted.

The sub-circuit recognition problem is informally described as the problem of finding all occurrences of a *template circuit* in a usually larger *main circuit*. Sub-circuit recognition is identical to the problem of finding all isomorphic sub-graphs in a graph [Read77]. In the mathematical literature it is an example of an NP-hard problem, implying that no method exists that solves each instance of the problem in polynomial time [Read77]. Every algorithm shows exponentially growing run times for some set of problem instances, unless the very unlikely condition known as "P = NP" holds. Therefore, the hope of finding a useful algorithm had vanished for some mathematicians [Berzt73]. From a practical point of view however, it still makes sense to search for algorithms that efficiently solve many often encountered sub-graph isomorphism problem instances, although no guarantee of run times can be given. In fact, without a powerful sub-circuit recognizer, the hierarchy reconstruction method cannot be employed.

The remainder of this chapter is organized as follows. Section 4.2 defines the sub-circuit recognition problem in a formal way. Section 4.3 describes the primary algorithm. Section 4.4 describes the post processing of the results of the primary algorithm. Section 4.5 shows some extensions that enhance the usability and flexibility of the primary algorithm. Section 4.6 describes diagnosis feedback when the recognition finds fewer matches than expected. Section 4.7 shows experimental results and an analysis of the run times. Section 4.8 finishes the chapter with conclusions.

# 4.2 Definitions

Section 4.2.1 enumerates notational conventions and several general notions. Section 4.2.2 defines formally a circuit. Based on the definition of a circuit, Section 4.2.3 defines the template circuit and the main circuit, followed by the sub-circuit recognition problem. To allow accurate efficiency argumentation for the algorithms in the next chapters, Section 4.2.4 briefly describes the data representation of a circuit in a computer.

# 4.2.1 General notions and notation

A set is a collection of elements, in which each member occurs once.

A multi-set is a collection in which elements may occur multiple times.

The *multiplicity* of an element a of a multi-set B, i.e., the number of occurrences of a in B, is denoted by  $\mu_a(B)$ .

For a (multi-)set B, |B| denotes the number of elements in B.

For a set B,  $2^B$  denotes the set of all sets over B, i.e., the *power set* of B.

For a set B,  $\mathbb{N}^B$  denotes the set of all multi-sets over B.

An ordered (multi-)set is denoted by  $(x_1, x_2, ...)$ . A shorthand notation for the ordered (multi-)set is  $\mathbf{x}$ , i.e., by using boldface fonts.  $\mathbf{x}_j$  denotes the prefix  $(x_1, \ldots, x_j)$ . An ordered multi-set is also called a sequence.

For a set B,  $B^+$  denotes the set of all non-empty sequences over B.

An unordered (multi-)set is denoted by  $\{x_1, x_2, \ldots\}$ .

The set operators for union, intersection and set-minus are denoted by the symbols  $\bigcup$ ,  $\bigcap$  and  $\setminus$ . The result of a set operator is an unordered set. An operand is either an unordered set, or it is interpreted as an unordered set, when the operand is an (un)ordered multi-set or an ordered set.

For sets A, B and a function F,  $F: A \to B$ , A is called the *domain* and B is called the *co-domain* of function F. Furthermore, F(A) denotes a subset of B called the *image*.

#### 4.2 Definitions

For sets A, B,  $B^A$  denotes the set of all functions having domain A and co-domain B.

In definitions, the first character of the notion being defined are written uppercase.

#### **Definition 4.1** Restriction of a Function

For a function  $F, F : A \to B$ , and a subset C of A, the Restriction of Function F to C is the function denoted by  $F|_C$ , defined as  $F|_C : C \to B$ , for all  $a \in C : F|_C(a) = F(a)$ .

#### **Definition 4.2** Equivalence Set

For  $a, b \in A$ , a is called equivalent to b when F(a) = F(b). The Equivalence Set of  $a \in A$  with respect to the function  $F : A \to B$ , denoted by  $[a]_F$ , is defined by  $[a]_F = \{x \in A \mid F(x) = F(a)\}$ .  $\Box$

#### **Definition 4.3** Quotient Set

For a function  $F : A \to B$ , the Quotient Set A/F is defined by  $A/F = \{[a]_F \mid a \in A\}$ . A/F is a partition of set A.

#### **Definition 4.4** Canonical Map

For a function  $F : A \to B$ , the Canonical Map  $g : A \to A/F$  is defined by  $g(a) = [a]_F$ . Hence, the canonical map maps an element onto the equivalence set of which it is a member.  $\Box$

#### **Definition 4.5** Characteristic Function

For a function  $F: A \to \{True, False\}, F$  subdivides set A into the equivalence sets  $[True]_F$  and  $[False]_F$ , called the true-set and false-set. Therefore,  $A/F = \{[True]_F, [False]_F\}$ . Since F can be used to define a set and its complement, F is called the Characteristic Function of set  $[True]_F$ .  $\Box$

The true-set of a characteristic function  $D : A \to \{True, False\}$ , i.e.,  $[True]_D$ , is denoted by  $\mathcal{D}$ . The true-set of a characteristic function  $d : A \to \{True, False\}$ , i.e.,  $[True]_d$ , is denoted by  $\delta$ . Hence calligraphic fonts are used for the true-set of a function denoted in uppercase, and Greek fonts are used for functions denoted in lowercase.

#### **Definition 4.6** Pair Function

For  $k \in \mathbb{N}$ , ordered sets  $A = (a_1, \ldots, a_k)$ ,  $B = (b_1, \ldots, b_k)$ , the Pair Function  $A \bullet B : A \to B$  is defined by  $A \bullet B(a_i) = b_i$  for  $i = 1, \ldots, k$ .  $\Box$

The (multi-)sets and functions of the main circuit are denoted in boldface, for example  $\mathbf{G} = (\mathbf{V}, \mathbf{T}, \mathbf{A}, \mathbf{E}, \mathbf{TC})$ . The (multi-)sets and functions of a *template circuit* are denoted emphasized, for example G = (V, T, A, E, TC). The (multi-)sets and functions of a *sub-circuit* of the main circuit are denoted calligraphically, for example  $\mathcal{G} = (\mathcal{V}, \mathcal{T}, \mathcal{A}, \mathcal{E}, \mathcal{TC})$ .

For an undirected edge e, vert(e) denotes the unordered pair of vertices  $\{u, v\}$  that are connected by e.

# 4.2.2 The circuit definition

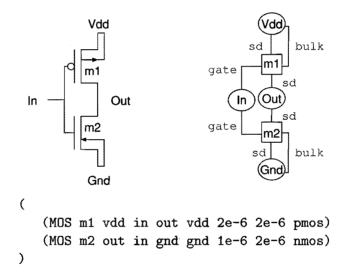

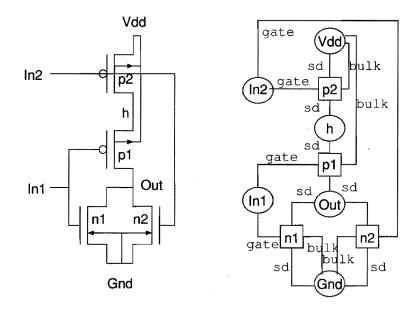

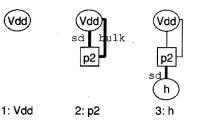

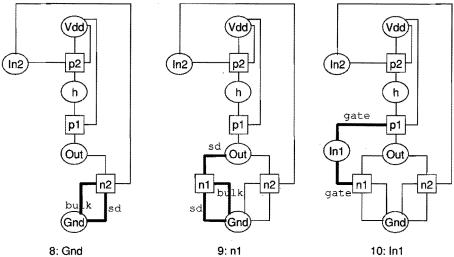

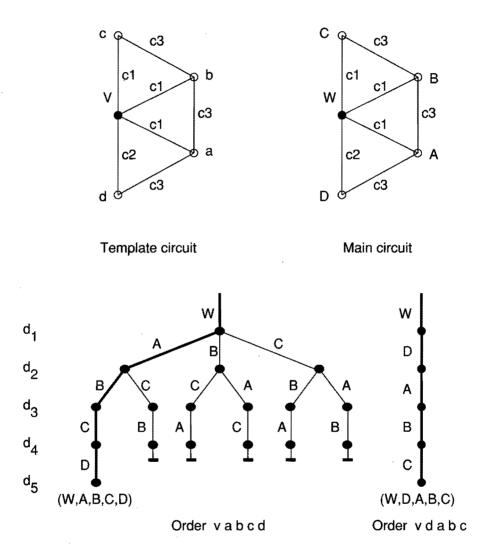

Figure 4.1: Schematics, graph picture and netlist representation of a circuit. The attribute names and attribute values of m1 and m2 are not included in the graph.

# An example

Figure 4.1 shows an example of a circuit. The figure displays the schematics, a picture of the circuit as a bipartite graph, and a netlist representation of a circuit. The schematic representation is normally used by electronic engineers. Since the circuit will formally be defined as a labeled bipartite multi-graph, the graph picture represents best the formal circuit definition. A netlist representation is a textual representation that can be used to store

#### 4.2 Definitions

a circuit in a computer file. Before formally defining a circuit, the relation between schematics, the picture of the graph and the netlist is explained. The schematics of Figure 4.1 consist of transistor components m1 and m2. and nets vdd, in, out and gnd. In the picture of the circuit graph, the components are depicted by squares, the nets are depicted by ovals. Together, the squares and ovals are the vertices of the graph. The connections of the schematics are depicted by lines, determining the undirected edges of the graph. Note that the graph is bipartite since ovals are only connected to squares and vice versa. Note also that the graph contains multi-edges, such as the connections between component m1 and net vdd. In order to distinguish between different kinds of connection, each edge of the graph is labeled with a terminal class. Both m1 and m2 are instances of the component type MOS. A component type defines the properties (property name and property value pairs) of a component, such as the number and kind of connections, the possible attribute names, etc. Figure 4.2 shows the MOS component type definition. The list of terminal classes defines the connections of MOS, i.e., one terminal of class gate, two terminals of class sd - short-hand for "source or drain", which are considered equivalent terminals - and one terminal of class bulk. The three attributes of MOS are named width, length and model. The attributes are not included in the graph of Figure 4.1. Figure 4.3, shows another component type definition, having other properties in addition to those of Figure 4.1.

The netlist representation is component oriented. It enumerates the component type, the component name, the connections to nets and attribute values corresponding to the attribute names. The connections and attribute values are ordered according to the terminal classes and attribute names found in the description of a component type; see Figure 4.2. For example, the last attribute, named model, is used to indicate a pmos attribute value for m1, and nmos for m2.

#### The formal definition of a circuit

The definitions are based on the following basic notions:

- $\tau$  denotes a non-empty set of types,

- $\Gamma$  denotes a non-empty set of terminal classes,

- $\alpha$  denotes a set of attribute names,

- $\beta$  denotes a set of attribute values.

Figure 4.2: Example of a component type, defining TTC(MOS) = (sd, gate, sd, bulk) with property name Terminal-classes and TA(MOS) = (width, length, model) with property name Attribute-names

The empty set, denoted by  $\emptyset$ , is not a member of  $\tau$ ,  $\Gamma$ ,  $\alpha$  or  $\beta$ . A circuit will be defined as an interconnected set of components and nets. Every component will have a type label, which will be defined by the type function. The "type terminal classes" function and the "type attributes" function will be defined on types, to prescribe the labels of connections to a component and the attribute names of a component. A component has a second label, the attribute, that will be defined by the attribute function to assign attribute values for corresponding attribute names. A net will not have an associated type label. The distinction between components and nets will therefore be defined based on the type function. The edges between components and nets will be labeled by a terminal class. The multi-set of terminal classes that are labels of the edges between two vertices will be defined as the terminal classes function which will used extensively in Section 4.2.3.

# Definition 4.7 Type Terminal Classes

For each type  $t \in \tau$ , the Type Terminal Classes function  $TTC : \tau \to \Gamma^+$  assigns to each type a sequence of terminal classes.

For example, in Figure 4.2, TTC(MOS) = (sd, gate, sd, bulk). Note that a sequence is an ordered enumeration of items in which repetition may occur.

#### **Definition 4.8** Type Attributes Function

For each type  $t \in \tau$ , the Type Attributes Function  $TA : \tau \to 2^{\alpha}$  assigns a set of attribute names to a type.

For example, in Figure 4.2, TA(MOS) = (width, length, model).

# Definition 4.9 Type Function

For a set of vertices V, the Type Function  $T: V \to \tau \cup \{\emptyset\}$  assigns either a type or  $\emptyset$  to a vertex.  $\Box$

#### **Definition 4.10** Set of Components

For a set of vertices V and a type function T, the Set of Components C is defined by  $\{ v \in V \mid T(v) \in \tau \}$ .

#### Definition 4.11 The Set of Nets

For a set of vertices V and a type function T, the Set of Nets N is defined by  $\{ v \in V \mid T(v) = \emptyset \}$ .

Obviously,  $N = V \setminus C$ , since  $\emptyset \notin \tau$ .

## Definition 4.12 Attribute Function

For a set of vertices V and a type function T, the Attribute Function  $A: V \to 2^{\alpha \times \beta}$  assigns to each component a set of ordered attribute name, attribute value pairs, and  $\emptyset$  to a net. For a component  $v \in C \subset V$ , every attribute name of A(v) must be a member of TA(T(v)), i.e., a member of the attribute names of the corresponding type of v, and only one attribute value is associated.

For example,  $A(m1) = \{(width, 1e-6), (length, 1e-6), (model, pmos)\}$  in Figure 4.1.

## Definition 4.13 Set of Multi-edges

For a vertex set V and a type function T, an edge connects a component  $u \in C \subset V$  and a net  $v \in N \subset V$ . The connected vertices  $\{u, v\}$  of an edge e are denoted by vert(e). A Set of Multi-edges is a set of edges for which several edges may connect the same vertices.

#### Definition 4.14 Terminal Class Function

For a set of multi-edges E, the Terminal Class Function  $TC : E \to \Gamma$  assigns a label to each edge, called the terminal class. It indicates what kind of connection is meant.

#### Definition 4.15 Terminal Classes Function

For a set of vertices V, a set of multi-edges E and a terminal class function TC, the Terminal Classes Function  $TCS : V \times V \to \mathbb{N}^{\Gamma}$  is defined by  $TCS(u, v) = \{ TC(e) \mid e \in E : vert(e) = \{u, v\} \}$ . It assigns the multi-set of all terminal class labels to a vertex pair  $\{u, v\}$ . Hence, it represents the edges connecting u and v, including their multiplicity. When  $TCS(u, v) = \emptyset$ , no edges connect u and v. Since an edge is undirected, TCS is a symmetric function.

In Figure 4.1 for example, we see two edges connecting vdd and m1, having labels sd and bulk, so  $TCS(vdd, m1) = \{sd, bulk\}$ .

#### Definition 4.16 Degree Function

For a set of vertices V, a set of multi-edges E and a terminal class function TC the Degree Function  $DEGREE: V \times \Gamma \to \mathbb{N}$  assigns to a vertex v and a terminal class c the number of edges incident with v having a terminal class label c.

## Definition 4.17 Circuit

A Circuit G is an undirected labeled bipartite multi-graph, defined by a 5-tuple G = (V, T, A, E, TC), for which

- V is a set of vertices,

- T is a Type function as defined in Definition 4.9,

- A is an Attribute function as defined in Definition 4.12,

- E is a set of multi-edges as defined in Definition 4.13,

- TC is a Terminal Class function as defined in Definition 4.14.

The set of components C is defined in Definition 4.10. The set of nets N is defined in Definition 4.11. The degree function DEGREE is defined in Definition 4.16. The terminal classes function of G is defined by Definition 4.15. Furthermore, for any component  $v \in C \subset V$ , any terminal class  $c \in \Gamma$  the following must hold:

$$DEGREE(v,c) = \mu_c(TTC(T(v))).$$

(4.1)

In other words, the number of edges per terminal class of a component v is determined by the type of the component v. The *size of the circuit*, denoted by |G|, is defined by the number of edges plus the number of vertices, i.e., |E| + |V|.

# 4.2.3 The sub-circuit recognition problem

The sub-circuit recognition problem aims at finding all occurrences of a template circuit, called the matches, in a usually larger main circuit. Every match is a sub-circuit of the main circuit. The sub-circuit recognition problem will be defined slightly more specifically than the abstract sub-graph

#### 4.2 Definitions