#### Exploiting instruction-level parallelism: a constructive approach

Citation for published version (APA):

Villar dos Santos, L. C. (1998). *Exploiting instruction-level parallelism : a constructive approach.* [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR516269

DOI:

10.6100/IR516269

Document status and date:

Published: 01/01/1998

Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 16. Nov. 2023

# Exploiting instruction-level parallelism

a constructive approach

Luiz Cláudio Villar dos Santos

## Exploiting instruction—level parallelism a constructive approach

## Exploiting instruction-level parallelism

a constructive approach

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de Rector Magnificus, prof.dr. M. Rem, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op maandag 23 november 1998 om 16.00 uur

door

Luiz Cláudio Villar dos Santos

geboren te Arapongas, Brazilië

Dit proefschrift is goedgekeurd door de promotoren:

prof.Dr.-Ing. J.A.G. Jess en prof.dr.ir. J.L. van Meerbergen

Copromotor:

dr.ir. C.A.J. van Eijk

#### © Copyright 1998 Luiz Cláudio Villar dos Santos

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission from the copyright owner.

Druk: Universiteitsdrukkerij Technische Universiteit Eindhoven

#### CIP-DATA LIBRARY TECHNISCHE UNIVERSITEIT EINDHOVEN

Villar dos Santos, Luiz C.

Exploiting instruction—level parallelism: a constructive approach / by Luiz C. Villar dos Santos. — Eindhoven: Technische Universiteit Eindhoven, 1998. Proefschrift. — ISBN 90-386-0490-4

**NUGI 832**

Trefw.: grote geintegreerde schakelingen ; CAD / digitale systemen ; CAD / combinatorische optimalisering / scheduling.

Subject headings: VLSI / digital systems / high level synthesis / scheduling.

#### Summary

The increasing complexity of integrated circuits provided by VLSI technology requires design automation at higher levels of abstraction. In such context, high-level synthesis translates a behavioral-level specification of the digital system into an architecture consisting of a data path and a control unit. Emerging design problems are prompting the utilization of instruction-level parallelism (ILP), traditionally an object of parallelizing compilers, for the synthesis of digital systems. In this thesis, techniques like code motion, speculation and loop pipelining are employed to expose ILP and their application is oriented to digital systems designed to operate under a global time-constraint. A resource-constrained optimization problem is formulated as a starting point. From a given specification and a set of resource constraints, the goal is to obtain a symbolic finite state machine (FSM) for the control unit of the digital system such as to minimize the schedule length of the critical execution path. An approach is proposed in which several alternative solutions are generated and explored by means of a local search algorithm.

For the construction of a FSM, our approach combines both graph algorithms and Boolean techniques. The flow of control is represented in the form of a graph consisting of branch and merge junctions and so-called basic blocks. During a top-down traversal of this graph, the operations scheduled in each state may come from different basic blocks and possibly from different iterations of a loop. Equivalent states are detected and merged on—the—fly. A code—motion pruning technique is proposed to prevent inefficient code motions caused by the typical unbalance between the potential parallelism exposed and the parallelism that can actually be exploited within the available resources.

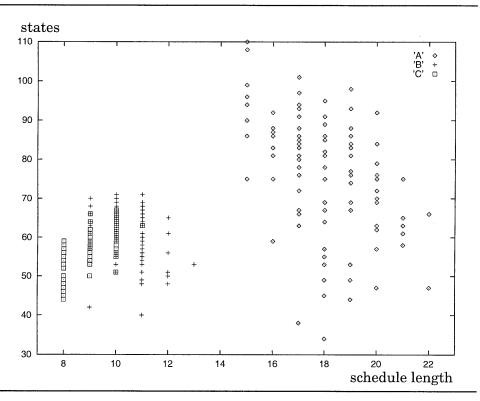

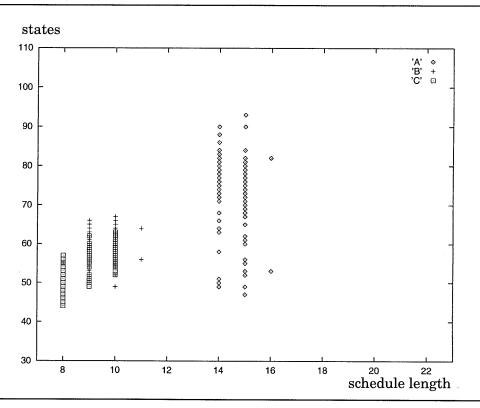

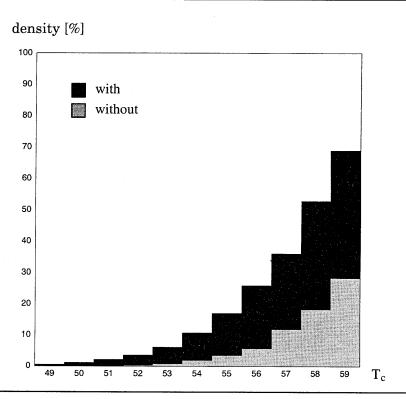

Experimental results show, on the one hand, that the growth of the number of states caused by ILP techniques can be restrained efficiently by the on–the–fly merging of equivalent states. On the other hand, they provide evidence that the pruning technique increases the density of good–quality solutions in the search space, thereby paving the way to a reduction of average search time.

#### Samenvatting

De toenemende complexiteit van de hedendaagse chips creëert een behoefte om op een hoger niveau van abstractie te ontwerpen. Vanuit een functionele beschrijving van een digitale systeem, genereert hoog-niveau synthese een architectuur die bestaat uit een datapad en een "control unit". Hedendaagse ontwerpproblemen suggereren het gebruik van instructie-niveau parallellisme (ILP), welbekend uit het vakgebied van compilers, voor de synthese van digitale systemen. In dit proefschrift wordt het gebruik van ILP technieken als "code motion", speculatieve executie en "loop pipelining" gericht op digitale systemen onder tijdsbeperkingen. Een optimaliseringsprobleem wordt geformuleerd waarin het aantal en soort bouwblokken wordt beperkt. Het doel is, om vanuit de beschrijving en het aantal bouwblokken, een symbolische FSM te genereren voor de "control unit" met minimaal kritiek executiepad. Een methode wordt gepresenteerd waarbij verschillende oplossingen gecreëerd en onderzocht worden met behulp van een lokale zoekmethode.

Om een FSM op te bouwen, gebruikt de methode graaf algoritmen en Boolse technieken. De controle-stroom wordt gerepresenteerd als een graaf die bestaat uit "branch" en "merge" knooppunten en zogenaamde "basic blocks". Tijdens het doorlopen van deze graaf, kunnen de operaties die geselecteerd zijn voor een toestand komen vanuit verschillende "basic blocks" en van verschillende loop iteraties. Gelijke toestanden worden geïdentificeerd en samengevat tijdens het opbouwen van de FSM. Door het gebrek aan evenwicht tussen het potentieel parallellisme en het echt bruikbaar parallellisme binnen de beschikbaar bouwblokken, wordt een techniek genaamd "code-motion pruning" (CMP) voorgesteld om inefficiënt "code motions" te voorkomen.

Resultaten uit experimenten tonen aan dat de toename van het aantal toestanden, door het gebruik van ILP technieken, kan worden beperkt door het samenvatting van gelijke toestanden. Andere resultaten tonen aan dat het percentage oplossingen van goede kwaliteit in de zoekruimte toeneemt door de CMP techniek. Dit baant de weg voor een reductie van de gemiddelde zoektijd.

### **Contents**

|   | Summary                                                                                                                                                                                                                                                                                                                                                                                           | $\mathbf{v}$                                                         |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|   | Samenvatting                                                                                                                                                                                                                                                                                                                                                                                      | vii                                                                  |

|   | Acknowledgements                                                                                                                                                                                                                                                                                                                                                                                  | хi                                                                   |

| 1 | Introduction  1.1 High-level synthesis  1.2 ILP techniques  1.3 ILP in high-level synthesis  1.4 Emerging time-constrained problems  1.5 Outline of this thesis                                                                                                                                                                                                                                   | 1<br>1<br>3<br>4<br>5<br>7                                           |

| 2 | Modeling the problem  2.1 Basic terminology  2.2 Design representation  2.2.1 Modeling behavior  2.2.2 Modeling the data path  2.2.3 Modeling the control unit  2.2.4 Modeling timing  2.3 Formulation of the optimization problem                                                                                                                                                                | 9<br>11<br>12<br>17<br>18<br>20<br>23                                |

| 3 | A constructive approach 3.1 Motivation 3.2 Related high-level synthesis approaches 3.3 Related approaches in the compiler arena 3.4 How our contribution relates to previous work 3.5 An overview of the constructive approach 3.6 The priority encoding 3.7 The constructor 3.7.1 The scheduler 3.7.2 The parallelizer 3.7.3 An example 3.7.4 Discussion 3.8 The Boolean oracle 3.9 The explorer | 27<br>28<br>29<br>30<br>31<br>33<br>34<br>35<br>37<br>40<br>42<br>46 |

| 4 | Code motion                                                                                                                                                                                                                                                                                                                                                                                       | <b>49</b><br>49                                                      |

|   | 4.3 Availability analysis                         | 58  |

|---|---------------------------------------------------|-----|

|   | 4.4 Code compensation                             | 62  |

|   | 4.4.1 Related work                                | 64  |

|   | 4.4.2 Bookkeeping code motions                    | 64  |

|   | 4.4.3 Overcoming the effects of greedy choices    | 68  |

|   | 4.5 Exploiting state equivalence                  | 70  |

|   | 4.5.1 Equivalent states in the SMG                | 71  |

|   | 4.5.2 On—the—fly detection of state equivalence   | 75  |

|   | 4.5.3 Comments on the implementation              | 80  |

|   | 4.5.4 Experimental results                        | 81  |

|   | 4.6 Discussion                                    | 83  |

| 5 | Code-motion pruning                               | 87  |

|   | 5.1 A data–flow analysis technique                | 87  |

|   | 5.1.1 Fundamental notions                         | 88  |

|   | 5.1.2 Formulation of our analysis technique       | 90  |

|   | 5.2 Pruning inefficient code motions              | 96  |

|   | 5.2.1 Motivation                                  | 96  |

|   | 5.2.2 A precedence relation based on the links    | 99  |

|   | 5.2.3 Reordering the sets of available operations | 100 |

|   | 5.3 Experimental results                          | 101 |

|   | 5.3.1 The impact on the search space              | 102 |

|   | 5.3.2 The impact on schedule length               | 105 |

|   | 5.3.3 The impact on the number of states          | 108 |

|   | 5.3.4 Comparison with other methods               | 109 |

|   | 5.4 Discussion                                    | 111 |

| 6 | Towards loop pipelining                           | 113 |

|   | 6.1 Motivation                                    | 113 |

|   | 6.2 Fundamental notions                           | 115 |

|   | 6.3 Related work                                  | 116 |

|   | 6.4 Our approach for loop pipelining              | 118 |

|   | 6.4.1 Required extensions                         | 119 |

|   | 6.4.2 Basic principle                             | 120 |

|   | 6.4.3 An example                                  | 122 |

|   | 6.5 Discussion                                    | 128 |

| 7 | Conclusions                                       | 131 |

|   | 7.1 Concluding remarks                            | 131 |

|   | 7.2 Topics for further research                   | 134 |

|   | References                                        | 137 |

| A | Experimental set-up                               | 143 |

| В | Auxiliary information                             | 145 |

|   | Biography                                         | 147 |

#### Acknowledgements

This Ph.D. thesis reports the research performed in the Design Automation Section of the Department of Electrical Engineering of the Eindhoven University of Technology in the Netherlands, under the supervision of prof.Dr.—Ing. J. A. G. Jess.

I am thankful to prof. Jess for the opportunity to work in his research group. Our first meeting occurred on March 1992, after his lectures during the  $2^{\rm nd}$  Brazilian Microelectronics School, held in the town of Gramado. Since then, many fruitful discussions have followed, influencing my research activities.

I would like to thank Marc Heijligers and Koen van Eijk for their cooperation in different phases of my research work. Marc has introduced me to important issues in high—level synthesis, thereby pointing the first stepping—stones. Koen found the time for various discussions and gave me many suggestions. Through a careful and fast proofreading of the first draft of this thesis, he has indicated various parts of the text requiring elaboration. I am also grateful to Jos van Eijndhoven for his suggestions in the course of my research. I appreciate his welcoming attitude towards me and my family in our early days in the Netherlands.

I would like to express my gratitude to the people whose software I reused or combined within my own programs. Marc Heijligers, Ric Hilderink, Adwin Timmer, Wim Philipsen and Harm Aarts have developed the NEAT System, upon which I have built my implementation. Geert Janssen has developed the BDD package that I have used for Boolean manipulation. The C<sup>++</sup> interface written by Koen van Eijk paved the way to bridging the BDD package with the NEAT System.

Furthermore, I am grateful to my roommate Michel Berkelaar and to Jeroen Rutten. I appreciate their help and our pleasant conversations. Also, I would like to thank all other members of the Information and Communication Systems Group, where I found a well–balanced combination of skills, sociability and good humor.

I am also grateful to the members of the reading committee for their remarks and suggestions.

I owe a lot to my compatriots living in the Netherlands. Special thanks to Carla and Reginaldo, Viviane and Cícero, Sônia and Egbert, Isabel and César, Sílvia, Javier, Luís Barbosa, Carlos, Lincoln, and many others.

Last, but not least, I would like to thank the patience and comprehension of my wife Joice and my son Rafael, who have made of this long stay in the Netherlands, a pleasant experience in family.

I was partially supported by the Federal University of Santa Catarina, my employer in Brazil, and by CNPq (Conselho Nacional de Desenvolvimento Científico e Tecnológico), one of the Brazilian agencies supporting research, under fellowship award n. 200283/94–4.

#### Chapter

## 1 Introduction

The term *instruction-level parallelism* (ILP) stands for the fine-grain parallelism observable among the elementary operations used to build up a program. Traditionally, exploitation of ILP is the object of parallelizing compilers. However, emerging design problems are prompting the utilization of ILP for the *synthesis* of digital systems. This thesis addresses the application of ILP techniques during the synthesis of synchronous digital systems. It focuses on systems which have to operate under a *time constraint*.

Several techniques to deal with ILP are proposed in the compiler—technology arena. Although most of the techniques to *expose* parallelism are quite general, the way of *exploiting* the exposed parallelism varies depending on the target application domain. As a consequence, the techniques conceived in the compiler domain can not be directly applied to the synthesis of time—constrained systems. This is due to the fact that the goal of parallelizing compilers is to optimize average program runtime, while time—constrained systems need support for worst—case runtime.

This chapter presents a brief overview of the available techniques and of the issues involved in the synthesis of digital systems for some emerging applications leading to time—constrained design problems.

#### 1.1 High-level synthesis

The increasing complexity of integrated circuits (ICs) provided by very large scale integration (VLSI) technology requires design automation at higher levels of abstraction, such as the behavioral level and the register—transfer level (RTL). At the behavioral level, the function of a digital system is described in the form of an algorithm which computes the output values of the system from its input values, abstracting from the way the system is actually implemented. At the register—transfer level, the structure of the digital system is described as a netlist of functional units (adders, ALUs, multipliers, etc.), memory elements and interconnect elements (buses, multiplexers, etc.).

High-level synthesis (HLS) has been defined as a translation "from an algorithmic level specification of the behavior of a digital system to a

register-transfer level structure that implements that behavior" [45]. HLS is a field of intensive research and comprehensive surveys can be found in the literature [16] [23].

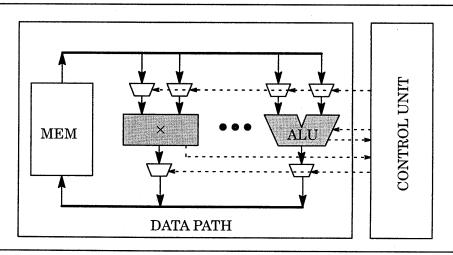

HLS results in the architecture of a digital system, consisting of a data path and a control unit, as shown in Figure 1.1. The data path is described as a network at the register–transfer level and the control unit is usually described in the form of a symbolic finite–state machine. In HLS, the design has to comply with a set of *constraints*, like completion time, throughput rate and execution order and it is driven by a set of *objectives*, like the minimization of IC area, power consumption or number of states.

HLS is usually decomposed in several subproblems, like module selection, allocation, scheduling and binding. *Module selection* determines the kind of resources needed in the data path, *allocation* evaluates how many of such resources are necessary, *scheduling* determines when the operations are executed, and *binding* assigns operations to specific resources. Although these subproblems are interdependent, they are solved separately in most cases, because a completely unified approach seems unpractical. Due to this interdependence, the order of solving these subproblems may lead to different final results. The most suitable order is dictated by the target application domain [63].

FIGURE 1.1. IC architecture at the register-transfer level

Traditionally, HLS tools are oriented to the synthesis of hard-wired VLSI circuits, which are known as *application specific integrated circuits* (ASICs). A recent trend broadens the scope of HLS to include the design of *application specific instruction set processors* (ASIPs), which are programmable circuits

tailored to an application domain [25] [68]. This broader scope has its roots in the adoption of an *architecture template*, as a starting point for HLS. An example of such a template is the MISTRAL architecture [64], which is oriented towards audio applications. This template is the result of early research on silicon compilation, in particular the CATHEDRAL silicon compilers [15], which are successfully used for digital signal processing (DSP) applications.

From a HLS perspective, the design of an ASIP core can be viewed as if module selection and allocation had already been performed, such that a complete data path suitable for the whole application domain is determined. As a consequence, the remaining tasks, scheduling and binding, are responsible for the programmability. After they are performed, the resulting symbolic finite—state machine is then mapped to a microcoded controller. Flexibility is obtained by providing on—chip RAM as control store, allowing microcode downloading. Within this scenario, the role of the remaining tasks is to accomplish the (micro) *code generation* for the application domain specific processor.

#### 1.2 ILP techniques

Modern architectures, such as superscalars and very long instruction word (VLIW) machines, have multiple functional units. They rely on the overlapped execution of independent instructions. Superscalar machines require specific hardware for run—time scheduling and dynamic dependence analysis, while VLIW machines perform compile—time scheduling and static dependence analysis. Although the ILP techniques described here are used by both superscalar and VLIW processors, this thesis focuses on *compile—time scheduling* techniques. A comprehensive overview of specific techniques for superscalar processors can be found in [30].

The traditional scope for exploiting parallelism in early compilers was the basic block (BB), a straight-line code sequence without branches, except at the entry and exit points. Since the amount of parallelism available in a basic block is limited, the ample resources present in modern architectures would be poorly utilized. As a consequence, techniques are required to expose parallelism beyond basic-block boundaries. This is performed by allowing code to move from one BB to another, which is called code motion. Some code motions place instructions ahead of conditional branches, a technique known as speculation.

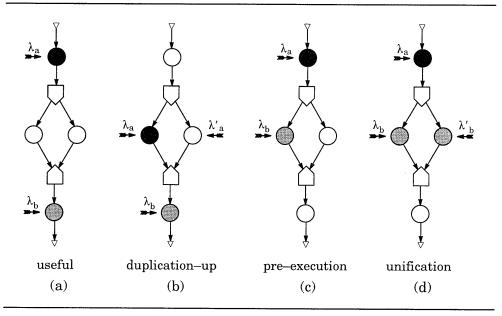

One of the first proposed ILP techniques is Trace Scheduling [22], which takes the most likely execution path and optimizes it as if it were a single basic block. Extra code is inserted to compensate for the side effects of some of the optimizations. However, this technique is not general enough since it assumes a highly predictable control—flow. A more general technique is Percolation Scheduling [48], which defines a set of semantics—preserving code motions. Percolation Scheduling provides a way of exposing parallelism iteratively, by the successive application of primitive code motions.

Nevertheless, these first ILP methods are essentially resource—unconstrained parallelization techniques. Their drawback is that some of the greedily performed code motions might have to be undone, since they can not be accommodated within the available resources. This lack of global management of resources motivated the development of resource—constrained parallelization techniques [19][46][47].

ILP can also be uncovered beyond loop boundaries, by means of a straightforward method called *loop unrolling*. It consists in replicating the loop body several times such that the resulting loop body contains multiple iterations of the original loop and, as a consequence, more parallelism is exposed. A more elaborate technique is *software pipelining*, which is also known as *loop pipelining* or *loop folding*. The main idea of software pipelining is to allow the exploitation of ILP across loop boundaries, by overlapping the execution of instructions belonging to different iterations of a loop, but without unrolling the loop.

A simple and widely used software pipelining technique is Modulo Scheduling [39]. It is a very efficient approach suitable for single basic—block loops, but it does not address properly the software pipelining of loops containing conditional constructs. This more general problem is tackled by other methods like Perfect Pipelining [2][3], which combines loop unrolling and the detection of a repeating pattern to form the pipelined schedule. Another suitable method is Enhanced Pipeline Scheduling [17], which relies on the motion of instructions around the loop.

#### 1.3 ILP in high-level synthesis

Most HLS methods are oriented to data—flow dominated designs. Although loop pipelining is commonly supported [13][24], code motion is rarely addressed [54][70]. Nevertheless, some methods have been proposed to cope with behavioral descriptions containing conditional constructs, such as "if—then—else". Path—based Scheduling [12] and Tree—based Scheduling [34] aim at optimizing the execution time of each path. Others, like conditional vector list scheduling [71][72] and the hierarchical reduction approach [37], are oriented to average execution time. The combination of speculation and

loop pipelining is addressed in [32]. Recently, an approach has been proposed to tackle applications with combined data and control–flow [9]. However, neither code motion nor loop pipelining is supported. Although powerful techniques [44] [67] are available for handling time—constraints, they can not cope properly with optimization under complex control flow, since they are oriented to data—flow dominated applications.

HLS for high-throughput applications, like real-time video encoding and decoding, is addressed in the PHIDEO system [43]. In this application domain, a typical behavioral description is structured as a hierarchy of nested loops. The basic concept of PHIDEO is the assumption that executions of a same operation are periodical in time. The loop hierarchy is translated to periodic operations and scheduling consists of selecting the start times and the periods of the operations [43]. Such specialized techniques for high-throughput applications do not fall within the scope of this thesis.

Since the starting point of HLS is a behavioral description and not a sequence of instructions, the techniques used in this thesis are actually applied to *operations*, instead of instructions. Although the term *operation-level* parallelism would be appropriate, the more usual term instruction-level parallelism is adopted and used throughout this thesis.

#### 1.4 Emerging time-constrained problems

Complex modern digital systems perform several tasks. Their design is typically approached by partitioning the tasks into a data–flow dominated and a control–flow dominated part, such that two different HLS tool–suites can be applied, each one specialized on one of these domains. An instance of this strategy can be found in [11], where the design of a videophone coder–decoder motion estimator is described.

Another example is reported in the design of an IC known as "I.McIC" chip [38][73]. This IC performs MPEG2 video encoding for applications in digital video recorders and cameras. It contains a PHIDEO processor for the high–throughput tasks and a MISTRAL core for the control tasks. The MISTRAL core is designed as an ASIP to provide the necessary programmability. It is conceived to accommodate different standards and all tasks that are subject to change in future products [38]. The behavioral description for the tasks assigned to the ASIP exhibits a structure of nested conditional constructs enclosed by an outer loop [65]. Those tasks must be completed within a limited interval of time. This interval is dictated by the time to process the information in a so–called macroblock of a video picture, which is a composition of one  $16 \times 16$  luminance block and two  $8 \times 8$  chrominance

blocks. In practice, this represents a tight time-constraint, which makes it difficult to add extra functionality to the ASIP, unless a better exploitation of parallelism is envisaged.

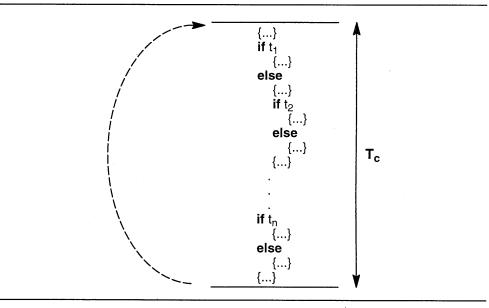

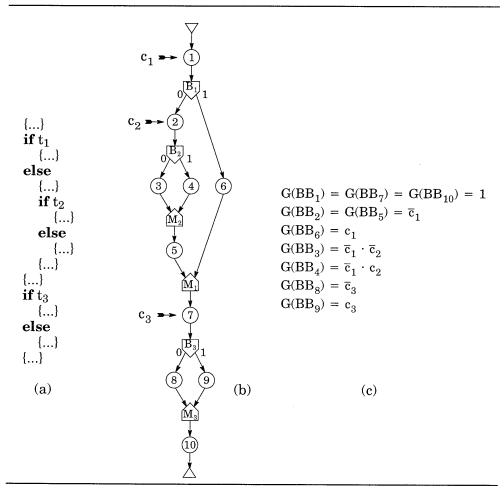

A somewhat similar behavioral description structure, also subject to a global cycle budget, is reported for applications in the area of Asynchronous Transfer Mode (ATM) [61]. A sketch of such a structure is given in Figure 1.2. In the figure, conditional constructs are explicitly shown and  $t_i$  designates the test associated with the  $i^{th}$  conditional construct. Braces represent the basic blocks enclosing operations such as additions, subtractions and multiplications. The dashed arrow represents the outer loop, while the bidirectional arrow depicts the time constraint (e.g. latency, data introduction interval), meaning that an upper bound of  $T_c$  clock cycles must be satisfied for the worst–case execution of the loop body.

FIGURE 1.2. Structure of a behavioral description under a time constraint

For these emerging problems, whose structure is sketched in Figure 1.2, if optimization is restricted to the scope of basic blocks, it might be impossible to meet a tight time-constraint. In this scenario, the application of ILP techniques, such as code motion, speculation and loop pipelining may reduce the schedule length of the critical execution path and grant time-constraint feasibility. Besides, the combination of intensive data-flow, complex control-flow and time constraints creates a challenging problem to which few solutions have been proposed, as shown in the previous section.

These reasons motivate the research described in this thesis, where the application of ILP techniques is oriented to the satisfaction of time constraints, instead of execution speeding up. As a consequence, speeding—up techniques such as those based on branch prediction are not addressed. More information on the application of prediction—based techniques in the domain of HLS can be found in [32].

#### 1.5 Outline of this thesis

As opposed to classical compilers, synthesis tools for embedded system design can often afford to spend more time on optimization. The effort in saving a few clock cycles to meet a tight constraint tends to outdo a redesign from scratch. For this reason, a good exploration of the design space is very important in HLS.

This thesis proposes a *constructive* approach oriented to the *synthesis* of time-constrained digital systems. The approach provides a way of *generating* and *exploring* several alternative solutions to a given optimization problem.

The proposed approach assumes that module selection and the allocation of functional units have been performed beforehand. In other words, the number and kind of functional units, henceforth referred to as *resource constraints*, are fixed prior to scheduling. Therefore, a *resource-constrained optimization problem* is formulated as a starting point. In the construction of each solution, ILP techniques are used in such a way that the parallelism exposed is constrained by the available resources. In this thesis, we assume that binding, along with the allocation of registers and interconnect elements, will be performed after scheduling.

An advantage of adopting a resource—constrained optimization problem as a starting point is that it paves the way to an unified approach comprising not only the synthesis of ASICs, but also the code generation for ASIPs, if registers and interconnect elements are also modeled as resource constraints.

The topics addressed in this thesis are organized as follows.

Chapter 2 describes the design representation and the terminology used throughout the thesis and defines the optimization problem to be tackled.

Chapter 3 summarizes the proposed constructive approach. It explains the interaction between the several engines which co-operate in the construction of a solution to the optimization problem.

Chapter 4 addresses code motion and related issues. It explains how code motion and speculation are modeled and induced in the frame of our

approach. Also, an expedient called code compensation is introduced for coping with some side effects of code motion. This broadens the range of legal code motions supported in the approach. In addition, a technique is proposed to control the growth of the number of states when code motion and speculation are applied. This technique exploits the notion of state equivalence in the course of scheduling. The experimental results in this chapter show that when a HLS tool is required to make use of flexible code motions in order to face a tight time—constrained problem, the resulting number of states would be unpractical if the notion of state equivalence is overlooked during scheduling.

Chapter 5 focuses on code—motion pruning, a technique proposed to prevent inefficient code motions. It shows that, due to the typical unbalance between the potential parallelism and the constrained amount of resources to accommodate it, some code motions do not contribute to shortening schedules and, as a consequence, they are not worth doing from a worst—case execution perspective. The experimental results reported in this chapter show that the application of the pruning technique increases the density of promising solutions observable during the search, paving the way to a reduction of average search time.

Chapter 6 addresses ILP techniques for dealing with loops. First, it explains the deficiencies of modulo scheduling in properly handling loop bodies containing conditional constructs. Then, it describes how our approach can be extended for inducing loop pipelining. The chapter illustrates the close relationship between code motion and loop pipelining.

Chapter 7 contains concluding remarks and suggestions for further work. It places the application of ILP techniques in perspective with some on–going work on related research topics.

#### Chapter

## 2

## Modeling the problem

#### 2.1 Basic terminology

Similarly to a high-level programming language, the core of a behavioral description consists of statements, conditional constructs and loop constructs. Statements define the *operations*, whereas conditional and loop constructs specify *conditional execution*.

As a consequence of conditional execution, a *flow of control* is introduced, creating junctions among different sequences of statements. A *junction* in the control flow is either a *fork*, where the flow diverges from a point, or a *join*, where the flow converges to a point. When associated with a conditional construct, a divergent junction is called a *branch* and a convergent junction is called a *merge*. Junctions split the control flow into basic blocks. A *basic block* (BB) is a sequence of consecutive statements in which the flow of control enters at the beginning and leaves at the end, without junctions in between.

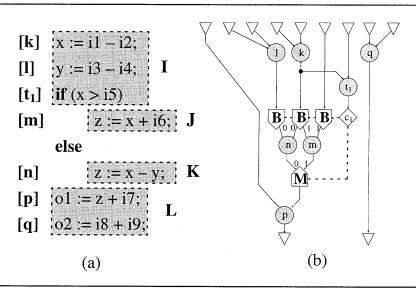

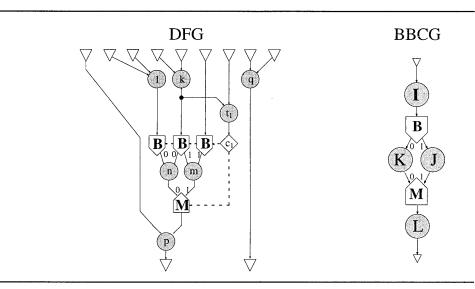

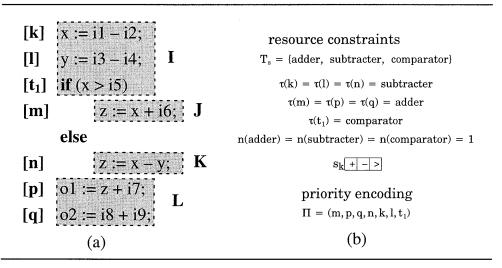

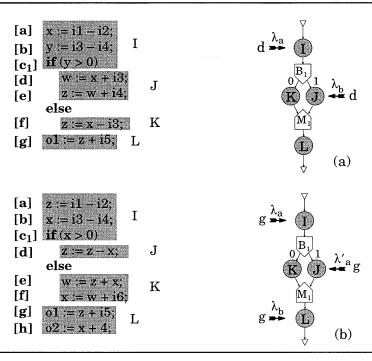

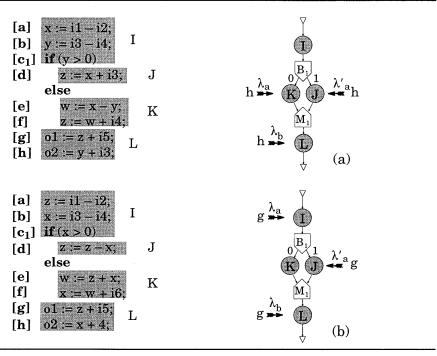

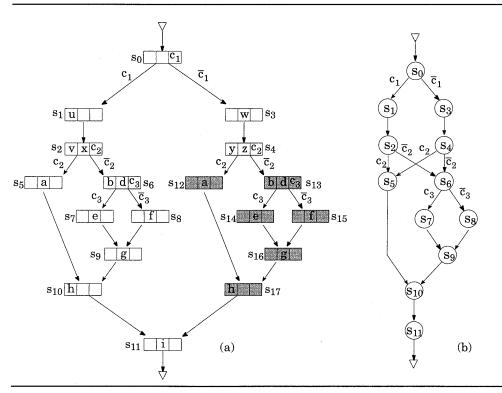

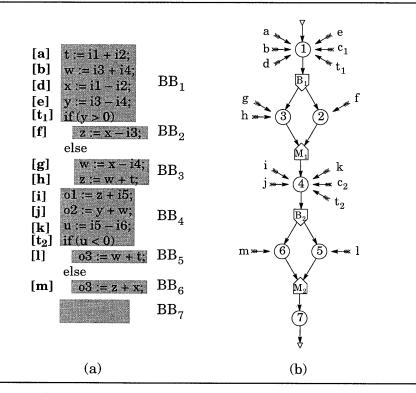

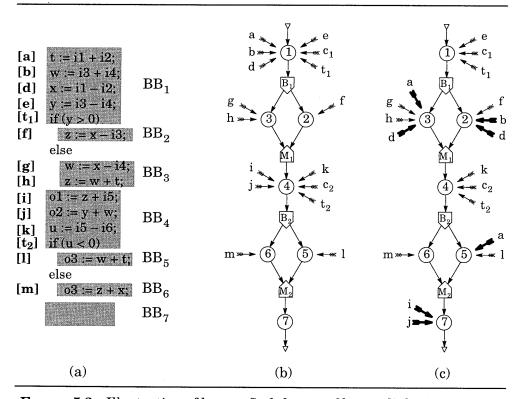

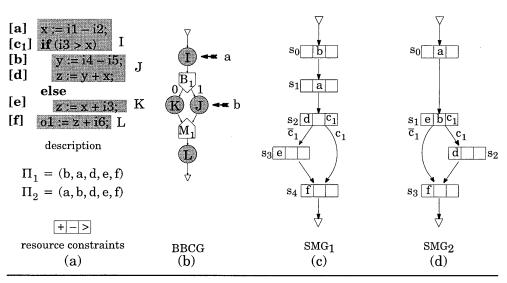

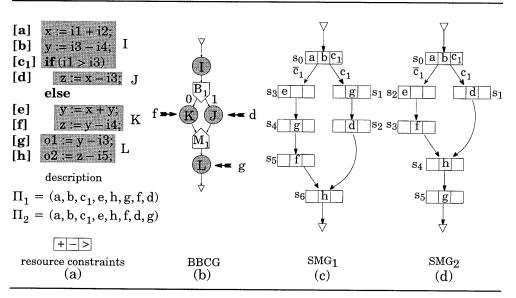

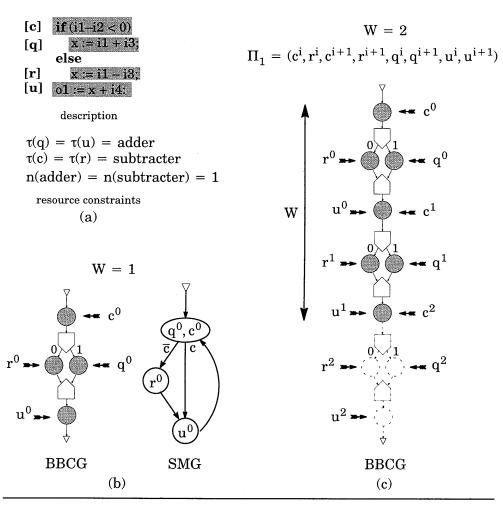

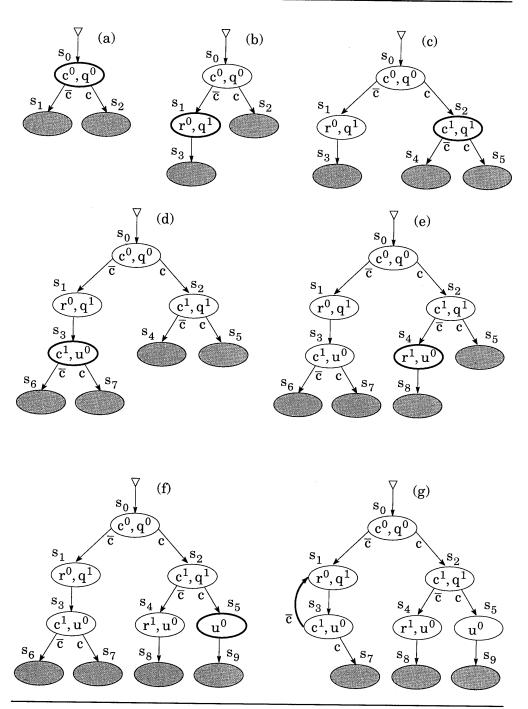

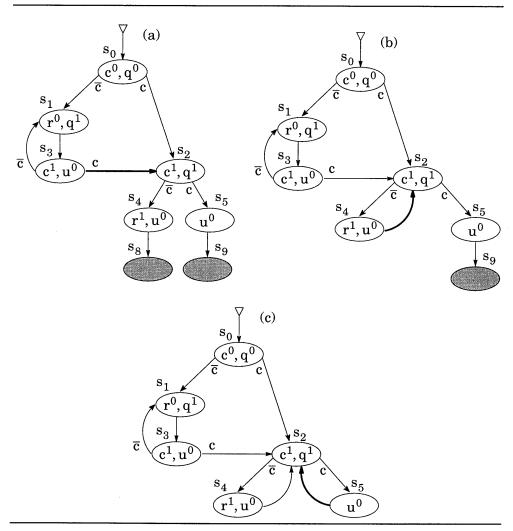

Consider, for instance, the description in Figure 2.1, where  $i_1$  to  $i_9$  represent inputs,  $o_1$  and  $o_2$  designate outputs and x, y and z are local variables. Operations are labeled with small letters at the left of their respective statements. In this description, a branch junction occurs after  $t_1$  and a merge junction before p. As a result, the control flow exhibits four BBs, which are depicted by the shadowed boxes and are labeled with capital letters.

Among the operations in a behavioral description, some perform relational tests (e.g. >, ==,  $\le$ ) and produce a Boolean value as outcome. Depending on the result of the test, a conditional branch will occur in the control flow. The operations which do not perform a test are called ordinary operations (e.g. +, -,  $\times$ ) or simply operations, whenever clear from the context.

The exploitation of parallelism in a behavioral description is constrained by the available resources, the so-called *resource constraints*. For the description in Figure 2.1, we assume, throughout this chapter, that an adder, a subtracter and a comparator are available.

Let us now analyze how the operations in the example of Figure 2.1 can be scheduled. We could think of scheduling each BB independently. Such

straightforward approach would not be efficient, because the amount of parallelism within a BB is limited. For example, in BB I the adder would remain idle during two cycles, even though operation q in BB L could be scheduled at the same time step as either k or l. The example suggests that we should exploit parallelism across BB boundaries, by allowing operations to move from one BB to another. This is called *code motion*.

Two operations can not always be executed in parallel, even if there are free resources. For example, operation m can not be executed in parallel with operation k, because the value of variable x consumed by operation m depends on the value produced by operation k. We say that operation m is data dependent on operation k. On the other hand, since there is no data dependence between operations q and k, they could be executed simultaneously. Note that, if operation q is allowed to move from BB L into BB I, a cycle will be saved in BB L. Since data dependences limit the order in which operations can be executed, they are sometimes called *precedence constraints*.

FIGURE 2.1. A behavioral description with conditional constructs

As a consequence of conditional execution, another kind of dependence arises. For instance, while operation q is always executed, operations m and n are conditionally executed, depending on the result of test  $t_1$ . We say that operations m and n are *control dependent* on test  $t_1$ .

Code motion may occur across branch junctions, because control dependences can be disregarded under certain circumstances, as opposed to data dependencies. For example, although m is control dependent on  $\mathbf{t}_1$ , they are not data dependent on each other and can be executed simultaneously. For the same reason, m and l could be executed in parallel. In both scenarios, the

motion of m from BB J to BB I causes the violation of a control dependence. However, this kind of motion is legal, provided that some mechanism be used to preserve semantics. This is obtained by either committing or discarding the result of the moved operation, as soon as the outcome of the test is known. The technique of moving an operation ahead of a conditional branch is called speculation or speculative execution. Note that, if operation m is speculatively executed and the result of test  $\mathbf{t}_1$  turns out to be true, a cycle will be saved, otherwise there will be no savings.

In the general case, it may be necessary to insert extra code in order to "clean" the outcome of the speculatively executed operation, the so-called *compensation code*. For this example, however, no compensation code is needed, since variable z (assigned by operation m) will be overwritten by operation n, if the result of test  $t_1$  turns out to be false.

When operations move across merge junctions, they do not violate control dependences. For instance, we can consider moving operation q into BB K, as it can be executed in parallel with operation n. However, as operation q must always be executed and the operations in BB K are only executed when the result of  $t_1$  is false, a copy of q has to be placed at the end of BB J. As a result, we say that duplication takes place and the copy can be seen as a form of compensation code. For this example, duplication saves a cycle if the result of  $t_1$  is false, but there are no savings otherwise.

To accomplish a code motion, the moved operation has to be deleted from its original position, copies might be inserted as compensation code and sometimes the control flow itself has to be changed. This whole procedure is known as *bookkeeping* in compiler—technology terminology and it is addressed in Chapter 4.

#### 2.2 Design representation

This section describes the design representation used throughout this thesis. It introduces the main notions used to model the system behavior, the data path structure, the symbolic description of the control unit and the execution timing.

Since most of our modeling relies on graph representations, it is convenient to briefly recollect some graph concepts [14] and associate them with the notation adopted throughout this text.

A graph G = (V, E) consists of a set of nodes V and a set of edges E, where  $E \subseteq V \times V$ . Most of the graphs in this thesis are directed graphs. In a

directed graph, the set E consists of ordered pairs of nodes and its elements are directed edges. If (u, v) is a directed edge, we say that (u, v) *leaves* node u and *enters* node v. Also, u is called a *predecessor* of v and v is said to be a *successor* of u. Given a node v, the set of all predecessors of v is denoted by PRED(v) and the set of all successors is designated by SUCC(v). The *out-degree* of a node v, written outdegree(v), is the number of edges leaving it. Conversely, the *in-degree* of a node v, written indegree(v), is the number of edges entering it. A fundamental notion throughout this thesis is the concept of a path, as defined below.

#### **DEFINITION 2.1**

A path in a graph G=(V,E), from node  $v_0$  to node  $v_k$ , is a sequence  $\langle v_0,v_1,...,v_k\rangle$  of nodes such that  $(v_{i-1},v_i)\in E$ , for i=1,2,...,k.

A path is *simple* if all nodes in the path are different. A *subpath* is a contiguous subsequence of the nodes of a path. A path  $\langle v_0, v_1, ..., v_k \rangle$  in a directed graph is said to form a *cycle* if  $v_0 = v_k$  and it contains at least one edge. A cycle is called *simple* when  $v_1, v_2, ..., v_k$  are distinct. A graph with no cycles is *acyclic*. In this thesis, since only simple cycles are of interest, the term cycle is used to mean a simple cycle. Two other central notions throughout this thesis, reachability and topological ordering, are highlighted below, where  $v_i$  and  $v_j$  designate arbitrary nodes of a directed graph G = (V, E).

#### **DEFINITION 2.2**

Given a directed graph G = (V, E) and two arbitrary nodes  $v_i, v_j \in V$ , node  $v_i$  reaches node  $v_j$  via p, written  $v_i \stackrel{p}{\rightarrow} v_j$ , if there is a path p from  $v_i$  to  $v_j$ .

Sometimes, it is unnecessary to name the path from  $v_i$  to  $v_j$ . We write  $v_i \stackrel{*}{\Rightarrow} v_j$  to mean that there is a path from  $v_i$  to  $v_j$ . Note that this path may be trivial if  $v_i = v_i$ .

#### **DEFINITION 2.3**

Given a directed acyclic graph G = (V, E), a topological ordering of G is a linear ordering  $<_T$  of all its nodes such that if an edge  $(v_i, v_j) \in E$ , then  $v_i$  precedes  $v_i$  in the ordering, written  $v_i <_T v_i$ .

#### 2.2.1 Modeling behavior

In HLS, a behavioral description is usually compiled to an intermediate representation. In this thesis, behavior is modeled in the form of a data flow graph, as defined below.

#### **DEFINITION 2.4**

A data flow graph DFG = (V, E) is a directed graph, where V is the set of nodes, representing operations, and  $E \subseteq V \times V$  is the set of edges, representing dependences between operations.

Several DFG representations are available in the literature and the choice of a particular representation does not limit the application of ILP techniques. In this thesis, we adhere as much as possible to the so-called ASCIS model [21].

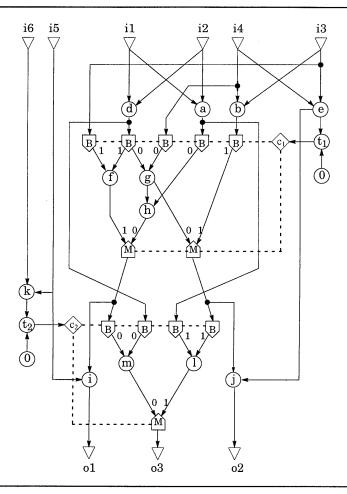

We assume that the behavioral description contains conditional constructs and that the respective DFG has special nodes to represent them. In the literature, a DFG supporting conditional constructs is also known as a control data flow graph (CDFG). An example is shown in Figure 2.2b for the description in Figure 2.2a. Circles represent either ordinary operations or tests. Triangles denote inputs or outputs. Pentagonal nodes are associated with control–flow decisions. A branch node (B) distributes a single value to different operations and a merge node (M) selects a single value among different ones.

Branch and merge nodes are controlled by a dummy node called a *conditional*, which is represented by a diamond in Figure 2.2b. A conditional transfers the outcome of a test to branch and merge nodes. It provides a simple way of modeling the fact that the result of a test is not necessarily used immediately after its evaluation. For instance, the outcome of a test can be stored to be recovered later on or it might not be available instantly (see Section 2.2.4).

The flow of data between operations is represented by *data edges*. The outcome of a test is carried by *control edges* (dashed edge in Figure 2.2b) from the conditional to branch and merge nodes. A detailed explanation of those symbols and their semantics can be found in [20].

Our DFG model also has special nodes to represent loop constructs. However, for simplicity, we postpone the discussion of loops to Chapter 6.

The operations in a DFG can be classified in different *operation types*, such as addition, subtraction, merge, branch, conditional, etc., as formalized below.

#### **DEFINITION 2.5**

Let  $T_v$  be the set of operation types such that  $T_v = T_o \cup T_x$ ,  $T_x = \{branch, merge, conditional\}$  and  $T_o = T_v \setminus T_x$ . The function  $\omega : V \mapsto T_v$  represents the mapping of an operation v to an operation type  $t_v$ .

Note that the set  $T_o$  contains the operation types associated with tests and ordinary operations, whereas the set  $T_x$  contains the types of special nodes representing conditional constructs.

In general, we refer to some node of the DFG as an operation  $v_k \in V$ . However, we sometimes need to emphasize, in the notation, the distinction

between a test, a conditional and an ordinary operation. When necessary, a test is designated by  $t_k$ , a conditional by  $c_k$  and an ordinary operation by  $o_k$ . Most of the time, however, we use the terms test and conditional interchangeably, since they refer to closely related notions.

FIGURE 2.2. A behavioral description and its DFG

In order to help us to keep track of code motion, an auxiliary graph is defined below. This graph is a condensation of the DFG.

#### **DEFINITION 2.6**

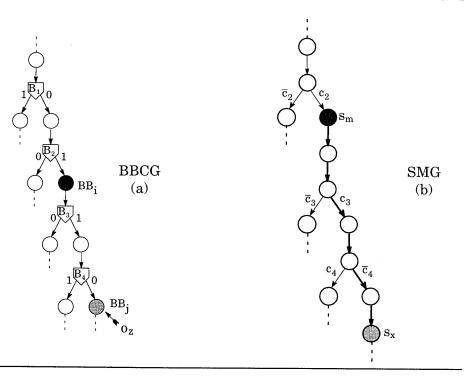

A basic-block control flow graph BBCG = (U, F) is a directed graph, where U is the set of nodes, representing basic blocks or junctions, and  $F \subseteq U \times U$  is the set of edges, representing the flow of control.

The BBCG is derived during a depth–first traversal of the DFG and it is built as follows. All operations in the DFG which are enclosed between a pair of branch and merge nodes controlled by the same conditional are condensed in the form of a basic block in the BBCG. All branch (merge) nodes in the DFG controlled by the same conditional are condensed into a single branch (merge) node in the BBCG domain. Similarly, all input nodes are contracted to a single source node and all output nodes to a *sink* node.

Figure 2.3 shows both the DFG and the BBCG for the description in Figure 2.1. In the BBCG, circles represent basic blocks and each BB is associated with a set of operations in the DFG. Branch and merge junctions in the control flow are explicitly represented, in the BBCG domain, by branch (B) and merge

(M) nodes, which are drawn as pentagons. Triangles denote the source and the sink nodes.

FIGURE 2.3. A DFG and its associated BBCG

In general, we designate by  $u_i$  an arbitrary node of the BBCG, although we sometimes distinguish a BB from branch and merge junctions in the notation. A basic block is denoted as  $BB_i$ , whereas  $B_k$  and  $M_k$  respectively represent branch and merge junctions associated with some conditional  $c_k$ .

Note that, for a given branch node  $B_k$ , the flow of control reaches a different BB, depending on the outcome of conditional  $c_k$ . In Figure 2.3b, this is marked by labeling the edges leaving the branch node with "1" and "0", depending on whether the outcome of  $c_1$  is true or false, respectively. We sometimes make a distinction on which BB is reached, as follows. Given a branch node  $B_k$ , we denote as  $\mathrm{succ}(B_k, \mathrm{true})$  the  $\mathrm{successor}$  of  $B_k$  when the outcome of conditional  $c_k$  is true. Similarly,  $\mathrm{succ}(B_k, \mathrm{false})$  designates the  $\mathrm{successor}$  when the result of  $c_k$  is false.

A path  $\langle u_0, u_1, \ldots, u_k \rangle$  in the BBCG=(U, F) with  $u_0$  = source and  $u_k$  = sink is called a control path. As the outcome of the tests is dependent on some setting of the data, the taken control path can be determined at execution time only. The set of operations enclosed by the BBs contained in a given control path is here called a trace or execution instance. In other words, each path in the BBCG corresponds to exactly one trace in the DFG. We say that an operation  $o_n$  executes on a control path  $o_n$  is in the trace associated with  $o_n$ .

The relationship between the DFG and the BBCG is kept by means of so-called *links*. A link connects one node v in the DFG with a node u in the

BBCG. Links play an important role in modeling code motion and for this reason we will especially be interested in the links connecting ordinary operations and tests to BBs. From now on, we will use the notation  $o_n \stackrel{\lambda}{\to} BB_i$  to designate that an operation  $o_n$  is connected to a basic block  $BB_i$  by means of link  $\lambda$ . This notion is illustrated in Figure 2.4, where each arrow represents a link. Only links from operations and tests are shown. Note that, in Figure 2.4, each operation is linked to the BB where it was initially described. We say that each operation is linked to its *initial* BB, or equivalently, that a set of *initial links* is defined. The fact that an operation  $o_n$  is *not* linked to a basic block  $BB_i$  is denoted as  $o_n \not \to BB_i$  throughout this thesis.

FIGURE 2.4. The initial links for the example in Figure 2.2

Now we formalize some classical notions from the compiler–technology domain [7], by casting them into our own representation. The notions of domination, postdomination and control equivalence are useful during bookkeeping. The definitions below assume an acyclic BBCG=(U, F) with single–source and single–sink nodes and in which  $u_i, u_j \in U$ .

#### **DEFINITION 2.7**

Node  $u_i$  dominates node  $u_j$ , written  $u_i$  dom  $u_j$ , if every path from the source to  $u_j$  includes  $u_i$ .

#### **DEFINITION 2.8**

Node  $u_j$  postdominates node  $u_i$ , written  $u_j$  pdom  $u_i$ , if every path from  $u_i$  to the sink includes  $u_i$ .

#### **DEFINITION 2.9**

Nodes  $u_i$  and  $u_j$  are *control equivalent*, written  $u_i$  equiv  $u_j$ , if and only if  $u_i$  dominates  $u_i$  and  $u_i$  postdominates  $u_i$  or vice-versa.

Note that, in the BBCG shown in Figure 2.3, BB I dominates BB K, but BB K does not postdominate BB I, while BBs I and L are control equivalent.

#### 2.2.2 Modeling the data path

The data path is modeled as a set of interconnected components, such as functional units, multiplexers and memory elements, which are here called *modules*. The data path is represented in the form of a graph, as defined below. Although this graph is a very abstract model for the RTL structure, it is sufficient for the purposes of this thesis.

#### **DEFINITION 2.10**

A network graph NWG=(M, W) is an undirected graph, where M is the set of nodes, representing modules, and  $W \subseteq M \times M$  is the set of edges, representing the connectivity of the modules.

The modules are classified according to their function, such as adder, multiplier, register, etc. This leads to the notion of *module type*. The mapping between modules and types is formalized as follows.

#### **DEFINITION 2.11**

Let M be a set of modules and  $T_m$  be a set of module types. The function  $\mu: M \mapsto T_m$  maps a module m to a module type  $t_m$ .

In HLS, the relation between operation types and module types is usually described in the form of a *library*. For example, given a set of module types  $T_m = \{adder\_subtracter, ALU, ripple\_carry\_adder, multiplier\}$ , we could instantiate modules by choosing from the set  $T_m$ . A plus—operation could be performed on any module of the three first types and a multiplication, on the last one only. This notion is formalized below.

#### **DEFINITION 2.12**

The operation mapping function  $\beta: T_o \mapsto P(T_m)$  maps each operation type  $t_o \in T_o$  to the subset of the available module types on which it can be executed.

For the example given above, we could thus write:  $\beta(\times) = \{\text{multiplier}\}\$ and  $\beta(+) = \{\text{adder\_subtracter}, ALU, \text{ripple\_carry\_adder}\}.$

Since an operation can be executed on various module types, it is the task of module selection to choose a subset of suitable module types, say  $T_s \subseteq T_m$ , and to assign each operation to a single module type  $t_s \in T_s$ , according to the formulation below.

#### **DEFINITION 2.13**

Let  $V_o = \{v \in V \mid \omega(v) \in T_o\}$ . The operation assignment function  $\tau : V_o \mapsto T_s$  maps each operation v to a selected module type  $t_s$  such that  $t_s \in \beta(\omega(v))$ .

#### 2.2.3 Modeling the control unit

As a consequence of the application of ILP techniques during scheduling, the operations from different parts of the DFG are packed together for simultaneous execution. In this thesis, the operations executing in parallel are represented in the form of a state, and an execution sequence is represented by transitions between states. When a given state  $s_k$  is reached, all operations associated with it are executed simultaneously. These notions are also cast into a graph representation, as follows.

#### **DEFINITION 2.14**

A state machine graph SMG = (S,T) is a directed graph, where S is set of nodes, representing states, and  $T \subseteq S \times S$  is the set of edges, representing transitions.

The SMG can be seen as a prototype for the state transition diagram of the underlying finite state machine (FSM), whose formal definition can be found, for instance, in [16].

We assume that the SMG has dummy nodes called *source* and *sink* states. The duration of every state is one clock cycle, except for the sink and the source, whose execution is assumed to take no time.

Recall from Section 1.4 that our goal is to focus on design problems subject to a global time–constraint  $T_c.$  From a DFG perspective, the time constraint can be interpreted as follows. The difference between the time when the input values are available and the time when the output values are determined can not exceed  $T_c$  clock cycles. The availability of input values in the DFG can be interpreted in the SMG domain as a transition from the source to an initial state  $s_0$ , whereas the availability of output values can be interpreted as a transition from a state  $s_{k-1}$  to the sink. As a consequence, the time to execute all the operations in every path from  $s_0$  to  $s_{k-1}$  must not exceed  $T_c$  clock cycles. This notion is formalized as follows.

#### **DEFINITION 2.15**

Given a simple path  $p = \langle source, s_0, s_1, ..., s_{k-1}, sink \rangle$  in a SMG, the *schedule length of path* p, written  $L_p$ , is the number k of states included in path p.

Our main goal is to find SMGs for which the inequality  $max(L_p) \leq T_c$  holds for every path p. For simplicity, we sometimes refer to the path with greatest schedule length as the "longest" path in the SMG.

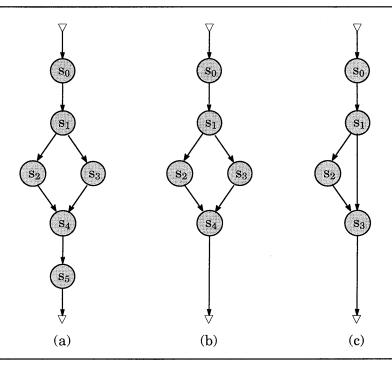

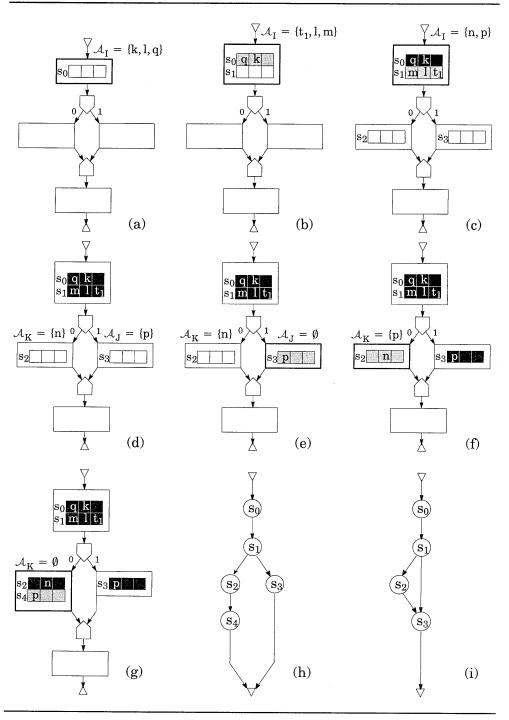

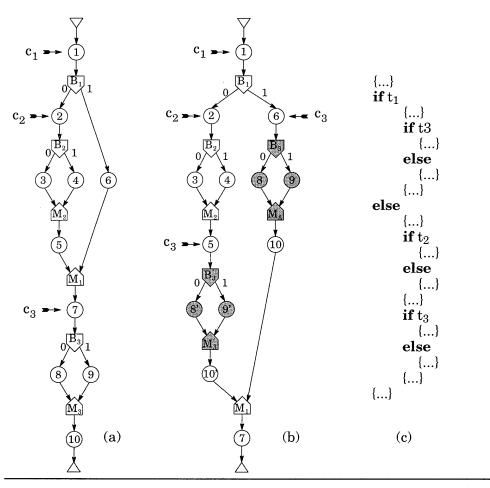

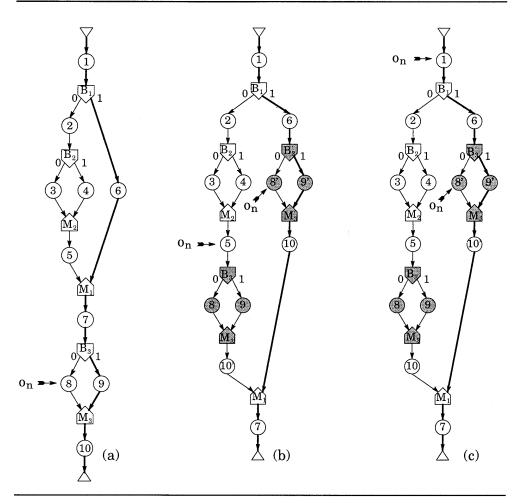

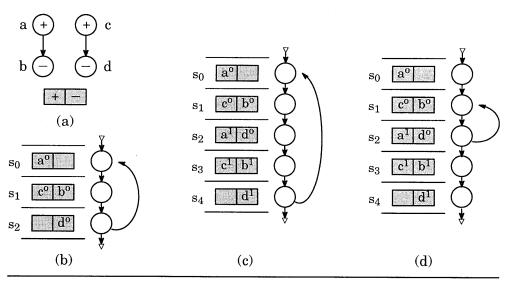

Given DFG and a set of resource constraints, several different SMGs can be synthesized, depending on how the operations are packed together. Figure 2.5 illustrates alternative SMGs, synthesized from the DFG in Figure 2.2b.

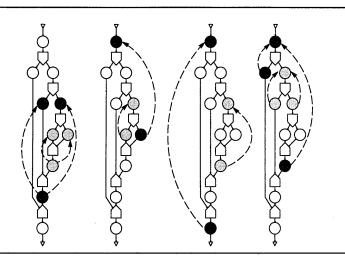

FIGURE 2.5. Alternative SMGs for the DFG in Figure 2.2b

To construct the first SMG in Figure 2.5a, exploitation of parallelism is restricted within BB boundaries. The remaining alternatives, however, are constructed using code motion. The operations executed in each of the states in those SMGs are given in Table 2.1. Although all alternatives comply with resource and precedence constraints, they have different properties. The choice of the most convenient alternative is based on the design objectives. For example, if we want to minimize completion time, the SMG in Figure 2.5a is of inferior quality when compared to the others. If we also want to reduce the number of states as a second objective, the SMG in Figure 2.5c should be preferred.

TABLE 2.1 Operations executed in each state for the SMGs in Figure 2.5

| SMG | $\mathbf{s}_0$ | $\mathbf{s}_1$            | $\mathbf{s}_2$ | $\mathbf{s}_3$ | $s_4$ | $\mathbf{s}_5$ |

|-----|----------------|---------------------------|----------------|----------------|-------|----------------|

| (a) | k              | $l, t_1$                  | n              | m              | p     | q              |

| (b) | k, q           | $\mathbf{l},\mathbf{t}_1$ | n              | m              | p     | _              |

| (c) | k, q           | $l, m, t_1$               | n              | p              | _     | _              |

In the context of code generation, the number of states in the SMG correlates with code size. The application of code motion may lead to SMGs with a larger number of states. In the compiler—technology arena, this is known as *code expansion* or *code explosion*. In this thesis, we sometimes use these customary terms informally to mean an increase in the number of states.

In summary, the DFG is the starting point for synthesis. The NWG is obtained by performing allocation and module selection. Our goal is to obtain a SMG complying with both design constraints and objectives. The BBCG is a useful intermediate representation which assists on the construction of a SMG from the DFG, under the resource constraints imposed by an already defined NWG.

#### 2.2.4 Modeling timing

The amount of time spent to execute an operation of the DFG on a module of the data path is usually modeled with the notion of *delay*. Different operations might have different delays. As a consequence, delays are usually normalized to the clock cycle and are represented by positive real numbers.

In general, the execution delay depends on both the operation type and on the module type (e.g. a plus-operation executes faster on a carry look-ahead adder than on a ripple-carry adder). This notion is formalized below.

#### **DEFINITION 2.16**

The execution delay is a function  $\delta: T_o \times T_m \mapsto \mathbb{R}^+$ , such that  $\delta(t_o, t_m)$  represents the number of clock cycles taken by module type  $t_m$  to complete the execution of an operation of type  $t_o$ .

Timing can also be affected by the advance choice of a controller. Although the synthesis of the controller is performed at a later phase of the design flow, the fact that a controller architecture is chosen beforehand imposes extra constraints for HLS. Although this problem can be postponed by performing a re–scheduling during the synthesis of the controller [42], a more elaborate approach is proposed in [36] for addressing this issue *during* HLS. This is performed by extending the DFG representation so as to capture the effects of the advance choice of a controller. In the following, we illustrate how one of this effects can be captured in our DFG representation. A detailed discussion of this issue can be found in [36].

Assume that the symbolic FSM generated by HLS is mapped to the microcoded controller of an ASIP. The operations assigned to a state of the symbolic FSM are mapped to a *micro-instruction* format. A micro-instruction consists of a number of operation fields. Each field is associated with the

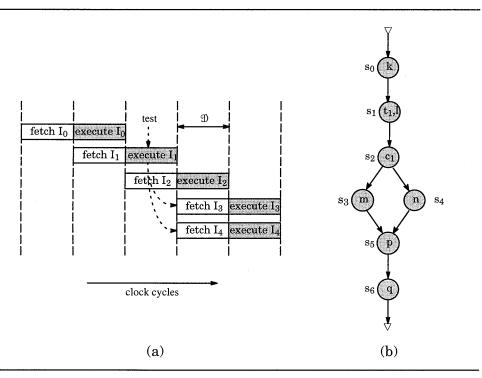

control signals steering the modules involved in the execution of a given operation. The micro-instructions are kept in a control-store memory, from where they are fetched prior to execution. It might be necessary to overlap the micro-instruction fetch in the control unit and the execution in the data path, for reducing the overall critical path. As a result, the whole digital system may be organized as a pipeline, by the proper insertion of registers to isolate pipeline stages. As a result of the latency of the pipeline, a delay occurs between the time in which the outcome of a test operation is made available to the control unit and the time when it actually influences the data path. This time interval is known as *delay slot*, which we denote as  $\mathfrak D$ . Given a pipeline with n stages, the delay slot is equal to n-1 clock cycles [36].

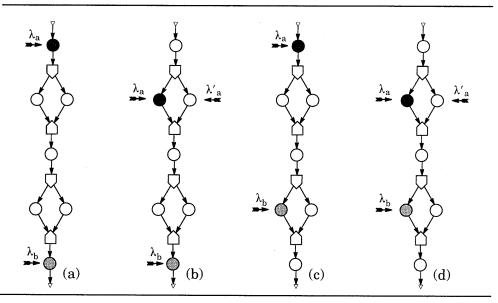

FIGURE 2.6. The notion of delay slot

If the effect of the latency of the pipeline is overlooked during HLS, the generated FSM may turn out not to satisfy the time constraint during microcode generation. To overcome this problem the effect of the latency of a pipeline can be modeled during HLS by associating a delay  $\mathfrak D$  to every conditional  $c_k$  in the DFG. This notion is illustrated in Figure 2.6. A simple pipeline with 2 stages is sketched in Figure 2.6a, where the  $k^{th}$  micro—instruction is denoted by  $I_k$  and the delay slot is indicated by  $\mathfrak D$ . In the first stage, a micro—instruction is fetched and in the second, it is executed. In Figure 2.6b,

a SMG is constructed such that the delay slot is taken into account. Note that the operations executing in state  $s_k$  (Figure 2.6b) correspond to micro–instruction  $I_k$  (Figure 2.6a). Assume that a test is executed in micro–instruction  $I_1$ . Depending on the outcome of test  $t_1$ , either  $I_3$  or  $I_4$  will be executed. Since one of them has to be fetched, the operations associated with the fetched micro–instruction will be executed one cycle later, after a delay  $\mathfrak D$ .

Recall that, after module selection is performed, the operation assignment  $\tau$  is determined. This fact allows us to combine the effects of execution delay and delay slot into the concept of operation delay, as defined below:

#### **DEFINITION 2.17**

The *operation delay* is a function  $d: V \mapsto \mathbb{R}^+$ , such that:

$$d(v) = \begin{cases} \delta(\omega(v), \tau(v)), if \omega(v) \in T_0 \\ \mathfrak{D}, if \omega(v) = conditional \\ 0, if \omega(v) = branch \ \lor \ \omega(v) = merge \end{cases}$$

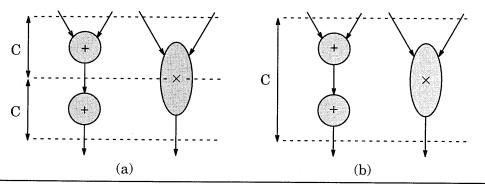

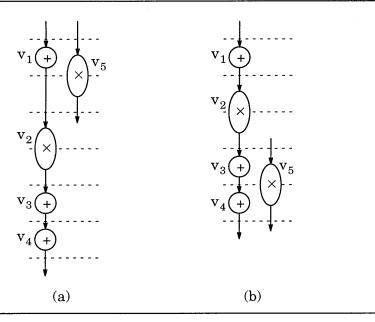

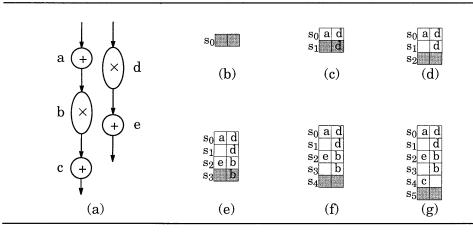

Note that an operation delay is a fraction of a clock cycle. If d(v) > 1, an operation v is said to be a *multicycle* operation, which means that its execution takes longer than a single cycle. On the contrary, when d(v) < 1, more than one operation could be executed within a clock cycle. This leads to the notion of *chaining*, which is the execution of data-dependent operations within a clock cycle. The occurrence of multicycling or chaining depends on the choice of value for the clock cycle. For instance, assuming that the execution delay of a multiplication is twice the execution delay of an addition, the multiplication in Figure 2.7a is a multicycle operation, while the additions in Figure 2.7b are chained.

FIGURE 2.7. The notions of multicycling and chaining

A module can be designed to operate as a *pipeline*, which means that it can process new input data while the execution for some old input data is still

unfinished, in such a way that the processing of different data can be overlapped.

#### **DEFINITION 2.18**

The data introduction interval is a function dii:  $T_m \mapsto \mathbb{N}^+$ , such that dii( $t_m$ ) represents the minimal number of clock cycles required between different executions of a same module of type  $t_m$ .

Although each operation takes d(v) cycles for completion, successive execution of operations can be issued each  $dii(\tau(v))$  cycles. If  $dii(\tau(v)) < d(v)$  then the execution is pipelined, otherwise the module does not operate as a pipeline, since it just starts the execution of the next operation after the completion of the previous one.

Part of the formulation in this section summarizes some of the major achievements of years of research in design representation for HLS, which are borrowed from many sources such as [16][21][28][63][66]. Other notions, however, are especially introduced as a consequence of our focus on ILP techniques applied to synthesis. The described design representations are implemented using the so-called NEAT System [29], an object-oriented framework for HLS.

# 2.3 Formulation of the optimization problem

Throughout this thesis, it is assumed that allocation and module selection have already been performed. As a result, the selected module types, the number of modules per type and the assignment of operations to module types are considered to be known and fixed. This is formalized as follows.

Recall that  $T_m$  designates the set of module types in the library, and that  $T_s \subseteq T_m$  is the set of *selected* module types. Also, remember that the function  $\tau: V \mapsto T_s$  maps each operation on a selected module type. Finally, let  $n(t_s)$  be the number of selected modules of type  $t_s$ . From now onwards, it is assumed that  $T_s$  is determined, that  $n(t_s)$  is known for each  $t_s \in T_s$  and that the mapping  $\tau$  has been accomplished. These parameters represent *resource constraints* for further synthesis steps. Without loss of generality, the application of resource constraints is restricted, in this thesis, to functional units. Extensions are suggested in Chapter 7.

Although the relation between a DFG and a SMG is described more formally in Chapters 3 and 4, we need to anticipate some notions thereof. Our goal is to generate a SMG such that each operation of the DFG is associated with some state. Assume that operations  $o_m$  and  $o_n$  are associated with states  $s_i$  and  $s_i$ , respectively. Essentially, operations are assigned to states such that:

- If  $o_n$  is data dependent on  $o_m$ , then there must be a simple path from the source to  $s_j$  that includes state  $s_i$ , such that the execution of operation  $o_m$  starts only after the execution of operation  $o_m$  is completed. If this condition holds for all data dependent operations, we say that the precedence constraints are obeyed.

- The resources needed for the execution of the operations associated with a given state can not exceed the available number of resources. When this holds for every state, we say that the resource constraints are satisfied.

The subproblems stemming from HLS can usually be formulated as combinatorial optimization problems [50]. An *instance* of an optimization problem is a pair  $(\mathfrak{F}, c)$ , where the *solution space*  $\mathfrak{F}$  is the set of all feasible solutions, and the cost function c is a mapping  $c: \mathfrak{F} \mapsto \mathbb{R}$ . An *optimization problem* (OP) is a collection of problem instances. An OP can be formulated either as a minimization or as a maximization problem. The goal is to find a solution for which the cost function reaches either its minimal or its maximal value, depending on whether a minimization or a maximization problem is envisaged.

One way of tackling the synthesis of time—constrained designs is to formulate an OP whose goal is to minimize completion time and to search for a solution satisfying the time constraint. The completion time of a path in the SMG depends on how the operations are scheduled in the states included in that path. As a result, cost is evaluated in this thesis as a function of schedule lengths of paths. In the following formulation, c is a monotonically increasing function and  $L_p$  denotes the schedule length of a path p in the SMG such that source  $\stackrel{p}{\Rightarrow}$  sink.

#### **OPTIMIZATION PROBLEM**

Given a DFG, a set  $T_s$  of selected module types, a number of available modules  $n(t_s)$  for each module type  $t_s$  and an operation mapping  $\tau$ , find a SMG in which the precedence constraints of the DFG are obeyed and the resource constraints are satisfied for each module  $t_s \in T_s$ , such that the cost function  $c(L_1, L_2, \ldots, L_n)$  is minimized.

The solution of this OP implies the solution of resource–constrained scheduling, a well–known intractable problem. In this thesis, instead of relying on an exact algorithm to solve the OP, we assume that promising solutions are explored via  $local\ search\ [50]$ . Local search is based on the notion of neighborhood. Given an instance  $(\mathfrak{F}, \mathfrak{c})$ , a neighborhood is a mapping  $\mathcal{N}: \mathfrak{F} \mapsto P(\mathfrak{F})$ . This leads to the notion of  $local\ optimum$  with respect to a given neighborhood, in contrast to the notion of  $global\ optimum$ , which refers to the whole scope of the solution space. Essentially, the principle of a local search algorithm is to explore a given neighborhood of the current solution

(or of a group of solutions) and search for a better solution, until some stopping criterion is satisfied. Examples of local search algorithms are iterative improvement, tabu search, simulated annealing and genetic algorithms (for an overview, see [69]).

Some solutions, although feasible, are deliberately not generated, for reasons of efficiency. Reconsider the solutions in Figure 2.5, for instance. Since code motion in general leads to shorter schedule lengths, it would be unnecessary to generate a solution like the one in Figure 2.5a, where code motion is prohibited, as far as minimization of schedule lengths is the primary objective. Therefore, a given synthesis method can be conceived such that some feasible solutions of poor quality are never constructed. As a result, not all feasible solutions in the solution space can be explored. In order to mark the distinction, we call *search space* the set of feasible solutions that can actually be explored during the search.

It should be noted that, unlike most HLS approaches, where greedy heuristic algorithms are used to come up with a single solution, our choice of a local search approach is more flexible, since it provides a way of *exploring* alternative solutions. This is especially important because some solutions to the OP might not satisfy a given time constraint and have to be ruled out.

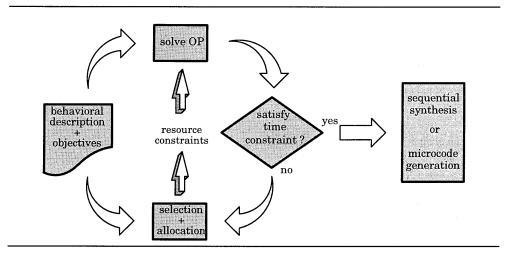

Figure 2.8 summarizes how the solution of the OP is placed in the context of a synthesis methodology. If the inequality  $\max(L_p) \leq T_c$  is not satisfied for some path p, previous decisions in the HLS design flow should be revoked and new decisions should be taken, through an iterative process, until the time constraint is met.

**FIGURE 2.8.** A design methodology for synthesis

# Chapter

# A constructive approach

## 3.1 Motivation

To tackle the optimization problem defined in the previous chapter, the following main difficulties have to be faced when conditionals and loops are present in the behavioral description:

- the NP-completeness of resource-constrained scheduling;

- the limited parallelism of operations enclosed by basic blocks, such that available resources are poorly utilized;

- the possibility of state explosion because the number of control paths may explode in the presence of conditionals;

- the limited resource sharing of mutually exclusive operations, due to the late availability of test results.

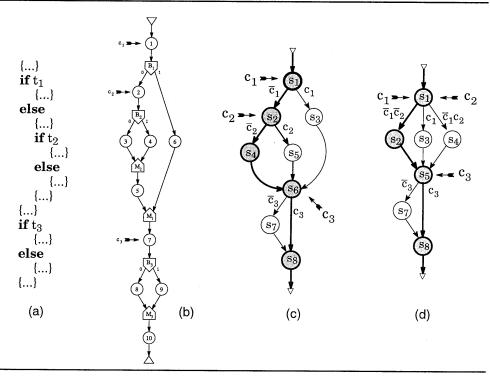

Most methods address these issues as separate subproblems (BB scheduling, code motion, code size reduction, conditional resource sharing). Since the optimization goals of different subproblems may conflict, the result typically depends on the order in which the subproblems are solved. Besides, most methods apply different heuristics to each subproblem, as if they were independent. An heuristic is used to determine the order of the operations during scheduling (like the many flavors of priority functions), another to decide whether a particular code motion is worth doing [22][48][54], yet another for reducing the number of states [71]. The application of an aggregate of unrelated heuristics makes it difficult to control the quality of the final result. Therefore, these approaches might miss optimal solutions.

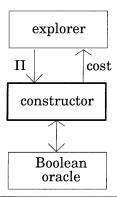

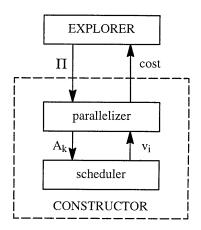

This chapter proposes a formulation [56] to encode potential solutions to the entire optimization problem, instead of addressing the interdependent subproblems separately. The formulation abstracts from the linear–time model commonly used in HLS and allows us to concentrate on the order of operations and on the availability of resources. Different priority encodings are used to induce alternative solutions and many solutions are generated and explored. The basic idea is to keep high–quality solutions in the search space when ILP techniques like code motion, speculative execution and loop pipelining are applied.

Before presenting our own approach to tackle the OP, later referred as the *constructive approach*, we review related approaches to similar problems.

# 3.2 Related high-level synthesis approaches

In path-based scheduling (PBS) [8][12] a so-called as-fast-as-possible (AFAP) schedule is found for each path independently, provided that a fixed order of operations be chosen in advance. Due to the fixed order and to the fact that scheduling is cast as a clique covering problem on an interval graph, code motions resulting in speculative execution are not allowed. The original method has been recently extended to relieve the fixed order [9], but reordering of operations is performed inside BBs only. Reordering is not allowed across branch junctions, because this would destruct the notion of interval, which is the very foundation of the PBS technique. Consequently, although reordering improves the capability of efficiently handling more complex data-flow, the method cannot support speculative execution, which limits the exploitation of parallelism with complex control flow [41]. This limitation is relieved in tree-based scheduling (TBS) [34], where speculative execution is allowed and the AFAP approach is conserved by keeping all paths on a tree. However, since the notion of interval is lost, an heuristic list scheduler is used to fill states with operations.

Condition vector list scheduling (CVLS) [71][72] allows code motion across branch and merge junctions, and supports some forms of speculative execution. Although it is shown in [53] that the underlying mutual exclusion representation is limited, the approach would possibly remain valid with some extension of the original condition vector or with some other alternative, such as the representations suggested in [6] and [53].

A hierarchical reduction approach (HRA) is presented in [37]. A DFG with conditionals is transformed into an "equivalent" DFG without conditionals, which is scheduled by a conventional scheduling algorithm. Code motion across merge points is allowed, but speculative execution is not supported.

In [54] an approach is presented where code—motions are exploited. At first, BBs are scheduled using a list scheduler and, subsequently, code motions are allowed. One priority function is used in the BB scheduler and another for code motion. Code motion is allowed only inside windows containing a few BBs to keep the runtime low, but then iterative improvement is needed to avoid restricting too much the kind of code motions allowed.

Among those methods, only PBS is exact, but it solves a partial problem where speculative execution is not allowed. TBS and CVLS address BB

scheduling and code motion simultaneously, but use classical list scheduler heuristics. In [54] a different heuristic is applied to each subproblem. All those methods may exclude optimal solutions from the search space.

In [52], an exact method is presented for solving a resource–constrained scheduling problem, which is entirely modeled in Boolean form. Code motion is largely supported. However, some traces are scheduled in such a way that they would lead to infeasible solutions, which requires a backtracking procedure for trace validation. As a consequence of being an exact method and due to the lack of efficient pruning, the reported runtime is large. Therefore, the use of this technique in the early (more iterative) phases of a design flow is unlikely.

# 3.3 Related approaches in the compiler arena

In Trace—scheduling (TS) [22] a main trace is chosen to be scheduled first and independently of the others, then another trace is chosen and scheduled, and so on. First, resource unconstrained schedules are produced and then heuristically mapped to the available resources. TS does not allow code motion between traces. The downside of TS is that its main—trace—first heuristic works well only in applications whose profiling shows a highly—predictable control flow (e.g. in numerical applications).