## Dry processing of GaAs-based MESFETs and pseudomorphic

Citation for published version (APA):

Hassel, van, J. G. (1995). *Dry processing of GaAs-based MESFETs and pseudomorphic HFETs*. [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR435811

DOI:

10.6100/IR435811

Document status and date:

Published: 01/01/1995

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 16. Nov. 2023

# Dry processing of GaAs-based MESFETs and pseudomorphic HFETs

J.G. van Hassel

# Dry processing of GaAs-based MESFETs and pseudomorphic HFETs

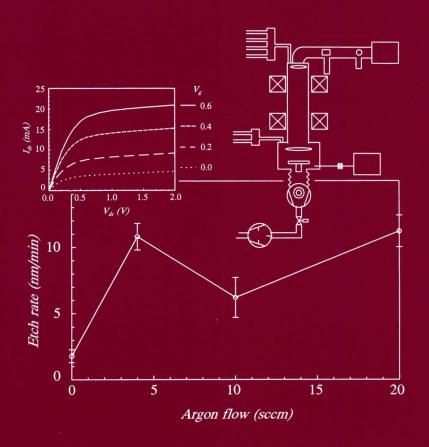

Cover:

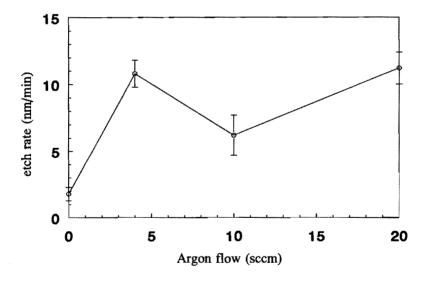

Top left:  $I_{ds}$ - $V_{ds}$  characteristics of a pseudomorphic AlGaAs/InGaAs/GaAs HFET. Top right: schematic layout of the electron cyclotron resonance plasma etch chamber. In the middle below the influence of increasing argon flow on the average etch rate of GaAs.

#### CIP-DATA KONINKLIJKE BIBLIOTHEEK, DEN HAAG

Hassel, Jan Gerard van

Dry processing of GaAs-based MESFETs and pseudomorphic HFETs / Jan Gerard van Hassel. - Eindhoven: Eindhoven University of Technology. - Fig., photos, tab.

Thesis Technische Universiteit Eindhoven. - With ref. - With summary in Dutch ISBN 90-386-0050-X NUGI 832

Subject headings: plasma etching / plasma deposition / semiconductors.

druk: wibro dissertatiedrukkerij, Helmond.

# Dry processing of GaAs-based MESFETs and pseudomorphic HFETs

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de

Technische Universiteit Eindhoven

op gezag van de Rector Magnificus, prof.dr. J.H. van Lint,

voor een commissie aangewezen door het College

van Dekanen in het openbaar te verdedigen

op dinsdag 2 mei 1995 om 16.00 uur

door

Jan Gerard van Hassel

geboren te Eindhoven

Dit proefschrift is goedgekeurd door de promotoren:

prof.Dr.-Ing. L.M.F. Kaufmann

prof.dr. M. van Rossum

en de copromotor:

dr. F. Karouta

aan Simon en Irene

## Table of contents

| Introduction                                  |                             | 1                                      |    |

|-----------------------------------------------|-----------------------------|----------------------------------------|----|

| Chapter I GaAs-based field-effect transistors |                             | 5                                      |    |

| 1.1                                           | Introd                      | uction                                 | 5  |

| 1.2                                           | Transistors                 |                                        | 6  |

|                                               | 1.2.1                       | MESFETs                                | 6  |

|                                               | 1.2.2                       | AlGaAs/GaAs HFETs                      | 9  |

|                                               | 1.2.3                       | Pseudomorphic AlGaAs/InGaAs/GaAs HFETs | 14 |

| 1.3                                           | Mask                        | layout                                 | 16 |

| 1.4                                           | The fabrication process     |                                        | 18 |

|                                               |                             | Introduction                           | 18 |

|                                               |                             | Mesa etch                              | 18 |

|                                               |                             | Ohmic contact formation                | 19 |

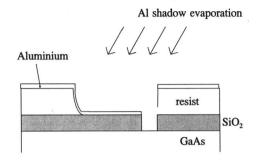

|                                               |                             | The gate metallisation                 | 23 |

|                                               | 1.4.5                       | Cascade overlay metallisation          | 25 |

| 1.5                                           | Electrical characterisation |                                        | 26 |

|                                               | 1.5.1                       | DC characterisation                    | 26 |

|                                               | 1.5.2                       | <i>5</i> 1 •                           | 28 |

|                                               |                             | 1.5.2.1 S-parameters                   | 28 |

|                                               |                             | 1.5.2.2 Noise figure (NF)              | 33 |

| 1.6                                           | Results                     |                                        | 34 |

|                                               | 1.6.1                       | MESFETs                                | 34 |

|                                               | 1.6.2                       | AlGaAs/GaAs HFETs                      | 35 |

|                                               | 1.6.3                       | AlGaAs/InGaAs/GaAs HFETs               | 36 |

|                                               | 1.6.4                       | The noise figure (NF)                  | 37 |

| 1.7                                           | Discu                       | assion                                 | 37 |

| 1.8                                           | Refer                       | rences                                 | 39 |

#### Table of contents

| Chapt | er II The influence of argon cleaning on GaAs-based<br>Schottky diodes and MESFETs                  | 43                   |

|-------|-----------------------------------------------------------------------------------------------------|----------------------|

| 2.1   | Introduction                                                                                        | 43                   |

| 2.2   | The characteristics of the ion-gun                                                                  | 44                   |

| 2.3   | Theory of Schottky diodes                                                                           | 47                   |

| 2.4   | Fabrication technology                                                                              | 50                   |

| 2.5   | The effect of Ar cleaning on diodes                                                                 | 51                   |

| 2.6   | The influence of in-situ argon cleaning on MESFETs                                                  | 57                   |

| 2.7   | The influence of Ar⁺ ion cleaning on Schottky diodes and MESFETs                                    | 60                   |

| 2.8   | Conclusions                                                                                         | 64                   |

| 2.9   | References                                                                                          | 65                   |

| Chapt | ter III Metal organic electron cyclotron resonance reactive ion etching                             | 67                   |

| 3.1   | Introduction                                                                                        | 67                   |

| 3.2   | MOECR plasma etching 3.2.1 The reactor 3.2.2 The ECR discharge 3.2.3 Sample and reactor preparation | 68<br>68<br>70<br>72 |

| 3.3   | Results                                                                                             | 73                   |

| 3.4   | InP MOECR plasma etching                                                                            | 80                   |

| 3.5   | Conclusions                                                                                         | 85                   |

| 3.6   | References                                                                                          | 86                   |

| Chapter IV |                                                                      | The influence of CH <sub>d</sub> /H <sub>2</sub> /Ar ECR plasma etching on GaAs |     |

|------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------|-----|

| 4.1        | Introd                                                               | luction                                                                         | 89  |

| 4.2        | Passivation and neutralisation                                       |                                                                                 | 90  |

|            | 4.2.1                                                                | Introduction                                                                    | 90  |

|            | 4.2.2                                                                | Determination of the passivation depth by C-V measurements                      | 92  |

|            | 4.2.3                                                                | The passivation depth                                                           | 93  |

|            | 4.2.4                                                                | Recovery of the passivation                                                     | 95  |

| 4.3        | Schottky diodes                                                      |                                                                                 | 97  |

|            | 4.3.1                                                                | Introduction                                                                    | 97  |

|            | 4.3.2                                                                | The influence of MOECR plasma etching on Schottky diodes                        | 97  |

| 4.4        | The influence of MOECR plasma etching on GaAs-based heterostructures |                                                                                 | 101 |

|            | 4.4.1                                                                | Introduction                                                                    | 101 |

|            | 4.4.2                                                                | The Hall effect                                                                 | 102 |

|            |                                                                      | 2-DEG Hall mobility                                                             | 104 |

|            | 4.4.4                                                                | Experimental results                                                            | 106 |

|            |                                                                      | 4.4.4.1 Influence on AlGaAs/GaAs heterostructures                               | 106 |

|            |                                                                      | 4.4.4.2 Influence on AlGaAs/InGaAs/GaAs heterostructures                        | 110 |

| 4.5        | Discussion and conclusions                                           |                                                                                 | 111 |

| 4.6        | Refer                                                                | ences                                                                           | 112 |

#### Table of contents

| Chapter V |                            | Microwave downstream plasma enhanced chemical vapour deposition of silicon oxide and silicon nitride |     |

|-----------|----------------------------|------------------------------------------------------------------------------------------------------|-----|

| 5.1       | Introdu                    | action                                                                                               | 117 |

| 5.2       | Silicon                    | oxide and silicon nitride deposition                                                                 | 118 |

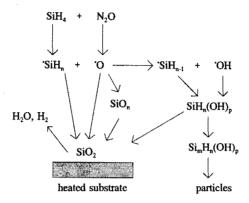

|           | 5.2.1                      | Deposition mechanism                                                                                 | 118 |

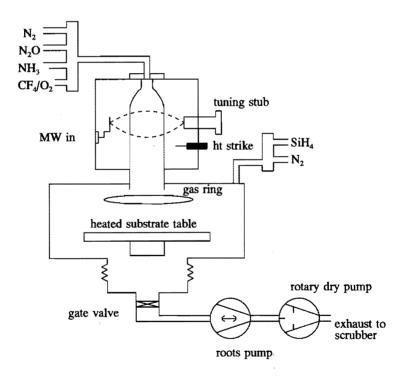

|           | 5.2.2                      | The reactor                                                                                          | 120 |

| 5.3       | Experimental               |                                                                                                      | 121 |

|           | 5.3.1                      | Introduction                                                                                         | 121 |

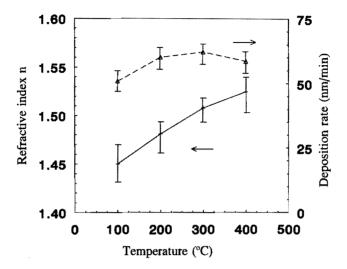

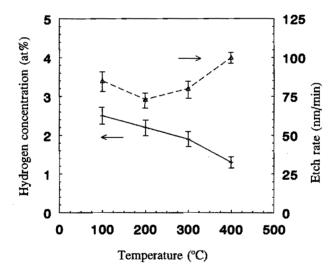

|           | 5.3.2                      | Refractive index, etch rate and deposition rate                                                      | 121 |

|           | 5.3.3                      |                                                                                                      | 122 |

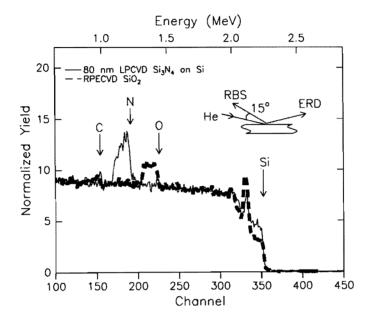

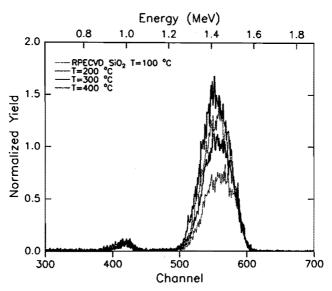

|           |                            | 5.3.3.1 Rutherford backscattering spectrometry (RBS)                                                 | 122 |

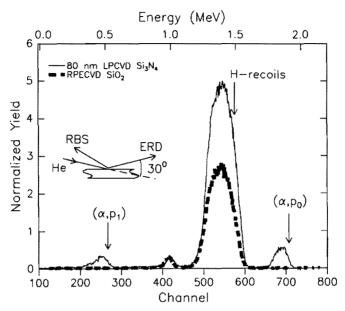

|           |                            | 5.3.3.2 Elastic recoil detection (ERD)                                                               | 124 |

| 5.4       | Silicon oxide deposition   |                                                                                                      | 126 |

|           | 5.4.1                      | Introduction                                                                                         | 126 |

|           | 5.4.2                      | The influence of the deposition temperature                                                          | 126 |

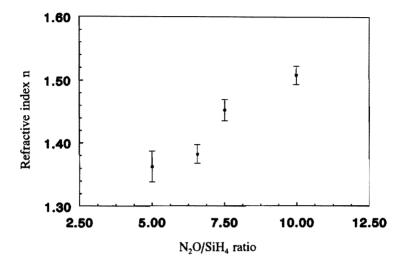

|           | 5.4.3                      | The influence of the silane and the nitrous oxide flow                                               | 128 |

|           | 5.4.4                      | The influence of the pressure, the table height and the nitrogen flow                                | 129 |

|           | 5.4.5                      | Summary                                                                                              | 130 |

| 5.5       | Silicon nitride deposition |                                                                                                      | 131 |

|           | 5.5.1                      | Introduction                                                                                         | 131 |

|           | 5.5.2                      | The influence of the deposition temperature                                                          | 132 |

|           | 5.5.3                      | The influence of the silane flow                                                                     | 133 |

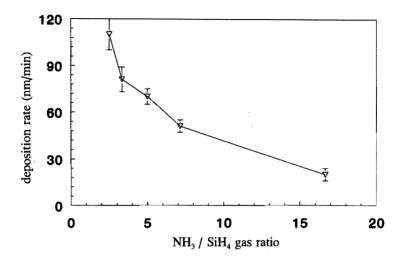

|           | 5.5.4                      | The influence of the NH <sub>3</sub> flow and the microwave power                                    | 135 |

|           | 5.5.5                      | 1                                                                                                    | 136 |

|           | 5.5.6                      | The influence of the nitrogen flow                                                                   | 136 |

|           | 5.5.7                      | Summary                                                                                              | 136 |

| 5.6       | Micro                      | wave downstream PECVD                                                                                | 137 |

| 5.7       | Refere                     | ences                                                                                                | 138 |

| Chapter VI       |                                   | Dry processed GaAs-based MESFETs and pseudomorphic HFETs                                                                                                                                                                            | 143                      |

|------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 6.1              | Introd                            | uction                                                                                                                                                                                                                              | 143                      |

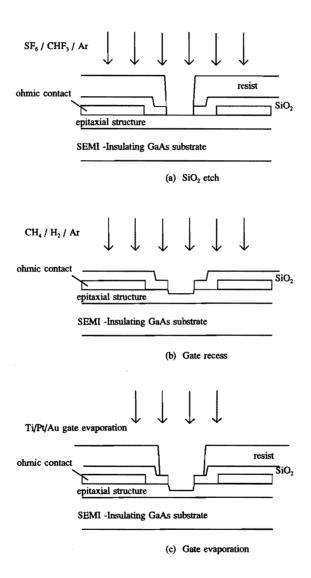

| 6.2              | Fabric<br>6.2.1<br>6.2.2<br>6.2.3 | Fabrication of transistors Fabrication process The influence of SiO <sub>2</sub> deposition on an AlGaAs/GaAs heterostructure The influence of a SF <sub>6</sub> /CHF <sub>3</sub> /Ar ECR plasma on an AlGaAs/GaAs heterostructure | 143<br>143<br>145<br>146 |

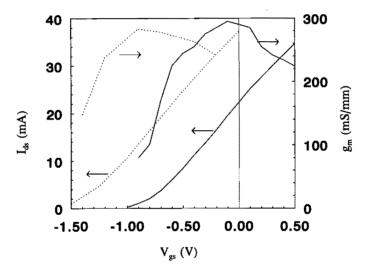

| 6.3              | Device 6.3.1 6.3.2 6.3.3          | e performance<br>MESFETs<br>Pseudomorphic HFETs<br>Pseudomorphic HFETs with an additional δ-doped layer                                                                                                                             | 147<br>147<br>147<br>149 |

| 6.4              | Concl                             | usions                                                                                                                                                                                                                              | 150                      |

| 6.5              | Refere                            | ences                                                                                                                                                                                                                               | 151                      |

| Chaj             | oter VII                          | Conclusions and Recommendations                                                                                                                                                                                                     | 153                      |

| 7.1              | Concl                             | usions                                                                                                                                                                                                                              | 153                      |

| 7.2              | Recor                             | nmendations                                                                                                                                                                                                                         | 156                      |

| 7.3              | Refer                             | ences                                                                                                                                                                                                                               | 159                      |

| App              | endix A                           |                                                                                                                                                                                                                                     | 160                      |

| Appendix B       |                                   |                                                                                                                                                                                                                                     | 163                      |

| Summary          |                                   |                                                                                                                                                                                                                                     | 164                      |

| Samenvatting     |                                   |                                                                                                                                                                                                                                     | 166                      |

| List of Symbols  |                                   |                                                                                                                                                                                                                                     | 168                      |

| CURRICULUM VITAE |                                   |                                                                                                                                                                                                                                     | 171                      |

## Introduction

Since 1985 an essential part of the research activities of the Eindhoven University of Technology (EUT) division of Electronic Devices (EEA) is concentrated on III-V compound semiconductors. The research is focused on the modelling, technology and characterisation of electronic components necessary for opto-electronic integrated circuits. The present study is limited to the technology of GaAs-based field-effect transistors. This work is performed in close collaboration with the EUT division of Solid State Physics (NV) where epitaxial structures are grown and characterised. Because no experience was available in the fabrication of field-effect transistors the research was started in close collaboration with the University of Duisburg. At the end of 1992 the research program started with the availability of the clean room and updated technological equipment.

This work is focused on GaAs-based MEtal Semiconductor Field-Effect Transistors (MESFETs) and (pseudomorphic) Heterostructure Field-Effect Transistors (PM)HFETs. The epitaxial structures necessary for transistor fabrication are grown by molecular beam epitaxy at the EUT division of Solid State Physics. Also one structure from the Walter Schottky Institute of the Technical University of Munich was used. Molecular beam epitaxy is known as to produce atomically smooth layers of high quality giving excellent interface properties and low impurity content. This is important since device characteristics are degraded by material defects. Besides, the present structures used for heterostructure field-effect transistors consist of very thin layers, typically 5 to 10 monolayers which emphasizes the requirements demanded from the growth facilities.

In MESFETs the current flows through a n-doped active layer. In a HFET the electrons are spatially separated from their donors and confined in a two-Dimensional Electron Gas (2-DEG) through which the transport takes place. Consequently improved properties are obtained in HFETs. In both structures the current or channel conductivity is controlled by a Schottky contact which is generally placed below the semiconductor surface. This fabrication step is known as the gate recess. The depth of the gate recess is important since it determines the operation characteristics of the device. By the gate recess the threshold voltage of the transistor can be adjusted and enhancement or depletion mode FETs can be defined. This gate recess can be done wet chemically or by dry plasma etching. Since plasma etching offers a great reproducibility and uniformity the interest for dry processes is rapidly increasing. A disadvantage of these processes is the introduction of damage to the epitaxial structures due to an ion bombardment. In this thesis the influence of dry processing on the characteristics of Schottky diodes and field-effect transistors is investigated. Our purpose was to obtain more information on the amount of damage introduced by the plasma. This is done as function of the process parameters in order to achieve optimised process parameters to reduce the damage. The results are continuously compared to wet chemically recessed diodes and transistors to determine the possibilities and disadvantages of using dry processes during the fabrication of these components.

Chapter 1 describes the processes developed for wet processing of GaAs-based MESFETs as well as AlGaAs/GaAs and AlGaAs/InGaAs/GaAs (pseudomorphic) HFETs. Due to the limitations of optical lithography the gate length of the transistors was restricted to 0.8 µm. Ge/Ni/Au ohmic contacts are optimised with respect to annealing time and temperature. Annealing was performed in a Rapid Thermal Annealer (AST SHS 100) in a nitrogen-hydrogen ambient. The different types of transistors are characterised by direct current and high frequency measurements. The microwave measurements are performed at frequencies ranging from 45 MHz to 40 GHz. Few measurements have been done on the noise characteristics. The results are used for comparison to dry processed transistors. Less attention was paid to the uniformity.

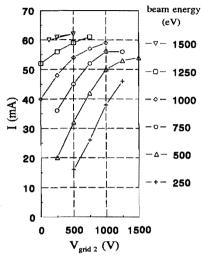

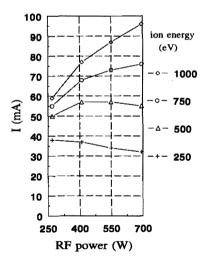

The new technological equipment in the clean room was arranged to reduce the damage. One facility is the single-wafer load-locked Leybold (L 560 UV) evaporator. The evaporator has two electron beam evaporators, to evaporate the different metallisations necessary for ohmic and Schottky contacts, and an ion gun (IQ 70). The ion gun is dedicated to clean the semiconductor surface: to reduce the amount of residual oxide and defects on the semiconductor surface. After optimising the characteristics of the ion gun and determining the GaAs etch rates the influence of argon cleaning on Schottky diodes and MESFETs is investigated. These experiments are performed for a neutralised and a non-neutralised argon ion beam. The energy of the argon beam was varied between 50 and 750 eV and in-situ the Schottky metallisations were evaporated. The results are described in chapter 2.

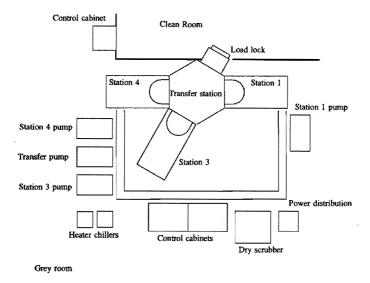

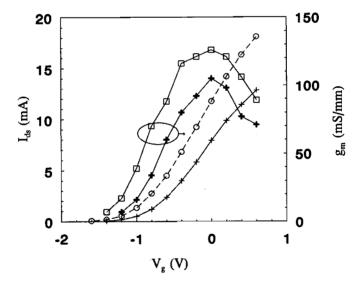

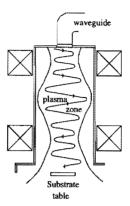

The second facility, dedicated to plasma processing, is the Oxford Plasma Technology cluster tool which was available mid 1993. The layout is shown schematically in figure 1. The cluster tool, installed in the grey room, consists of three different process chambers (stations) connected to a general transfer chamber which is loaded by an additional load lock. The load lock is located inside the clean room. Single-wafer transport is accomplished through a robot arm located in the transfer chamber. The total system is controlled by a microprocessor. Station 1 is an Electron Cyclotron Resonance Reactive Ion Etching (ECR-RIE) system dedicated for etching dielectrics. The process uses a mixture of sulphur hexafluoride (SF<sub>6</sub>), fluoroform (CHF<sub>3</sub>) and argon. Station 3 is used for Remote Plasma Enhanced Chemical Vapour Deposition (RPECVD) of silicon oxide and silicon nitride. For silicon oxide deposition a gas mixture of nitrous oxide (N<sub>2</sub>O) and silane (SiH<sub>4</sub>) diluted by nitrogen (N<sub>2</sub>) is used. For silicon nitride deposition the nitrous oxide is replaced by ammonia (NH<sub>3</sub>). A carbontetrafluoride/oxygen (CF<sub>d</sub>/O<sub>2</sub>) mixture is used for cleaning the process chamber and to minimise the cross contamination between these two processes. Station 4 is an ECR-RIE etch chamber for III-V materials. Here methane (CH<sub>4</sub>), hydrogen (H<sub>2</sub>) and argon (Ar) are used as process gases. It is possible to upgrade the cluster tool with a fourth process chamber (station 2). In all chambers the plasma is created and sustained remote and independent from the substrate to prevent an excessive ion bombardment. For this reason less damage is expected compared to the more conventional Reactive Ion Etching (RIE) or PECVD processes. In RIE additional RF power on the substrate table is used for maintaining the plasma and providing an adequate bias for processing.

Figure 1, Schematic layout of the OPT cluster tool.

In ECR based plasmas the additional RF power (DC bias) is generally low since the first condition is already satisfied. The different processes are clustered together in one system to minimise the exposure to air to allow subsequent processing in different chambers within one run.

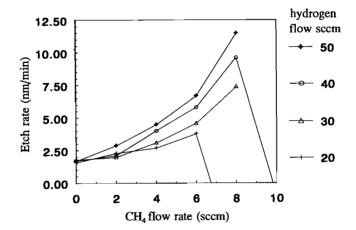

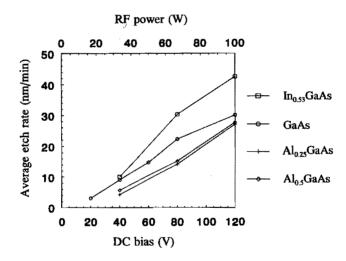

Station 4 is dedicated to perform the gate recess. The chemical nature of this process is based on the formation of group III metalorganic compounds and group V halides. Chapter 3 describes the etch characteristics of the CH<sub>4</sub>/H<sub>2</sub>/Ar ECR plasma on different III-V semiconductors as a function of different process parameters. The attention was mainly focused on GaAs.

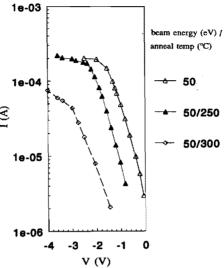

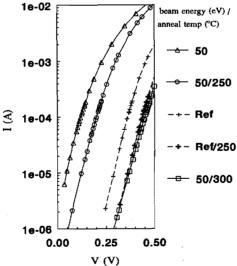

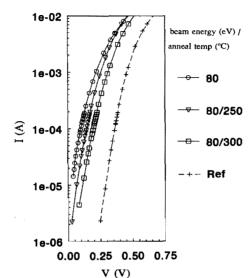

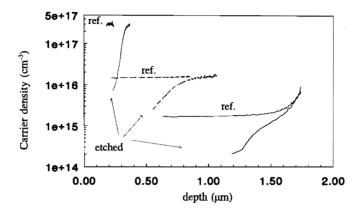

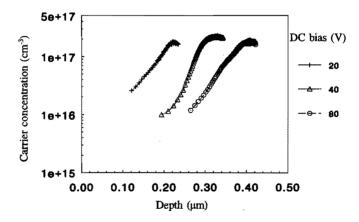

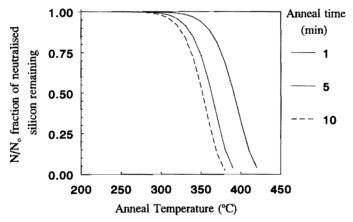

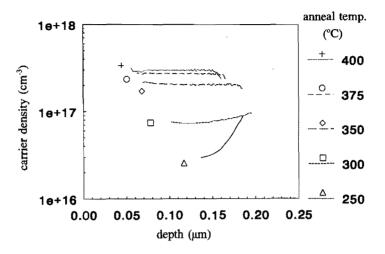

Beside the chemical nature of the process a physical component is present due to additional DC bias. In addition to the structural damage created by the CH<sub>4</sub>/H<sub>2</sub>/Ar ECR plasma also passivation occurs due to the presence of hydrogen. Passivation originates from the formation of Si-H complexes which result in a loss of electrical activity of the donor atoms in the semiconductor layers. The passivation can be restored by a heat treatment which was done in the rapid thermal annealer in a nitrogen ambient. The influence and amount of damage is described in chapter 4. Capacitance-Voltage (C-V) measurements were used to study the passivation depth as function of silicon donor concentration and as function of the additional process bias. This is investigated on MBE grown silicon doped n-GaAs bulk layers. By

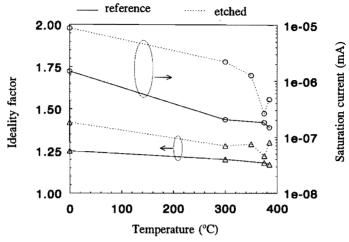

current-voltage (I-V) measurements on Schottky diodes the damage is investigated as a function of the substrate bias. The characteristics are compared to wet chemically etched diodes.

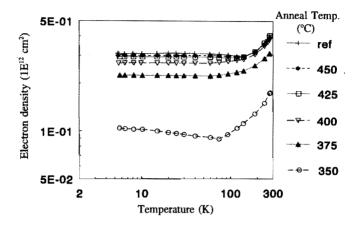

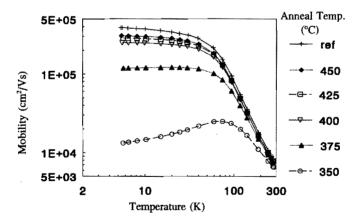

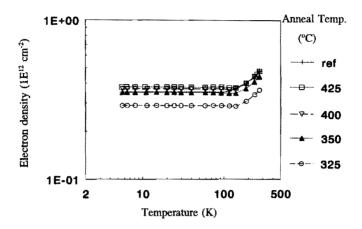

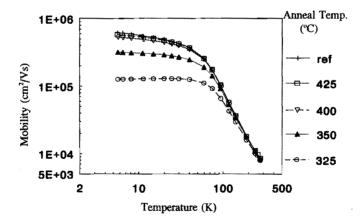

For AlGaAs/GaAs and AlGaAs/InGaAs/GaAs heterostructures the influence of the plasma on the sheet density and the Hall mobility of the 2-DEG is investigated as function of the measurement temperature. Upon annealing full recovery of the sheet density was obtained for the AlGaAs/GaAs heterostructure, whereas the Hall mobility only partially recovered. Introduction of an additional silicon  $\delta$ -doped layer in the structure behaved as a shield and prevented the 2-DEG for further damage introduction. The effect of an additional  $\delta$ -doped layer was even more pronounced in the pseudomorphic heterostructure. The results are compared to identical experiments with CH<sub>4</sub>/H<sub>2</sub> reactive ion etching on the same structures.

Because thin resist layers, necessary for 1  $\mu$ m patterns, were not resistant to the CH<sub>4</sub>/H<sub>2</sub>/Ar ECR plasma process, silicon nitride or silicon oxide layers had to be used in the fabrication of transistors. Since little was known about the quality of these layers this is investigated as function of the process parameters. Chapter 5 describes the deposition of silicon oxide and silicon nitride films as function of the process conditions. The composition of the films was measured by Rutherford Backscattering Spectrometry (RBS) using 4 MeV Helium ions. Simultaneously the hydrogen incorporation was measured by Elastic Recoil Detection Analysis (ERDA or ERD). Furthermore the refractive index, deposition rate and etch rate have been determined and compared to the results obtained with the compositional analysis.

Chapter 6 describes the results obtained on dry recessed MESFETs and pseudomorphic HFETs. These results will be compared to wet chemically processed transistors which are described in chapter 1. Additional process steps, necessary for the fabrication of these dry processed transistors, will be discussed.

In chapter 7 the work is summarised and recommendations for further investigations are made.

With the contribution and collaboration of many people this work is realised. For that reason I would like to thank prof. Dr.-Ing. L.M.F. Kaufmann for giving me the opportunity to realise this work and for stimulating of contacts with other researchers. I also acknowledge dr. F. Karouta and dr. ir. Th.G. van de Roer for fruitful discussions during the work and preparation of this thesis and my second promoter prof. dr. M. van Rossum and prof. dr. P. van Daele for critical reviewing this work. In particular I would like to thank some people from the physics department of the EUT: P.A.M. Nouwens for performing the Hall measurements, ir. C.M. van Es for discussions, W.C. van der Vleuten for having grown the epitaxial layer structures (division of Solid State Physics) and dr. L.J. van IJzendoorn (division of Particle Physics) for measuring and interpretation of the RBS and ERD measurements. I wish to acknowledge ing. J.J.M. Kwaspen and ir. H.C. Heyker for measuring the high frequency characteristics. I appreciate the collaboration and technical assistance of drs. E. Smalbrugge, B.H. van Roy, ing. J.J.A. Stegeman, H.P.J.C. Rooijakkers, dr. A. Kalfane, dr. Y. Zhu, J.H. Maahury and the other members of the group. Finally I will not forget my family for their support and especially Réjane and Vicky for their patience during the work and preparation of this thesis.

### CHAPTER I

GaAs-based field-effect transistors.

#### 1.1 Introduction.

GaAs-based field-effect transistors are widely used in integrated circuits such as oscillators, amplifiers and mixers. MEtal Semiconductor Field-Effect Transistors (MESFETs) and Heterostructure Field-Effect Transistors (HFETs) are commonly the devices on which this integration is based. The heterostructure configuration is known under different names. Beside HFET also MOdulation Doped Field-Effect Transistor (MODFET), Two-dimensional Electron Gas Field-Effect Transistor (TEGFET or 2DEGFET), High Electron Mobility Transistor (HEMT) and Selectively Doped Heterostructure Transistor (SDHT) are frequently used. Here the term HFET will be used. The advantages of these HFETs over MESFETs are its lower power dissipation, lower noise and the fast response times. The fast response times can be ascribed to the high electron mobility and saturation velocity in these semiconductor materials.

In a MESFET the current flows through a normally n-doped layer. This current is controlled by a Schottky diode. Because of the presence of both the donor atoms and the electrons in the same layer the mobility as well as the response time are reduced in these structures. According to Hilsum [1] the mobility  $\mu$  decreases with increasing donor concentration  $N_d$ . This reduction is due to an increase of the Coulomb scattering. See equation 1.1.

$$\mu = \frac{10^4 cm^2 / Vs}{1 + \sqrt{\frac{N_d}{10^{17} cm^{-3}}}}$$

(1.1)

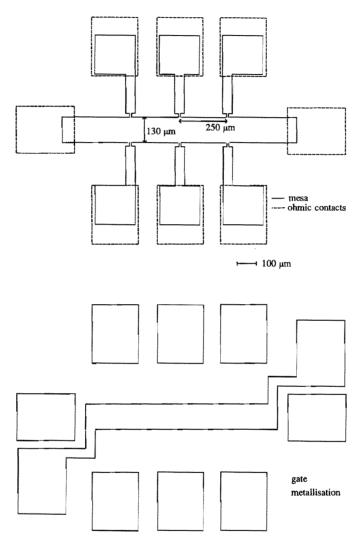

In a heterostructure field-effect transistor the electrons are spatially separated from their donor atoms. The electrons are transferred from the higher bandgap doped material to the lower bandgap undoped material. The electrons in the lower bandgap material are confined in the vicinity of the interface in a Two-Dimensional Electron Gas (2-DEG). The Coulomb scattering is minimised by this separation which leads to an increased mobility especially at low temperatures. This can be enhanced if the lower bandgap material has improved electron velocity saturation properties. In this way superior device performances are obtained.

In the present work a technology for the fabrication of different types of compound semiconductor transistors had to be developed first. This was the base from which further investigations proceeded.

This chapter describes the wet chemical processes developed for GaAs-based transistors. With this technology GaAs MESFETs, AlGaAs/GaAs and AlGaAs/InGaAs/GaAs HFETs have been made and characterised. The principles of operation of MESFETs and HFETs are discussed in paragraph 1.2. The mask layout, the fabrication and optimisation of the process are described in paragraph 1.3 and 1.4 respectively. Paragraph 1.5 describes the electrical measurements used to characterise the transistors. The transistors are characterised by direct current and high frequency measurements at room temperature. Paragraph 1.6 lists the results obtained on wet chemically processed MESFETs, AlGaAs/GaAs and AlGaAs/InGaAs/GaAs HFETs. Here the structures and the data obtained with DC and microwave measurements are shown. Finally the results are compared to literature.

#### 1.2 Transistors.

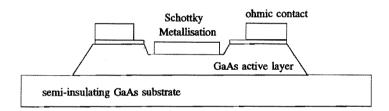

#### 1.2.1 MESFETs

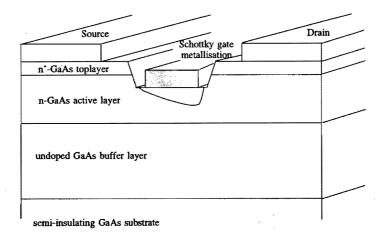

A typical schematic cross section of a MESFET is shown in Figure 1.1. The epitaxial structure consists of 2  $\mu m$  undoped GaAs buffer layer, a 200 nm thick n-GaAs active layer (3·10<sup>17</sup> cm<sup>-3</sup>) and a 20 nm highly silicon doped (2·10<sup>18</sup> cm<sup>-3</sup>) n<sup>+</sup>-GaAs top or contactlayer. The electron transport is carried within the active layer. The structure is grown on a semi-insulating GaAs substrate.

Figure 1.1, Schematic cross section of the layer structure of a MESFET.

The structures are grown with Molecular Beam Epitaxy (MBE). The semi-insulating substrates were produced using the Liquid Encapsulated Czochralski (LEC) technique.

With the Schottky gate metallisation between the ohmic contacts (see Figure 1.1) the channel conductivity can be modulated by applying a negative bias to this gate with respect to the source. If a voltage is applied between the drain and the source a current according to equation 1.2 will flow in the active GaAs layer.

$$I_{ds} = q \cdot W \cdot N_d [A - A_d(x)] \cdot v(x)$$

(1.2)

Here  $I_{ds}$  is the current between the drain and the source, q the electron charge, W is the width of the transistor, x the coordinate along the channel, A the thickness of the active layer under the gate,  $A_d(x)$  the depletion depth and v(x) the electron velocity. For small voltages the electron velocity is linear to the longitudinal electric field E(x).

$$v(x) = \mu \cdot E(x) = \mu \cdot \frac{dV(x)}{dx} \tag{1.3}$$

with V(x) the potential along the channel. According to the abrupt junction depletion approximation and the one dimensional Poisson equation the depth of the depletion region under the gate  $A_d(x)$  can be written as:

$$A_{d}(x) = \left[ \frac{2\epsilon \cdot (V(x) + V_{bi} - V_{g})}{q \cdot N_{d}} \right]^{\frac{1}{2}}$$

(1.4)

Here  $\epsilon$  is the dielectric permittivity of GaAs,  $V_{bi}$  the built in voltage of the Schottky barrier and  $V_g$  the gate voltage.

In figure 1.1 it is shown that the depletion region extends further into the active GaAs layer at the drain side of the gate. This occurs due to the higher reverse bias across the drain-gate diode as compared to the source-gate diode.

Substituting equation 3 and 4 in equation 2 and integrating over x along the channel from the source side to the drain side of the gate gives the fundamental equation of field-effect transistors [2].

However if the electrical field under the gate is greater than the critical electric field  $E_c$  the electron velocity saturates [3]. This can be modelled by dividing the region under the gate in two regions [4,5]. A region where the electron velocity is linear with the electric field and a region with constant electron velocity.

$$v = \mu \cdot E(x)$$

for  $E < E_c$

$v_s$  for  $E > E_c$  (1.5)

In this case the saturation current (I<sub>ds</sub>)<sub>sat</sub> of a transistor can be expressed as:

$$(I_{dv})_{sat} = \beta (V_{r} - V_{T})^{2}$$

(1.6)

where the threshold voltage  $V_T$  is the gate-source voltage needed to deplete the channel at the drain side of the gate. The factor  $\beta$  can be written as [2]:

$$\beta = \frac{2 \epsilon \mu v_s W}{A (\mu V_{po} + 3 v_s L)} \tag{1.7}$$

with  $V_{po} = V_{bi} - V_T$  the pinch off voltage and L the gate length. It can be seen that the DC saturation characteristics, according to equation 1.6 and 1.7, have a more or less linear dependence on the electron mobility. The voltage drops across the drain and the source resistances are however not included in this model. The influence of these resistances on the performance of the transistors will be treated later in this chapter.

As stated in the introduction the mobility decreases with increasing donor concentration. This holds certainly for MESFETs. In HFETs this effect is reduced because the donors are spatially separated from the 2-DEG that forms the transistor channel.

#### 1.2.2 AlGaAs/GaAs HFETs

Figure 1.2 shows schematically a cross section of an AlGaAs/GaAs HFET structure and its band structure at the semiconductor interface. On the semi-insulating GaAs substrate an undoped GaAs buffer layer is grown. Subsequently a few nanometer thick undoped AlGaAs spacer and a n\*-AlGaAs donor layer are grown. On the top there is a n\*-GaAs caplayer. The thickness of the spacer layer is typically between 2 and 5 nanometer in HFET structures. This shows the importance of epitaxial techniques with atomic resolution.

The highly doped GaAs toplayer prevents the AlGaAs layer from surface oxidation and so from surface depletion due to this oxidation. This layer also facilitates the formation of ohmic contacts.

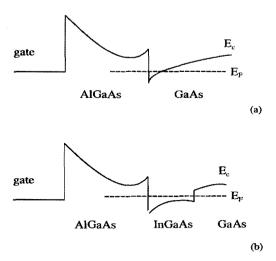

Figure 1.2, The cross section of the structure used in an AlGaAs/GaAs HFET. On the right side the AlGaAs-GaAs conduction band discontinuity is shown.

Between the n\*-AlGaAs donor layer and the GaAs buffer layer discontinuities in the valence and conduction bands occur due to the difference in bandgap of these materials. This is shown in the right hand side of figure 1.2 and in figure 1.3. The band discontinuity  $\Delta$ Eg between GaAs and Al<sub>y</sub>Ga<sub>1-y</sub>As for an aluminium concentration less than 45 percent can be written as [6]:

$$\Delta Eg = 1.247 \cdot Y$$

for Y < 0.45 (1.8)

This bandgap difference leads to discontinuities in the conduction band  $\Delta E_c$  and the valence band  $\Delta E_v$ , which nowadays are generally accepted to be about [7]:

$$\Delta E_c = 0.67 \cdot \Delta Eg$$

and for Y < 0.45 (1.9)

$$\Delta E_v = 0.33 \cdot \Delta Eg$$

Although in the past different figures have been used [8]. Due to these discontinuities the electrons of the AlGaAs layer are transferred into an approximately triangular potential well on the GaAs side of the interface. There the electrons are accumulated in a two-dimensional electron gas. The electron energies are quantised in this well. The concentration in the 2-DEG can be calculated by self-consistently solving the Schrödinger (1.10) and Poisson equations (1.11) [9,10]

$$\frac{(h/2\pi)^2}{2m} \cdot \frac{d^2\phi(z)}{dz^2} + [E_i - V(z)]\phi_i(z) = 0$$

(1.10)

$$\frac{d^2V}{dz^2} = \frac{q\rho(z)}{\epsilon} \tag{1.11}$$

where z is the coordinate perpendicular to the epitaxial layers, h is the Plancks constant,  $\phi_i(z)$  the electron wave function,  $\rho(z)$  the space charge density, m the electron mass and  $E_i$  the i<sup>th</sup> subband energy level. The electron potential energy in GaAs perpendicular to the interface can be found with help from the Poisson equation and:

$$-\rho(z) = q \cdot \sum_{i} n_{i} |\phi_{i}|^{2}(z) \tag{1.12}$$

Here the charge density due to donor and acceptor impurities in GaAs are neglected. Using the Fermi-Dirac distribution function, the electron concentration in the i<sup>th</sup> subband can be expressed as:

$$n_{j} = D \frac{kT}{q} \cdot \ln[1 + \exp \frac{E_{F} \cdot E_{i}}{k_{b}T}]$$

(1.13)

with D= $4\pi qm/h^2$  the density of states for a two dimensional electron gas. An analytical approximation of the energy of the i<sup>th</sup> subband can be represented as [11]:

$$E_i = \left[\frac{(\hbar/2\pi)^2}{2m}\right]^{\frac{1}{3}} \left[\frac{3}{2}qE_s\pi(i+\frac{3}{4})\right]^{\frac{2}{3}}$$

(1.14)

The surface electric field  $E_s$  can be related to the 2-DEG charge density by solving the Poisson equation over the depletion region which gives  $\in E_s = q \, n_s$ . Combining with equation 1.14 the energy of the subbands can be related to the 2-DEG sheet density  $n_s$ :

$$E_{1} = \zeta_{1} n_{s}^{\frac{2}{3}}$$

$$E_{0} = \zeta_{0} n_{s}^{\frac{2}{3}}$$

(1.15)

Here  $\zeta_i$  are parameters which can be adjusted to fit experimental results. When using the Fermi-Dirac statistics the 2-DEG sheet charge concentration can be given as function of the Fermi level position [11,12]:

$$n_s = D(\frac{kT}{q}) \cdot \ln[(1 + e^{\frac{q(E_{p'} - E_{p})}{k_b T}})(1 + e^{\frac{q(E_{p'} - E_{p})}{k_b T}})]$$

(1.16)

It is assumed that only the first two subbands are occupied. Electron transport in a HFET is in the lateral direction through the 2-DEG. The separation of the ionised donors in the donor layer and the electrons of the 2-DEG reduces the Coulomb scattering. In this way the mobility is increased compared to the mobility of a MESFET. This improved mobility was observed for the first time by Dingle et al. [13]. In spite of this separation the electrostatic Coulomb

interaction is still present. For this reason an undoped AlGaAs spacer is introduced in the layer structure to increase the spatial separation. Intense research has been performed on the influence of the spacer thickness on the electron mobility and the 2-DEG sheet density. The influence of the spacer is investigated mainly at low temperatures since the effects are more pronounced in that regime. In general the mobility increases and the 2-DEG sheet concentration decreases with increasing spacer thickness [14,15]. The mobility also increases with increasing electron density in the 2-DEG until the electrons start to fill the first subband. Then the mobility is reduced by inter subband scattering. In a HFET it is preferred to have a high sheet concentration and a high electron mobility. The thickness of the AlGaAs spacer is typically between 2 and 5 nanometer to satisfy both conditions.

The band discontinuity and the donor density in the AlGaAs layer also have an influence on the 2-DEG sheet concentration. The aluminium content in the donor layer needs to be high to improve the band discontinuity at the interface and to improve the Schottky barrier height (equation 1.8). Also a high (Si) donor density in the AlGaAs layer is preferred for creating a high 2-DEG sheet concentration and to reduce the distance between the gate and the 2-DEG. However having as well a high aluminium concentration and a high donor concentration leads to the formation of deep centres in the donor layer [16]. These centres, named DX centres, occur if the aluminium content increases beyond 25 percent. Due to these DX centres transistors suffer from persistent photoconductivity, shifts in the threshold voltage and a collapse of the drain-source I-V characteristics, especially at low temperatures [17]. Another difficulty is that at band discontinuities of > 0.3 eV carrier transfer to higher valleys in the conduction band of GaAs can occur. This leads to a degradation of the mobility and the saturation velocity. For these reasons the aluminium content that will be used is below 30 percent.

The sheet density in the 2-DEG is controlled by a Schottky diode between the ohmic contacts. For an effective control of the electron density in the channel it is necessary to place the gate electrode below the highly doped toplayer in the AlGaAs donor layer. This is achieved by a gate recess which is usually done wet chemically or by a dry plasma etch process. By the gate recess it is possible to obtain different threshold voltages for the HFETs. In this way enhancement (normally off: positive threshold voltage) and depletion (normally on) mode field-effect transistors can be made. In depletion mode FETs the depletion by the gate built-in voltage extends just to the interface depletion. In normally off FETs a smaller AlGaAs donor layer is present and the depletion of the gate extends to the electron gas.

The depth of the gate recess is important since parallel conduction through the AlGaAs donor layer occurs if the recess is not performed adequately [18].

By increasing the gate bias in the positive direction the sheet density of the 2-DEG increases to its maximum value  $n_{so}$ . A further increase of the voltage also leads to a conduction in the AlGaAs donor layer in parallel to the current transport in the 2-DEG. The performance of a HFET decreases as a consequence of this parasitic MESFET behaviour.

Considerations on the doping level, the spacer thickness and the thickness of the AlGaAs donor layer are given by Das et al. [19].

The 2-DEG sheet concentration can be written as a function of the gate voltage according to equation 1.17 [6,20].

$$q \cdot n_s = c_o [V_{gs} - V_T]$$

(1.17)

with co the gate to the 2-dimensional electron gas capacitance.

$$c_o = \frac{\epsilon}{d + d + \Delta d} \tag{1.18}$$

where d is the distance between the gate electrode and the AlGaAs spacer layer,  $d_i$  is the thickness of the spacer and  $\Delta d$  is the distance of the 2-DEG to the AlGaAs/GaAs interface. Applying a drain-source voltage gives an additional -V(x) term within the brackets of equation 1.17. Then the sheet density varies in the lateral direction and the I-V characteristics can be calculated.

#### 1.2.3 Pseudomorphic AlGaAs/InGaAs/GaAs HFETs

The performances of HFETs can be improved by growing a thin InGaAs layer below the AlGaAs spacer through which the current transport takes place. InGaAs is known as having a higher electron saturation velocity compared to GaAs. Ketterson et al. [21] clearly showed the influence of an increasing indium content on the direct current and high frequency characteristics of these transistors.

The bandgap discontinuity and so the conduction band discontinuity between AlGaAs and InGaAs increases with respect to the AlGaAs/GaAs heterostructure. Figure 1.3 shows the band diagrams for an AlGaAs/GaAs and an AlGaAs/InGaAs/GaAs heterostructure. The band gap difference between  $In_xGa_{1-x}As$  and  $Al_yGa_{1-y}As$  can be defined as [6]:

$$\Delta E_g = 1.247 \cdot Y + 1.5 \cdot X - 0.4 \cdot Y^2$$

for  $Y < 0.45$  (1.19)

and the discontinuities in the valence and conduction band are respectively accepted to be:

$$\Delta E_c = 0.6 \cdot \Delta Eg$$

and

$$\Delta E_v = 0.4 \cdot \Delta Eg$$

(1.20)

Beside better transport properties of electrons in InGaAs, the increased bandgap allows a higher sheet density, a greater carrier confinement and the upper valleys are farther away than in GaAs. The aluminium content of the spacer and donor layer can be reduced in this structure to avoid DX centre related problems. Due to a lattice mismatch of about 1 percent between InGaAs and the AlGaAs and GaAs the thickness of the InGaAs layer needs to be less than its critical thickness. Above the critical thickness misfit dislocations occur during the epitaxial growth which degrade the performance of transistors. Below the critical thickness the InGaAs accommodates to the lattice of GaAs with a certain strain. The critical thickness of InGaAs decreases with increasing Indium content. For this reason the amount of indium in pseudomorphic transistors is not allowed to exceed 35 percent, although degradation of the characteristics is often observed at indium contents higher than 25 percent [9].

A further improvement in HFETs can be obtained by adding a Si  $\delta$ -doped layer or pulse doped layer between the AlGaAs spacer and donor layer [22]. The advantages of this Si  $\delta$ -doped layer are a larger gate-voltage swing and a reduction of traps associated with the dopant atoms in uniformly doped AlGaAs layers. Extended discussions of this and other kind of structures can be found in references 6 and 20.

Figure 1.3, The conduction band diagram for an AlGaAs/GaAs heterostructure is shown in (a) The AlGaAs/InGaAs/GaAs heterostructure band diagram in (b).

#### 1.3 Mask layout.

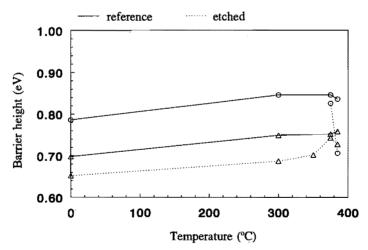

In collaboration with the University of Duisburg (Germany) a mask set has been developed for the fabrication of transistors. Beside transistors, control structures to measure the contact resistance and diodes are present on the mask. An extended discussion of the layout and the design rules concerning the alignment marks and the overlap between the different masks is given by Bertenburg [23]. Here only the main features of the mask will be mentioned.

The mask set consist of six different masks which need to be processed subsequently to obtain complete transistors. The first four masks are used in our processes, because the fabrication of air bridges (last 2 masks) has not been implemented. The different process steps will be treated in paragraph 1.4.

Each mask is divided in unity cells of 4 \* 4 mm<sup>2</sup>. which is repeated over a 3 inch circle. Each unity cell contains:

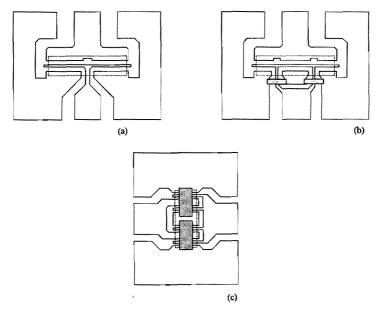

- Different transistor layouts (single-finger end-gate FETs, T-gate FETs, π-gate FETs and multiple-finger gate FETs) with gate lengths varying from 4 μm down to 0.6 μm. The width of the transistors varies from 200 μm down to 40 μm. Figure 1.4 shows a schematic layout of some different transistors. The shaded squares represent air bridges. The transistors have a Cascade layout necessary for on wafer high frequency characterisation.

- A transmission line pattern (TLM) to extract and to optimise the ohmic contact resistance. The transmission line pattern consists of six 200 μm width contacts separated from each other by increasing distances (2.5, 5, 10, 20 and 40 μm). A short discussion of the extraction of the contact resistance is given in paragraph 1.4.3.

- A 200 \* 200 μm² Schottky diode surrounded by an ohmic contact to determine the diode characteristics like barrier height, leakage current and ideality factor.

Figure 1.4, Schematically a T-gate (a), a  $\pi$ -gate (b) and a multiple finger (c) field-effect transistor is shown. The dashed squares represent air bridges.

#### 1.4 The fabrication process.

#### 1.4.1 Introduction

In this paragraph the different process steps necessary to obtain devices will be treated. All the processes are based on optical lithography. This restricts the minimum feature size to  $0.8 \mu m$ . The four main processing steps necessary for the fabrication of a transistor are:

- Mesa isolation etch.

- Drain and source ohmic contact metallisation.

- Gate recess and metallisation.

- Contact paths (Cascade overlay metallisation).

The different process steps will be discussed below. A detailed description of the different processes is written in Appendix A.

#### 1.4.2 Mesa etch.

Figure 1.5 shows the isolation of an active area of a T-gate FET. The etch is performed wet chemically in a  $H_2SO_4$ : $H_2O_2$ : $H_2O$  solution at room temperature. The etch is through the active layer into the semi-insulating buffer layer. This etch separates the devices electrically from each other and confines the current flow to a certain area.

Figure 1.5, The mesa of a T-gate field-effect transistor with a width of 150  $\mu m$ .

#### 1.4.3 Ohmic contact formation.

The ohmic drain and source contacts are processed by a lift-off technique. This process leaves the metallisation that is on the GaAs surface and lifts the metal which is on the resist when the resist is dissolved in acetone (see also Appendix A). After lift-off the metallisation is annealed to obtain an ohmic contact. This annealing is necessary to obtain a low voltage drop over the contacts compared to the voltage drop in the active region under the gate. The annealing process is optimised with respect to the surface morphology of the metallisation, the ohmic contact resistance and the edges of the metallisation. Apart from the influence of annealing on the smoothness of the metallisation edges, the quality of the edges is very sensitive to the profile obtained in the patterned resist. An undercut resist profile as shown in [23] is desirable in this case.

To obtain good ohmic contacts a number of different metallisations and fabrication techniques have been described in literature [24,25]. These metallisations have to be annealed generally between 300 and 600 °C [25,26]. In our process the metallisation is evaporated by an e-beam process in the Leybold (L 560 UV) evaporator. The base pressure of this system is  $3 \cdot 10^8$  mbar. The distance between the sample and the e-gun is 50 cm to minimise heating up of the resist which facilitates the lift off process. The metallisation used for the ohmic contacts is germanium, nickel and gold (20 nm/15 nm/200 nm).

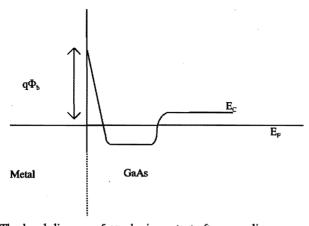

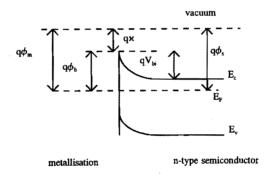

During annealing the germanium diffuses into the GaAs whereas gallium diffuses towards the metallisation. The purpose of the nickel is to prevent the metallisation from boiling up and to enhance the diffusion process. It is believed that grains of NiAs(Ge) are formed on the GaAs side of the interface below an AuGa intermixing layer [27,28,29]. Beside the vertical direction of the alloy it also extends in the lateral direction [30,31]. Since germanium is known as a n-dopant of GaAs, the GaAs surface layer becomes highly doped. This highly doped surface concentration causes an extremely narrow potential barrier. The energy band diagram of an ohmic contact is shown in Figure 1.6.

Figure 1.6, The band diagram of an ohmic contact after annealing.

Due to this narrow barrier the probability of tunnelling from the metallisation to the GaAs is increased and the transport mechanism of the ohmic contact works mainly due to this tunnelling effect.

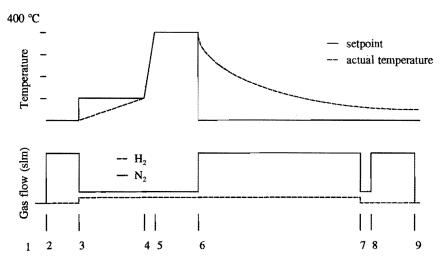

The annealing process is optimised with respect to the annealing temperature and time. The minimal contact resistance observed as function of these two parameters is ascribed to the size of the grains formed [28]. Annealing is performed in a rapid thermal annealer (AST SHS 100) in a hydrogen and nitrogen ambient. In the RTA the sample is situated on a graphite plate in a quartz tube. With halogen lamps on both sides of the quartz chamber it is possible to increase the temperature of the sample very fast. The actual temperature is controlled by a thermocouple connected to the graphite plate. A detailed description of the annealing process is described in Appendix B. The contact resistance is determined from measurements on the transmission line which has been described in paragraph 1.3. The mesa restricts the current flow across the contact of width W. Then the contact resistance can be defined as [32]:

$$R = 2 \cdot R_c + \frac{R_{sh}}{W} \cdot L_c \tag{1.21}$$

where  $R_c$  is the contact resistance,  $R_{sh}$  is the sheet resistance of the GaAs layer,  $L_c$  the distance between the ohmic contacts and R the measured resistance. It is assumed that the sheet resistance under the contacts equals the sheet resistance between the contacts.

The contact resistance was measured using a four probe method. Plotting the measured resistances as function of the distance between the ohmic contacts gives  $2R_{\rm c}$  as an intercept with the Y-axis. This resistance is usually expressed in  $\Omega\text{-mm}$ . The slope of the line reveals the sheet resistance divided by the width of the contact. These values are extracted with a least squares line fit.

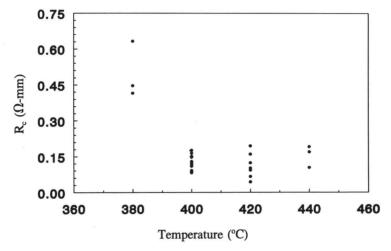

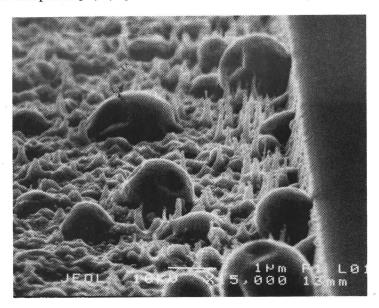

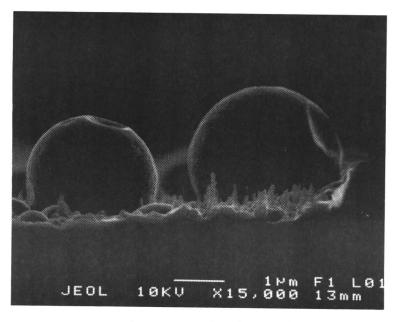

To optimise the contacts with respect to the criteria mentioned above the annealing time and temperature are varied respectively. The ohmic contacts are optimised on the MESFET layer described in paragraph 1.2.1. The MESFET structure has a highly doped toplayer since the contact resistance decreases with increasing donor concentration [29,32]. Figure 1.7 shows the contact resistance as a function of annealing temperature for 1 minute processes. The contact resistance decreases rapidly from 380 to 400 °C. At 420 °C the spreading in the resistance increases, the edges of the ohmic contacts become rough and the surface morphology deteriorates. As an example figure 1.8 shows a photograph of an ohmic contact annealed at 440 °C for 1 minute. A part of the spreading, observed at all temperatures, can be explained by the temperature overshoot of about 10 % which sometimes occurs between the ramp-up from 100 to 400 °C and the stable 400 °C period. See also appendix B.

Figure 1.7, The contact resistance on a MESFET structure as a function of the RTA anneal temperature. The annealing time is kept constant at 60 seconds.

Figure 1.8, A photograph of the surface morphology of an ohmic contact annealed at 440 °C for 1 minute.

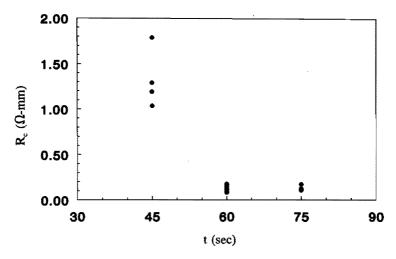

Figure 1.9, The optimisation of the contact resistance as a function of the annealing time. The temperature is kept constant at 400 °C.

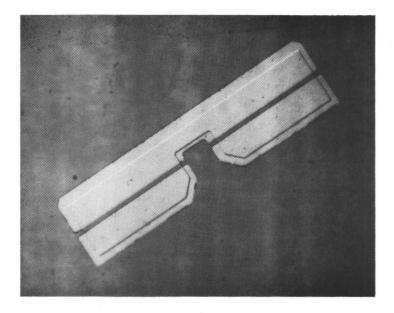

Figure 1.9 shows the extracted contact resistance after annealing at 400 °C as function of increasing annealing time. The resistance rapidly decreases if the time is increased from 45 to 60 seconds. At 75 seconds the value of the contact resistance is still low. At this time however a degradation of the surface morphology occurs. The standard annealing process used in the fabrication of the transistors is according to these experiments performed at 400 °C for 1 minute. This annealing leads to a contact resistance of 0.12  $\Omega$ -mm which is good compared to those in the literature [33]. Figure 1.10 shows a photograph of the source and drain ohmic contacts after annealing.

Figure 1.10, The ohmic drain and source contacts after the lift off process and annealing. The mesa is still visible.

#### 1.4.4 The gate metallisation.

The process for the gate metallisation is comparable to the lift off process used for the ohmic contacts. The difference is the gate recess. After defining the gate pattern in the resist between the drain and the source and before the evaporation of the Schottky metallisation the recess etch is performed. The recess is done wet chemically in a  $NH_4OH:H_2O_2:H_2O$  solution at room temperature. In later chapters processes will be described for dry etching of the recess. The importance of the gate recess is already mentioned in the theoretical discussion on the transistors. The etch is performed by subsequently etching and measuring the drain source saturation current. This is continued until an adequate saturation current is reached. In this way it is possible to fabricate enhancement and depletion mode transistors.

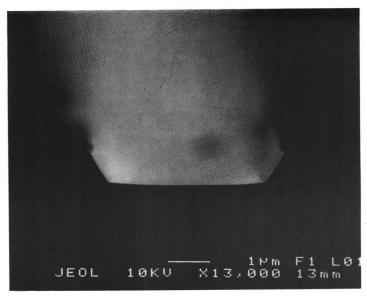

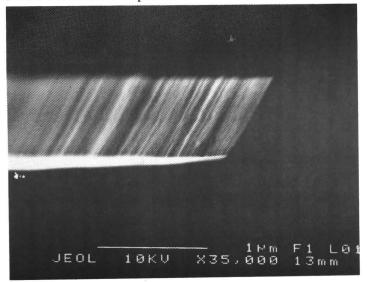

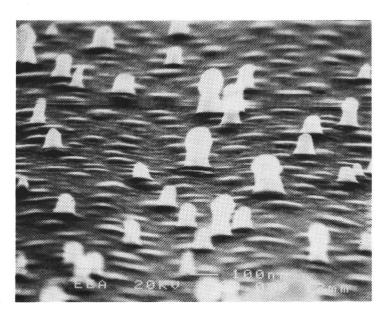

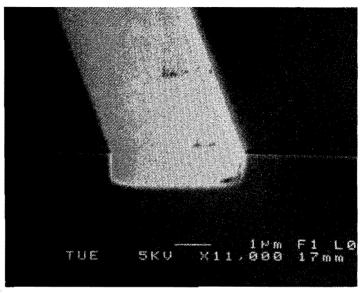

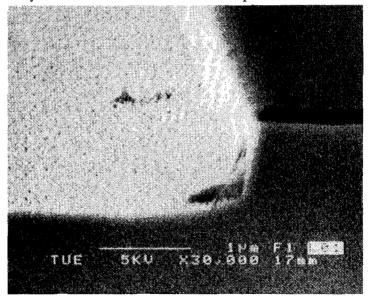

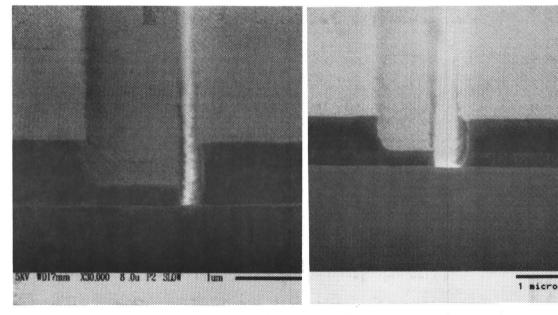

After the gate recess a titanium, platinum, gold (50 nm/20 nm/150 nm) Schottky metallisation is evaporated in the Leybold evaporator. The results after lift-off are shown in figures 1.11 and 1.12.

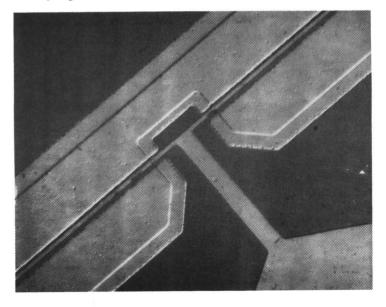

Figure 1.11, The 1  $\mu m$  gate metallisation.

Figure 1.12, A detail photograph of the T-gate metallisation.

# 1.4.5 Cascade overlay metallisation.

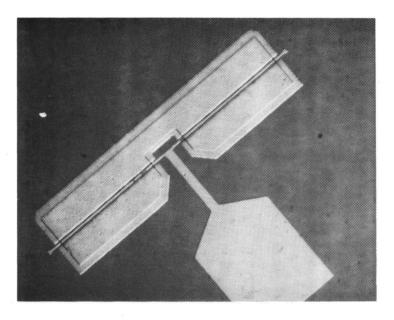

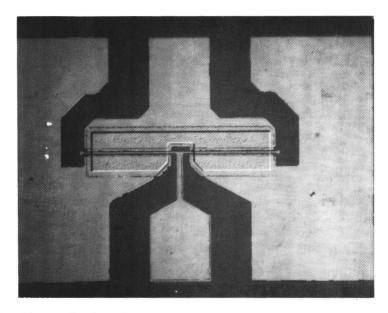

The contact or overlay metallisation is made by a lift off technique. This metallisation is intended for contact paths necessary for the on-wafer high frequency measurements and the DC characterisation. The metallisation sequence is the same as used for the gate. Figure 1.13 shows the Cascade contacts and the completed transistor after processing of the fourth mask.

Figure 1.13, The completed transistor.

#### 1.5 Electrical characterisation.

#### 1.5.1 DC characterisation

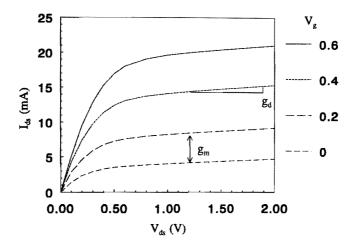

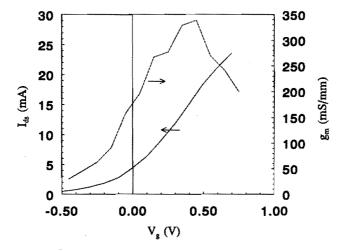

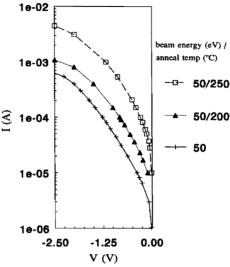

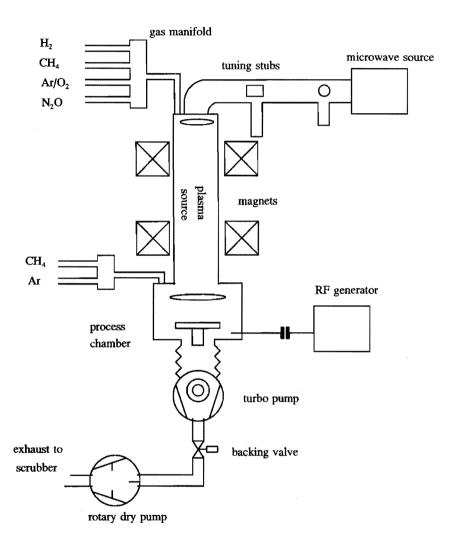

As already mentioned, the drain to source current of field-effect transistors can be modulated by applying a DC bias to the gate with respect to the source. By decreasing the gate voltage of a MESFET the depletion layer extends more into the active layer and the conductivity of the current carrier layer is modulated. In a HFET the sheet charge density is modulated by the gate voltage. In both cases the drain to source saturation current changes. The variation in this saturation current as a function of a change in the gate voltage is expressed by the transconductance (See figure 1.14 and 1.15). The transconductance  $g_m$  is defined as:

$$g_m = \frac{\partial I_{ds}}{\partial V_{es}} \tag{1.22}$$

The transconductance is usually expressed in mmho/mm or mS/mm and increases with decreasing gate length. The transconductances observed for HFETs are usually higher than those of MESFETs. This is because the HFETs have a better carrier confinement and the distance between the gate and the 2-DEG is strongly reduced.

The source resistance of a transistor has a significant influence on the external measured transconductance. The source resistance is defined as the sum of the contact resistance  $R_c$  and the resistance of the GaAs path between the source and the channel  $R_s$ . The source resistance causes a negative feedback whose influence on the transconductance can be written as:

$$g_{m_{\text{extern}}} = \frac{g_{m_{\text{intern}}}}{1 + R_s \cdot g_{m_{\text{intern}}}} \tag{1.23}$$

The resistance can be minimised by a short gate-to-source distance and an adequate technology for ohmic contacts with low resistivity. The optimisation of the ohmic contact is already treated in paragraph 1.4.3. Another parameter which is often referred to is the output conductance  $g_d$ . This is the slope of the drain-to-source saturation current at a constant gate voltage with respect to  $V_{ds}$  (see also figure 1.14).

$$g_d = \frac{\partial I_{ds}}{\partial V_{ds}} \tag{1.24}$$

At the end of the chapter these parameters will be compared to those in literature.

Figure 1.14, The drain-source current as a function of the drain-source voltage  $V_{ds}$  at different gate voltages  $V_g$  for a pseudomorphic HFET. The HFET has a gate length of 1  $\mu m$  and a width of 100  $\mu m$ . The transconductance  $g_m$  and the output conductance  $g_d$  are shown schematically.

Figure 1.15, The transconductance  $g_m$  and the drain-source current  $I_{ds}$  as a function of the gate voltage  $V_g$  for the pseudomorphic HFET mentioned above ( $V_{ds} = 2$  V).

## 1.5.2 High frequency measurements.

#### 1.5.2.1 S-parameters

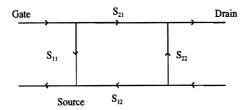

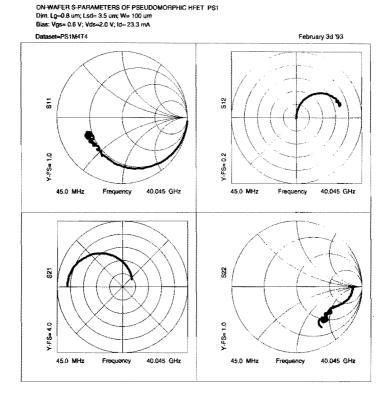

The performance of the transistors is characterised at microwave frequencies ranging from 45 MHz to 40 GHz. The S-parameters or scattering parameters represent the reflection and the transmission coefficients. This is shown schematically in figure 1.16.  $S_{11}$  and  $S_{22}$  represent the reflection coefficients at the input and output respectively.  $S_{12}$  and  $S_{21}$  represent the transmission coefficients. They are measured on wafer with a HP 8510 network analyzer and represented in polar plots and Smith charts. For a wet chemically processed pseudomorphic HFET with gate length of 1  $\mu$ m and width 100  $\mu$ m figure 1.17 shows an example of these measurements.

Figure 1.16, The microwave representation of the transistor twoport and the explanation of the different S-parameters.

From these measurements other parameters can be derived such as:

- The Maximum Available Gain (MAG): is the gain if the transistor is unconditional stable.

- The Maximum Stable Gain (MSG): is the gain if the transistor is not unconditional

stable. The transition between these two parameters is determined by the k-factor which

can be deduced from the measurements.

- f<sub>t</sub> : the cut off frequency is the frequency of unity current gain.

- f<sub>max</sub>: is the maximum frequency of oscillation or unity

power gain frequency.

Figure 1.17, The different S-parameters in polar plots and Smith charts for a 1 \* 100  $\mu$ m pseudomorphic HFET as function of the frequency.  $S_{11}$  and  $S_{22}$  represent the reflection coefficients at the input and output respectively.  $S_{12}$  and  $S_{21}$  represent the transmission coefficients

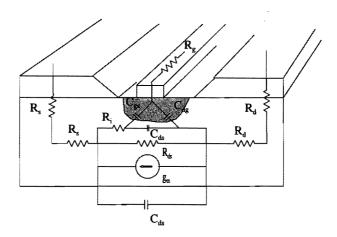

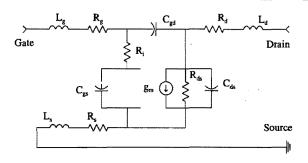

From these S-parameters the parameters of a small-signal equivalent circuit can be extracted. An example of such a circuit is shown in figure 1.18.

Figure 1.18, The small signal equivalent circuit of a MESFET.

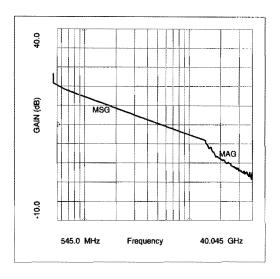

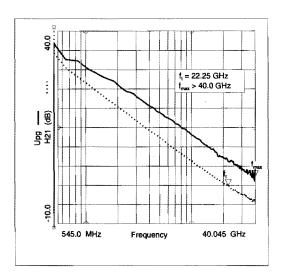

For the 1 \* 100  $\mu$ m wet chemically processed pseudomorphic HFET the maximal stable and maximal available gain are shown in figure 1.19. Figure 1.20 shows the unilateral power gain and the current gain from which the maximum frequency of oscillation  $f_{max}$  and the frequency of unity current gain  $f_t$  are extracted. The cut off frequency, measured for a conventional AlGaAs/GaAs HFET, is generally lower than for the pseudomorphic HFET. This is explained by a lower modulation efficiency [34] and a lower electron saturation velocity under the gate in the conventional HFET. The cut off frequency depends on the average electron velocity  $v_{avg}$  as  $v_{avg}/2\pi$  L. Beside the influence of the average velocity the cut off frequency increases with decreasing gate lengths [35,36].

The parameters extracted for the equivalent circuit of this HFET are listed in figure 1.21. The DC characteristics have been shown in Figure 1.14 and 1.15 in the previous paragraph.

Figure 1.19, The maximum stable gain (MSG) and the maximum available gain (MAG) as function of the frequency for a 1 \* 100 µm pseudomorphic HFET.

Figure 1.20, The current gain  $H_{21}$  and the unilateral power gain  $U_{pg}$  from which the frequency of unity current gain  $f_t$  and the maximum frequency of oscillation  $f_{max}$  are determined.

Figure 1.21, The small signal equivalent circuit for the above mentioned pseudomorphic HFET. The extracted parameters from the simulation are listed below.

# The extracted S-parameters are:

| W<br>L                                                                  | =                                       | 100<br>1                      | μm,<br>μm,            |  | $L_{g}$ $L_{s}$ $L_{d}$                               | =           | 1.2<br>6.7<br>10.0 | pH,<br>pH,<br>pH, |

|-------------------------------------------------------------------------|-----------------------------------------|-------------------------------|-----------------------|--|-------------------------------------------------------|-------------|--------------------|-------------------|

| $egin{array}{l} R_{ m g} \ R_{ m d} \ R_{ m i} \ R_{ m ds} \end{array}$ | = = = = = = = = = = = = = = = = = = = = | 7.1<br>0.5<br>0.5<br>6<br>750 |                       |  | C <sub>gs</sub><br>C <sub>gd</sub><br>C <sub>ds</sub> | =<br>=<br>= | 260<br>34<br>16    | fF,<br>fF,<br>fF. |

| g <sub>m</sub><br>T <sub>delay</sub><br>Angle                           | =                                       | 36.4<br>3.0<br>0              | mS,<br>ps,<br>degree, |  |                                                       |             |                    |                   |

#### 1.5.2.2 Noise Figure (NF).

The Noise Figure (NF) represents the noise performance of a transistor. It corresponds to the signal to noise ratio of the input signal divided by the signal to noise ratio of the output signal. The noise factor is usually expressed in dB and is defined as:

$$NF = \frac{\left(\frac{signal}{noise}\right)_{inp}}{\left(\frac{signal}{noise}\right)_{out}}$$

(1.25)

The noise figure is a function of the measurement frequency, the applied DC bias voltages and the matching. Obtaining the minimal noise figure NF<sub>o</sub> requires the optimisation of these parameters. According to Fukui the minimal noise figure can be defined as [37]:

$$NF_o = 1 + 2\pi \cdot K_f f C_{gs} \cdot \sqrt{\frac{(R_s + R_g)}{g_m}} \cdot 10^{-3}$$

(1.26)

Here  $K_f$  is a material and frequency dependent constant, f the frequency in GHz and  $C_g$ , the gate to source capacitance in pF. The source resistance needs to be minimised to obtain a low noise figure. This resistance can be improved by a short gate to source distance, to minimise the resistance in the GaAs path, and in a second way by optimising the contact resistance between the ohmic metallisation and the active GaAs layer. Further more the noise can be reduced by decreasing the gate length though its influence on the gate to source capacitance.

Some measurements have been made on the noise performance of MESFETs and pseudomorphic HFETs. The results of these measurements will be presented at the end of this chapter.

# 1.6 Results.

The next pages show some typical results obtained on MESFETs, AlGaAs/GaAs HFETs and pseudomorphic AlGaAs/InGaAs/GaAs HFETs. First the layer structure will be shown, then the parameters extracted from the DC and microwave measurements. The contact resistances are measured with the transmission line method. Finally the noise figures of typical MESFETs will be compared to those of pseudomorphic HFETs.

#### 1.6.1 MESFETs.

wafer number:

W314 E3 FET

#### layer structure:

| caplayer             | $2.10^{18}$ | cm <sup>-3</sup> | (Si) | 20  | nm | n⁺-GaAs, |  |

|----------------------|-------------|------------------|------|-----|----|----------|--|

| active layer         | $3.10^{17}$ | cm <sup>-3</sup> | (Si) | 200 | nm | n-GaAs,  |  |

| buffer layer         | undope      | ed               |      | 2   | μm | GaAs,    |  |

| S.I. GaAs substrate. |             |                  |      |     |    |          |  |

#### Fet 9 M4T1:

#### DC characterisation

| L              | gate length                                        | 1    | μm,    |

|----------------|----------------------------------------------------|------|--------|

| $L_{ds}$       | drain-source separation                            | 4    | μm,    |

| w              | gate width                                         | 150  | μm,    |

| $I_{ds,sat}$   | $V_{g} = 0 \text{ V},  V_{ds} = 2.0 \text{ V}$     | 33.2 | mA,    |

| g <sub>m</sub> | $V_{g} = 0 \text{ V},  V_{ds} = 2.0 \text{ V}$     | 176  | mS/mm, |

| $g_{m,max}$    | $V_g = 0.25 \text{ V}, V_{ds} = 2.0 \text{ V}$     | 190  | **     |

| g <sub>d</sub> | $V_g = 0 \text{ V}, \qquad V_{ds} = 2.0 \text{ V}$ | 6.7  | mS/mm, |

| V <sub>T</sub> | -                                                  | -2.0 | V.     |

#### TLM measurement

$R_c$  0.12  $\Omega$ -mm

#### HF characterisation

measured at  $V_{ds}$  = 2.0 V,  $V_g$  = +0.25 V and  $I_{ds}$  = 38.03 mA.

$f_{t}$  16.8 GHz,  $f_{max}$  35.4 GHz.

# 1.6.2 AlGaAs/GaAs HFETs.

wafer number:

MO383-3\*

# layer structure:

| caplayer             | $3.5 \cdot 10^{18}$ | cm <sup>-3</sup> | (Si) | 90  | nm | n⁺-GaAs,                                    |

|----------------------|---------------------|------------------|------|-----|----|---------------------------------------------|

| donor layer          | $1.5 \cdot 10^{18}$ | cm <sup>-3</sup> | (Si) | 50  | nm | n-Al <sub>0.23</sub> Ga <sub>0.77</sub> As, |

| spacer               | undoped             |                  |      | 2   | nm | $Al_{0.23}Ga_{0.77}As$ ,                    |

| buffer layer         | undoped             |                  |      | 0.8 | μm | GaAs,                                       |

| S.I. GaAs substrate. |                     |                  |      |     |    |                                             |

# HW1 M4T2:

# DC characterisation

| L                  | gate length                                    | 0.8   | μm,    |

|--------------------|------------------------------------------------|-------|--------|

| $L_{ds}$           | drain-source separation                        | 3.5   | μm,    |

| w                  | gate width                                     | 150   | μm,    |

| $I_{ds,sat}$       | $V_g = 0$ V, $V_{ds} = 2.0$ V                  | 39.8  | mA,    |

| g <sub>m</sub>     | $V_{g} = 0$ V, $V_{ds} = 2.0$ V                | 175   | mS/mm, |

| g <sub>m,max</sub> | $V_g = -0.5 \text{ V}, V_{ds} = 2.0 \text{ V}$ | 224   | mS/mm, |

| $g_d$              | $V_{g} = 0$ V, $V_{ds} = 2.0$ V                | 20.9  | mS/mm, |

| $V_{\rm T}$        | •                                              | -1.83 | V,     |

## TLM measurement

$$R_c$$

< 0.1  $\Omega$ -mm.

#### HF characterisation

measured at  $V_{ds}$  = 2.0 V,  $V_g$  = -0.50 V and  $I_{ds}$  = 17.80 mA.

| f,               | 22.3 | GHz, |

|------------------|------|------|

| f <sub>max</sub> | 36.1 | GHz. |

\* This layer structure is grown at the Walter Schottky Institute of the Technical University of Munich.

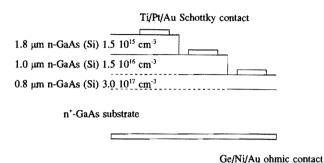

# 1.6.3 AlGaAs/InGaAs/GaAs HFETs.

wafer number: W385 H79

# layer structure:

| caplayer             | 2.0.1018            | cm <sup>-3</sup> | (Si) | 70  | nm | n⁺-GaAs,                                    |

|----------------------|---------------------|------------------|------|-----|----|---------------------------------------------|

| donor layer          | $1.5 \cdot 10^{18}$ | cm <sup>-3</sup> | (Si) | 50  | nm | n-Al <sub>0.20</sub> Ga <sub>0.80</sub> As, |

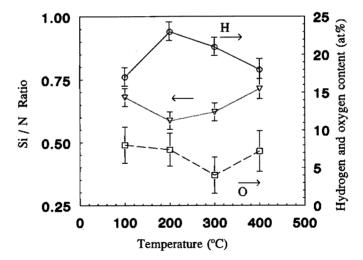

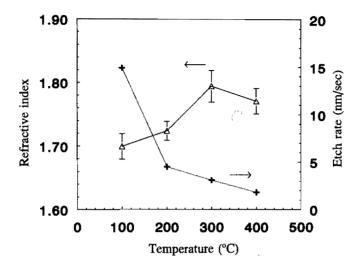

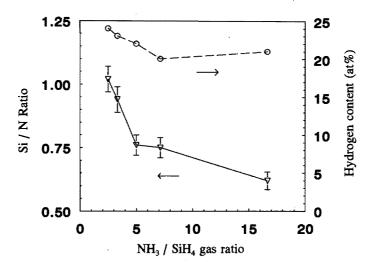

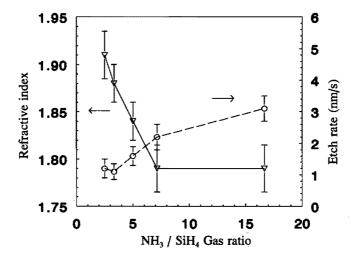

| spacer               | undoped             |                  |      | 3   | nm | $Al_{0.20}Ga_{0.80}As$ ,                    |