Received 8 February 2023, accepted 23 March 2023, date of publication 3 April 2023, date of current version 6 April 2023.

Digital Object Identifier 10.1109/ACCESS.2023.3264265

## APPLIED RESEARCH

# IXIAM: ISA EXtension for Integrated Accelerator Management

## BIAGIO PECCERILLO<sup>®1</sup>, ELHAM CHESHMIKHANI<sup>®2</sup>, MIRCO MANNINO<sup>®1</sup>, ANDREA MONDELLI<sup>3</sup>, AND SANDRO BARTOLINI<sup>®1</sup>

<sup>1</sup>Department of Information Engineering and Mathematics, University of Siena, 53100 Siena, Italy

<sup>2</sup>Department of Computer Engineering, Amirkabir University of Technology (Tehran Polytechnic), Tehran 15875-4413, Iran <sup>3</sup>Huawei Technologies Research and Development (U.K.) Ltd., CB4 0WG Cambridge, U.K.

Corresponding author: Biagio Peccerillo (peccerillo@diism.unisi.it)

This work was supported by Huawei Technologies Research and Development (U.K.) Ltd.

ABSTRACT During the last few years, hardware accelerators have been gaining popularity thanks to their ability to achieve higher performance and efficiency than classic general-purpose solutions. They are fundamentally shaping the current generations of Systems-on-Chip (SoCs), which are becoming increasingly heterogeneous. However, despite their widespread use, a standard, general solution to manage them while providing speed and consistency has not yet been found. Common methodologies rely on OS mediation and a mix of user-space and kernel-space drivers, which can be inefficient, especially for fine-grained tasks. This paper addresses these sources of inefficiencies by proposing an ISA eXtension for Integrated Accelerator Management (IXIAM), a cost-effective HW-SW framework to control a wide variety of accelerators in a standard way, and directly from the cores. The proposed instructions include reservation, work offloading, data transfer, and synchronization. They can be wrapped in a high-level software API or even integrated into a compiler. IXIAM features also a user-space interrupt mechanism to signal events directly to the user process. We implement it as a RISC-V extension in the gem5 simulator and demonstrate detailed support for complex accelerators, as well as the ability to specify sequences of memory transfers and computations directly from the ISA and with significantly lower overhead than driver-based schemes. IXIAM provides a performance advantage that is more evident for small and medium workloads, reaching around  $90 \times$  in the best case. This way, we enlarge the set of workloads that would benefit from hardware acceleration.

**INDEX TERMS** Hardware accelerators, domain-specific architectures, parallel architectures, heterogeneous systems, RISC-V.

#### I. INTRODUCTION

Today hardware accelerators are employed in a variety of contexts that span from wearable and embedded computing to supercomputers and data-centers. Hwu and Patel [1] define a hardware accelerator as "a separate architectural substructure [...] that is architected using a different set of objectives than the base processor, where these objectives are derived from

The associate editor coordinating the review of this manuscript and approving it for publication was Thomas Canhao  $Xu^{\textcircled{D}}$ .

the needs of a particular class of applications".<sup>1</sup> They are now regarded as the primary driving force of computer architecture [3], thanks to their ability to improve non-functional metrics such as throughput and energy efficiency. With respect to general-purpose resources, they can take advantage of efficient forms of parallelism, local/optimized memories, ad-hoc

<sup>1</sup>Some works refer to them as *loosely-coupled accelerators*, to distinguish them from *tightly-coupled accelerators* [2]. According to the definition, tightly-coupled accelerators are rather *specialized functional units* integrated into the processor.

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 License. For more information, see https://creativecommons.org/licenses/by-nc-nd/4.0/ datapaths, reduced fetch and decode overheads, and support for special data-types [3], [4].

In the last years, accelerators have greatly influenced the design of computing systems, with a profound impact on Systems-on-Chip (SoCs) in particular [5]. These have become increasingly heterogeneous, with various accelerators integrated with the central general-purpose cores on the same chip. Core-accelerator communication is achieved through a dedicated Network-on-Chip (NoC) or a bus with a standard interface such as ARM's Advanced Microcontroller Bus Architecture (AMBA) [6]. Usually, accelerators access the system's physical memory by connecting to a shared Last-Level Cache (LLC) [7], [8] or the DRAM [9], [10], relying on DMA techniques not to burden the CPU.

From a software perspective, functional units are usually targeted at the Instruction Set Architecture (ISA) level, but on-chip accelerators commonly require a mix of userspace and kernel-space drivers [5]. Programmers interact with a high-level accelerator-specific Application Programming Interface (API) that transparently invokes functions provided by the underlying driver layer. Drivers, in turn, may rely on system calls that ask for the Operating System (OS) mediation in a variety of tasks: management of accelerators' resources, scheduling of simultaneous accesses from different processes, data consistency maintenance across different privilege levels, virtual-to-physical address translation whether as the main actor or as an accelerator assistant [11], [12]. The presence of many layers and different privilege levels to achieve CPU-accelerator communication can be a source of inefficiencies and limit the set of tasks eligible for acceleration [2], [13], [14]. In fact, the latency associated with CPU-accelerator interaction is significantly longer than the conventional core operations. This communication overhead can be amortized only when the accelerated task has a coarsegrain nature, as fine-grain ones would be dominated by communication latency and thus their acceleration would not be convenient.

Albeit the driver-oriented solution is the most common to achieve CPU-accelerator interaction, it is not the only one [5]. Some hardware accelerator proposals rely on special instructions added to the ISA of the processor [15], [16], [17], [18], [19], [20]. These ISA extensions, however, are always accelerator-specific, and as a result, they cannot be scaled. By adding new accelerators, the ISA would have to be further extended, leading to ISA bloating that would be particularly harmful to fixed-size instruction sets and negatively impact both the chip area and energy consumption of the decoding phase.

Overall, both accelerator-specific ISA extensions and userspace/kernel-space drivers have drawbacks – summarizing, lack of generality and low scalability in the first case, and high latency in the second. In this paper, we present an *ISA eXtension for Integrated Accelerator Management* (IXIAM), a low-latency, high-performance, general solution to orchestrate on-chip accelerators from CPU cores. It is based on a general ISA extension that supports a wide variety of accelerators and a limited hardware infrastructure. The proposed instructions facilitate managing accelerator reservation, work offloading, synchronization, and data transfers with finegrained control of accelerator local memories. It is paired with a user-space interrupt mechanism to signal events such as execution completion and error occurrence from the accelerators directly to the user process. The supported hardware infrastructure implements communication and some tasks normally delegated to the OS, such as reservation. As a result, the entire proposal can be, in principle, implemented in user space while still guaranteeing security and isolation.

We extend and enrich our previous proposal presented in [21]. The main differences with the previous proposal are: a) the possibility to have fine-grained control of accelerator local memories, b) the user-space interrupt mechanism, c) the support of a far broader class of accelerators, since we do not require them to work according to a fixed finite state machine. Moreover, in this work, we discuss further aspects such as memory coherency and data consistency.

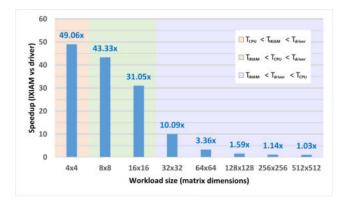

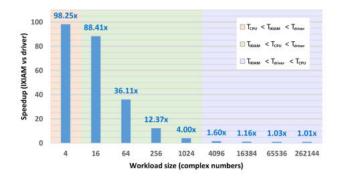

We implement our framework in the gem5 simulator [22] by extending the RISC-V ISA and adding all the necessary modules to simulate the proposed hardware infrastructure. We evaluate it performance-wise in comparison with conventional driver-based interfacing, on five different simulated accelerators. We show that our proposal dramatically improves performance for small workloads (around 90×) and medium workloads (more than 4×), surpassing in most cases even an optimized CPU-only implementation – thus, enlarging the set of workloads that benefit from hardware acceleration.

The main contributions of this paper can be summarized as follows:

- We propose IXIAM, an HW-SW framework articulated in an ISA extension and hardware infrastructure to manage on-chip accelerators, taking care of reservation, work offloading, data transfers, fine-grained control of accelerator local memories, and synchronization;

- We propose a user-space interrupt mechanism to signal execution completion and errors directly to the user process, with no OS mediation;

- We implement the whole proposal in the gem5 simulator by extending RISC-V ISA and providing the necessary hardware modules;

- We evaluate our proposal in the case of five widelyused accelerators and compare it against a conventional driver-based solution, showing that we improve performance in all the cases, but mostly for small and medium workloads;

- We show that our proposal enriches the set of workloads that are eligible for hardware acceleration, as we achieve better performance than a non-accelerated implementation in cases where a driver-based one would not be convenient.

The remainder of the paper is organized as follows. In Section II, we present the proposed framework in detail, and in Section III we analyze it critically and discuss some limitations and criticalities. Then, in Section IV we evaluate the proposal by simulating various accelerators in the gem5 simulator. Section V presents some related work. Finally, we conclude in Section VI.

#### **II. PROPOSED FRAMEWORK**

In this section, we present the details of IXIAM, our proposed general framework to implement instruction-based communication between accelerators and processors in SoCs. First, we present the reference architectural context. Then, we discuss the hardware infrastructure that must be added to it as part of our proposal. Finally, we present the additional instructions that must be added to the processor ISA.

#### A. ARCHITECTURAL REFERENCE

In this work, we assume a heterogeneous SoC as our architectural reference. The SoC includes a general-purpose processor with m cores and n accelerators.

With reference to the taxonomy presented in [5], we assume these accelerators are integrated on-chip, nonprogrammable, but may be reconfigurable and possibly endowed with heterogeneous memory resources. They accelerate tasks in any application domain. From an architecture point of view, they can have a register file (e.g., 32-bit, 64-bit registers), any level of cache memories (also no caches), and one or more addressable local memories. These can be used to store input data to be consumed by the accelerated task, or intermediate and output data produced during its execution. We do not impose any constraint on the nature of their computing engines. They have access to the physical memory of the system through a level of the memory hierarchy. Without loss of generality, we assume that they are connected to the LLC, which is located on the chip and shared between cores and accelerators - which is a common choice adopted by SoC designers [7], [8], [19], [23], [24]. They are equipped with a DMA controller to load/store data from/to the LLC without CPU intervention.

Cores and accelerators are connected through an interconnect, which can be a simple bus or a ring-/mesh-based NoC. We take as a reference a ring-based NoC, which is general and is used in different kinds of conventional acceleratorprocessor interconnections [25], [26]. The evaluation of different kinds of NoCs is beyond the scope of this paper and is left as future work. The network allows any core to send messages/packets to any accelerator and vice versa. We refer to these messages as Accelerator-Core Messages (ACMs).

#### **B. IXIAM HARDWARE INFRASTRUCTURE**

IXIAM requires some hardware additions to the SoC described above as a necessary infrastructure to allow the proposed instructions to control on-chip accelerators. We identify these additions as the *IXIAM Hardware Infrastructure*.

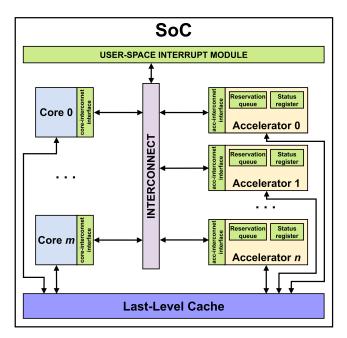

FIGURE 1. Reference SoC with IXIAM Hardware Infrastructure components highlighted in green.

Figure 1 shows the reference SoC architecture, with the additions highlighted in green.

Each accelerator must be identified by a unique id (in the following, *accId*). Without loss of generality, we assume an 8-bit id, to support up to 256 different accelerators on the same SoC. This id must be known to the NoC in order to deliver ACMs coming from the cores to the right target accelerator.

Accelerators must be reservable to processes running on the cores. To achieve this, each of them must be equipped with a FIFO *reservation queue* where reservation requests from different processes must be enqueued up until the queue is full – then, the requests are dropped. An accelerator is considered *reserved* to the process whose id (*procId* in the following) is at the front of the queue. We denote this process as the *owning process*. We adopt a process-based reservation scheme rather than a core-based or thread-based one for two main reasons:

- Processes are the *natural* entities to take advantage of task acceleration by offloading portions of work to dedicated accelerators;

- In a standard multi-core environment, a process can be made of various threads of execution, and the OS is free to schedule them on any core at any time according to a policy.

Some authors prefer a thread-based reservation scheme [2]. We could also adopt this solution with no substantial modifications to our proposal. However, reserving an accelerator to a single thread of execution would force the programmer to concentrate all the accelerator-related code in the same thread. With a process-based reservation scheme, conversely, the code can be structured more freely: for instance, one thread could be used to ask for reservation in a timer-like

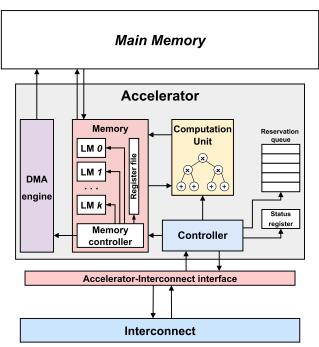

FIGURE 2. Sample internal structure of an accelerator.

fashion, signaling another thread to transfer data/launch accelerated tasks if reservation succeeds or execute non-accelerated fallback code otherwise, etc.

We consider an accelerator *busy* when it is executing an accelerated task. Each accelerator must be equipped with a *status register* to summarize the accelerator's status. Its values are interpreted as pertaining to three possible statuses:

- "0" if the accelerator is not busy and no errors occurred;

- "1" if the accelerator is busy and no errors occurred;

- error code if an error occurred.

The owning process can read the status register through a convenient instruction that will be discussed in Subsection II-D. If the status register holds an error state, it is cleared upon read. Figure 2 shows a block diagram of an accelerator with internal details.

In order to support a user-space interrupt mechanism, the SoC must be augmented with an ad-hoc module to let processes register their routines and hold information about occurred user-space interrupts, which include, for each interrupt: the process that should handle it, the accelerator where it originated, and some parameters to detail its reason. It will be discussed in-depth in Subsection II-E.

The last components of the IXIAM Hardware Infrastructure are the modules that allow cores and accelerators to deliver messages through the NoC. We denote them as the *core-NoC interface* and the *accelerator-NoC interface*. Both have sender and receiver complementary roles, as they take command from their attached module (core in one case, accelerator in the other) and send/receive messages through the NoC.

Summarizing, the IXIAM Hardware Interface includes:

• a unique identifier accId for each accelerator;

- a reservation queue for each accelerator;

- a status register for each accelerator;

- a user-space interrupt module on the SoC;

- a core-NoC interface for each core;

- an accelerator-NoC interface for each accelerator.

#### C. ACCELERATOR-CORE MESSAGES

Every accelerator-oriented instruction causes an ACM sending from the core where it is executed to the target accelerator. We call it a *request ACM*, as opposed to the *response ACM* that may be sent back from the accelerator to the core. The majority of instructions do not need a response ACM. In those cases, the instructions are committed immediately right after a request ACM has been sent. Conversely, some instructions need a response ACM to carry a return value that will be written in an output register, typically specified as instruction operand. Thus, they will be committed when the response ACM is received.

Based on this, we define *synchronous* and *asynchronous* instructions as follows:

- Asynchronous instructions are committed immediately after sending a request ACM;

- Synchronous instructions are committed when the response ACM is received on the core.

Although synchronous instructions need a response ACM reception to be committed, they do not need to stall the pipeline till such event. For instance, in a core with out-of-order execution, no special care is needed apart from the ordinary Read after Write (RAW) dependency management among instructions: since these instructions have an output register, successive dependent instructions (i.e., having such register as input) are blocked until the synchronous instruction is committed.

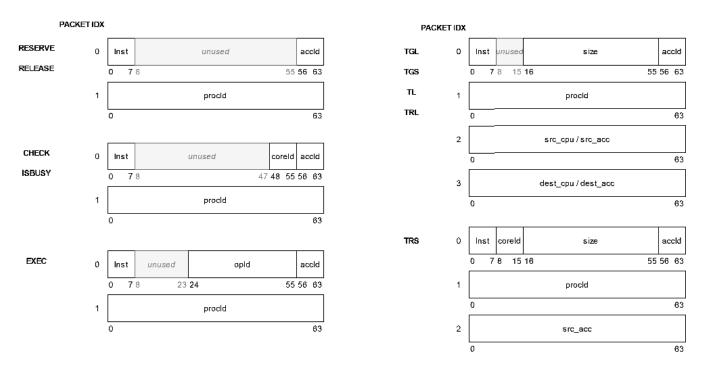

Figure 3 shows the ACMs associated to the proposed instructions, that will be discussed in-depth in the next subsection. Without loss of generality, we adopt a sample format organized in indexed 64-bit packets.

Every ACM contains the parameters needed by the NoC and the accelerator to execute the intended operations. The first byte, Inst, identifies the executed instruction, and the others are usually provided as instruction operands. coreId and procId make an exception.

coreId is present only in CHECK, ISBUSY, and TRS, which are the only synchronous instructions in our proposal. It identifies the id of the core where the instruction has been executed. This is necessary because, this way, the accelerator can enrich the response ACM with the same coreId it received in the request, so the NoC can deliver it to the right core, the output register can be written and the instruction can be committed.

procld is necessary to identify the process that want to communicate with the accelerator. procld is used to reserve the accelerator to the calling process, and to check the legitimacy of subsequent requests, e.g., data transfers and operation execution, that should be granted only to the

FIGURE 3. Possible request ACMs generated by different instructions, organized in 64-bit packets.

owning process. Since this value determines uniquely what can be done (or not) with an accelerator, it cannot be a user-provided parameter for security reasons. A malevolent process could easily disguise itself as another one by simply using another procld value. For this reason, this value is read automatically by the IXIAM Hardware Infrastructure from the Control and Status Registers (CSRs). An example of process identifier that would work in our proposal could be the pointer to the page table, which uniquely identifies each process.

The target accelerator is always determined with a userprovided accId parameter, which is needed by all the instructions and is present in all the related request ACMs. In this example, 8 bits are dedicated to it, so 256 different accelerators are supported. The NoC reads it to deliver the ACM to the right accelerator, and generates an exception like "Illegal Instruction" if this does not correspond to any accelerator in the SoC.

The remaining parameters will be discussed in the next subsection as operands of the proposed instructions.

#### D. ISA EXTENSION

In the following, we present our accelerator-oriented ISA extension. In principle, it could be implemented as an extension to any existing ISA, as it is independent on existing instructions. In this work, we design it as a RISC-V extension. More precisely, we extend the RISC-V RV64I instruction set with Zicsr instructions [27], and implement our instructions using the R-type format. All the operands are *register operands*: they indicate the register in which the needed

| TABLE 1. Details of the proposed instructions. CPU-reg operands are     |

|-------------------------------------------------------------------------|

| read from a conventional CPU register (e.g., t0). CSR operands are read |

| from Control and Status Registers.                                      |

| Instruction    | 1 Input                        | Output               | CPU-reg | CSR                     |

|----------------|--------------------------------|----------------------|---------|-------------------------|

| RESERVE        | E accId                        |                      |         | procId                  |

| CHECK          | accId                          | $\operatorname{ret}$ |         | $\operatorname{procId}$ |

| $\mathrm{TGL}$ | size, src_cpu,<br>dest_acc     |                      | accId   | procId                  |

| TGS            | size, src_acc,<br>dest_cpu     |                      | accId   | procId                  |

| $\mathrm{TL}$  | size, src_acc,<br>dest_acc     |                      | accId   | procId                  |

| $\mathrm{TRL}$ | size, src_reg_cpu,<br>dest_acc |                      | accId   | procId                  |

| TRS            | size, $src\_acc$               | $\operatorname{ret}$ | accId   | $\operatorname{procId}$ |

| EXEC           | accId, opId                    |                      |         | $\operatorname{procId}$ |

| ISBUSY         | accId                          | ret                  |         | $\operatorname{procId}$ |

| RELEASE        | E accId                        |                      |         | procId                  |

value is stored. Our instructions have the minimum privilege level, so they can be executed by user-space code. Table 1 summarizes them.

#### 1) RESERVE INSTRUCTION

Conventionally, accelerator-processor communication in SoCs needs to start with some handshaking protocol between the two entities involved. For instance, the processor could ask if the requested accelerator is ready to work or not. If so, it could *reserve* the accelerator and offload work to it until it is done. Then, it can *release* it.

In this work, we adopt this scheme on a per-process basis, allowing the process to reserve the accelerator for itself and offload work to it from any thread of execution, independently of the core where it is scheduled. We propose the RESERVE instruction to achieve this, with format RESERVE <accid>.

RESERVE execution generates an ACM containing accld, which is the only operand of the instruction, and procld, which is provided by the IXIAM Hardware Infrastructure as specified. The instruction is asynchronous: it is committed immediately, and the ACM is sent through the NoC to the target accelerator identified by accld.

As discussed in Subsection II-B, if the accelerator is free, the received procld is enqueued and the calling process becomes the owning process. Conversely, if the queue is not empty neither full and procld has not been previously enqueued, it is enqueued to wait for its turn to own the accelerator. Finally, if the queue is full the reservation request is just dropped. Listing 1 shows the RESERVE algorithm.

This way, the accelerator reservation is compatible with a multi-process environment, which is the most common use case nowadays. However, the choice of having a reservation queue in hardware permits implementing the whole logic in a secure manner without asking for OS intervention, which is beneficial from a latency point of view.

| Algorithm 1 Micro-Operations of RESERVE      |     |

|----------------------------------------------|-----|

| Instruction                                  |     |

| RESERVE(accId, procId);                      |     |

| acc = accelerators[accId];                   |     |

| if acc.reservationQueue.empty() then         |     |

| acc.reservationQueue.enqueue(procId);        |     |

| acc.status = RESERVED;                       |     |

| else if not acc.reservationqueue.full() then |     |

| acc.reservationQueue.enqueue(procId);        |     |

| else                                         |     |

| /* NOP *                                     | + / |

| end                                          |     |

#### 2) CHECK INSTRUCTION

As discussed, RESERVE instruction is asynchronous and no feedback is sent back to the user. In order to query the accelerator about the reservation outcome, we provide the CHECK instruction, with format CHECK <accid> <ret>.

Same as RESERVE, also CHECK causes an ACM sending where accId is used to select the target accelerator and procId is added by the IXIAM Hardware Infrastructure to identify the calling process. Moreover, coreId is added to the request to identify the core and send back the response ACM.

The accelerator that receives the CHECK ACM accesses the reservation queue and checks whether it contains procld or not. Depending on this check, the outcome can be threefold: a) it can be 0 (MISSING), if procld is not contained in the queue; b) it can be 1 (ENQUEUED), if procld is in the queue but it is not at its head; and c) it can be 2 (RESERVED), if procld is found at the head of the queue.

The outcome is written into a response ACM together with coreId and sent through the NoC. When it is received by the core identified by coreId, it is written in the ret register so it can be read by the program logic.

In Subsection II-E, we discuss user-space interrupts and the possibility to employ that mechanism to avoid synchronous instructions altogether. Listing 2 summarizes the CHECK algorithm.

| Algorithm 2 Micro-Operations of CHECK Instruc- |                                 |  |  |  |  |

|------------------------------------------------|---------------------------------|--|--|--|--|

| tion                                           |                                 |  |  |  |  |

| CHECK(accId, procId, ret);                     |                                 |  |  |  |  |

| acc = accelerators[accId];                     |                                 |  |  |  |  |

| if not acc.reservationQueue.co                 | ontains(procId) then            |  |  |  |  |

| ret = 0;                                       | /* MISSING */                   |  |  |  |  |

| else if acc.reservationqueue.he                | $ead() \neq procId$ <b>then</b> |  |  |  |  |

| ret = 1;                                       | /* ENQUEUED */                  |  |  |  |  |

| else                                           |                                 |  |  |  |  |

| ret = 2;                                       | /* RESERVED */                  |  |  |  |  |

| end                                            |                                 |  |  |  |  |

|                                                |                                 |  |  |  |  |

#### 3) TRANSFER INSTRUCTIONS

Accelerators can have various memory resources: a register file, cache memories, and one or more local memories. These can serve different purposes and be optimized for different tasks. NVIDIA GPUs' local memories are an example of such variability: *shared memory* is optimized for coalesced accesses from neighbor CUDA threads, *constant memory* is optimized to broadcast the same value to numerous threads, and *texture memory* is optimized for spatially local accesses [28], [29].

Local memories can be further grouped into *non-addressable* and *addressable* memories. While the former are managed by the accelerator transparently, e.g., to store intermediate results, the latter can be explicitly managed by the programmer. We propose five instructions to load data from/store data into *addressable* local memories or registers in a register file.

The operands of these instructions can refer to local memory locations or accelerator register files. To implement them, we adopt the *IXIAM Location Format*, exemplified in Figure 4. Bit 40 specifies whether a location indicates an address in local memory (0) or a register 1. Bits 61-63 indicate the local memory number in the accelerator: since there can be multiple local memories in each accelerator, we dedicate 3 bits to specify the one referred by the memory location – thus, we support 8 possible local memories for each accelerator. If bit 40 is set, this field is meaningless and is just ignored. Finally, bits 0-39 indicate the address in local memory, if bit 40 is 0, or the register number, if bit 40 is 1.

**FIGURE 4.** IXIAM Location Format. Bits 0-39 are dedicated to the *location*, which can be a memory address or a register number, depending on bit 40. Bits 61-63 indicate the local memory number in the accelerator.

Thus, we admit local memories with up to  $2^{40}$  bytes (1 TiB) or, equivalently, register files with  $2^{40}$  registers.

All the transfer instructions have four operands. Since the RISC-V ISA is limited to 3 operands, we choose to pass the fourth in a *convenience* register - e.g.,  $\pm 0$ .

All the transfer instructions generate a request ACM that contains a procld value read by the IXIAM Hardware Infrastructure to identify the calling process. Its role, in this case, is to let the target accelerator establish whether the transfer operation can be performed or not: the operation is performed only if the accelerator is reserved to the process identified by procld, and the request is ignored otherwise.

### a: TGL, TGS

Transfer Global Load (TGL) is used to load data from the main memory into a location in the accelerator, and Transfer Global Store (TGS) stores data from a location in the accelerator into the main memory. Thus, *load* and *store* are expressed from the accelerator point of view.

Their formats are: TGL <size, src\_cpu, dest\_ acc, accId> and TGS <size, src\_acc, dest\_ cpu, accId>. accId, the fourth operand, is read by a convenience CPU register.

size indicates the data size in bytes to load/store. dest\_acc in TGL and src\_acc in TGS are locations on the accelerator (local memory address or register) expressed in the IXIAM Location Format described above. Finally, src\_cpu in TGL and dest\_cpu in TGS are pointers to locations in the main memory.

In this proposal, we suppose the virtual-to-physical address translation is performed CPU-side. The programmer specifies a virtual address in src\_cpu or dest\_cpu operands, which is translated into a physical address phys\_addr. This is put in the request ACM that is sent to the accelerator, so it can load/store data from/to phys\_addr with DMA techniques.

It is possible that the address range involved (i.e., [phys\_addr,phys\_addr+size)) spans more than one physical memory page. If that is the case, a single TGL/TGS instruction generates multiple ACMs, each with a physical address and a partial size that refers to a piece of the buffer located in the same memory page.

At this point, a page fault can occur on the accelerator if the accessed physical page has been swapped out. In this case, the accelerator can send an interrupt to the OS that would be served by loading the page and letting the accelerator retry the memory transfer. In general, pinning the memory involved in transfers is sufficient to avoid page faults.

### b: TL

The Transfer Local (TL) instruction is used to move data between different locations on the accelerator. Its format is TL <size, src\_acc, dest\_acc, accId>, with both src\_acc and dest\_acc expressed in the IXIAM Location Format. What said about size and accId operands in TGL/TGS description applies also here. In this case, no memory translation is involved, since both locations are on the accelerator.

#### c: TRL, TRS

Transfer Register-wise Load (TRL) and Transfer Registerwise Store (TRS) are two convenient instructions to load/store data into/from the accelerator without accessing the main memory. The source in TRL and the destination in TRS are CPU registers. TRL reads a value from a CPU register and loads it into an accelerator location, while TRS reads a value from an accelerator location and stores it into a CPU register. Since TRS has an output register, it is a synchronous instruction – as such, it is committed when a response ACM is received. Thus, coreId is added to its request ACM with the usual role.

The instruction formats are TRL <size, src\_reg\_ cpu, dest\_acc, accId> and TRS <size, src\_ acc, accId> <ret>. dest\_acc and src\_acc are locations expressed in the IXIAM Location Format. Also in this case, accId is read from a convenience register in both TRL and TRS.

## 4) EXEC INSTRUCTION

The EXEC instruction permits executing an operation on the accelerator. It is intended to trigger the actual computation on the accelerator, usually manipulating data previously stored in registers and local memories.

The EXEC format is EXEC <accid, opid>. As usual, accid indicates the target accelerator. Since an accelerator can be capable of performing various operations, we dedicate the opid parameter to specify the operation to perform. As shown in the EXEC request ACM in Figure 3, 32 bits are dedicated to this value – so  $2^{32}$  possible operations can be performed. This does not limit the number of possible operations: real accelerators can take advantage of registers to let programmers specify operation parameters (e.g., start address in local memory, size, operation *mode*, etc.) and use opid as a *coarse-grained* operation identifier. In principle, all the parameters needed could be written in registers and opid remain unused. We will discuss some possibilities in Section IV.

The EXEC instruction causes a request ACM to be sent with procld parameter with the usual meaning. Same as the transfer instructions, it is used by the accelerator to check if the request is legitimate or not. If it is, the accelerator sets the status register to "busy" 1 and the intended operation can start execution. Since the operation can last for several clock cycles, EXEC has been designed as an asynchronous instruction: it is committed immediately, and the process can continue executing different instructions without waiting for operation completion. In principle, its thread of execution could even be de-scheduled by the OS while the accelerator completes its task.

When the operation completes, the accelerator updates the status register with "non-busy" (0) or an error code if the execution was not successful.

## 5) ISBUSY INSTRUCTION

The ISBUSY instruction is used to query the status of the accelerator, which is stored in the status register. Its format is: ISBUSY <accid> <ret>.

As usual, accId denotes the target accelerator. ret denotes the register where the return value, which is read from a response ACM, is written. As explained in Subsection II-B, the possible values are 0 if the accelerator is not busy, 1 if it is busy, or an error code. The error code informs of the failure of a previous transfer or EXEC instruction, which are the only ones that can fail accelerator-side.<sup>2</sup> If that is the case, the status register is cleared and set to 0.

Since ISBUSY is a synchronous instruction, its request ACM contains coreId as well as procId. In principle, the accelerator status could be communicated also to processes that do not own it. However, revealing this information could constitute a security risk, as a malevolent process could gather information about the accelerator usage of another process. For this reason, the procId value is checked and, if it does not correspond to the owning process, an error is written in the ret register or a default value (whether 0 or 1) independently of the actual accelerator status.

## 6) RELEASE INSTRUCTION

Finally, the RELEASE instruction is intended to release the accelerator when the owning process finishes using it. Its format is: RELEASE <accild>, with accild denoting the target accelerator as usual.

The instruction execution causes a request ACM sending containing the procld of the calling process. When the instruction is received, it is eliminated from the reservation queue of the accelerator. If the calling process' procld occupies the head of the queue, the accelerator is assigned to the next procld in the queue or is set *idle* if the queue is empty.

## E. IXIAM USER-SPACE INTERRUPT MECHANISM

In this subsection, we discuss our proposal for a user-space interrupt mechanism. Before presenting its details, we briefly examine instruction synchronicity.

#### 1) INSTRUCTION SYNCHRONICITY

Among the proposed instructions, summarized in Table 1, only CHECK, TRS, and ISBUSY are synchronous. These need a return value from the accelerator, which they read from a response ACM and write it into an output register in the calling process.

For CHECK and ISBUSY instructions, the accelerator should immediately manage the request and send a value independently of its activity: even if it is busy executing a long operation, CHECK and ISBUSY requests should not be enqueued and should be managed immediately. This way, their latency would be known upfront and would amount to roughly the NoC round-trip time.

Conversely, the TRS case may be more critical, as the accelerator could be occupied in a long transfer operation that may involve the target local memory, and thus it could be forced to enqueue the transfer demanded by the TRS request and perform it later. So, the latency associated to a TRS instruction cannot be known in advance, and the core executing it could remain stalled for many clock cycles in the presence of RAW dependencies.

Another instruction that, in principle, could be designed as synchronous is EXEC, with the calling process waiting for the execution completion and getting a return value that informs it of the execution outcome. However, the execution of an operation on the accelerator can take up to thousands or even millions clock cycles, depending on the accelerator, and the possibility that a RAW dependency could stall the core for so much time makes this solution unfeasible: it could cause a huge performance degradation and would even have an impact on the whole system, since the OS could not dispose of the stalled core – e.g., to schedule other processes' threads of execution. Hence, the core should be able to continue its normal operation after delivering the EXEC instruction to the accelerator and should work in parallel with accelerator computations. For this reason, we keep EXEC asynchronous and rely on the ISBUSY synchronous instruction, that has a predictable and short latency, to allow the programmer to query the execution state. The intended use of ISBUSY is thus as part of a *polling* mechanism: after executing an EXEC, the process keeps calling ISBUSY in loop until it returns 0 or an error code, sleeping for a custom time interval or doing other work in-between loop iterations. In both cases, the process keeps a core busy-waiting.

### 2) IXIAM INTERRUPT MODULE

In all the aforementioned scenarios, an interrupt-based solution could prove beneficial. Synchronous instructions could be made asynchronous by eliminating the output registers and committing the instructions immediately upon sending their associated request ACM; the return value could be retrieved in the management of an interrupt originated on the accelerator. EXEC completion could be communicated through an interrupt as well, freeing the calling process from depending on multiple ISBUSY invocations.

$<sup>^2</sup>All$  instructions can fail before being delivered if <code>accId</code> does not refer to any existing accelerator.

Although it is possible to utilize the inherent interrupt handling mechanism in the core, its significant overhead associated with context switching and Interrupt Service Routine (ISR) invocation motivate us to propose a new *lightweight* interrupt mechanism. It could be used to make synchronous instructions asynchronous and also to inform the process of execution completion. In line with our ISA extension, we design the IXIAM User-space Interrupt Mechanism to live mostly in user-space.

As anticipated in Subsection II-B, the IXIAM User-space Interrupt Mechanism requires an ad-hoc module on the SoC – in the following, the IXIAM User-space Interrupt Module. This module is necessary to gather interrupt messages from the accelerators, keep information, and deliver messages to the cores. The whole mechanism is synthetically depicted in Figure 5 and explained in the following.

In order to handle user-space interrupts, each process should select a function that acts as a User-space Interrupt Service Routine (UISR). To achieve this, we propose the Register User-space Interrupt Service Routine (RUISR) instruction, with the following format: RUISR <accid, func\_addr>, where func\_addr indicates the address of the UISR, and accid specifies the accelerator whose interrupts should be handled by that routine. Without loss of generality, a possible UISR C signature is the following:

void sample\_uisr(const uisr\_params\* params);

Where the only parameter is a pointer to a C struct containing the interrupt parameters, such as the accId where the interrupt originates, an enum to indicate the interrupt reason, and other possibly useful values to handle it. RUISR execution stores the UISR address in a convenient location of the program memory (e.g., in the Process Control Block), so it can be retrieved and invoked when a user-space interrupt occurs. It is sufficient that a process executes RUISR once for each accelerator it intends to use.

When an interrupt occurs on an accelerator, this sends a User-space Interrupt Message (UIM) to the IXIAM Userspace Interrupt Module. The module stores the interrupt information into a private table that can be indexed per accId, since at most one process at once can own an accelerator - a fixed size of 256 entries would be sufficient in our proposed implementation. This information includes the aforementioned interrupt parameters, the procld of the owning process, and a coreId. The latter refers to the core that sent the request ACM carrying the command that originated this accelerator-side interrupt. As we specified, the interrupts can be associated to make synchronous instructions asynchronous or inform the core of the execution completion event. In the first case, the request ACMs already include the id of the originating core, as shown in Figure 3. In the second, it must be added to the EXEC request ACM for this purpose.

Then, the IXIAM User-space Interrupt Module sends the UIM to the core identified by coreId and erases its entry. At this point, that core may be executing a thread associated to procId (it was the case when the request ACM was sent),

or not. In the first case, the core will handle the user-space interrupt by jumping into the stored UISR like a classic userspace function, adopting the same calling conventions dictated by the ISA. If the second case occurs, different policies can be adopted: the user-space interrupt could be elevated to a *classic* interrupt that the OS would be responsible to serve (or discard it if the owning process died), also accessing the owning process' UISR; conversely, it could be enqueued and served later.

#### **III. DISCUSSION**

In this Section, we do an in-depth discussion of some aspects that affect our proposal at various levels, as well as we introduce possible development and implementation variations of the proposed scheme.

#### A. MEMORY COHERENCY

In the proposed configuration, accelerators and processor's cores share the memory space, as they have access to the same physical memory through the on-chip LLC. Through TGL and TGS instructions, they load data buffers from the main memory and store data buffers into it, respectively. Since these buffers are located in a memory space shared with the cores, data coherence issues may arise: a datum write from the accelerator, issued with a TGS, would update the value in the LLC (and DRAM, if LLC is a write-through cache), but an older copy could be cached also in the lower levels of one or more cores' cache hierarchy - L1 and L2. If no coherence mechanism is enforced, a subsequent read performed by such a core of its local copy in the L1 would read an outdated value. The opposite is true, as a core could modify a local datum and the updated value would not be read by a subsequent TGL, unless both L1 and L2 caches adopt write-through policies or some coherence mechanism is enforced.

Core-accelerator coherence is an issue that needs to be addressed in order to have correct programs. According to state-of-the-art, accelerator coherence (or lack of) in SoCs can be addressed in four different ways [24], [30]:

- Non-Coherent;

- LLC-Coherent;

- I/O-Coherent;

- Fully-Coherent.

- **Non-Coherent** Accelerators access directly the DRAM through DMA bypassing the cores' cache hierarchy. In order to get coherent data, the processor caches must be flushed upon accelerator access, so to store updated values in the main memory. This protocol is affordable if large DMA bursts are supported, if few accelerators are connected to the system and each of them executes *long* operations i.e., at least  $1 \times$  or  $2 \times$  DRAM access time. In order to use this protocol, data read/written by the accelerator must be locked.

- **LLC-Coherent** Accelerator's memory requests are sent directly to the LLC. The accelerator is kept coherent with the LLC, but not with the private caches of the

## **IEEE**Access

(a) An interrupt occurs on accelerator n. It sends a UIM containing the interrupt information to the IXIAM User-space Interrupt Module.

(b) The module stores the interrupt information carried by the UIM at the n-th row of its user-space interrupt table.

(c) The module forwards the UIM to the mth core, which delegated to the accelerator the command that generated this user-space interrupt.

FIGURE 5. The IXIAM User-space Mechanism.

processor cores, which must be flushed before accelerator's reads and invalidated after accelerator's writes. This model is efficient only if the LLC has high hit rates.

- **I/O-Coherent** Similar to the LLC-coherent accelerator, since accelerator requests are sent directly to the LLC also in this case. The main difference is that the cache hierarchy itself maintains full hardware coherence, and the LLC is responsible for invalidating or recalling data in the lower-level caches.

- **Fully-Coherent** Accelerators are included in the coherence protocol of the processor cores, usually MESI or MOESI. This is a common choice for accelerators that have their own private caches. This protocol permits achieving data coherence transparently, but can be harmful for the system performance if the accelerator has frequent memory accesses, since it would block the bus to the cores most of the time.

In the state-of-the-art, each of these protocols are used based on the requirements and system design. Often, coherence choices are done based on the nature of the accelerator. For instance, the coherence protocol used by GPUs is entirely software-based, with this usually assuming race-free data accesses, regular data storage, and coarse-grained synchronizations [31]. Cache invalidations and flushes are performed at synchronization points. An alternative is DeNovo [31], which does not require writer-initiated invalidation, because it assumes property of written data. Conversely, readers are responsible for invalidations and are tracked by the hardware.

Putting it all together, although our proposed instructions are compatible with any coherence protocol, in this work we assume LLC-coherent accelerators. From the architectural point of view, as shown in Figure 1, all the accelerators are connected to the LLC. Before a TGL instructions that would load data into the accelerator, private L1 and L2 caches of the cores must be flushed in order to update data values at least in the LLC. If supported by the architecture, the best option would be to flush only the dirty cache lines involved. Before a TGS instruction that would store data from the accelerator into the LLC, all private copies in L1 and L2 caches must be invalidated. Again, if supported, the best option would be to invalidate only the relevant lines – i.e., do a *selective* invalidation. This means that, in the LLC-coherent case, our instructions should be integrated with proper signals addressing the caches. It could be done by invoking cacheoriented instructions before ours, if provided by the ISA, or by sending the proper signals during TGL and TGS execution.

#### **B. DATA CONSISTENCY**

Another problem that may arise from different processing elements (i.e., cores and accelerators) loading data from / storing data to a shared memory space in parallel is the difficulty to maintain *data consistency*. This issue is relevant in our proposed framework.

To illustrate it in the context of our proposal, let's consider Listing 3. The registers in the example hold the following values: t0 holds an accelerator id accId, t1 holds a pointer to the main memory cpu\_ptr, t2 holds a location in the accelerator's local memory expressed in IXIAM Location Format acc\_ptr, t3 holds a buffer size in bytes size, and t4 can hold any value. Therefore, the first instruction instructs the accelerator to store size bytes of data from the location acc\_ptr to the main memory, at address cpu\_ptr. The following instruction loads 64-bit from cpu\_ptr into the register t4. So, it is a classic Read-After-Write (RAW) dependency: the LD instruction loads a value from a memory location that should have been just written by the previous TGS instruction – thus, it should read an *updated* value.

| Algorithm 3 Sample Code Causing Memory Con-<br>tention                                                       |

|--------------------------------------------------------------------------------------------------------------|

| <pre>/* t0=accId, t1=cpu_ptr,<br/>t2=acc_ptr, t3=size, t4=any */<br/>TGS t3, t2, t1;<br/>LD t4, 0(t1);</pre> |

TGS, as previously specified, is committed immediately on the core side as soon as the request ACM is sent. It is possible that, while the following load instruction LD enters the pipeline stages to be fetched, decoded, and executed, the data transfer is not complete, or did not even start if the request ACM has not reached the accelerator yet. Even worse, in principle, if the processor implements *Out-of-Order* (OoO) execution, the LD instruction may be executed *even before* the TGS instruction. In both cases, it is possible that LD reads an outdated value and the correctness of the program is not guaranteed.

This is a very well-known and studied problem. Various solutions have been proposed during the years to address it, since its emergence that dates back to the diffusion of multi-tasking execution [32], [33].

Commonly, the processes use semaphores to access shared memory in a mutually exclusive manner [34]. They disallow shared data swapping and allow the OS kernel to avoid the internal page locking code. In this regard, some levels of concurrency control is applied to maintain data integrity in the shared memory.

Atomic Read-Modify-Write (RMW) instructions used in different ISAs, e.g., x86, IBM Power, ARMv8, and RISC-V are another solution to synchronize operations [35]. They are used either directly by programmers or OS libraries to provide higher-abstraction synchronization mechanisms. Locks, barriers, and other constructs are utilized to establish mutual exclusion among threads of parallel applications in those synchronization mechanisms [36]. The atomic RMWs in current Intel x86 processors serialize all outstanding load and store operations, and block subsequent memory operations until their commit [37]. Through the use of memory fences, i.e., fetch-and-increment, test-andset, and compare-and-swap, this serialization can be easily implemented [38], [39].

Another way to guarantee consistency is Load Linked/-Store Conditional (LL/SC) pairs [40]. LL/SC are pairs of instructions that can be used to implement, in software, the same atomic operations as RMWs. Unlike the latter, however, LL and SC are distinct instructions, usually used to surround another operation. Thus, the whole primitive can be interrupted, e.g., by a context switch in-between. Moreover, an LL/SC pair will fail due to relevant external events such as coherence invalidations and cache evictions [35].

Another option are memory arbitration mechanisms, which have been proposed to decrease the impact of memory contention in contexts with multiple cores [32], [41]. This arbitration mechanism have been presented by the PREM execution model [42], [43], BWLOCK [44], and MEMGUARD [45].

In the rather common case of a CPU paired with an integrated GPU, both computing elements have access to the same physical memory – so, a reliable synchronization and memory consistency support is needed [31]. Two main memory consistency models widely used in GPUs are *Data-Race-Free* (DRF) [31], [46] and *Heterogeneous-Race-Free* (HRF) [47]. Common implementations of DRF and HRF enforce a program order requirement. DRF ensures sequential consistency to datarace-free programs, while HRF is defined similarly to DRF to handle scoped (i.e., a hardware-inspired mechanism that exposes the memory hierarchy to the programmer) synchronization problem of DFR. Each synchronization access has a scope attribute in the proposed HRF [31], [48]. Although HRF is a very well-defined

model, it cannot hide the inherent complexity of using scopes.

The CUDA programming language for NVIDIA GPUs defines two memory fences, \_\_threadfence and \_\_threadfence\_block, to enforce consistency between loads and stores [29], [49]. VectorPU expands CUDA with C++ functions that act as access specifiers for buffers [50]. This protocol realizes automatic creation of on-demand copies of to-be accessed elements in device memory, with all the copies kept coherent and data transfers performed only when needed. Global Memory for Accelerators (GMAC) [51] expands CUDA as well with device-independent allocation/deallocation primitives that enforce coherence.

Some works are based on data-containers, sometimes also referred to as *smart* containers: objects to perform coherent software caching of accessed elements in the different memory spaces [52], [53]. Therefore, they can be reused in order to avoid unnecessary data transfers, which are usually transferred lazily when needed.

As manually managing data to ensure programmers to have a consistent program state between the CPU and GPU memories is tedious and error-prone, some semi-automatic techniques have been proposed. These techniques are usually annotation-based, with programmers specifying the access modes of buffers in memory [52].

There are also completely automatic solutions to manage data and optimize communication. Some examples are Inspector-Executor (IE) [54], CPU-GPU Communication Management (CGCM) [55], and DyManD, an automatic system to manage complex and recursive data-structures without static analyses [56].

In general, relying on an explicit use of ad-hoc fences is the most straightforward solution to address consistency issues. In its most basic version, it puts the burden on the application programmer, but it could be easily wrapped in library constructs or be integrated in (semi-)automatic techniques.

In this work, we define our fence and show how to use it explicitly. We leave an in-depth analysis of alternative, more sophisticated techniques to future work.

We propose an ad-hoc fence instruction: Accelerator FENCE (AFENCE). We take inspiration from the simple RISC-V FENCE instruction, which blocks all the subsequent loads and stores. Its format is AFENCE <accid>, where accid identifies the target accelerator. Also in this case, procid is added to the associated request ACM with the usual role: to check if the process executing the instruction is the same as the owning process, so to ignore the request if that is not the case.

The AFENCE instruction should be selectively inserted in the code flow to enforce consistency. It should be placed between a read instruction and a write instruction involving overlapping memory locations. Listing 4 shows the three RAW hazards solved by using AFENCE this way, with the first one being the example from Listing 3 *corrected* with the fence.

| Algorithm 4 Three Possible Core-Accelerator RAW |

|-------------------------------------------------|

| Hazards Solved With AFENCE Instruction          |

| /* t0=accId, t1=cpu_ptr,      |    |

|-------------------------------|----|

| t2=acc_ptr, t3=size, t4=dummy | */ |

| /* acc->core                  | */ |

| TGS t3, t2, t1;               |    |

| AFENCE t0;                    |    |

| LD t4, 0(t1);                 |    |

| /* core->acc                  | */ |

| SD t4, 0(t1);                 |    |

| AFENCE t0;                    |    |

| TGL t3, t1, t2;               |    |

| /* acc->acc                   | */ |

| TGS t3, t2, t1;               |    |

| AFENCE t0;                    |    |

| TGL t3, t1, t2;               |    |

|                               |    |

We implement AFENCE as a synchronous instruction. It drains the Load-Store Queue (LSQ), and prevents any subsequent load or store instruction from surpassing it, being it core-oriented (e.g., LD, SD) or accelerator-oriented (e.g., TGS, TGL). It causes a request ACM to be sent to the accelerator and instruct it to do the same with its flying loads and stores: wait for their completion and prevent any subsequent memory operation to surpass the AFENCE. When these are complete, the accelerator sends the response ACM to the core to instruct it to commit the AFENCE and proceed. Should the accelerator be controlled by a single in-order instruction queue, the implementation of its logic would be trivial. It would be sufficient that the response ACM is sent when the AFENCE is popped from the head of the instruction queue. Moreover, in that case, the third RAW issue depicted in Listing 4 would not need any fences and would be solved by design.

#### C. WATCHDOG

It is possible that a process does not release the accelerator after the demanded job is completed. This can happen for various reasons: a code bug, malicious behaviour, the process died before executing the release instruction, etc. To prevent this scenario, we design a hardware *watchdog* mechanism that keeps track of the accelerator utilization.

The watchdog lays in the accelerator interface logic circuitry and interacts with it: when an accelerator completes an EXEC operation, the watchdog's stopwatch starts. If a RELEASE request is not received after a configurable number of clock cycles, the watchdog releases the accelerator automatically. The same mechanism can be applied for any request sent to the accelerator that is not followed, within a *reasonable* and configurable time-span, by a request that would come in a normal utilization flow. An example is a RELEASE that would normally be followed by a CHECK.

## D. OS-BASED ARBITRATION

Our instruction extension is designed so all instructions can be executed from user-space, with the minimum privilege level. Tasks that would normally require higher privilege levels (e.g., reservation management), usually delegated to the OS, are implemented in hardware. This way, we are reducing the latency associated to many operations, as we will show in the next section.

These functionalities implemented in hardware, despite taking advantage of a reduced latency, necessarily require a higher chip area to host the transistors to implement them. Moreover, the flexibility that can be adopted in a hardwarebased solution is generally significantly lower than that achievable in software.

Focusing on reservation queues and their management logic, the hardware reservation mechanism allows users to leverage accelerators with no OS intervention, pushing their requests in hardware queues that will extract them with a FIFO policy. Although this solution could be sufficient for various real use cases, it could be too limiting for others. For instance, in heavily virtualized environments, a finer grain distinction between what users (and their processes) can do or cannot do would certainly be needed. Configurable access policies based on subscription options could be needed as well, even preventing some accelerators from user-space programs altogether. Thus, a more strict control from the OS, despite not being the solution with the lowest latency, may be needed.

We could achieve this by elevating RESERVE and RELEASE instructions at kernel privilege level. This way, user processes would rely on apposite system calls to ask for an accelerator reservation/release, and the system call execution in kernel-space would implement custom logic to allow/prevent reservation/release and execute the highprivilege RESERVE/RELEASE instructions as part of its code.

Apart from allowing a finer-grained access control, this solution would simplify the management of other relevant scenarios. First, watchdog logic could be delegated to the OS, that could force release of inactive processes, or even monitor (and limit) the accelerator usage after a configurable time interval. Any scheduling policy could be implemented by the OS - e.g., round robin or priority-based scheduling. In the round robin case, the preemption implementation would require the OS to release the accelerator from the owning process, reserve it for itself, save its state to convenient locations, restore the state of the next process (if present), release the accelerator, and reserve it for the newly-scheduled process. The backed-up state would be restored the next time the preempted process is scheduled. This is doable by adding to the high-privilege instructions an explicit procld operand, which is a safe choice because it would be limited to kernel-space code.

One of the advantages of relying on user-space instructions is that the code would work also in virtual environments

#### TABLE 2. System configuration details.

| CPU             | Quad-core, 3.4GHz, RISC-V                      |

|-----------------|------------------------------------------------|

| L1 I/D Cache    | 32KB, 8-way, write-back, 64B block size, non-  |

|                 | blocking, 2-cycles access time, private        |

| L2 Cache        | 512KB, 8-way, write-back, 64B block size, non- |

|                 | blocking, 10-cycles access time, private       |

| L3 Cache        | 8MB, 16-way, write-back, 64B block size, non-  |

|                 | blocking, 36-cycles access time, shared        |

| Interconnection | ring-based, 15-cycles average latency          |

| Main Memory     | DRAM-DDR3, 2GB, 300-cycles access time         |

with no substantial modifications. Elevating RESERVE and RELEASE privilege level would not change the virtualization-friendliness of the proposal, as it would require only a proper extension of the hypervisor to take care of the system calls associated to them. This hypervisor modification would allow an implementation of the subscription policies mentioned above, and would be possible with a limited effort from kernel programmers.

#### **IV. EXPERIMENTAL RESULTS**

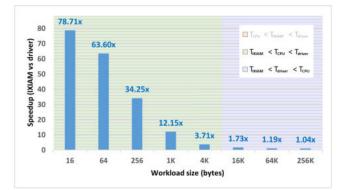

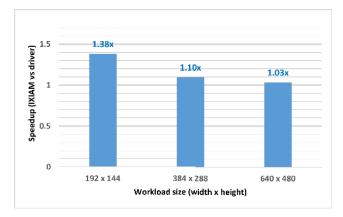

In order to assess the value of our proposed interfacing for a variety of accelerators, we implement five different accelerators that meet the constraints expressed in Section II and pertain to different domains:

MatMul accelerates matrix-matrix multiplication;

**Crypto** accelerates data encryption/decryption;

**DisparityMap** accelerates disparity map calculation;

FFT accelerates Fast Fourier Transform;

CNN accelerates Convolutional Neural Network computation.

We model them as part of a simulated SoC in the gem5 simulator v21.2.1 [22]. The SoC includes a quad-core RISC-V processor, three levels of on-chip caches, and a dedicated NoC to connect the cores to the accelerators. We enrich the SoC with the additions dictated by the IXIAM Hardware Infrastructure, the IXIAM User-space Interrupt Module, and all the logic necessary to execute the proposed instructions and the user-space interrupt mechanism. The accelerators are connected to the L3 cache to access the main memory. The details of the system configuration are depicted in Table 2.

For each accelerator, we implement a benchmark in which the accelerator performs one offloaded operation. We execute each benchmark with two different interfacing and compare the obtained performance. In one case, we adopt our proposal, in the other, we use a conventional driver-based solution.

### A. SIMULATED ACCELERATORS

We select five accelerators from different domains and with different characteristics, so to show the flexibility of our approach in terms of the variety of accelerators supported.

Table 3 lists the CPU-side and accelerator-side latencies associated to the fetch and decode of each instruction. Accelerators receive these commands in request ACMs together with their parameters, through the interconnect. The latencies

| TABLE 3. Latencies associated to the proposed instructions. L <sub>CPU</sub> is the |

|-------------------------------------------------------------------------------------|

| number of CPU cycles needed to fetch and decode instructions on the                 |

| CPU. Lacc is the number of accelerator cycles needed to fetch and decode            |

| commands on the accelerator.                                                        |

| Command | $L_{\rm CPU}$ | $L_{\rm acc}$ | Command | $L_{\rm CPU}$ | $L_{\rm acc}$ |

|---------|---------------|---------------|---------|---------------|---------------|

| RESERVE | 2             | 3             | TRS     | 2             | 1             |

| CHECK   | 2             | 3             | EXEC    | 2             | 1             |

| TGL     | 2             | 1             | BUSY    | 2             | 1             |

| TGS     | 2             | 1             | RELEASE | 2             | 3             |

| TL      | 2             | 1             | AFENCE  | 2             | 1             |

| TRL     | 2             | 1             |         |               |               |

in the table are expressed with respect to their clock cycles and are the same for all the simulated accelerators.

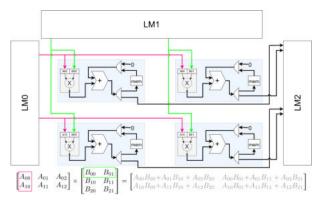

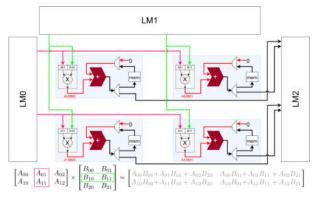

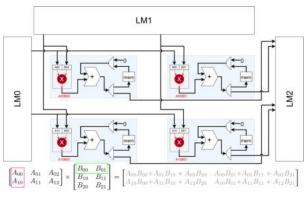

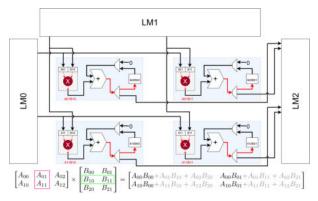

1) MatMul

We design a Matrix Multiplication accelerator, *MatMul* in this paper, that calculates the matrix  $C \in \mathbb{R}^{M \times P}$  as the product of matrices  $A \in \mathbb{R}^{M \times N}$  and  $B \in \mathbb{R}^{N \times P}$ , according to Eq. 1.

$$C_{ij} = \sum_{k=1}^{N} A_{ik} \cdot B_{kj}$$

for  $i = 1, \dots, M; j = 1, \dots, P$  (1)

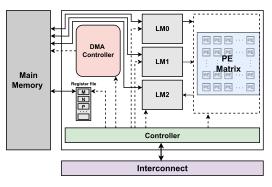

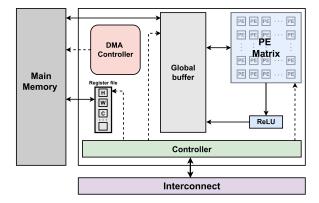

Figure 6 shows the block diagram of the MatMul accelerator. Each element is represented as an IEEE-754 single precision floating-point value. It has three local memories to hold the three matrices: LM0, LM1, and LM2 for matrices A, B, and C, respectively. Its register file has three 32-bit registers to hold matrix dimensions M, N, and P.

The accelerator performs the matrix-matrix multiplication by multiplying fixed-side tiles together. Its computing core is a matrix of Processing Elements (PEs), each one capable of performing one tile-tile multiplication and one tile-tile addition. An internal controller fetches tiles from the input matrices, multiply them together, and stores the resulting tile into LM2 until all the output matrix has been covered.

We assume each PE is equivalent to an NVIDIA Tensor Core, and can perform a multiplication between two  $4 \times 4$  tiles in one clock cycle [57]. Analyzing the die-shot of an NVIDIA TU102 chip [58], considering it features 72 Streaming Multiprocessors (SMs), each with 8 Tensor Cores [28], and considering the whole die area is 754 mm<sup>2</sup> [59], we calculate that each SM occupies around 1.98 mm<sup>2</sup> (0.263% of the total area), and thus each Tensor Core occupies at most 0.25 mm<sup>2</sup>. We assume PEs in our MatMul accelerator have this size.

We design an accelerator with a 7 mm<sup>2</sup> die area, similar to a Kirin 990 5G NPU [60]. It has three 1 MiB local memories, that take 0.46 mm<sup>2</sup> with a 12 nm technology node (i.e., the same as the Tensor Core), as we estimate with CACTI [61]. This way, the MatMul accelerator can host up to 16 PEs arranged in a  $4 \times 4$  matrix, as they would occupy 4 mm<sup>2</sup> and leave 2.54 mm<sup>2</sup> (36.28%) for the remaining *uncore* logic.

The fetching logic can fetch up to 4 tiles from A, each one broadcasting to a PE row, and 4 from B, each one broadcasting to a PE column.

FIGURE 6. Block diagram of the MatMul accelerator.

Figure 7 shows the steps performed by the accelerator. For simplicity, we show a  $2 \times 2$  PE matrix. Five distinct phases can be identified as follows:

- **Fetch (F)** 4 tiles from matrix *A* are fetched from LM0 and broadcasted to each row of PEs. At the same time, 4 tiles from matrix *B* are fetched from LM1 and broadcasted to each column of PEs.

- Multiply (M) in each PE, the two tiles are multiplied together.

- Add (A) in each PE, the result tile extracted from the multiplication is added to an all-zero block at the first iteration, and to the partial result of the PE in the following iterations.

- Accumulate (Ac) in each PE, the result tile extracted from the addition is stored in an accumulator large enough to hold one tile.

- **Store (S)** in each PE, when the last tile from a row in A and the last tile from a column in B are multiplied together and added to the partial result in the accumulator, the resulting C's tile is available and is stored to LM2.

As depicted in Figure 7, some phases are independent and can be safely overlapped in a pipeline. Considering the matrices A, B, and C in the figure, the resulting pipeline will be as follows:

S

In order to operate the accelerator with our proposed interface, the programmer needs to write the matrix dimensions in the registers (TRL instructions), the matrix data in the local memories (TGL instructions), and trigger the matrix multiplication operation (EXEC instruction). The accelerator's controller will take care of performing all the steps needed to multiply the matrices together in the tiling fashion expressed above and write the resulting matrix C to LM2. When done, the programmer can read C from LM2 and copy it into the main memory (TGS instruction).

Table 4 summarizes the accelerator configuration parameters.

#### TABLE 4. Configuration parameters of the MatMul accelerator.

| Frequency   | $1.0  \mathrm{GHz}$ | LM0 size    | 1 MiB   |

|-------------|---------------------|-------------|---------|

| Add latency | 1 cycle             | LM1 size    | 1  MiB  |

| Mul latency | 1 cycle             | LM2 size    | 1  MiB  |

| PEs         | $4 \times 4$        | LMs latency | 1 cycle |

| tile dims   | $4 \times 4$        | -           | -       |

#### 2) CRYPTO

Cryptography accelerator, which is called *Crypto* in this paper, encrypts/decrypts a given message using NIST Advanced Encryption Standard (AES) cipher [62]. The AES algorithm involves dividing the input into 16-byte blocks, represented as  $4 \times 4$  byte matrices called *state* and applying the encryption/decryption algorithm to each block separately. According to the standard, there are three key lengths that can be used: 128, 192, and 256 bits [62]. Commonly, the algorithm is denoted as AES128, AES192, or AES256 depending on the key-length.

The classic AES algorithm requires the execution of the same sequence of operations for each *round*, with the number of rounds being 10, 12, or 14, according to the key length being 128, 192, or 256 bits, respectively. Since each round needs its own key, the initial key is expanded into an array of keys through the so-called *KeyExpansion* phase.

Then, for the encryption algorithm, the rounds are performed as fixed sequences of operations involving byte substitution (*SubBytes*), byte permutation (*ShiftRows, Mix-Columns*), and byte-key XORring (*AddRoundKey*). The decryption algorithm is similar, but the *plain* operations are replaced with their inverses. In both cases, the final round does not comprise *MixColumns* nor its inverse operation.

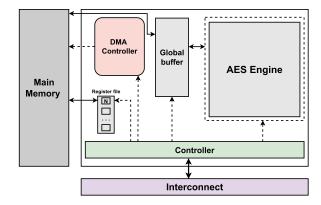

The accelerator implementation is based on the AES Engine IP core by Xilinx [63], which provides some variants of AES128, AES192, and AES256 ciphers. In our design, shown in Figure 8, we add a controller, a DMA controller, a small register file, and a global buffer alongside the AES Engine. These components are used to communicate with the AES Engine and orchestrate the cipher execution on it.

The global buffer is used to store both input (i.e., message and initial key) and output data locally. The input is retrieved from the main memory and the output is stored in the main memory, with the DMA controller managing the transfers. The register file provides three registers to store data addresses in the global buffer (i.e., message, initial key, and output) and one to store the message length. The controller is in charge of interpreting commands received as request ACMs from the interconnect and execute the necessary operations related to them. It also orchestrates execution on the AES engine by providing message blocks in a streaming fashion, taking advantage of the pipelining capabilities of the AES Engine [63].

In order to use the accelerator, a programmer needs to load the message length into the *size* local register (TRL instruction), the initial key into the global buffer (TGL instruction),

(a) Fetch tiles from matrices A in LM0 and B in LM1. Tiles from LM0 are broadcasted to all the PEs in a row, while tiles from LM1 are broadcasted to all PEs in a column.

(c) Add the partial results together, picking an all-zeros tile at the first iteration and the partial result at the following iterations. Fetch the next tiles from both LM0 and LM1

#### FIGURE 7. Highlight of a MatMul accelerator with a 2 × 2 PE matrix and its functioning.

#### TABLE 5. Configuration parameters of the Crypto accelerator.

| Frequency         | 250  MHz  | Global buffer size    | 2 MiB    |

|-------------------|-----------|-----------------------|----------|

| Encr AES128 block | 12 cycles | Global buffer latency | 2 cycles |

| Decr AES128 block | 22 cycles |                       |          |

and the message into the global buffer (TGL instruction). Then, execution can be triggered (EXEC instruction) and, when it completes, the result can be retrieved by reading from the global buffer (TGS instruction).

Table 5 summarizes the accelerator configuration parameters.

#### 3) DisparityMap

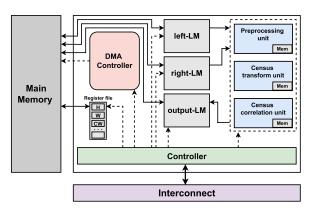

A disparity map accelerator is used to compute the disparity map of two stereo images (i.e., left image and right image). Given a stereo image pair, a disparity map can be used to reconstruct depth information about the scene represented in the two images.

We simulate the disparity map accelerator described by Ibarra-Manzano et al. in [64], where the authors discuss an FPGA-based implementation. They use an algorithm based on the correlation of census transforms [65] of input images.

(b) Multiply the tiles together.

(d) Store the partial result in the PE's memory and multiply the previously fetched tiles together. At the last iteration, this step will be replaced with a store in LM2.

FIGURE 8. Block diagram of the Crypto accelerator.

Initially, through arithmetic mean filter, input images are smoothed to remove acquisition noise (*Image preprocessing*). This process is carried out using a  $3 \times 3$  pixels window. In the next step, filtered images are processed by the census transform unit, producing images in which each pixel is represented as a binary string that encodes intensity with respect to neighbor pixels (*Census transformation*). In this case, a  $7 \times 7$  window is used. Finally, census transforms are

FIGURE 9. Block diagram of the Disparity accelerator.

TABLE 6. Configuration parameters of the DisparityMap accelerator.

| Frequency                | $1.0 \mathrm{GHz}$ | left-LM size  | 2 MiB    |

|--------------------------|--------------------|---------------|----------|

| $192 \times 144$ latency | 34500  cycles      | right-LM size | 2  MiB   |

| 384×288 latency          | 138000 cycles      | out-LM size   | 2  MiB   |

| $640 \times 480$ latency | 384000  cycles     | LMs latency   | 3 cycles |

used as input of census correlation unit, that is able to find disparity measures (*Census correlation*). The maximal disparity measure selected is 64. Each algorithm step is implemented as a separate module in the accelerator.

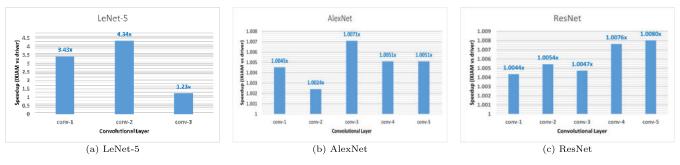

The implemented accelerator has three 2 MiB local memories used to store input left image (left-LM), input right image (right-LM), and processing output (out-LM). In addition, each module is equipped with memories used to save temporary values during computation transparently. The total amount of these memories is 104 Kib.