# Control Method, Circuit Topology, and Power Architecture for High-performance AC-DC Converters

## Huan Li

Supervisor: Weidong Xiao Associate Supervisor: Jianguo Zhu

A thesis submitted in fulfilment of the requirements for the degree of Doctor of Philosophy

School of Electrical and Information Engineering

Faculty of Engineering

The University of Sydney

Australia

14 March 2023

## **Originality Statement**

This is to certify that to the best of my knowledge, the content of this thesis is my own work. This thesis has not been submitted for any degree or other purposes.

I certify that the intellectual content of this thesis is the product of my own work and that all the assistance received in preparing this thesis and sources have been acknowledged.

14/03/2023

## **Authorship Attribution Statement**

In addition to the statements above, in cases where I am not the corresponding author of a published item, permission to include the published material has been granted by the corresponding author.

14/03/2023

As the supervisor for the candidature upon which this thesis is based, I can confirm that the authorship attribution statements above are correct.

14/03/2023

#### **Abstract**

This thesis explores new approaches, including a new control method, a new power factor correction (PFC) front-end topology, and two power architectures to improve the performance of AC–DC power converters.

- Control method: A modulation and control method for an active-clamp flyback (ACF) converter is developed. It is first found that the internal clamping capacitor in the ACF converter can be used as an active buffer without any modifications on topology, by adopting the proposed modulation method. The clamping capacitor of the ACF converter can tolerate a much greater voltage swing than the buffer capacitor in a two-stage architecture, allowing for a single-stage adapter design with reduced capacitance requirements. A 100-W universal-input laboratory prototype is built, which achieves 94 % peak efficiency and up to 10x size reduction of the buffer capacitor.

- Circuit topology: A new topology for the PFC front end is developed, which enables simultaneous size reduction of both the inductor and the buffer capacitor by achieving zero-voltage-switching (ZVS) of all switches and active power buffering. An apple-to-apple experimental comparison is made between a typical critical-mode boost PFC and the proposed PFC front end. The prototype achieves a 47 % size reduction of the magnetics, a 21 % size reduction of the buffer capacitor, and an almost constant DC-link voltage while maintaining comparable efficiency performance.

- Power architecture ①: A stacked-switch PFC architecture is developed. The stacked-switch architecture allows all switches to achieve full-load-range ZVS at a universal input and under a constant switching frequency, which has not yet been demonstrated in any PFC applications before. This valuable property is achieved by simply removing the high-frequency diode in the two-stage architecture. Hence, higher power density can be achieved via high-frequency operations while requiring lower costs as the total component counts are

ABSTRACT V

reduced. A 150-W universal-input prototype is built, which measures 92.9 % peak efficiency and 53.9 W/in<sup>3</sup> power density by box volume.

• Power architecture ②: A star PFC architecture is developed. It is first discovered that the current ripple in the second stage of a two-stage architecture can be used to 1) reduce the current ripple of the first boost PFC stage and to 2) assist full-range ZVS of the first PFC stage under a constant switching frequency. The star architecture thereby enables higher efficiency and smaller magnetics in the boost PFC front end while maintaining the performance of the second DC–DC stage, leading to a high-power-density and high-efficiency AC–DC converter. A 300-kHz, 240-W, 48-V-output, and universal input prototype is built, showcasing a high power factor, constant output voltage, 97.1 % full-load efficiency, and 55.6 W/in³ power density by box volume. The star architecture is experimentally verified to achieve a 40 % loss reduction given the same power density compared to the two-stage architecture.

### Acknowledgements

First, I want to thank my supervisor Prof. Weidong Xiao for his support. I found power electronics interesting and developed a strong passion for building hardware over the past five years, which would not be possible without his carefully prepared lectures and rigorous attitude toward teaching. He always opens his mind to my naive ideas and patiently corrects my understanding, which motivates me to think independently and develop my taste. Building hardware is never easy and sometimes heartbreaking, especially when watching your carefully designed circuits catch fire again and again. Without Prof. Xiao's encouragement and support, I can't imagine overcoming all the failures. I also learned a lot from his can-do attitude, which helped me stay positive against any challenges in life.

I would like to thank Dr. Sinan Li for sharing his experience in active power buffering with me and giving me many insightful suggestions to improve my work. I appreciate the help from Ms. Yuezhu Lu, from whom I learned many hands-on skills. I am also grateful to Dr. Ruihong Chu, who helped me a lot with components and equipment since I was a master's student. Many thanks to Dr. Samir Gautam, Mr. Rasedul Hasan, Dr. Waqas Hassan, Ms. Yechen Zhu, Dr. Bowen Wang, Dr. John Long Soon, Prof. Dylan Lu, Ms. Wanrong Li, Ms. Shuang Jiao, Mr. Lei Wang, Mr. Jinghang Li, Mr. Fujian Li, Prof. Jin Ma, Dr. Yuechuan Tao, Dr. Shuying Lai, Mr. Yuan Ma, Mr. Hongjie Zhang, Mr. Qiyang Lei, Dr. Yikai Yang, Dr. Nhan Duy Truong, and Dr. C. M. F. S. Reza for helping me along my Ph.D. journey.

Finally, I want to express my sincerest gratitude to my parents and my girlfriend, Yuqi Pan, for their accompany and encouragement during my study.

## **Contents**

| Originality  | Statement                                                     | ii  |

|--------------|---------------------------------------------------------------|-----|

| Authorship   | Attribution Statement                                         | iii |

| Abstract     |                                                               | iv  |

| Acknowled    | gements                                                       | vi  |

| Contents     |                                                               | vii |

| List of Figu | ires                                                          | X   |

| Chapter 1    | Introduction                                                  | 1   |

| Chapter 2    | A Modulation Method for Capacitance Reduction in Active-clamp |     |

|              | Flyback Converter                                             | 5   |

| 2.1 Bac      | kground                                                       | 5   |

| 2.2 Top      | ology and Operating Principle                                 | 7   |

| 2.2.1        | Conventional Operating Method                                 | 8   |

| 2.2.2        | Proposed Operation                                            | 11  |

| 2.3 Mod      | dulation and Control Method                                   | 11  |

| 2.3.1        | Dual On-time Modulation                                       | 13  |

| 2.3.2        | Control Circuit Implementation                                | 15  |

| 2.4 Des      | ign Consideration                                             | 17  |

| 2.4.1        | Design of Winding Turns Ratio n                               | 17  |

| 2.4.2        | Design of $v_b$ and $C_b$                                     | 18  |

| 2.4.3        | Design of $L_m$ and $L$                                       | 19  |

| 2.4.4        | Concept Design                                                | 20  |

| 2.5 Exp      | erimental Results and Evaluation                              | 21  |

viii Contents

|      | 2.5.1  | Verification                                        | 21         |

|------|--------|-----------------------------------------------------|------------|

|      | 2.5.2  | Comparison                                          | 27         |

| 2.6  | Sun    | nmary                                               | 32         |

|      | _      |                                                     |            |

| •    | oter 3 | ·                                                   | 33         |

| 3.1  | Bac    | ekground                                            | 33         |

| 3.2  | 2 Top  | ology and Operating Principle                       | 36         |

|      | 3.2.1  | Development of the Proposed Topology                | 36         |

|      | 3.2.2  | Operating Principle                                 | 37         |

|      | 3.2.3  | Circuit Analysis                                    | 40         |

|      | 3.2.4  | Impact of $L_b$ on Power Density                    | 42         |

|      | 3.2.5  | Comparison of Electrical Energy Storage             | 43         |

| 3.3  | Des    | sign Considerations                                 | 45         |

|      | 3.3.1  | Effects of Parasitic Capacitance and $D_2$          | 45         |

|      | 3.3.2  | Design of $C_b$                                     | 46         |

|      | 3.3.3  | Design of $L_a$ and $L_b$                           | 48         |

|      | 3.3.4  | Design of $C_{in}$                                  | 48         |

|      | 3.3.5  | ZVS Range Analysis                                  | 49         |

|      | 3.3.6  | Control Circuit                                     | 54         |

|      | 3.3.7  | Common-mode Noise Reduction                         | 57         |

| 3.4  | Exp    | perimental Verification                             | 58         |

| 3.5  | Sun    | nmary                                               | 71         |

|      |        |                                                     |            |

| Chap | ter 4  | Stacked-switch Power Factor Correction Architecture | <b>7</b> 3 |

| 4.1  | Bac    | ekground                                            | 73         |

| 4.2  | . Sta  | cked-switch PFC Architecture                        | 75         |

|      | 4.2.1  | Operating Principle                                 | 75         |

|      | 4.2.2  | Switching Sequence and ZVS Realization              |            |

|      | 4.2.3  | Comparison to Existing Single-stage PFC Solutions   |            |

| 4.3  |        | sign Considerations                                 |            |

|      |        | Modulation and Control                              | 83         |

| ix |

|----|

|    |

| 4.3.2     | Clamping State and Design of $C_{in}$                            |

|-----------|------------------------------------------------------------------|

| 4.3.3     | B Design of $L$                                                  |

| 4.3.4     | Design of $L_m$                                                  |

| 4.3.5     | Design of Magnetics                                              |

| 4.3.6     | 6 Case Study                                                     |

| 4.4 Ex    | perimental Results                                               |

| 4.5 Su    | mmary                                                            |

| Chapter 5 | Star Power Factor Correction Architecture 107                    |

| 5.1 Ba    | ckground                                                         |

| 5.2 Op    | perating Principle of Star Architecture                          |

| 5.2.1     | Examples of Star PFC Operations                                  |

| 5.2.2     | 2 ZVS Realizations                                               |

| 5.3 Co    | emparison Between Star Architecture and Two-stage Architecture   |

| 5.3.1     | Comparison of Power Loss                                         |

| 5.3.2     | Comparison of Current Stress on $C_b$                            |

| 5.4 Co    | ontrol Circuit                                                   |

| 5.5 De    | sign                                                             |

| 5.5.1     | Design of The Isolated Stage                                     |

| 5.5.2     | Design of The PFC Stage                                          |

| 5.6 Ve    | rification                                                       |

| 5.7 Su    | mmary                                                            |

| Chapter 6 | Conclusion 139                                                   |

| 1 App     | endix                                                            |

| 1.1       | Derivations of $f_{sw}$                                          |

| 1.2       | Derivations of $i_{L.min}$                                       |

| 1.3       | Maximum Magnetic Energy Storage in Buck and Boost Converters 141 |

| Appendix  | Bibliography 144                                                 |

## **List of Figures**

| 1.1  | Two-stage PFC architecture.                                                                           | 1  |

|------|-------------------------------------------------------------------------------------------------------|----|

| 2.1  | Architectures of adapters: (A) two-stage architecture typically used when high                        |    |

|      | power factor is required (B) single-stage architecture.                                               | 6  |

| 2.2  | The topology of ACF converter.                                                                        | 7  |

| 2.3  | Operating states. (A) State I: $[T_o-T_1]$ . (B) State II: $[T_1-T_2]$ . (C) State III: $[T_2-T_3]$ . |    |

|      | (D) State IV: $[T_3-T_4]$ . (E) State V: $[T_4-T_5]$ . (F) State VI: $[T_5-T_6]$ .                    | 8  |

| 2.4  | Operating waveforms.                                                                                  | 9  |

| 2.5  | Charging and discharging phases of $C_b$ : (A) power flows of input power $p_{in}$ and                |    |

|      | output power $p_o$ (B) charging phase (C) discharging phase.                                          | 12 |

| 2.6  | (A) Proposed control architecture for the single-stage ACF PFC converter. (B)                         |    |

|      | Conventional control architecture for the single-stage ACF PFC converter [14].                        | 14 |

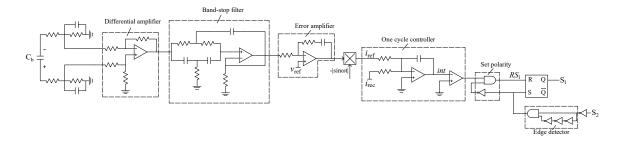

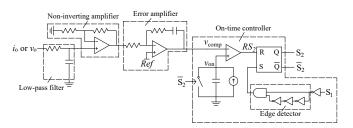

| 2.7  | Analog circuit implementation of the ac-port power loop.                                              | 15 |

| 2.8  | Analog circuit implementation of the dc-port power loop.                                              | 15 |

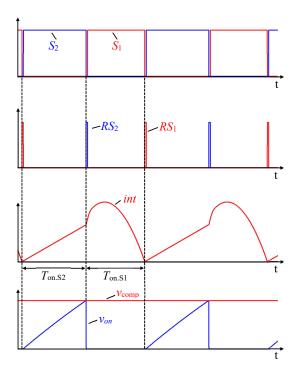

| 2.9  | Detailed signals of the proposed control circuits.                                                    | 16 |

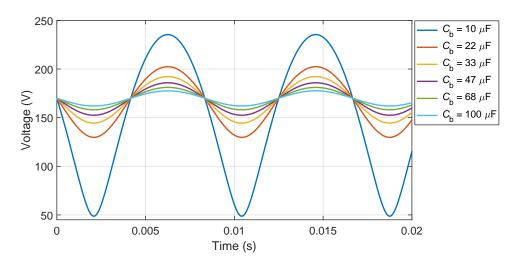

| 2.10 | Effects of $C_b$ on $v_b$ . $p_o = 100 \text{ W}$ and $V_b = 170 \text{ V}$ .                         | 19 |

| 2.11 | Equivalent resonant circuit during the ZVS of $S_1$ and $S_2$ . (A) $i_L$ is discharging the          |    |

|      | output capacitance of $S_1$ . (B) $i_L$ is discharging the output capacitance of $S_2$ .              | 20 |

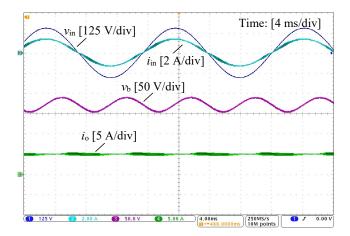

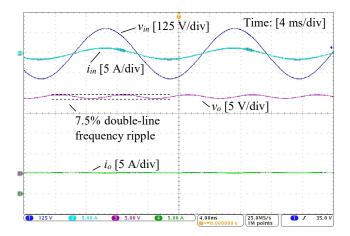

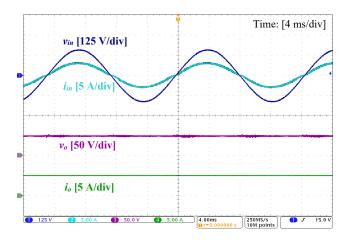

| 2.12 | Operating waveforms of $v_{in}$ , $i_{in}$ , $v_b$ , and $i_o$ at 110 V AC.                           | 22 |

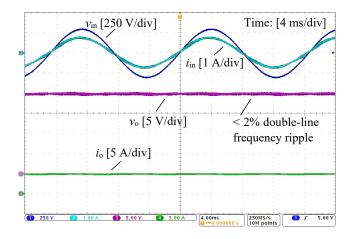

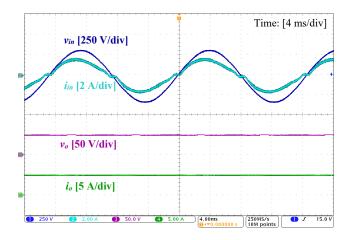

| 2.13 | Operating waveforms of $v_{in}$ , $i_{in}$ , $v_o$ , and $i_o$ at 230 V AC.                           | 22 |

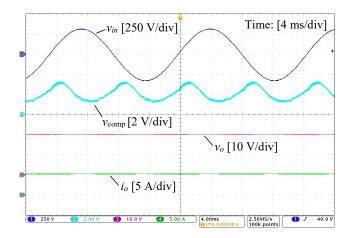

| 2.14 | Operating waveform of $v_{in}$ , $v_{comp}$ , $v_o$ , and $i_o$ under 230 V AC                        | 23 |

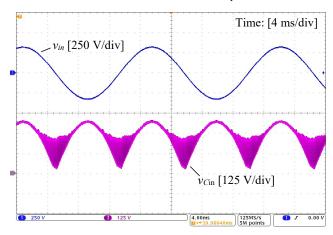

| 2.15 | Operating waveform of $v_{in}$ and $v_{C_{in}}$ under 230 V AC                                        | 23 |

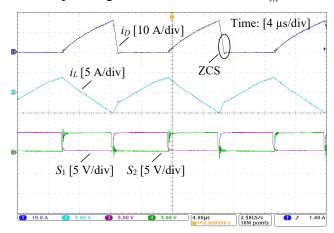

| 2.16 | Operating waveform of $i_D$ , $i_L$ , logic signal to $S_1$ , and logic signal to $S_2$ under 110     |    |

|      | V AC                                                                                                  | 23 |

| 2.17 | Operating waveform of $i_D$ , $i_L$ , logic signal to $S_1$ , and logic signal to $S_2$ under 230     |    |

|      | V AC                                                                                                  | 24 |

|      | LIST OF FIGURES                                                                                     | xi |

|------|-----------------------------------------------------------------------------------------------------|----|

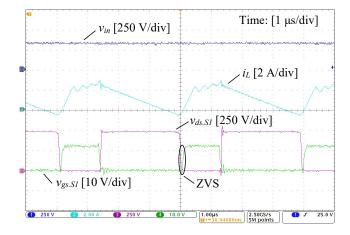

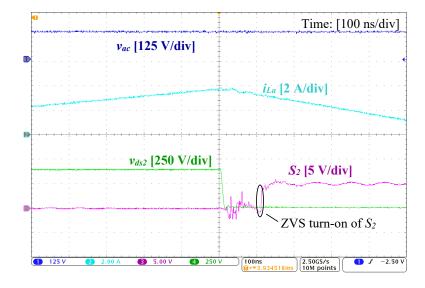

| 2.18 | ZVS waveforms of $S_1$ under 110 V AC.                                                              | 24 |

| 2.19 | ZVS waveforms of $S_1$ under 230 V AC.                                                              | 25 |

| 2.20 | ZVS waveforms of $S_2$ under 110 V AC.                                                              | 25 |

| 2.21 | ZVS waveforms of $S_2$ under 230 V AC.                                                              | 25 |

| 2.22 | Transient waveforms with a load change from 100 W to 50 W.                                          | 26 |

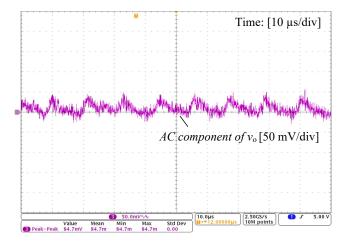

| 2.23 | Plot to check the peak-to-peak ripple of $v_o$ .                                                    | 26 |

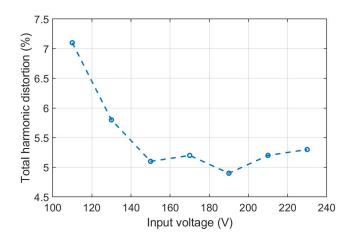

| 2.24 | Total harmonic distortion of $i_{in}$ versus input voltage.                                         | 27 |

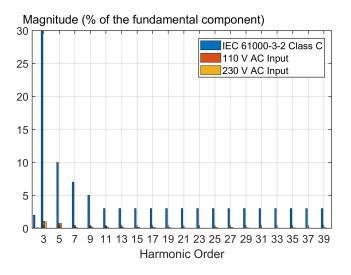

| 2.25 | Harmonic spectrum of the prototype.                                                                 | 27 |

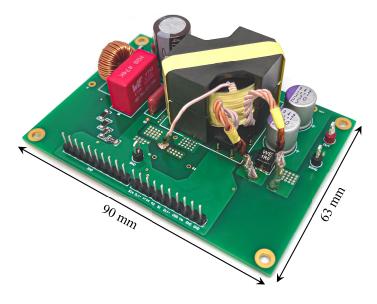

| 2.26 | Hardware implementation. Dimensions: $90 \times 63 \times 26 \text{ mm}^3$ .                        | 28 |

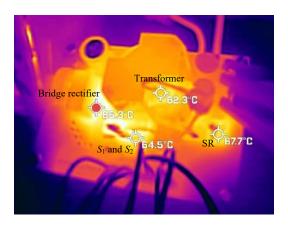

| 2.27 | Thermal image under the steady-state condition of 110 V AC input, 20 V / 5 A                        |    |

|      | output, and 23 °C room temperature.                                                                 | 28 |

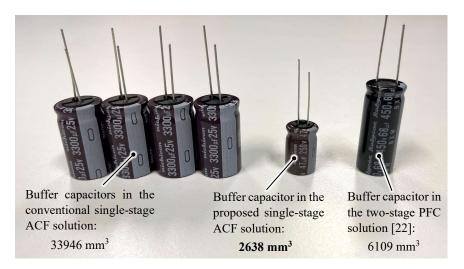

| 2.28 | Comparison of buffer capacitors between the conventional single-stage ACF                           |    |

|      | solution, the proposed solution, and the two-stage solution. Left: buffer capacitor                 |    |

|      | used in the 100 W conventional single-stage ACF solution. Middle: buffer                            |    |

|      | capacitor used in the proposed single-stage ACF solution. Right: buffer capacitor                   |    |

|      | used in a typical 100 W two-stage solution[27].                                                     | 29 |

| 2.29 | Steady state waveforms of the conventional single-stage ACF solution ( $C_o = 13860$                |    |

|      | $\mu$ F, $C_b = 470 \text{ nF}$ ).                                                                  | 30 |

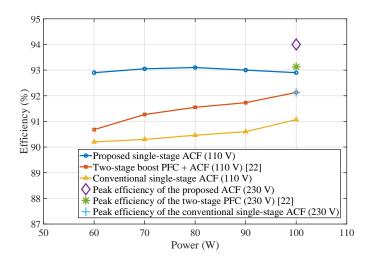

| 2.30 | Efficiency curves.                                                                                  | 30 |

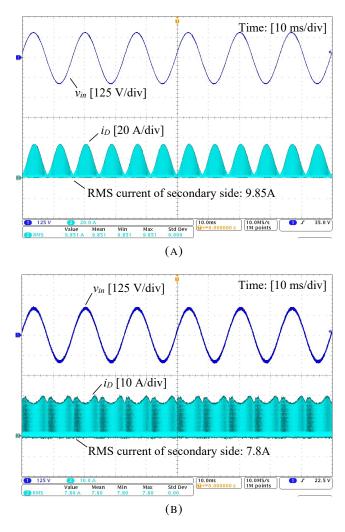

| 2.31 | $i_{D}$ in (A) the conventional single-stage ACF solution and (B) the proposed                      |    |

|      | single-stage ACF solution.                                                                          | 31 |

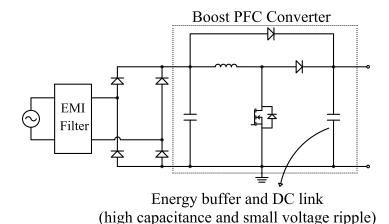

| 3.1  | Conventional boost-based PFC front end                                                              | 34 |

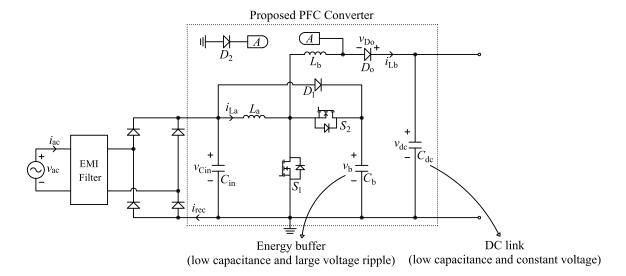

| 3.2  | Proposed topology for PFC front end.                                                                | 36 |

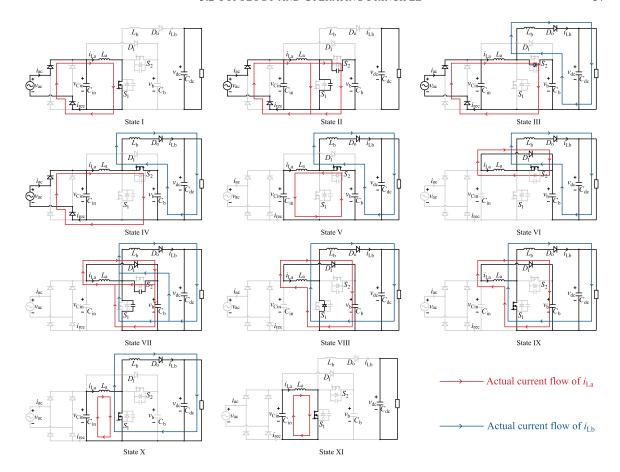

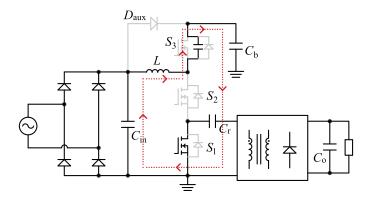

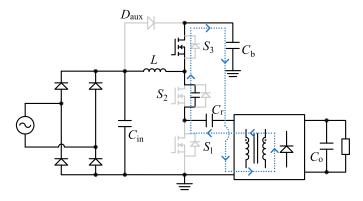

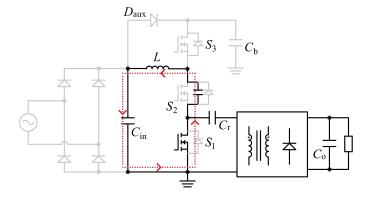

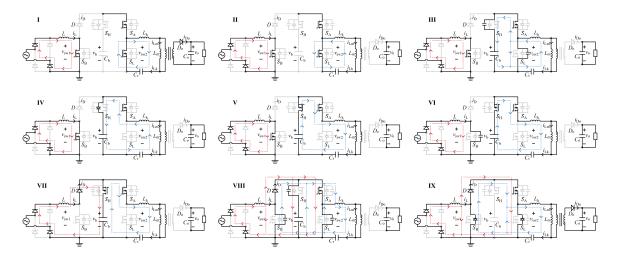

| 3.3  | Operating states of the proposed converter.                                                         | 37 |

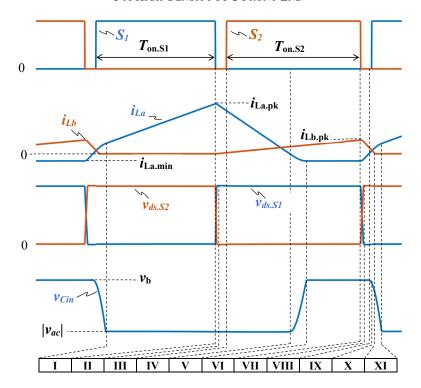

| 3.4  | Detailed waveforms of the proposed converter. $v_{ds.S1}$ and $v_{ds.S2}$ are the drain-source      |    |

|      | voltage of $S_1$ and $S_2$ .                                                                        | 38 |

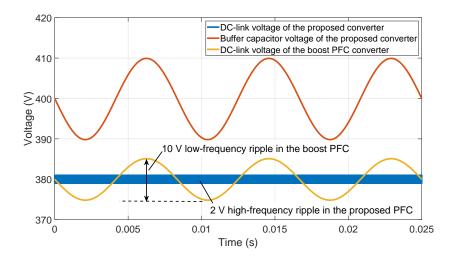

| 3.5  | Waveforms of DC-link voltage in the proposed converter and the conventional                         |    |

|      | boost PFC converter ( $C_b$ = 33 $\mu$ F, $C_b^*$ = 68 $\mu$ F). The proposed converter can achieve |    |

|      | a lower DC-link voltage ripple than the conventional boost PFC converter while                      |    |

|      | requiring lower capacitance.                                                                        | 45 |

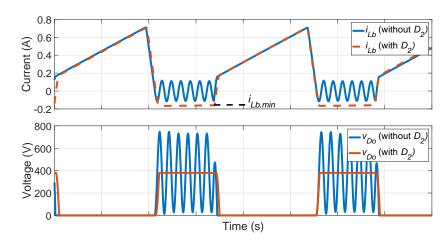

| 3.6  | Operating waveforms with and without $D_2$ considering 10 pF parasitic capacitance              |    |

|------|-------------------------------------------------------------------------------------------------|----|

|      | of $Do$ .                                                                                       | 46 |

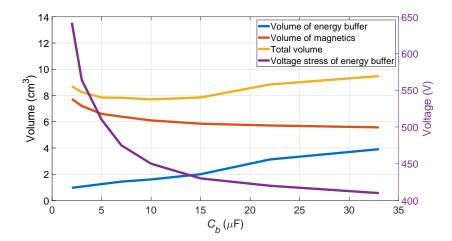

| 3.7  | Volume of magnetics and energy buffer versus $C_b$ for a 100-W prototype. Lower                 |    |

|      | $C_b$ leads to higher voltage stress, smaller energy buffer, and bigger magnetics. The          |    |

|      | volume of the energy buffer capacitor is calculated based on existing electrolytic              |    |

|      | capacitors from Rubycon. The volume of magnetics is calculated assuming 0.065                   |    |

|      | $\mu$ J/mm $^3$ energy density and 400 kHz switching frequency.                                 | 47 |

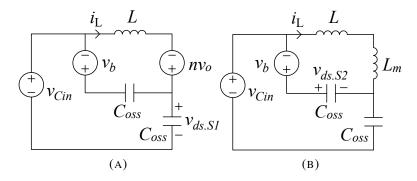

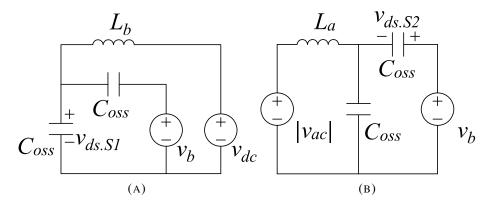

| 3.8  | Approximate resonant circuit during the ZVS transition of $S_1$ and $S_2$ . (A) $i_{Lb}$ is     |    |

|      | discharging the output capacitance of $S_1$ while charging the output capacitance of            |    |

|      | $S_2$ . (B) $i_{La}$ is discharging the output capacitance of $S_2$ while charging the output   |    |

|      | capacitance of $S_1$ .                                                                          | 50 |

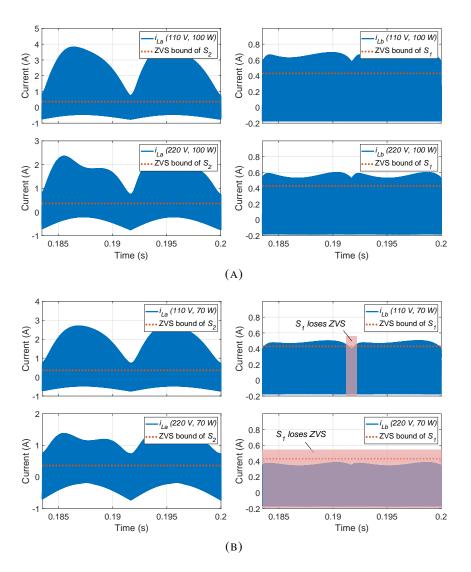

| 3.9  | ZVS range under different AC voltages and power levels. The regions where                       |    |

|      | ZVS is lost are highlighted in red. $L_a$ is 50 $\mu$ H and $L_b$ is 100 $\mu$ H. (A) Simulated |    |

|      | waveforms of $i_{La}$ and $i_{Lb}$ under 110 V and 220 V inputs at 100 W. ZVS of switches       |    |

|      | can be achieved as $i_{La.pk}$ and $i_{Lb.pk}$ are higher than the ZVS boundaries plotted       |    |

|      | in dashed lines. (B) Simulated waveforms of $i_{La}$ and $i_{Lb}$ under 110 V and 220 V         |    |

|      | inputs at 70 W. The ZVS of $S_1$ is lost when $i_{Lb.pk}$ is lower than the ZVS boundary        |    |

|      | of $S_1$ .                                                                                      | 51 |

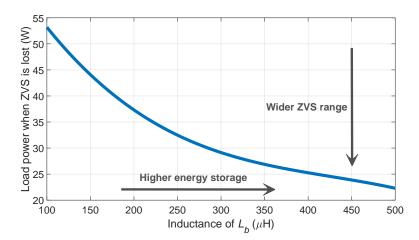

| 3.10 | The relationship between $L_b$ and ZVS range. The figure is plotted using the same              |    |

|      | specifications and circuit parameters as in Table. 3.1 and 3.2.                                 | 52 |

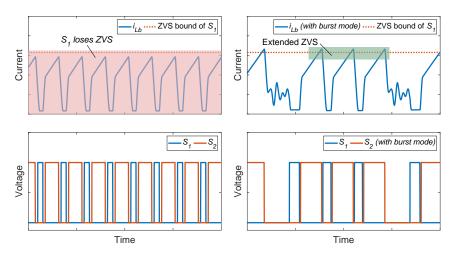

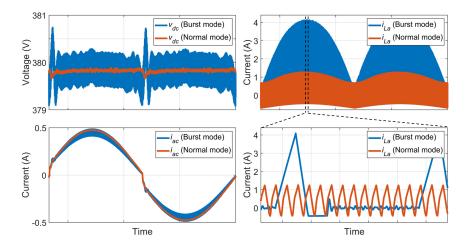

| 3.11 | ZVS extension through the burst-mode operations. Left: simulated waveforms                      |    |

|      | under the normal-mode operations. Right: simulated waveforms under the                          |    |

|      | burst-mode operations. Both cases are measured at 220-V AC input and 70-W                       |    |

|      | output, and the circuit parameters are the same as the hardware prototype in the                |    |

|      | experimental section.                                                                           | 52 |

| 3.12 | Comparison of waveforms between the normal-mode operations and burst-mode                       |    |

|      | operations (30 W output, 110 V AC). The parameters used to simulate the                         |    |

|      | waveforms are the same as the hardware prototype in the experimental section.                   |    |

|      | The average switching frequency is reduced after using the burst mode operations.               |    |

|      |                                                                                                 |    |

|                 | •••  |

|-----------------|------|

| LIST OF FIGURES | V111 |

| LIST OF FIGURES | XIII |

|      | Higher ripple occurs as a trade-off for lower switching frequency and the                              |    |

|------|--------------------------------------------------------------------------------------------------------|----|

|      | corresponding switching-related losses.                                                                | 53 |

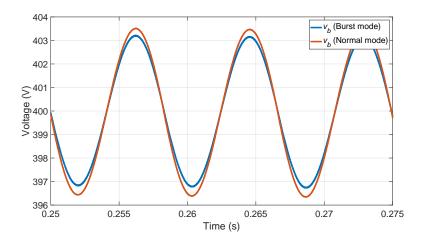

| 3.13 | Comparison of $v_b$ between the burst-mode operations and normal-mode operations                       |    |

|      | (30 W output, 110 V AC). The ripple of $v_b$ under burst-mode operations is lower                      |    |

|      | than that under normal-mode operations because the burst-mode operations                               |    |

|      | improve efficiency and reduce the 120 Hz ripple power.                                                 | 53 |

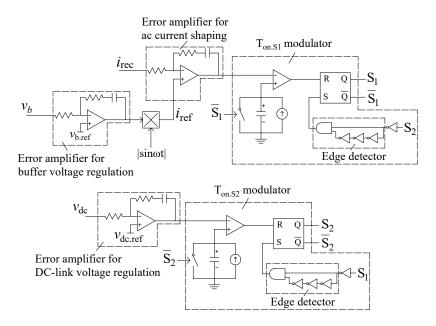

| 3.14 | Implementation of the control circuit.                                                                 | 54 |

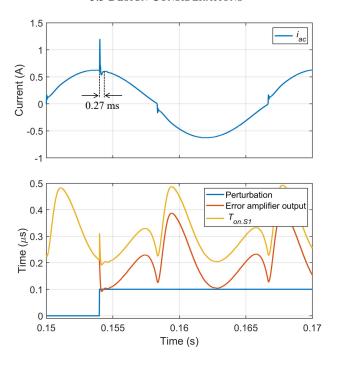

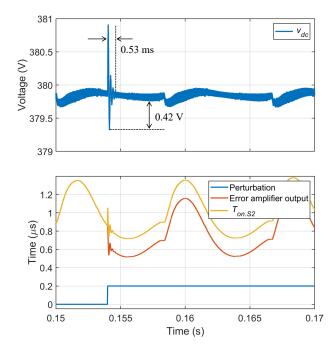

| 3.15 | The effects of 100 ns perturbation of $T_{on.S1}$ on $i_{ac}$ .                                        | 55 |

| 3.16 | The effects of 200 ns perturbation of $T_{on.S2}$ on $v_{dc}$ .                                        | 55 |

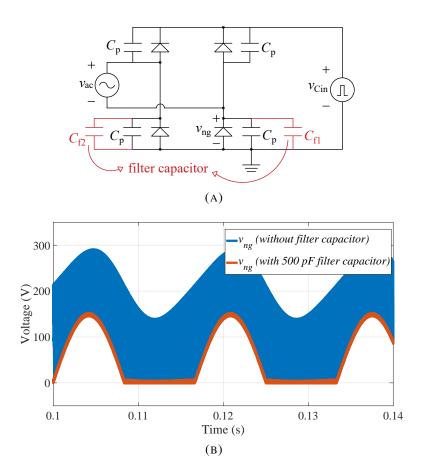

| 3.17 | (A) Proposed filtering method to reduce the common-mode noise. $C_p$ is the                            |    |

|      | junction capacitance of the diodes. $C_{f1}$ and $C_{f2}$ are the added filter capacitors. (B)         |    |

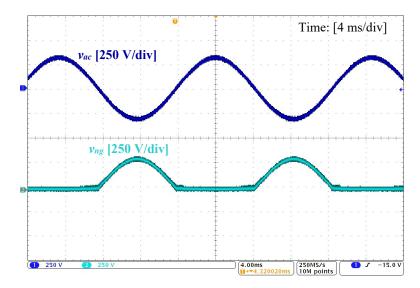

|      | $v_{ng}$ before and after adding the filter capacitors.                                                | 57 |

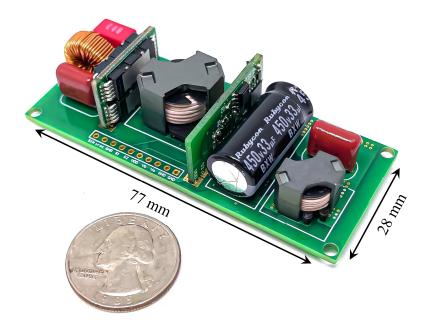

| 3.18 | Photo of the 100 W-rated prototype measured as $77 \times 28 \times 15 \text{ mm}^3$ .                 | 59 |

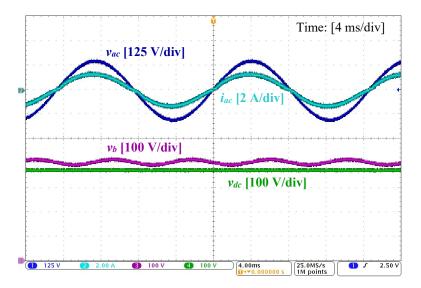

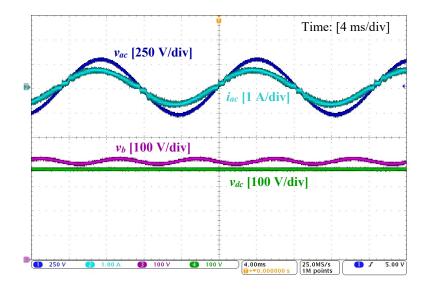

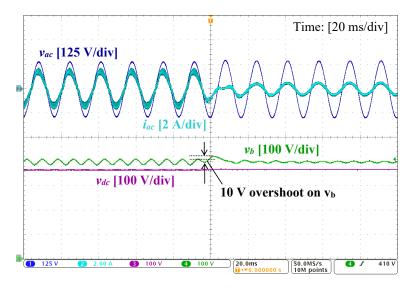

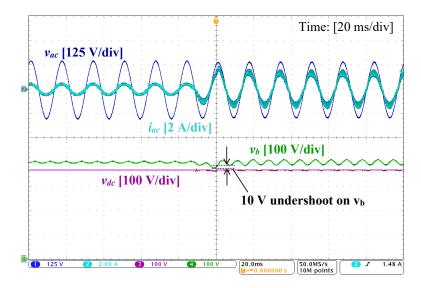

| 3.19 | Waveforms of $v_{ac}$ , $i_{ac}$ , $v_b$ , and $v_{dc}$ at 110 V AC.                                   | 60 |

| 3.20 | Waveforms of $v_{ac}$ , $i_{ac}$ , $v_b$ , and $v_{dc}$ at 220 V AC.                                   | 60 |

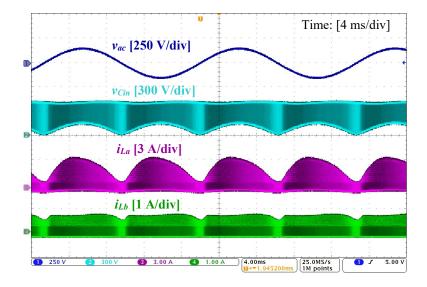

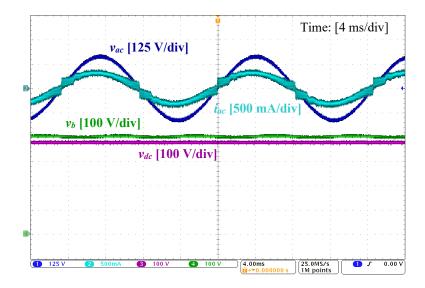

| 3.21 | Waveforms of $v_{ac}$ , $v_{Cin}$ , $i_{La}$ , and $i_{Lb}$ at 110 V AC.                               | 61 |

| 3.22 | Waveforms of $v_{ac}$ , $v_{Cin}$ , $i_{La}$ , and $i_{Lb}$ at 220 V AC.                               | 61 |

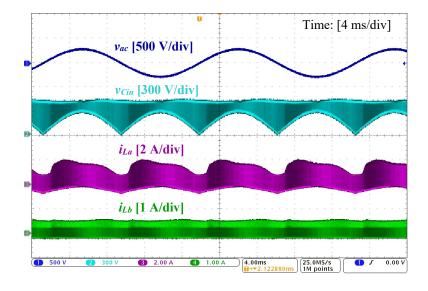

| 3.23 | Detailed waveforms of $v_{ac}$ , $v_{Cin}$ , $i_{La}$ , and $i_{Lb}$ at 220 V AC.                      | 62 |

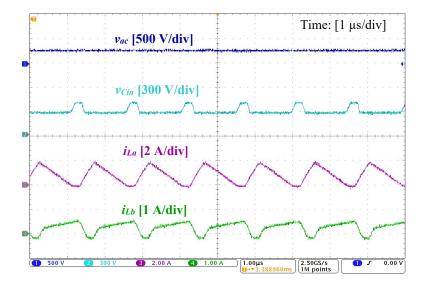

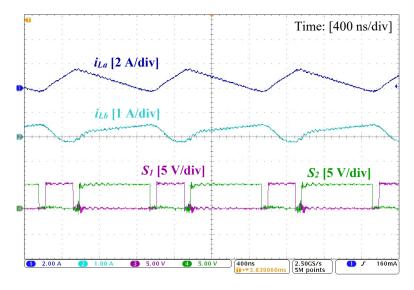

| 3.24 | Detailed waveforms of $i_{La}$ , $i_{Lb}$ , logic signal to $S_1$ , and logic signal to $S_2$ at 220 V |    |

|      | AC.                                                                                                    | 62 |

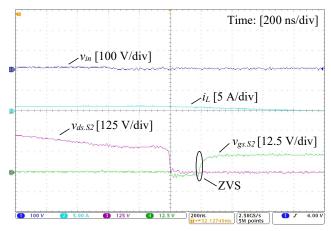

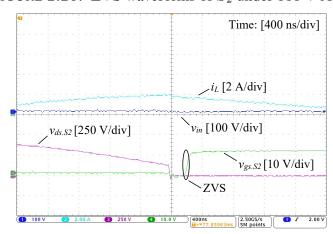

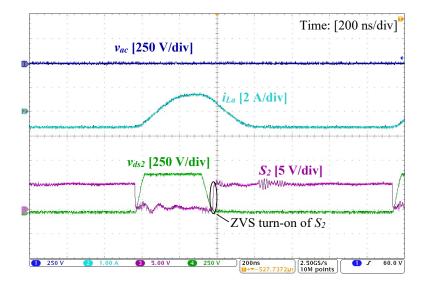

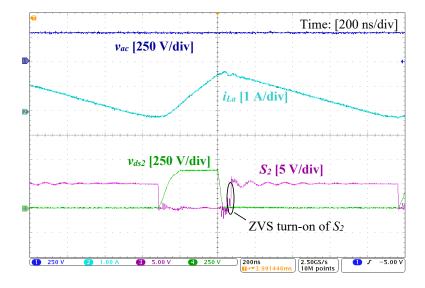

| 3.25 | ZVS waveforms of $S_2$ at the zero-crossing of $v_{ac}$ (220 V AC).                                    | 63 |

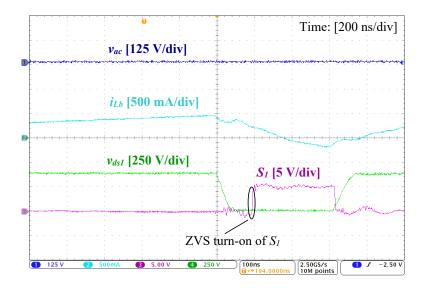

| 3.26 | ZVS waveforms of $S_1$ at the peak of $v_{ac}$ (220 V AC).                                             | 63 |

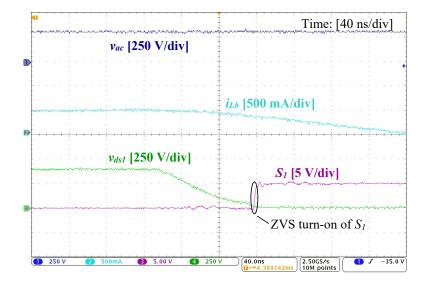

| 3.27 | ZVS waveforms of $S_1$ at the zero-crossing of $v_{ac}$ (220 V AC).                                    | 64 |

| 3.28 | ZVS waveforms of $S_2$ at the peak of $v_{ac}$ (220 V AC).                                             | 64 |

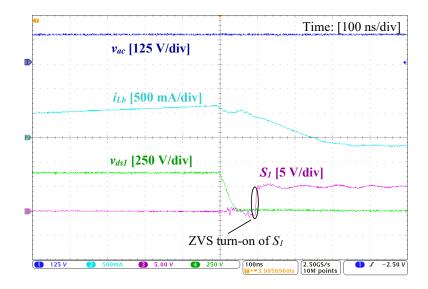

| 3.29 | ZVS waveforms of $S_1$ at the zero-crossing of $v_{ac}$ (110 V AC).                                    | 65 |

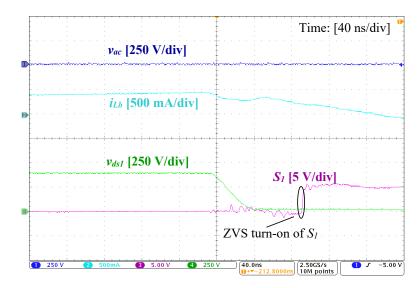

| 3.30 | ZVS waveforms of $S_1$ at the peak of $v_{ac}$ (110 V AC).                                             | 65 |

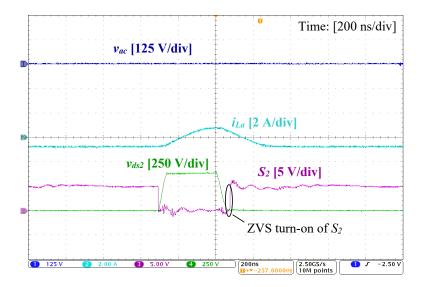

| 3.31 | ZVS waveforms of $S_2$ at the zero-crossing of $v_{ac}$ (110 V AC).                                    | 66 |

| 3.32 | ZVS waveforms of $S_2$ at the peak of $v_{ac}$ (110 V AC).                                             | 66 |

| 3.33 | The voltage potential between the circuit ground and neutral.                                          | 67 |

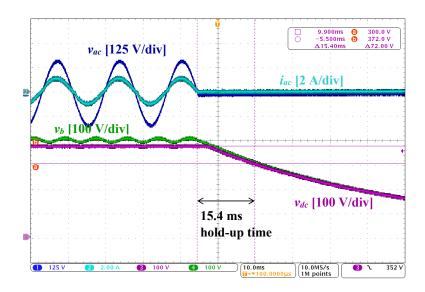

| 3.34 | Waveforms of a shutdown process.                                                                       | 67 |

|      |                                                                                                        |    |

xiv List of Figures

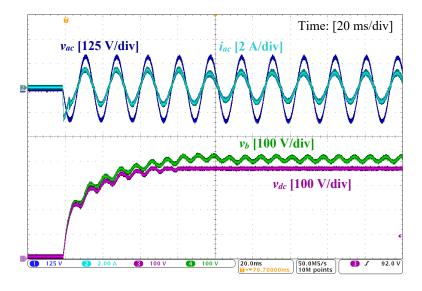

| 3.35 | Waveforms of a startup process.                                                           | 68 |

|------|-------------------------------------------------------------------------------------------|----|

| 3.36 | Waveforms of a load step-down process from 100 % to 20 % load power.                      | 68 |

| 3.37 | Waveforms of a load step-up process from 20 % to 100 % load power.                        | 69 |

| 3.38 | Waveforms of $v_{ac}$ , $i_{ac}$ , $v_b$ , and $v_{dc}$ at 20 W output.                   | 69 |

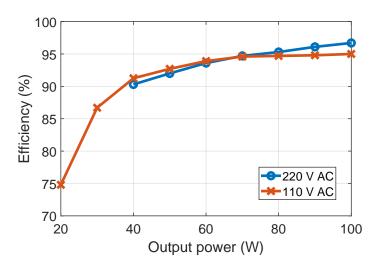

| 3.39 | Efficiency curves of the prototype.                                                       | 70 |

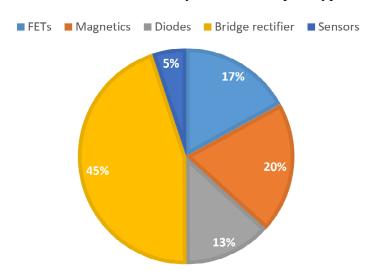

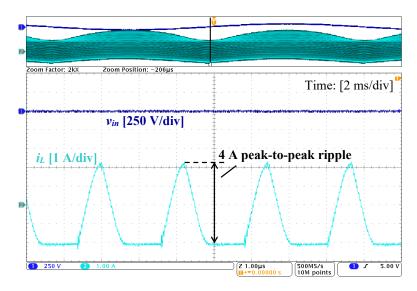

| 3.40 | Loss breakdown under full-load output and 110 V AC input.                                 | 70 |

| 3.41 | Loss breakdown under full-load output and 220 V AC input.                                 | 71 |

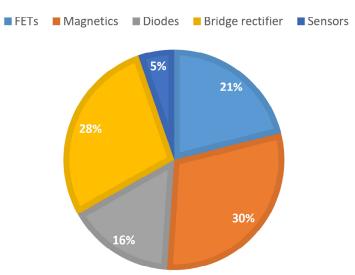

| 3.42 | Measured power factor and total harmonic distortion under high-line and low-line          |    |

|      | conditions.                                                                               | 71 |

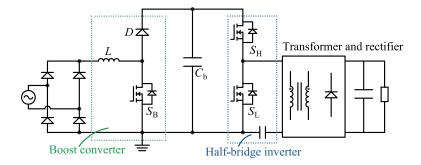

| 4.1  | Two-stage PFC architecture.                                                               | 74 |

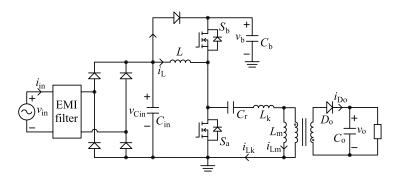

| 4.2  | Stacked-switch PFC architecture.                                                          | 75 |

| 4.3  | Operating principle of the stacked-switch PFC architecture.                               | 76 |

| 4.4  | Two possible switching sequences in Configuration I of stacked-switch PFC                 |    |

|      | architecture.                                                                             | 76 |

| 4.5  | ZVS transition from State I to State II. $S_1$ 's output capacitance is discharged by     |    |

|      | the transformer current highlighted in blue. The charging/discharging effects of          |    |

|      | $i_L$ on the output capacitance of $S_1$ is negligible because $L$ is designed to work at |    |

|      | discontinuous-conduction mode (DCM) in this thesis.                                       | 80 |

| 4.6  | ZVS transition from State II to State III. $S_3$ 's output capacitance is discharged by   |    |

|      | the boost inductor current highlighted in red.                                            | 80 |

| 4.7  | ZVS transition from State III to State I. $S_2$ 's output capacitance is discharged by    |    |

|      | the transformer current highlighted in blue.                                              | 80 |

| 4.8  | ZVS transition from State III to State II. $S_2$ 's output capacitance is discharged by   |    |

|      | the boost inductor current highlighted in red. Complicated digital calculations and       |    |

|      | high-speed current sensing are required to precisely regulate the negative current of     |    |

|      | $i_L$ to guarantee ZVS without incurring excessive circulating power.                     | 81 |

| 4.9  | A single-stage PFC converter based on integration of boost and flyback converters         |    |

|      | [64].                                                                                     | 83 |

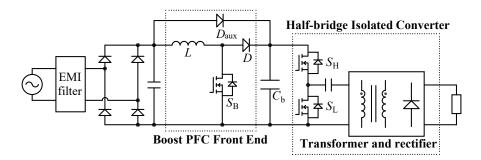

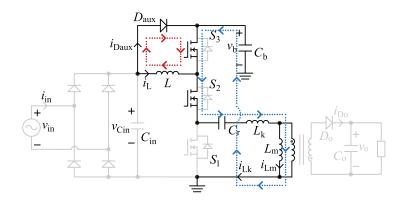

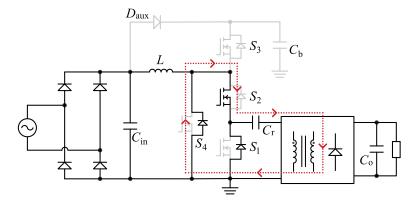

| 4.10 | Schematic diagram of an implementation of the stacked-switch PFC architecture,            |    |

|      | where the asymmetrical half-bridge flyback converter is adopted as the isolated           |    |

LIST OF FIGURES

|      | LIST OF FIGURES                                                                                     | XV |

|------|-----------------------------------------------------------------------------------------------------|----|

|      | DC-DC stage and Configuration I is used. A synchronous rectifier is used to                         |    |

|      | implement the secondary diode $D_o$ .                                                               | 83 |

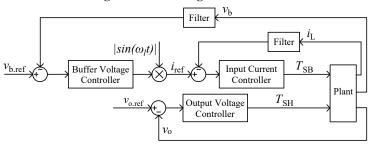

| 4.11 | Control block diagrams for the two-stage PFC architecture and the stacked-switch                    |    |

|      | PFC architecture. $T_{SB}$ and $T_{SH}$ refer to the on-time of $S_B$ and $S_H$ , respectively.     |    |

|      | $T_{S1\&S2}$ refers to the time duration when both $S_1$ and $S_2$ are turned on. $T_{S2\&S3}$      |    |

|      | refers to the time duration when both $S_2$ and $S_3$ are turned on. $\omega_l$ is the angular line |    |

|      | frequency.                                                                                          | 84 |

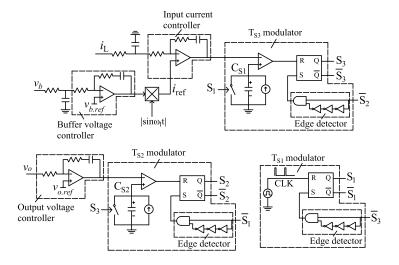

| 4.12 | Control circuit implementation.                                                                     | 84 |

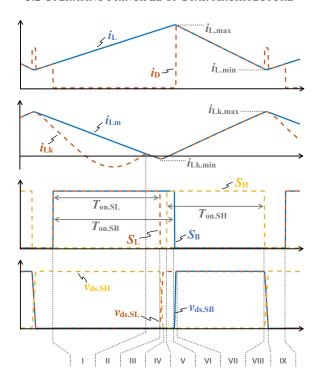

| 4.13 | Operating waveforms under the proposed modulation and control method when                           |    |

|      | the boost stage works in continuous-conduction mode and the AHB flyback stage                       |    |

|      | works in resonant mode. $v_{AG}$ is the switching node voltage of the boost stage and               |    |

|      | $v_{BG}$ is the switching node voltage of the isolated stage.                                       | 86 |

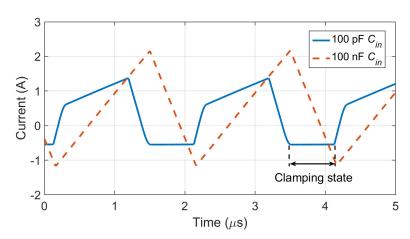

| 4.14 | Operating waveforms of $i_L$ under different $C_{in}$ values. The waveforms are                     |    |

|      | measured at 500 kHz switching frequency and 0.5 A average current.                                  | 87 |

| 4.15 | Clamping state. $v_{Cin}$ is clamped at $v_b$ and $i_L$ remains unchanged during the                |    |

|      | clamping state. The current flow of $i_L$ is highlighted in red and that of $i_{Lk}$ is             |    |

|      | highlighted in blue.                                                                                | 87 |

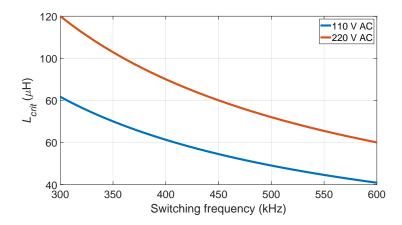

| 4.16 | $L_{crit}$ versus switching frequency under different AC voltage ( $V_{b.max}$ = 400 V, $P_o$ =     |    |

|      | 150 W).                                                                                             | 88 |

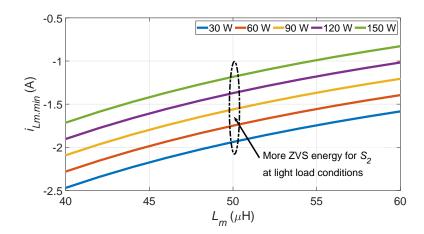

| 4.17 | $i_{Lm.min}$ versus $L_m$ under different power levels. The circuit parameters used to plot         |    |

|      | the figure are the same as Table. 4.3. There is more negative $i_{Lm.min}$ under lower              |    |

|      | $L_m$ and lower power level.                                                                        | 88 |

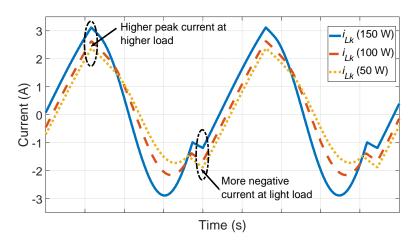

| 4.18 | Waveforms of $i_k$ under different power levels. The circuit parameters used to plot                |    |

|      | the figure are the same as Table. 4.3.                                                              | 89 |

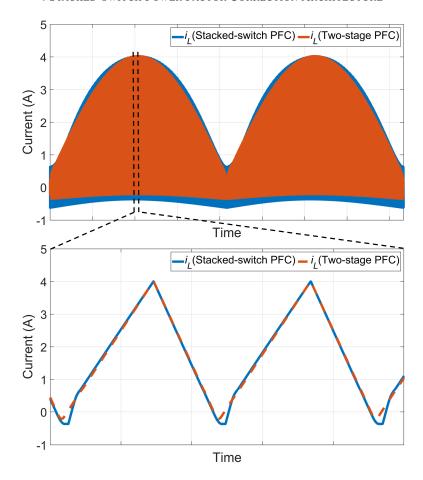

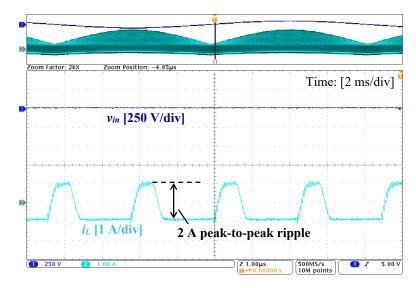

| 4.19 | Comparison of boost inductor current waveforms between the two-stage                                |    |

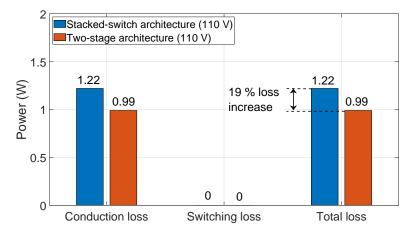

|      | architecture under CRM operations and the stacked-switch architecture under                         |    |

|      | DCM operations (110 V AC, 150 W). The top figure shows the waveforms over a                         |    |

|      | line period, and the bottom plot is a zoomed-in version of the top one.                             | 92 |

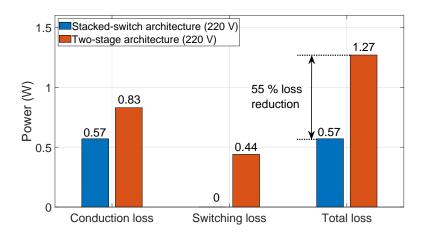

| 4.20 | Comparison of power losses in the intermediate semiconductors between the two                       |    |

|      | cases. (220 V AC, 150 W)                                                                            | 93 |

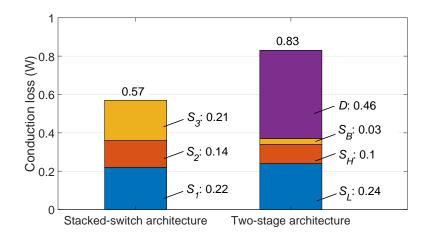

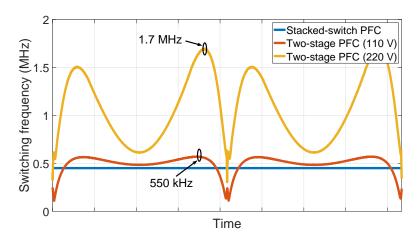

| 4.21 | Breakdown of the conduction loss at 220 V AC and 150-W output.                                   | 93  |

|------|--------------------------------------------------------------------------------------------------|-----|

| 4.22 | Comparison of the switching frequency of the boost PFC front end between                         |     |

|      | the two-stage architecture and the stacked-switch architecture. The switching                    |     |

|      | frequency of the CRM boost converter in the two-stage architecture increases at                  |     |

|      | high-line conditions, and the maximum switching frequency is around 1.7 MHz.                     |     |

|      | The stacked-switch architecture maintains a constant 450-kHz switching frequency                 |     |

|      | under different AC voltages and power levels.                                                    | 94  |

| 4.23 | Comparison of power losses in the intermediate semiconductors between the two                    |     |

|      | cases. (110 V AC, 150 W)                                                                         | 94  |

| 4.24 | Proposed method of connecting $S_4$ in parallel with $S_1$ and $S_2$ to reduce the               |     |

|      | conduction loss. $S_4$ is turned on together with $S_1$ and turned off together with             |     |

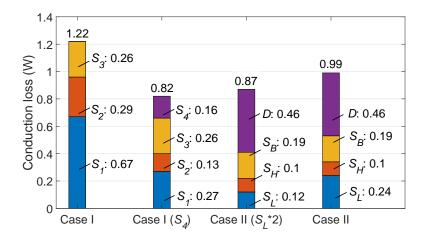

|      | $S_2$ to reduce the current stress on $S_1$ and $S_2$ . Similar to $S_1$ , $S_4$ can realize ZVS |     |

|      | by utilizing the transformer current highlighted in red to discharge its output                  |     |

|      | capacitance.                                                                                     | 95  |

| 4.25 | Breakdown of the conduction loss at 110 V AC and 150-W output. Paralleling $\mathcal{S}_4$       |     |

|      | helps Case I to achieve lower conduction loss than Case II using two switches in                 |     |

|      | parallel to implement $S_L$ .                                                                    | 95  |

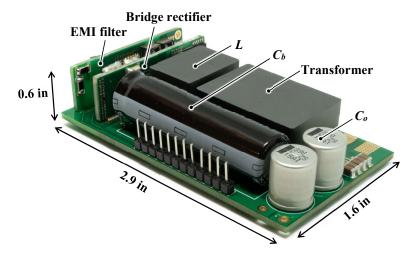

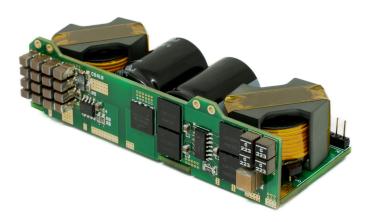

| 4.26 | Hardware prototype. The prototype measures 53.9 W/in <sup>3</sup> power density by box           |     |

|      | volume.                                                                                          | 98  |

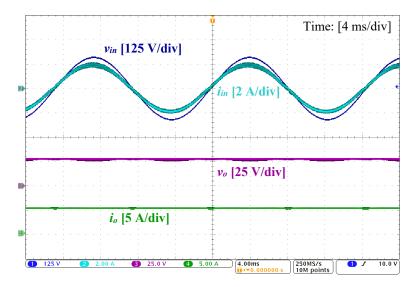

| 4.27 | Operating waveforms of $v_{in}$ , $i_{in}$ , $v_o$ , and $i_o$ at 110 V AC and 150 W output.     | 98  |

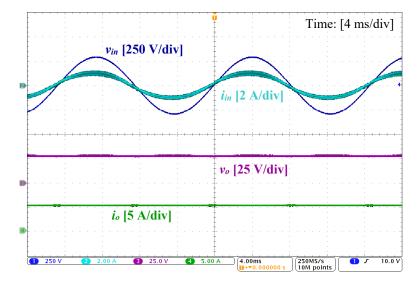

| 4.28 | Operating waveforms of $v_{in}$ , $i_{in}$ , $v_o$ , and $i_o$ at 220 V AC and 150 W output.     | 99  |

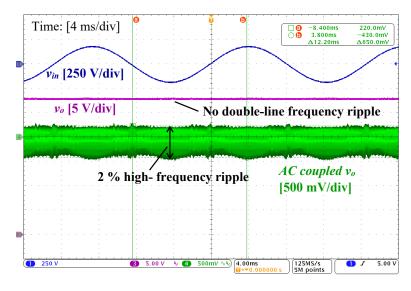

| 4.29 | Measured output voltage ripple at full-load condition. The output voltage ripple is              |     |

|      | around 2 %.                                                                                      | 99  |

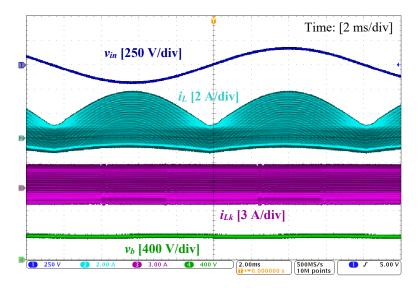

| 4.30 | Overview of operating waveforms of $v_{in}$ , $i_L$ , $i_{Lk}$ , and $v_b$ at 110 V AC.          | 100 |

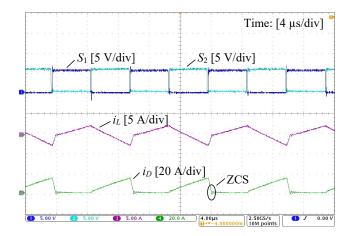

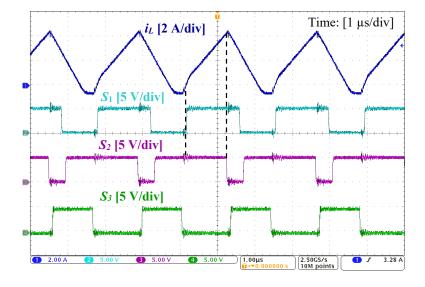

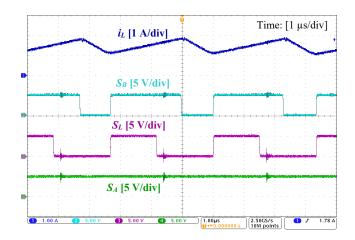

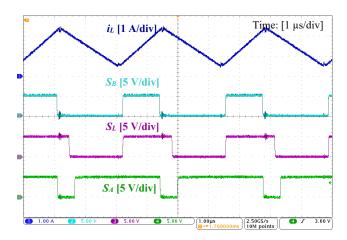

| 4.31 | Detailed operating waveforms of $i_L$ , $S_1$ , $S_2$ , and $S_3$ .                              | 100 |

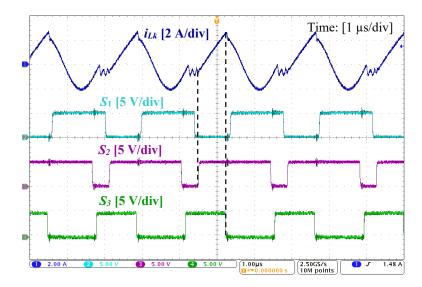

| 4.32 | Detailed operating waveforms of $i_{Lk}$ , $S_1$ , $S_2$ , and $S_3$ .                           | 101 |

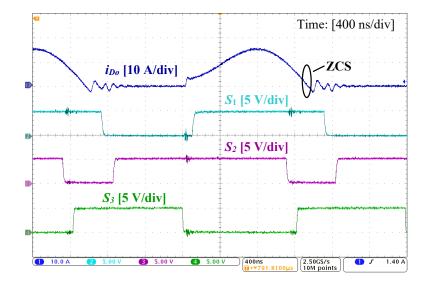

| 4.33 | Detailed operating waveforms of $i_{Do}$ , $S_1$ , $S_2$ , and $S_3$ .                           | 101 |

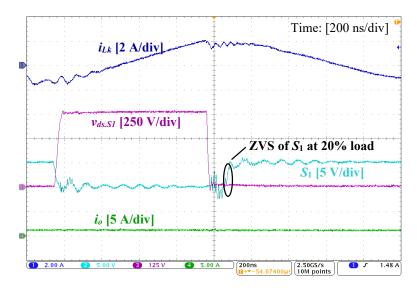

| 4.34 | ZVS waveforms of $S_1$ under 20 % load condition (220 V AC). This is the worst                   |     |

|      | condition for ZVS of $S_1$ as $i_{Lm.max}$ is minimal.                                           | 102 |

List of Figures xvii

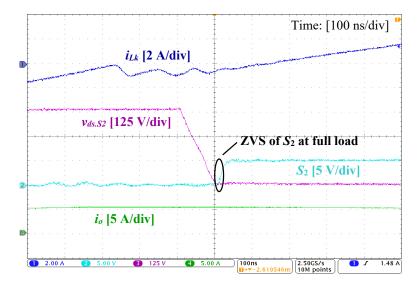

| 4.35 | ZVS waveforms of $S_2$ under full load condition (220 V AC). This is the worst                   |     |

|------|--------------------------------------------------------------------------------------------------|-----|

|      | condition for ZVS of $S_2$ as $i_{Lm.min}$ is closest to zero.                                   | 102 |

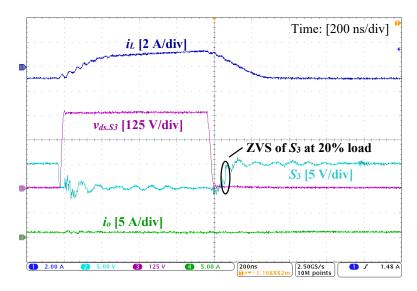

| 4.36 | 36 ZVS waveforms of $S_3$ under 20 % load condition and at the zero-crossing of $v_{in}$         |     |

|      | (220 V AC). This is the worst condition for ZVS of $S_3$ as the energy stored in $i_L$ is        |     |

|      | minimal.                                                                                         | 103 |

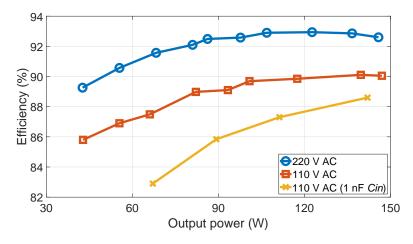

| 4.37 | Measured efficiency curves under different AC voltages and output power.                         | 103 |

| 4.38 | Operating waveform of $i_{Lin}$ at the zero-crossing of $v_{in}$ with 102 pF $C_{in}$            | 104 |

| 4.39 | Operating waveform of $i_{Lin}$ at the zero-crossing of $v_{in}$ with 1000 pF $C_{in}$           | 105 |

| 4.40 | Loss distribution under 110 V AC and full-load output.                                           | 105 |

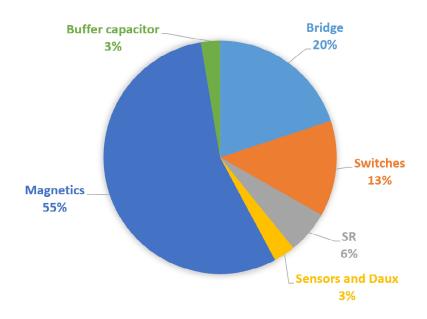

| 4.41 | THD and power factor of the prototype under different input voltage and load                     |     |

|      | conditions. The curves under 110 V and 220 V are plotted in solid lines and dashed               |     |

|      | lines, respectively.                                                                             | 106 |

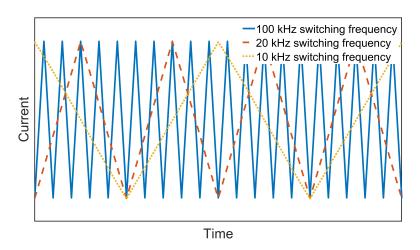

| 5.1  | Two-stage PFC architecture based on boost PFC front end and half-bridge isolated                 |     |

|      | DC-DC stage.                                                                                     | 108 |

| 5.2  | Inductor current waveforms of CRM operation at different switching frequencies                   |     |

|      | The current waveforms have the same average value. The current ripple doesn't                    |     |

|      | change with the increase of switching frequency.                                                 | 108 |

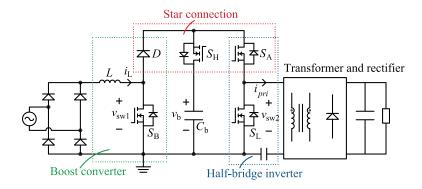

| 5.3  | Star PFC architecture.                                                                           | 111 |

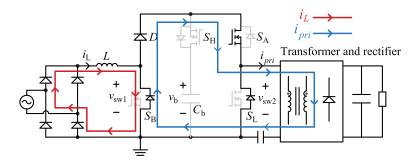

| 5.4  | 4 Key operating state of the star architecture enabling CCM operation and ZVS of                 |     |

|      | $S_B$ . The blue current path refers to the high-frequency transformer current in the            |     |

|      | isolated stage and the red path refers to the current flow of the boost inductor. The            |     |

|      | drain-source voltages of $S_B$ and $S_L$ can be discharged to zero if the blue current           |     |

|      | flow is greater than the red one.                                                                | 111 |

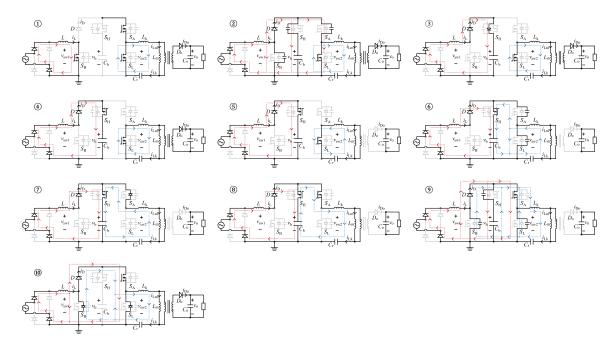

| 5.5  | Operating states of the star architecture when the second stage is the asymmetrical              |     |

|      | half-bridge flyback and $T_{on.SB} \geq T_{on.SL}$ . The current flows of $i_L$ and $i_{Lk}$ are |     |

|      | highlighted in red and blue, respectively.                                                       | 112 |

| 5.6  | Operating waveforms when $T_{on.SB} \geq T_{on.SL}$ . $S_A$ is always on.                        | 113 |

| 5.7  | Operating states of the star architecture when the second stage is the asymmetrical              |     |

|      | half-bridge flyback and $T_{on.SB} < T_{on.SL}$ . The current flows of $i_L$ and $i_{Lk}$ are    |     |

|      | highlighted in red and blue, respectively.                                                       | 113 |

xviii List of Figures

| 5.8  | Operating waveforms when $T_{on.SB} < T_{on.SL}$ . $S_A$ is turned off when $S_B$ is turned              |     |

|------|----------------------------------------------------------------------------------------------------------|-----|

|      | off, and $S_A$ is turned on after $S_L$ is turned off.                                                   | 114 |

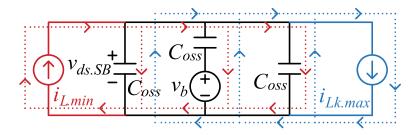

| 5.9  | Equivalent circuit of the resonant process in State VIII and State $@$ . $C_{oss}$ is the                |     |

|      | output capacitance of $S_B$ , $S_L$ , and $S_A$ . The red and blue paths represent the current           |     |

|      | flows of $i_L$ and $i_{Lk}$ , respectively. The net current between $i_L$ and $i_{Lk}$ discharges the    |     |

|      | output capacitances of $S_B$ and $S_L$ to achieve ZVS under CCM.                                         | 114 |

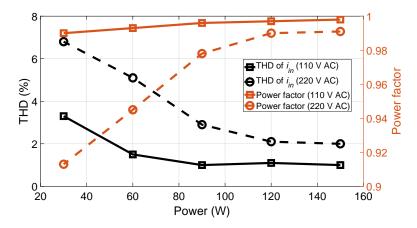

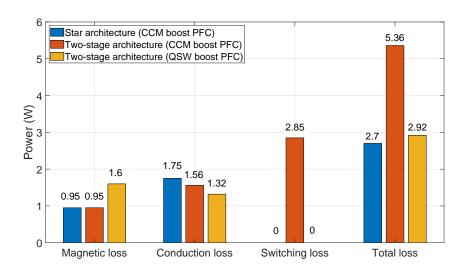

| 5.10 | Loss comparison between star architecture and two-stage architecture under                               |     |

|      | different modes of operations (110 V AC). The magnetic loss includes conduction                          |     |

|      | loss and core loss of the boost inductor.                                                                | 117 |

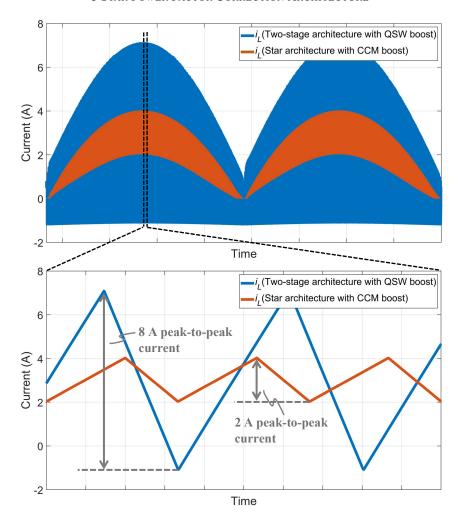

| 5.11 | Comparison of inductor current ripple between CCM and QSW operations (110                                |     |

|      | V AC). The star architecture allows four times smaller current ripple than the                           |     |

|      | two-stage architecture under QSW operations when the magnetic energy storage of                          |     |

|      | both cases are the same.                                                                                 | 118 |

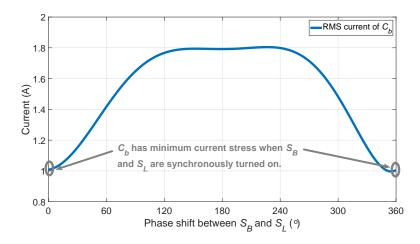

| 5.12 | RMS current of $C_b$ under different phase shift between $S_B$ and $S_L$ in the two-stage                |     |

|      | architecture (115 V, 240 W). The circuit parameters used to plot the figure are the                      |     |

|      | same as the hardware prototype. The two stages have the same switching frequency                         |     |

|      | It is found that synchronously turning on $S_B$ and $S_L$ leads to the lowest RMS                        |     |

|      | current in $C_b$ , which is an inherent feature with the star architecture.                              | 121 |

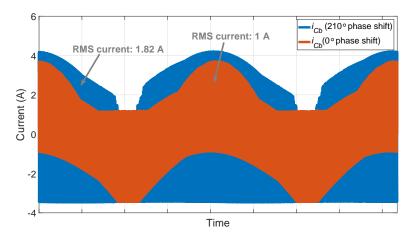

| 5.13 | Comparsion of current flows in $C_b$ , $i_{Cb}$ , under different phase shift between $S_B$ and          |     |

|      | $S_L$ (115 V, 240 W). The star architecture has $0^\circ$ phase shift between $S_B$ and $S_L$            |     |

|      | by turning on $S_B$ and $S_L$ synchronously, enabling up to 45 % reductions of RMS                       |     |

|      | current in $C_b$ .                                                                                       | 121 |

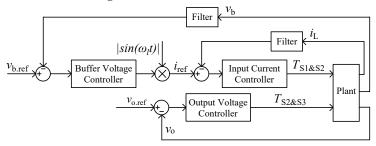

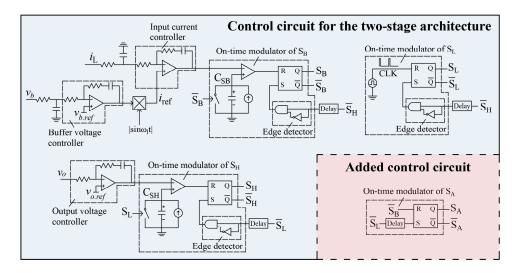

| 5.14 | Control circuit. The control circuit in the two-stage architecture is blue-shaded, and                   |     |

|      | the added control circuit is red-shaded. The star architecture only adds a delay                         |     |

|      | block and an SR latch compared with the two-stage architecture. All of the SR                            |     |

|      | latches are configured to be set-prioritized.                                                            | 123 |

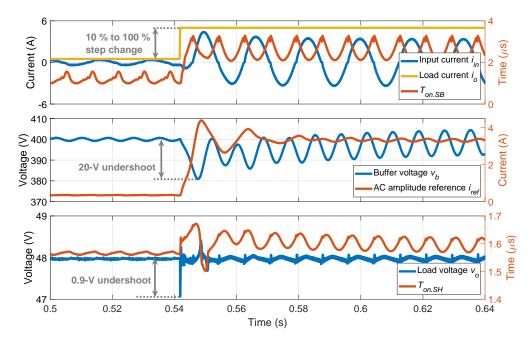

| 5.15 | Transient waveforms under a step change of load from 10 % to 100 %. $T_{on.SB}$ , $i_{ref}$              |     |

|      | and $T_{on.SH}$ are actively controlled and increased during the step change to achieve                  |     |

|      | sinusoidal $i_{in}$ , balanced $v_b$ , and constant $v_o$ . The proposed control circuit allows $i_{in}$ |     |

|      | $v_b$ , and $v_o$ to reach steady states with small undershoots after the transient event.               | 123 |

LIST OF FIGURES xix

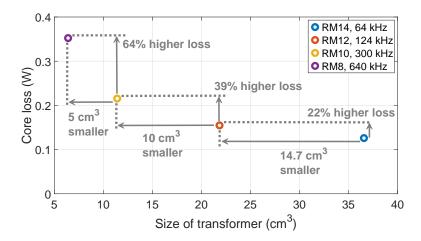

| 5.16                                                                    | Trade-off between the size of transformer and core loss. All cases follow the                          |              |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------|

| same specifications as the hardware prototype in experimental verificat |                                                                                                        |              |

|                                                                         | are designed to have the same flux density and current density. Higher switching                       | <del>,</del> |

|                                                                         | frequency enables a smaller transformer at the expense of higher core loss. The                        |              |

|                                                                         | loss penalty increases while the benefit of size reduction becomes marginal with                       |              |

|                                                                         | the increase of switching frequency.                                                                   | 125          |

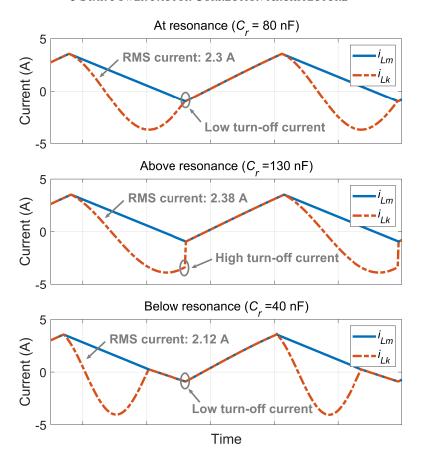

| 5.17                                                                    | Waveforms of $i_{Lk}$ and $i_{Lm}$ under different $C_r$ (240-W output). The parameters                |              |

|                                                                         | used to plot the figure are the same as the hardware prototype in experimental                         |              |

|                                                                         | verification. Varying $C_r$ changes the resonant frequency of the AHB flyback                          |              |

|                                                                         | converter, leading to three operating modes (i.e., at, above, and below resonance)                     |              |

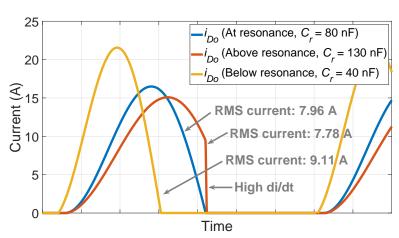

|                                                                         | Reducing $C_r$ helps to achieve a lower turn-off current of $S_L$ and a lower RMS                      |              |

|                                                                         | current on the primary side of the transformer.                                                        | 126          |

| 5.18                                                                    | Waveforms of $i_{Do}$ under different $C_r$ (240-W output). The parameters used to plot                | -            |

|                                                                         | the figure are the same as the hardware prototype in the experimental verification                     |              |

|                                                                         | All waveforms have the same average value at 5 A. Operating above resonance                            |              |

|                                                                         | leads to lower current stress on the secondary side of the transformer but results in                  | l            |

|                                                                         | higher reversed recovery loss due to higher di/dt of $i_{Do}$ .                                        | 127          |

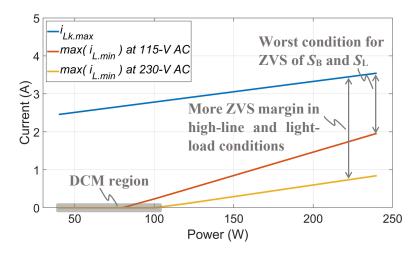

| 5.19                                                                    | $i_{Lk.max}$ and $max(i_{L.min})$ under different AC input and load power. The circuit                 |              |

|                                                                         | parameters used to plot the figure are the same as the hardware prototype in                           |              |

|                                                                         | the experimental verification. The worst condition for ZVS, which is when the                          |              |

|                                                                         | mismatch between $i_{Lk.max}$ and $max(i_{L.min})$ is minimal, is highlighted by the                   |              |

|                                                                         | double arrow.                                                                                          | 127          |

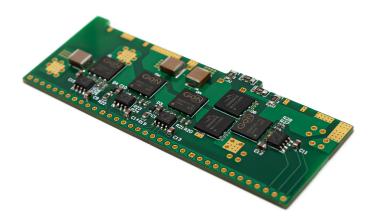

| 5.20                                                                    | Hardware prototype. The size is $3.6 \times 1.5 \times 0.8$ in <sup>3</sup> (length × width × height). |              |

|                                                                         | The power density is 55.6 W/in <sup>3</sup> .                                                          | 129          |

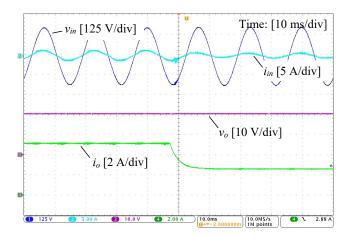

| 5.21                                                                    | Bottom side of the prototype.                                                                          | 129          |

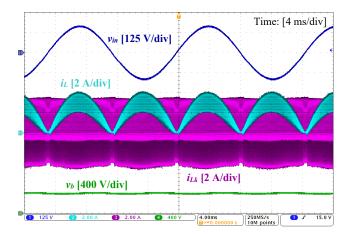

| 5.22                                                                    | Operating waveforms of $v_{in}$ , $i_{in}$ , $v_o$ , and $i_o$ at 115-V input and 240-W output.        | 131          |

| 5.23                                                                    | Operating waveforms of $v_{in}$ , $i_{in}$ , $v_o$ , and $i_o$ at 230-V input and 240-W output.        | 131          |

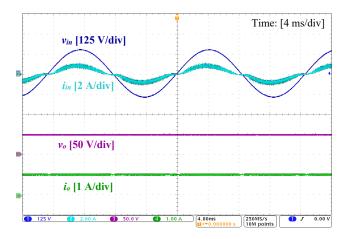

| 5.24                                                                    | Operating waveforms of $v_{in}$ , $i_{in}$ , $v_o$ , and $i_o$ at 115-V input and 48-W output.         | 132          |

| 5.25 | Operating waveforms of $i_L$ , $S_B$ , $S_L$ , and $S_A$ when $T_{on.SB} > T_{on.SL}$ . $S_A$ is always     |     |

|------|-------------------------------------------------------------------------------------------------------------|-----|

|      | on in a switching period as designed. The switching frequency is constant at 300                            |     |

|      | kHz, as expected.                                                                                           | 132 |

| 5.26 | Operating waveforms of $i_L$ , $S_B$ , $S_L$ , and $S_A$ when $T_{on.SB} < T_{on.SL}$ . Both $S_A$ and      |     |

|      | $S_B$ switch off to reduce $i_L$ . The switching frequency is constant at 300 kHz, as                       |     |

|      | expected.                                                                                                   | 133 |

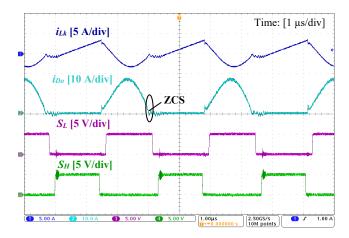

| 5.27 | Operating waveforms of $i_{Lk}$ , $i_{Do}$ , $S_L$ , and $S_H$ at 240-W output. The circuit is finely       | ,   |

|      | tuned to achieve near zero circulating energy.                                                              | 133 |

| 5.28 | Operating waveforms of $v_{in}$ , $i_L$ , $i_{Lk}$ , and $v_b$ at 115-V input and 240-W output.             |     |

|      | $i_{L.min}$ is lower than $i_{Lk.pk}$ across the whole line period, enabling ZVS of $S_L$ and               |     |

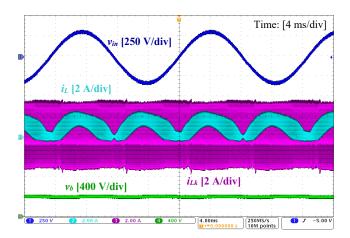

|      | $S_B$ .                                                                                                     | 134 |

| 5.29 | Operating waveforms of $v_{in}$ , $i_L$ , $i_{Lk}$ , and $v_b$ at 230-V input and 240-W output.             |     |

|      | There is more ZVS margin for $S_L$ and $S_B$ compared with that of 115-V input                              |     |

|      | because the difference between $i_{L.min}$ and $i_{L.pk}$ is larger.                                        | 134 |

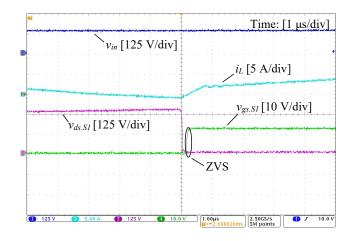

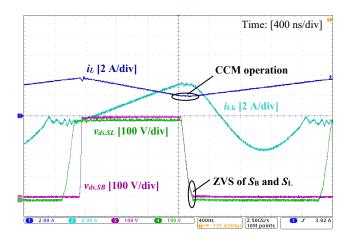

| 5.30 | ZVS waveforms of $S_L$ and $S_B$ at the peak of 115-V input and 240-W output.                               |     |

|      | This is the most stringent condition for the ZVS realizations of $\mathcal{S}_L$ and $\mathcal{S}_B$ as the |     |

|      | mismatch between $i_{L.min}$ and $i_{Lk.pk}$ is minimal. ZVS of $S_L$ and $S_B$ as well as CCM              | •   |

|      | operation of $i_L$ are achieved.                                                                            | 135 |

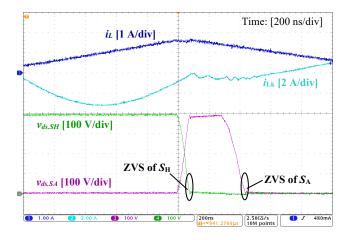

| 5.31 | ZVS waveforms of $S_A$ and $S_H$ at 240-W output. This is the most stringent                                |     |

|      | condition for the ZVS realization of $S_A$ as $i_{Lk.min}$ is closest to zero.                              | 135 |

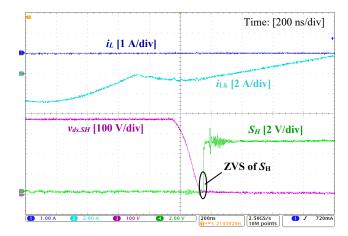

| 5.32 | 5.32 ZVS waveforms of $S_H$ near the zero-crossing of 115-V input and at 240-W output                       |     |

|      | This is the most stringent condition for the ZVS realization of $S_H$ as both $i_{L.max}$                   |     |

|      | and $i_{Lk.min}$ are closest to zero.                                                                       | 136 |

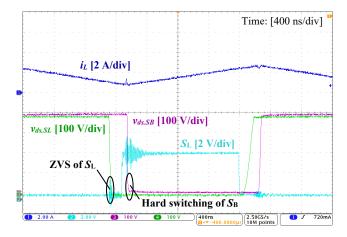

| 5.33 | Loss of ZVS in the conventional two-stage architecture under CCM operation. $S_L$                           |     |

|      | can still realize ZVS but $S_B$ cannot. $S_B$ (not shown in the figure) is turned on                        |     |

|      | simultaneously with $S_L$ to reduce the current stress of $C_b$ .                                           | 136 |

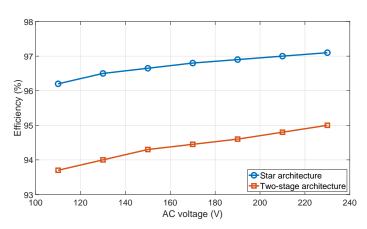

| 5.34 | Efficiency curves of the star architecture and the two-stage architecture at 240-W                          | r   |

|      | output across different input voltage. The efficiency of the two-stage architecture is                      |     |

|      | measured at the same prototype as the star architecture.                                                    | 137 |

|      |                                                                                                             |     |

| LIST OF FIGURES |  |

|-----------------|--|

|                 |  |

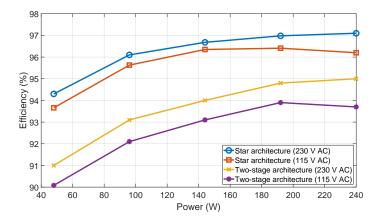

| 5.35 | Efficiency curves of the star architecture and the two-stage architecture at different |     |

|------|----------------------------------------------------------------------------------------|-----|

|      | power levels.                                                                          | 137 |

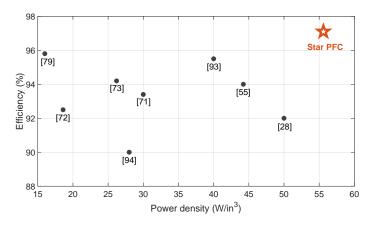

| 5.36 | Comparison of efficiency and power density with recent works.                          | 137 |

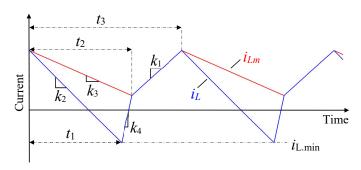

| .1   | Detailed waveforms of $i_L$ and $i_{Lm}$ .                                             | 140 |

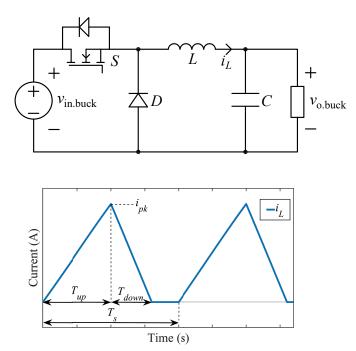

| .2   | Topology and operating waveform of a buck converter.                                   | 141 |

#### CHAPTER 1

#### Introduction

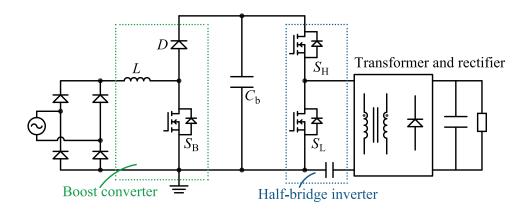

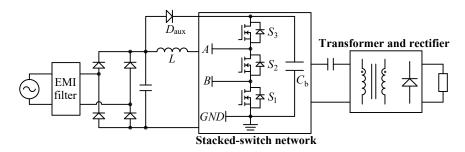

AC–DC converters are widely used to transfer power from the utility grid to various DC load such as batteries, LEDs, computing devices, and so on [1]. The future trend of AC–DC converters is toward higher efficiency, higher power density, and lower cost to tackle the energy crisis, enable new applications, and reduce electronic waste. Among many solutions, a two-stage PFC architecture has been a dominant solution for AC–DC converters in commercial products over 75 W where power factor correction (PFC) is mandatory. The two-stage architecture generally consists of a boost PFC front end for sinusoidal input current and an isolated DC–DC back end for output voltage regulation, as shown in Fig. 1.1. The wide adoption of the two-stage architecture is mainly because multiple tasks in PFC applications can be divided and optimally addressed by each of the two stages, leading to high overall performance in efficiency, power density, operating range, design simplicity, and cost. Nevertheless, the performance of the two-stage architecture is increasingly challenged by the demand for lower cost, higher efficiency, and higher power density.

FIGURE 1.1: Two-stage PFC architecture.

2 1 Introduction

This thesis takes the two-stage architecture as a benchmark and investigates new control methods, circuit topology, and power architectures to improve the performance of AC–DC converters. The key contributions are summarized as follows:

#### 1. Control method:

Single-stage active-clamp flyback (ACF) converter has been abandoned in PFC application due to the requirement of excessive output capacitance to reduce the double-line frequency ripple. This thesis finds a new method to control the ACF converter, enabling the clamping capacitor to be utilized as an active energy buffer without any modifications to the topology. As a result, lower buffer capacitance can be used without affecting the output voltage's ripple performance. With this new control method, it is demonstrated that up to 92 % size reduction of the buffer capacitor can be realized while achieving higher efficiency and lower component count than the two-stage solution [2].

#### 2. Circuit topology:

The boost PFC front end of the two-stage architecture suffers from hard switching, making it hard to reduce the size of inductor through high-frequency operations. In addition, high capacitance is required in the boost PFC front end to reduce the low-frequency ripple, leading to bulky buffer capacitors. This thesis introduces a new circuit topology for PFC front end applications. The new topology features ZVS across a universal input, ripple-free DC-link voltage, and reduced buffer capacitance, allowing for size reduction of both the inductor and the buffer capacitor. A 100-W universal input prototype is built, measuring a 96.7 % peak efficiency and 50.8 W/in<sup>3</sup> power density. Compared to a typical critical-mode (CRM) boost PFC front end, the prototype achieves a 47% size reduction of the magnetics, a 21% size reduction of the buffer capacitor, and an almost constant DC-link voltage while maintaining comparable efficiency performance [3].

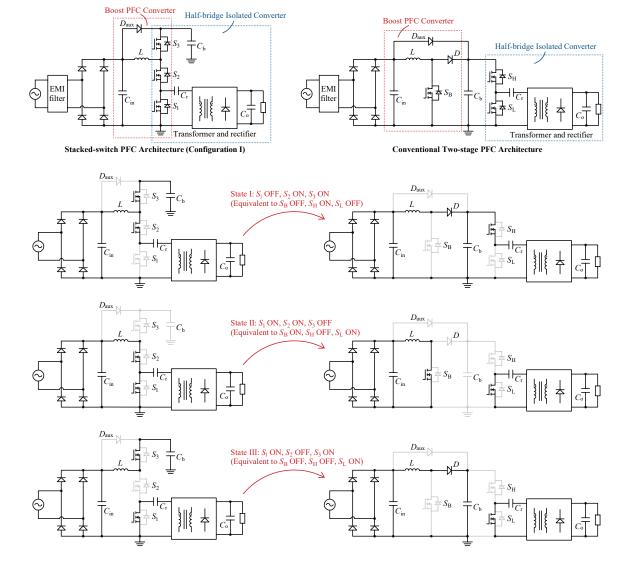

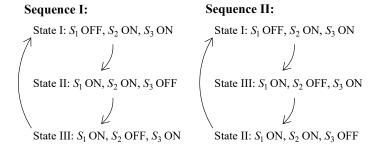

#### 3. Stacked-switch architecture:

The author found that the above solutions have some issues that may hinder their practical applications, including losing ZVS at light-load conditions, requiring additional passive components, and varying switching frequencies. Motivated by 1 Introduction 3

these issues, a stacked-switch PFC architecture is developed. The stacked-switch architecture has lower component counts and, thus, lower cost than the two-stage architecture. In addition, it is first demonstrated that full-range ZVS of all active switches can be achieved under a constant switching frequency in PFC applications, enabling higher power density than the two-stage architecture and simplifying the hardware design and implementation. It is also demonstrated that the stacked-switch architecture can directly take advantage of the existing control circuits for the two-stage architecture and a simple analog circuit is enough. A 150-W-universal-input prototype is built, measuring 92.9 % peak efficiency and 53.9 W/in<sup>3</sup> power density by box volume [4].

#### 4. Star architecture:

While high-frequency operations enable smaller magnetic components, the achievable power density is also constrained by the temperature rise, calling for solutions that can operate at a higher frequency while having higher efficiency. The author, therefore, tried to find a scaling law in magnetic components that may lead to higher efficiency at a higher frequency. Interestingly, one such scaling law is found — the inductor features lower root-mean-square (RMS) current and lower peak-to-peak flux density with the increase of switching frequency in continuousconduction-mode (CCM) operations of the boost converter. However, it is hard to take advantage of this scaling law because the conventional CCM boost PFC converter is hard-switched, resulting in high switching loss if the switching frequency is increased. Targeting at 1) achieving CCM operations to take advantage of the scaling law and 2) achieving soft switching to unlock higher switching frequency, a star PFC architecture is developed, which only has one additional transistor compared to the two-stage architecture. With the star architecture, it is first found that the second stage's ripple current allows reduced current ripple in the first PFC stage and can assist full-range ZVS of the PFC stage even under CCM operations. The high performance of star architecture is enabled by realizing (i) continuous-conduction-mode (CCM) operation of the boost PFC stage and (ii) full-range zero-voltage-switching (ZVS) of all active switches. In addition, the star architecture can (i) operate at a 4 1 Introduction

constant frequency via a proper selection of the circuit topology and modulation method and (ii) be controlled based on simple and low-cost analog electronic circuits. A 300-kHz, 240-W, 48-V-output, and universal-input prototype is built to verify the performance of the star architecture, showcasing high power factor, constant output voltage, 97.1 % full-load efficiency, 55.6 W/in<sup>3</sup> power density by box volume [5].

This thesis is organized as follows. Chapter two introduces the new control method for ACF converter. Chapter three introduces the new circuit topology for PFC front end. Chapter four introduces the stacked-switch architecture, and the star architecture is introduced in Chapter five. Finally, chapter six concludes this thesis.

#### CHAPTER 2

## A Modulation Method for Capacitance Reduction in Active-clamp Flyback Converter

## 2.1 Background

In an effort to promote consumer convenience and reduce electronic waste, the Universal Series Bus (USB), originally created in 1996 as a communication interface with only limited power delivery capabilities, has now become a primary method for powering and charging a wide range of electronics products [6]. The recently released USB Power Delivery 3.1 (USB-PD 3.1) has just pushed the power delivery profile to 240-W power range, making it possible to extend its applicability to an even greater number of application scenarios [7].

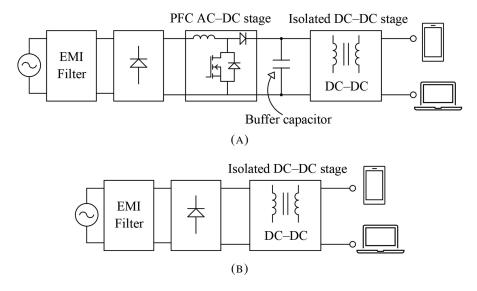

The increased power demand, however, poses great challenges to existing adapter design regarding system cost and power density, especially as the power level exceeds 75 W when power factor correction (PFC) becomes mandatory [8]. Conventional solutions in the above-75W range usually adopt a two-stage topology [9], consisting of an AC–DC stage for PFC followed by a DC–DC stage for output regulation and galvanic isolation, with a twice-line frequency buffer capacitor in between (see Fig. 2.1 (a)) [9]–[12]. On the one hand, a two-stage topology requires multiple switches, drivers, sensors, magnetics, auxiliary power supplies and control circuits, generally leading to complex and costly design. On the other hand, the buffer capacitor is a well-known bottleneck in realizing a high-density adapter design: its size is generally large as its energy storage requirement depends on the line frequency, thereby cannot be reduced by increasing the switching frequency [13]. Thus, to lower system cost and increase power density, it is highly desirable to develop single-stage isolated solutions with

FIGURE 2.1: Architectures of adapters: (A) two-stage architecture typically used when high power factor is required (B) single-stage architecture.

reduced buffer capacitance requirement while being able to retain the conventional two-stage solutions' efficiency, PFC and galvanic isolation function (see Fig. 2.1 (b)).

Targeting the limitations of the two-stage solution, significant research efforts have focused either on single-stage isolated AC-DC power conversion [14]–[16] or buffer capacitance reduction [17]–[20] or both, through the development of advanced topology, modulation method and/or power devices. For those focusing only on single-stage isolated (or buffer capacitance reduction), the issues of large buffer capacitor (or high component count) remain unsolved. On the other hand, those focusing on both targets, in general, cannot outperform the conventional two-stage solutions. For example, [21] presents a hybrid converter that merges a two-stage converter into one stage and utilizes the intermediate capacitor as an active power buffer for capacitance reduction. However, the solution is based on hard switching and the leakage energy is lost per switching cycle, presenting high switching and leakage energy losses at the high operating frequency. A modified single-stage active-clamped flyback (ACF) converter is proposed in [22], effectively integrating the active power buffer function into the clamping capacitor. Buffer capacitance can be reduced, but the cost and losses are increased, as a tertiary winding and two extras secondary MOSFETs are needed and the two MOSFETs and output diodes are hard switched. A modified flyback-based solution is presented in [23].

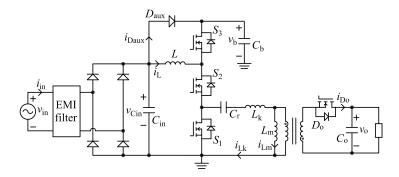

FIGURE 2.2: The topology of ACF converter.

Capacitance requirement is reduced by integrating the active power buffer into the system, but two additional switches and one tertiary winding are required while all switches are hard switched.

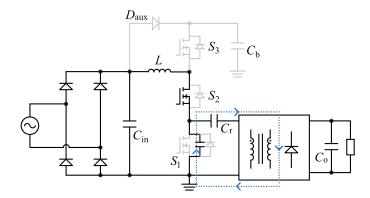

Focusing on single-stage power conversion and buffer capacitance reduction, this thesis discusses a new modulation method for ACF converter [24]. Without the need for hardware modifications, this modulation method enables ACF converter to achieve (i) PFC, (ii) active power buffering, (iii) zero-voltage-switching (ZVS) of active switches, (iv) zero-current-switching (ZCS) of output rectifier diode or synchronous rectifier (SR), (v) galvanic isolation, and (vi) leakage recycling, all in a single power-conversion stage. Although this approach requires a more elaborate control strategy than the conventional ACF control method, it provides an economically viable and technologically elegant solution to the problem of costly and bulky adapter design for high-power delivery.

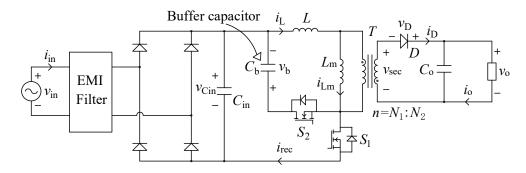

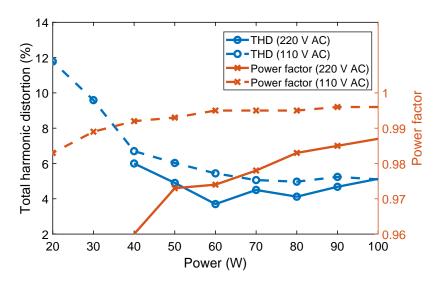

## 2.2 Topology and Operating Principle

Fig. 2.2 illustrates the basic circuit of an ACF-based AC-DC adapter, consisting of an EMI filter, a diode bridge rectifier, a high frequency filter  $C_{in}$ , a half-bridge switch leg  $S_1$  and  $S_2$ , a clamping and energy buffer capacitor  $C_b$ , a transformer T with a magnetizing inductance of  $L_m$  and a turns ratio of  $N_1:N_2$ , a resonant inductor L, an output rectifier D, and an output filter  $C_o$ . Here, L may be further integrated with T, and D replaced with an SR. To explain the proposed modulation method, the operation of the conventional continuous conduction mode ACF converter is briefly reviewed [25].

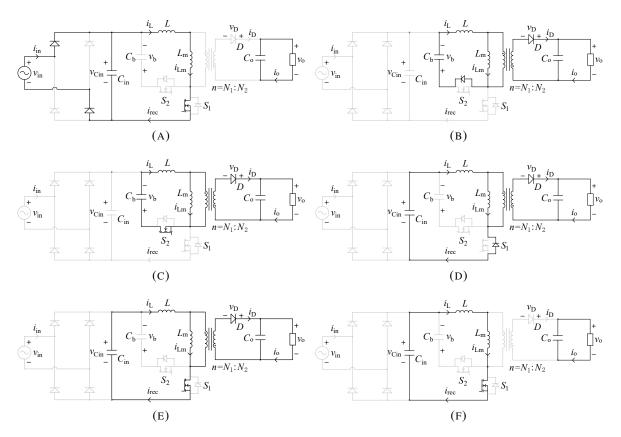

FIGURE 2.3: Operating states. (A) State I: $[T_o-T_1]$ . (B) State II: $[T_1-T_2]$ . (C) State III: $[T_2-T_3]$ . (D) State IV: $[T_3-T_4]$ . (E) State V: $[T_4-T_5]$ . (F) State VI: $[T_5-T_5]$ .  $T_6$ ].

## 2.2.1 Conventional Operating Method

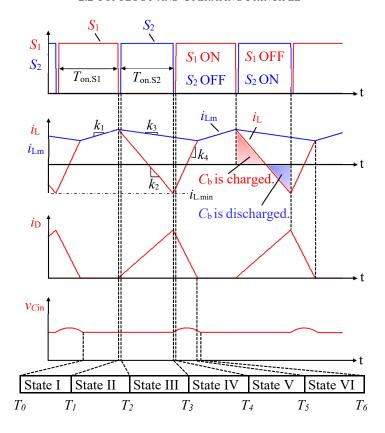

The key operating waveforms of the conventional ACF converter are shown Fig. 2.4. Neglecting the deadtime, 6 operating states can be identified over one switching cycle.

State I [ $T_0$ – $T_1$ ]:  $i_L$  and  $i_{Lm}$  are linearly charged by  $v_{in}$  as shown in Fig. 2.3 (a) with a rising slope  $k_1$  expressed by

$$k_1 = \frac{v_{in}}{L + L_m}. (2.1)$$

The diode D is reverse-biased as the voltage across the secondary side of T, annotated as  $v_{sec}$ in Fig. 2.2, is negative. State I ends when  $S_1$  is turned off at  $T_1$ .

State II  $[T_1-T_2]$ : L and  $L_m$  begin to resonate with the total output capacitances of  $S_1$  and  $S_2$ . The resonance ends when the body diode of  $S_2$  starts to conduct. State II ends when  $S_2$  is

FIGURE 2.4: Operating waveforms.

turned on with ZVS at  $T_2$ . The condition,  $v_b \ge N_1 v_o / N_2$ , is essential to ensure a sufficient voltage across the secondary winding to turn on D so that energy can be transferred from the primary side to the secondary side.

State III  $[T_2-T_3]$ :  $S_1$ 's drain-source voltage is clamped at  $(v_b + v_{Cin})$  while  $i_L$  and  $i_{Lm}$  start to decrease. During this period,  $i_L$  and  $i_{Lm}$  become

$$i_L = i_{L,min} + k_2(t - T_3)$$

(2.2)

$$i_{Lm} = i_{L.min} + k_3(t - T_3) (2.3)$$

where  $i_{L.min}$  is the minimum  $i_L$  within each switching period and the expression of  $i_{L.min}$  is derived in Appendix,  $k_2$  is the slope of  $i_L$  in State III, and  $k_3$  is the slope of  $i_{Lm}$  in State III.  $k_2$  and  $k_3$  can be derived as

$$k_2 = \frac{N_1 v_o - N_2 v_b}{N_2 L} \tag{2.4}$$

$$k_3 = -\frac{N_1 v_o}{N_2 L_m}. (2.5)$$

In State III,  $C_b$  is first charged and then discharged by  $i_L$  as the polarity of  $i_L$  reverses (see Fig. 2.4). The amount of charge absorbed by and released from  $C_b$  are highlighted as red and blue areas in Fig. 2.4, respectively. With the conventional operation method,  $S_2$  needs to be controlled to ensure the charges are balanced in  $C_b$  per switching period at a steady state. State III ends when  $S_2$  is turned off at  $T_3$ .

State IV  $[T_3-T_4]$ : The reversed  $i_L$  discharges the output capacitance of  $S_1$ . The body diode of  $S_1$  starts to conduct, and  $S_1$  is ready for ZVS turn-on as shown in Fig. 2.3 (d). Since  $i_L < i_{Lm}$ , D continues to conduct, clamping the voltage of  $L_m$  at  $(N_1v_o/N_2)$ . Based on Kirchhoff's Voltage Law, the voltage across L is  $(v_{Cin} + N_1v_o/N_2)$ .  $i_L$  thus increases with a slope of

$$k_4 = \frac{N_1 v_o + N_2 v_{Cin}}{N_2 L_m}. (2.6)$$

The current slope of  $i_{Lm}$  remain the same as  $k_3$ . State IV ends when  $S_1$  is turned on with ZVS at  $T_4$ .

State V [ $T_4$ – $T_5$ ]: During this state, L resonates with  $C_{in}$ , causing  $v_{Cin} > |v_{in}|$ . Hence, the front-end bridge rectifier is reverse-biased.  $i_{Lm}$  continues to decrease with a slope of  $k_3$ , while  $i_L$  increases. Therefore,  $i_D$  gradually decreases. State V ends when  $i_D$  reaches zero, and D is turned off with ZCS at  $T_5$ .

State VI  $[T_5-T_6]$ : L continues to resonate with  $C_{in}$  as shown in Fig. 2.3 (f). The resonance ends at  $T_6$  when  $v_{Cin}$  drops to  $|v_{in}|$  and the front-end bridge rectifier starts to conduct and clamps  $v_{Cin}$  at  $|v_{in}|$ .

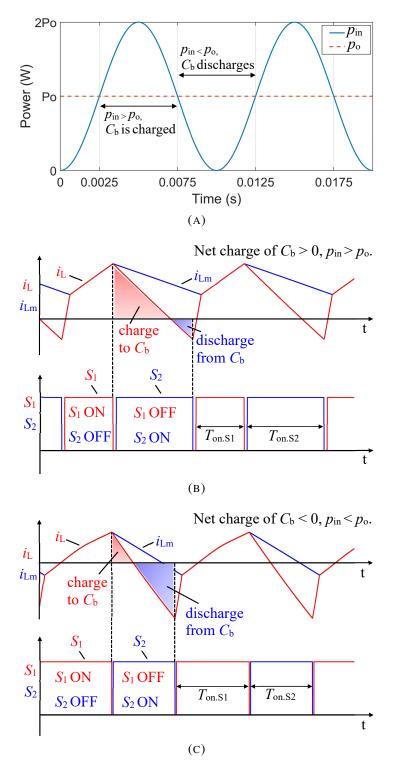

### 2.2.2 Proposed Operation

The proposed operating method is identical to the conventional one except for State III. According to the operating principles mentioned above,  $C_b$  is first charged and then discharged in State III when  $S_2$  is maintained 'on'. As a result, the net charge per switching period can be controlled by the duration of State III (or  $S_2$ 's on time). In other words, one may turn  $C_b$  into a twice-line frequency energy storage buffer (or an active power buffer) by actively controlling  $S_2$ 's on time properly. In particular, when  $p_{in} > p_o$ , as shown in Fig. 2.5 (a), the turn on time of  $S_2$ ,  $T_{on.S2}$ , needs to be reduced such that  $C_b$  is in effect absorbing power, as shown in Fig. 2.5 (b) where the red area is larger than the blue one. Similarly, when  $p_{in} < p_o$ , the turn on time of  $S_2$  needs to be increased such that  $C_b$  is in effect releasing power, as shown in Fig. 2.5 (c) where the blue area is greater than the red one. The proposed converter operation is thus different from the conventional approach, which aims to achieve zero net charges in  $C_b$  per switching period. Thereby,  $C_b$  cannot offer low-frequency energy storage capability. This new approach indicates that one can integrate the active power buffering function into ACF circuit topology shown in Fig. 2.2 without modifying the hardware. Furthermore, all features of ACF are retained, including soft switching of  $S_1$ ,  $S_2$  and D, leakage inductor energy recycling, galvanic isolation, and active voltage clamping for  $S_1$ .

Table. 2.1 summarises the key differences between the conventional and the proposed operating methods of ACF converter. Although the PFC function can be achieved with ACF converters, most existing works only utilise the ACF converter for DC/DC conversions without performing the PFC function. The reason is that the conventional method of AC–DC ACF requires high capacitance of  $C_o$  to mitigate twice-line frequency ripples and maintain a low voltage ripple of the DC side.

## 2.3 Modulation and Control Method

The modulation and control schemes are newly developed and discussed in this section to support the proposed operation in Section 2.2.2.

FIGURE 2.5: Charging and discharging phases of  $C_b$ : (A) power flows of input power  $p_{in}$  and output power  $p_o$  (B) charging phase (C) discharging phase.

TABLE 2.1: Comparison between the conventional operating methods and the proposed operating method.

|                          | Conventional Method Conventional Method                |                   | Proposed Method           |

|--------------------------|--------------------------------------------------------|-------------------|---------------------------|

|                          | of DC-DC ACF                                           | of AC-DC ACF      | of AC-DC ACF              |

| Soft switching           |                                                        |                   |                           |

| Leakage recycling        | $\sqrt{}$                                              | $\sqrt{}$         | $\sqrt{}$                 |

| PFC                      | X                                                      | $\sqrt{}$         | $\sqrt{}$                 |

| Active power buffering   | X                                                      | X                 | $\sqrt{}$                 |

| Extra PFC Stage          | Require                                                | Not require       | Not require               |

| 100/120 Hz buffer        | $C_{in}$                                               | $C_o$             | $C_b$                     |

| Bias of buffer voltage   | $\operatorname{High}\left(>\left v_{in}\right \right)$ | Small (= $v_o$ )  | Medium (> $N_1 v_o/N_2$ ) |

| Voltage swing of buffer  | Small                                                  | Highly restricted | Large                     |

| Size of buffer capacitor | Medium                                                 | Large             | Small                     |

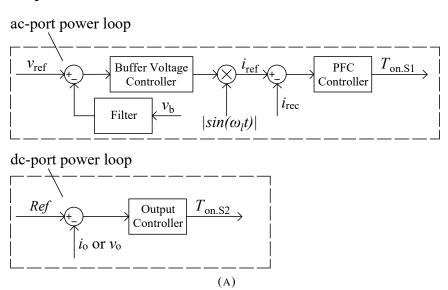

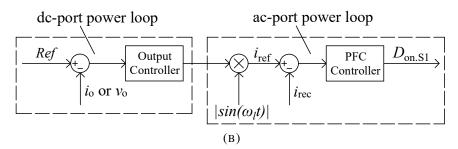

#### 2.3.1 Dual On-time Modulation

According to Fig. 2.4, the current (or equivalently power) at the ac-port of ACF over one switching period is determined by the duration of the State I. Therefore, the ac-port current (or power),  $i_{in}$ , scales with the on-time of  $S_1$ , denoted as  $T_{on.S1}$ , which can be utilized as a control variable for ac-port current (power) regulation. On the other hand, according to Fig. 2.4, the current (power) at the dc-port,  $i_o$ , is determined by the duration of State III. In particular, the longer State III is, the more energy is to be released from  $C_b$  and the deeper L will be negatively charged, leading to an increased peak of secondary diode current and average dc current. Therefore, the dc-port current (power) scales with the on-time of  $S_2$ , denoted as  $T_{on.S2}$ , which can be utilized as a control variable for dc-port voltage (power) regulation. According to the automatic power decoupling control theory [26], and based on the two reasons mentioned above,  $T_{on.S1}$  and  $T_{on.S2}$  are chosen as modulation signals. Such a control method is named dual on-time modulation thereafter.

The architecture of the proposed dual on-time modulation is shown in Fig. 2.6 (a). The control scheme consists of an ac-port power loop and a dc-port power loop. For the ac-port, a PFC controller regulates  $i_{rec}$  to follow a rectified sinusoidal reference  $i_{ref}$  to achieve PFC function by adjusting  $T_{on.S1}$ , which is the on-state time of  $S_1$ . The amplitude of  $i_{ref}$  is obtained from the outer buffer voltage loop, which regulates the DC value of  $v_b$  at a predefined reference signal  $v_{ref}$ . The value of  $v_{ref}$  shall be properly specified to balance the current stress of  $C_b$

#### **Proposed control architecture:**

#### **Conventional control architecture:**

FIGURE 2.6: (A) Proposed control architecture for the single-stage ACF PFC converter. (B) Conventional control architecture for the single-stage ACF PFC converter [14].