#### Wright State University

#### **CORE Scholar**

Browse all Theses and Dissertations

Theses and Dissertations

2022

## Quadrature Phase-Domain ADPLL with Integrated On-line Amplitude Locked Loop Calibration for 5G Multi-band **Applications**

Xiaomeng Zhang Wright State University

Follow this and additional works at: https://corescholar.libraries.wright.edu/etd\_all

Part of the Engineering Commons

#### **Repository Citation**

Zhang, Xiaomeng, "Quadrature Phase-Domain ADPLL with Integrated On-line Amplitude Locked Loop Calibration for 5G Multi-band Applications" (2022). Browse all Theses and Dissertations. 2565. https://corescholar.libraries.wright.edu/etd\_all/2565

This Dissertation is brought to you for free and open access by the Theses and Dissertations at CORE Scholar. It has been accepted for inclusion in Browse all Theses and Dissertations by an authorized administrator of CORE Scholar. For more information, please contact library-corescholar@wright.edu.

# QUADRATURE PHASE-DOMAIN ADPLL WITH INTEGRATED ON-LINE AMPLITUDE LOCKED LOOP CALIBRATION FOR 5G MULTI-BAND APPLICATIONS

A Dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

by

#### XIAOMENG ZHANG

M.S.Eg., Wright State University, 2014

B.E., Dalian Jiaotong University, People's Republic of China, 2012

2022

Wright State University

## COPYRIGHT BY XIAOMENG ZHANG 2022

## WRIGHT STATE UNIVERSITY GRADUATE SCHOOL

Nov 29, 2021

I HEREBY RECOMMEND THAT THE DISSERTATION PREPARED UNDER MY SUPERVISION BY Xiaomeng Zhang ENTITLED Quadrature Phase-Domain ADPLL with Integrated On-line Amplitude Locked Loop Calibration for 5G Multi-band Applications BE ACCEPTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF Doctor of Philosophy.

|                                 | Saiyu Ren, Ph.D. Dissertation Director                                              |

|---------------------------------|-------------------------------------------------------------------------------------|

|                                 | Amab Shaw, Ph.D. Director, Electrical Engineering PhD. Program                      |

|                                 | Barry Milligan, Ph.D. Vice Provost for Academic Affairs Dean of the Graduate School |

| Committee on Final Examination: |                                                                                     |

| Raymond E. Siferd, Ph.D.        |                                                                                     |

| Marian K. Kazimierczuk, Ph.D.   |                                                                                     |

| Henry Chen, Ph.D.               |                                                                                     |

| Yan Zhuang, Ph.D.               |                                                                                     |

#### **Abstract**

Zhang, Xiaomeng. Ph.D., Department of Electrical Engineering, Wright State University, 2022. Quadrature Phase-Domain ADPLL with Integrated On-line Amplitude Locked Loop Calibration for 5G Multi-band Applications.

5<sup>th</sup> generation wireless systems (5G) have expanded frequency band coverage with the low-band 5G and mid-band 5G frequencies spanning 600 MHz to 4 GHz spectrum. This dissertation focuses on a microelectronic implementation of CMOS 65 nm design of an All-Digital Phase Lock Loop (ADPLL), which is a critical component for advanced 5G wireless transceivers. The ADPLL is designed to operate in the frequency bands of 600MHz-930MHz, 2.4GHz-2.8GHz and 3.4GHz-4.2GHz. Unique ADPLL sub-components include: 1) Digital Phase Frequency Detector, 2) Digital Loop Filter, 3) Channel Bank Select Circuit, and 4) Digital Control Oscillator. Integrated with the ADPLL is a 90-degree active RC-CR phase shifter with on-line amplitude locked loop (ALL) calibration to facilitate enhanced image rejection while mitigating the effects of fabrication process variations and component mismatch. A unique high-sensitivity high-speed dynamic voltage comparator is included as a key component of the active phase shifter/ALL calibration subsystem. 65nm CMOS technology circuit designs are included for the ADPLL and active phase shifter with simulation performance assessments. Phase noise results for 1 MHz offset with carrier frequencies of 600MHz, 2.4GHz, and 3.8GHz are -130, -122, and -116 dBc/Hz, respectively. Monte Carlo simulations to account for process variations/component mismatch show that the active phase shifter with ALL calibration maintains accurate quadrature phase outputs when

operating within the frequency bands 600 MHz-930 MHz, 2.4 GHz-2.8 GHz and 3.4 GHz-4.2 GHz.

### Table of Contents

| I.   |     | Introduction                                                      | 1  |

|------|-----|-------------------------------------------------------------------|----|

|      | 1.1 | Background                                                        | 1  |

|      | 1.2 | 5G Spectrum                                                       | 3  |

|      |     | 1.2.1 5G 3-Band Spectrum Architecture                             | 3  |

|      |     | 1.2.2 5G Spectrum Allocations                                     | 4  |

|      | 1.3 | Beamforming and Image Rejection in 5G System                      | 7  |

|      |     | 1.3.1 Beamforming                                                 | 7  |

|      |     | 1.3.2 Image Rejection                                             | 8  |

|      | 1.4 | Frequency Synthesizer                                             | 9  |

|      |     | 1.4.1 Direct Analog Synthesizer                                   | 10 |

|      |     | 1.4.2 Direct Digital Synthesizer                                  | 10 |

|      |     | 1.4.3 Phase Locked Loop                                           | 11 |

|      | 1.5 | 90-Degree Phase Shifter                                           | 12 |

|      | 1.6 | Motivation                                                        | 13 |

|      | 1.7 | Objective                                                         | 15 |

| II.  |     | 90-Degree Active RC-CR Phase Shifter                              | 16 |

|      | 2.1 | Introduction                                                      |    |

|      | 2.2 | Conventional RC-CR Phase Shifter                                  | 16 |

|      | 2.3 | Active RC-CR Phase Shifter                                        |    |

|      | 2.4 | Circuit Implementation and Simulation                             |    |

|      | 2.5 | Conclusion                                                        |    |

| III. |     | Dynamic Voltage Comparator                                        | 26 |

|      | 3.1 | Introduction                                                      |    |

|      | 3.2 | Comparator Architecture                                           |    |

|      |     | 3.2.1 Static Comparator                                           |    |

|      |     | 3.2.2 Dynamic Comparator                                          |    |

|      | 3.3 | Conventional Single-Stage Dynamic Comparator                      |    |

|      | 3.4 | <b>Proposed Dynamic Comparator with Clocked Parallel Switches</b> |    |

|      | 3.5 | Simulation Results                                                |    |

|      | 3.6 | Conclusion                                                        |    |

| IV.  |     | Integrated On-line Amplitude Locked Loop Calibration System       |    |

|      | 4.1 | Introduction                                                      |    |

|      | 4.2 | Sub-circuits in Calibration System                                |    |

|      |     | 4.2.1 Peak Detector                                               |    |

|      |     | 4.2.2 Comparator                                                  |    |

|      |     | 4.2.3 Proposed Digital Control Logic                              |    |

|      | 4.2 | 4.2.4 Charge Pump                                                 |    |

|      | 4.3 | Simulation Results                                                |    |

|      | 4.4 | Conclusion                                                        |    |

| V.   |     | Phase-Domain Digital Phase Locked Loop                            |    |

|      | 5.1 | Introduction                                                      | 53 |

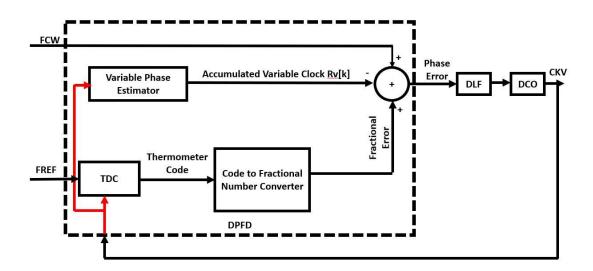

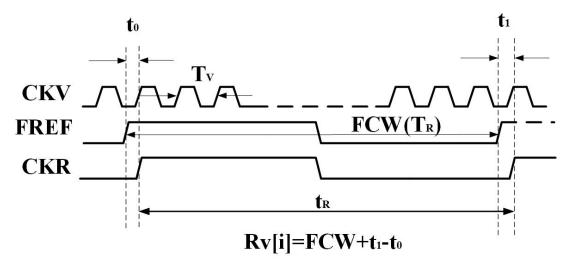

| 5.2        | Pro        | posed Simplified Phase-Domain PLL                              | 57       |

|------------|------------|----------------------------------------------------------------|----------|

| 5.3        | Tim        | ne to Digital Converter                                        | 59       |

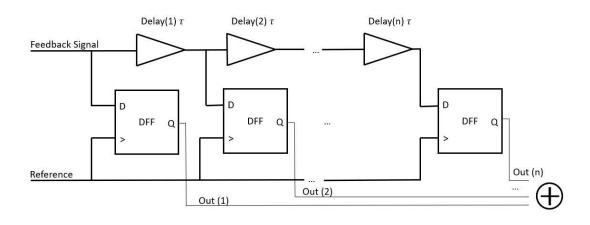

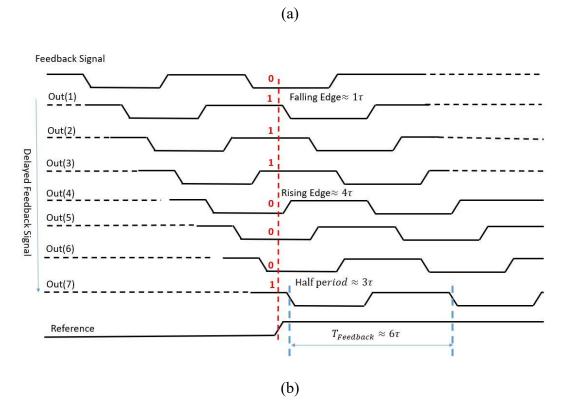

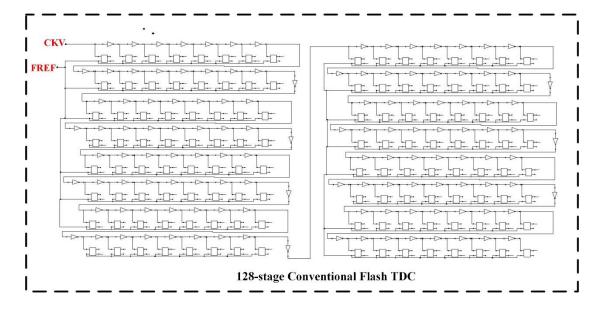

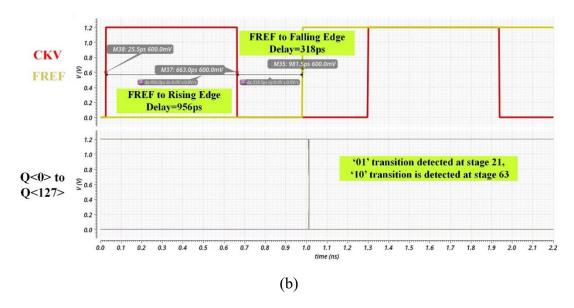

|            | 5.3.1      | Conventional Flash TDC                                         | 60       |

|            | 5.3.2      | Conventional Flash TDC Design of Proposed ADPLL                | 62       |

|            | 5.3.3      | Flash TDC Implementation                                       | 63       |

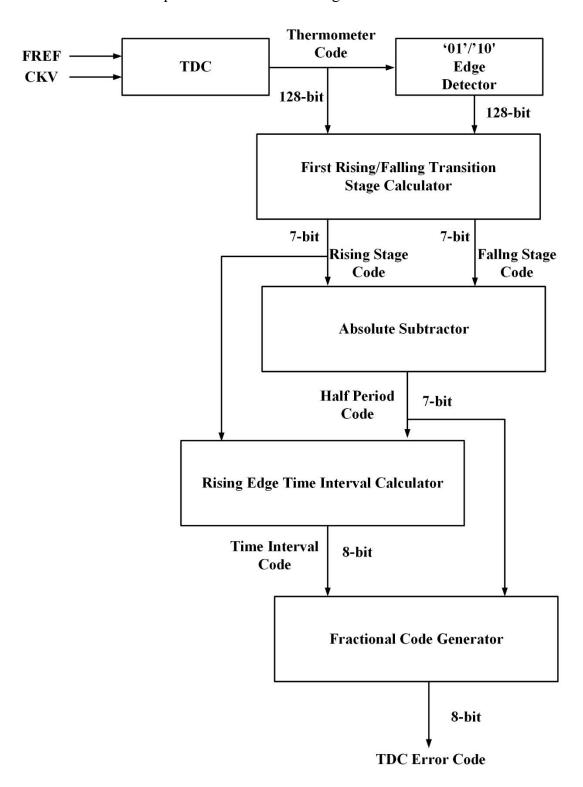

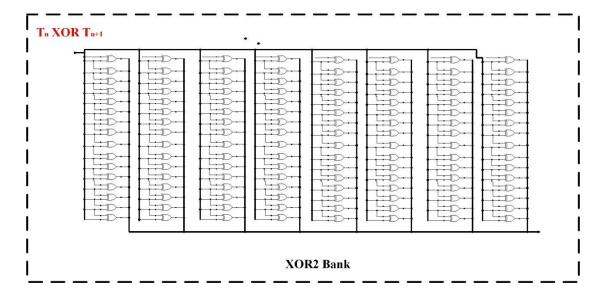

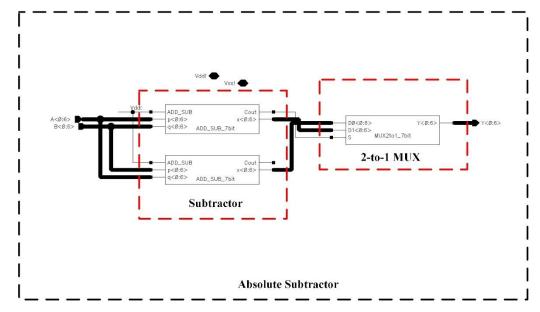

|            | 5.3.4      | Thermometer Code to Fractional Digital Number Conver           | ter65    |

| 5.4        | Sim        | plified Phase Domain Digital Phase Frequency Detector          | 73       |

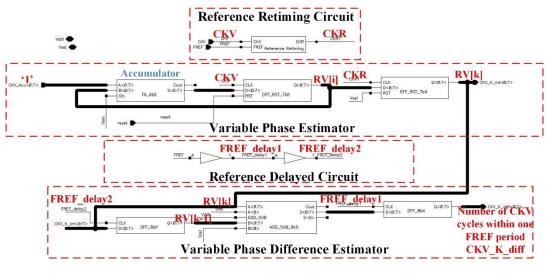

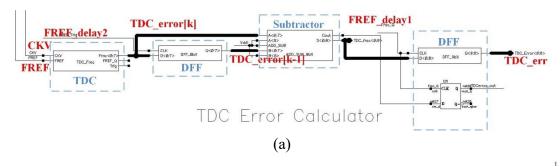

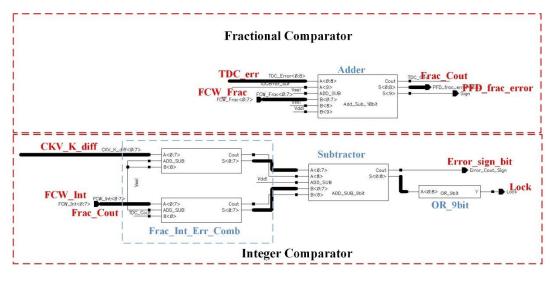

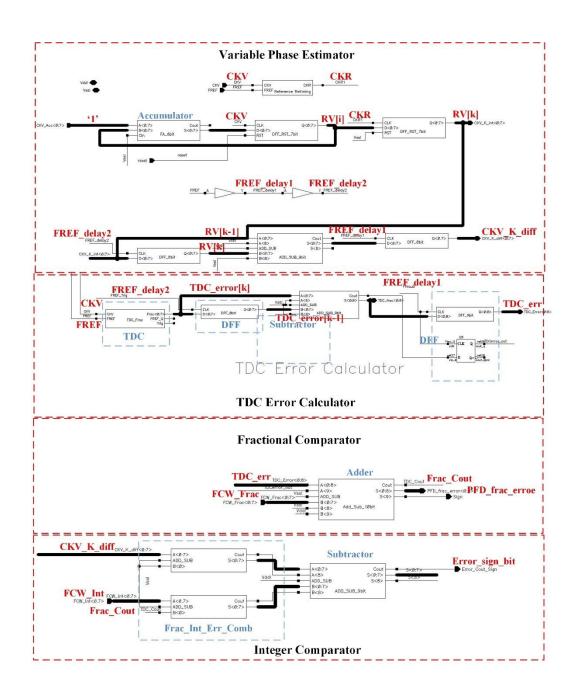

|            | 5.4.1      | <b>Circuit Implementation of Variable Phase Estimator</b>      | 74       |

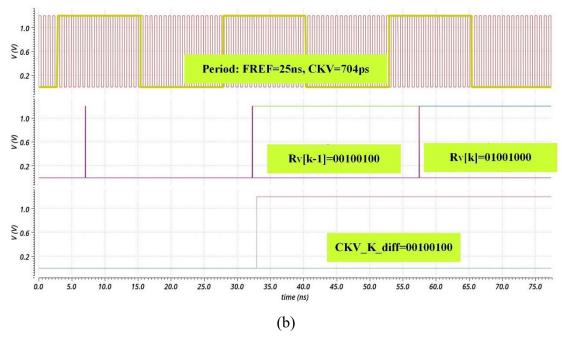

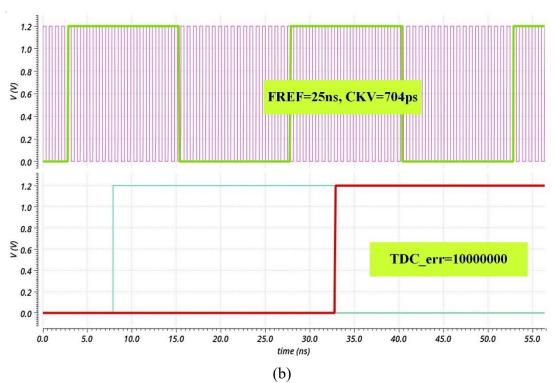

|            | 5.4.2      | Circuit Implementation of TDC Error Calculator                 | 75       |

|            | 5.4.3      | Circuit Implementation of Fractional and Integer               | r Code   |

|            | Comp       | arator                                                         | 77       |

|            | 5.4.4      | <b>Schematic of Proposed Digital Phase Frequency Detector.</b> | 78       |

| 5.5        | Dig        | ital Loop Filter                                               | 79       |

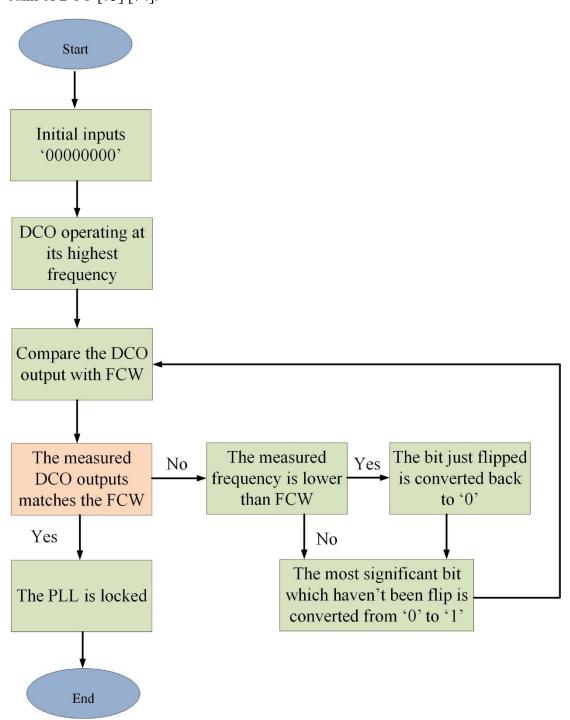

| 5.6        | Dig        | ital Control Oscillator                                        | 83       |

|            | 5.6.1      | Capacitor Bank and Frequency Tuning Range in Conv              | entional |

|            | <b>DCO</b> | 84                                                             |          |

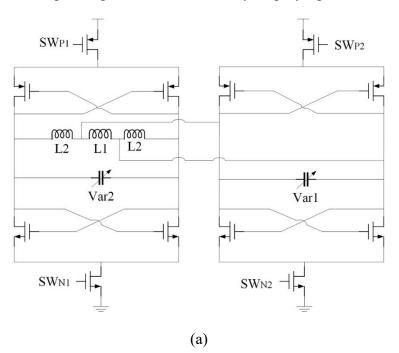

|            | 5.6.2      | Quad-mode DCO                                                  | 85       |

|            | 5.6.3      | Implementation and Simulation of Digital Control Oscilla       | tor87    |

| 5.7        | Imp        | olementation and Simulation of Simplified Phase-Domai          | n Phase  |

| Loc        | ked Lo     | oop                                                            | 96       |

| VI.        | Circuit    | t Implementation and Simulation of Proposed Quadrature         | e Phase- |

| Domain     | ADPL       | L with Integrated On-line Amplitude Locked Loop Calibration    | n System |

|            | 102        |                                                                |          |

| 6.1        | Circ       | cuit implementation and Simulation                             | 102      |

| 6.2        | Con        | nclusion                                                       | 107      |

| VII.       | Conclu     | usion and Future Works                                         | 110      |

| <b>7.1</b> | Con        | ıclusion                                                       | 110      |

| 7.2        | Maj        | jor Contribution                                               | 110      |

| 7.3        | Pub        | olications                                                     | 111      |

| 7.4        | Fut        | ure Work                                                       | 113      |

| Referen    | ces        |                                                                | 114      |

## List of Figure

| Fig | 1.1.1 Standard transceiver system2                                            |

|-----|-------------------------------------------------------------------------------|

| Fig | 1.2.1 "Cell" concept of 5G network3                                           |

| Fig | 1.3.1 Analog beamforming8                                                     |

| Fig | 1.3.2 Hartley architecture9                                                   |

| Fig | 1.4.1 General architecture of receiver front end design11                     |

|     | 1.4.2 Architecture of phase locked loop12                                     |

| Fig | 1.6.1 Top-level block diagram of proposed circuit14                           |

|     | 2.2.1 Conventional 90-degree RC-CR phase shifter17                            |

|     | 2.2.2 Frequency response of conventional RC-CR phase shifter18                |

|     | 2.3.1 Active RC-CR phase shifter18                                            |

| Fig | 2.4.1 Schematic circuit of active RC-CR phase shifter21                       |

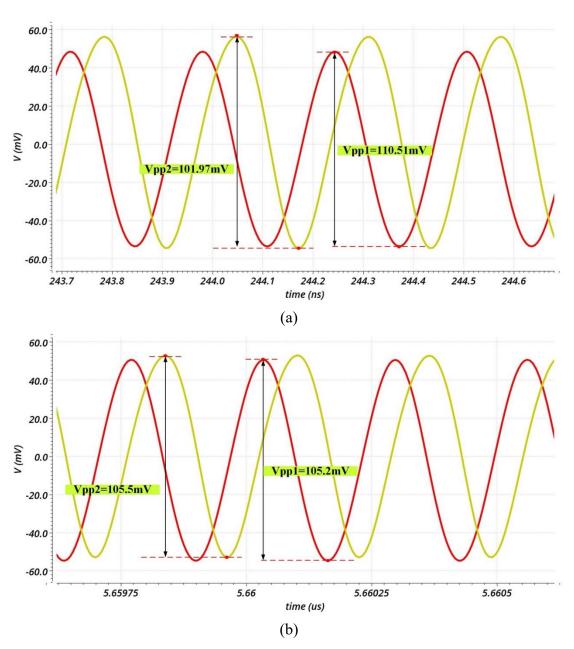

| _   | 2.4.2 Simulation plots (a) Free run outputs with 3.8GHz input frequency (b)   |

| Ü   | Adjusted output signals at 930MHz input frequency (c) Adjusted output         |

|     | signals at 2.4GHz input frequency (d) Adjusted output signals at 3.8GHz23     |

| Fig | 2.5.1 Block diagram of RC-CR phase shifter ALL calibration system25           |

| Fig | 3.2.1 Conventional static comparator27                                        |

| Fig | 3.2.2 Static latched comparator28                                             |

| Fig | 3.2.3 Conventional double-tail dynamic comparator29                           |

| Fig | 3.3.1 Conventional single-stage dynamic comparator30                          |

| Fig | 3.4.1 Proposed dynamic comparator with parallel clocked input switches33      |

| Fig | 3.4.2 Evaluation mode of proposed dynamic comparator34                        |

| Fig | 3.5.1 CMOS implementation of proposed dynamic voltage comparator37            |

| Fig | 3.5.2 Transient simulation of proposed comparator versus conventional         |

|     | comparator37                                                                  |

| Fig | 3.5.3 Transient simulation results with considering process variations: (a)   |

|     | Proposed design for CLK=2GHz (b) Proposed design for CLK=4GHz (c)             |

|     | Conventional design for CLK=500MHz38                                          |

| Fig | 3.5.4 Monte-Carlo simulation results for proposed and conventional dynamic    |

|     | comparator40                                                                  |

| Fig | 4.2.1 Schematic diagram of peak detector42                                    |

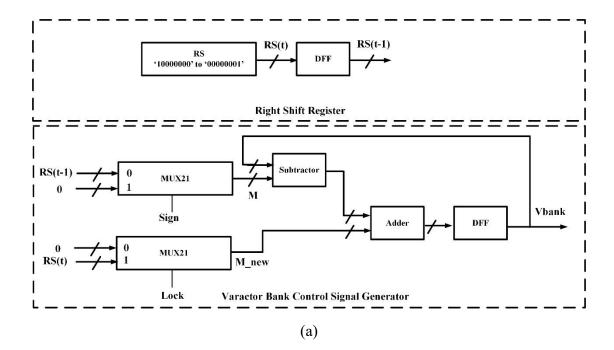

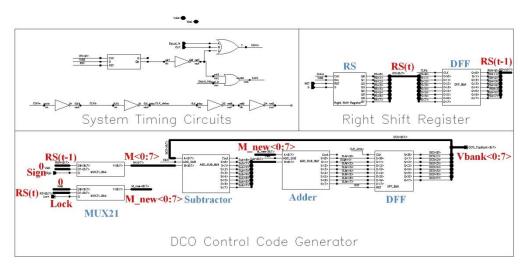

| Fig | 4.2.2 Proposed digital control filter system: (a) System architecture (b)     |

|     | Comparison of transient simulation waveform45                                 |

| Fig | 4.2.3 Schematic diagram of charge pump circuit46                              |

| Fig | 4.3.1 Block diagram of proposed 90-degree active phase shifter with           |

|     | integrated on-line amplitude locked loop calibration47                        |

| Fig | 4.3.2 Schematic diagram of (a) Peak detector (b) Dynamic comparator (c)       |

|     | Digital logic filter (d) Charge pump49                                        |

| Fig | 4.3.3 Transient simulation waveform of proposed 90-degree phase shifter       |

| _   | with on-line ALL calibration system at (a) 600MHz (b) 2.4GHz (c) 3.8GHz 50    |

| Fig | 4.3.4 Transient simulation results of output waveforms (a) Before calibration |

|     | (b) After calibration 51                                                      |

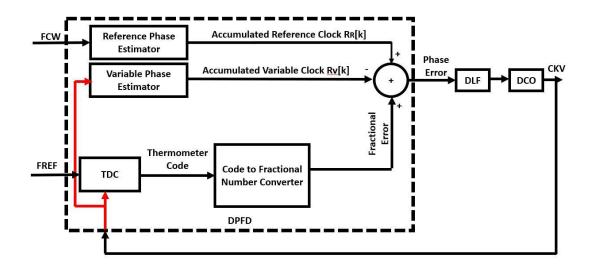

| Fig 5.1.1 Basic model of PLL                                                     | 53  |

|----------------------------------------------------------------------------------|-----|

| Fig 5.1.2 Top level diagram of conventional PD DPLL                              | 56  |

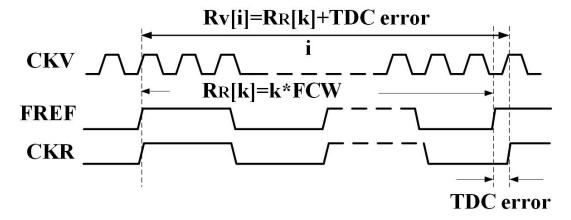

| Fig 5.1.3 Waveform of conventional PDDPLL                                        |     |

| Fig 5.2.1 Top level diagram of proposed simplified phase-domain DPLL             | 57  |

| Fig 5.2.2 Time domain waveform of proposed simplified phase-domain PFD           |     |

| Fig 5.3.1 (a) Conventional flash TDC architecture (b) Thermometer outputs of     |     |

| conventional flash TDC                                                           |     |

| Fig 5.3.2 (a) Circuit implementation of Flash TDC (b) Simulation plots of Flash  | h   |

| TDC                                                                              |     |

| Fig 5.3.3 Design theory of TCFDC                                                 | 66  |

| Fig 5.3.4 Circuit implementation of '01'/'10' edge detector                      | 67  |

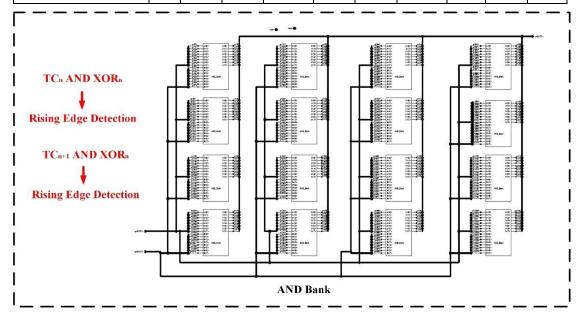

| Fig 5.3.5 Circuit implementation of AND bank                                     | 68  |

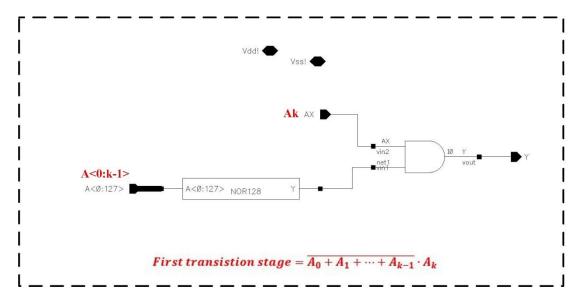

| Fig 5.3.6 Circuit implementation of first transition edge detector               | 69  |

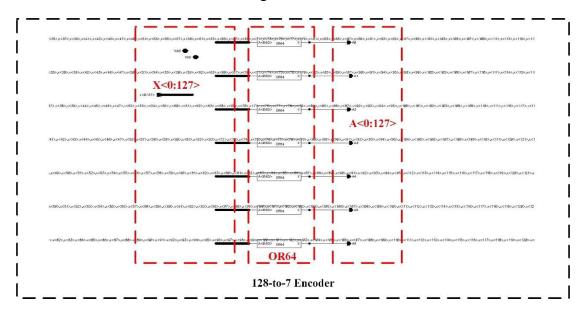

| Fig 5.3.7 Circuit implementation of 128 to 7 encoder                             | 70  |

| Fig 5.3.8 Delay Calculator                                                       | 70  |

| Fig 5.3.9 Fractional code generator                                              | 71  |

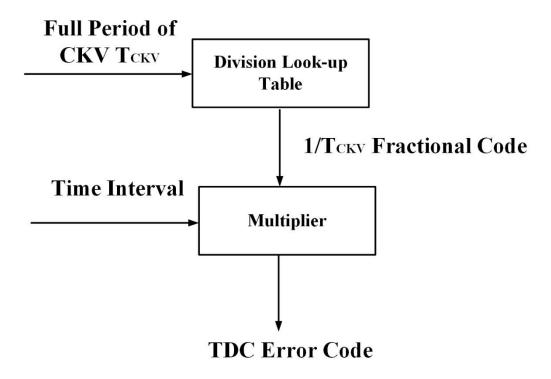

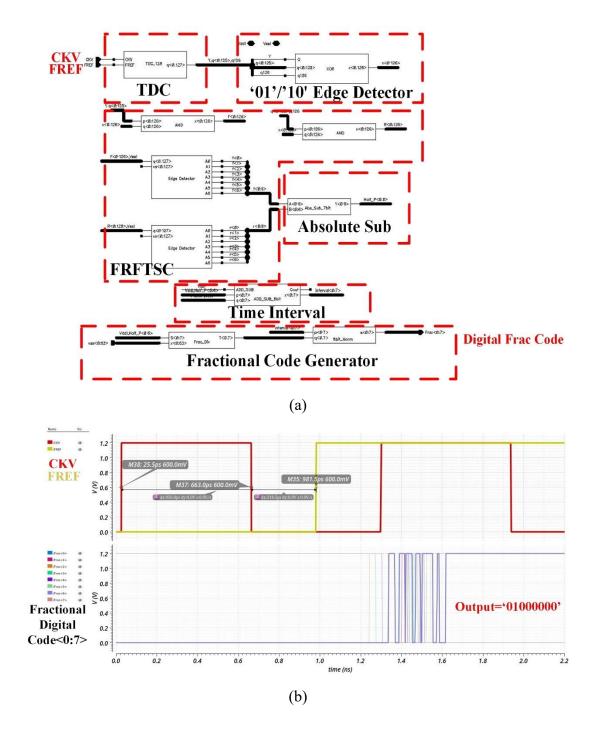

| Fig 5.3.10 TDC error fractional code generator (a) Schematic (b) Simulation      |     |

| waveform                                                                         | 72  |

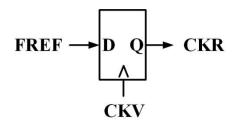

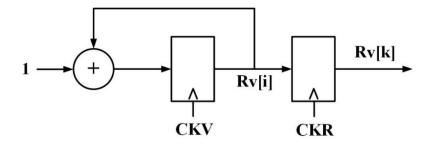

| Fig 5.4.1 Reference retimed circuit                                              | 74  |

| Fig 5.4.2 Hardware implementation of variable phase estimator                    | 74  |

| Fig 5.4.3 (a) Circuit implementation of variable phase estimator (b) Simulation  | n   |

| result of the variable phase estimator                                           | 75  |

| Fig 5.4.4 (a) Schematic of TDC error calculator (b) Simulation result of TDC     |     |

| error calculator                                                                 | 76  |

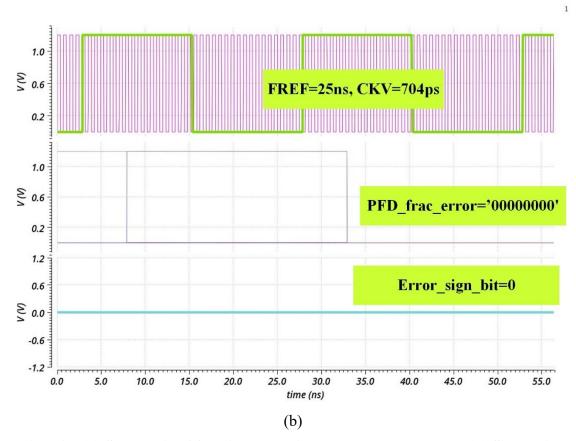

| Fig 5.4.5 (a) Schematic of fractional and integer code comparator (b) Simulation | on  |

| results of fractional and integer combiner                                       |     |

| Fig 5.4.6 Schematic of proposed DPFD                                             | 79  |

| Fig 5.5.1 Flow chart of PEVBC                                                    |     |

| Fig 5.5.2 Circuit implementation of PEVBC                                        | 82  |

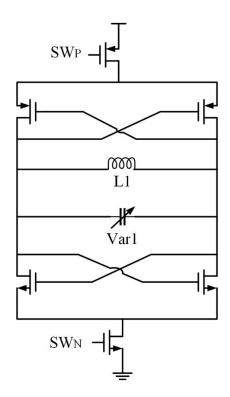

| Fig 5.6.1 Schematic diagram of conventional DCO                                  | 84  |

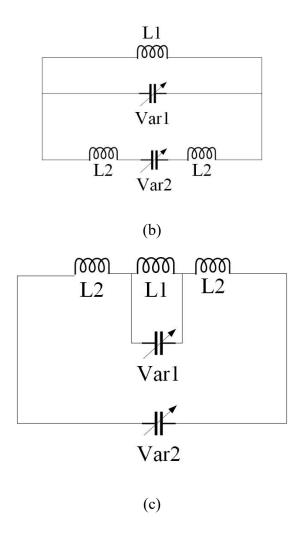

| Fig 5.6.2 (a) Schematic diagram of Quad-DCO (b) Equivalent circuit of            |     |

| Structure I (c) Equivalent circuit of Structure II                               |     |

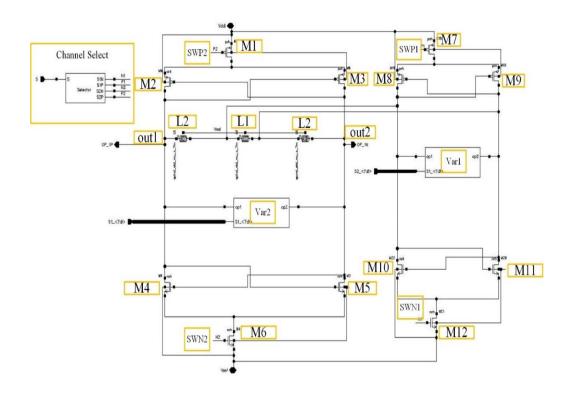

| Fig 5.6.3 Schematic of quad-mode DCO                                             | 88  |

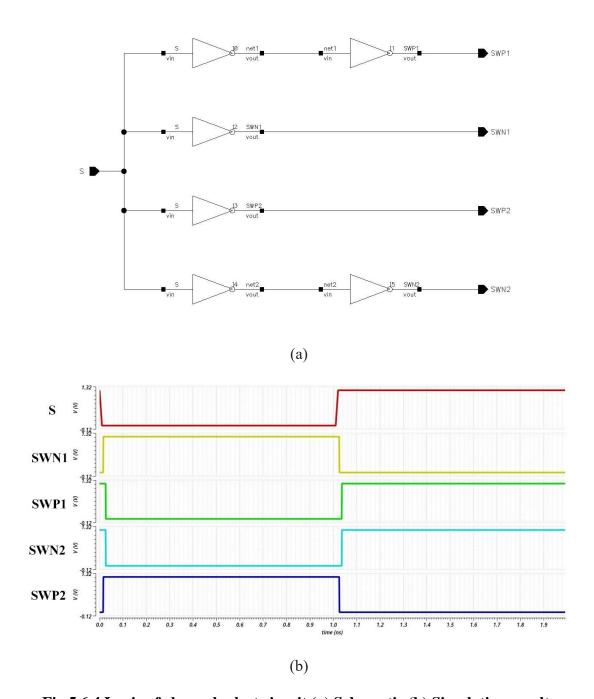

| Fig 5.6.4 Logic of channel select circuit (a) Schematic (b) Simulation results   | 89  |

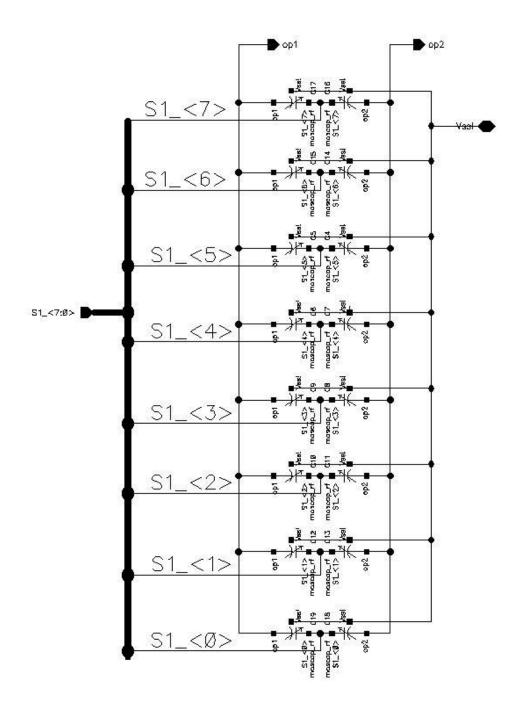

| Fig 5.6.5 Schematic diagram of varactor bank                                     | 90  |

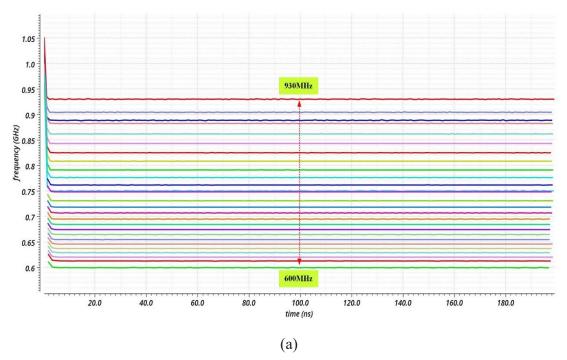

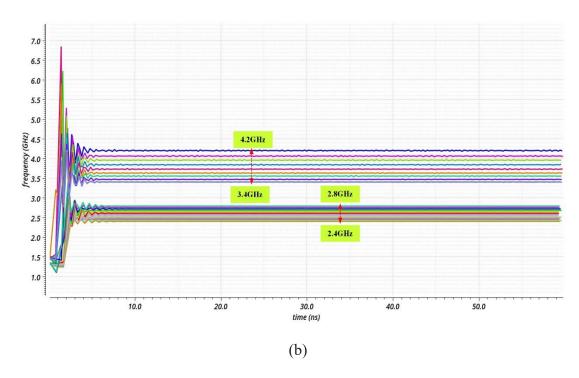

| Fig 5.6.6 Simulation results of frequency response (a) Low band (b) Mid band     | .93 |

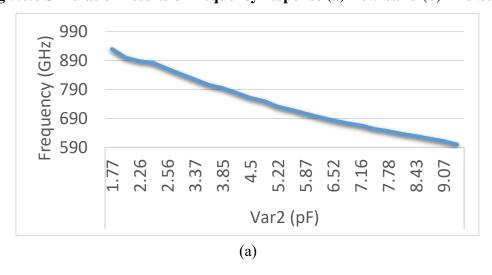

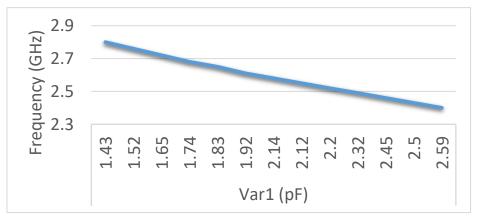

| Fig 5.6.7 Frequency versus varactor plots (a) 600MHz to 930MHz band (b)          |     |

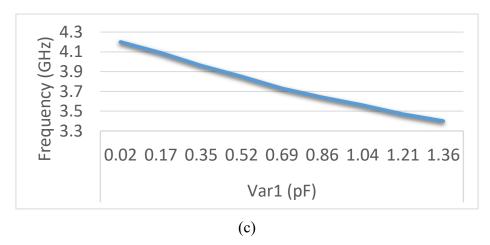

| 2.4GHz to 2.8GHz band (c) 3.4GHz to 4.2GHz band                                  | 94  |

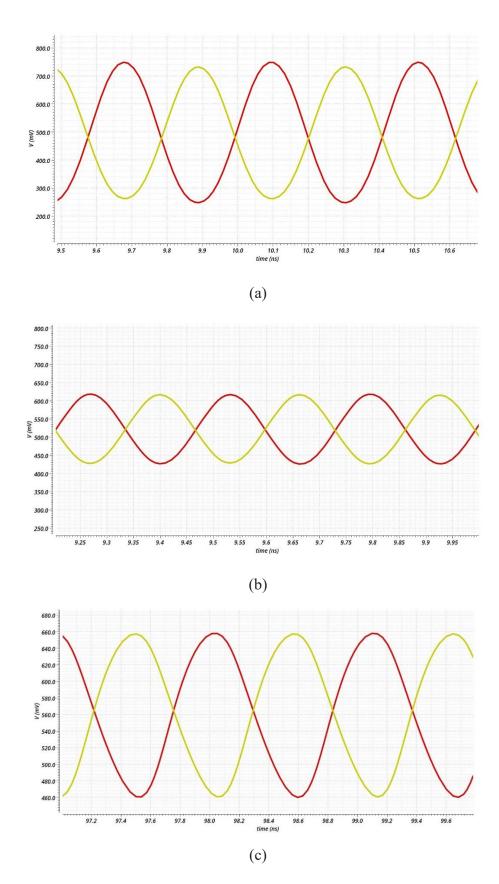

| Fig 5.6.8 Transient simulation results for (a) Structure I at 3.8GHz (b) Structu | re  |

| II at 2.4GHz (c) Structure III at 930MHz                                         |     |

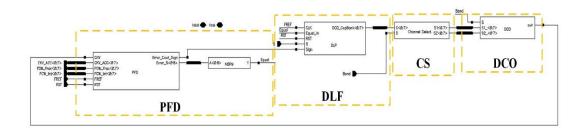

| Fig 5.7.1 Schematic of Proposed Simplified Phase-Domain                          |     |

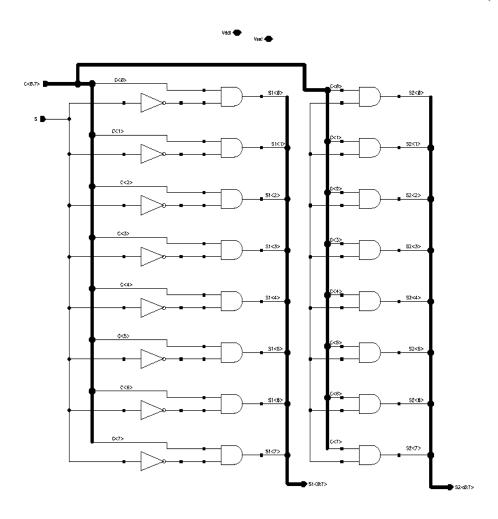

| Fig 5.7.2 Circuit implementation of channel select                               | 97  |

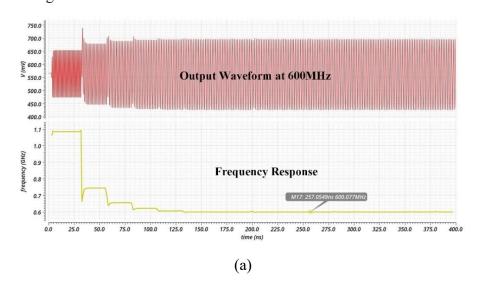

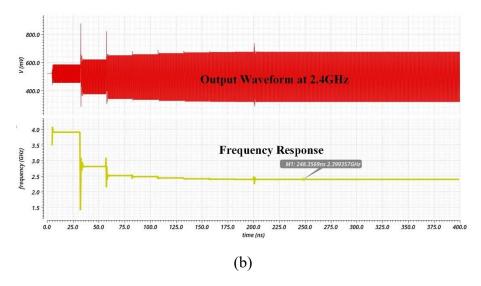

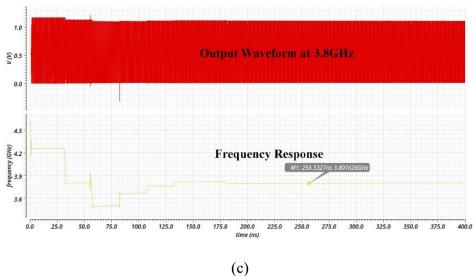

| Fig 5.7.3 Transient simulation for proposed simplified phase-domain PLL (a) a    | at  |

| 600MHz (l       | b) at 2.4GHz (c) at 3.8GHz                            | 99              |

|-----------------|-------------------------------------------------------|-----------------|

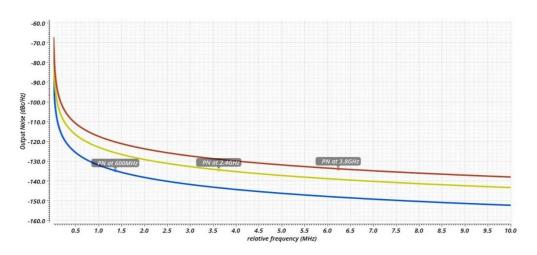

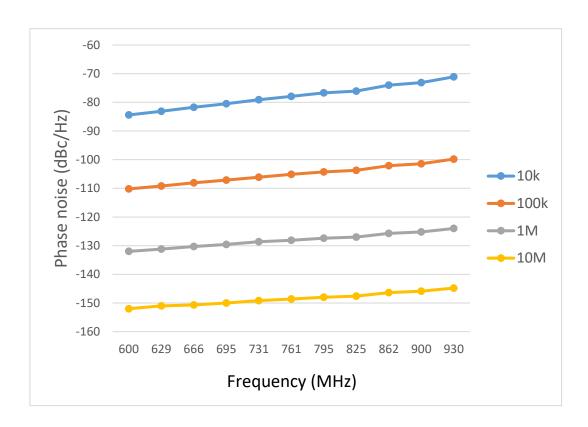

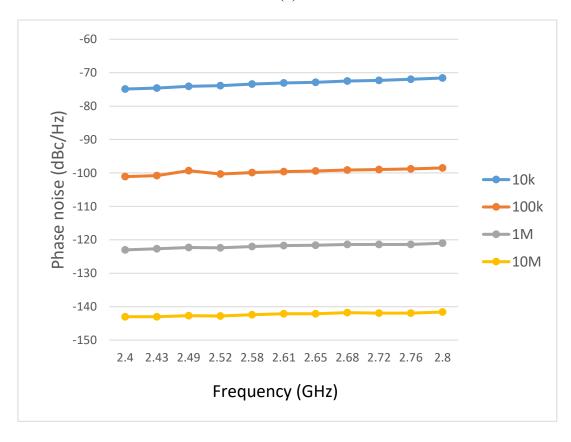

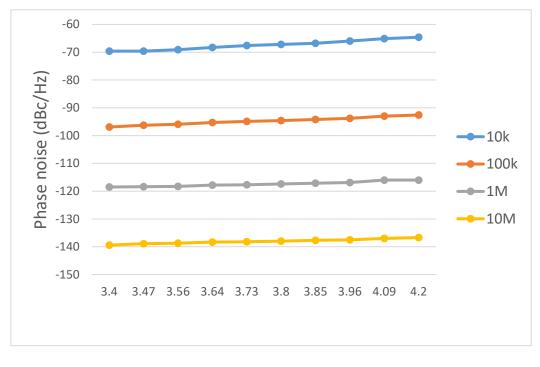

| Fig 5.7.4 Phase | e noise performance of the proposed phase-domain o    | digital PLL (a) |

| Simulation      | n results of the PLL operating at 600MHz, 2.4GHz a    | nd 3.8GHz (b)   |

| PN results      | s for PLL at 600MHz to 930MHz band (c) PN results     | for PLL at      |

| 2.4GHz to       | 2.8GHz (d) PN results for PLL at 3.4 to 4.2GHz        | 101             |

| Fig 6.1.1 Circu | uit implementation of proposed ADPLL with 90-degi     | ee phase        |

| shifter         |                                                       | 103             |

| Fig 6.1.2 Trans | sient simulation results of proposed DPLL with 90-d   | egree phase     |

| shifter (a)     | Frequency at 600MHz (b) Frequency at 2.4GHz (c)       | Frequency at    |

| 3.8GHz (d)      | ) Zoom-in version of transient simulation result at 2 | .4GHz105        |

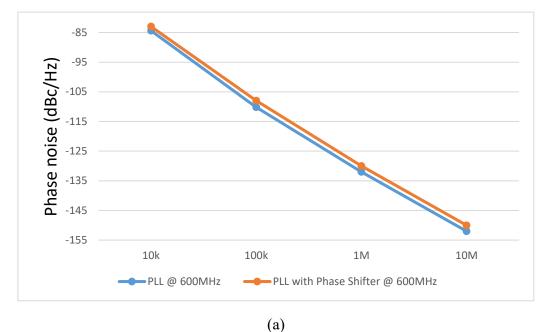

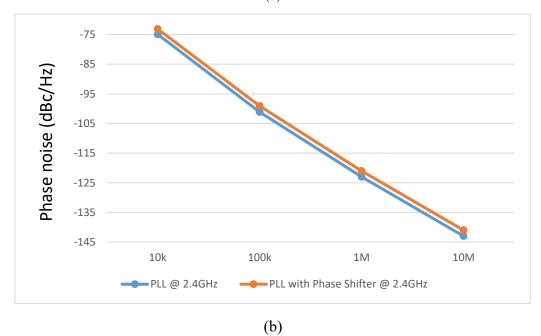

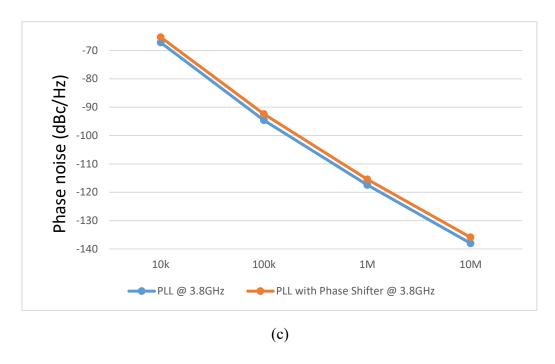

| Fig 6.1.3 Phase | e noise performance of quadrature phase-domain D      | PLL             |

| without/wi      | ith integrated on-line amplitude calibration system ( | (a) at 600MHz   |

| (b) at 2.4G     | GHz (c) at 3.8GHz                                     | 107             |

|                 |                                                       |                 |

## List of Table

| Table 1.2.1 US 5G spectrum [8]                                             | 5      |

|----------------------------------------------------------------------------|--------|

| Table 1.2.2 China 5G spectrum [9]                                          |        |

| Table 1.2.3 France 5G spectrum                                             | 6      |

| Table 1.2.4 United Kingdom 5G spectrum                                     | 6      |

| Table 1.2.5 Japan 5G spectrum                                              | 6      |

| Table 1.2.6 South Korea 5G spectrum                                        |        |

| Table 3.5.1 Transistor Sizes                                               |        |

| Table 3.5.2 Performance comparison of dynamic voltage comparators          | 39     |

| Table 4.2.1 Truth table of digital control filter                          | 45     |

| Table 5.3.1 Design specifications of frequency resolution for proposed ADP | LL .63 |

| Table 5.3.2 TCFDC Look-up Table                                            | 68     |

| Table 5.6.1 Transistor sizes of varactor banks                             | 91     |

| Table 5.6.2 Transistor sizes of quad-DCO                                   | 91     |

| Table 5.6.3 Frequency Resolution of quad-mode DCO                          | 94     |

| Table 5.7.1 Truth Table of Channel Select Circuit                          |        |

| Table 5.7.2 Phase Noise Performance Summary                                | 101    |

| Table 6.1.1 Circuit performance of proposed quadrature DPLL                | 108    |

| Table 6.1.3 Performance comparison of proposed wide band quadrature dis    | gital  |

| PLL with other state of art designs                                        | 108    |

|                                                                            |        |

#### Acknowledgements

First and foremost, I would like to express my sincere gratitude to my dissertation advisor Dr. Saiyu Ren who encourages and helps me during my master and PhD study, and her supports and experience also leads me for my life in the future.

Besides, I would like to offer my special thanks to Dr. Raymond E. Siferd who shares his valuable academic advice and research experience with me in my dissertation and papers.

Additionally, I am deeply grateful to my committee members, Dr. Henry Chen, Dr. Marian K. Kazimierczuk, and Dr. Yan Zhuang for their insightful comments and suggestions, and special thanks to my defense observer, <u>Dr. Travis E. Doom</u> for his kindness and time.

I would also like to thank Wright State University where I pursued both master and doctoral degree, and specially thanks to the Department of Electrical Engineering. I had a wonderful time with the staff and students, and it is their kind help and support that made me have a great time in these 9 years.

Finally, my appreciation goes to my family and friends for their encouragement and support all through my studies. Thanks to my parents for their endless trust and patient who are always my strong backing all through my life. Thanks to my husband and my son for their unparalleled love and tremendous understanding to complete this research work. It is their unconditional trust that makes me to be a strong woman during this beautiful journey.

#### I. Introduction

#### 1.1 Background

5G is short for "5th generation", and in telecommunication, it is the next generation wireless network technology of existing 4th Generation Long-Term Evolution (4G LTE) network [1]. 5G network is expected to provide faster speed, lower latency, and connect more devices compared to current 4G network. Such benefit enables new methods that people live and work [2]. For example, with new 5G technology, the autonomous vehicles can communicate with each other on the road to improve safety and performance. Moreover, the concept of future "Smart City" can be a reality only with the help of 5G technology. Taking the advantages of ultra-low latency and wide bandwidth, almost everything in the city is connected and operated coordinately to reduce the energy consumption and resources efficiency [3] [4] [5].

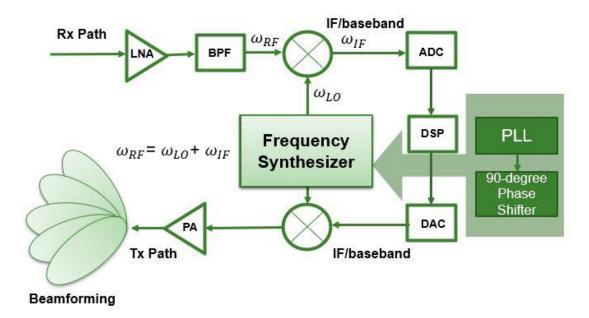

The 5G spectrum are sliced into multiple bands, and each band provides unique features to deliver the overall best performance of 5G network. The operating spectrum of 5G is not uniform across countries, in this case, the transceiver system is very important. As shown in Fig 1.1.1, the standard transceiver system consists of receiving path and transmitting path. The Radio Frequency (RF) signal is down converted into either Intermediate Frequency (IF) signal or baseband signal by a mixer in receiving path. Similarly, the IF or baseband signal is up converted into RF signal through the mixer in transmitting path. The relationship between RF, IF and Local Oscillator (LO) is expressed in (1-1-1):

$$\omega_{RF} = \omega_{IF} + \omega_{LO} \tag{1-1-1}$$

To keep the same Analog to Digital Converter (ADC), Digital to Analog Converter (DAC) and Digital Signal Processor (DSP) in one device, an adjustable and wideband frequency synthesizer is the key.

Fig 1.1.1 Standard transceiver system

This dissertation is focusing on frequency synthesizer design to support different regulations among countries within one device. Usually, it consists of a phase locked loop and a 90-degree phase shifter. The phase locked loop generates accurate frequency signals, and the 90-degree phase shifter provides precise quadrature phases and constant gain. In 5G transceiver system, the 90-degree phase shifter can be used for beamforming and image rejection purpose. A quadrature phase-domain ADPLL with integrated on-line amplitude locked loop calibration system is proposed in this dissertation to meet the 5G multi-band standard.

#### 1.2 5G Spectrum

#### 1.2.1 5G 3-Band Spectrum Architecture

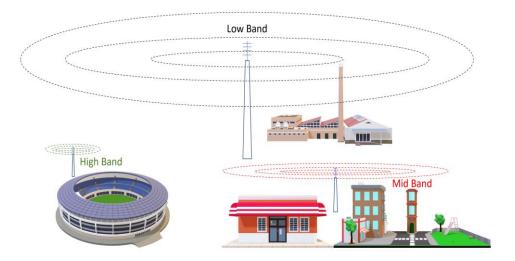

With the consideration of both signal coverage area and performance, most 5G regulations are using 3 bands to support the network. The 5G network is establish under the topology of "Cells", which describes the service area of each base station. As shown in Fig 1.2.1, the largest cell provides the stable connection in wide area, and low band is used for this cell. It can be used in big factories or warehouses to control the machines and robots to realize automation; Mid band is used for middle size cell such as office buildings or schools, which deliver high quality signal within a smaller zone. The ultrasmall cell with high band is designed to allow large number of connection and achieve the highest speed in a compact environment like stadium or shopping mall.

Fig 1.2.1 "Cell" concept of 5G network.

The low band usually is operating below 2 GHz. The advantage of this band is good transmission distance that covers hundreds of square miles service area. Another benefit of this band is the penetration capability of low frequency radio wave, which

provides the connection inside of the building or even basement [6]. Even though this band 5G service offers the slowest peak speed, the data rate is still much faster than current 4G LTE common speed.

The mid band spectrum takes 2 to 6 GHz frequency band to enable larger bandwidth than the low band. Such frequency range is currently used by 2G, 3G, and 4G services, which will be re-used by 5G in the future. The mid band is expected to serve the most of user as it carries plenty of data with descent covered area (several-mile radiuses coverage). The peak speed of this band is 600 - 700 Mbps in US currently and can go up to 2 Gbps in China, Korean, and other countries. Many carriers and chip makers recognize this band as the optimal point in terms of cost, coverage, quality, and latency [7].

The high band of 5G system uses millimeter Wave (mmWave) signal as the carrier to transfer data. The spectrum of this band is above 24 GHz that can easily provide very large channel bandwidth to achieve high-speed data transmission. Even though the signal at this frequency band suffers a huge path loss referring to (1-2-1), where d is the path distance, f is signal frequency and c is speed of light, the incredible data rate still enables the future of many applications in industry and daily life.

$$P_{Path\ Loss} = \left(\frac{4\pi * d * f}{c}\right)^2 \tag{1-2-1}$$

#### 1.2.2 5G Spectrum Allocations

As describe in the section 1.2.1, most of the 5G spectrum are sliced into multiple bands to work jointly. Each band provides unique features to provide the overall

performance of 5G system.

Just like previous generations of communication bands, the operating spectrum is not uniform across countries. In the following content of this section, the 5G spectrum of several countries is listed in the tables below. Some bands have already been auctioned or licensed, and others are in the auction process or under serious consideration.

Table 1.2.1 US 5G spectrum [8]

| Band      | Frequency (GHz)      |

|-----------|----------------------|

| Low-Band  | 0.6 (Upcoming)       |

|           | 0.8 (Upcoming)       |

|           | 0.9 (Upcoming)       |

| Mid-Band  | 2.5 (Upcoming)       |

|           | 3.5 (Upcoming)       |

|           | 3.7 – 4.2 (Upcoming) |

| High-Band | 24                   |

|           | 28                   |

|           | 37                   |

|           | 39                   |

|           | 47                   |

Table 1.2.2 China 5G spectrum [9]

| Band     | Frequency (GHz) |

|----------|-----------------|

| Low-Band | 0.7             |

|          | 2.515 – 2.675   |

| Mid-Band | 3.4 – 3.5       |

| Mid-Band | 3.5 – 3.6       |

|          | 4.8 – 4.9       |

| High-Band | 24.75 – 27.5 (Upcoming) |

|-----------|-------------------------|

|           | 37 – 40 (Upcoming)      |

|           | 3 – 42.5 (Upcoming)     |

**Table 1.2.3 France 5G spectrum**

| Band      | Frequency (GHz)       |

|-----------|-----------------------|

| Mid-Band  | 3.4 - 3.8             |

| High-Band | 3.2 – 27.5 (Upcoming) |

Table 1.2.4 United Kingdom 5G spectrum

| Band      | Frequency (GHz)       |

|-----------|-----------------------|

| Mid-Band  | 3.4 – 3.6             |

|           | 3.6 – 3.8 (Upcoming)  |

| High-Band | 3.2 – 27.5 (Upcoming) |

Table 1.2.5 Japan 5G spectrum

| Band      | Frequency (GHz)        |

|-----------|------------------------|

| Mid-Band  | 3.6 – 3.7              |

|           | 3.7 – 3.8              |

|           | 3.8 – 3.9              |

|           | 3.9 – 4                |

|           | 4 – 4.1                |

|           | 4.5 – 4.6              |

| High-Band | 27 – 27.4              |

|           | 27.4 – 27.8            |

|           | 27.8 – 28.2            |

|           | 28.3 – 29.1 (Upcoming) |

Table 1.2.6 South Korea 5G spectrum

| Band      | Frequency (GHz) |

|-----------|-----------------|

| Mid-Band  | 3.42 – 3.5      |

|           | 3.5 – 3.6       |

|           | 3.6 – 3.7       |

|           | 4.5 – 4.6       |

| High-Band | 26.5 – 27.3     |

|           | 27.3 – 28.1     |

|           | 28.1 – 28.9     |

#### 1.3 Beamforming and Image Rejection in 5G System

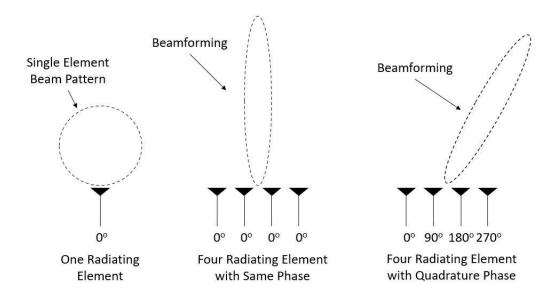

To deliver the best performance of 5G network, many technologies are used in both analog and digital domain. On carrier side, two main techniques help improve the signal quality and they are beamforming and image rejection. Both techniques require multi-phase feature of carrier generator.

#### 1.3.1 Beamforming

Beamforming is widely used in RF phase array design to narrow the transmission beam in certain angle. Every antenna in the array is connected with a phase shifter which can steer the phase of feeding signal. As shown in Fig 1.3.1, the signal emitting from each antenna is constructed to a new beam pattern based on the phase difference between transmitters. Using such technique in 5G system, multiple users can connect to base-station simultaneously with better quality of communication.

Fig 1.3.1 Analog beamforming

#### 1.3.2 Image Rejection

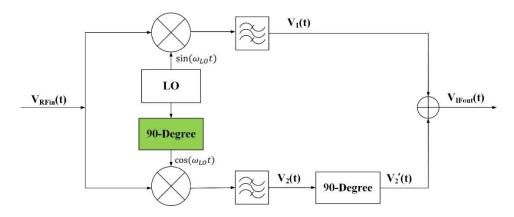

For RF transceiver design, Low-IF baseband architecture has the advantages of high integration, less passive components and low flicker noise properties compared with high-IF Heterodyne and Zero-IF receivers [10] [11] [12]. In a low-IF receiver, the desired radio frequency signal is down-converted to intermediate frequency by a mixer. There is an RF image signal (offset from the desired RF signal) that is down converted to the same IF frequency as the desired RF signal causing interference noise in the IF bandwidth. The noise cannot be filtered out at the IF section and it degrades the wanted signal quality. To reject the image signal with front-end design and reduce the high-level interference effect, the Hartley system is widely studied based on phase cancellation methodology [12]. The key circuit element in Hartley system is the 90-degree phase shifter after local oscillator as shown in Fig 1.3.2. The desired signal is preserved, and image signal is suppressed if the phase shifter generates a precise quadrature phase and matched gain across the entire operating bands. However, the

power of the image signal with respect to the desired tone becomes worse with the imbalance of gain and phase of I/Q (in phase and quadrature) signals, resulting in degradation of the Signal to Noise Ratio (SNR) in the receiver system. There is approximately a 40dB loss in SNR for 1-4 degree phase mismatch or 0.2-0.6dB gain imbalance [13] [14]. Therefore, the frequency synthesizer in 5G system should be featured with quadrature phase and high accuracy phase shifting over wide frequency range to cover as many spectrum bands as possible.

Fig 1.3.2 Hartley architecture

#### 1.4 Frequency Synthesizer

In RF transceiver system, frequency synthesizer is a key component to dominant system noise performance. It should generate precise signals with high spectral purity. The signal generator block not only oscillate at carrier frequency with channel spacing resolution but also translate into baseband clock frequency for DSP. Phase Noise (PN) is a particularly important property for frequency synthesizer. Excessive phase noise can create channel-to-channel interference, and the higher PN will increase the noise floor and degrades SNR so that the ADC performance is limited [15]. Besides, high resolution of channel spacing is also demanded in wireless communication because of the high customer density in limited bandwidth. Thirdly, a wide bandwidth or multiple

bands are desired in portable wireless devices to meet the Federal Communication Commission (FCC) arrangement for different applications. Meanwhile, the response/locking time is another important property, which represents the efficiency of the frequency synthesizer, and a fast speed is needed in transceiver system. In other words, the design of frequency synthesizer for portable wireless devices becomes challenging because of the tradeoffs of phase noise, frequency resolution, response time, bandwidth, circuit size and power consumption.

The frequency synthesizer can be divided into three categories: Direct Analog Synthesizer (DAS), Direct Digital Synthesizer (DDS) and indirect or Phase Locked Loop (PLL). Usually, there are three kinds of PLLs, which are All Analog PLL (AAPLL), All Digital PLL (ADPLL) and hybrid PLL (combination of both analog and digital circuit). The definition of each category is discussed as followed.

#### 1.4.1 Direct Analog Synthesizer

Direct analog synthesizer is a way to use mixing, frequency multiplication and abundant of filters to generate the desired frequency from one stable signal source with good phase noise performance [16]. However, it is not widely used in frequency synthesizer design due to the poor phase noise performance.

#### 1.4.2 Direct Digital Synthesizer

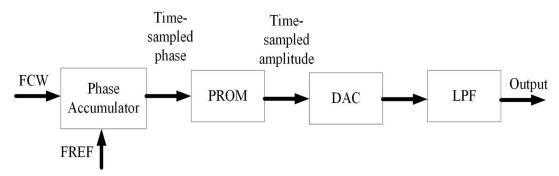

Direct digital synthesizer is using digital control words to control system generating desired frequency from reference digitally. Basically, a DDS is formed by phase accumulator, phase to amplitude converter, DAC and Low Pass Filter (LPF). As shown in Fig 1.4.1, the phase accumulator is controlled by the Frequency Control Word (FCW), and it is sampled by reference clock to construct the time-sampled phase. A

Programmable Read Only Memory (PROM) is the next stage of the synthesizer, where stores the phase information of the sinewave, and the memory is regarded as the lookup table to generate the desired phase based on the phase accumulator outputs. The digitized output from the memory is processed by a DAC followed by an LPF to realize the analog output signal [16] [17].

Fig 1.4.1 General architecture of DDS

#### 1.4.3 Phase Locked Loop

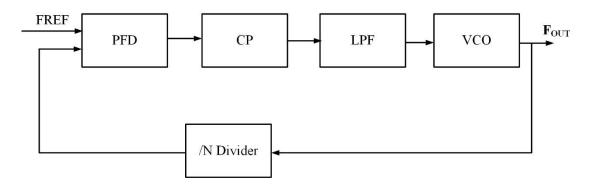

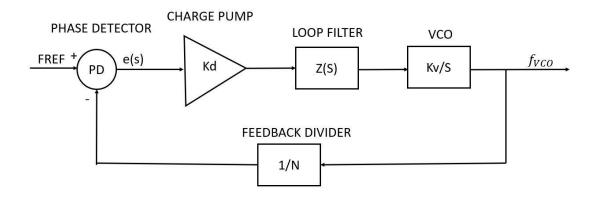

A phase locked loop generates stable high frequencies from fixed low frequency reference, and it is widely used in data recovery, coherent demodulation, bit synchronization, etc. [18] [19]. As described in Fig. 1.4.2, it consists of a Voltage Control Oscillator (VCO), divider, Phase Frequency Detector (PFD), Charge Pump (CP) and Loop Filter (LF). There are three operating states for a PLL, and they are frequency free running, comparing and locking. Initially, the oscillator is oscillating at its natural frequency. Then, the loop is closed, and the feedback frequency is comparing and adjusting to make it equal to reference frequency. The phase error will be eliminated at the matched point. It can be implemented in either an analog intensive or digitally intensive. The PLLs can also be categorized in fractional-N or integer-N operations based on its frequency resolution.

Among these different kinds of frequency synthesizers, PLL is mostly used in wireless transceivers than the first and second types. The DDS sometimes can be used as the reference to replace crystal oscillator reference, but the penalty is the complexity of the circuit implementation. The PLL architecture is employed for the multi-band 5G frequency synthesizer, and a detailed architecture of phase locked loop will be introduced in this chapter.

Fig 1.4.2 Architecture of phase locked loop

#### 1.5 90-Degree Phase Shifter

For 5G wireless communication, beam forming technique is widely used to transmit and process more useful information, which requires quadrature phases of the carrier signal. Ring oscillator has the advantage of generating multiple phases [20], but the poor phase noise performance is the limitation for 5G applications. LC tank oscillator is a good candidate to generate signals for 5G standard with low phase noise [21], however, only a pair of differential outputs is generated by the LC tank. Therefore, a phase shifter block is needed after the LO circuit to generate the quadrature phase as described in Fig 1.3.2.

There are many approaches to phase shifter designs for transceiver sub-systems; e.g. Gilbert mixer in the quadrature signal generator and image rejection for the dual band low IF application [12], phase selector circuit for a phased array beamforming

system application [22] [23], and differential scheme in the VCO/phase locked loop application [24]. The passive RC-CR phase shifter is a good candidate for narrowband I/Q generator since it achieves the 90-degree phase difference outputs at all frequencies [25] and the gain of the I and Q are matched at the pole frequency  $(f_P = 1/2\pi RC)$ . Acceptable IMMRs are achieved for narrow bands near the pole frequency, but output gain matching degrades at frequencies away from the pole frequency, so additional techniques are needed for wideband applications. A polyphase filter can be employed to increase the accuracy of the passive RC-CR phase shifter over a wide bandwidth; however, multiple stages increase the design complexity [12] [26]. Other designs using capacitor bank achieves good Image Rejection Ratio (IMRR) compensation with the penalty of increasing layout size [27]. A hardware calibration system coupled with an active RC-CR phase shifter is proposed in this paper to generate quadrature output after the phase lock loop. The objective is the reduction of image interference with high quality IMRR resulting in enhanced quality of the desired signal while maintaining low circuit complexity. Pole frequencies are adjusted and monitored by a feedback loop, and precise phase and gain are realized within a wide frequency band in this proposed architecture.

#### 1.6 Motivation

With the advantages of the faster speed, higher volume of customers, and wider bandwidth, the 5G network has a promising prospect of Internet-of-Things (IoTs). This new generation of communication also enables the full potential of smart city, telehealth, and autonomous driving.

However, the spectrum allocations currently are varied in different countries. To satisfy the protocols and regulations with one single electric device, a CMOS wideband

or multi-band phase locked loop is preferred. Meanwhile, the phase shifter circuit is a key component in 5G beamforming and image rejection techniques. An integrated wideband and high accuracy 90-degree phase shifter is also desired.

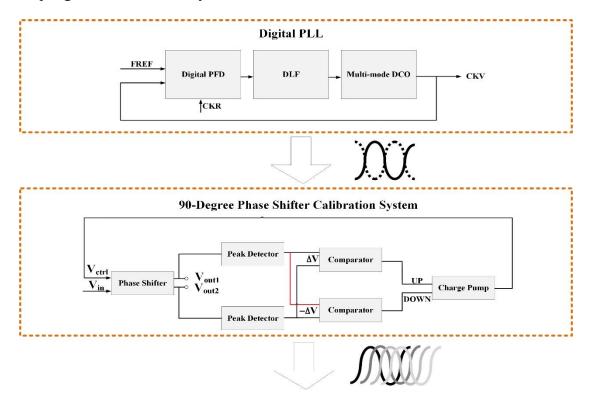

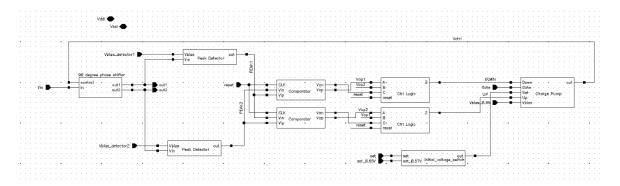

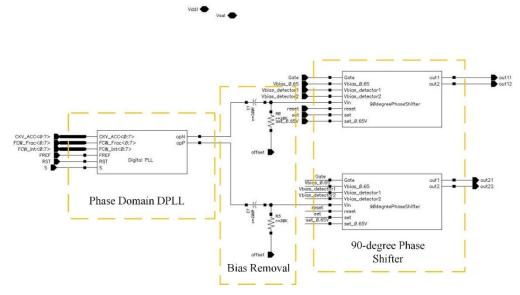

The top-level block diagram of proposed circuit is shown in Fig 1.6.1. In order to meet the frequency synthesizer requirement for 5G network, a multiple band highly programmable and fine resolution all digital PLL is implemented in this dissertation. Meanwhile, a multiband (600MHz-930MHz, 2.4GHz-2.8GHz and 3.4GHz-4.2GHz) active 90-degree RC-CR phase shifter is also designed after the PLL stage, followed with integrated on-line amplitude locked loop calibration system to provide constant output gain for transceiver system.

Fig 1.6.1 Top-level block diagram of proposed multi-band quadrature phasedomain DPLL with ALL calibration system

#### 1.7 Objective

- Design a wideband 90-degree phase shifter which can be used after the LC tank oscillator to generate quadrature phase for 5G beamforming and image rejection purpose.

- Design a hardware integrated on-line amplitude locked loop calibration system for active RC-CR phase shifter to reduce the image interference with high quality IMRR resulting in enhanced quality of desired signal while maintaining low circuit complexity.

- Design a digital phase locked loop that can operate with multiple bandwidths for 5G standard.

- Design and simulate the digital PLL with active RC-CR phase shifter circuit in 65nm technology.

#### II. 90-Degree Active RC-CR Phase Shifter

(The discussion in the following chapter is substantially drawn from [28], where we first reported the development and evaluation of this technique.)

#### 2.1 Introduction

For the purpose of beamforming and image rejection in 5G communication network, quadrature phase is needed at the frequency synthesizer output over multiple frequency bands (600MHz-930MHz, 2.4GHz-2.9GHz and 3.4GHz-4.2GHz). In transceiver system, the desired signal is preserved, and image signal is suppressed if the phase shifter generates a precise quadrature phase and matched gain across the entire operating bands. However, the power of the image signal with respect to the desired tone becomes worse with the imbalance of gain and phase of I/Q (in phase and quadrature) signals, resulting in degradation of the SNR in the receiver system. There is approximately a 40dB loss in SNR for 1-4 degree phase mismatch or 0.2-0.6dB gain imbalance [29] [30].

The passive RC-CR phase shifter generates the required two quadrature outputs with an accurate 90-degree phase shift over the required bandwidth but lack the required accuracy in amplitude matching. In this chapter, a wide band active 90-degree RC-CR phase shifter is proposed to improve the IMRR performance.

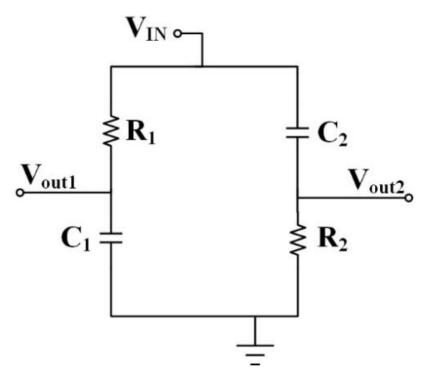

#### 2.2 Conventional RC-CR Phase Shifter

As shown in Fig 2.2.1, a conventional RC-CR phase shifter consists of two identical capacitors and resistors, which forms a pair of parallel high-pass and low-pass filters with the same pole frequency. The outputs  $(V_{out1} \text{ and } V_{out2})$  and their equivalent

phases are expressed in (2-2-1) to (2-2-3). According to these equations, the phase differences between I and Q paths are equal to 90 degree and are independent of frequencies.

$$V_{out1} = \frac{j\omega RC}{1+j\omega RC} \cdot V_{in} \Rightarrow \angle V_{out1} = \frac{\pi}{2} - \tan^{-1}(\omega RC)$$

(2-2-1)

$$V_{out2} = \frac{1}{1 + j\omega RC} \cdot V_{in} \Rightarrow \angle V_{out2} = -\tan^{-1}(\omega RC)$$

(2-2-2)

$$\angle V_{out} = \angle V_{out1} - \angle V_{out2} = \frac{\pi}{2}$$

(2-2-3)

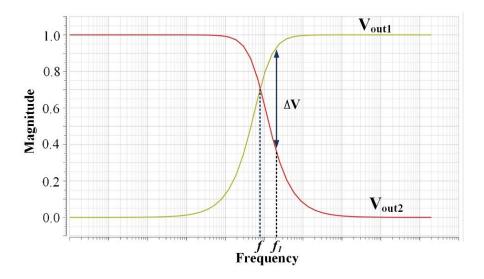

However, the amplitudes of  $V_{out1}$  and  $V_{out2}$  are equal only at the pole frequency in (2-2-4) as shown in Fig 2.2.2. In this case, the wideband performance of conventional RC-CR phase shifter is limited by the passive resistors and capacitors.

$$f_P = \frac{1}{2\pi R_1 C_1} = \frac{1}{2\pi R_2 C_2} \tag{2-2-4}$$

Fig 2.2.1 Conventional 90-degree RC-CR phase shifter

Fig 2.2.2 Frequency response of conventional RC-CR phase shifter

#### 2.3 Active RC-CR Phase Shifter

Fig 2.3.1 Active RC-CR phase shifter

As explained in Fig 2.2.2, gain mismatch ( $\Delta V$ ) happens when input frequency varies from the pole frequency, and the gain error increases with deviation of the

operating frequency from the pole frequency. As a result, the image rejection performance is not guaranteed within the required input bandwidth.

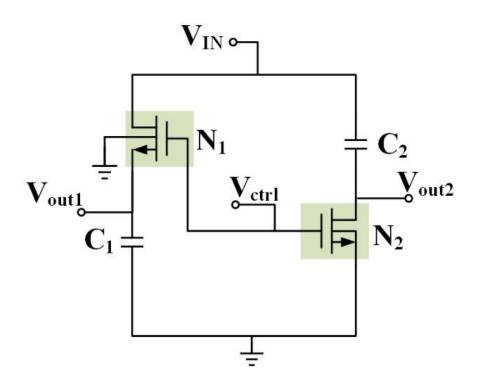

An active RC-CR 90-degree phase shifter is proposed in this section (Fig 2.3.1), where the passive resistors are replaced by active resistors with controllable gate voltage  $(V_{ctrl})$ . The output amplitudes are forced to be equal, then  $R_1C_1 = R_2C_2 = 1/(2\pi f_P)$ , and the 90-degree phase differential is obtained with equality of the RC products.

A second issue is post fabrication process variation which varies the components parameter from the designed value. Such variation on R1, C1, R2, and C2 potentially results in both gain and phase error on phase shifter outputs at any input frequency.

Thus, to design a wideband 90° phase shifter with constant gain, the pole frequency of the two paths should be aligned as the input frequency varies over the required bandwidth and considering process variation effects on the resistor/capacitor pairs. The proposed active RC-CR 90-degree phase shifter in Fig 2.3.1 is used to keep the magnitudes of Vout1 and Vout2 equal over the bandwidth and considering post fabrication circuit value variation due to process variation. The capacitors C1 and C2 are designed with a fixed value. Since C1 and C2 are designed with symmetry and are close together on the chip layout, the difference of their value for given fabrication run is very small [31] [32]. The proposed design facilitates adjusting the resistor values equally to obtain equal output amplitudes under the assumption that with careful design layout procedures the magnitudes of the C1 and C2 remain essentially equal.

When a CMOS transistor is in triode mode, the drain to source current  $I_D$  is estimated by (2-3-1):

$$I_D = \beta (V_{GS} - V_T) V_{DS} \tag{2-3-1}$$

Where  $\beta$ =k(W/L) and k is the process gain factor. W and L describe the width and length of a transistor and  $V_T$  is the threshold voltage. Note that the gate-to-source voltage  $V_{GS}$  must be greater than  $V_T$  to allow  $I_D$  flowing through transistor and to operate in liner region; also, the drain-to-source voltage  $V_{DS}$  needs to be smaller than  $(V_{GS}-V_T)$ .

Thus, the equivalent resistance  $R_{ON}$  is expressed in (2-3-2).

$$R_{ON} = \frac{V_{DS}}{I_D} = \frac{1}{\beta(V_{GS} - V_T)}$$

(2-3-2)

So  $R_1$  and  $R_2$  are expressed as (2-3-3) and (2-3-4):

$$R_1 = \frac{1}{\beta(V_G - V_{out1} - V_T)} \tag{2-3-3}$$

$$R_2 = \frac{1}{\beta(V_G - V_T)} \tag{2-3-4}$$

In the proposed design, an input frequency range of 600MHz to 3.8GHz is needed to meet 5G network requirement. A set of 130fF capacitor is used for the lower frequency band (600MHz to 930MHz) and two 40fF capacitors are used for higher frequency band (2.4GHz to 4.2GHz). With the input frequency varying from 600MHz to 3.8GHz, the gate voltage of  $N_1$  and  $N_2$  can be adjusted over a certain range to vary the active resistance. Note that  $V_{in}$  is a sine wave with a relatively small magnitude (about 0.1V) and no offset (mean value=0V).  $V_{out1}$  and  $V_{out2}$  are sine wave with almost equal small magnitudes, zero mean, and almost 90-degree phase difference. The drain of  $N_1$  is connected to the input sine wave and the source is the output sine wave with 45-degree relative to input, and the source is grounded. The mean value of the drains and sources are zero for both transistors. With the gate of both  $N_1$  and  $N_2$  converging

to a constant DC value, both  $N_1$  and  $N_2$  assume a resistance value associated with the zero mean of their source and drain. In this case, the wide band active RC-CR phase shifter is realized by adjusting the gate voltage of  $N_1$  and  $N_2$  based on  $R_{ON}$  being inversely proportional to  $V_{GS}$ .

#### 2.4 Circuit Implementation and Simulation

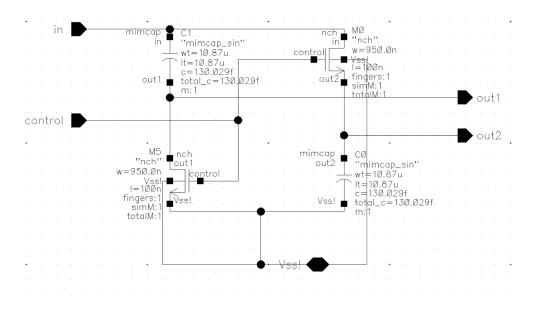

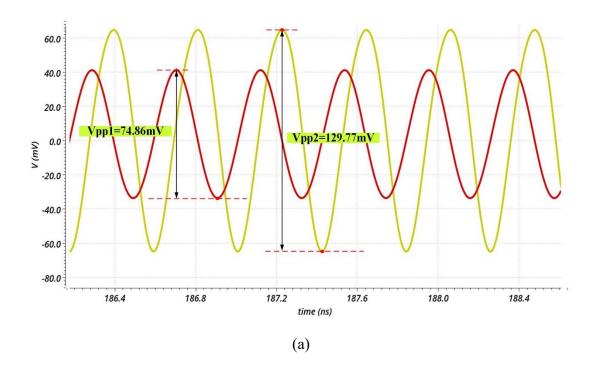

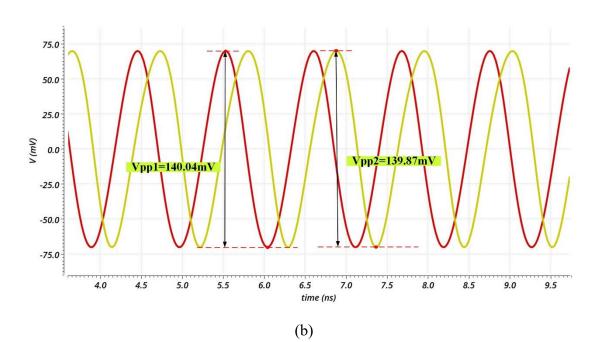

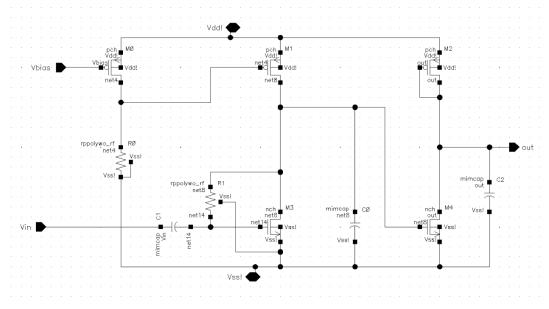

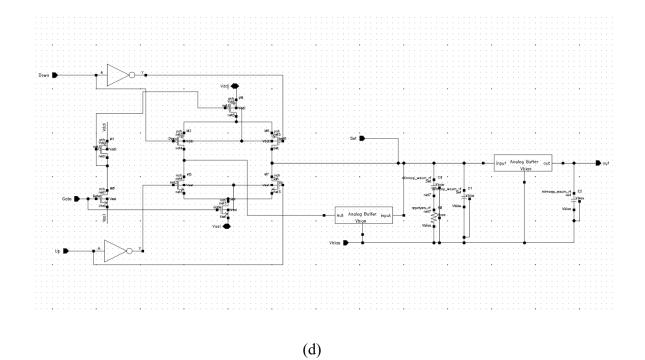

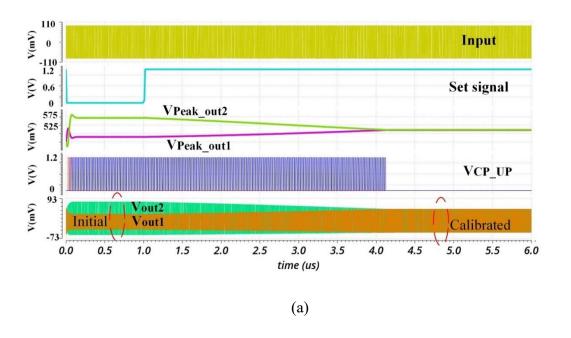

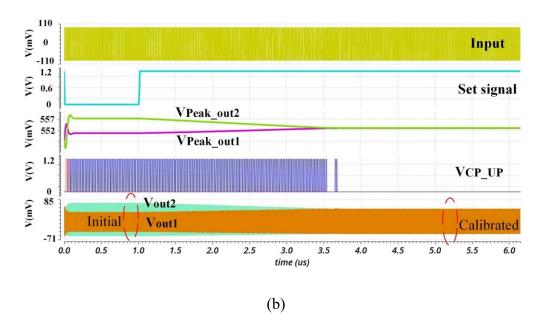

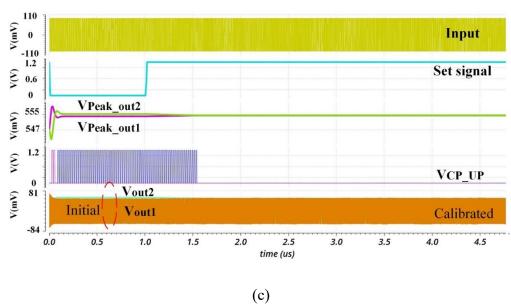

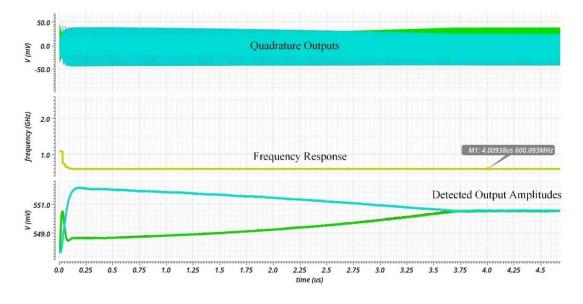

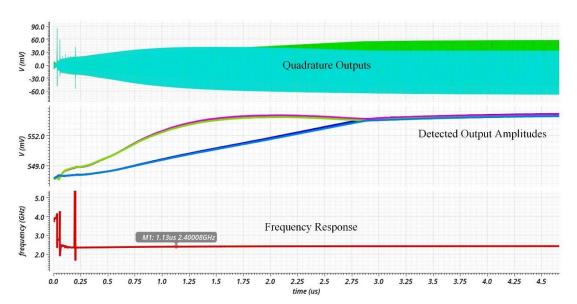

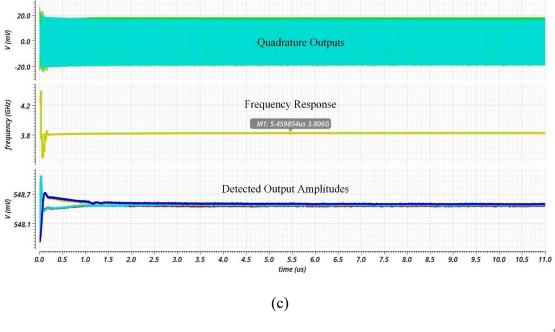

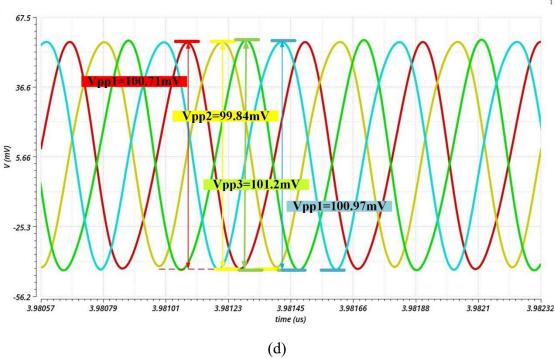

An active RC-CR 90-degree phase shifter circuit is implemented in Cadence 65nm process as explained in Fig 2.4.1. Without modifying the gate voltage  $V_{ctrl}$ ,  $V_{out1}$  and  $V_{out2}$  are 90-degree phase difference but with different gain as shown in Fig 2.4.2 (a). By adjusting  $V_{ctrl}$ , the pole frequency is moved to the input case, and the 90-degree phase with identical amplitude for  $V_{out1}$  and  $V_{out2}$  is achieved. For the input frequency range from 600MHa to 3.8GHz, three different cases (930MHz for 600MHz to 930MHz band, 2.4GHz for 2.4GHz to 2.9GHz band and 3.8GHz for 3.4GHz to 4.2GHz band) are listed in Fig 2.4.2 (b) to (d) for simplicity.

Fig 2.4.1 Schematic circuit of active RC-CR phase shifter

Fig 2.4.2 Simulation plots (a) Free run outputs with 3.8GHz input frequency (b) Adjusted output signals at 930MHz input frequency (c) Adjusted output signals at 2.4GHz input frequency (d) Adjusted output signals at 3.8GHz

#### 2.5 Conclusion

The active RC-CR 90-degree phase shifter is implemented by replacing the passive resistors with NMOS transistors. By adjusting the gate voltage of the transistors, the

pole frequency of the low/high pass filters can be varied with input frequency, and the wide band property for the phase shifter is realized. However, it is very complicate to change gate voltages with the variation of input frequencies manually. Besides, the accuracy of the phase shifter cannot be guaranteed with considering process variation effect when a look up table is used. In other words, an integrated and automatic calibration system is necessary for the active RC-CR circuit. The transistor gate voltages can be used in calibration system to vary the pole frequency as the input frequency changes and compensate for the gain mismatch error between two paths.

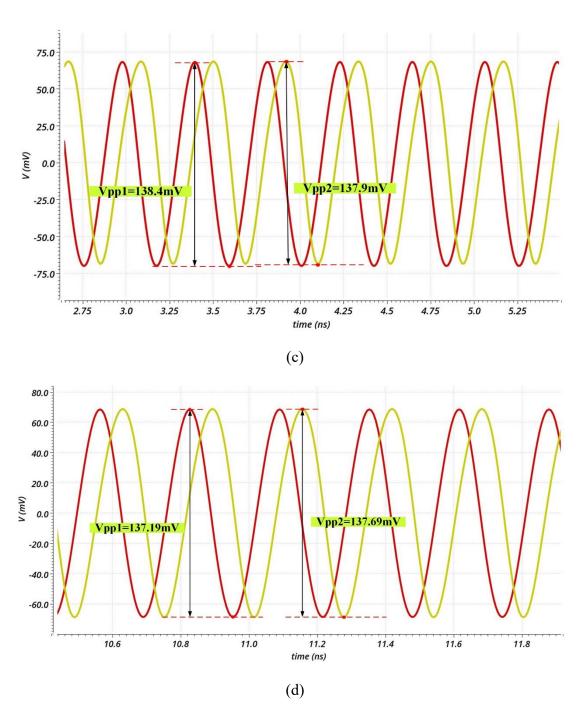

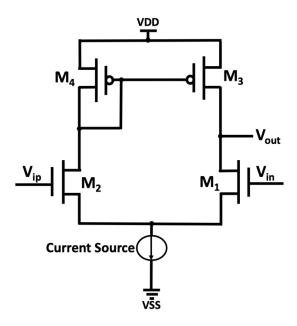

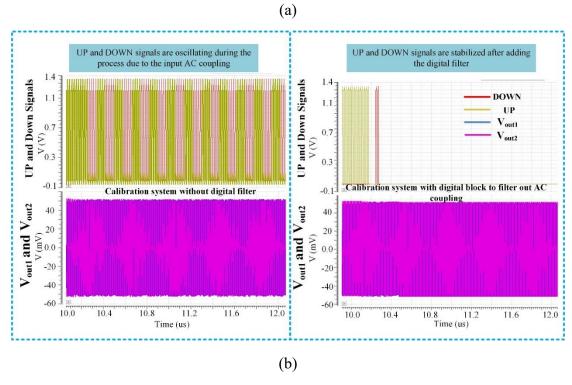

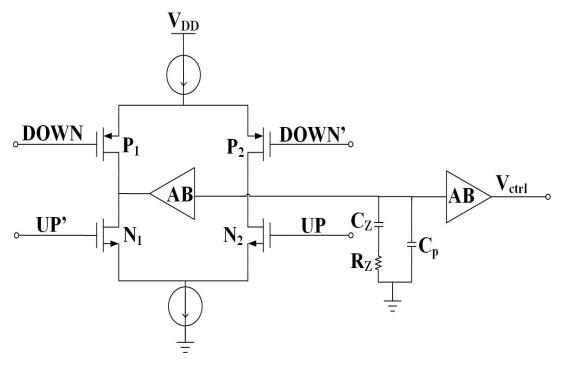

A top-level block diagram of the proposed in the loop real time calibration system is shown in Fig 2.5.1. Two peak detectors are connected to each output of active phase shifter to convert the AC amplitude into a unique DC voltage. Then, these two DC signals are fed into two parallel and identical comparators to cross check the two output amplitudes. When two DC inputs are very close (within the comparator resolution), the two comparator outputs are the same ('00' or '11'); When the difference between the two DC values is greater than the resolution, the comparator outputs have opposite results ('01' or '10'). Hence, the comparison results control the output of the next stage charge pump. If comparator outputs are '01' or '10', then charge pump modifies the gate voltage of the phase shifter (V<sub>ctrl</sub>) up or down to vary the active resistance and adjust the pole frequency to match the input frequency for gain error compensation. If the two comparators output '00' or '11', the charge pump keeps V<sub>ctrl</sub> constant to preserve equal gain in the I and Q paths.

According to the analysis in this chapter, the amplitude of  $V_{out1}$  and  $V_{out2}$  is function of frequency, resistance, and capacitance. Therefore, by changing the value of

resistance in each path, the amplitude mismatch due to frequency variation can be significantly reduced if capacitance in the path is fixed. A more detailed analysis of the comparator circuit of the calibration system is introduced in Chapter 2, and the proposed RC-CR phase shifter ALL calibration system is explained in Chapter 3.

Fig 2.5.1 Block diagram of RC-CR phase shifter ALL calibration system

# III. Dynamic Voltage Comparator

(The discussion in the following chapter is substantially drawn from [33], where we first reported the development and evaluation of this technique.)

#### 3.1 Introduction

Comparators are widely used in CMOS designs such as flash and Successive-Approximation Register (SAR) Analog-to-Digital Converters (ADCs) [34], memory sense amplifiers [35], peak detectors of calibration systems [36], etc. It senses the voltage difference between two inputs and converts the analog signals into digital outputs. The response time, power consumption, sensitivity, input referred offset, and kickback noise are key elements for a comparator design, which decide the speed, power, signal to noise ratio and bit error rate of the system.

As discussed in previous chapter, to maintain the phase shifter generating constant gain quadrature outputs a voltage comparator stage is used after the peak detector to convert the voltage signal into a digital sign for charge pump adjusting feedback gate voltage  $V_{ctrl}$ . The resolution of the comparator directly decides the variation of the quadrature outputs  $V_{out1}$  and  $V_{out2}$ . Thereby, the IMRR performance is depending on the sensitivity of the voltage comparator block.

This chapter presents a high-sensitivity high-speed dynamic voltage comparator, which is a key component for low power CMOS mixed signal application. The proposed dynamic comparator employs ten transistors with only one cross-coupled latch to reduce the circuit complexity. The parallel clocked input switches reduce parasitic resistance in the latch ground path that results in a significant decrease in latch delay time. In addition, a symmetric, three stacked transistor, single stage architecture

reduces the process variation effects, increases input resolution, and provides more head room for low power-supply applications.

### 3.2 Comparator Architecture

#### 3.2.1 Static Comparator

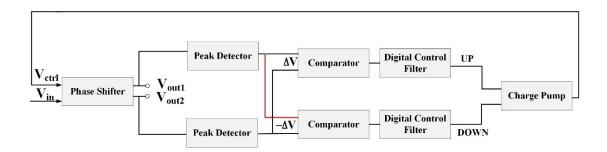

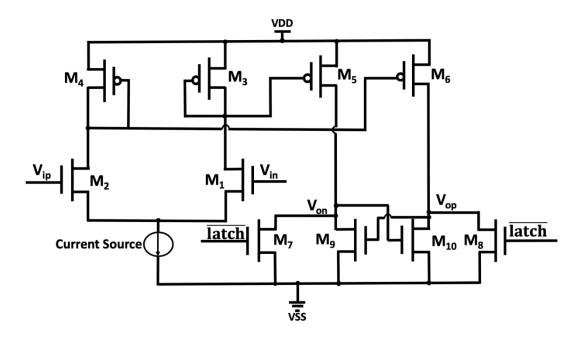

A conventional static comparator is shown in Fig 3.2.1 referred from [37], which is an opamp-type comparator. It consists of a pair of differential inputs  $V_{in}$  and  $V_{ip}$ , a current source and a pair of current load transistors  $M_3$  and  $M_4$ . Clock signal is not applied in this circuit, so the system compares the inputs constantly. However, this circuit consumes large static power because of the constant source current.

Fig 3.2.1 Conventional static comparator

A static latched comparator is expressed in Fig 3.2.2 referred from [37], which add a latch stage after the conventional static comparator. The operation of this comparator is as follows. When circuit is in reset mode, latch transistor  $M_{7,8}$  is on with latch signal low, and the differential outputs  $V_{op}$  and  $V_{on}$  are pulled down to ground. While latch signal goes high, the comparator is in comparison mode, so  $M_{7,8}$  turns off.  $M_5$  and  $M_6$

starts to charge the outputs  $V_{op}$  and  $V_{on}$  associated with first stage current mirror transistor  $M_{3,4}$  and  $V_{ip}$  and  $V_{in}$ . Once one output  $V_{on}/V_{op}$  is charging to  $M_{10}/M_9$  threshold voltage  $V_{tn}$ , the other node will go down to ground and keep the other one charging to  $V_{DD}$ . The latch block in this comparator provides more gains in regeneration process, however, the static power in this circuit is not attractive in comparator designs.

Fig 3.2.2 Static latched comparator

### 3.2.2 Dynamic Comparator

Dynamic comparators have the advantage of low static power consumption compared with static architectures. The conventional dynamic comparator architecture analyzed in [38] was first published by Kobayashi in [39] and continues to be a widely used structure for comparator/sense amplifier circuits in low power microelectronic applications. The high-speed rail-to-rail swing is obtained by the positive feedback of the cross-coupled latch circuit, which reduces the response time, boosts the operating frequency, and decreases the static power in evaluation mode.

There have been many alternative proposals for dynamic comparator structures

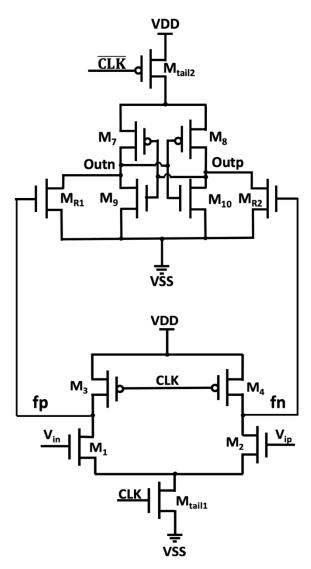

targeted for low power, high frequency, nano-scale microelectronic applications. The double-tail structure in Fig 3.2.3 provides more head room for low power-supply design due to less stacked transistors [40] [41], and an input amplifying stage is added to decrease the latch delay time for the latched dynamic comparator. Nonetheless, it suffers the trade-offs of extra delay elements and circuit complexity, which reduces the speed and sensitivity of the comparator compared with single stage dynamic comparator.

Fig 3.2.3 Conventional double-tail dynamic comparator

Fig 3.3.1 Conventional single-stage dynamic comparator

# 3.3 Conventional Single-Stage Dynamic Comparator

A conventional dynamic comparator produces rail-to-rail outputs in response to the differential inputs  $V_{in}$  and  $V_{ip}$ , while consuming no static power [38]. As shown in Fig 3.3.1, the basic components are a differential pair  $(M_1, M_2)$ , four precharge switches  $(S_1-S_4)$ , a tail switch  $S_7$ , and two cross coupled pairs  $(M_3-M_4)$  and  $M_5-M_6$  to form a back-to-back latch.

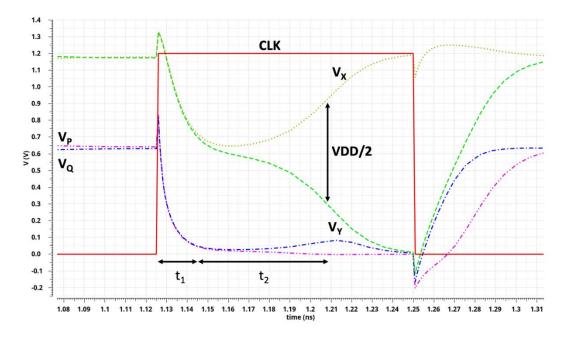

The operation is as follows. The output nodes X, Y and nodes P, Q are charged to  $V_{DD}$  during the precharge phase (CLK is low). The shared source of  $M_1$  and  $M_2$  is charged to  $V_{cm} - V_{tn}$ .  $V_{in}$  and  $V_{ip}$  have the values of  $V_{cm}$  and  $V_{cm} + \Delta V_{in,p}$  or vice versa. After charging of capacitors, the only current flow is leakage since the tail switch is off.

When CLK is high the circuit is in evaluation mode, which can be divided into three phases. In phase 1, evaluation begins with the tail transistor S<sub>7</sub> switching on as an

active resistor  $(R_{ON\_S7})$  in triode mode, and it takes the sources of  $M_1$  and  $M_2$  to a voltage of  $2I_{cm1,2}R_{ON\_S7}$ , where  $R_{ON\_S7}=1/g_{ON\_S7}$  and  $g_{ON\_S7}$  represents the conductance of  $S_7$ . The switch action of  $S_7$  activates the differential pair  $M_1$  and  $M_2$ , which initially operate in the saturation mode with transconductance  $g_{m1,2}$  in (3-3-1):

$$g_{m1,2} = \beta_{M1,2}(V_{cm} - V_{tn}) \tag{3-3-1}$$

Where  $\beta_{M1,2} = K_{M1,2} \cdot (\frac{W}{L})$  and  $K_{M1,2}$  is the process gain factor of  $M_{1,2}$ . The P and Q node capacitors at the sources of  $M_3$  and  $M_4$  are discharged through  $M_1$  and  $M_2$  at slightly unequal rates due to the  $\Delta V_{in,p}$  at the inputs.

Note that the values of  $g_{m1}$  and  $g_{m2}$  are degraded by negative feedback resistance  $R_{ON\_S7}$  in the source to ground path; the effective values of  $g_{m1}$  and  $g_{m2}$  are estimated as (3-3-2):

$$g_{m1,2eff} = \frac{g_{m1,2} \cdot g_{ON\_S7}}{g_{m1,2} + g_{ON\_S7}} \tag{3-3-2}$$

The differential voltage  $\Delta V_{P,Q}$  at time  $t_1$  can be estimated by (3-3-3):

$$\Delta V_{P,Q}(t_1) = |V_P - V_Q| = \frac{g_{m1,2eff} \cdot \Delta V_{in,p}}{c_{P,Q}} t_1$$

(3-3-3)

$M_3$  and  $M_4$  starts to turn on when P and Q reach  $V_{DD} - V_{tn}$ , so time  $t_1$  ends when this occurs and is estimated by the time to discharge  $C_{P,Q}$  by  $V_{tn}$  volts, which is expressed as (3-3-4):

$$t_1 = C_{P,O} \cdot V_{tn} / I_{cm1,2} \tag{3-3-4}$$

$t_2$  is the time for M<sub>3</sub> and M<sub>4</sub> to discharge X and Y from  $V_{DD}$  to  $V_{DD}$ - $|V_{tp}|$  to activate the back-to-back latch formed by M<sub>3,4</sub> and M<sub>5,6</sub>, and this time is recorded as phase 2. The estimated value of  $t_2$  is calculated by (3-3-5):

$$t_2 = \frac{C_{X,Y} \cdot |V_{tp}|}{I_{m_{3,4}}} \tag{3-3-5}$$

The differential voltage at P and Q at time  $t_1$  results in a small difference in discharge rate of X and Y node capacitance  $C_{X,Y}$ . So a differential voltage  $\Delta V_{X,Y}$  is developed and estimated by (3-3-6).

$$\Delta V_{X,Y}(t_2) = |V_X - V_Y| = \frac{g_{m3,4eff} \cdot \Delta V_{P,Q}(t_1)}{c_{X,Y}} t_2$$

(3-3-6)

$M_1$  and  $M_2$  go into triode when  $V_{P,Q} = V_{cm} - V_{tn}$  and at this time the sources of  $M_3$  and  $M_4$  are connected to ground through active resistor  $R_{ON\_M1,2}$  in series with active resistor  $R_{ON\_S7}$ . With both  $S_7$  and  $M_{1,2}$  in triode,  $g_{ON\_M1,2eff}$  is calculated as (3-3-7):

$$g_{\text{ON\_M1,2eff}} = \frac{g_{\text{ON\_M1,2}} \cdot g_{\text{ON}_{S7}}}{g_{\text{ON\_M1,2}} + g_{\text{ON}_{S7}}}$$

(3-3-7)

The effective value of  $g_{m3,4eff}$  is reduced by the series active resistors in the source to ground path based on  $g_{m3,4eff} = (g_{m3,4} \cdot g_{ON_{M1,2eff}})/(g_{m3,4} + g_{ON_{M1,2eff}})$ , and  $g_{m3,4eff}$  is reduced compared to  $g_{m3,4}$ . The comparator is in phase 3 with  $M_{5,6}$  transistor on, and the back to back latch takes the outputs to the rails with time  $t_3$  as expressed in (3-3-8) [42]:

$$t_3 = \frac{c_{X,Y}}{g_{m,latcheff}} \ln \frac{V_{DD}/2}{\Delta V_{X,Y}(t_2)}$$

(3-3-8)

Where  $g_{m,latcheff}$  is the effective transconductance of the latch, and it is proportional to the sum of  $g_{m,latcheff}$  and  $g_{m5,6eff}$ . The smaller value of  $g_{m3,4eff}$  due to the ground path resistance results in a smaller value of  $g_{m,latcheff}$  and longer  $t_3$ . The total delay  $t_{total}$  for evaluation phase is  $(t_1 + t_2 + t_3)$ . Based on previous discussion, our proposed comparator will focus on reducing the parasitic resistance in the ground path for latch phase resulting in a significant reduction in the delay time. Also, if the

input voltage difference can be sensed and translated to an output voltage difference  $\Delta V_{X,Y}$  during precharge phase, then the first phase  $t_1$  for conventional comparator can be eliminated with the additional benefit of increased sensitivity.

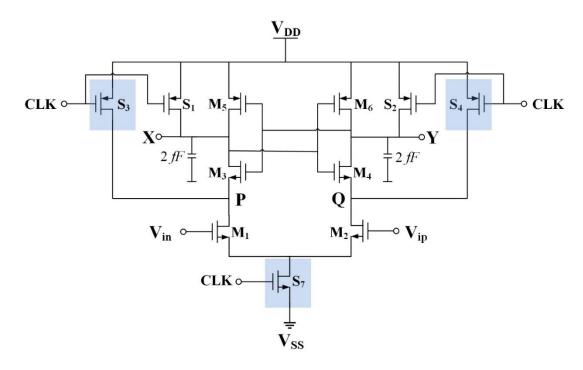

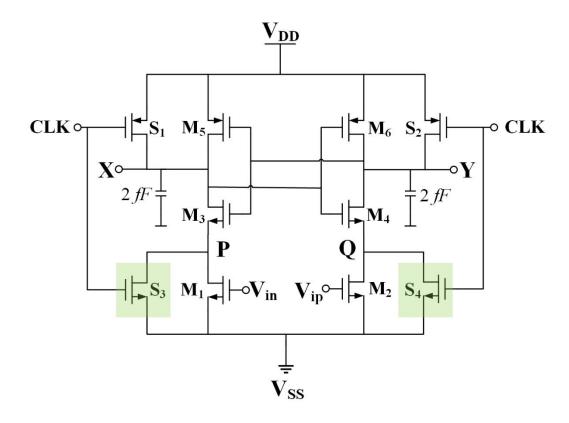

## 3.4 Proposed Dynamic Comparator with Clocked Parallel Switches

Fig 3.4.1 Proposed dynamic comparator with parallel clocked input switches

The proposed dynamic comparator is shown in Fig 3.4.1. As seen the structure has similarities to the conventional comparator but with addition of two clocked parallel n-channel switches  $S_3$  and  $S_4$  and the deletion of the tail switch  $S_7$  and two clocked p-channel precharge switches  $S_3$  and  $S_4$ . The basic motivation is to reduce the parasitic active resistance in the ground path during evaluation phase resulting in significant decrease in delay time. Additionally, a differential voltage proportional to the input difference  $\Delta V_{in,p}$  is produced at the output nodes during precharge mode to eliminate

the requirement for differential sensing during evaluation phase and also presenting the opportunity for increased sensitivity.

The basic operation is as follows. When CLK is low, the comparator is in precharge mode.  $S_3$  and  $S_4$  switch off, while  $S_1$  and  $S_2$  are switched on to precharge  $V_{X,Y}$  to near  $V_{DD}$  causing  $M_{5,6}$  to be off.  $M_1$  and  $M_2$  are on with input difference  $\Delta V_{in,p}$ , which creates a current difference  $\Delta I_{in,p}$  at nodes X and Y. Since the precharge phase is relatively long, the capacitors  $C_{P,Q}$  and  $C_{X,Y}$  reach a steady state value drawing no current. Then drain currents and current differences of  $M_{1,2}$ ,  $M_{3,4}$  and  $S_{1,2}$  must be the same at the end of the precharge phase. Note that the node voltage  $V_{P,Q}$  are near a value of  $V_{DD} - V_{cm}$  (depending on the ratios of  $\beta m_{1,2}$  to  $\beta m_{3,4}$ ) to force  $I_{cm1,2} = I_{cm3,4}$ . The equality of drain currents requires the following ratio to hold in (3-4-1) to (3-4-2):

$$\frac{\Delta V_{P,Q}(t_0)}{\Delta V_{in,p}(t_0)} = \frac{\beta_{m1,2}(V_{cm} - V_{tn1,2})}{\beta_{m3,4}(V_{DD} - V_{P,Q} - V_{tnm3,4})}$$

(3-4-1)

$$\frac{\Delta V_{X,Y}(t_0)}{\Delta V_{in,p}(t_0)} = \frac{\beta_{m1,2}(V_{cm} - V_{tn1,2})}{\beta_{S1,2}(V_{DD} - |V_{tpS1,2}|)}$$

(3-4-2)

Fig 3.4.2 Evaluation mode of proposed dynamic comparator

In this case, at the end of precharge phase, the differential voltages have been

established at  $\Delta V_{P,Q}$  and  $\Delta V_{X,Y}$  proportional to  $\Delta V_{in,p}$ . Note that the  $\Delta V_{X,Y}/\Delta V_{in,p}$  and  $\Delta V_{P,Q}/\Delta V_{in,p}$  are independent of the node capacitances  $C_{P,Q}$  and  $C_{X,Y}$ . When clock is high, the comparator is in evaluation mode, and it can be divided into two phases as shown in Fig 3.4.2. Phase 1 is the latch activation mode, switches  $S_3$  and  $S_4$  are clocked on (in triode mode) with relatively large conductance  $g_{ON,S3,4}$ .  $M_1$  and  $M_2$  are initially in the saturation state with drain voltage of about  $V_{DD} - V_{cm}$ , but quickly enter triode mode due to fast pull-down action of  $S_{3,4}$  in parallel with  $M_{1,2}$ . Then the effective transconductance in  $M_{3,4}$  ground path is  $g_{ON,S3,4} + g_{ON,M1,2}$  so the effective transconductance  $M_{3,4}$  ( $g_{m3,4}$ ) is derived in (3-4-3).

$$g_{m3,4eff} = \frac{g_{m3,4}(g_{ON\_S3,4} + g_{ON\_M1,2})}{g_{m3,4} + g_{ON\_S3,4} + g_{ON\_M1,2}} \approx g_{m3,4}$$

(3-4-3)

Unlike the conventional dynamic comparator, the transconductance  $g_{m3,4}$  has very little reduction due to the ground path resistance. So the effective action of  $M_{1,2}$  and  $S_{3,4}$  quickly discharge  $C_{P,Q}$ , which increases the drain currents  $I_{m3,4}$  to discharge node voltage of  $V_{X,Y}$  from near  $V_{DD}$  to  $V_{DD} - |V_{tp}|$  turning on  $M_{5,6}$  and activating the back to back latch. The latch activation time  $t_1$  is calculated as  $t_1 = C_{X,Y} \cdot |V_{tp}|/I_{m3,4}$ , and voltage difference for output nodes at  $t_1$  are expressed in (3-4-4):

$$\Delta V_{X,Y}(t_1) = \frac{g_{m3,4eff} \cdot \Delta V_{P,Q}(t_0)}{c_{X,Y}} t_1 + \Delta V_{X,Y}(t_0)$$

(3-4-4)

The second phase in evaluation mode is the latch delay  $t_2$ . With  $M_{5,6}$  on, the backto-back latch takes the outputs to the rails with time  $t_2$  [42] in (3-4-5):

$$t_2 = \frac{c_{X,Y}}{g_{m,latcheff}} \ln \frac{v_{DD}/2}{\Delta v_{X,Y}(t_1)}$$

(3-4-5)

Where  $g_{m,latcheff}$  is the effective transconductance of the latch, and is proportional to the sum of  $g_{m5,6eff}$  and  $g_{m3,4eff}$ . For this proposed dynamic

comparator,  $g_{m3,4eff}$  has not been reduced by ground path resistance so the total delay of evaluation phase  $t_{total} = t_1 + t_2$  is much smaller than the latch delay in conventional comparator.

#### 3.5 Simulation Results

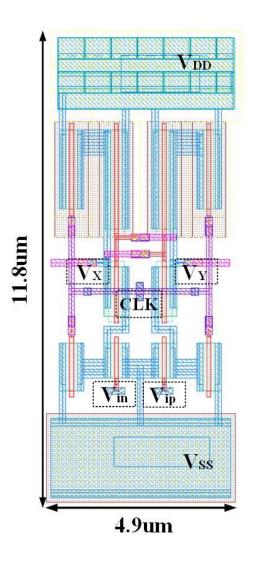

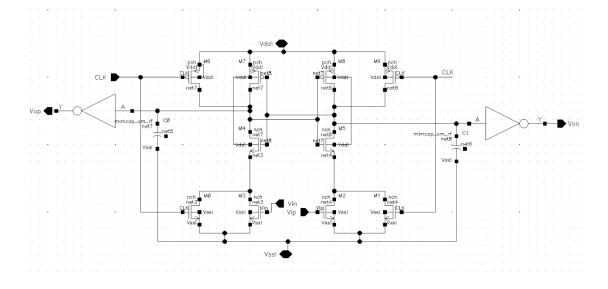

The proposed dynamic comparator is implemented in Cadence Virtuoso software (shown in Fig 3.5.1) with transistor size shown in Table 3.5.1. A conventional latched comparator in [38] is also implemented under the same process for comparison with the sizes in Table 3.5.1. A comparison of the response time (evaluation delay time) between conventional and proposed dynamic comparator is given in Fig 3.5.2 under  $30\mu V \Delta V_{in,p}$ , 0.6V  $V_{cm}$ , 500MHz clock frequency and 2fF load capacitance. The response delay of conventional latch is 452ps compared to 175ps for the proposed comparator, demonstrating that the maximum operating frequency is limited by the large parasitic resistance in ground path and longer latch delay in a conventional design.

**Table 3.5.1 Transistor Sizes**

| Conventional                   | Dynamic Comparator   | Proposed Dynamic Comparator    |                      |  |

|--------------------------------|----------------------|--------------------------------|----------------------|--|

| Transistor                     | Aspect ratio (W/L in | Transistor                     | Aspect ratio (W/L in |  |

| Name                           | μm)                  | Name                           | μm)                  |  |

| $S_1/S_2$                      | 1/0.1                | $S_1/S_2$                      | 1.8/0.1              |  |

| $S_3/S_4$                      | 1/0.1                | S <sub>3</sub> /S <sub>4</sub> | 1.2/0.1              |  |

| S <sub>7</sub>                 | 3/0.1                | -                              | -                    |  |

| $M_1/M_2$                      | 1.5/0.1              | $M_1/M_2$                      | 0.88/0.1             |  |

| M <sub>3</sub> /M <sub>4</sub> | 1.25/0.1             | $M_3/M_4$                      | 1.25/0.1             |  |

| $M_5/M_6$                      | 2.5/0.1              | $M_5/M_6$                      | 2.5/0.1              |  |

Fig 3.5.1 CMOS implementation of proposed dynamic voltage comparator

Fig 3.5.2 Transient simulation of proposed comparator versus conventional comparator

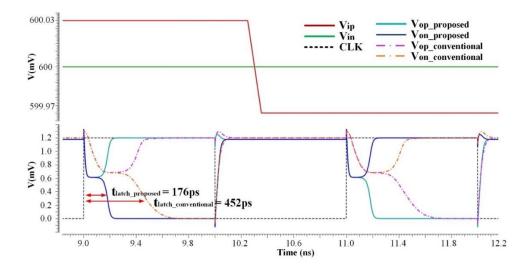

Fig 3.5.3 Transient simulation results with considering process variations: (a) Proposed design for CLK=2GHz (b) Proposed design for CLK=4GHz (c) Conventional design for CLK=500MHz

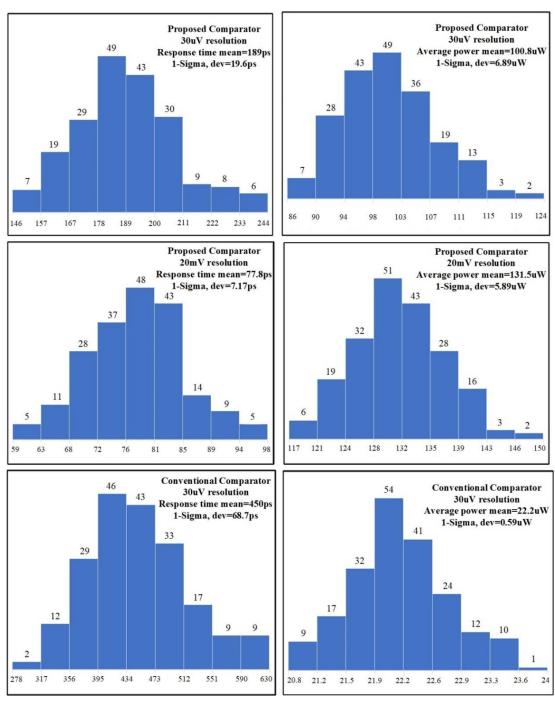

Monte Carlo Analysis is applied to assess process variation effects with 200 runs.

The test configuration is  $0.6V V_{cm}$  with 2fF output load capacitance. A transient

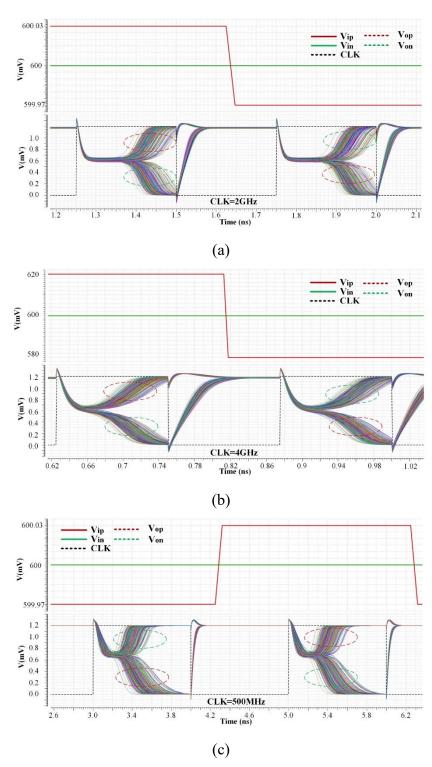

simulation plot of the proposed design under process variations is shown in Fig 3.5.3. The average power consumption of the proposed comparator over the 200 Monte Carlo runs is  $100.8\mu W$  with  $30\mu V$   $\Delta V_{in,p}$  and 2GHz CLK, and  $131.4\mu W$  with 20mV  $\Delta V_{in,p}$  and 4GHz CLK. The response delay is averaged at 189.4ps and 77.8ps with  $30\mu V$  and 20mV input resolution, respectively. The 1-sigma value of delay and power are calculated as 19.64ps and  $6.89\mu W$  at  $30\mu V$   $\Delta V_{in,p}$  and 7.17ps and  $5.89\mu W$  at 20mV  $\Delta V_{in,p}$  compared with 68.66ps and  $0.59\mu W$  for 500MHz clock for the conventional dynamic comparator in Fig 3.5.4. The proposed comparator retains full functionality for all of the 200 runs of the Monte Carlo analysis.

Performance comparisons of this work with conventional dynamic comparator and other alternatives are summarized in Table 3.5.2. The structures in [34], [43], [40], [37] and [44] all incorporate an input amplifying/latch stage to generate a differential input voltage to the output latch resulting in increased complexity and delay compared to the proposed design. The data under [38] is based on our implementation of conventional latch in same process.

Table 3.5.2 Performance comparison of dynamic voltage comparators

| Parameters       | [34]   | [43]   | [40]   | [37]        | [44]   | [38]      | T    | his woı | :k   |

|------------------|--------|--------|--------|-------------|--------|-----------|------|---------|------|

| Technology       | 65nm   | 180nm  | 180nm  | 40nm        | 180nm  | 90nm      | 90   | nm 1.2  | 2V   |

| reciliology      | 1.2V   | 1.8V   | 1.2V   | 1.1V        | 1.8V   | 1.2V      |      |         |      |

| Design<br>Type   | Layout | Layout | Layout | Fabrication | Layout | Schematic |      | Layout  |      |

| Power (µW)       | 376    | 420    | 1400   | 346         | 347    | 22        | 106  | 77      | 131  |

| Frequency (GHz)  | 0.02   | 0.5    | 2.4    | 6           | 0.5    | 0.5       | 2    | 2       | 4    |

| Sensitivity (mV) | 0.036  | 1      | 7.8    | 20          | 2.19   | 0.03      | 0.03 | 20      | 20   |

| Delay Time (ns)  | 13     | 0.3    | 0.3    | 0.06        | 0.35   | 0.45      | 0.19 | 0.08    | 0.08 |

| Area (μm²)       | -      | 486    | 392    | 64.5        | 361    | -         |      | 57.8    |      |

Fig 3.5.4 Monte-Carlo simulation results for proposed and conventional dynamic comparator

# 3.6 Conclusion

This dissertation presents a 10-transistor dynamic comparator with parallel clocked input switches that decreases the response time in evaluation mode along with

improved sensitivity. The proposed circuit performs input differential sensing simultaneously with pre-charge and the magnitude of the differential output voltage is independent of the magnitude of the output node capacitance. This eliminates the need for generating differential output voltages during evaluation phase resulting in the backto-back latch activation at earlier time. The parallel clocked input switches with relatively high conductance result in low parasitic resistance in ground path of latch circuit significantly reducing latch delay. The proposed circuit draws static power in precharge phase, but the current is limited by the drain current of input transistors. Also, only two nodes are precharged to  $V_{DD}$ , so the average power consumption compares favorably to existing implementations. Meanwhile, it maintains 100% functionality under simulated process variations due to the symmetric and low-complexity architecture. Compared with conventional single stage and double-tail dynamic comparators, the proposed design has balanced properties of sensitivity, speed and power consumption, which is used in the integrated on-line amplitude locked loop calibration system.

# IV. Integrated On-line Amplitude Locked Loop Calibration System

(The discussion in the following chapter is substantially drawn from [28], where we first reported the development and evaluation of this technique.)

# 4.1 Introduction

As mentioned in previous chapters, a calibration system is needed to vary the control voltage of active RC-CR phase shifter for variable input frequency and compensate process variation. A top-level block diagram of the proposed calibration system is explained in Chapter 2. A detailed analysis of sub-circuits in integrated online amplitude locked loop calibration system is added in this chapter.

# 4.2 Sub-circuits in Calibration System

### 4.2.1 Peak Detector

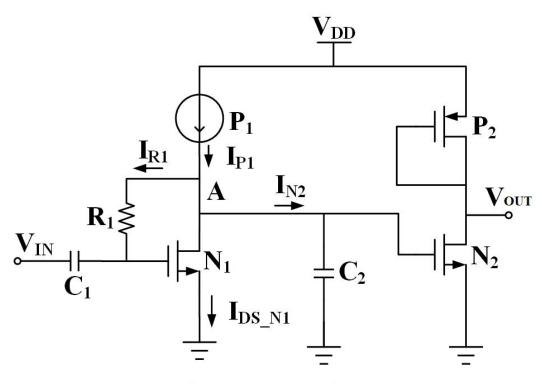

Fig 4.2.1 Schematic diagram of peak detector

A low power CMOS peak detector is used in this proposed architecture as the second stage to convert the amplitude of  $V_{out1,2}$  into corresponding DC voltage [45]. It consists of two stages. The first stage detects the amplitudes and converts them into DC results, and the second stage is an active load amplifier to enhance the detection sensitivity and flip the inverted results of stage-one.

As seen in Fig 4.2.1,  $C_1$  is a DC blocking capacitor, and  $R_1$  is a voltage feedback resistor between the drain of  $N_1$  and the AC input voltage (gate voltage). In the first stage, the current of current source  $P_1$ , feedback current through  $R_1$ , and drain to source current of  $N_1$  are balanced at node A. Since current across  $R_1$  is also the gate leakage current of  $N_1$  which is very small,  $I_{DS}$  of  $N_1$  is approximately equal to  $I_{P1}$ . To maintain the equality, if the amplitude of  $V_{in}$  increases, the drain voltage of  $N_1$  (also the voltage of node A) must be reduced to keep the same current as  $I_{P1}$ . Thus, the DC voltage at node A is inversely proportional to input amplitude, and this DC result is held by  $C_2$ . To improve the detection sensitivity and reduce following circuits design complexity, an active load inverter amplifier/buffer is used as an output stage to drive the follow-on comparators which is consisted of  $P_2$  and  $N_2$  transistors

## 4.2.2 Comparator

A high-speed high-sensitivity dynamic latched comparator is placed at the third stage to convert the voltage signal from peak detector to digital signal. As mentioned in Chapter 3, the proposed dynamic voltage comparator is used in the calibration system. The high sensitivity of the latched comparator significantly improves the comparison resolution of peak detector outputs.

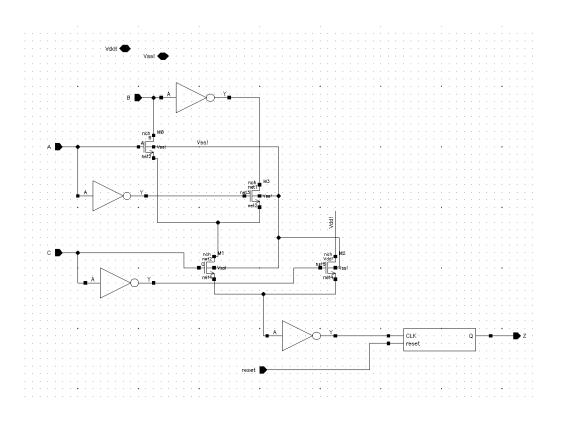

However, a small variation of amplitude difference between  $V_{out1}$  and  $V_{out2}$