Portland State University PDXScholar

**Dissertations and Theses**

**Dissertations and Theses**

1998

# **Rtl Power Estimation of Sequential Circuits**

Sridhar Muthrasanallur Portland State University

Follow this and additional works at: https://pdxscholar.library.pdx.edu/open\_access\_etds

Part of the Electrical and Computer Engineering Commons Let us know how access to this document benefits you.

#### **Recommended Citation**

Muthrasanallur, Sridhar, "Rtl Power Estimation of Sequential Circuits" (1998). *Dissertations and Theses*. Paper 6434. https://doi.org/10.15760/etd.3579

This Thesis is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. Please contact us if we can make this document more accessible: pdxscholar@pdx.edu.

## THESIS APPROVAL

The abstract and thesis of Sridhar Muthrasanallur for the Master of Science in Electrical Engineering were presented May 27, 1998, and accepted by the thesis committee and the department.

COMMITTEE APPROVALS:

Dr. W. Robert Daasch, Chair

Dr. Douglas V. Hall

Dr. Timothy R. Anderson Representative of the Office of Graduate Studies

DEPARTMENT APPROVAL:

Dr. Lee W. Casperson, Chair Electrical and Computer Engineering

#### ABSTRACT

An abstract of the thesis of Sridhar Muthrasanallur for the Master of Science in Electrical Engineering presented May 27, 1998.

#### Title: RTL Power Estimation of Sequential Circuits

Power consumption has become a major concern in the electronic industry in recent years because of the increased demand for portable electronic devices. Part of the problem in power conscious design is accurate power estimation. Power estimation at low-levels of design abstraction is slow since the units of low-levels of design abstraction are transistors or gates. But designers need reliable power estimates early in the design process. Therefore designers need to have tools for fast and accurate power estimation at higher levels of design abstraction such as the Register Transfer Level (RTL).

This thesis introduces a new method for RTL power estimation of CMOS sequential circuits. This method tries to estimate the average power of a sequential circuit through the combination of a low-effort synthesis of the RTL description of the sequential circuit and the parameters readily available from the RTL description of the circuit like the sum-of-product count and literal count. The quantitative and qualitative aspects of the new model are studied with MCNC91 benchmark circuits and a large set of randomly generated circuits. Quantitative power estimation with the new model is seen to be very difficult because of the highly irregular surfaces of the functions that are being modeled in an effort to understand how a synthesis tool changes the power of a circuit during optimization. A qualitative measure is then proposed for the performance of a synthesis tool in preserving the qualitative ordering of power values of different implementations of a sequential circuit. An inference about such a performance of the synthesis tool would help the designer make informed decisions about the choice of implementation of a sequential circuit from a set of broad alternatives.

# (RTL POWER ESTIMATION OF SEQUENTIAL CIRCUITS

by SRIDHAR MUTHRASANALLUR

A thesis submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE in ELECTRICAL ENGINEERING

Portland State University 1998

# Acknowledgements

First and foremost, I would like to thank my advisor, Prof. Daasch, who was instrumental in the development of this thesis. His invaluable guidance at each stage of this thesis was very vital. He is a researcher I hold in high respect. I thank Prof. Anderson and Prof. Hall for their very valuable feedback which helped me improve this document and also for their valuable suggestions for future directions.

I'm more than thankful to my friends, Sandeep, Easwar, Ryan and Vikranth, who cheerfully and painstakingly proof read my document. Their excellent feedback was highly important for the fast turn around time in preparing this document. And, my parents. Eventhough they are far away, their support throughout this thesis was nothing but great.

# Contents

| List of Tables |              |         |                                                       |              |  |

|----------------|--------------|---------|-------------------------------------------------------|--------------|--|

| Lis            | t of         | Figure  | es                                                    | $\mathbf{v}$ |  |

| 1              | Introduction |         |                                                       |              |  |

|                | 1.1          | Power   | Estimation - The Variety of Solutions                 | 1            |  |

|                | 1.2          | Source  | es of Power Consumption                               | 3            |  |

|                |              | 1.2.1   | Static Power                                          | 3            |  |

|                |              | 1.2.2   | Dynamic Power                                         | 4            |  |

|                | 1.3          | Factor  | s Affecting Power Dissipation                         | 6            |  |

|                | 1.4          | Combi   | inational Circuit Power Estimation                    | 7            |  |

|                |              | 1.4.1   | Low-level Power Estimation                            | 7            |  |

|                |              | 1.4.2   | RTL Power Estimation                                  | 8            |  |

| 2              | Prev         | vious V | Work In Sequential Circuit Power Estimation           | 12           |  |

|                | 2.1          | Gate-l  | evel Sequential Circuit Power Estimation              | 15           |  |

|                |              | 2.1.1   | Simulation-Based Techniques                           | 15           |  |

|                |              | 2.1.2   | Analytical Techniques                                 | 21           |  |

|                | 2.2          | RT-lev  | el Sequential Circuit Power Estimation                | 22           |  |

|                |              | 2.2.1   | Predictive Techniques                                 | 24           |  |

|                |              | 2.2.2   | Descriptive Techniques                                | 26           |  |

|                | 2.3          | Chapte  | er Summary                                            | 27           |  |

| 3              | New          | RTL     | Power Estimation Method For Sequential Circuits       | 28           |  |

|                | 3.1          |         | ation For A New Power Model                           | 31           |  |

|                | 3.2          | Power   | Model                                                 | 32           |  |

|                | 3.3          | Power   | Characterization                                      | 35           |  |

|                |              | 3.3.1   | High-level Circuit Synthesis                          | 38           |  |

|                |              | 3.3.2   | Input Vector Generation                               | 39           |  |

|                |              | 3.3.3   | Low-level Power Estimation                            | 39           |  |

|                |              | 3.3.4   | Model Coefficient Extraction                          | 40           |  |

|                |              | 3.3.5   | Analysis of Power-Ratio Sensitivity to Input Activity | 40           |  |

|                | 3.4          | Power   | Analysis                                              | 41           |  |

|    |                                                             | 3.4.1   | High-level Circuit Synthesis Without Optimization  | 41 |  |  |

|----|-------------------------------------------------------------|---------|----------------------------------------------------|----|--|--|

|    | 3.4.2 Low-level Power Analysis of the Unoptimized Circuit . |         |                                                    | 42 |  |  |

|    |                                                             | 3.4.3   | Power-Ratio Extractor                              | 43 |  |  |

|    |                                                             | 3.4.4   | Correction Factor for Power                        | 43 |  |  |

|    | 3.5                                                         | Chapt   | er Summary                                         | 44 |  |  |

| 4  | Power Model Evaluation 45                                   |         |                                                    |    |  |  |

|    | 4.1                                                         |         | imental Setup                                      | 46 |  |  |

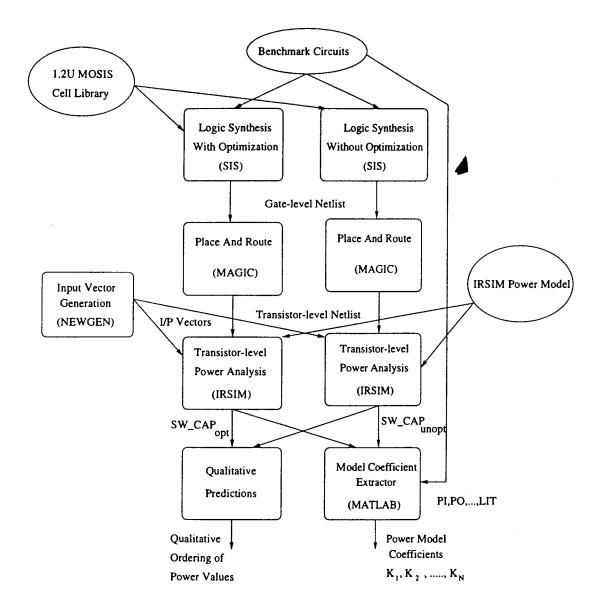

|    |                                                             | 4.1.1   | Power Characterization Implementation              | 46 |  |  |

|    |                                                             |         | 4.1.1.1 Logic Synthesis with SIS                   | 46 |  |  |

|    |                                                             |         | 4.1.1.2 Place and Route with MAGIC                 | 48 |  |  |

|    |                                                             |         | 4.1.1.3 Input Vector Generation with NEWGEN        | 49 |  |  |

|    |                                                             |         | 4.1.1.4 Transistor-level Power Analysis with IRSIM | 49 |  |  |

|    |                                                             |         | 4.1.1.5 Model Coefficient Extraction with MATLAB   | 50 |  |  |

|    |                                                             |         | 4.1.1.6 FSMs and Randomly Generated Circuits       | 50 |  |  |

|    |                                                             |         | 4.1.1.7 Qualitative Predictions                    | 50 |  |  |

|    |                                                             | 4.1.2   | Power Model Performance Evaluation Setup           | 51 |  |  |

|    | 4.2                                                         | Result  | S.,                                                | 53 |  |  |

|    |                                                             | 4.2.1   | Quantitative Power Analysis                        | 53 |  |  |

|    |                                                             |         | 4.2.1.1 MCNC91 Benchmark Set Results               | 53 |  |  |

|    |                                                             |         | 4.2.1.2 Random-Circuit-Set Results                 | 60 |  |  |

|    |                                                             |         | 4.2.1.3 Statistical Confirmation of Independence   | 65 |  |  |

|    |                                                             | 4.2.2   | Qualitative Power Analysis                         | 68 |  |  |

|    | 4.3                                                         | Chapt   | er Summary                                         | 75 |  |  |

| 5  | Fut                                                         | ure Wo  | ork                                                | 76 |  |  |

| 6  | Conclusions                                                 |         |                                                    | 78 |  |  |

| Ŭ  | 001                                                         | crusio  |                                                    | 10 |  |  |

| Bi | bliog                                                       | graphy  |                                                    | 80 |  |  |

| A  | ppen                                                        | dices   |                                                    |    |  |  |

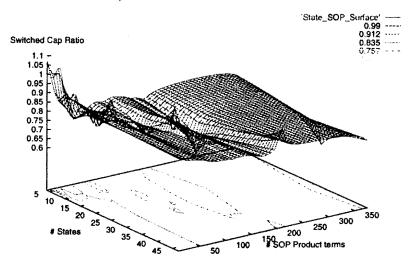

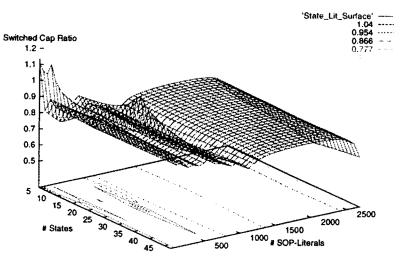

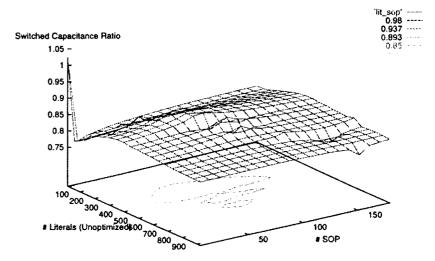

| A  | Sur                                                         | face Pl | ots of Switched Cap Ratio for MCNC91 Circuits      | 85 |  |  |

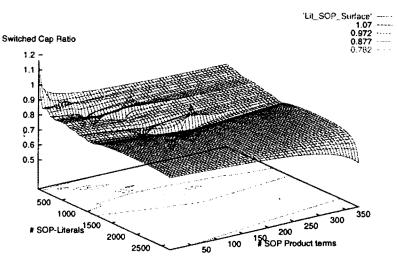

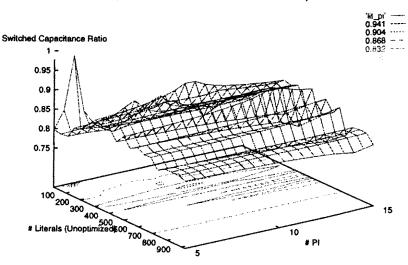

| В  | Sur                                                         | face Pl | ots of Switched Cap Ratio for Random Circuits      | 91 |  |  |

|    |                                                             |         | -                                                  | 95 |  |  |

| С  | C FSM Description in Kiss Format                            |         |                                                    |    |  |  |

| D  | Random Boolean Circuits 96                                  |         |                                                    |    |  |  |

# List of Tables

| 3.1 | Notation                                                          | 30 |

|-----|-------------------------------------------------------------------|----|

| 4.1 | Characteristics of MCNC91 Benchmark FSM Circuits                  | 54 |

| 4.2 | Run Times for High-level Logic Synthesis of 13 MCNC91 FSM Cir-    |    |

|     | cuits Using SIS                                                   | 56 |

| 4.3 | Results of Least Squares Solution in Predicting Switched Capaci-  |    |

|     | tance Ratio for 11 MCNC91 Circuits                                | 59 |

| 4.4 | Results Of Least Squares Solution in Predicting Switched Capaci-  |    |

|     | tance Ratio for 51 Randomly Generated Circuits                    | 64 |

| 4.5 | Results of Spearman Rank Correlation Test For Test of Correlation |    |

|     | Between Top-level Variables and Switched Capacitance Ratio        | 67 |

|     |                                                                   |    |

# List of Figures

| $\begin{array}{c} 1.1 \\ 1.2 \end{array}$ | Power Estimation Time vs. Level of Hierarchy       2         Sources Of Power Dissipation In CMOS Circuits       4 |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| 2.1                                       | Model of a Finite State Machine and its State Transition Graph<br>Representation                                   |

| 2.2                                       | Monte-Carlo Power Estimation Method                                                                                |

| 2.3                                       | Structural RTL Representation of an IC                                                                             |

| 3.1                                       | Illustration of Different Synthesis Results for Circuits with same<br>number of ON-minterms and DC-minterms        |

| 3.2                                       | number of ON-minterms and DC-minterms34Power-Ratio Matrix36                                                        |

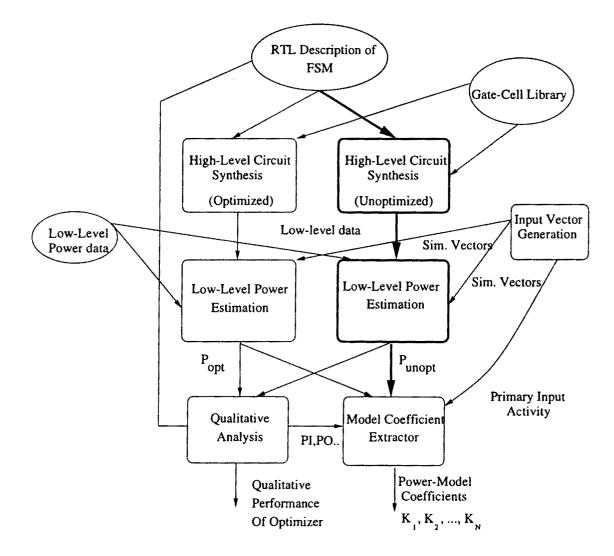

| 3.2<br>3.3                                | Power Model Characterization                                                                                       |

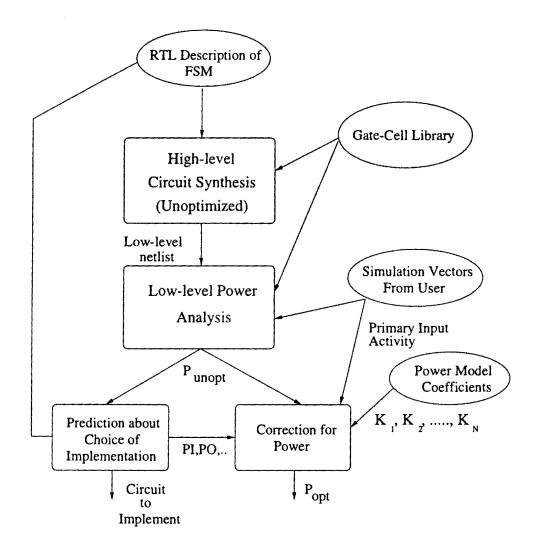

| 3.4                                       | Power Analysis With New Power Model                                                                                |

|                                           |                                                                                                                    |

| 4.1                                       | Implementation of Power Model Characterization                                                                     |

| 4.2                                       | Power Model Performance Evaluation                                                                                 |

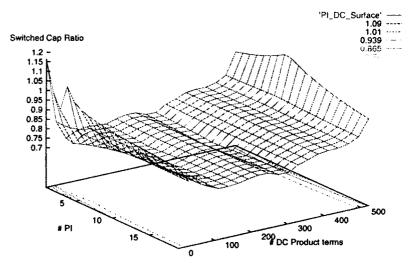

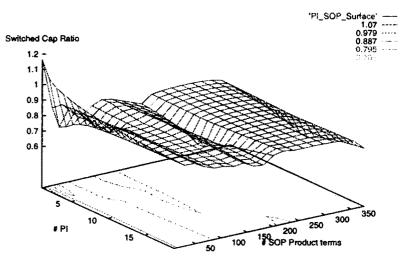

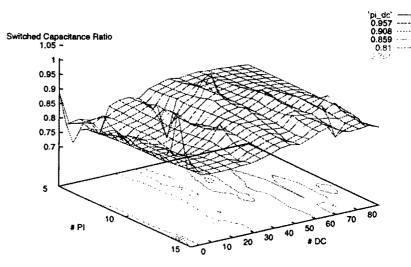

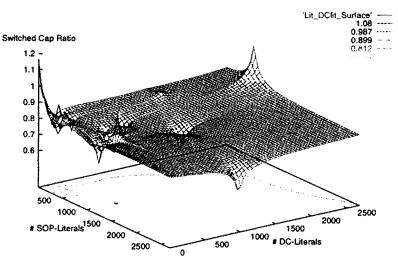

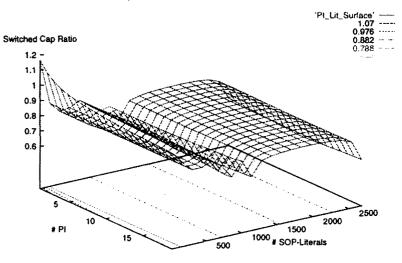

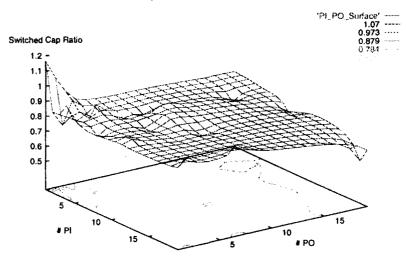

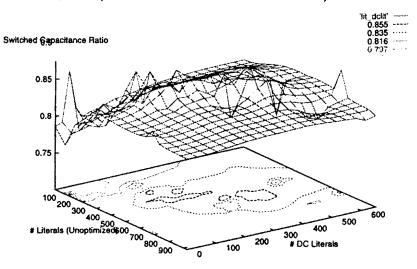

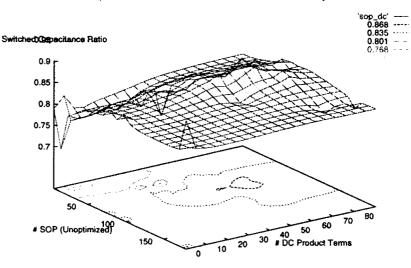

| 4.3                                       | Surface Plot of PI and DC for MCNC91 Circuits                                                                      |

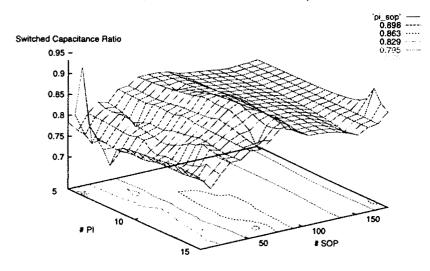

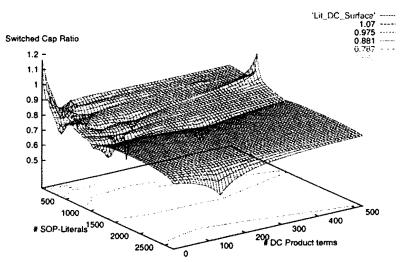

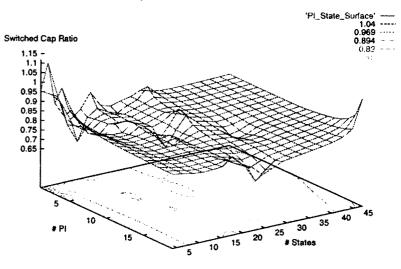

| 4.4                                       | Surface Plot of PI and SOP for MCNC91 Circuits                                                                     |

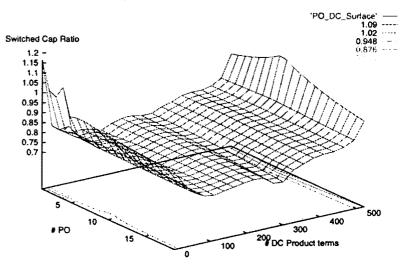

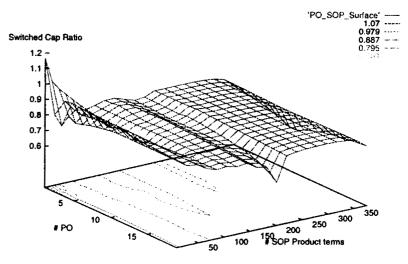

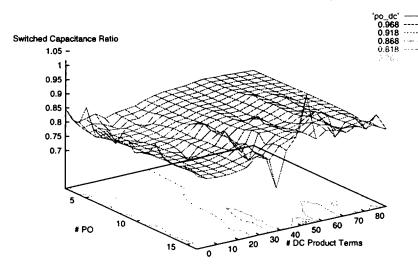

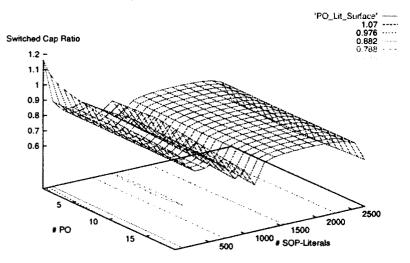

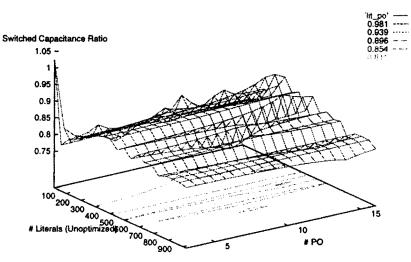

| 4.5                                       | Surface Plot of PO and DC for MCNC91 Circuits                                                                      |

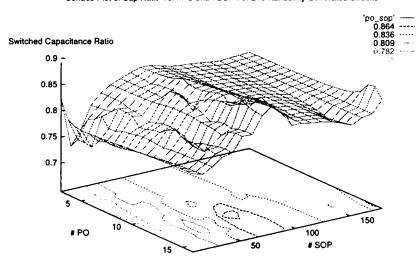

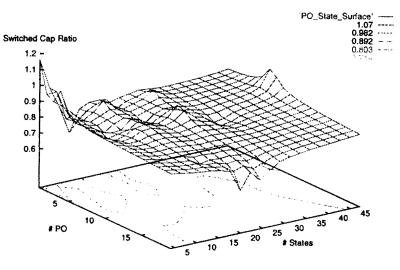

| 4.6                                       | Surface Plot of PO and SOP for MCNC91 Circuits                                                                     |

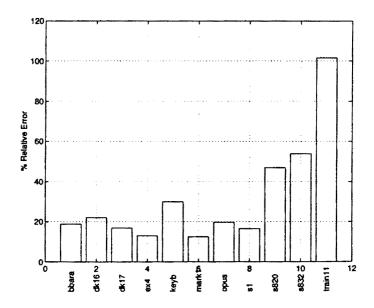

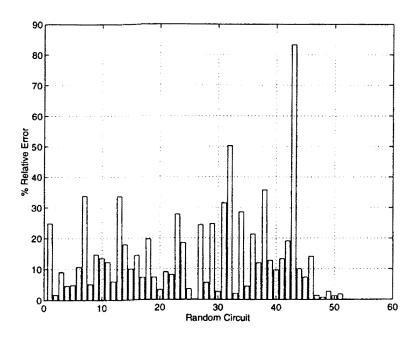

| 4.7                                       | Relative Error in Switched Capacitance Predicted by the Power Modelfor 11 MCNC91 Circuits58                        |

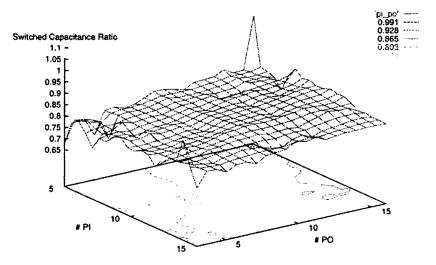

| 4.8                                       | Surface Plot of PI and DC for Random Boolean Circuits 62                                                           |

| 4.0                                       | Surface Plot of PI and SOP for Random Boolean Circuits 62                                                          |

|                                           | Surface Plot of PO and DC for Random Boolean Circuits 63                                                           |

|                                           | Surface Plot of PO and SOP for Random Boolean Circuits 63                                                          |

|                                           | Relative Error in Switched Capacitance Predicted by the Power Model                                                |

| 1.12                                      | for 51 Randomly Generated Boolean Circuits                                                                         |

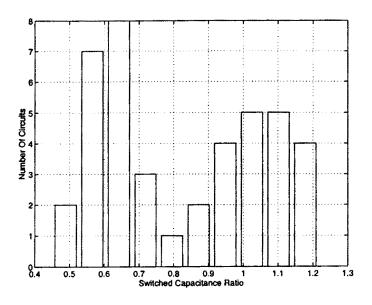

| 4 13                                      | Distribution Of Switched Capacitance Ratio for 41 MCNC91 Bench-                                                    |

| 1.10                                      | mark Circuits                                                                                                      |

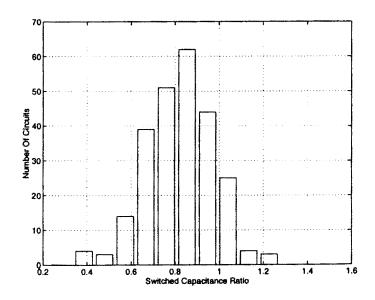

| 4.14                                      | Distribution Of Switched Capacitance Ratio for 249 Randomly Gen-                                                   |

|                                           | erated Boolean Circuits                                                                                            |

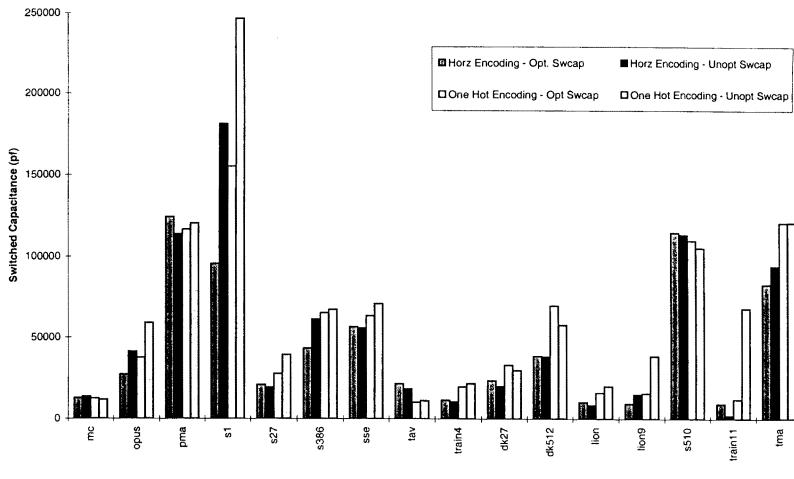

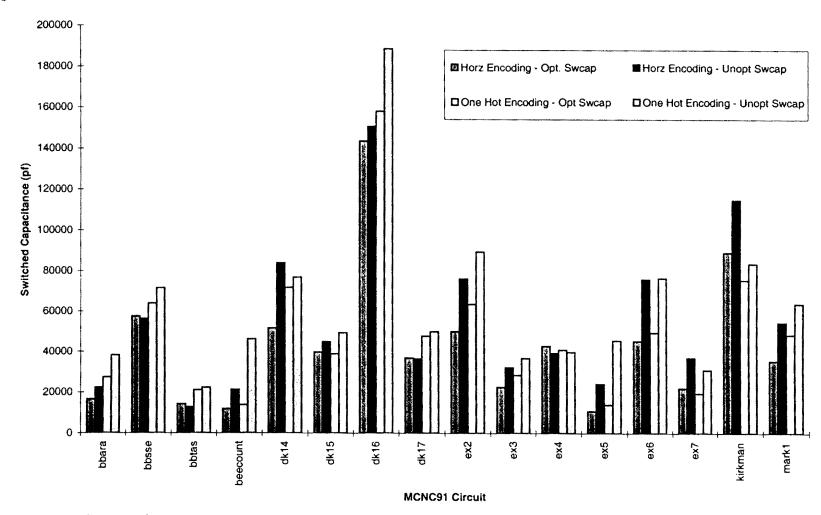

| 4.15                                      | Switched Capacitance Values of 32 MCNC91 Benchmark Circuits                                                        |

|                                           | Implemented with One-Hot and Horizontal Encodings - (a) 73                                                         |

|                                           |                                                                                                                    |

| 4.16 | Switched Capacitance | Values of 32 | MCNC91      | Benchmark     | Circuits   |    |

|------|----------------------|--------------|-------------|---------------|------------|----|

|      | Implemented with One | -Hot and Hor | izontal End | codings - (b) | <i>.</i> . | 74 |

.

# Chapter 1

# Introduction

The growing demand for portable electronic devices has led to an increased emphasis on power consumption within the semiconductor industry. Consumers demand smaller devices at lower prices and increased speed. This demand for smaller size and higher speed has resulted in extremely dense designs. Functionality which was once achieved with several chips is now being integrated into a single chip. This has led to increased thermal concerns and an acute concern over how to sustain and improve battery life. Overheating and battery life are major concerns in portable consumer products. A design that generates too much heat or shortens battery life can delay or sometimes obstruct the successful introduction of a new product. The best and most cost effective solution is for designs to consume less power and this requires a methodology for practical power analysis. Designers are now encouraged to consider the impact of their decisions not only on speed and area, but also on power, throughout the design process. CAD (computer aided design) tools are aiding them in solving many of the problems associated with low power design.

# 1.1 Power Estimation - The Variety of Solutions

Power estimation of a CMOS VLSI chip is possible at different levels in the design hierarchy - transistor, gate, RTL (architectural), behavioral - each offering its own advantages and disadvantages. As you move up the design hierarchy, from

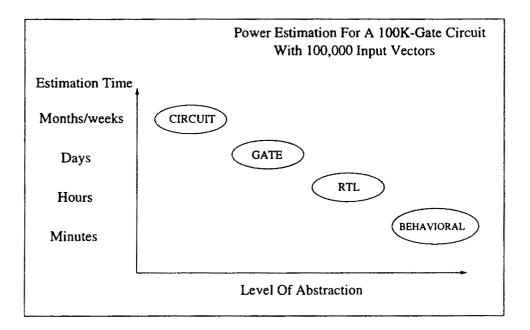

Figure 1.1: Power Estimation Time vs. Level of Hierarchy

transistor to behavioral, you gain in speed but lose in accuracy. Figure 1.1 shows the time needed for power estimation versus the level of abstraction [Nur97]. At RT and behavioral levels, accurate quantitative power measurements become a hard problem. Qualitative measures that help designers in choosing the right kind of circuits to implement from among the available design choices, are useful at these early stages of the design process.

At each of these levels, designers require a full spectrum of analysis choices : estimation, optimization and simulation. Although research has produced some promising methods [Landman94] to help designers create reduced-power systems and chips, a full power analysis solution still presents a significant development challenge. While most agree that design changes at the earlier stages of the design process (architecture or RTL) offer the highest potential gain, a proven general methodology is not yet available. Available solutions are very limited in their scope. At the other end of the spectrum, there is transistor-level analysis, which enables the highest level of accuracy, but is simply not an option for most designers, because of the simulation time involved with transistors. Gate-level power analysis is faster by several orders of magnitude than transistor-level analysis while still providing the accuracy necessary to produce low power designs. All details about transistors are abstracted away in gate-level analysis which makes them much faster than transistor-level analysis. While RTL estimation is typically used to provide early feedback to the designer to make decisions among design choices, gate/transistor level analysis is used for formal verification of a design's power consumption.

# **1.2** Sources of Power Consumption

Power consumption in CMOS circuits can be divided into two types: static and dynamic, also known as DC and AC power.

### 1.2.1 Static Power

Static power represents the power dissipated when a gate is in a steady state. Although the static power is only a small component of the total power, it is becoming important for portable designs where static power dissipation during idle phases becomes a significant part of the overall power dissipation. The sources of static power dissipation in a digital CMOS device are

- leakage currents

- static currents.

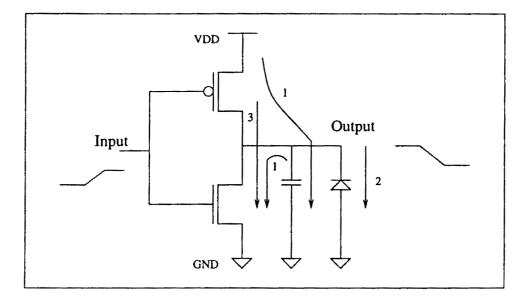

Leakage currents consist of reverse-bias diode leakage at the transistor drains, and sub-threshold leakage through the channel of an off device. This is shown with arrow 2 in Figure 1.2. Leakage power is process technology dependent and typically in the microamp range. While this is typically a small fraction of the total power consumption, it could be significant for a system application which spends much of its time in standby operation, since this power is always being dissipated even when no switching is occurring. Static current represents the current which is

Figure 1.2: Sources Of Power Dissipation In CMOS Circuits

continuously drawn from the supply in certain kinds of circuits, when the circuit is in a certain state. For example, in a pseudo-NMOS inverter [Weste93], the pullup transistor is on all the time and whenever the pull-down transistor is also on, current flows from supply to ground, continuously, contributing to static power.

### 1.2.2 Dynamic Power

Dynamic power represents the power dissipated when a gate is switching. The sources of dynamic power consumption are

- Short circuit current

- Capacitive load switching current

The short circuit current is the current flowing directly from power supply positive to ground when both NMOS and PMOS are conducting at the same time during an output transition. This is shown with the arrow labeled 3 in Figure 1.2. The capacitive load switching current is the current flowing in charging and discharging the output load capacitance, during an output transition. This is shown with arrows labeled 1 in Figure 1.2.

The total power of a CMOS gate is then,

#### Totalpower = Dynamic power + Static power

In modern CMOS circuits, dynamic power is the dominant component of the total power. This will change in the future as we move towards very low supply voltages, and static leakage power could become a significant portion of the overall power dissipation [Chandrakasan96]. Veendrick [Veendrick84] showed that with proper gate sizing, the short circuit component of the dynamic power will be less than 15% of the total power dissipation of the circuit. Hence the capacitive load switching power becomes the dominant component of power dissipation in digital CMOS ICs. The average capacitive load switching power of a digital CMOS gate can be given as

$$P_{av} = \frac{1}{2} . C_L . V_{dd}^2 . F_{clk} . \alpha$$

(1.1)

where,

$C_L$  is the load capacitance at the output of a gate  $V_{dd}$  is the power supply voltage  $F_{clk}$  is the clock frequency of the circuit  $\alpha$  is the activity factor

The activity factor  $\alpha$  is the probability with which the output of the gate changes state during a clock cycle. The term  $\alpha F_{clk}$  is then the frequency at which the gate output switches and is referred to as *transition density* of the node.

## **1.3 Factors Affecting Power Dissipation**

From the power equation Eqn. 1.1, it is clear that the power dissipation of a CMOS circuit depends on the load capacitance, the power supply voltage and the clock frequency. The load capacitance is fixed by the circuit structure. The supply voltage is constant for a design and so is the clock frequency. The activity factor,  $\alpha$ , depends on

- 1. Switching activity of circuit inputs

- 2. Spatial and temporal correlations among the circuit inputs

- 3. Logic function of the circuit

The first factor is related to the pattern dependency of the power as discussed in [Najm1'95]. The higher the input switching activity, the higher the power. This value can vary for different circuits and different data representations. For finite state machines, this varies from 0.08 to 0.18 [Rabaey96]. For video signals the most significant bits have switching activities of 0.1 whereas the least significant bits have 0.5. The commonly used Uniform White Noise (UWN) has a switching activity range of 0.4-0.5. The second factor takes care of the temporal correlations and spatial dependencies of the circuit inputs. For example, if two inputs to a circuit cannot be one at the same time, then they are said to be spatially correlated. If there are dependencies for a signal in the time domain, then there is said to be a temporal correlation for that signal (e.g. a signal is a 1 only if its previous value is 0). Feedback in a finite state machine (FSM) creates temporally and spatially correlated signals. These correlations at the inputs of a circuit determine what switching happens at the output, as not all switching combinations might then be possible [Pedram96]. The logic function of the gate naturally plays a part in the activity of the output. For example, the activity at the output of a 2-input XOR is 1/2, if all possible combinations of input transitions (equally likely) are considered (i.e. 16). While the activity at the output of a two input AND gate is 3/8, if all

possible combinations of the input transitions are considered.

# **1.4** Combinational Circuit Power Estimation

Pure combinational circuits are also called *datapath* circuits in the IC jargon. They are identified by a lack of a memory element in the circuit. Power estimation techniques for these kinds of circuits can be divided into low-level (gate/transistor) estimation techniques and RTL (architectural) estimation techniques.

### 1.4.1 Low-level Power Estimation

Low-level techniques use a gate or a transistor as the basic design unit. These techniques provide very good accuracy because they use accurate transistor or gate models. And because they work with a fixed circuit structure, they account for all signal correlations within the circuit. Transistor-level analysis is much more flexible than gate-level analysis in that it can handle various device models and design styles. But it is slow and so cannot scale to higher levels of integration. Gate-level analysis is less flexible than transistor-level analysis but much faster. The low-level power estimation techniques can be divided into:

- 1. Simulation-based techniques

- 2. Analytical techniques

Simulation-based techniques simulate the circuit with a sample set of input vectors and then report the power resulting from the simulation. An important design question is the number of input vectors to be used for the simulation. Techniques like Monte-Carlo [Najm92] [Xakellis94] solve this problem by an appropriate choice of input vectors, based on statistical theory. IRSIM [Horowitz89], PowerMill [Deng94] (transistor-level) and QUICK POWER [Nguyen97] (gate-level) are examples of this kind of simulator. Analytical techniques propagate the circuit input signal probabilities (which is the probability of the node being in '1' state) from the primary inputs of the circuit to the primary outputs of the circuit, without any simulation. Since they do not use any simulation, they are quite fast. Once the switching activity of each node in the circuit is known, the average power dissipated by each node can be calculated using Eqn. 1.1. Addition of all node powers yields the average circuit power. These techniques use either a zero delay model or a finite delay model [Ghosh92] [Najm94] for the gates. The finite delay model has the ability to capture glitches and the zero delay model does not have that capability. The assumption made while propagating the activity values is that the input values at two consecutive clock cycles are temporally independent. With this assumption, the switching activity of a circuit node can be expressed as  $\alpha = 2p(1 - p)$ , where p is the probability of the signal being a '1'. There are other proposed methods which improve this basic model by including spatial and/or temporal correlations [Roy94] [Marce94] in the input signals in the calculation of switching activity.

### **1.4.2 RTL Power Estimation**

While low-level estimation techniques use a gate or a transistor as the basic unit of design, RTL estimation techniques for the *datapath* work with *reusable microarchitectural blocks* (like adders, multipliers, memory) as the basic unit of design. RTL techniques are also sometimes referred to as architectural techniques. Since the granularity of an RTL description is larger, the power analysis at this level is faster, but this speed of estimation comes at the expense of accuracy. The combinational power estimation techniques at this level can be divided into two groups: predictive and descriptive. These two techniques differ in that the predictive techniques do not require a pre-characterization step as part of the power estimation process whereas the descriptive techniques do.

Predictive techniques proposed thus far depend on

- Complexity-based models or

- Entropy-based Models

Complexity-based models return quick, but inaccurate values for power by characterizing the complexity of the design in terms of the gate-equivalent count [Glaser91] [Svensson94]. Gate equivalent count is the average number of reference gates needed to build a particular functional block. These models require only information about the gate-equivalent count and technology parameters. The main drawback of these models, is that the predicted power is independent of the circuit input activity, which is not true in practice.

Entropy-based techniques [Nemani97] [Marce96] introduce the concept of Entropy, which is a measure of the amount of information available in a signal. The entropy-based power model proposed by Najm et. al. in [Nemani97], is

### Power = Average Entropy.Area

The entropy term is an approximation for the average switching activity of the circuit and the area term is an approximation for the total switched capacitance of the circuit. The basic assumption made while deriving the above model is that, the capacitance of the circuit is uniformly distributed over the circuit. Temporal and spatial correlations among the input signals are ignored. The average entropy of the circuit is calculated using the approximation that the entropy of the circuit nodes decreases quadratically with circuit depth. The area of the circuit is estimated using the concept of "average cube complexity". Average cube complexity is the average number of literals in the prime implicants of the boolean function implemented by a circuit. The relative erroirs of this model are more than 100% in some cases.

Descriptive techniques have a pre-characterization step in the power estimation process and build an RTL power library, which means that the basic RTL blocks used in the design (e.g. multiplier, multiplexer, ALU) are pre-characterized for their power dissipation. The circuit functionality and structure are known apriori for these RTL blocks and a characterization process of these RTL blocks would yield the RTL power library. Fixed activity descriptive techniques are based on the assumption of fixed input activity for the functional blocks. Example of fixed activity models is PFA [Chau91], which uses uniform white noise activity for the circuit inputs. Activity sensitive models take into account the effect of circuit input activity on power. Examples are ESP [Sato95] and dual bit type method (DBT) [Rabaey94] [Rabaey95]. The power model in all these techniques is basically an equation which gives the relation between circuit input activity, complexity of the circuit and the power. For example, the data-path power model for DBT, which works with 2's complement representation of data, is

$$P_{av} = (N_u C_u + N_s C_s) V_{dd}^2 f$$

(1.2)

$N_u$  and  $N_s$  are the number of sign and data bits in 2's complement representation of the data.  $C_u$  and  $C_s$  are the extracted coefficients in the characterization process. The activity factors are embedded in these coefficients. [Gupta97] approaches activity sensitive power modeling by building a power table indexed by the primary input activity and the primary output activity. The characterization process of the circuit yields this table. [Nur97] and [Wu97] independently propose an RTL power estimation procedure, where the power dissipated by an RTL block is captured as an equation in terms of the circuit input activity. They account for limited spatial and temporal correlations at the circuit inputs.

All the methods described so far are targeted towards power estimation of pure combinational logic blocks (datapath logic). To complete the RTL power picture of an IC, power estimation methods need to be developed for the control logic (finite state machines) also. These control circuits have a memory element in them and the combinational techniques described above cannot be directly applied for their power estimation. *Control logic* has the same meaning as *sequential circuit*, *finite state machine* and *random logic* and these will be used interchangeably throughout this thesis. The next chapter discusses the methods proposed so far for power estimation of control logic (sequential circuits). Chapter 3 discusses the new method proposed in this thesis for RTL power estimation of control logic. Chapter 4 presents the results of evaluation of the new power model. Future work and conclusions follow in the last two chapters.

# Chapter 2

# Previous Work In Sequential Circuit Power Estimation

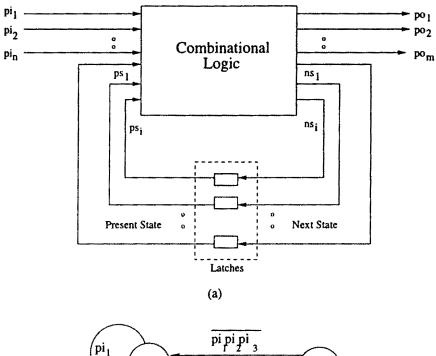

All sequential circuit power estimation techniques assume the popular and wellstructured design style of a synchronous sequential circuit, shown in Figure 2.1(a). The circuit contains a single clock driving a bank of edge-triggered flip-flops. On the rising edge of the clock, the flip-flops transfer the values at their inputs to their outputs. The signals  $pi_1, pi_2, ..., pi_n$  are the primary inputs to the sequential logic circuit and the signals  $po_1, po_2, ..., po_m$  are the primary outputs of the sequential logic circuit and the signals  $p_{s_1}$ ,  $p_{s_2}$ , ...,  $p_{s_i}$  are the present-state lines. Signals  $ns_1, ns_2, ..., ns_i$  are the next state lines. The primary inputs and the present state lines determine the next state lines and the primary outputs and this circuit implements a finite state machine (FSM). During any clock cycle the finite state machine is in a known state, determined by the values of the present state lines. A symbolic representation of a finite state machine is shown in Figure 2.1(b). Such a representation is called a state transition graph (STG). A state transition graph enumerates all the different states in a state machine and the primary input combinations that take the state machine from one state to the other. The transitions from one state to the other are indicated by directed arrows in the STG and the primary input combinations that cause a transition to occur are shown beside the transition. For example, in the STG in Figure 2.1(b), the state machine transitions from state S1 to S2 when the primary input combination  $\{pi_1, pi_2, pi_3\}$  is  $\{111\}$ .

.

Figure 2.1: Model of a Finite State Machine and its State Transition Graph Representation

.

Sequential circuit power estimation techniques differ from combinational circuit power estimation techniques in that the sequential circuit power estimation techniques need to account for the presence of feedback (through the state lines) in the circuit. There is no feedback in pure combinational circuits. This presence of feedback in the circuit makes sequential circuit power estimation a hard problem. It is hard on two counts:

1. The presence of feedback in an FSM introduces spatial and temporal correlations among the state inputs to the combinational logic block. These correlations are very important to power estimation [Kozhaya97] and any sequential circuit power estimation technique should model these correlations properly for accurate power estimation. Not all methods proposed in literature model these correlations for want of faster estimation and so loose some accuracy in the estimation.

2. The test vectors applied to the sequential circuit during power estimation should not take the state machine into parts of the state space where it does not belong i.e., into modes of operation that are unrealistic and may never be exercised in practise. For example, the transition from state S1 to S2 in the STG in Figure 2.1(b) might rarely happen in a typical application of the finite state machine, whereas with randomly generated inputs to the finite state machine, this transition might happen more often. These modes of operation of an FSM are application specific. The solution to this problem is to choose vectors directly from the target application and hence to exercise the state machine as it would be in the real world. But these sets of vectors tend to be very large (sometimes in millions) and it is unrealistic to simulate the FSM for all of these vectors. Vector compaction techniques come in to play here.

With this background, let us review the previous work done in sequential circuit power estimation. Power estimation methods for sequential circuits have been proposed at both the RTL and gate-level of abstraction. RTL techniques rely on building a *power model* for finite state machine power dissipation, either through a characterization process or through theoretical models for circuit activity. Gatelevel techniques estimate power either through simulation of the circuit or through analytical techniques for propagating the circuit input switching probabilities to the output of the circuit. Power estimation at the RT-level has the advantage that if the circuit input statistics change, only the power model needs to be reapplied with the changed input statistics, to reevaluate the power. This is a trivial process. At gate-level, the designer needs to go through the whole process of power estimation every time the input statistics change. This might include simulation of the circuit or re-propagating the circuit input probabilities to the output. This is a time consuming process.

# 2.1 Gate-level Sequential Circuit Power Estimation

Power estimation techniques at the gate-level of abstraction, use gates (e.g. Nand, Nor, Xor) as the basic design unit. The RTL description of the design is synthesized into gates (unique to each technology-library) and the resulting gate netlist is the input to the gate-level power estimation techniques. Techniques at this level are either simulation-based or analytical.

### 2.1.1 Simulation-Based Techniques

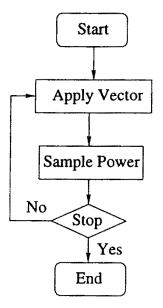

Simulation-based techniques, in general, apply a limited set of vectors to the circuit under consideration and observe the resulting power dissipation. The flow chart in Figure 2.2 gives an overall view of one kind of simulation-based technique called Monte-Carlo. The vectors applied to the circuit can be either randomly generated or could be picked from a set of typical vectors from an application (if available). The power value at the end of the sample phase is noted and used to decide whether to stop the process or to apply another vector. The decision is made based on the mean( $\eta_T$ ) and standard deviation( $s_T$ ) of the power values observed at

Figure 2.2: Monte-Carlo Power Estimation Method

the end of successive iterations. For a given confidence level  $(1 - \alpha)$ , the circuit is simulated till,

$$\frac{t_{\alpha/2}s_T}{\eta_T\sqrt{N}} < \varepsilon \tag{2.1}$$

where N is the number of the simulation run  $\varepsilon$  is the percentage error tolerable in the measured power  $t_{\alpha/2}$  is obtained from the t distribution [Papoulis84] at N-1 degrees of freedom

The circuit power is found as the average value of the power values obtained during the successive sample phases.

Najm et. al. proposed a Monte-Carlo simulation-based technique [Najm2'95] which takes advantage of the existing combinational circuit power estimation techniques, to compute the average power of a sequential circuit. They break the FSM into a combinational logic block and a set of latches and independently estimate their power. To do so, the state line statistics at the input of the combinational logic block of the FSM must be known. Their technique, then, consists in applying

a number of *randomly* generated input vectors to the circuit and collecting statistics (i.e. signal probabilities) on the latch outputs using fast zero-delay logic simulation or using functional simulation of a structural RTL description. High-level simulation can be done very fast, so one can afford to simulate a large of number cycles. Once these statistics are available, it is then possible to use any of the existing combinational circuit techniques, discussed in the previous chapter, to compute the total power.

The state line probability estimation starts with putting the FSM in some known initial state X0. With the assumption that state of the machine becomes independent of its initial state as time  $\rightarrow \infty$ , we can write for the signal probability of a state signal  $ps_i$ :

$$\lim_{k \to \infty} P(ps_i | X0) = \lim_{k \to \infty} P(ps_i (k) = 1 | X(0) = X0) = \lim_{k \to \infty} P(ps_i (k) = 1) = P(ps_i)$$

(2.2)

The index k represents time. The term  $P(ps_i|X0)$  represents the signal probability of the state signal  $ps_i$ , given that the initial state of the state machine is X0. So the method consists of estimating  $P(ps_i|X0)$  for increasing values of k until convergence according to the above equation is achieved. The method is actually implemented by doing repeated simulation runs of the circuit, starting from some initial state X0, and randomly generated input vectors (consistent with the statistics of the primary inputs of the state machine) and each of these will result in a logic waveform  $ps_i^{j}(k)$ , k=0,1, 2.... where j indicates the run number. If we average the results at every time k, we obtain an estimate of the probability at that time as follows:

$$ps_i^{N}(k) = \frac{1}{N} \sum_{j=1}^{N} ps_i^{j}(k)$$

(2.3)

From the law of large numbers, it follows that:

$$\lim_{N \to \infty} p s_i^N(k) = P(p s_i | X0)$$

(2.4)

The value of N for a user-specified error-tolerance and confidence level can be found from estimation of proportions as  $N \ge max(N_1^2, N_2^2, N_3^2)$ , where

$$N_1 = \frac{z_{\alpha/2}2}{2\varepsilon} \quad N_2 = \frac{z_{\alpha/2}\sqrt{2\varepsilon + 0.1} + \sqrt{(\varepsilon + 0.1)z_{\alpha/2}^2 + 3\varepsilon}}{2\varepsilon}$$

$$N_3 = \frac{\sqrt{63} + z_{\alpha/2}}{2\sqrt{\varepsilon}}$$

So with N known, N parallel simulations of the circuit are started and simulated for increasing values of k till  $P_k(ps_i|X0) = P(ps_i)$ , as per Eqn. 2.2. To answer the question of what value of k is large enough to achieve this convergence, Najm starts two sets of simulation runs of the circuit with different initial states X0 and X1 and finds out  $P(ps_i|X0)$  and  $P(ps_i|X1)$ . When both the difference and average remain within a window of  $\pm \varepsilon$  for three consecutive time instances, convergence is declared. The disadvantage with this approach is that the latch and combinational logic block are decoupled during power analysis and hence the spatial and temporal correlations at the state inputs of the combinational block are ignored. This leads to inaccuracies. Unfortunately, no results for actual power measurements are reported in the paper. Only the efficiency of the method in computing the state line statistics for uniform white noise (UWN) inputs is reported.

An improved Monte-Carlo method proposed in [Saxena97] consists of simulating the finite state machine as one whole block, thereby automatically accounting for the spatial and temporal correlations among the state bits of the FSM. Here again, the assumption is made that the FSM becomes independent of the initial state as the circuit is simulated for an increasing amount of time. The power estimation procedure starts by doing two sets of N simulations each. The two sets have different initial states for the state machine. All simulations within a set have the same initial state and the input vectors for each of these simulation runs are chosen independent of each other. For each simulation run in a set, j=1,2,...N and for each clock cycle k=1,2,... we can compute the energy consumed per cycle and the power up to time K:

$$P_{K}{}^{j} = \frac{1}{KT_{c}} \sum_{k=1}^{K} e^{j}(k)$$

(2.5)

where  $T_c$  is the clock cycle time.

$e^{j}(k)$  is the energy in cycle k in the simulation run j.

For a given K, the set  $(P_K^1, P_K^2, ..., P_K^N)$  will form a random sample of the random variable  $P_K$ , and from law of large numbers, the average of these values will tend to  $E(P_K|X0)$ .

$$\mu_N(K) = \frac{P_K^{\ 1} + P_K^{\ 2} + P_K^{\ 3} + \dots + P_k^{\ N}}{N} \approx E[P_K|X0]$$

(2.6)

Najm fixes N to be 50 and to improve the convergence of the average value of the 50 samples to  $E(P_K|X0)$ , he increases the value of K, because

$$\lim_{k \to \infty} Var[P_K | X0] = 0 \tag{2.7}$$

If the value of K is large enough such that

$$\sigma_N(K) \le \frac{\varepsilon \mu_N(K) \sqrt{N}}{z_{\alpha/2}} \tag{2.8}$$

is satisfied, then the condition in Eqn. 2.6 is achieved. We can then start monitoring the two power values resulting from the two sets of runs to determine if their  $\mu_N(K)$ have converged to  $E(P_K)$ . When this convergence is achieved, the simulation is stopped. Because of the assumption that the machine becomes independent of the initial state as time tends to infinity, the two values of power must converge to the same value as simulation is done longer and longer. Convergence is declared when the average and the difference of the two values are within a window of  $\pm \varepsilon$ , in three consecutive clock cycles. The advantage with this approach is that the correlations at the state inputs of the finite state machine are automatically considered as the latch and combinational logic block are not decoupled. Errors of less than 5% at reasonable computation time have been reported.

The modified Monte-Carlo method [Roy96] removes the assumption made in [Najm2'95] [Saxena97], of the state-machine becoming independent of the initial state as the machine is exercised over a long period of time. This could prove important in some machines because of the existence of near-closed (NC) sets, which can bias the sampled power value and cause the simulation to terminate improperly. A Near-closed set is a set of states such that once the state machine enters that set of states, the probability that the state machine will leave that set of states is very low, or vice-versa. These NC sets are a problem, because if during simulation the initial state of the state machine is chosen to be in one of these sets, then the sampled power value during the simulation will be reflective of only those states inside that set. This is because with the set of vectors applied during the simulation, the state machine might have never gone from one NC set to the other. This method builds over the existing Monte-Carlo techniques. The only difference is that, instead of simulating the circuit with some random initial state, this method carefully selects the initial state, after identifying the presence of nearclosed sets. For example, if there are two near-closed sets in a state machine, with probabilities  $P(G_1)$  and  $P(G_2)$   $(P(G_1) + P(G_2) = 1)$ , then in each of N simulations of the circuit, the initial state is chosen from G1 with probability  $P(G_1)$  and from  $G_2$  with probability  $P(G_2)$ . So the normalized power would be given as

$$Power = (Power|G_1)P(G_1) + (Power|G_2)P(G_2)$$

(2.9)

The increased accuracy that this method brings, comes at the cost of extra computation to determine first the presence of near-closed sets and if present, their probabilities. Average relative errors of less than 3% have been reported with this method.

Yuan and Kang [Kang97] propose a statistical procedure to overcome the problem in all statistical mean estimation techniques of requiring independent and identically distributed power data i.e., a random sample of mutually independent power data. The sequential procedure they recommend determines an appropriate *independence interval*, separated by which two sample power data in a power simulation can be treated as mutually independent. A distribution-independent stopping criterion is applied to choose an appropriate convergent sample size for the power data. Very accurate results have been reported for this method (less than 1.5% error), for input activity of 0.5.

All the simulation-based techniques discussed so far require simulation vectors to be either randomly generated or to be picked directly from a typical application of the state machine. Sometimes these typical vector sets are very large (in the order of millions). It is unrealistic to simulate the machine for all these vectors. Techniques have been proposed for vector compaction while preserving the correlations present in the vector set, both temporal and spatial. They either use data structures [Pedram97] [Marce97] to capture the correlations of a fixed order in the input or use statistical techniques [Kozhaya97] to select a limited set of "blocks of vectors" from the large input set.

### 2.1.2 Analytical Techniques

Analytical techniques for sequential circuit power estimation, in general, are based on solving a system a linear or non-linear equations, for the state line probabilities. All these techniques assume that the FSM is Markov [Papoulis84], while calculating the state line probabilities, so that its future is independent of its past once its present state is known. Once the state line probabilities are known, and with primary input probabilities available from the user, the activity of the internal circuit nodes is calculated by propagating these input signal probabilities. The input signal/state probabilities are propagated to the internal circuit nodes under the assumption of input spatial independence. Average power of the circuit is then calculated from the basic power equation. The approach in [Hachtel] attempts a direct solution of the Chapman-Kolmogorov equations [Papoulis84]. While it is accurate, it remains computationally quite expensive and the largest test cases presented contain less than 30 latches. The method in [Devadas94] solves a system of non-linear equations to get the present-state probabilities. Given the probabilities  $p_1, p_2, ..., p_n$  of the primary inputs of the state-machine and the probabilities of the present state lines  $P_{ps} = (ps_1, ps_2, ..., ps_n)$  and assuming that the present state lines are independent, one can compute the next state probabilities as  $F(P_{ps})$ . The function F() is non-linear and is determined by the combinational function implemented by the state machine. In general, if the next state probabilities form a vector  $P_{ns}$ , then  $P_{ns} \neq F(P_{ps})$ , because the present state lines are not independent. But the method in [Devadas94] makes the assumption that  $P_{ns} \approx F(P_{ps})$ . Since  $P_{ns} = P_{ps}$ , due to feedback, the system solves for the system P = F(P). One of the problems with this approach is that of independence assumption for the state lines, which is not true in practice. [Devadas94] also tries to correct this problem by accounting for m-wise correlations between state bits when computing their probabilities. Inspite of all these shortcomings, good results have been reported with this method (errors less than 5%).

# 2.2 RT-level Sequential Circuit Power Estimation

Register-Transfer Level power estimation of sequential circuits is better than gate-level power estimation in two ways:

- Power estimation at the Register-Transfer level is available earlier in the design cycle. In the absence of RTL power estimation, synthesis of the RTL design to gates and power estimation with gate-level power tools are necessary steps in the design process.

- Power estimation at this level is faster. This is because at the RT-level we work with boolean equations rather than circuits, which means that the granularity is larger.

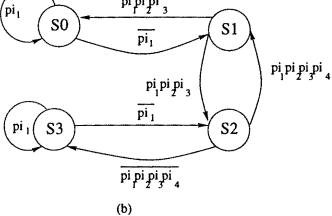

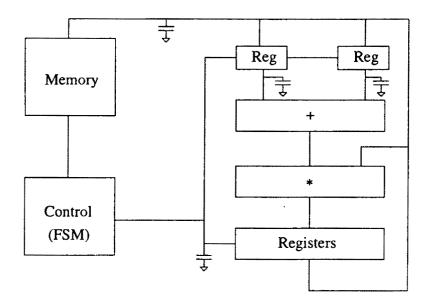

The structural RTL representation of a VLSI IC is shown in Figure 2.3 [Nur97]. At the RT-level, an FSM has no fixed circuit structure yet i.e., the RTL description of

Figure 2.3: Structural RTL Representation of an IC

the FSM has not yet been synthesized into gates. This makes power estimation of an FSM at RT-level a very hard problem. Each design has its own unique control path, which means that there are, to most parts, no standard control path designs. This is unlike the datapath elements (micro-architectural blocks) like the adder, multiplexer etc., which are commonly used in most designs. The functionality and circuits for these standard datapath elements are known apriori, which in effect, fixes the physical capacitance (or power) of these elements. Characterizing these known circuits for power would then allow for RTL power estimation of the datapath. But the power dissipated by a finite state machine depends on the specification of the finite state machine, which is not known until run time. So power prediction at this level has to be purely based on parameters available at this level, like the number minterms in the boolean function representing the state machine, the number of literals in the sum of product terms of the boolean function etc.. All proposed techniques for sequential circuit power estimation at RT-level fall into one of two categories:

• Predictive techniques

#### Descriptive techniques

All of these techniques break the FSM into a combinational block and a set of latches. The techniques then estimate the power of the combinational block. The latch power, which could be calculated from a knowledge of the latch output activity obtained from a high level simulation, is then added to the combinational logic power to yield the total power. Since these techniques decouple the latch and the combinational logic block, the correlation information at state inputs of the combinational logic block are lost.

## 2.2.1 Predictive Techniques

These techniques estimate power without the need for a pre-characterization step. All predictive techniques found in literature for FSM power estimation at RT-level use the concept of entropy, an information theoretic measure, to estimate circuit activity. The entropy of a random boolean variable X is defined as

$$H(X) = p \, \log \frac{1}{p} + 1 - p \, \log \frac{1}{1 - p} \tag{2.10}$$

where p represents the signal probability. In the entropy-based power model presented in [Nemani97] [Nemani96], the authors observe that the power is proportional to the product of physical capacitance and activity. They then use area as a measure of physical capacitance and entropy as a measure of activity. In using entropy as an approximation for activity, the input signals are assumed to be temporally independent.

$$P_{av} \propto Capacitance imes Activity \propto H \sum_i C_i$$

A model is then derived for the average entropy (H) as a function of input and output entropies, under the assumption that the entropy inside the circuit decreases quadratically with circuit depth. The final expression obtained for the average entropy is shown in Eqn. 2.11, where n is the number of primary inputs, m is the number of primary outputs, H is the total entropy,  $H_i$  is the total input entropy and  $H_o$  is the total output entropy.

$$H \approx \frac{2}{3} \frac{(H_i + 2H_o)}{n+m} \tag{2.11}$$

Nemani and Najm also present a model for the area complexity of a boolean function based on the concept of average cube complexity. Average cube complexity is the average literal count of the prime implicants of the function. The area model is

$$A(f) = 2^{C(f)}k(H)$$

(2.12)

where C(f) is the average cube complexity and k(H) is a proportionality constant that depends on the entropy H. The relative errors of the above models have been more than 100% [Nemani97] in some cases. The average entropy proposed in [Nemani96], underestimated the circuit activity in some examples. This is understood because the circuit activity depends on the functionality of the circuit as well as the type of data being processed. For example, the proposed model will return the same result for two different functions that have identical average entropy. Additionally the average entropy may be predicted to be the same for two different input streams applied to the circuit. Marculescu et. al. [Marce96] have made an effort to estimate switching activity based on both the entropy and the distribution of nodes in the circuit.

All the predictive techniques discussed above have some practical limitations. First of all, they ignore glitch power because they assume zero-delay model of operation. Temporal correlations at the inputs are ignored because of the assumption of independence of signal values in successive clock cycles. And finally, the circuit capacitance is assumed to be uniformly distributed over the circuit, which might not hold in practise.

### 2.2.2 Descriptive Techniques

These techniques require pre-characterization of existing finite state machines of varying complexities and construction of an RTL power model equation. Activity based control model (ABC) proposed by Landman [Landman96] builds a model for an FSM implemented in standard cells as:

$$P_{av} = (C_i t_i N_i N_M + C_o t_o N_o N_m) V_{dd}^2 f$$

(2.13)

The first product term measures the input plane complexity of the FSM i.e., the amount of decoding that needs to be done at the input of the FSM. Similarly the second term measures the output plane complexity.  $t_i$ ,  $t_o$  are the transition probabilities of the inputs and outputs i.e., the fraction of the input and output bits that toggle per cycle.  $N_i$  is the sum of the number of state bits and primary inputs.  $N_o$ is the sum of the number of state bits and primary outputs.  $N_M$  is the number of minterms in the logic minimized control table of the finite state machine.  $C_i$ and  $C_o$  are the capacitive coefficients estimated during the characterization phase. The characterization phase consists of actually measuring the switched capacitance (a proxy for power) for FSM (in control table format) implementations of varying complexities and input and output activities. Since it is impractical to characterize all possible FSM implementations, randomly generated control tables are used instead. The observed switched capacitance values are then used to find the capacitive coefficients that give the best fit to the measured data. All terms except  $N_M$  are available from a high level description/simulation of the state machine.  $N_M$  is obtained by optimizing the circuit using a logic optimizer like espresso and then using the number of min-terms in the minimized boolean table as an estimate of  $N_M$ . Max error of 29% has been reported [Landman96] with this approach. Unfortunately, results of model performance are shown for just two circuits. The disadvantage with this approach is the requirement of a logic optimization step to determine  $N_M$ . State line correlations are not accounted for since this technique decouples the combinational block from the latches.

## 2.3 Chapter Summary

This chapter summarized the techniques proposed so far for sequential circuit power estimation. Each method has its own advantages and disadvantages. Only the gate-level Monte-Carlo simulation-based techniques take care of the correlations among the state bits of a sequential circuit. None of the RTL methods account for the correlations among the state bits. Gate-level circuits require the synthesis of the FSM RTL description to a set of technology-dependent library-gates. None of the RTL methods need this step, though the ABC model requires a single run of a logic-minimization tool like espresso. Errors in excess of 100% have been reported for some of the RTL techniques. Gate-level techniques are much more accurate with errors less than 5%. The power model studied in this thesis takes a path in between the existing RTL and gate-level techniques in an attempt to balance speed and accuracy. This will be discussed in the next chapter. Note that none of the techniques found in literature attempt a qualitative judgement about choice of finite state machine implementation (like one-hot Vs. horizontalencoded FSM) from a set of broad alternatives. They all attempt only a quantitative measurement of the average power of an FSM. The new method studied in this thesis affords both a quantitative measurement of the average power of an FSM and also a qualitative comparison among different finite state machine implementations. This new method is studied in the next chapter.

## Chapter 3

# New RTL Power Estimation Method For Sequential Circuits

Chapters I and II talked about the general problem of power estimation and the methods proposed so far for power estimation of sequential circuits. The picture that emerges from these two chapters is that power estimation at the RT-Level is much faster than at the lower levels, but at a reduced accuracy. The goal of this chapter is to introduce the new method proposed in this thesis for RTL power estimation of sequential circuits. The proposed RTL power estimation technique differs from the existing techniques in two ways:

- It requires a *low-effort synthesis* step as part of the RTL power estimation process. Low-effort typically means synthesis without optimization.

- The model developed is synthesis-tool-specific.

Previous methods were either not synthesis-tool-specific [Nemani97] [Nemani96] [Marce96] or did not require a low-effort synthesis step [Landman96] or both [Nemani97] [Nemani96] [Marce96]. These techniques are fast in power estimation, as is required at the RT-level, but are poor in accuracy. Errors in excess of 100% are reported for some of these techniques, as discussed in the previous chapter. The new method studied in this thesis aims to strike a balance between accuracy and speed of estimation. Also, it includes both qualitative and quantitative measures for power estimation. The quantitative measure attempts to give quantitative results for the average power dissipation of finite state machines. The qualitative aspect of it tries to give enough information to the designer to make informed decisions about choice of finite state machine implementation from a set of broad alternatives.

Pure RTL estimation techniques [Nemani97] [Marce96] [Landman96] are fast, but are inaccurate. Where as, pure gate-level [Najm2'95] [Saxena97] [Roy96] [Devadas94] estimation techniques have very good estimation accuracy, but are slow. The new method attempts to improve the accuracy without trading-off "too much" of estimation time through a "quick" gate-level analysis of the circuit. A "quick" gate-level power analysis of the circuit could be done through probabilistic [Devadas94] [Marce94] or empirical [Shravan98] techniques for propagation of the circuit input activity values to the internal nodes of the circuit and calculating the power dissipated at each node in the circuit. Addition of all these power values yields the overall circuit power. The gate-level analysis takes place on an unoptimized circuit, which is got through a "quick" low-effort synthesis of the RTL description. Low-effort synthesis means a synthesis without any design constraints imposed or a synthesis without any synthesis optimization steps, which is much faster than a synthesis step with optimizations included. This time gain is crucial to make the new technique work at RT-level speeds. Examples of time gain achieved for different benchmark circuits will be presented in the next chapter. A secondary factor affecting the speed of this technique, is the speed of the gate-level power analysis itself. The faster the analysis, the better. The requirement of a synthesis step as part of the power estimation process binds the model developed to the synthesis tool used to develop the model. The implication of this requirement is that the model has to be recomputed if the synthesis tool changes. But, the proposed method is generic in its applicability towards power estimation from any given RTL description. Though the new model has a direct application in power estimation of finite state machines, it could as well be used to predict the power of an unsynthesized RTL-block (also called micro-architectural block) like an adder, multiplexer etc., which are combinational.

| Term                 | Meaning                                                       |  |  |  |  |  |

|----------------------|---------------------------------------------------------------|--|--|--|--|--|

| SOP                  | The number of product terms in the sum-of-product expressions |  |  |  |  |  |

|                      | of the primary outputs of the FSM.                            |  |  |  |  |  |

| LIT                  | The number of literals in the sum-of-product expressions      |  |  |  |  |  |

|                      | of the primary outputs of the FSM.                            |  |  |  |  |  |

| DC                   | The number of product terms in the sum-of-product expressions |  |  |  |  |  |

|                      | of the don't-care set of the output functions of the FSM.     |  |  |  |  |  |

| DCLIT                | The number of literals in the sum-of-product expressions      |  |  |  |  |  |

|                      | of the don't-care set of the output functions of the FSM.     |  |  |  |  |  |

| PI                   | Number of primary inputs to the finite state machine          |  |  |  |  |  |

| PO                   | Number of primary outputs from the finite state machine       |  |  |  |  |  |

| STATES               | Number of states in the finite state machine                  |  |  |  |  |  |

| Popt                 | Power of the optimized implementation of the FSM              |  |  |  |  |  |

| Power <sub>opt</sub> |                                                               |  |  |  |  |  |

| Punopt               | Power of the unoptimized implementation of the FSM            |  |  |  |  |  |

| Powerunopt           |                                                               |  |  |  |  |  |

| SW_CAP               | Switched Capacitance of the FSM                               |  |  |  |  |  |

| $K_x$                | Power-model coefficients                                      |  |  |  |  |  |

### Table 3.1: Notation

Quantitative power estimation with the new method has two main phases, built upon a *power model*:

- Power Characterization Phase

- Power Estimation Phase

These two phases are discussed in the next few sections. Qualitative measures with the new model would require the same phases mentioned above but without actually building the *power model*. Table 3.1 summarizes the notation used throughout this thesis. The next section discusses the motivation for the new power model and section 3.2 explains the new power model in detail. Sections 3.3 and 3.4 discuss the power characterization and power analysis phases with the new power model. Discussion in the rest of the chapter centers around finding a quantitative measure for the average power. As required, changes that are needed in the different phases to reflect qualitative predictions about power will be made.

## 3.1 Motivation For A New Power Model

Finite state machine power estimation at the RT-Level can be approached in two ways. One approach would be to assume nothing about the structure of the circuit synthesized from the RTL description of the finite state machine, except to build theoretical models for the distribution of activity within a circuit, as is done in [Nemani96] [Nemani97]. These are *pure-RTL* techniques. This approach has two main disadvantages. The first and foremost being the loss of the ability to model correlations (both temporal and spatial) among the internal signals of the circuit. This is because the circuit structure dictates what correlations exist among the different signals inside the circuit. The resulting inaccuracies could result in errors as high as 100% [Nemani97]. The second disadvantage with all proposed techniques which follow this approach is that, they decouple the latch and the combinational logic of the FSM and work with either the average value of the input signal activity or the average value of the input entropy. This results in the loss of information about the spatial and temporal correlations that exist among the inputs (primary inputs and state bits) to the combinational logic block of the state machine, leading to additional inaccuracies in estimation.

The second approach to RTL power estimation of sequential circuits needs some information about the circuit structure of the synthesized RTL description. Because it needs structural information about the circuit, techniques which follow this approach are not pure-RTL techniques, but rather a combination of RTL and gatelevel techniques. Previously done research which follows this approach [Marce96], is analytical in nature and is based on the notion of estimating the average switching activity of the circuit from the input and output entropies (informational energy) of the circuit and an implementation dependent information scaling factor. It does

not account for the correlations that exist among the input signals to the finite state machine and also among the signals internal to the circuit. Unfortunately, results are reported in [Marce96] for only RTL combinational-blocks and none for FSMs. The method investigated in this thesis follows the second approach of using some structural information about the finite state machine. The proposed method is motivated by the need for fast power estimation of random logic and finite state machines, at acceptable levels of error. Existing methods are either not sufficiently accurate [Nemani97] or not fully proven [Landman96] [Marce95] to be of commercial value. Looking back at [Nemani97] [Landman96] [Marce95], it is clear that the primary source of error in RT-Level power estimation is the lack of gate-level circuit implementation of the RTL description. So, if it is possible to get a gate-level implementation of the RTL description "quickly", we could extract accurate values of power, through either gate-level simulation or gate-level probabilistic or empirical techniques, at close to RT-level speeds. This method would be accurate because it is based on gate-level power analysis and it would be fast because it needs only a synthesis step with no optimization. But, in practise we are more interested in the power of the optimized implementation of the circuit and it is also a known fact that synthesis with optimization produces very different results for the circuit structure, and hence power, compared to synthesis without optimization. So, a necessary step in the new power estimation method, would then be to characterize the change in power between the optimized and unoptimized implementations of a given circuit.

## 3.2 Power Model

As discussed in the previous section, the new method estimates the power of an unoptimized implementation of the FSM, through a gate-level power analysis and then from a knowledge of how the optimizer changes the power of a circuit during optimization, applies a scaling factor to that power, to yield a final power value. The effect of the optimizer on power is what is captured in the power model.

The parameters available from an RTL description, which are indicative of the complexity of the boolean circuit are listed in Table 3.1. There are parameters other than the ones listed in the table, which could also be obtained from an RTL description. An example would be the average literal count in the prime-implicants of a boolean function. But, these need more processing of the RTL description and are not listed and used in the new model. [Nemani97] uses the average value of literal count in the prime implicants of a function to estimate the gate count and hence the power of the optimized implementation of the function. The idea behind the new power model is to capture the effect of the optimizer (i.e. the synthesis tool) on the power of the unoptimized circuit, as a function of these top-level variables (parameters), i.e.

$$\frac{Power_{opt}}{Power_{unopt}} = f(PI, PO, LIT, SOP, DC, DCLIT, STATES)$$

(3.1)

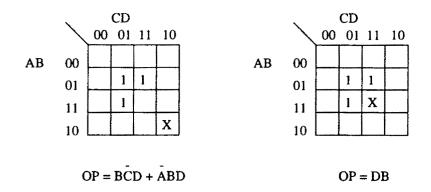

It is known that all of these top-level variables have some influence on how the optimizer optimizes the circuit. But, the degree of dependence of the optimization on each of these top-level variables, individually, and their interaction effects are not clear. No previous work exists, which models these inter-relationships. As an example of these complex relationships, two circuits with the same number of number of ON(1)-minterms and DC(don't care)-minterms can result in entirely different optimizations (an ON-minterm is a product-term corresponding a '1' entry in the Karnough map and a don't-care-minterm is a product-term corresponding an 'X' entry in the Karnough map). For the two functions shown in Figure 3.1, which have the same number of 1 and don't-care-minterms, optimization results in different expressions for the output function and hence the structure of the circuit. It requires the higher sophistication of a synthesis tool to model all these effects accurately. This is a computationally expensive process and is not amenable to

Figure 3.1: Illustration of Different Synthesis Results for Circuits with same number of ON-minterms and DC-minterms

RT-level speeds. Also, it is a question of how each optimizer optimizes the circuit. Every optimizer applies its own set of local optimization techniques. Frequently, optimizers use heuristics in their optimization steps. Every optimizer uses a different heuristic. Modeling all optimizer details would then preclude the new technique from being a generic technique. The question in this thesis is whether the optimizer's behavior is predictable from an analysis of interaction of all the top-level variables. If for example the power-ratio is linear in all top-level variables, then the function in Eqn. 3.1 can take on a form like:

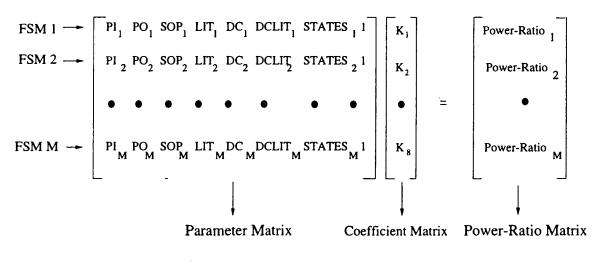

$$\frac{Power_{opt}}{Power_{unopt}} = K_1 P I + K_2 P O + K_3 L ITERALS + K_4 S O P + K_5 ST A T E S + K_6 D C + K_7 D C L I T + K_8$$

(3.2)

Henceforth, we will call the ratio  $Power_{opt}/Power_{unopt}$  as the power-ratio. The coefficients  $K_1$  to  $K_7$  represent the slopes associated with the different terms in the equation. The constant term  $K_8$  represents an average value of the power-ratio, in a least-squares sense. The values of these coefficients are estimated through a characterization process, and are specific to a set of cell-library and synthesis and layout tools used. Although these coefficients are in general evaluated for power-ratio values, they would not change if they are instead evaluated for the switched capacitance ratio values, as long as the time period over which the power values are calculated is the same for both the optimized and the unoptimized circuits. Under