# **Transcoding Unicode Characters with AVX-512** Instructions

# Robert Clausecker<sup>1\*</sup> | Daniel Lemire<sup>2†</sup>

<sup>1</sup>Zuse Institute Berlin, Germany <sup>2</sup>DOT-Lab Research Center, Université du Québec (TELUQ), Montréal, Canada

#### Correspondence

Daniel Lemire, DOT-Lab Research Center, Université du Québec (TELUQ), Montreal, Quebec, H2S 3L5, Canada Email: daniel.lemire@teluq.ca

#### **Funding information**

Natural Sciences and Engineering Research Council of Canada, Grant Number: RGPIN-2017-03910

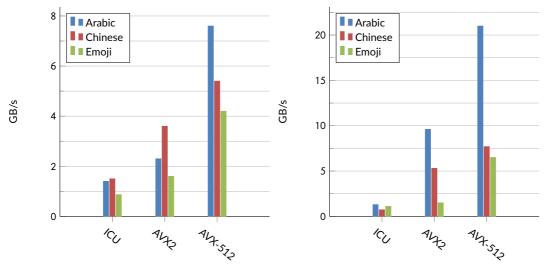

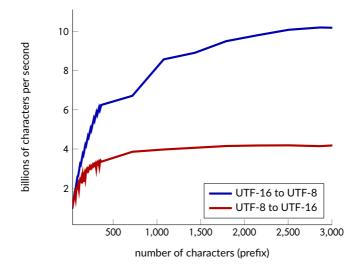

Intel includes in its recent processors a powerful set of instructions capable of processing 512-bit registers with a single instruction (AVX-512). Some of these instructions have no equivalent in earlier instruction sets. We leverage these instructions to efficiently transcode strings between the most common formats: UTF-8 and UTF-16. With our novel algorithms, we are often twice as fast as the previous best solutions. For example, we transcode Chinese text from UTF-8 to UTF-16 at more than 5 GiB  $s^{-1}$  using fewer than 2 CPU instructions per character. To ensure reproducibility, we make our software freely available as an open source library. Our library is part of the popular Node.js JavaScript runtime.

#### **KEYWORDS**

Vectorization, Unicode, Text Processing, Character Encoding

#### INTRODUCTION 1

Computers store strings of text as arrays of bytes. Unicode is a standard for representing text as a sequence of universal characters represented by code points. Code points are stored as short sequences of bytes according to a given unicode transformation format (UTF), the most popular being UTF-8 and UTF-16. Not all sequence of bytes are valid UTF-8 or UTF-16 strings [1]. Validation is required to detect incorrectly encoded or corrupted text before it is processed.

We often need to transcode strings between the two formats. For example, a database might store data in UTF-16 and yet the programmer might need to produce UTF-8 strings for a web site. Thankfully, transcoding is relatively efficient. Conventional transcoders often achieve a throughput between  $0.5 \,\text{GiB}\,\text{s}^{-1}$  to  $1.5 \,\text{GiB}\,\text{s}^{-1}$  on commodity processors [2] (cf. § 8).<sup>1</sup> Yet this falls far below the sequential-read speed of a fast disk (e.g., 5 GiB s<sup>-1</sup>) or the throughput

<sup>&</sup>lt;sup>1</sup>The speed is measured by taking the size of the input and dividing by the time elapsed.

of a fast network connection.

IBM mainframes based on z/Architecture provide special-purposes instructions named "CONVERT UTF-8 TO UTF-16" and "CONVERT UTF-16 TO UTF-8" for translation between the two encodings [3]. By virtue of being implemented in hardware, these exceed 10 GiB s<sup>-1</sup> processing speed for typical inputs. While commodity processors currently lack such dedicated instructions, they can benefit from single-instruction-multiple-data (SIMD) instructions. Unlike conventional instructions which operate on a single machine word (e.g. 64 bits), these SIMD instruction may add eight pairs of 16-bit words at once. We can transcode gigabytes of text per second [2] by a deliberate use of conventional SIMD instructions (e.g., ARM NEON, SSE, AVX2).

In recent years, Intel introduced new SIMD instruction sets operating over registers as wide as 512 bits. If Intel had merely doubled the width of the registers, there would be little need for further work on our part. However, our experience suggests that to fully benefit from AVX-512 instructions, we need to use adapted algorithms [4]. Indeed, while AVX-512 instructions benefit from wider registers, Intel has also added many more instructions than what is typically found in SIMD instruction sets. There is also a slightly different model: AVX-512 instruction may consume or generate masks in *mask* registers which have no equivalent in prior commodity instruction sets. In AVX-512, a mask is conceptually an array of 8, 16, 32, or 64 bits corresponding to vectors of 8, 16, 32, or 64 elements.

We present novel transcoding functions using AVX-512 instructions. On average, we are roughly twice as fast as the previous fastest functions [2] on commodity processors.

#### 2 | UNICODE AND ITS ENCODINGS

Unicode is a standard based on the Universal Character Set (UCS). An extension to ASCII, UCS is a character set whose characters (called *universal characters*) have code points numbered from U+0<sup>2</sup> to U+10FFFF (decimal 1114 111). These code points are organized into 17 *planes* of 65 536 characters each, with the first plane U+0000–U+FFFF being called the *Basic Multilingual Plane* (BMP). Code points in the range 0xd800–0xdfff are reserved for *surrogates* used in the UTF-16 encoding and do not represent universal characters.

Unlike simpler character sets like ASCII, universal characters are seldomly stored directly as integers, as such a storage format is wasteful and incompatible to existing byte-oriented environments. Instead, several *Unicode Transformation Formats* (UTF) are employed to store and process universal characters, depending on the use case at hand.

A Unicode Transformation Format transforms each universal character into a sequence of integers, with the size of the integer being dependent on the format. Popular Unicode Transformation Formats include:

UTF-32 representing each universal character as a 32-bit integer. Mainly used as an internal representation.

- **UTF-16** representing each universal character as one or two 16-bit integers [5]. All code-point values up to U+FFFF are stored as 2-byte integer values directly. Otherwise we use surrogate pairs: two consecutive 2-byte values, each storing 10 bits of the codepoint. Used by Java, Windows NT, databases, binary protocols, and others.

- **UTF-8** representing each universal character as 1–4 bytes [6]. An extension to ASCII, UTF-8 is by far the most popular text encoding on the World Wide Web.

Though our software work covers many cases (from UTF-8 to UTF-16 or UTF-32, from UTF-16 to UTF-8 or UTF-32, and so forth), we study the two most difficult cases: from UTF-8 to UTF-16 and back.

Multi-byte words in computers representing numerical values can be stored in either little-endian format or bigendian format, depending on whether the first byte is the least significant or the most significant. Unicode Transfor-

<sup>&</sup>lt;sup>2</sup>U+ followed by a hexadecimal number is notation for a universal character's code point.

| case   | UTF-16                      | UTF-8                                                |

|--------|-----------------------------|------------------------------------------------------|

| ASCII  | 0000 0000 0GFE DCBA         | <u>O</u> GFE DCBA                                    |

| 2-byte | 0000 OLKJ HGFE DCBA         | <u>110</u> L KJHG <u>10</u> FE DCBA                  |

| 3-byte | RQPN MLKJ HGFE DCBA         | <u>1110</u> RQPN <u>10</u> ML KJHG <u>10</u> FE DCBA |

| 4-byte | <u>1101 10</u> vu tsRQ PNML | 1111 OWVU 10TS ROPN 10ML KJHG 10FE DCBA              |

|        | 1101 11KJ HGFE DCBA         |                                                      |

(a) Bit-by-bit correspondence between UTF-16 and UTF-8 encodings in the four possible cases. The bits are named A to W starting at the least significant bits with 0vuts = WUTS - 1.

| codepoint | UTF-16                         | UTF-8                                                                   |

|-----------|--------------------------------|-------------------------------------------------------------------------|

| U+0       | 0000 0000 0000 0000            | <u>0</u> 000 0000                                                       |

| U+7F      | 0000 0000 0111 1111            | <u>0</u> 111 1111                                                       |

| U+80      | 0000 0000 1000 0000            | <u>110</u> 0 0010 <u>10</u> 00 0000                                     |

| U+7FF     | 0000 0111 1111 1111            | <u>110</u> 1 1111 <u>10</u> 11 1111                                     |

| U+800     | 0000 1000 0000 0000            | <u>1110</u> 0000 <u>10</u> 10 0000 <u>10</u> 00 0000                    |

| U+FFFF    | 1111 1111 1111 1111            | <u>1110</u> 1111 <u>10</u> 11 1111 <u>10</u> 11 1111                    |

| U+10000   | <u>1101 10</u> 00 0000 0000    | <u>1111 0</u> 000 <u>10</u> 01 0000 <u>10</u> 00 0000 <u>10</u> 00 0000 |

|           | $\underline{110111}0000000000$ |                                                                         |

| U+10FFFF  | <u>1101 10</u> 11 1111 1111    | <u>1111 0</u> 100 <u>10</u> 00 1111 <u>10</u> 11 1111 <u>10</u> 11 1111 |

|           | $\underline{110111}1111111111$ |                                                                         |

(b) Examples of matched code-point values in UTF-32, UTF-16LE and UTF-8. For U+10000 and U+10FFFF, UTF-16 requires a surrogate pair.

FIGURE 1 Correspondence between UTF-16 and UTF-8. Format-specific prescribed bits (tag bits) are underlined.

mation Formats representing characters in units larger than bytes are subject to endianess. If the endianess is not known from the context<sup>3</sup>, it can be given by adding a LE or BE suffix to the name of the Unicode Transformation Format, giving e.g. UTF-16BE or UTF-32LE. We can reverse the order of the bytes—between big and little endian—at high speed: e.g., using one instruction per 64 bytes. For simplicity, we present our results on UTF-8 and UTF-16LE.

#### 2.1 | UTF-16

When the Universal Character Set was initially defined, it was meant to be a 16-bit character set with UTF-16 being its natural encoding, representing each universal character in one 16-bit word. It was later realized that 65 536 code points are insufficient to represent the writing systems of the world's many cultures, especially when having to account for over 50 000 Chinese, Japanese, and Korean ideographs. UCS was therefore extended past the Basic Multilingual Plane to code points up to U+10FFFF and UTF-16 retrofitted with a *surrogate* mechanism to permit representation of these newly added characters.

UTF-16 is a versatile Unicode Transformation Format as it permits (absent surrogates) easy processing of text in many popular languages, while not being as memory-hungry as UTF-32. It is widely used in databases and binary file

<sup>&</sup>lt;sup>3</sup>Big endian is the prescribed default byte order [5], although it is less common.

| type              | range     | pattern           |

|-------------------|-----------|-------------------|

| ASCII lead byte   | 0x00-0x7f | <u>o</u> xxx xxxx |

| continuation byte | 0x80-0xbf | <u>10</u> XX XXXX |

| 2-byte lead byte  | 0xc2-0xdf | <u>110</u> X XXXX |

| 3-byte lead byte  | 0xe0-0xef | <u>1110</u> XXXX  |

| 4-byte lead byte  | 0xf0-0xf4 | <u>1111 0</u> XXX |

TABLE 1 Types of UTF-8 bytes with tag bits underlined.

formats and is the preferred internal text representation on Windows NT. Nevertheless, with the advent and growing popularity of universal characters outside of the Basic Multilingual Plane, UTF-16 has been steadily declining in use.

Despite big-endian byte order being prescribed for UTF-16, the little-endian variant UTF-16LE is more commonly encountered under the influence of x86's little-endian orientation. A common convention to deal with this ambiguity is to prefix UTF-16 encoded documents with the *byte order mark* (BOM) U+FEFF.<sup>4</sup> Its byte-swapped counterpart U+FFFE is a reserved "uncharacter" and should not occur in Unicode text. If a UTF-16 encoded document begins with U+FFFE, it can thus be assumed to be in wrong byte order, permitting automatic byte-order detection in many situations. Our algorithms do not make use of this convention and strictly assume UTF-16LE throughout. A BOM is neither generated, nor checked for, nor stripped.

As illustrated in the "UTF-16" column of Fig. 1, code points in the Basic Multilingual Plane are represented as themselves. Code points outside of this plane have 0x10000 subtracted from them (the *surrogate plane shift*), yielding a 20-bit number. This number is split into two 10-bit halves. The high half is tagged with 0xd800, yielding a *high surrogate*. Likewise, the low half is tagged with 0xdc00, yielding a *low surrogate*. The character is then encoded by giving its high surrogate, directly followed by its low surrogate. It is for this purpose that code points in the range 0xd800-0xdfff do not represent universal characters.

Decoding UTF-16 is a matter of joining the bits of surrogate pairs, leaving Basic-Multilingual-Plane characters unchanged. Care must be taken to validate that each high surrogate is succeeded by a low surrogate and vice versa. With this sequencing requirement ensured, all UTF-16 sequences are valid and have a 1:1 mapping to code points.

#### 2.2 | UTF-8

The most popular Unicode Transformation Format is UTF-8, representing each universal character as a sequence of 1–4 bytes. Replacing the earlier UTF-1, the format was designed to be backwards-compatible to ASCII while also being safe for use in UNIX file names, and comes with many other desirable features. Under many circumstances, UTF-8 text can be processed as if it was a conventional ASCII-based 8-bit encoding like those of the ISO-8859 family. This includes common applications like concatenation, substring search, field-splitting (with ASCII characters or UTF-8 strings for separators), and collation, rendering it the most popular UTF.

UTF-8 can be seen as an extension to ASCII, where each ASCII character (U+00-U+7F) is represented as itself with other characters being represented by sequences of bytes in the range 0x80-0xf4 (cf. Table 1). Such sequences start

<sup>&</sup>lt;sup>4</sup>U+FEFF only has this function as the first character of a document. In other positions, it should be treated as an ordinary universal character and must not be stripped or altered.

| expression                      | description                                                |

|---------------------------------|------------------------------------------------------------|

| ¬ <i>a</i>                      | bitwise complement of a                                    |

| ctz(a)                          | number of trailing zeroes in a                             |

| width(a)                        | number of bits needed to represent a                       |

| popcount(a)                     | number of bits set in a                                    |

| pext(a, b)                      | the bits given in a extracted from b                       |

| pdep(a, b)                      | b deposited into the bits given in a                       |

| compress( <i>m</i> , <i>v</i> ) | vector $v$ compressed by mask $m$                          |

| a + b                           | sum of <i>a</i> and <i>b</i>                               |

| a ≪ b                           | a logically shifted to the left by b places                |

| $a \gg b$                       | a logically shifted to the right by b places               |

| a = b                           | mask indicating elements of $a$ equal to those of $b$      |

| $a \wedge b$                    | bitwise and of <i>a</i> and <i>b</i>                       |

| $a \lor b$                      | bitwise or of a and b                                      |

| $a \oplus b$                    | bitwise exclusive-or of a and b                            |

| a ? b : c                       | ternary operator; equal to $a \land b \lor \neg a \land c$ |

TABLE 2 Summary of notation

with a *lead* byte  $(0xc2^5-0xf4)$  indicating the length of the sequence in its *tag* bits, followed by 1-3 *continuation* bytes (0x80-0xbf), making the encoding stateless, and self-synchronizing.

The details are summarized in the "UTF-8" column of Fig. 1: The bits of the code point are numbered A–W starting at the least significant bit. For each of the four possible cases (the ASCII/1-byte case, the 2-byte case, the 3-byte case, and the 4-byte case<sup>6</sup>), the bits of the code point are copied into the lead and continuation bytes as indicated in the figure. Tag bits are applied (underlined in Fig. 1) to distinguish ASCII, lead, and continuation bytes.

For many universal characters, more than one encoding seems to be possible according to the figure. However, only the shortest possible encoding for each character is permitted to ensure uniqueness of the encoding. While 4-byte sequences could encode code points in excess of U+10FFFF, such sequences are not legal either. The bytes 0xc0, 0xc1, and 0xf5-0xff are thus not used by UTF-8.

Decoding UTF-8 begins by looking at the tag bits to tell the start and length of each sequence. Then, the code point is assembled from the payload of these bytes. A critical part in decoding UTF-8 is validation, especially against overly-long sequences and illegal code points (surrogates, code points greater than 10FFFF). In the algorithm presented in § 6 we demonstrate how decoding UTF-8 with comprehensive validation and then reencoding it into UTF-16 can be implemented efficiently, leveraging AVX-512 instructions.

<sup>5</sup>0xc0 and 0xc1 would introduce 2-byte sequences corresponding to ASCII characters, which are encoded as single bytes instead.

<sup>6</sup> the 1–3-byte cases represent Basic-Multilingual-Plane characters, the 4-byte case corresponds to characters represented as surrogate pairs in UTF-16.

#### 3 | RELATED WORK

There are relatively few academic publications on Unicode string processing using SIMD instructions. Cameron [7] proposed a UTF-8 to UTF-16 transcoder using SIMD instruction using *bit streams*. A bit stream is a transposition on the character inputs. For example, from 128 bytes of data, we produce eight 128-bit registers with the first register containing the most significant bits of each input byte, and the last register containing the least significant bits of each input byte. The transcoding from UTF-8 to UTF-16 is done in this bit stream form with a final phase where unused bytes are removed. Inoue et al. [8] presented a limited UTF-8 to UTF-16 transcoder which lacked validation and could not handle 4-byte UTF-8 characters. They rely on a 105 KiB lookup table.

Lemire and Muła [2] presented a generic approach that does full UTF-8 to UTF-16 and UTF-16 to UTF-8 transcoding, with validation. Their UTF-8 to UTF-16 transcoding function is similar in principle to the strategy used by Inoue et al. [8] in that they rely on the presence of instructions to quickly permute bytes within a register in an arbitrary manner, based on a lookup table. The accelerated UTF-8 to UTF-16 transcoding algorithm processes up to 12 input UTF-8 bytes at a time. Given the input bytes, it finds beginning of each character, forming a 12-bit word which is used as a key in a 1024-entry table. Each entry in the table contains the number of UTF-8 bytes to consume and an index into another table where we find *shuffle masks*. The tables use about 11 KiB. The shuffle masks are applied to the 12 input bytes to form a vector register that can be transformed efficiently. This 12-byte routine works within 64-byte blocks. The 64-byte blocks are validated using a fast technique [1]. Their UTF-16 to UTF-8 algorithm uses one of several paths. E.g., if all 16-bit words are in the range U+0000-U+07FF, the 16-bit words, the algorithm uses one of several paths. E.g., if all 16-bit words are in the range U+0000-U+07FF, the 16-bit words are converted to 32-bit words to ultimately produce 1-byte, 2-byte or 3-byte characters. A series of lookup tables allow the efficient permutations, using a total of 8.5 KiB.

Gatilov [9] produced one of the best and most complete software library for Unicode transcoding (utf8lut). It is similar in spirit to the work of Lemire and Muła [2], but utf8lut requires larger tables: 2 MiB for the UTF-8 to UTF-16 transcoder and 16 KiB for the UTF-16 to UTF-8 transcoder.

Unlike this prior work, our proposals do not require lookup tables. This is possible through the use of novel *compression instructions* introduced with AVX-512VBMI2 (see § 4.3, Tbl. 3), allowing us to move bytes to the right places within registers entirely in hardware, without in-memory tables.

#### 4 | NOTATIONAL CONVENTIONS

In the algorithms described below, all logical symbols refer to bitwise logic. Comparisons are performed between corresponding elements of vectors, yielding a bit mask of those elements for which the comparison holds. All arithmetic operations, shifts, and comparisons are performed on unsigned numbers. The width of the number depends on the vector used.

As a general convention, scalars, vectors of bytes, and masks derived from them are indicated with lowercase letters. Vectors of 16- or 32-bit words are indicated with uppercase letters.<sup>7</sup> The symbol *n* is number of bytes in a vector; for AVX-512 it is n = 64. This convention permits us to explain the algorithms in terms of AVX-512 instructions while giving generic formulæ potentially applicable to other future instruction sets.

<sup>&</sup>lt;sup>7</sup>The convention attempts to underline that byte vectors correspond to UTF-8 whereas word vectors correspond to UTF-16.

The operator precedence follows C precedence rules with

$$a + b \ll c = d \wedge e \vee f$$

being parsed as

$((((a+b) \ll c) = d) \land e) \lor f.$

Table 2 gives a list of symbols used in decreasing order of precedence.

#### 4.1 | Mask Operations

Masks are conceptually arrays of bits—containing between 8 and 64 bits—meant to be used in conjunction with vectors having the same number of elements. For example, *byte masks* (noted  $m_1, m_{234}, ...$ ) may contain 64 bits if they correspond to vectors of 64 bytes. We also have *word masks* (e.g.,  $M_3$ ) containing 16 bits when they corresponding to 512-bit vectors of 32-bit values. See Appendices A and B for detailed lists of our masks and other variables. We operate on masks as if they were unsigned integer values:  $m_{+3} = m_4 \ll 3$  means that the whole mask  $m_4$  is shifted to the left by three places to give  $m_{+3}$ ; the 64 individual mask bits are always either 0 or 1. The logical operations *or* ( $\lor$ ), *and* ( $\land$ ) and *not* ( $\neg$ ) are applied bitwise. We have that m = 0 sets all bits to zero whereas  $m = \neg 0$  sets all bits to one.

In practice, the processor has several instructions dedicated to AVX-512 mask registers (e.g., kshiftrd, kandq, korb). Mask registers can be converted back and forth to general-purpose registers as needed—with the caveat that the conversion from mask registers to general-purpose registers may have a high latency (e.g., 3 cycles).

#### 4.2 | Vector Operations

When operating on vectors, equations have to be read as "SIMD formulæ" applying element-by-element. For example, we write

to mean "each element of w is set to the sum of the corresponding elements in a and b if the corresponding bit is set in m or to c otherwise." With an explicit index  $i = 0 \dots n - 1$ , the previous expression could be written as

$$w[i] = m \land 1 \ll i ? a[i] + b[i] : c[i]$$

for  $i = 0, 1, ..., n - 1$

We believe that the presentation as "SIMD formulæ" is easier to understand and prefer it where possible. Explicit indices are only used when permutations are involved. For example, we write

$$w[i] = v[p[i]]$$

to mean "w is v permuted by the index vector p."

Conversions from one element size to another are not explicitly written out; watch the letter case of the variables used to see when this happens. All such conversions are zero-extensions or truncations.

**Remark** The conventional binary notation presents the least significant bits last. When working with masks and vectors, these least significant bits correspond to the first elements of the vectors. This discrepancy in the order is a source of confusion, but it is difficult to avoid. Intel intrinsic functions reflect this confusion by providing two sets of functions to create new vectors: \_mm512\_set\_\* and \_mm512\_rset\_\* depending on the prefered order [10].

#### 4.3 | Special Functions

We use several special bit-manipulation functions corresponding to instructions available on contemporary x86 computers:

ctz The count trailing zeroes operation ctz(a) counts the number of trailing (least significant) zero bits in a, i.e. how often a can be divided by 2 until leaving an odd number. It corresponds to the bsf/tzcnt instructions of the x86 instruction set. Our algorithms never invoke ctz(0).

width The bit width operation width(a) counts the number of bits needed to represent a. It is

width(

$$a$$

) = ( $a \neq 0$ ) ? [log<sub>2</sub>  $a$ ] + 1 : 0. (1)

This operation is efficiently implemented on many architectures through the *count leading zeroes* operation (x86 instruction bsr/lzcnt). Our algorithms never invoke width(0).

- **popcount** The *population count* operation popcount(*a*) computes the number of bits set in *a*. This can also be understood as the sum of the bits of *a*. It corresponds to the popcnt instruction of the x86 instruction set.

- pext The parallel extract operation pext(a, b) takes a bit mask a indicating a possibly non-consecutive bit field and extracts those bits from b, packing them into popcount(a) bits. This corresponds to the pext instruction on recent x86 processors. The operation is perhaps best understood with a diagram:

| а          | 1010111011000100         |     |

|------------|--------------------------|-----|

| Ь          | 1000101011110001         | (2) |

| bit field  | 1-0-101-110              | (2) |

| pext(a, b) | 00000000 <u>10101110</u> |     |

pdep The parallel deposit operation pdep(a, b) takes a bit mask a indicating a possibly non-consecutive bit field and deposits the bits from b into this field. It performs the opposite operation to pext and corresponds to the pdep instruction on recent x86 processors. We can likewise visualize its operation through a diagram:

| а         | 1010111011000100         |     |

|-----------|--------------------------|-----|

| Ь         | 10110100 <u>10101110</u> | (3) |

| bit field | 1-0-101-110              | (3) |

| pdep(a,b) | 1000101011000000         |     |

**compress** The *compress vector* operation compress(m, v) is the only vector operation among our special functions. It performs the same operation as the parallel extract operation pext, but instead of extracting bits from a bit field, it extracts elements from a vector. This corresponds to the vpcompressb instruction on recent x86 processors. For the visualization, we have given the mask m = 0xcd with the least significant bit on the left to make the operation easier to see. The least significant mask bit decides whether to keep the first vector element and so on until the

most significant mask bit decides whether to keep the last vector element:

$$m \quad 1 \quad 0 \quad 1 \quad 1 \quad 0 \quad 0 \quad 1 \quad 1$$

$$v \quad 12 \quad 34 \quad 56 \quad 78 \quad 9a \quad bc \quad de \quad f0$$

(4)

kept elements

$$12 \quad -56 \quad 78 \quad --- \quad de \quad f0$$

compress(m, v)

$$\frac{12 \quad 56 \quad 78 \quad de \quad f0}{12 \quad 56 \quad 78 \quad de \quad f0} \quad 00 \quad 00 \quad 00$$

Observe how we reversed the bit order of the mask *m* to match the natural vector order: its usual binary representation is 11001101.

#### 5 | AVX-512

Our algorithms are based on the AVX-512 family of instruction-set extensions to the Intel 64<sup>8</sup> instruction-set architecture [11]. An extension to the AVX family of instruction-set extensions, AVX-512 provides a comprehensive set of SIMD instructions for operation on vectors of 16, 32, or 64 bytes organized into bytes or words of 16, 32, or 64 bits. A register file of 32 vector registers zmm0-zmm31 complemented by 8 mask registers k0-k7 is provided.

AVX-512 instructions are generally non-destructive, writing their output into a separate operand from their inputs. In most AVX-512 instructions, one operand is permitted to be a memory operand with the remaining operands being register or immediate operands. This is usually the first input operand, but for some instructions it may also be the output operand.

The AVX-512 instruction set is split into a set of extensions. Each extension adds new instructions to the Intel 64 architecture, enhancing the capabilities of AVX-512. Depending on the microarchitecture used, not all AVX-512 extensions might be available. Table 3 gives a list of AVX-512 instructions used and the extension they hail from. In the following, we list those AVX-512 extensions needed to execute the algorithms described in this paper:

AVX-512F The *foundation* extension implements the basic AVX-512 instruction set on 64-byte vectors. Every AVX-512 implementation must support AVX-512F.

AVX-512BW The byte/word extension extends the AVX-512F instructions to vectors of bytes and 16-bit words.

AVX-512DQ The dword/qword extension provides additional instructions on 32- and 64-bit words.

- **AVX-512VBMI** The vector byte manipulation instructions extension adds instructions to permute and manipulate bytes.

- AVX-512VBMI2 The vector byte manipulation instructions 2 extension adds compress/expand support and doublewidth shifts for bytes and 16-bit words.

The first generation of Intel 64 processors supporting all required AVX-512 extensions are those code named *lcelake*, based on the microarchitecture code named *Sunny Cove*. By emulating vpcompressb through other instructions, it is likely possible to adapt the algorithms to processors as early as the generation code named *Cannon Lake*, albeit at significant reduction in performance.

<sup>8</sup>The 64 bit variant of the x86 (IA-32) instruction-set architecture, also known as AMD64, x86-64, EM64T, and IA-32e.

| instruction    | extension | description                                     |

|----------------|-----------|-------------------------------------------------|

| vmovdqu8/16    | BW        | move byte/word/dword vector                     |

| vpblendmw/d    | BW/F      | blend words/dwords with mask                    |

| vpbroadcastd/q | F         | broadcast dword/qword to vector                 |

| vextracti32x8  | DQ        | extract 256-byte word from vector               |

| vpmovzxbw/wd   | BW/F      | zero-extend byte to word or word to dword       |

| vpaddb/w/d     | BW        | add bytes/words/dwords                          |

| vpsubb/w/d     | BW        | subtract bytes/words/dwords                     |

| vpcmpub/w      | BW        | compare unsigned bytes/words                    |

| vpternlogd     | F         | logic on 3 operands by given truth table        |

| vpandd         | F         | bitwise and dwords                              |

| vpandnd        | F         | bitwise and-not dwords                          |

| vpsllw/d       | BW/F      | logically shift words/dwords left by immediate  |

| vpsrlw/d       | BW/F      | logically shift words/dwords right by immediate |

| valignd        | F         | right-shift elements between operands           |

| vpmultishiftqb | VBMI      | shift bytes within qword, see § 7.3             |

| vpcompressb    | VBMI2     | compress byte vector, see § 4.3                 |

| vpermb         | VBMI      | permute byte vector by byte index vector        |

| kmovd/q        | BW        | move 32/64-bit mask                             |

| kord/q         | BW        | bitwise or 32/64-bit mask                       |

| kandnd/q       | BW        | bitwise and-not 32/64-bit mask                  |

| knotd/q        | BW        | bitwise complement 32/64-bit mask               |

| kshiftrd/q     | BW        | logically shift 32/64-bit mask right by imm.    |

| ktestd/q       | BW        | test bitwise and/and-not of masks for all-zero  |

| kortestd/q     | BW        | test bitwise or of masks for all-zero/all-one   |

instruction extension description

TABLE 3 Selected AVX-512 instructions.

#### 5.1 | Masking

The output of most vector instructions is subject to *masking*, a novel feature of AVX-512. A mask register  $k1-k7^9$  is applied to the output operand, specifying either *merge masking* or *zero masking*. With merge masking, only those vector elements indicated by bits set in the mask register are modified in the output operand. The other vector elements remain unchanged. With zero masking, vector elements for which the bits in the mask register are clear are zeroed out.

<sup>9</sup>Mask register k0 cannot be used for masking, but remains available for logic on masks.

For example, the merge and zero masking instructions

```

vpaddb zmm0{k1}, zmm2, zmm3 (merge masking), and

vpaddb zmm4{k5}{z}, zmm6, zmm7 (zero masking)

```

perform a packed addition of bytes, giving

```

zmm0 = k1 ? zmm2 + zmm3 : zmm0 and

zmm4 = k5 ? zmm6 + zmm7 : 0.

```

Masking on register operands is free for most instructions, though merge masking introduces an input dependency on the old value of the output operand.

Masking on memory operands enables *memory fault suppression* for most instructions. This means that the CPU does not signal memory faults for masked-out vector elements, permitting masked out elements to extend into unmapped or non-writable pages. This suppression affects both input and output memory operands.

#### 5.2 | Microarchitectural Details

To simplify the implementation of AVX-512 on microarchitectures designed to execute the older SSE and AVX families of instruction-set extensions, most SIMD instructions operate within *lanes* of 16 bytes. That is, in many ways, it is as if the 64-byte vector registers were made of four nearly independent 16-byte subregisters. Instructions that process data across lanes (such as vpermb or vpcompressb) exist, but can typically execute on less execution units and take longer to execute in comparison to instructions that do not. We thus want to avoid cross-lane operations if feasible.

On current Intel microarchitectures including Sunny Cove (Icelake), Cypress Cove (Rocket Lake), and Willow Cove (Tiger Lake), most AVX-512 instructions<sup>10</sup> can execute on *execution ports* 0, 1, and 5. Instructions that do not cross lanes usually execute in a single cycle, instructions that do take 3 or more cycles. Some instructions are restricted in the ports they can execute on: shifts can only execute on ports 0/1, permutations and other cross-lane instructions, as well as comparisons into masks can only execute on port 5. Instructions operating on masks (i. e. those whose mnemonics start with k) are restricted to one of ports 0 or port 5, depending on the instruction [12, 13].

In addition to these restrictions, ports 0 and 1 support a vector length of only 32 bytes while port 5 supports the whole 64 bytes. Instructions operating on a vector length of 64 bytes are executed either on port 5 or on ports 0/1 joined together, occupying both ports for one cycle simultaneously. Thus, there are effectively only two ports available to execute instructions with a 64-byte vector length. While 32-byte vectors are processed at 3 vectors of 32 bytes (i. e. 6 lanes) per cycle, 64-byte vectors are processed at only 2 vectors of 64 bytes (or 8 lanes) per cycle, leading to a theoretical speedup by a factor of 4/3 or 33 % of 64-byte vectors over 32-byte vectors for an otherwise identical algorithm. This stands in contrast to the factor 2 or 100 % speedup one would naïvely expect from doubling the vector length.

It is vital for the performance of AVX-512 code to keep track of which ports instructions execute on, rearranging or editing the code such that both port 0/1 and port 5 can execute instructions at the same time [14]. Through the use of microarchitectural simulation [15] in the design of the algorithms, good port utilization has been ensured.

<sup>10</sup>assuming no memory operands

### 6 | TRANSCODING FROM UTF-8 TO UTF-16

We transcode UTF-8 to UTF-16 by gathering the bytes that make up each character from the last byte of each character to its first byte. This exploits the similarity in bit arrangement between the four cases (ASCII, 2-byte, 3-byte, and 4-byte) highlighted in Fig. 1a. The bytes of each UTF-8 sequence are isolated from the input string, liberated of their tag bits, shifted into position, and finally summed up into a code point.

Using the exact correspondence between 4-byte UTF-8 characters and characters represented as surrogate pairs in UTF-16, we treat 4-byte characters as an overlapping pair of a 3-byte sequences and a 2-byte sequence that is later fixed up into a high and a low surrogate. This saves us extra code for extracting the fourth-last byte of each sequence and avoids the costly use of 32-bit words for intermediate results.

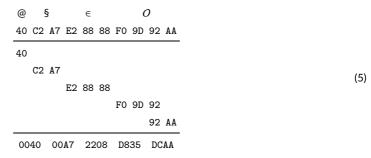

To illustrate this idea, consider the following example, translating the Unicode characters U+40 (@), U+A7 (§), U+2208 ( $\in$ ), and U+1D4AA (O) from UTF-8 to UTF-16:

These four characters demonstrate the behavior of the algorithm on the four UTF-8 cases, representing ASCII, 2byte, 3-byte, and 4-byte respectively. Observe especially how the code sequence F0 9D 92 AA for *O* is split into two overlapping sequences F0 9D 92 and 92 AA. The first of these two is translated into the high surrogate D835 with the second one becoming the low surrogate DCAA.

The algorithm can be roughly described with the following plan of attack:

- 1. Read a vector of 64 bytes.

- Classify each byte according to whether it is an ASCII byte, continuation byte, 2-byte lead byte, 3-byte lead byte, or 4-byte lead byte.

- Construct a mask indicating the last byte of each UTF-8 sequence. For 4-byte characters, the third byte is indicated, too, treating them as a 3-byte sequence for the high surrogate and a 2-byte sequence for the low surrogate.

- 4. Use the mask to gather the last, 2<sup>nd</sup> last, and 3<sup>rd</sup> last byte of each sequence.

- 5. Strip tag bits, shift bits into place and or them into UTF-16 words.

- 6. Postprocess surrogates by shifting their bits into place, and applying tag bits and surrogate plane shift.

- Write the resulting bytes to the output, incrementing the input and output pointers by the number of bytes consumed/generated.

- 8. Repeat until the end of input or an encoding error are encountered.

Apart from this general plan, there are also fast paths for the cases (a) ASCII characters only, (b) ASCII, and 2-byte sequences only, and (c) 1–3-byte sequences only.

Validation is performed throughout the transcoding process, as explained in § 6.4. In comparison to previous algorithms, it is simplified by advancing the input only by complete UTF-8 sequences; if the input is correct UTF-8,

each vector of input thus begins with a complete sequence.

#### 6.1 | Classification and Masks

After reading a vector of bytes from the input buffer, the characters in it are classified according to the range they fall into. Various masks are then built from this classification. In the following explanations, we follow the convention from § 4 where names of the form  $m_{...}$  refer to masks about the input vector  $w_{in}$  while names of the form  $M_{...}$  refer to masks about the output vector.

These two kinds of masks are connected through the pext and pdep operations, relating the end bytes of the decoded UTF-8 sequences to the UTF-16 words they correspond to and vice versa.

The first set of masks is derived directly from  $w_{in}$ , classifying the input into ASCII

$$m_1 = (w_{\rm in} < 0 \pm 80),$$

(6)

2/3/4-byte sequence lead bytes

$$m_{234} = (0 \ge w_{in}),$$

(7)

3/4-byte sequence lead bytes

$$m_{34} = (0 \ge w_{\text{in}}) \tag{8}$$

and 4-byte sequence lead bytes

$$m_4 = (0 \text{xf0} \le w_{\text{in}}). \tag{9}$$

From these we then derive a mask

$$m_{1234} = m_1 \vee m_{234} \tag{10}$$

indicating the presence of any kind of lead byte. All other bytes ( $\neg m_{1234}$ ) are continuation bytes.

Then we construct the important mask  $m_{end}$  identifying the last bytes of each sequence to be decoded. These are the last bytes of each UTF-8 sequence as well as the third byte of each 4-byte sequence. Working backwards from these last bytes, we later use this mask to gather the last, second-last and third-last bytes of each sequence.

The key insight in constructing  $m_{end}$  is that as each UTF-8 sequence is followed by another UTF-8 sequence, we can find the positions of the last bytes as those preceding the lead bytes of the next sequence ( $m_{1234} \gg 1$ ). The third byte of each 4-byte sequence is added by first computing the fourth byte of each sequence

$$m_{+3} = m_4 \ll 3$$

(11)

and then shifting the result to the right to obtain the last third bytes

$$m_{\rm end} = (m_{+3} \lor m_{1234}) \gg 1 \lor m_{+3}.$$

(12)

An unfortunate consequence of defining  $m_{end}$  by going backwards from the lead bytes of the next characters is that we only catch the last character of the vector when it is followed by an incomplete character whose lead byte we can shift to the right. For 4-byte sequences right at the end of the vector, this leads to us only detecting the third last byte in the character. Oring in  $m_{+3}$  at the end fixes this problem for the 4-byte case.

For the other cases, the only effect of this process is that if  $w_{in}$  does not end in a partial character, decodes to no more than 32 words of UTF-16, and the last character is not a 4-byte sequence, we process one less character in the current iteration than possible. However, the minor performance impact of hitting this edge case is more than outweighed by not spending extra time computing the mask correctly.<sup>11</sup>

To visualize the various masks, consider the strings " $x \nabla \mathfrak{P}$ " and " $\varepsilon \leq \pm 1$ " with a vector length of n = 8 bytes:

|                                                             | х  |    | V  |    |    | ş  | ß  |    |    | ε  |    | $\leq$ |    | =  | £  | 1  |      |

|-------------------------------------------------------------|----|----|----|----|----|----|----|----|----|----|----|--------|----|----|----|----|------|

| w <sub>in</sub>                                             | 78 | e2 | 88 | 87 | fO | 9d | 94 | 93 | ce | b5 | e2 | 89     | a4 | c2 | b1 | 31 |      |

| $m_1 = w_{\rm in} < 0 {\rm x80}$                            | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0      | 0  | 0  | 0  | 1  |      |

| $m_{234} = 0 \text{xc} 0 \leq w_{\text{in}}$                | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 1  | 0      | 0  | 1  | 0  | 0  |      |

| $m_{34} = 0 \text{xeO} \le w_{\text{in}}$                   | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 0      | 0  | 0  | 0  | 0  | (13) |

| $m_4 = 0 \text{xf0} \le w_{\text{in}}$                      | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0      | 0  | 0  | 0  | 0  |      |

| $m_{1234} = m_1 \vee m_{234}$                               | 1  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 1  | 0      | 0  | 1  | 0  | 1  |      |

| $m_{+3} = m_4 \ll 3$                                        | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0      | 0  | 0  | 0  | 0  |      |

| $m_{\text{end}} = (m_{+3} \lor m_{1234}) \gg 1 \lor m_{+3}$ | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 0  | 1  | 0  | 0      | 1  | 0  | 1  | 0  |      |

In this example, masks are arrays of eight bits corresponding to eight-byte sequences: in our actual implementation, we use 64-bit masks. Note in particular how  $m_{end}$  accounts for the last character in the left string (being a 4-byte character), but not in the right string, where it is an ASCII character. Also note how the character  $\mathfrak{P}$  has two end bits, being treated as a 3-byte sequence overlapping a 2-byte sequence.

#### 6.2 | Assembling Characters

With these masks in hand, we can strip off the tag bits and assemble characters. The UTF-8 tag bits are stripped off by clearing the most significant two bit of each non-ASCII byte in  $w_{in}$ , giving

$$w_{\text{stripped}} = m_1 ? w_{\text{in}} : w_{\text{in}} \land 0x3f.$$

(14)

The tag bits of 3/4-byte lead bytes are not completely removed by this step; this is sufficient for our purposes as these tag bits get shifted out later on.

Characters are assembled by selecting from  $w_{stripped}$  the last ( $W_{end}$ ), second-last ( $W_{-1}$ ) and third-last bytes ( $W_{-2}$ ) of each sequence, zero-extending them to 16 bits and joining their bits into a UTF-16 word. We do this by first preparing a permutation vector P that holds for each word in the output vector, the index of the last byte of the

$m'_{end} = (m_1 \lor m_2 \ll 1 \lor m_{34} \ll 2 \lor m_4 \ll 3) \land \neg (m_4 \ll 2 \land 1 \ll (n-1)),$

<sup>&</sup>lt;sup>11</sup>If a perfect mask is desired, you can instead use

where  $m_2 = m_{234} \wedge \neg m_{34}$  indicates 2-byte sequence lead bytes. The first byte of each sequence is shifted to the position of its last byte (and the third byte of a 4-byte sequence). The mask is then post-processed by clearing the third byte of a 4-byte sequence starting in the third-last byte of  $w_{in}$ , as only complete sequences can be processed.

corresponding sequence. This vector is prepared by compressing (vpcompressb) a byte vector holding an identity permutation (0, 1, ..., 63) subject to  $m_{end}$ . The compressed vector is then zero-extended (vpmovzxbw) to 16-bit words, keeping its first n/2 elements:

$$P = \text{compress}(m_{\text{end}}, (0, 1, \dots, n-1)).$$

(15)

We only generate one vector of UTF-16 words per iteration representing at most 32 characters. When the input contains ASCII characters, it might be possible for  $m_{end}$  to contain more than 32 set bits. Bits set in  $m_{end}$  past the 32<sup>nd</sup> bit are discarded during the processing: *P* contains only n/2 (or 32) elements. With *P* in hand, we can load the last byte of each sequence

$$W_{\text{end}}[i] = w_{\text{stripped}}[P[i]] \tag{16}$$

with a single permutation instruction (vpermb).<sup>12</sup>

By decrementing the entries of P, we produce index vectors corresponding to the second-last and third-last bytes of each sequence. To avoid loading the third-last byte of a 1/2-byte sequence or the second-last byte of an ASCII sequence, we mask  $w_{\text{stripped}}$  with masks

$$m_{-1} = \neg m_1 \gg 1$$

and (17)

$$m_{-2} = m_{34} \wedge \neg 0 \gg 2 \tag{18}$$

to clear out bytes before ASCII characters resp. those that do not start a 3/4-byte sequence, accounting for possible wrap around.<sup>13</sup> We then obtain our vectors

$$W_{-1}[i] = (m_{-1} ? w_{\text{stripped}} : 0) [P[i] - 1] \text{ and}$$

(19)

$$W_{-2}[i] = (m_{-2} ? w_{\text{stripped}} : 0) [P[i] - 2]$$

(20)

as desired. The last, second-last, and third-last bytes are shifted into place and ored such that the bits A-W are contiguous, giving

$$W_{\rm sum} = W_{-2} \ll 12 \lor W_{-1} \ll 6 \lor W_{\rm end}.$$

(21)

<sup>&</sup>lt;sup>13</sup> P[i] - 1 and P[i] - 2 may yield negative numbers; we assume that in a permutation, such indices either wrap around to the end of the vector or produce 0 as an output. If negative permutation indices yield zeroes, the term  $\neg 0 \gg 2$ , serving as wraparound protection, can be omitted from  $m_{-2}$ .

| The value of W <sub>sum</sub> | depending | on the cas | e taken can | be visualized | as follows: |

|-------------------------------|-----------|------------|-------------|---------------|-------------|

|                               |           |            |             |               |             |

| case    | byte seq              | Juence              | W <sub>sum</sub>    |      |

|---------|-----------------------|---------------------|---------------------|------|

| ASCII   |                       | OGFE DCBA           | 0000 0000 0GFE DCBA |      |

| 2 byte  | 1                     | 110L KJHG 10FE DCBA | 0000 OLKJ HGFE DCBA | (22) |

| 3 byte  | 1110 RQPN 1           | 10ML KJHG 10FE DCBA | RQPN MLKJ HGFE DCBA | (==/ |

| hi surr | 1111 OWVU 10TS RQPN 1 | 10ML KJHG           | OWVU TSRQ PNML KJHG |      |

| lo surr | 1                     | 10ML KJHG 10FE DCBA | 0000 MLKJ HGFE DCBA |      |

This representation is close to UTF-16LE format with only the surrogate cases diverging. To address this difference, we first identify the locations of surrogates in  $W_{out}$ . Sequences in  $w_{in}$  corresponding to low surrogates end at the fourth bytes of 4-byte sequences. By extracting the locations of these through  $m_{end}$  into the space of  $W_{out}$ , we obtain the locations of low surrogates

$$M_{\rm lo} = {\rm pext}(m_{\rm end}, m_{+3}) \tag{23}$$

in Wout. High surrogates

$$M_{\rm hi} = M_{\rm lo} \gg 1 \tag{24}$$

always precede low surrogates.

Surrogates are fixed up by shifting high surrogates into position and applying surrogate plane shift and tag bits,<sup>14</sup> giving

$$W_{\text{out}} = \begin{cases} (W_{\text{sum}} \gg 4) + 0 \text{xd7c0} & \text{if } M_{\text{hi}} \\ W_{\text{sum}} \lor 0 \text{xdc00} & \text{if } M_{\text{lo}} \\ W_{\text{sum}} & \text{otherwise.} \end{cases}$$

(25)

The operation of Eq. 25 can be visualized as follows, where Ovuts = WVUTS - 1:

| case           | W <sub>sum</sub>    | W <sub>out</sub>    |      |

|----------------|---------------------|---------------------|------|

| high surrogate | OWVU TSRQ PNML KJHG | 1101 10vu tsRQ PNML | (26) |

| low surrogate  | 0000 MLKJ HGFE DCBA | 1101 11KJ HGFE DCBA | (==) |

| other          | RQPN MLKJ HGFE DCBA | RQPN MLKJ HGFE DCBA |      |

For illustration purposes, we provide C code implementing equation Eq. 25 using Intel intrinsic functions: see Fig. 2.

The vector  $W_{out}$  holds the UTF-16LE encoded characters we want to write out. There is a final issue: the 64 bytes of UTF-8 data in the input may correspond to anywhere from 21 to 64 words of output, of which the first up to 32 words are processed.<sup>15</sup> If a surrogate pair happened to straddle the end of  $W_{out}$ , we would discard the corresponding low surrogate and produce an incorrect result. So once again, special care must be taken to omit the 32<sup>nd</sup> word of

$<sup>^{14}\</sup>text{Adding }0\text{xd7c0}$  = 0xd800 - 0x0020 applies the tag bits and the surrogate plane shift in one step.

<sup>&</sup>lt;sup>15</sup>Input data corresponding to the remaining words (if any) is reprocessed in the next iteration.

```

__m512i mask_d7c0d7c0 = _mm512_set1_epi32(0xd7c0d7c0);

__m512i mask_dc00dc00 = _mm512_set1_epi32(0xdc00dc00);

//...

// Mlo, Mhi and Wsum have been computed, we compute Wout.

__m512i lo_surr_mask = _mm512_maskz_mov_epi16(Mlo, mask_dc00dc00);

__m512i shifted4_Wsum = _mm512_srli_epi16(Wsum, 4);

__m512i tagged_lo_surrgates = _mm512_or_si512(Wsum, lo_surr_mask);

__m512i Wout = _mm512_mask_add_epi16(tagged_lo_surrogates, Mhi,

__m512i Wsum, mask_d7c0d7c0);

```

FIGURE 2 C code using Intel intrinsic functions equivalent to Eq. 25.

output if it is a high surrogate. We do so by computing a mask

$$M_{\rm out} = \neg (M_{\rm hi} \land 1 \ll (n/2 - 1)) \tag{27}$$

of the elements of  $W_{out}$  excluding the last element if it happens to be a high surrogate. We introduce a variable *b* which is set to all ones (b = -0) except at the end of the input (cf. § 6.3). By depositing the mask  $M_{out}$  into the last bytes of each sequence, we obtain a mask

$$m_{\text{processed}} = \text{pdep}(b \land m_{\text{end}}, M_{\text{out}})$$

(28)

holding the locations of the last byte of each sequence that has been processed into a word in Wout.

With this mask, we can compute the number of bytes of input processed

$$n_{\rm in} = {\rm width}(m_{\rm processed})$$

(29)

and the number of words of output produced

$$n_{\rm out} = {\rm popcount}(m_{\rm processed}).$$

(30)

The first  $n_{out}$  bytes of the output vector are then deposited into the output buffer, input and output buffers are advanced by  $n_{in}$  and  $n_{out}$  and we continue with the next iteration.

To visualize the generation of  $m_{\text{processed}}$ , consider the example string " $\pm 1 = O$ " with a vector length of n = 8 bytes:

$\pm 1 = O$   $w_{in} C2 B1 31 3D F0 9D 92 AA$   $m_{end} 0 1 1 1 0 0 1 1$  (31)

As the character D835 DCAA straddles the end of the vector, it cannot be processed in the current iteration:

$$\pm 1 = O$$

$$W_{out} \ 00B1 \ 0031 \ 003D \ D835 \ (DCAA)$$

$$M_{hi} \ 0 \ 0 \ 0 \ 1$$

$$1 \ll (n/2 - 1) \ 0 \ 0 \ 0 \ 1$$

$$M_{out} \ 1 \ 1 \ 1 \ 0$$

$$(32)$$

Depositing the bits of  $M_{out}$  through  $m_{end}$ , we then obtain

$$m_{\text{processed}} = 0 \ 1 \ 1 \ 1 \ 0 \ 0 \ 0 \ 0$$

bytes processed C2 B1 31 3D -- -- (33)

words produced 00B1 0031 003D ----

and advance buffers by  $n_{in} = 4$  bytes and  $n_{out} = 3$  words respectively. The bytes corresponding to O will be processed again in the next iteration.

#### 6.3 | Processing the Tail

The final bit of input with less than 64 characters remaining (tail) is handled through the variable *b*. This variable holds a mask of those bytes in  $w_{in}$  we are permitted to process. Initially we set  $b = \neg 0$ , permitting all bytes to be processed. When the end of the input with  $\ell < n$  bytes remaining to be processed is reached, we set *b* to a mask of the first  $\ell$  bytes of  $w_{in}$ , giving

$$b = (1 \ll \ell) - 1. \tag{34}$$

The tail of input is read zero-masked by *b*, padding it with NUL bytes. Then, a final iteration of the main loop is performed, processing only the bytes accounted for in *b*.

#### 6.4 | Input Validation

Throughout the transcoding process, we check the input for encoding errors and abort transcoding if any such error occurs. Aborting is done by determining the location of the encoding error and setting the remaining input length  $\ell$  to the number of bytes preceding the first error. We then clear all input bytes starting at the first erroneous byte and jump to the tail-handling code from § 6.3, effectively restarting the current iteration as "final" iteration.

Having talked about how to continue after an error has occurred, we shall now direct our attention to the kinds of errors we have to check for. A UTF-8 encoded document must conform to the following rules:

- 1. Bytes 0xf5-0xff must not occur.

- Lead and continuation bytes must match: each byte in 0xc0 to 0xdf must be followed by one continuation byte, each byte from 0xe0 to 0xef by two continuation bytes and each byte from 0xf0 to 0xf4 by three continuation bytes.

- 3. Continuation bytes may not otherwise occur.

- The decoded character must be larger than U+7F for 2-byte sequences, larger than U+7FF for 3-byte sequences, and larger than U+FFFF for 4-byte sequences.

- 5. The character must be no greater than U+10FFFF.

- 6. The character must not be in the range U+D800-U+DFFF.

We check for these rules throughout the algorithm, mostly reusing masks we already have to compute for other steps of the code. Three checks are performed in total:

#### **Overlong 2-byte sequences**

Right at the beginning, we check whether any of the bytes 0xc0 or 0xc1 occur. Presence of these bytes indicates a 2-byte sequence that encodes a code point below U+80, violating condition 4. The first invalid input byte is the first 0xc0 or 0xc1 byte found:

valid if

$$(m_{234} \land (w_{in} < 0xc2)) = 0.$$

(35)

#### Mismatched continuation bytes

After computing the various classification masks, we check if conditions 2 and 3 hold. As each byte of UTF-8 is either a lead or continuation byte, we check this by computing where continuation bytes should be  $(m_c)$  and comparing this with where lead bytes are not:

valid if

$$m_c = \neg m_{1234}$$

. (36)

We compute  $m_c$  from the location of the second  $(m_{+1})$ , third  $(m_{+2})$ , and fourth byte  $(m_{+3})$ , see Eq. 11) of each sequence:

$$m_{\pm 1} = m_{234} \ll 1, \tag{37}$$

$$m_{+2} = m_{34} \ll 2,$$

(38)

$$m_c = m_{+1} \vee m_{+2} \vee m_{+3}. \tag{39}$$

Conveniently, this check also fails on the input if it starts with continuation bytes, violating the invariant established earlier. We do not catch a UTF-8 sequence straddling the end of the vector; such a sequence is checked properly in the next iteration once additional bytes have been fed in.

If this check fails, we must distinguish two cases to determine the location of the first encoding error: If the first mismatch of  $m_c$  and  $m_{1234}$  is due to a continuation byte present where there should not be one, the first invalid byte is that byte, giving

$$\ell = \operatorname{ctz}(m_c \oplus \neg m_{1234}). \tag{40}$$

Otherwise a continuation byte is missing where there should be one and the corresponding lead byte is the first invalid byte. This byte can be found by masking  $m_{1234}$  to all bits preceding the mismatch

$$m_{\rm pre} = \left(1 \ll \operatorname{ctz}(m_c \oplus \neg m_{1234})\right) - 1$$

(41)

and then finding the last (most significant) bit in it, corresponding to the lead byte that is missing a continuation byte. This gives

$$\ell = \text{width}(m_{1234} \wedge m_{\text{pre}}) - 1. \tag{42}$$

#### **Encodings out of range**

Finally, we check if the codepoints encoded by 3- and 4-byte sequences are in range (conditions 4 and 5) and that 3-byte sequences do not encode surrogates (condition 6). The algorithm treats input bytes in the range 0xf5-0xff as lead bytes of 4-byte sequences. Such sequences encode code points well in excess of U+110000, allowing us to verify

condition 1 as a side effect with no extra code.

We augment our existing mask set with a mask

$$m_3 = m_{34} \wedge \neg m_4 \tag{43}$$

indicating the location of 3-byte sequence start bytes in  $w_{in}$ . Shifting the mask to indicate the last byte of each 3-byte sequence, extracting through  $m_{end}$ , and truncating to n/2 bits, we obtain a mask

$$M_3 = \text{pext}(m_{\text{end}}, m_3 \ll 2) \tag{44}$$

indicating which words in  $W_{out}$  correspond to 3-byte sequences. We then use  $M_3$  to check if any 3-byte sequences encode codepoints below U+800,

$$M_{<\rm U+800} = M_3 \land (W_{\rm out} < 0x800) \tag{45}$$

indicating violations of condition 4.

Then we check for surrogates: words in  $M_3$  must not encode surrogates, words in  $M_{hi}$  must encode high surrogates (condition 6).<sup>16</sup> A word in  $M_{hi}$  produces a high surrogate if and only if the code point it encodes is in range U+10000–U+10FFFF (conditions 1, 4, and 5). The masks

$$M_{3s} = M_3 \land (0xd800 \le W_{out} < 0xe000)$$

=  $M_3 \land (W_{out} - 0xd800 < 0x0800)$  (46)

and

$$M_{4s} = M_{hi} \wedge \neg (0 \text{xd} 800 \le W_{out} < 0 \text{xd} c00)$$

$$= M_{hi} \wedge (W_{out} - 0 \text{xd} 800 \ge 0 \text{x} 0400)$$

(47)

indicate violations of these conditions.<sup>17</sup> The check succeeds if no offending words are found:

valid if

$$M_{ (48)$$

If an offending word is found, the first invalid byte is the start byte of the corresponding sequence. As the error can never occur in a low surrogate, we can find its location by projecting its location back onto the locations of the first and fourth bytes of every sequence:

$$\ell = \operatorname{ctz}(\operatorname{pdep}(m_{+3} \lor m_{1234}, M_{$$

<sup>&</sup>lt;sup>16</sup>by construction, words produced from 1- and 2-byte sequences never produce surrogates and *M*<sub>Io</sub> always produces low surrogates; we do not need to validate these.

$<sup>^{17}\</sup>mbox{As}$  all comparisons are unsigned (vpcmpltuw), one comparison for each range check suffices.

#### 6.5 | Fast Paths

Three fast paths are provided, speeding up common cases. The first two are programmed such that they cannot be triggered in the "final" iterations for the tail or in case of an encoding error, allowing us to omit the handling of *b* in their length computations for a further performance increase.

#### ASCII only

If the first 32 bytes of input are all ASCII bytes, we process these by zero-extension (vpmovzxbw) of the first 32 bytes to 16-bit words. The number of processed bytes is always 32, the number of words written out always 32, shortening the dependency chain to the next iteration. No validation is needed in this case as ASCII bytes are always valid.

Only the first 32 bytes are considered before embarking on the fast path as the default path does not process more than 32 characters in any case. Hence, while checking for all 64 bytes to be ASCII would allow for slightly faster processing in the all-ASCII case, performance for documents with short runs of ASCII characters amidst other characters (e.g. HTML documents) suffers significantly, outweighing the benefits of the other case.

#### 1/2 byte only

In the absence of 3- and 4-byte sequences ( $m_{34} = 0$ ), we employ a simplified variant of the algorithm. While following the same operating principles as the main algorithm, we can take some shortcuts in the proven absence of 3- and 4-byte sequences. First, the computation of some masks is greatly simplified, with most masks being entirely irrelevant for this path:

$$m_2 = m_{234},$$

(50)

$$m_{\rm end} = \neg m_2, \quad \text{and}$$

(51)

$$M_{\rm out} = {\rm pdep}(m_{\rm end}, (1 \ll n/2) - 1).$$

(52)

We then employ a simplified scheme to compute  $W_{out}$ : Instead of masking out tag bits, we subtract 0xc2 from the lead byte of each two-byte sequence to cancel out the tag bits of both lead and continuation byte, giving

1

$$w_{-0xc2} = m_1 ? 0 : w_{in} - 0xc2.$$

(53)

Instead of first building a permutation vector *P* and then using it to permute the input bytes into place, we directly compress the bytes into position (vpcompressb) and then zero extend to 16-bit words (vpmovzxbw), giving

$$W_{\text{end}} = \text{compress}(m_{\text{end}}, w_{\text{in}})$$

and (54)

$$W_{-1} = \text{compress}(m_{1234}, w_{-0xc2}).$$

(55)

Vectors  $W_{end}$  and  $W_{-1}$  must be merged by addition instead of bitwise or to correctly cancel out tag bits, giving

$$W_{\text{out}} = (W_{-1} \ll 6) + W_{\text{end}}.$$

(56)

The operation on 2-byte characters can be visualized as follows; 0xc2 is subtracted separately to illustrate the idea:

$$W_{end} = 0000 \ 0000 \ \underline{10FE \ DCBA} + W_{-1} \ll 6 \quad 00 \\ \underline{110 \ LKJ \ HG} 00 \ 0000 \\ - 0xc2 \ll 6 \quad 00 \\ \underline{11 \ 0000 \ 10} 00 \ 0000 \\ = W_{out} = 0000 \ 0LKJ \ HGFE \ DCBA$$

(57)

We want to increment the input pointer quickly—without a long chain of operations. We find it advantageous to always process half a vector (32 bytes or 33 bytes to include a final continuation byte) of input data per iteration like in the ASCII-only fast path. While this approach usually processes less data than first determining the maximum number of input bytes we can process, being able to load the next data quicker is more important. We avoid accessing the SIMD masks to determine whether we advance by 32 bytes or 33 bytes.

Thus we have

$$n_{\rm in} = \begin{cases} n/2 + 1 & \text{if } 0x80 \le w_{\rm in}[n/2] < 0xc0\\ n/2 & \text{otherwise,} \end{cases}$$

(58)

processing 32 bytes per iteration unless a 2-byte sequence straddles the middle of the vector<sup>18</sup>, in which case we process that extra byte, too.

The output buffer is advanced by the number of characters starting in the first 32 bytes, giving

$$n_{\text{out}} = \text{popcount}(m_{1234} \land (1 \ll n/2) - 1).$$

(59)

As for validation, the checks for "encodings out of range" are omitted. The check for "mismatched continuation bytes" is simplified to

valid if

$$m_2 \ll 1 = \neg m_{1234}$$

(60)

as continuation bytes must always directly follow 2-byte sequence lead bytes. The combination of all these simplifications yields a code path of roughly half the latency of the standard code path.

#### 1/2/3 byte only

In the absence of 4-byte sequences ( $m_4 = 0$ ), all characters are in the Basic Multilingual Plane. In this common case, we can slightly simplify the main routine. We have that  $m_{+3} = m_4 \ll 3$  is zero. Consequently, we can simplify the definitions of  $m_c$  and  $m_{end}$  to

$$m_c = m_{+1} \lor m_{+2}$$

and (61)

$$m_{\rm end} = m_{1234} \gg 1.$$

(62)

The computation of  $W_{out}$  and  $M_{out}$  is eliminated. As no surrogates are present, we can omit the surrogate postprocessing and don't need to account for surrogate pairs straddling the end of the vector. Instead, we directly get

$$W_{\rm out} = W_{\rm sum}$$

and (63)

$$M_{\rm out} = \neg 0. \tag{64}$$

Finally, the validation check for out-of-range encoding is slightly simpler: as surrogates cannot occur, we can drop the  $M_{4s}$  term off Eq. 48.

#### 7 | TRANSCODING FROM UTF-16 TO UTF-8

As explained in § 2.1, UTF-16 encodes characters in the Basic Multilingual Plane (U+0000–U+FFFF) in one 16-bit word and all others in two words as *surrogate pairs*. To encode a code point as a surrogate pair, 0x10000 is subtracted from the character code to obtain a 20-bit binary number. The most significant 10 bits are added to 0xD800 to form a *high surrogate*, which is followed by the less significant 10 bits added to 0xDC00, producing the corresponding *low surrogate*.

UTF-8 encodes Unicode characters in the range U+0000–U+007F in one byte, characters in the range U+0800– U+07FF in two bytes, characters in the range U+0800–U+FFFF in three bytes and the other characters in four bytes. Characters encoded in one UTF-16 word thus correspond to characters encoded in 1–3 bytes of UTF-8 and characters encoded in two UTF-16 words correspond to characters encoded in 4 bytes of UTF-8. This suggests the following *plan of attack* for transcoding UTF-16 to UTF-8:

- 1. Read a vector of 16-bit words.

- Classify the input words into ASCII (0x0000-0x007F), 2-byte (0x0080-0x07FF), high surrogate (0xD800-0xDBFF), low surrogate (0xDC00-0xDFFF), and 3-byte (0x0800-0xFFFF).

- 3. Zero extend each 16-bit word to a 32-bit word and join low and high surrogates.

- Shuffle the bits within each 32-bit word into the right positions and apply tag bits according to the type of character, producing UTF-8 sequences padded with null bytes.

- 5. Compress this vector, squeezing out the padding bytes.

- 6. Write the byte string to the output buffer and proceed to the next iteration.

Apart from this general plan, we also have fast code paths for the three cases of (a) ASCII characters only, (b) all in U+0000–U+07FF, and (c) no surrogates, complementing the default code path (d) surrogates present. Which code path to take is decided based on the characters in the current 62-byte chunk of input. We expect that most text inputs would consistently rely on the same code paths. Thus branches corresponding to the various fast paths are easy to predict, and we expect that they may provide a significant performance boost.

We would now like to explain the steps in the *plan of attack* in detail. The steps are interlinked with information produced in each step being reused for the subsequent steps. Additionally, the classification masks are reused for input validation.

First, 32 words (i. e. 64 bytes) of input are loaded from memory into  $W_{in}$ . Of these words, 31 words are encoded in the iteration with the last word serving as a *look ahead* for surrogate processing (§ 7.2). The mask

$$L = 1 \ll n/2 - 1 \tag{65}$$

indicates the position of the lookahead word in  $W_{in}$ .

#### 7.1 | Classification and Fast Paths

We first need to find out what UTF-8 cases the characters in our input correspond to. Comparing the 16-bit words in the input vector with 0x0080 and 0x0800, we produce the masks

$$M_{234} = (0 \ge 0.080 \le W_{\text{in}}) \land \neg L \quad \text{and} \tag{66}$$

$$M_{12} = (0x0800 > W_{\rm in}) \tag{67}$$

telling us if non-ASCII (i. e. 2-, 3-, or 4-byte) characters and ASCII or 2-byte characters are present. ASCII characters in the lookahead are ignored to simplify some later bits of the algorithm. Based on this information, we can then embark on a code path suitable for this chunk of input.

#### ASCII only

If all input words represent ASCII characters ( $M_{234} = 0$ ), we handle the input in an ASCII-only fast path: the vector is truncated to bytes (vpmovwb) and deposited into the output buffer, advancing it by 31 bytes. Though we could advance by 32 bytes, we want the the algorithm to proceed with a constant stride through memory irrespective of the content.

#### Default path

If some 3- or 4-byte characters are present ( $M_{12} \lor L \neq \neg 0$ ), we check for surrogates. We do this by masking the words with 0xfc00 and then checking if the result is equal to 0xd800 (high surrogate,  $M_{hi}$ ) or 0xdc00 (low surrogate,  $M_{lo}$ ), giving

$$M_{hi} = (0xd800 \le W_{in} < 0xdc00) \land \neg L$$

= (W\_{in} \land 0xfc00 = 0xd800) \land \neg L and (68)

$$M_{lo} = (0xdc00 \le W_{in} < 0xe000)$$

= (W\_{in} \land 0xfc00 = 0xdc00). (69)

If surrogates are found to be present ( $M_{hi} \vee M_{lo} \neq 0$ ), we proceed to § 7.2 to handle them.<sup>19</sup> Otherwise we skip that step, set  $W_{joined} = W_{in}$  zero-extended from 16-bit to 32-bit (vpmovzxwd), and directly go to § 7.3.

#### 1/2 byte only

In the third and final case, we know that the input is a mix of ASCII and 2-byte characters. We process this case by shuffling the bits of two-byte characters into position.<sup>20</sup> The most significant two bits of each byte are cleared and tag bits are applied. Through this whole process, ASCII characters are left unchanged, giving us

$$W_{\text{out}} = M_{234} ? (W_{\text{in}} \ll 8 \lor W_{\text{in}} \gg 6) \land 0x3f3f \lor 0x80c0 : W_{\text{in}}.$$

(70)

<sup>&</sup>lt;sup>19</sup>Low surrogates in the lookahead are registered to permit detection of sequencing errors.

<sup>&</sup>lt;sup>20</sup>As we are on a little-endian architecture, the lead byte is the less-significant of the two.

We illustrate this equation in the 2-byte case:

$$W_{in} = 0000 \text{ OLKJ HGFE DCBA}$$

$$W_{in} \ll 8 \lor W_{in} \gg 6 \qquad \text{HGFE DCBA 000L KJHG} \qquad (71)$$

$$W_{out} = 10\text{FE DCBA 110L KJHG}$$

The words of  $W_{out}$  before the lookahead are then bytewise compared with  $0 \times 0800^{21}$  producing a mask

$$m_{\text{keep}} = W_{\text{out}} \ge_{\text{byte}} (L ? \text{ 0xffff} : \text{0x0800})$$

(72)

holding binary 01 for ASCII characters, 11 for 2-byte characters, and 00 for the lookahead. With this mask, we finally compress  $W_{out}$  into a UTF-8 stream

$$w_{out} = compress(m_{keep}, W_{out})$$

(73)

and write it to the output.

The output buffer pointer is advanced by the number of bytes of output produced, which is one byte for each word of input (sans lookahead) and another byte for each 2-byte character.

$$n_{\text{out}} = \text{popcount}(M_{234}) + n/2 - 1.$$

(74)

#### 7.2 | Surrogates

When surrogates are present in the input, the bits of low surrogate have to be merged into those of the corresponding high surrogate, yielding the code point of the character to be encoded.

First,  $W_{in}$  is zero extended to 32 bits per element.<sup>22</sup> A vector  $W_{lo}$ , holding for each high surrogate in  $W_{in}$  its corresponding low surrogate, is produced by rotating  $W_{in}$  to the right by one element.

Then, the surrogates are joined by subtracting the tag bits (0xd800 for the high surrogate, 0xdc00 for the low surrogate), undoing the surrogate plane shift for the high surrogate, shifting the bits of the high surrogate into place and then adding the two together. By pulling out the constants representing the tag bits and the plane shift, these additions and subtractions can be combined into one using 32-bit unsigned arithmetic. This gives us

$$W_{\text{joined}} = M_{\text{hi}} ? ((W_{\text{in}} - 0 \times d800 + 0 \times 0040) \ll 10) + (W_{\text{lo}} - 0 \times dc00) : W_{\text{in}}$$

=  $M_{\text{hi}} ? ((W_{\text{in}} \ll 10) - 0 \times 35 \times 100) + (W_{\text{lo}} - 0 \times dc00) : W_{\text{in}}$

=  $M_{\text{hi}} ? (W_{\text{in}} \ll 10) + W_{\text{lo}} + 0 \times 100 \times 100 \times 100) : W_{\text{in}}.$  (75)

With the surrogate pairs decoded, we can then proceed to § 7.3 to encode into UTF-8. The vector elements corresponding to low surrogates are ignored for the rest of the algorithm.

$^{22}$ From here on, each vector holds 2n bytes of data. These can be implemented as pairs of *n*-byte vectors.

$<sup>^{21}</sup>$  a constant we have already loaded into a register; any other constant with high-byte in range 0x01-0x7f and low byte 0 works.

(76)

#### 7.3 | Encoding into UTF-8

When we reach this step, we have transformed  $W_{in}$  into a vector  $W_{joined}$  of 32-bit integers, holding the code points of the characters in the input.<sup>23</sup> We would now like to encode these code points into UTF-8, producing 1–4 bytes of output per code point.

Consider Fig. 1a: for the 2-, 3- and 4-byte case, the bits A–W making up the code point always appear in the same position. This suggests using the same encoding procedure for the 2-, 3-, and 4-byte case with merely different tag bits applied at the end. ASCII characters are handled with a shift into position.

The encoding procedure is based on the vpmultishiftqb instruction introduced with the VBMI instruction set extension. Given a vector of 64-bit words and for each such word a vector of eight bytes, the instruction uses the byte vectors as indices to pick eight 8-bit chunks of data (8 consecutive bits) from the corresponding source words. By choosing these indices such that they do not cross a 32-bit boundary, we can effectively use the instruction to select four 8-bit chunks out of each 32-bit word.

Applying the index vector (18, 12, 6, 0) to each 32-bit word<sup>24</sup> of  $W_{joined}$ , we obtain  $W_{shifted}$  with each bit shifted into the right position with some bits left over:

| <i>W</i> joined | 0000 0000 000w vuts RQPN MLKJ HGFE DCBA |

|-----------------|-----------------------------------------|

| index 18        | 00 000w vu                              |

| index 12        | vuts RQPN                               |

| index 6         | PN MLKJ HG                              |

| index 0         | HGFE DCBA                               |

|                 |                                         |

W<sub>shifted</sub> HGFE DCBA PNML KJHG vuts RQPN 0000 Owvu

To fix up the left-over bits, we mask with 0x3f3f3f3f, reusing the mask from the 2-byte fast path. Then, appropriate tag bits  $W_{tag}$  are applied:

| case   | W <sub>shifted</sub> masked with 0x3f3f3f3f | tag bits   |      |

|--------|---------------------------------------------|------------|------|

| 2-byte | 00FE DCBA 000L KJHG 0000 0000 0000 0000     | 0x80c00000 | (77) |

| 3-byte | OOFE DCBA OOML KJHG OOOO RQPN OOOO OOOO     | 0x8080e000 | (,   |

| 4-byte | 00FE DCBA 00ML KJHG 00ts RQPN 0000 0wvu     | 0x808080f0 |      |

Finally, the ASCII case is handled by just shifting the ASCII words into position and merging these shifted characters into the output of the other cases, giving us

$$W_{\rm out} = M_{234}$$

?  $W_{\rm shifted} \wedge 0x3f3f3f3f \vee W_{\rm tag}$ :  $W_{\rm in} \ll 24$ . (78)

We end up with UTF-8 encoded characters in  $W_{out}$ . Each character occupies a 32-bit word and is padded with 0x00 bytes to 4 bytes. Input words corresponding to low surrogates have been passed through, being decoded into junk content. We get rid of the padding and the low surrogate junk by preparing a mask of bytes we want to keep and compressing out the unwanted bytes using the vpcompressb instruction.

In the mask, we want to keep the most significant byte of each 32-bit word and all non-zero bytes-except for

<sup>&</sup>lt;sup>23</sup>In the presence of surrogates, some of these elements are ignored.

<sup>&</sup>lt;sup>24</sup>i. e. the index vector (18, 12, 6, 0, 50, 44, 38, 32) applied to each 64-bit word

processed low surrogates. These seemingly complex requirements can be negotiated in two steps by first building a comparison mask and then taking all bytes that are not lower than the mask. For low surrogate bytes and the lookahead, the mask is 0xff which cannot occur in  $w_{out}$ .<sup>25</sup> For the most significant byte of all other words, it is 0x00 which admits every byte. For other bytes, it is 0x01, admitting only nonzero bytes. Thus we have

$$W_{\text{keep}} = M_{\text{lo}} \lor L ? \text{ 0xffffffff} : \text{ 0x00010101}, \text{ building}$$

(79)

$$m_{\text{keep}} = (W_{\text{out}} \ge_{\text{byte}} W_{\text{keep}}). \tag{80}$$

With this mask, we compress Wout into

$$w_{out} = compress(m_{keep}, W_{out}),$$

(81)

write it to the output buffer and advance the output by

$$n_{\text{out}} = \text{popcount}(m_{\text{keep}})$$

(82)