# Electrical design of Switched-Capacitor second-order high-Q low-pass filter with channel multiplexing

Reeja Iqbal

#### **School of Electrical Engineering**

Thesis submitted for examination for the degree of Master of Science in Technology.

Espoo 10.04.2023

Supervisor

Prof. Kari Halonen

**Advisor**

M.Sc. Tero Sillanpää

# Aalto University, P.O. BOX 11000, 00076 AALTO www.aalto.fi Abstract of the master's thesis

**Author** Reeja Iqbal

**Title** Electrical design of Switched-Capacitor second-order high-Q low-pass filter with channel multiplexing

**Degree programme** Electronics and Nanotechnology

Major Micro- and Nanoelectronic Circuit Design Code of major ELEC0007

Supervisor Prof. Kari Halonen

Advisor M.Sc. Tero Sillanpää

Date 10.04.2023 Number of pages 66 Language English

#### **Abstract**

The aim of this thesis is to design a discrete-time second-order low-pass filter with channel multiplexing for the electronic stability control system. The purpose of this design is to study the current and noise behavior of the multiplexed discrete-time design in comparison to a single-channel continuous-time design. This work discusses the importance of a discrete-time analog filter topology over continuous time in context of integrated area, cost and complexity. It argues about the selection of a ladder-type switched-capacitor filter for the required application and presents the steps for the design from an equivalent RLC filter. It addresses the component design of the selected topology as well as the operational amplifier design. It also discusses the reasons behind the selection of the folded cascode operational amplifier topology for the design. The clocking sequence for the switched-capacitor switches as well as the channel multiplexing switches is explained. The design is verified with simulations and the results of the essential parameters describing the performance of the design are presented. These parameters include the frequency response of the design, current consumption, noise levels, total harmonic distortion of the output signal, and channel isolation between the multiplexed channels. The work is concluded with an explanation of the results and a discussion on the reasons behind out of specification results. Based on this discussion, future work as well as improvements to the existing designs are suggested.

**Keywords** channel-multiplexing, discrete-time low-pass filter, folded-cascode operational amplifier, ladder-filter, Switched-Capacitor

## **Preface**

The work in this thesis has been done for Murata Electronics as part of an ongoing research project. First of all, I am thankful to Allah Almighty for giving me strength and always guiding me towards the right path. I want to express my gratitude towards my advisor, M.Sc. Tero Sillanpää for his continuous support, valuable suggestions and useful corrections in the scientific writing. I am grateful towards my supervisor, Professor Kari Halonen for introducing me to the attributes of the analog design techniques. I will also like to thank D.Sc. Lasse Aaltonen, Jouni Erkillä and other members from the ASIC design team at Murata for providing me with useful assistance whenever it was needed.

I am also grateful to Murata Electronics for not only providing me with the opportunity and a useful topic for my Master's thesis, but also the required tools and setup for the completion of the work.

Finally, I am grateful for the love and support of my husband through out my studies and career decisions. I am also thankful to my parents for always motivating me and arranging the finances at the right time through out my education. I would also like to thank my daughter who bring content, peace and happiness in my life.

Otaniemi, 10.04.2023

Reeja Iqbal

# Contents

| A            | bstra | et e e e e e e e e e e e e e e e e e e       | 2         |

|--------------|-------|----------------------------------------------|-----------|

| P            | refac | е                                            | 3         |

| $\mathbf{C}$ | onter | nts                                          | 4         |

| Sy           | mbo   | ds and abbreviations                         | 6         |

| 1            | Intr  | roduction                                    | 9         |

|              | 1.1   | Background                                   | 9         |

|              | 1.2   | Motivation                                   | 9         |

|              | 1.3   | Purpose                                      | 10        |

|              | 1.4   | Scope                                        | 10        |

|              | 1.5   | Structure                                    | 10        |

| 2            | Low   | y-pass Filters                               | 11        |

|              | 2.1   | Continuous-Time Low Pass Filters             | 11        |

|              |       | 2.1.1 Active-RC Filters                      | 12        |

|              |       | 2.1.2 $G_m$ -C Filters                       | 16        |

|              | 2.2   | Discrete-time Low-pass Filters               | 18        |

|              |       | 2.2.1 Switched Capacitor Bi-quad [25]        | 19        |

|              |       | 2.2.2 Switched Capacitor Ladder Filters [25] | 23        |

|              | 2.3   | Comparison                                   | 23        |

| 3            | Mo    | delling and Design                           | <b>25</b> |

|              | 3.1   | Design Specifications and requirements       | 25        |

|              | 3.2   | Design                                       | 27        |

|              | 3.3   | Clock Signals and Multiplexing               | 30        |

|              | 3.4   | Component design                             | 33        |

|              |       | 3.4.1 Switch design [25]                     | 33        |

|              |       | 3.4.2 Capacitor design                       | 37        |

|              | 3.5   | Operational Amplifier design [28]            | 37        |

|              |       | 3.5.1 Two stage Miller Compensated Op Amp    | 39        |

|              |       | 3.5.2 Folded Cascode Op Amp                  | 41        |

|              |       | 3.5.3 Folded Cascode Op Amp Design           | 43        |

|              |       | 3.5.4 Biasing Circuit                        | 47        |

|              |       | 3.5.5 Common mode feedback                   | 49        |

|              | 3.6   | Final fully differential schematic           | 51        |

| 4            | Sim   | ulation Results                              | 53        |

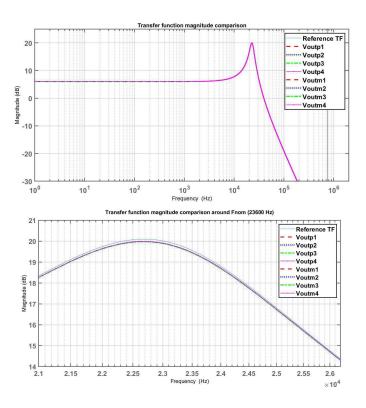

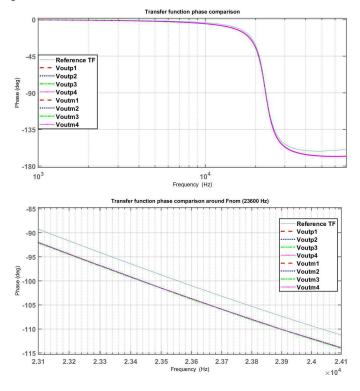

|              | 4.1   | Transfer function                            | 53        |

|              | 4.2   | Total harmonic distortion                    | 57        |

|              | 4.3   | Power Supply Rejection Ratio [30]            | 58        |

|              | 4.4   | Channel Isolation                            | 59        |

|              |       |                                              |           |

|    |       | Noise simulations    |    |

|----|-------|----------------------|----|

| 5  | Sun   | nmary and Conclusion | 63 |

| Re | efere | nces                 | 64 |

## Symbols and abbreviations

## **Symbols**

$\Phi$  Phase

$\omega$  Angular frequency

r small signal resistance

$\sigma$  variance  $\mu$  micro

$\mu_n$  Electron mobility

$\mu_p$  Hole mobility

$\begin{array}{ll} p & \operatorname{Pico} \\ \Omega & \operatorname{Ohm} \\ A & \operatorname{Ampere} \\ A_{DC} & \operatorname{DC Gain} \end{array}$

$A_{GND}$  Analog Ground C Capacitance  $C_L$  Load Capacitor  $C_{ox}$  Oxide capacitance

$\begin{array}{cc} dB & ext{decibels} \\ F & ext{Farad} \end{array}$

$F_S$  Sampling Frequency Fnom Operating Frequency  $G_m$  Trans-Conductance H Transfer Function

Hz Hertz I current

$I_{out}$  Output Current  $I_{ref}$  Reference current

k Kilo Linductor

$L \hspace{1cm} {\it Transistor \ length}$

M Mega

$M_N$  n-channel MOSFET  $M_P$  p-channel MOSFET

m milli n nano

Q Quality factor R Resistance  $R_{on}$  On resistance

second or Laplace variable

TTemperature

VVoltage

Supply Voltage  $V_{DD}$

$V_{DS}$ Drain Source voltage

$V_{GS}$ Gate Source voltage

Input Voltage  $V_{in}$

Output Voltage  $V_{out}$

Ground Voltage  $V_{SS}$

$V_T V^3$ Threshold voltage

Phase 3 Voltage

$V^4$ Phase 4 Voltage

z-domain variable z

#### Abbreviations

AC Alternating Current

ADAS Advance Driver Assist System

ASIC Application Specific Integrated Circuit

BCD Bipolar CMOS DMOS

BW Band-width

CMOS Complementary Metal Oxide Semiconductor

DC Direct Current dps degrees per second

ESC Electronic Stability Control

FF Fast Fast FS Fast Slow

GBW Gain Bandwidth

GF Global Foundaries

KCL Kirchoff's Current Law

KVL Kirchoff's voltage Law

MC Monte-Carlo

MOS Metal Oxide Semiconductor

NMOS N-channel Metal Oxide Semiconductor OTA Operational Transconductance Amplifier PMOS P-channel Metal Oxide Semiconductor

PS Phase Shift

PSRR Power Supply Rejection Ratio PVT Process Voltage Temperature

RC Resistive Capacitive

RLC Resistor Inductor Capacitor SAE Society of Automative Engineers

SF Slow Fast SS Slow Slow

SC Switched Capacitor

THD Total Harmonic Distortion

VDD Supply Voltage VSS Ground Voltage

## 1 Introduction

#### 1.1 Background

Self-driving cars have become a popular topic of research due to their enhanced safety, reduced carbon footprint, better efficiency, and reliability on the automotive industry. According to the Society of Automotive Engineers (SAE), there are six levels of vehicle autonomy ranging from zero for completely manual vehicles to five for fully autonomous driver-less vehicles [1]. As autonomous driving assumes more importance in the automobile industry, there have been significant improvements especially in the field of safety owing to Advance Driver Assist Systems (ADAS). This system is on level two of driver autonomy and requires the driver to remain alert and resume control whenever needed. The ADAS is an important step towards the realization of autonomous driving as was Electronic Stability Control (ESC) towards ADAS [2].

#### 1.2 Motivation

Gyroscope is a device which measures and maintains the stable position of the car. Essential parts of ESC are the gyroscope and accelerometer. Accelerometer along-with gyroscope prevent the straying of the vehicle from its intended path by applying or removing the brakes to and from its wheels [3][4][5]. There are three principal axes for the rotation of an object, known as pitch, roll, and yaw axes. The pitch is the rotation of an object around transverse axis, for a car, it is the rotation from the front wheel towards the back wheel. The roll is the rotation of an object around the longitudinal axis; in other words from the left door of a vehicle towards the right. The yaw is the movement around the vertical axis; this kind of movement is likely to occur when a car is turning rapidly on a curve or slippery surface, especially on ice. The yaw movement of a vehicle is also called car skidding. The yaw rate is the measurement of an angular velocity of a vehicle around its axis of rotation; it is measured in degrees per seconds (dps). The ADAS requires the accurate yaw rate to predict the position of a car from initial speed. When the ADAS has predicted the position of the car accurately, it is able to maintain the stability of a car by keeping it on the track [6].

Physically, the accelerometer and gyroscope are used to determine and maintain the position of a vehicle. There are two types of gyroscopes that are being used in automotive industry. In the first type of gyroscope one or two axes in the loop and it is part of the ESC system, the second type has three axes and is part of the ADAS. For a three-axes stability control of a vehicle, generally three paths are required to measure the rotation around x(roll), y(pitch), and z(yaw) axes [7]. A channel is a term used to describe a path to control the rotation in this work. The exact number of paths or channels to be implemented depends on the sensing element. In this work four channels are implemented because it is easier to derive multiplexing clock for four channels instead of three. The part of application specific integrated circuit (ASIC) which measures and maintains the rotation of the car is gyroscope, there

are two controlling loops in a gyroscope, named as a primary and a secondary loop. Apart from other signals processing sections, a low pass filter is an important part of the secondary loop. Conventionally, one low pass filter is used to process one channel. This approach is simple to design, and the implementation is straightforward. However, this approach is expensive as it occupies the large silicon area on the chip. A potential solution to reduce area is to perform channel multiplexing with a single low pass filter block. Multiplexing is a method that is used to combine multiple signal paths in a single path and process it through a common resource. Multiplexing is difficult to obtain using continuous time circuitry and therefore a discrete time circuitry named as switched capacitor circuitry is implemented in this work. Noise folding is an unavoidable trait of sampling circuits. Therefore, due to sampling, the noise in the circuit increases because of noise folding to the band of interest [8]. Moreover, multiplexing requires a higher bandwidth operational amplifier, which means that the current consumption of the circuit will also increase [9].

#### 1.3 Purpose

The aim of this thesis is to implement the electrical design of switched capacitor low pass filter with channel multiplexing for the ASIC by using the provided specifications and the equivalent continuous-time filter; while targeting reduced silicon area, smaller current consumption, and lower noise levels in the circuit. The application of this work has critical safety requirements, therefore, several other parameters, for example, functionality of the circuit at various operating frequencies, process, voltage, and temperature variation corners, requires verification according to the given specifications. This study also determines the current and noise level in the circuit while proceeding the design with the intent that all other parameters remain within predefined specifications. All the specifications together with current consumption and noise level determine the feasibility of the practical implementation of the circuit.

## 1.4 Scope

The scope of this work is limited to the electrical design of the filter. The layout design is out of scope from this thesis. The current consumption and noise levels are defined as targets for this work, but it is not the requirement.

#### 1.5 Structure

The contents of the thesis are organized as follows. Chapter 2 gives the literature review and background knowledge of the design. Chapter 3 provides the already optimized specification for this design as well as the detailed steps followed for the design and development of the circuit following those specifications. Chapter 4 presents the required simulation results. Chapter 5 summarizes the work, reveals conclusions, and describes future aspects.

## 2 Low-pass Filters

This chapter describes different types of low pass filters and their feasibility for the application in ESC gyroscope loop. Section 2.1 describes the traditional passive low pass filters as well as active RC filters, including topologies of the Sallen-Key and transconductance-capacitor filters. Section 2.2 describes how continuous-time filters are sampled using switches and capacitors, and different topologies for the discrete-time implementation of low-pass filters. Section 2.3 provides an overall comparison of the discussed topologies and selects one to be implemented for the final design.

#### 2.1 Continuous-Time Low Pass Filters

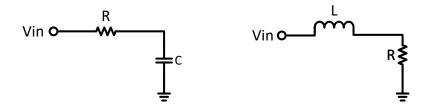

Low-pass filter is a device which attenuates signals higher than a certain frequency, known as the cutoff frequency. In the former times, low pass filters were implemented using resistors, capacitors and inductors. These kind of filters having no active component, e.g., transistor or operational amplifier are termed as passive filters [10] [11]. Due to the absence of these active components, the signal amplitude at the output of a passive filter is always less than the input [12]. The order of a filter is defined by the amount of attenuation it provides per decade after the cutoff frequency, i.e., gain reduction for every ten- fold increase in the signal frequency. The order of the filter is one, if the attenuation after cutoff frequency is 20dB per decade, and the order is two, if the attenuation is 40dB per decade and so on.

An inductor is a reactive component and it shows low reactance to low frequency signals, conversely, a capacitor shows high reactance to high frequency signals. Therefore, the first order passive low pass filters can be implemented as shown in Figure 1.

Figure 1: Passive Low Pass Filters

This passive implementation of low-pass filter especially with an inductor, has several drawbacks. In an integrated circuit, there are two main limitations for the use of an inductor, i.e., they have low quality factor because of parasitic resistance and capacitance and also the size of an inductor becomes very large for low frequency applications. Therefore, inductors are used only in radio frequency integrated circuits

and for low frequency applications they should be used only when absolutely necessary. Capacitors are preferred to be used in an integrated circuit over inductors because of the smaller size, lower cost and higher precision. It is easier to confine the electrical field in a capacitor than to control a magnetic field around an inductor coil [13]. For an integrated circuit, active filters are preferred over passive filters. Active filters are inexpensive and the response of the filter can be easily controlled by the powering part of the filter, i.e., how fast and how steep the signal moves from its pass-band to stop-band or vice versa.

There are two types of active analog filters, i.e., continuous-time and discrete-time filters. To realize a filtering transfer function in a continuous domain we need integrators, adder, and gain blocks. Based on the device used to build integrator, there are two popular types of continuous-time filter structures, i.e.,  $G_m - C$  filters and active-RC filters.  $G_m - C$  filters are realized using transconductors while active-RC implies the use of operational amplifiers [14]. These types of filters are discussed in the following subsections.

#### 2.1.1 Active-RC Filters

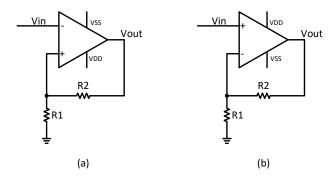

Active-RC filters has an operational amplifier (Op Amp) as its main building block, an Op Amp greatly amplifies the difference of two input signals it is receiving at its input. As a device an Op Amp shows high impedance to the signal coming at its input and low impedance at its output. To understand the working principle of these filters, one needs to understand how integration is performed with an Op Amp. Therefore, let's consider how an Op Amp works with a feedback circuit. Consider the Op Amp in both of its configurations in Figure 2. In Figure 2(a), the Op Amp is

Figure 2: Op amp in positive and negative feedback configuration

connected in positive feedback configuration. If  $R_1$  and  $R_2$  are equal, the voltage at the positive input terminal is half of voltage at the output terminal. If input voltage is higher than the half of output voltage, the output will saturate to the negative supply rail, i.e., VSS of the Op Amp. This happens because the positive terminal tends to adjust to the change at the input by decreasing the voltage at output. As the output signal is limited by the supply voltage, the decreased voltage cannot go below the supply range. Hence output remains saturated to VSS unless  $V_{in}$  is reduced back to

VSS/2. If the voltage at input drops beyond that, the positive feedback tends to increase the output voltage and it will eventually saturate to VDD.

Next, consider the Op Amp in a negative feedback configuration as shown in Figure 2(b), here the output voltage is fed back to the negative input terminal of the Op Amp. For equal  $R_1$  and  $R_2$ , the voltage at the negative terminal is half of the output voltage. If the input voltage at the positive terminal of the feedback is greater than the negative terminal, the negative terminal raises its voltage by increasing voltage at the output terminal till the voltage at both terminals are equal. Op Amp here is connected in the non-inverting configuration and its gain is always greater than 1 [15].

Figure 3: Inverting op amp with Gain = 1 and integrator

In the inverting configuration shown in Figure 3(a), the voltage at the negative terminal tends to be equal to ground voltage, hence, if the input voltage is rising, the output voltage decreases and thus the output voltage is 180 degrees out phase with the input voltage. The amplification of this circuit is given by the ratio of the feedback resistor to the input resistor.

In an integrator, the feedback resistor in the inverting configuration of an Op Amp is replaced by a capacitor. This is shown in Figure 3(b). To understand the integrator operation, consider a square wave being fed at the input terminal. Ideally, no current flows into the input terminal of the Op Amp. Therefore when a positive input voltage is applied to the resistor, the current flows through the capacitor and it starts charging by storing charge on its plates. This flow of current produces a negative voltage ramp at the integrator output. If the voltage at the input is negative, the current flows in the reverse direction and the capacitor gets discharged giving a negative ramp at the negative input terminal of the operational amplifier and a positive voltage ramp at the output node. Therefore, for a square wave input, output of the integrator is a triangular wave. For a triangular wave input, the output is a sine wave. For a sine wave input, the output is a cosine or 90 degrees shifted sine wave. Hence, an integrator is a first order low pass filter. For practical implementations, a resistor is added in parallel to the feedback capacitor, because at DC and low frequencies, the capacitor acts an open circuit and reduces the amount of feedback. Adding a resistor in parallel compensates for the reduced feedback. Let's consider some low pass filters implemented using operational amplifiers.

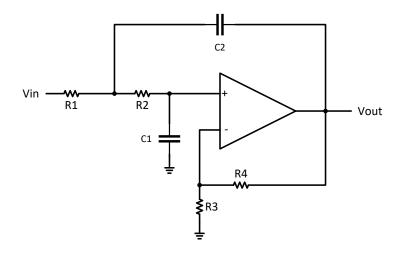

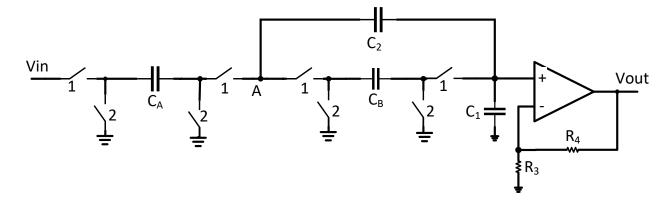

Sallen-Key low pass filter: Sallen-Key filter is a popular implementation for attaining high-Q in continuous-time filters. This topology implies positive feedback amplifier which is controlled around the cut-off frequency, if not limited by the power supply or component tolerances, very high Q values can be achieved using these filters [16]. Figure 4 shows a low-pass implementation of the Sallen-key filter. It is a

Figure 4: Sallen-Key low-pass filter

single amplifier implementation, near DC and lower frequencies, capacitors provide high impedance and the input voltage appears at the output as an amplified signal, depending on the value of gain resistors  $R_3$  and  $R_4$ . At higher frequencies, capacitors impedance decrease as we move closer to the cutoff frequency, the amount of positive feedback increases and negative feedback tends to balance voltage level at the Op Amp input by increasing voltage at the output node. Hence, we get a peaking behaviour of the output voltage around the corner frequency. The higher is this peak, the better is the Q-value of the filter. The transfer function for this low pass filter is given by [16]:

$$H(s) = \frac{K}{s^2(R_1R_2C_1C_2) + s(R_1C_1 + R_2C_1 + R_1C_2(1 - K)) + 1}$$

(1)

Comparing it with a standard second order frequency domain equation, i.e.,

$$H(s) = \frac{K}{\frac{s^2}{(\omega_p)^2} + \frac{1}{\omega_p Q} s + 1}$$

(2)

gives

$$\omega_p = \frac{1}{\sqrt{R_1 R_2 C_1 C_2}} \tag{3}$$

$$Q = \frac{\sqrt{R_1 R_2 C_1 C_2}}{R_1 C_1 + R_2 C_1 + R_1 C_2 (1 - K)} \tag{4}$$

$$K = 1 + \frac{R_3}{R_4} \tag{5}$$

In this topology, the amplifier is not grounded, therefore the common mode voltage changes with the changes in the output voltage and the differential implementation of this filter is challenging.

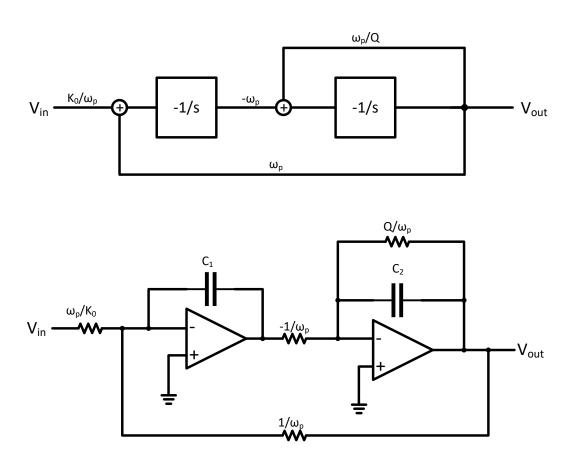

Figure 5: Tow-Thomas Biquad

**Tow-Thomas Biquad:** Tow-thomas biquad is a topology which implements transfer function using resistors, capacitors and Op Amps [17]. The Op Amp functions as a gain block and the co-efficients of the transfer functions are provided through the resistors and capacitors. To understand this topology, consider the transfer function:

$$\frac{V_{out}}{V_{in}} = \frac{s^2 K_2 + sK_1 + K_0}{s^2 J_2 + sJ_1 + J_0} \tag{6}$$

For a low-pass filter  $K_2 = K_1 = 0$ , rearranging the above equation for low-pass filter gives:

$$V_{out} = -\frac{1}{s} \left( \frac{\omega_p}{Q} - \omega_p \left( -\frac{1}{s} \left( \frac{K_0}{\omega_p} V_{in} + \omega_p V_{out} \right) \right) \right)$$

(7)

This equation and its equivalent circuit is represented in a signal flow graph as shown in Figure 5.

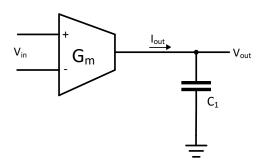

#### 2.1.2 $G_m$ -C Filters

Apart from an active-RC, the above mentioned filter topologies can also be realized using  $G_m$ -C technique. This topology applies transconductors and capacitors to perform filtering [14]. A transconductor is a circuit which takes in voltage and gives output in the form of a current which is linearly related to the input voltage. Ideally, the input and output impedance of a transconductor block is infinite. A transconductor block should have a well defined transconductance( $g_m$ ) value [18]. Consider a single ended Gm-C integrator in Figure 6.

Figure 6:  $G_m$ -C Filter

Here, the output voltage is given by:

$$V_{out} = -\frac{I_{out}}{sC_L} = -\frac{G_m}{sC_L} V_{in} \tag{8}$$

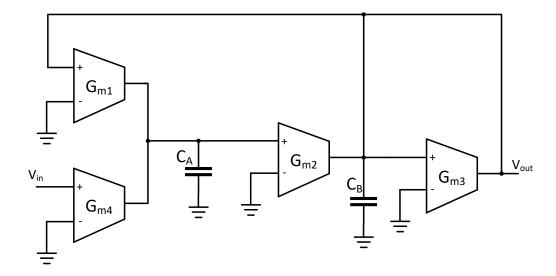

Hence, the output is the integration of input voltage scaled by the transconductance of the transconductor. Unlike operational amplifier, there is no feedback involved in  $G_m$ -C technique for filter implementation. As mentioned above, the Sallen-key low-pass filter involves feedback to obtain high-Q values around corner frequencies. Therefore, this implementation is not feasible to be used with Sallen-key filter. General transfer function equation for a  $G_m$ -C based second order filter is given by:

$$\frac{V_{out}(s)}{V_{in}(s)} = \frac{s^2 \frac{C_X}{C_X + C_B} + s \frac{G_{m5}}{C_X + C_B} + \frac{G_{m2}G_{m4}}{C_A(C_X + C_B)}}{s^2 + s \frac{G_{m3}}{C_X + C_B} + \frac{G_{m1}G_{m2}}{C_A(C_X + C_B)}}$$

(9)

For a low pass filter,  $C_X$  and  $G_{m5}$  becomes zero, and the transfer function becomes:

$$\frac{V_{out}(s)}{V_{in}(s)} = \frac{\frac{G_{m2}G_{m4}}{C_A C_B}}{s^2 + s\frac{G_{m3}}{C_B} + \frac{G_{m1}G_{m2}}{C_A C_B}}$$

(10)

A single-ended implementation of this transfer function is represented in Figure 7.

Figure 7: Second Order transfer function implementation using  $G_m$ -C topology

$G_m$ -C based filters are generally faster but less linear as compared to their operational amplifiers counterparts. Contrarily, the filter implementation using Op Amp requires high gain-bandwidth which makes these filters slower, i.e., slew rate of these filters is high. The feedback capacitor in the active integrator gives better linearity for this circuit, whereas, the  $G_m$ -C based filters are less linear.

In order to fully-integrate these circuits on a chip using MOS technology, a high quality capacitor can be fabricated but a capacitor greater than 5pF is seldom used, in order to obtain a cutoff frequency of 23.6kHz, the resistor required for the RC-integrator would be  $1.3 \mathrm{M}\Omega$ , which would occupy a large portion of an integrated circuit. Also, the behaviour of these resistors is nonlinear in general. Therefore, a resistor not only occupies a large amount of area but it is also not very accurate. Although the capacitors are fabricated using different fabrication steps as compared to resistors, they also have the same order of individual error.

The capacitors and resistors variations are uncorrelated, the time constants achieved by them will also vary over temperature and voltage variations. Therefore, high accuracy and stability performance are difficult to achieve from active RC filters. Furthermore, if several channels needs to be filtered using these, every channel would require its own filter as it is difficult to imagine how a multiplexed signal in time domain can be filtered using single structure. Therefore, to save area and achieve multiplexing, switched capacitor filters need to be considered for the desired application. As described in the previous chapter, using switched capacitor circuit would require higher bandwidth Op Amps, leading to additional current consumption and higher noise floor due to noise aliasing resulting from the sampling nature of the circuit [13][19][20].

#### 2.2 Discrete-time Low-pass Filters

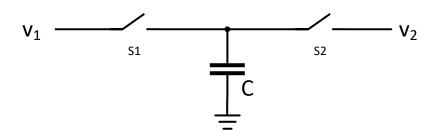

Analog discrete-time filters implies switched-capacitors, these capacitors can be used in place of resistors in a circuit[21][22][23]. These switched capacitors provides path to the signal by sampling it at different intervals and thus approximating the behaviour of an equivalent continuous-time resistor. To understand how a switched-capacitor behaves like a resistor, consider a capacitor and two switches shown in Figure 8. The switches are switched from non-overlapping clocks and thus these two switches

Figure 8: Switched Capacitor Circuit 1

are not closed at the same time. When transistor S1 is turned on, the capacitor is charged to the voltage  $v_1$  in steady state, when S1 is turned off and S2 is also turned off during the non-overlapping time, the charge on the capacitor corresponds to the voltage  $v_1$ . Now, when switch S2 is turned on, the voltage on the capacitor is now  $v_2$ , due to this different voltage the charge on the capacitor changes, if  $v_1$  is greater than  $v_2$ , the current defined as rate of change of charge is given by [24]:

$$I = \frac{C(v_1 - v_2)}{T} \tag{11}$$

where T is the time period during which S1 and S2 are turned on once. The value C/T is a constant in this equation and if we replace it with an equivalent of 1/R, we have implemented an equivalent circuit of a resistor.

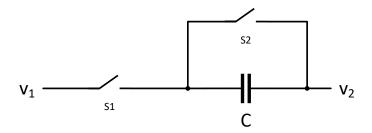

The switched-capacitor equivalent resistor can also be implemented using the circuit shown in Figure 9. Here during phase 1, the capacitor is charged to the voltage  $v_1$  -  $v_2$ , and during phase 2 the capacitor is discharged to 0. Hence, the rate of change of charge during one time period is equivalent to previous case and the circuit is behaving like a resistor of value C/T. Hence, any resistor in an integrated circuit can be replaced with a switched capacitor, resulting in more accurate time constants or equivalent resistance values as the accuracy now depends on the ratios of the capacitor and not on an individual capacitor value. Consider the integrator structure of Figure 3b, if the resistor  $R_1$  is replaced by a switched capacitor of Figure 8, in the resulting circuit, the resulting discrete-time transfer-function is given by:

$$V_{out}(z) = -\frac{\frac{C}{C_1}}{z - 1} V_{in}(z)$$

Figure 9: Switched Capacitor Circuit 2

Whereas, the s-domain transfer function of the active low-pass filter is given by:

$$H(s) = -\frac{\frac{1}{R_1 C_1}}{s}$$

For the low-pass filter implementation using switched capacitors, these topologies can be considered for implementation. First is switched capacitor bi-quad and the second topology is called switched-capacitor ladder filter.

#### 2.2.1 Switched Capacitor Bi-quad [25]

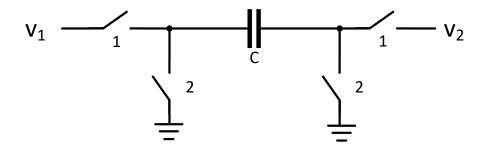

Consider the switched capacitor shown in Figure 8, depending on the clock phase, the top plate of the capacitor is connected to the drain or source terminal of either switch S1 and S2, these terminals of the transistor have some capacitance to the substrate and this capacitance is not fixed and hence it disturbs the accuracy of the capacitance value of capacitor C. This effect is significant when the capacitor is connected to high-impedance nodes and high potential difference increases the stray capacitance values. Therefore, the capacitor is discharged to ground after each sampling phase and the effect of stray capacitance is prevented. This implementation is shown in Figure 10. Here, the numbers 1 and 2 represents the clock phase during which the transistors are switched.

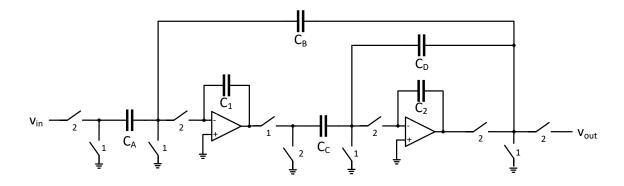

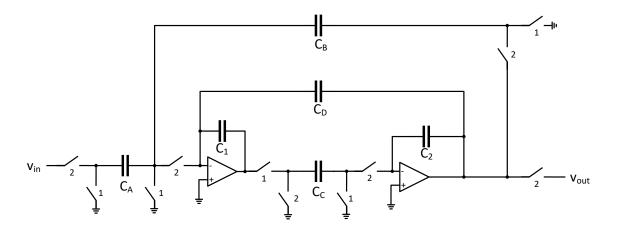

Switched capacitor biquad implementation is the discrete-time implementation of the circuit shown in Figure 5. All the resistances in this circuit can be replaced by switched capacitor equivalent and the switching scheme depends on the sign of the resistor value in transfer function or signal flow graph. The switched capacitor implementation of this circuit is shown in Figure 11. The value of the integrating capacitors  $C_1$  and  $C_2$  remains the same, rest of the capacitance values are given as follows:

$$C_A = \frac{K_0 T}{\omega_o} \tag{12}$$

$$C_B = \omega_p T \tag{13}$$

$$C_C = \omega_p T \tag{14}$$

Figure 10: Switched Capacitor topology preventing capacitor value from stray capacitances

Figure 11: Implementation of a second order transfer function using switched capacitors

$$C_D = \frac{\omega_p T}{Q} \tag{15}$$

There is another possible implementation of a bi-quad filter, referring to equation 7, the relation can also be expressed as:

$$V_{out} = -\frac{1}{s} \left( -\omega_p \right) \left( -\frac{1}{s} \left( \frac{K_0}{\omega_p} V_{in} + \omega_p \left( \frac{s}{Q} + \omega_p \right) V_{out} \right) \right)$$

(16)

The signal flow graph, equivalent RC circuit and the switched capacitor implementation for this equation is shown in Figure 12 - Figure 14. The difference in the two biquads is the connection of  $C_D$ , which is now not a switched capacitor rather it is an integrated capacitor with its value related to Q value of the circuit, given as

$$C_D = \frac{1}{Q} \tag{17}$$

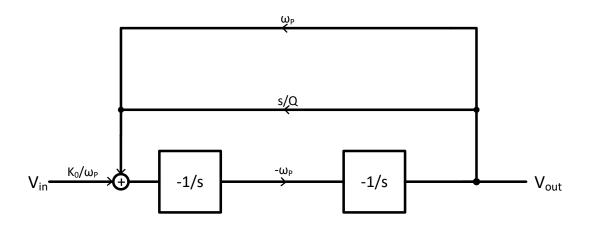

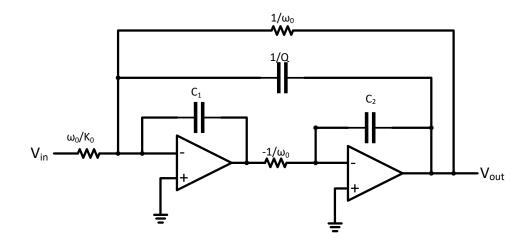

Figure 12: Signal Flow Graph

Figure 13: RC circuit for the SFG in Figure 12

Figure 14: Switched capacitor bi-quad implementation of the SFG in Figure 12 and RC circuit in Figure 13

.

To minimize area, choice of smallest capacitance defines the minimum sampling frequency for the circuit, given by  $C/\omega_p$ . Therefore, the low-Q implementation of the circuit is possible using the circuit shown in Figure 11. For example, comparing equation 14 and 15, Q is defined as the ratio of capacitors  $C_C/C_D$ . In order to get Q=2 from this topology capacitor  $C_C$  and  $C_B$  are needed to be increased by a factor of 2 for the same sampling frequency. Therefore, for high-Q implementation, the circuit in Figure 14 is used in which Q value is not dependent on other capacitance values or sampling frequency. If these two circuits are compared, there are two channel specific capacitors for the low-Q implementation in the first circuit. But for high-Q implementation the number of channel specific capacitors is three. Therefore, channel multiplexing performed using this topology would require more area for high-Q requirements.

Figure 15: Design Flow for SC Ladder Circuit

Figure 16: Switched capacitor Sallen Key Implementation of the circuit shown in Figure 4

#### 2.2.2 Switched Capacitor Ladder Filters [25]

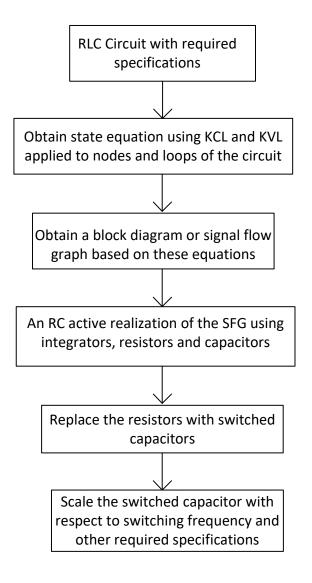

Switched capacitor ladder filters is a widely used technology to design filters. It's concept is based on a two port device, if the input and output impedance of this device is perfectly matched at operating frequency, the device would have maximum gain. Now, if any of the elements within this port changes and the operation was already at a maximum nominal operation, the output of the circuit is going to decrease as it cannot increase from the nominal value. Hence, the sensitivity of this circuit is ideally zero when the gain is maximum. On the other hand for high-Q values switched capacitor biquads have high sensitivity and thus low stability and slight variation in any of the component values can cause the z-domain poles to move outside the unit circle and causes instability.

For sensitive applications and ease of fabrication, ladder filters are preferred over cascaded filters. This technique implies derivation of signal flow graph based on the current-voltage relationship in an equivalent passive filter. The switched capacitor filter is then derived from the signal flow graph. The design flow for switched capacitor ladder circuits is shown in Figure 15. The number of Op Amps required for this implementation depends on the order of the filter. Also, the capacitance nodes with high stray capacitance are always connected to low-impedance source which are the input and output nodes or to the virtual ground which is the input terminal of the Op Amp. Because of this stray-insensitive behaviour, this topology is used in many practical applications containing switched capacitor circuits.

## 2.3 Comparison

All of the topologies considered in this chapter are summarized in Table 1. Here, in this table the  $\checkmark$  represent positive factor of the given topology while the  $\times$  represent negative factor. Although the Sallen-Key low pass filter is implemented for continuous-time application, a switched capacitor implementation can also be acquired by replacing resistors with switched capacitors as shown in Figure 16. This implementation is sensitive to stray capacitance affect as node A is not connected to

| Topology          | Multiplexing | Current     | Area for         | Noise        |

|-------------------|--------------|-------------|------------------|--------------|

| Topology          | Withipicking | Consumption | multiple channel | TTOISC       |

| Active RC         | ×            | √ ·         | ×                | <b>√</b>     |

| Sallen-Key        | ×            | ✓           | ×                | <b>√</b>     |

| Tow-Thomas biquad | ×            | ✓           | ×                | <b>√</b>     |

| $G_m$ -C          | ×            | ✓           | ×                | $\checkmark$ |

| SC biquad         | ✓            | ×           | <b>√</b>         | ×            |

| SC ladder         | ✓            | ×           | ✓                | ×            |

Table 1: Comparison of all topologies for various parameters

ground neither to low impedance node during switching, this affect the accuracy of the capacitance  $C_2$  value and hence the overall accuracy of the circuit. Hence, this topology is not considered further.

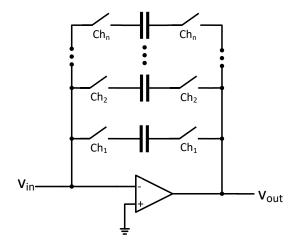

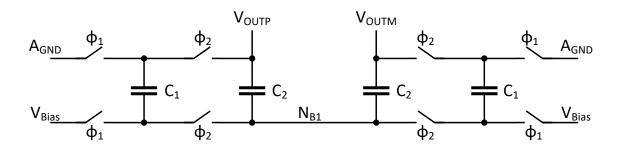

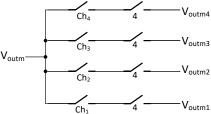

As we need to save area, channel multiplexing is implemented. The channel multiplexing is performed by placing integration capacitors equivalent to the number of channels to be multiplexed and switching them along-with the channel as shown in Figure 17. The non-overlapping phase clocks of the non-integration switched capacitors remains same. In comparison of switched capacitor biquad and ladder topology for low-pass filter, the latter one has fewer number of integrated or channel specific capacitors and is more stable structure for practical implementation. Therefore, the next chapter describes the design of switched capacitor ladder low-pass filter for the gyroscope secondary loop implementation.

Figure 17: Channel Multiplexing

## 3 Modelling and Design

This chapter describes the modelling and design of switched capacitor ladder low-pass filter for the required specifications. Section 3.1 describes the requirement specifications and the target for the design. In Section 3.2, the SC low-pass filter is designed from the RLC equivalent circuit. Section 3.3 presents the multiplexed design with respect to clock cycles and the number of channels. In section 3.4, the switch and capacitor design used for the filter is listed followed by the Op Amp design in section 3.5.

## 3.1 Design Specifications and requirements

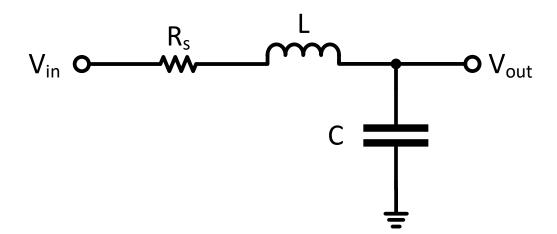

As described in the introduction chapter, the low-pass filter design that is to be designed for this work should be precise enough as it is intended to be used in safety critical automotive related applications. It is a requirement to multiplex and simulate second order switched-capacitor filter through an equivalent RLC while targeting lower current consumption of 1mA. The schematic of RLC prototype that needs to be modelled is shown in Figure 18. The specifications required from this RLC prototype and from its switched-capacitor equivalent as a whole is given in Table 2. The targets that are needed to be studied and achieved as close as possible are stated in Table 3.

As described, the clock sampling frequency per channel is 1.51 MHz. For multiplexing of four channels, each channel should sample once during one sampling period. And as a whole four samples would be taken per sampling period. The sampling period of each channel and their phases would be described later while implementing multiplexing to a single channel design.

Figure 18: RLC prototype

Table 2: Design requirements

| Parameter                      | Requirement                                                                                                     |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Pole frequency $f_p$           | 23.01kHz                                                                                                        |

| Channels to be filtered        | 4                                                                                                               |

| Q-value                        | 5                                                                                                               |

| Channel data rate              | $64 \times \text{Fnom} \pm 10 \% \text{ (Fnom} = 23.6 \text{ kHz)}$                                             |

| Switch on time                 | Half period of $512 \times Fnom-nonoverlappingtime$                                                             |

|                                | $2.5 \pm 0.05 \text{ V}$                                                                                        |

| Ground $V_{SS}$                | 0V                                                                                                              |

| Analog Ground $A_{GND}$        | $1.25 \pm 0.025V$                                                                                               |

| Temperature range:             | $-40^{\circ}C \dots 145^{\circ}C$                                                                               |

| S-domain transfer function     | Second order low pass filter                                                                                    |

|                                | $V_{out}(s) = A_{dc} \frac{\omega_p^2}{s^2 + \frac{\omega_p}{Q} s + \omega_p^2} V_{in}(s), \omega_p = 2\pi f_p$ |

| Differential DC gain $A_{dc}$  | 2(approx.6dB)                                                                                                   |

| Differential DC output offset: |                                                                                                                 |

| room temperature               | $\pm 25mV$                                                                                                      |

| temperature drift              | $\pm 4.5mV$                                                                                                     |

| Output Signal Range            | 0.375V - 2.125V                                                                                                 |

| PSRR DC-100kHz                 | 25 dB min                                                                                                       |

| Harmonic distortion at Fnom    | 0.3% at max output range                                                                                        |

| Channel Isolation              | >100 dB                                                                                                         |

| Transistor technology          | GF 55nm BCD                                                                                                     |

Table 3: Design targets

| Parameter                           | Target                     |

|-------------------------------------|----------------------------|

| Phase shift (PS) at $f_p$ :         |                            |

| Typical:                            | -86.9 degrees              |

| Over process variation:             | $\pm$ 6 degrees            |

| Over supply drift:                  | $\pm 0.6 \text{ degrees}$  |

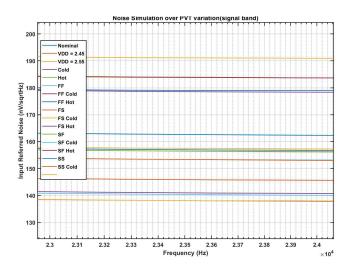

| Input referred noise in signal band | $500 \text{ nV}/\sqrt{Hz}$ |

| Current consumption                 | 1.0mA                      |

#### 3.2 Design

According to the required pole frequency and Q-Value, the s-domain second-order transfer function [26] can be written as:

$$H(s) = \frac{V_{out}}{V_{in}} = 2\frac{2.09 \times 10^{10}}{s^2 + 28915.2187s + 2.09 \times 10^{10}}$$

(18)

Comparing it with standard second-order RLC low-pass filter transfer function for R = 1:

$$H(s) = A_{dc} \frac{\frac{1}{LC}}{s^2 + \frac{R_s}{L}s + \frac{1}{LC}}$$

(19)

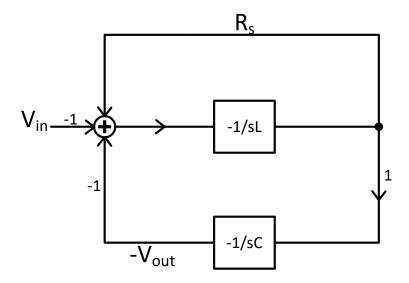

gives L = 34.58  $\mu$ H and C = 1.38  $\mu$ F. Writing the current and voltage equations for the voltage and current through the RLC circuit shown in Figure 18, gives:

$$I_S = -\frac{1}{sL}(V_{out} + I_s R_s - V_{in})$$

(20)

$$-V_{out} = -\frac{1}{sC}(I_s) \tag{21}$$

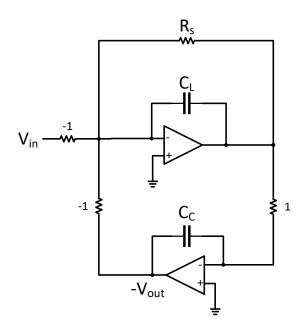

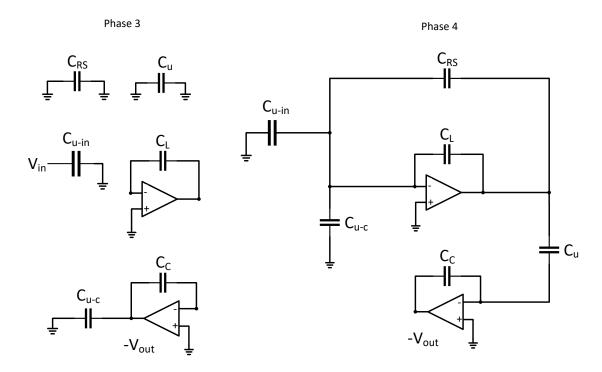

where  $I_s$  is the current through the circuit. The signal flow graphs for these equations is drawn in Figure 19. The single-ended RC implementation for this signal flow graph is shown in Figure 20. All the resistors when replaced by switched-capacitors gives the implementation as shown in Figure 21.

Here, all the resistors with negative values have opposite clock phases in the equivalent switched-capacitors. As the sampling frequency  $(f_s)$  is  $64 \times$  Fnom, the capacitor value with unity gain is  $R/f_s$  which is equal to 0.662  $\mu$ F. Hence, all the unit capacitors  $(C_{RS}, C_{u-in}, C_{u-c} \text{ and } C_u)$  are equal to 0.662  $\mu$ F. The circuits samples the incoming signal at phase3. The output of the second integrator during phase4 of the clock

Figure 19: Signal Flow Graph

.

Figure 20: RC Implementation

Figure 21: Switched-Capacitor Circuit.

cycle is the output of the filter. If  $V_1$  is the voltage node at the output of the first Op Amp and  $V_1^4$  is its output during phase clock 4. The equivalent circuit during phase 3 and phase 4 is shown in Figure 22. The z-domain transfer function for the circuit in Figure 21 can be computed using the following equations [27].

$$V_1^4 = z^{1/2} V_1^3 (22)$$

$$V_{out}^4 = z^{1/2} V_{out}^3 (23)$$

Figure 22: Equivalent Circuits during Phase 3 and Phase 4

$$-C_{u-in}z^{-1/2}V_{in} - C_{u-c}z^{-1/2}V_{out}^3 + (C_L + C_{RS})V_1^4 - C_Lz^{-1/2}V_1^3 = 0$$

(24)

$$C_u V_1^4 + C_c V_{out}^4 - C_c z^{-1/2} V_{out}^3 = 0 (25)$$

Solving these equations for the z-domain transfer function gives,

$$H(z) = \frac{V_{out}^4}{z^{-1/2}V_{in}} = \frac{C_u C_{u-in}}{C_C C_{RS} + C_C C_L - (2C_C C_L + C_C C_{RS} - C_u C_{u-c})z^{-1} + C_C C_L z^{-2}}$$

(26)

Substituting the capacitance values into this transfer function and normalizing denominator constant to 1 gives:

$$H(z) = \frac{0.00899}{1 - 1.972z^{-1} + 0.981z^{-2}}$$

(27)

The gain in this transfer function is 1. To increase the gain by two, the capacitances  $C_C$  and  $C_{u-c}$  needs to be scaled by half. The z-domain transfer function thus becomes,

$$H(z) = \frac{0.01798}{1 - 1.972z^{-1} + 0.981z^{-2}}$$

(28)

In addition to that, for optimized dynamic range, the gain at the output of the first Op Amp and at the output of low-pass filter at the operating frequency should be same. The transfer function till the output of the first operational amplifier is given by:

$$H_1(z) = \frac{C_c C_{u-in} - C_c C_{u-in} z^{-1}}{C_C C_{RS} + C_C C_L - (2C_C C_L + C_C C_{RS} - C_u C_{u-c}) z^{-1} + C_C C_L z^{-2}}$$

(29)

| Capacitor             | Unscaled        | Gain            | Maximized        | Optimized        | Scaled    |

|-----------------------|-----------------|-----------------|------------------|------------------|-----------|

|                       | Value           | Scaling         | Dynamic          | Dynamic          | Value     |

|                       |                 |                 | Range            | Range            |           |

| $\overline{C_{u-in}}$ | $0.66208 \mu F$ | $0.66208 \mu F$ | $0.66208 \mu F$  | $0.66208 \mu F$  | 0.53248pF |

| $\overline{C_{RS}}$   | $0.66208 \mu F$ | $0.66208 \mu F$ | $0.062169 \mu F$ | $0.068386 \mu F$ | 55fF      |

| $C_u$                 | $0.66208 \mu F$ | $0.66208 \mu F$ | $0.062169 \mu F$ | $0.062169 \mu F$ | 50fF      |

| $C_{u-c}$             | $0.66208 \mu F$ | $0.33104 \mu F$ | $0.33104 \mu F$  | $0.33104 \mu F$  | 0.26624pF |

| $\overline{C_L}$      | $34.58 \mu F$   | $34.58\mu F$    | $3.24706 \mu F$  | $3.5717 \mu F$   | 2.8726pF  |

| $C_C$                 | $1.3834 \mu F$  | $0.6917 \mu F$  | $0.6917 \mu F$   | $0.6917 \mu F$   | 0.50572pF |

Table 4: Capacitor Values

When substituting the values it is given by:

$$H_1(z) = \frac{0.01878 - 0.01878z^{-1}}{1 - 1.972z^{-1} + 0.981z^{-2}}$$

(30)

For dynamic range optimization, scale the capacitors connected at the output of the first operational amplifier  $(C_L, C_{RS} \text{ and } C_u)$  by factor of 0.01878 times of half of maximum gain. As the maximum gain of the transfer function is 20 dB, the scaling factor is thus 0.0939. The capacitor values then become 3.24706  $\mu$ F, 0.062169  $\mu F$  and 0.062169  $\mu F$  respectively. These capacitance values gives the dynamic range optimization at 21.6KHz, to make it optimized at operating frequency of 23.6kHz, the capacitance,  $C_{RS}$  needs to be scaled further by a factor of 1.1. This also changes the values of the capacitor  $C_L$  by the same factor according to the transfer function in Equation 19. $C_u$  is the smallest capacitance for the required low pass filter implementation. The benefit of switched-capacitor as compared to RC circuits is that their overall performance depends on the capacitor ratios and not on the individual capacitor values. Therefore, all capacitor values can be scaled by the same factor. The lowest capacitance values available for the fabrication technology is 50fF. The value of the smallest capacitance affects the noise performance of the circuit. The noise performance is inversely proportional to this value, lower the capacitance value higher is the noise. Moreover the ratio of the largest capacitance to the smallest, affects the matching of these components. At this point, all other capacitance including integration capacitors are scaled by  $50 fF/0.062169 \mu F$  to minimize area. The overall scaling factor is thus  $8.04265 \times 10^{-7}$ . The unscaled (initial capacitor values) and scaled capacitor values are given in Table 4. The noise performance of the circuit as well as the capacitor mismatch results would be shown in later sections.

## 3.3 Clock Signals and Multiplexing

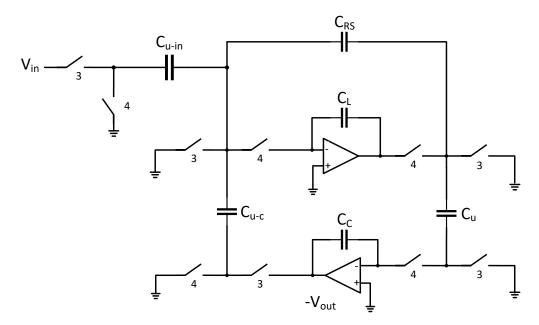

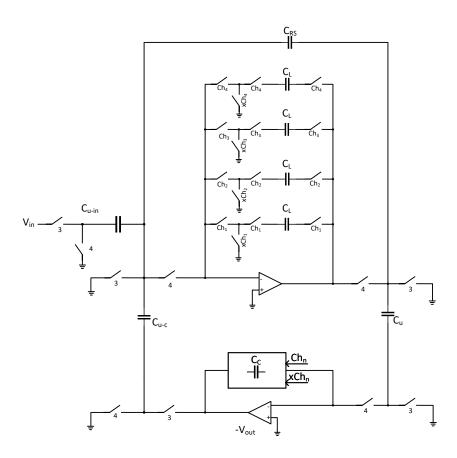

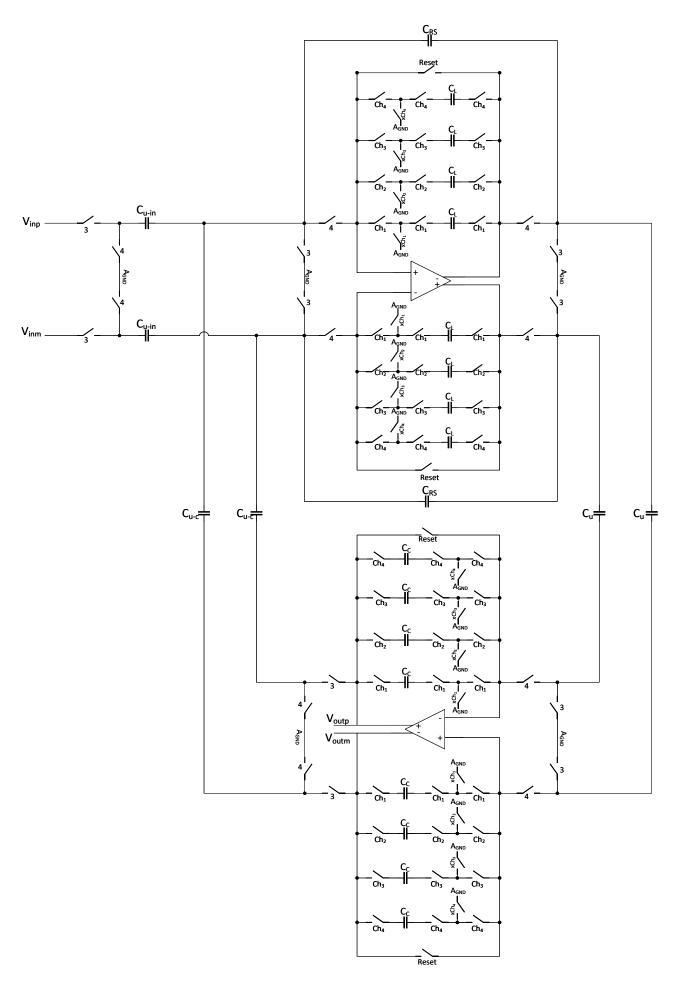

This section describes how the required number of channels are multiplexed for the required sampling frequency. The single stage channel multiplexed schematic is shown

Figure 23: Full single ended schematic depicting channel multiplexing for the first stage of the filter, multiplexing for Capacitor  $C_C$  is also similar to the first stage capacitor  $C_L$ .

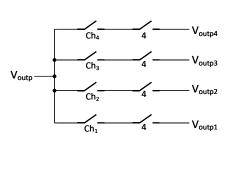

in Figure 23. The channel multiplexing is performed by providing de-multiplexed path for the integration capacitors. The operational amplifier performs integration to the signal separated by the switches Chn and xChn, where n is the number of channels that are required to be multiplexed. "Chn" switches provide the integration path to the specific channel signal. "xChn" switches hold the capacitor charge against ground when the channel is turned off. Therefore, the Chn and xChn switches needs to be non-overlapping. Just like the phase3 and phase 4 clocks of the low pass filter needs to be non-overlapping to prevent charge leaking[28]. The two extra switches Ch and xCh in contrast to the scheme shown in Figrue 17, helps in improving channel isolation or crosstalk when combined with a reset switch connecting input and output of the Op Amp[32]. The full schematic with the reset switch is shown in Figure 40.

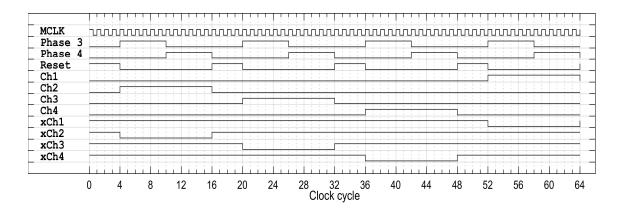

For the carrier frequency of  $23.6 \mathrm{kHz}$  and sampling frequency of  $64 \times \mathrm{Fnom}$ , one phase of single channel switched capacitor filter is switched 64 times during Fnom. Fnom is thus the carrier frequency for the sampling. When multiplexing is applied to this filter, the number of channels are increased. The overall switch-on interval for

Figure 24: Clocking Sequence

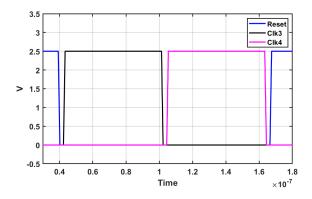

one phase decreases because of the non-overlapping time but the sampling frequency per channel remains same. The maximum oscillation that can be obtained within the ASIC is 100MHz. This information was provided in advance. The highest multiple of carrier frequency that can be obtained on ASIC is  $4096 \times$  Fnom (approx. 96.66 MHz). The switching is distributed according to half period of the master clock cycle. The clocking sequence is shown in Figure 24. Here, one clock cycle is equivalent to the one period of master clock. The 64 clock cycles are equivalent to one sampling interval i.e  $1/(64 \times$  Fnom). The multiplexing is performed within this one sampling interval. It is not easy to see the non-overlapping time in Figure 24 as the figure is showing one complete sampling period but there is 2ns of non-overlapping time between Phase 4 and Reset switches as shown in Figure 25.

A sampling interval starts with a reset phase. In this phase, the output of the operational amplifiers of the circuit is connected to the input. As a result, we have the zero offset at the Op Amp's input nodes. After reset phase, channel two is turned on and after a minor delay, the phase3 clocks samples the input signal. After non-overlapping time between phase 3 and phase 4, the switches for phase 4 are turned on. After phase 4 the channel goes off. The xCh switch is turned on to hold the charge and then reset is performed again before next channel is turned on. The clock signals and their characteristics are described in Table 5. Figure 26 depicts the

Figure 25: Non-overlapping time

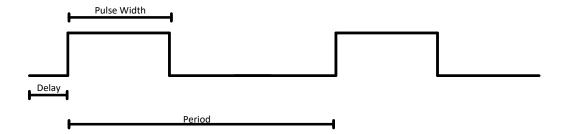

| Clock name | Period                         | Delay                                         | Pulse Width                      |

|------------|--------------------------------|-----------------------------------------------|----------------------------------|

| Reset      | $16/(4096 \times \text{Fnom})$ | 1 ns                                          | $3.6/(4096 \times \text{Fnom})$  |

| 3          | $16/(4096 \times \text{Fnom})$ | $4/(4096 \times \text{Fnom}) + 1 \text{ ns}$  | $5.6/(4096 \times \text{Fnom})$  |

| 4          | $16/(4096 \times \text{Fnom})$ | $10/(4096 \times \text{Fnom}) + 1 \text{ ns}$ | $5.6/(4096 \times \text{Fnom})$  |

| $Ch_1$     | $64/(4096 \times \text{Fnom})$ | $52/(4096 \times \text{Fnom})$                | $11.8/(4096 \times \text{Fnom})$ |

| $Ch_2$     | $64/(4096 \times \text{Fnom})$ | $4/(4096 \times \text{Fnom})$                 | $11.8/(4096 \times \text{Fnom})$ |

| $Ch_3$     | $64/(4096 \times \text{Fnom})$ | $20/(4096 \times \text{Fnom})$                | $11.8/(4096 \times \text{Fnom})$ |

| $Ch_4$     | $64/(4096 \times \text{Fnom})$ | $36/(4096 \times \text{Fnom})$                | $11.8/(4096 \times \text{Fnom})$ |

| $xCh_1$    | $64/(4096 \times \text{Fnom})$ | 0                                             | $51.8/(4096 \times \text{Fnom})$ |

| $xCh_2$    | $64/(4096 \times \text{Fnom})$ | $16/(4096 \times \text{Fnom})$                | $51.8/(4096 \times \text{Fnom})$ |

| $xCh_3$    | $64/(4096 \times \text{Fnom})$ | $32/(4096 \times \text{Fnom})$                | $51.8/(4096 \times \text{Fnom})$ |

| $xCh_4$    | $64/(4096 \times \text{Fnom})$ | $48/(4096 \times \text{Fnom})$                | $51.8/(4096 \times \text{Fnom})$ |

Table 5: Clock Signals

definition of delay, pulse width and period of the signal. The rise and fall time for all of these clock signals is 1ns.

Figure 26: Timing Definition

## 3.4 Component design

Apart from Op Amp, switches and capacitors are important part of switched-capacitor circuits.

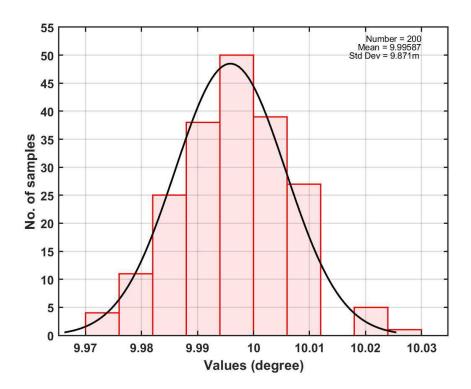

## 3.4.1 Switch design [25]

A simple MOSFET in its unit form can always be used as a switch. When the voltage at the gate terminal of the transistor goes high. The current starts to flow between the drain and source terminal due to the potential difference between them. For an NMOS transistor this gate to source voltage needs to be positive while for a PMOS

Figure 27: Parasitic Capacitances of the transistor

.

the gate to source voltage should be negative for the switch to be turned on. This gate signal is coming from the clock source and is 2.5V. Thus, the transistor can be assumed to be operating in the linear region and the current equation for this region is given by:

$$i_D = \frac{1}{2}\mu_n C_{ox} \frac{W}{L} (2(V_{GS} - V_T)V_{DS} - V_{DS}^2)$$

(31)

where  $\mu_n$  is the mobility of electrons and  $C_{ox}$  is the capacitance of the oxide material. These are the process dependent parameters. The resistance to this current when  $V_{GS} - V_T$  is greater than  $V_{DS}$  is called the on- resistance of the transistor and is given by:

$$R_{on} = \frac{1}{2k(V_{GS} - V_T)} \tag{32}$$

where,

$$k = \frac{1}{2}\mu_n C_{ox} \frac{W}{L} \tag{33}$$

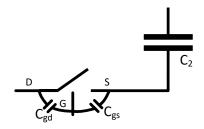

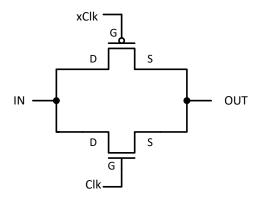

In a real switch, during the switching transient, there are capacitive currents coming from the parasitic capacitances of the device. The main source of these noise currents are capacitances  $C_{gd}$  and  $C_{gs}$ . In the switched-capacitor applications, there are capacitors connected to one or both terminal of the transistor. Therefore, the  $C_{gd}$  and  $C_{gs}$  form a capacitor divider with the switched capacitors as shown in Figure 27. If the capacitor  $C_2$  is of the order of 1pF and the  $C_{gs}$  is 10fF, then for the gate on voltage of 2.5V, this clock signal would be divided by 100 and would contain a clock-feedthrough noise of 25mV. Similarly, if the source terminal of the transistor is connected to a virtual ground node, and  $C_2$  is the feedback capacitor for an integrator. A charge equivalent to  $C_{gs}$  times 2.5V = 25fC can enter  $C_2$  and cause an output voltage step of 25mV. Hence, in order to minimize these transient affects, a transmission gate can be used as a switch. The on-resistance of this CMOS switch is the parallel equivalent of both NMOS and PMOS. The schematic for this switch is shown in Figure 28.

Thus this switch has lower voltage drop and increased dynamic range as smaller signal can be passed through it. A transmission gate consists on both NMOS and

Figure 28: Transmission Gate Implementation

Figure 29: Gate Signals for the TG transistors

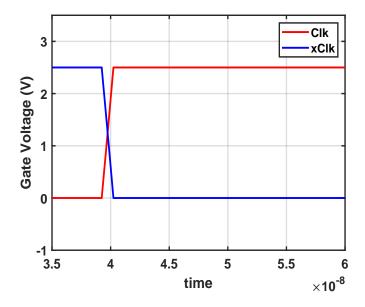

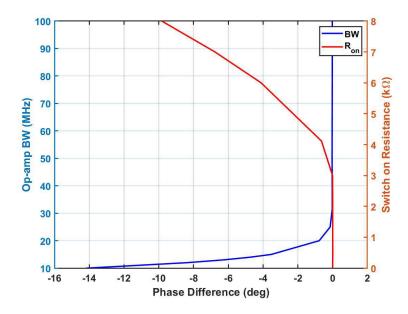

PMOS transistors. The clock signals applied to these NMOS and PMOS transistors are complementary as shown in Figure 29. The complementary gate signals can be achieved through an inverter, connected to the gate of the PMOS transistor. The incoming control signal is connected to the gate of NMOS transistor directly and to the gate of PMOS transistor through an inverter. When the control signal is high both PMOS and NMOS are turned on and the transmission gate is conducting else it is not conducting. The equivalent resistance of a transmission gate is lower compared to the individual transistor resistance because of the parallel connection. Therefore, the gate signals for the transmission gate is complementary. Moreover, this type of switch can conduct in both directions depending on the voltage polarity at its drain and source terminals. As a rule of thumb, a good switch-on resistance along-with the largest capacitance in the circuit makes the time constant equal to 1/7th of the sampling time. Switch on-resistance has a direct impact on the gain and phase shift

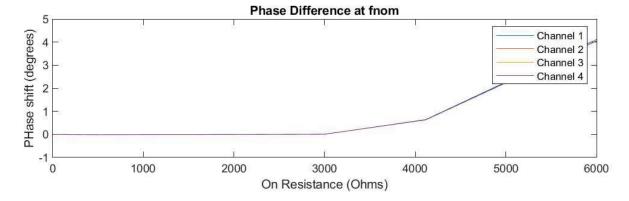

at the filter output. In the requirement specifications shown in the table above, the phase shift at the pole frequency has some limitation. As a target, the phase shift should not exceed 6 degrees over process variation. The main contributors to the phase shift in this circuit are transmission gate on-resistance and the bandwidth of the operational amplifier. To study the impact of the switch-on resistance, the circuit was simulated with ideal components and ideal Op Amp model. The switches used in this study were ideal. The switch resistance was varied and the phase shift from the nominal ideal cases was observed. The result of this study is shown in Figure 30.

Table 6: On Resistance

| Number of fingers (m) | $R_{on}$               | $oxed{5	ext{-sigma}\ R_{on}}$ | 5-sigma Phase-shift |

|-----------------------|------------------------|-------------------------------|---------------------|

| 3                     | $3.5 \mathrm{k}\Omega$ | $4.6 \mathrm{k}\Omega$        | 1.2 degrees         |

| 4                     | $2.7\mathrm{k}\Omega$  | $3.45 \mathrm{k}\Omega$       | 0.2 degrees         |

Table 7: Transmission gate design

| Transistor | Width                | Length | Number of fingers(m) |

|------------|----------------------|--------|----------------------|

| NMOS       | 400nm                | 560nm  | 4                    |

| PMOS       | $1.4 \mu \mathrm{m}$ | 560nm  | 4                    |

For the optimized design process of the transmission gate, first of all the PMOS and NMOS transistors that were to be used in the design were selected. The selected transistors are Global Foundaries 55nm triple-well 6 terminal NMOS and the corresponding PMOS. The reason for using these transistors was their triple well structure. The bulk of these transistors is less noisy and as noise is one of the main factors in the performance of switched-capacitor circuits. This would help in minimizing the bulk noise affect in the ASIC. Next, the minimum width

Figure 30: Phase Shift caused due to TG resistance

NMOS transistor was selected for the NMOS part of the transmission gate and the corresponding PMOS was 3.5 times wider than the NMOS. The PMOS transistor is usually 2.5 times wider than the NMOS transistor in the complementary structures. The reason for this is the mobility of holes which is 2.5 times slower than the mobility of the electrons. Here, the PMOS is 3.5 times wider because through simulations, it was found that this ratio gives a flat resistance across a large part of the operating voltage. This is the basic cell of the transmission gate and it has the resistance of  $9k\Omega$ . The resistance was then varied by changing the number of fingers and hence the width of the transistors.

From Figure 30, it can be seen that there is no significant difference in the phase shift when the switch on resistance is around  $3k\Omega$  and  $4k\Omega$ . Further, the Monte-Carlo simulation was performed for m=3 and m=4 and the 5 sigma variation for the on-resistance was calculated. The on-resistance value for these number of fingers and the corresponding 5-sigma values are summarized in Table 6.

Phase shift is also affected by the bandwidth of the operational amplifier and the mismatch in the capacitors. Out of the 6 degrees phase shift that we can have in the worst case, if m is chosen as 4, their is more margin for the phase shift caused by the mismatch and bandwidth of the Op Amp. Therefore, the switch design is summarized in Table 7 for lesser phase shift allowed because of the on-resistance.

#### 3.4.2 Capacitor design

For a constant distance between the capacitor plates for the technology, i.e., d, the capacitor dimensions for the capacitor values shown in Table 4 are calculated and computed in Table 8. Capacitor mismatch also has an affect on the phase shift of the

| Capacitor       | Width                 | Length                |

|-----------------|-----------------------|-----------------------|

| $Cu_{in}$       | $16.963 \mu { m m}$   | $16.963 \mu m$        |

| $Cu_c$          | $11.93 \mu { m m}$    | $11.93 \mu { m m}$    |

| $\overline{Cu}$ | $5.021 \mu { m m}$    | $5.021 \mu { m m}$    |

| $C_{rs}$        | $5.28 \mu \mathrm{m}$ | $5.28 \mu \mathrm{m}$ |

| $C_c$           | $16.525 \mu { m m}$   | $16.525 \mu { m m}$   |

| $C_L$           | $39.7 \mu \mathrm{m}$ | $39.7 \mu \mathrm{m}$ |

Table 8: Capacitor design

design. To study this affect, Monte-Carlo simulations were performed and 5-sigma variation for the phase shift because of mismatch was observed. The Monte-Carlo simulation result of this simulation are shown in Figure 31.

# 3.5 Operational Amplifier design [28]

Operational amplifier or an an Op Amp, is an active component of any switched capacitor circuit, ideally it is a voltage controlled voltage source which means that

Figure 31: Monte Carlo Simulation results for Phase Shift due to Capacitor Mismatch in the TG

the output voltage of an op-amp depends on the change of the voltage at its input terminal. Moreover ideally, an Op Amp has infinite voltage gain, infinite bandwidth, infinite input resistance and zero output resistance. Practically, the Op Amps have finite gain which is highest for the low frequency signals. The carrier mobility and stray capacitance effect increases at higher frequencies. As a result, the gain decreases at higher frequencies. This limits the bandwidth of the Op Amp. Bandwidth is defined as the range of input signal frequency for which the output is greater than 0dB or unity. There is also a slew rate limitation for a real Op Amp. The slew rate is defined as the rate of change of output signal level of the Op Amp with respect to the change in input voltage. It is measured in V/s. For a large step at the input, the output will follow the input voltage slowly. The maximum rate of input change that an amplifier can follow is called it's slew rate.

The low-pass filter is required to be implemented in differential form, for this purpose it requires a fully- differential Op Amp. A fully-differential amplifier has differential outputs whereas a standard operational amplifier has single ended output. For a fully differential amplifier a common-mode circuitry is needed to set the common mode voltage of the amplifier to a predefined level. Conventionally, this is at the middle of the maximum available supply range. Whereas, for a standard single ended operational amplifier, the output voltage level is the same as input signal. This is the reason behind increased dynamic range of the fully differential amplifier. A

fully-differential system has inherited rejection to the external noise source. The noise or signal that appears at the input of the Op Amp as common mode signal is fully rejected by the differential Op Amp. This is the reason behind immunity of the fully differential amplifiers against common mode noise signals. Moreover, in comparison to the single-ended differential amplifier, fully differential op amps have increased dynamic range because the output signal is differential in contrast to the single-ended output signal.

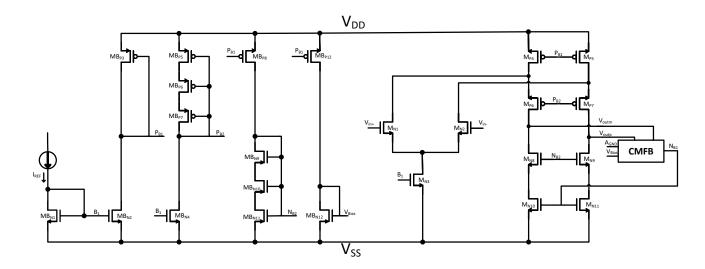

Two types of operational amplifiers were considered to be implemented in the switched-capacitor circuit, i.e., the miller compensated two stage Op Amp and the folded cascode Op Amp. These amplifiers are discussed and compared in context of the low-pass filter Op Amp design in the later sections.

#### 3.5.1 Two stage Miller Compensated Op Amp

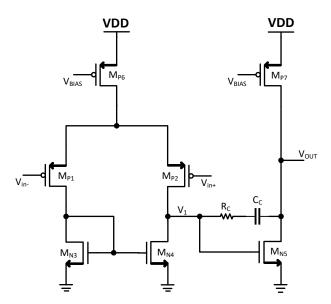

As the name implies, a two stage amplifier consists of two stages, i.e., a differential amplifier stage and a gain stage. The overall gain of the amplifier consists on the gain of these two stages. Typically, the first stage is a differential input single ended output amplifier while the second stage is the common-source amplifier. The second stage has an active load. The circuitry is shown in Figure 32.

Figure 32: Two Stage Miller Compensated Operational Amplifier

It has the p-channel devices for the input differential pair formed by the transistors  $M_{P1}$  and  $M_{P2}$ , whereas the n-channel  $M_{N3}$  and  $M_{N4}$  is the active load for this stage. Common source gain stage is formed by the n-channel  $M_{N5}$  with  $M_{P7}$  acting as an active load for this stage. Transistor  $M_{P6}$  is the current mirror biasing transistor for the differential stage. Here, the Op Amp is implemented using complementary devices for both the gain stages.  $C_C$  and  $R_c$  provides the dominant pole compensation and lead compensation respectively. To understand these compensations, consider

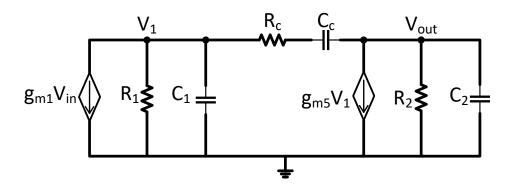

the small signal equivalent model for the Op Amp in Figure 33.

Here,  $V_1$  is the single ended output from the first stage of the Op Amp.  $R_1$  and  $C_1$  is the output resistance and capacitance of the first stage. Similarly,  $R_2$  and  $C_2$  is the resistance and capacitance at the output node. The transfer function for the dominant pole compensation alone can be written as:

$$\frac{V_{out}}{V_{in}} = \frac{g_{m1}g_{m5}R_1R_2(1 - \frac{sC_c}{g_{m5}})}{1 + sa + s^2b}$$

(34)

where

$$a = g_{m5}R_1R_2C_c + R_1(C_1 + C_c) + R_2(C_2 + C_c)$$

(35)

$$b = R_1 R_2 (C_1 C_2 + C_1 C_c + C_2 C_c) (36)$$

Solving the transfer function for the first and second pole( $\omega_{p1}$  and  $\omega_{p2}$  respectively) gives,

$$\omega_{p1} = \frac{1}{g_{m5}R_1R_2C_c} \tag{37}$$

and

$$\omega_{p2} \simeq \frac{g_{m5}}{C_1 + C_2} \tag{38}$$

and a zero at

$$\omega_{z1} = \frac{-g_{m5}}{C_c} \tag{39}$$

Whereas without the compensation capacitor, the transfer function for the small signal model would give two poles defined by the capacitors  $C_1$  and  $C_2$ . As these capacitance values are defined approximated by the gate to source capacitance of transistor  $M_{N5}$  and load capacitance. In the magnitude bode plot of the two pole transfer function, the gain decreases with the slope of 20 dB/decade after first pole and after the second pole it decreases with 40 db/decade. Also, there is a phase shift of 180 degrees after the second pole. The phase margin of the transfer function is measured as the difference of phase between the unity gain frequency and 180 degrees. The more difference there is the more stable is the Op Amp in negative

Figure 33: Small Signal Model for the op amp in Figure 32

feedback configuration. As the small change in the load capacitance value in the feedback can affect the phase and if the feedback becomes positive that makes the Op Amp unstable. Without compensation, the two poles are very close to each other and the phase margin is very low any parasitic pole or an additional capacitor in the feedback can decrease the phase margin further. From the above relations, we can see that first pole of the system depends on the transconductance  $g_m$  of the common-source drive transistor. Thus, the pole is moved to the lower frequency which decreases the 3-dB bandwidth of the system but increase the phase margin and stability. For the lead compensation, an additional pole and modified zero is introduced to the transfer function. In equation 34 the zero is now given as:

$$\omega_{z1} = \frac{-1}{C_c(\frac{1}{g_{m5}} - R_C)} \tag{40}$$

Choosing the value of  $R_C$  to be greater than  $1/g_{m5}$  moves this right half plane zero to left half plane zero. It cancels the affect of  $\omega_{p2}$  if the load capacitance is known and to increase the phase margin further as discussed above select  $R_C$  even greater than that to move this zero at a frequency slightly higher than the unity gain frequency. The compensation is an important part of op-amp design if the op-amp is intended to be used in the feedback configuration. One important thing to consider here is the type of devices used for input differential stage and common source stage, they are always used in complementary manner.

The choice of whether to use p-channel or n-channel devices as the input stage transistors and the complementary device for the common source stage depends on several trade-offs. For a high frequency applications, the above mentioned configuration is preferred as it increases the transconductance of the second stage and the second pole and unity gain frequency of the op amp is dependent on the transconductance of the second stage. Also p-channel transistors have less 1/f noise than the n-channel devices because 1/f is mainly caused when carriers (electrons or holes) of a device are trapped in the surface states and holes have less tendency to get trapped in the surface states than electrons. When the resistive loads are meant to be driven, an output buffer stage is added to the above mentioned topology. This decreases the output impedance of the Op Amp. If no resistive load is required to be driven, the output node can have higher impedance. One of the Op Amps which have high output impedance node is the folded cascode Op Amp described in the next section.

#### 3.5.2 Folded Cascode Op Amp

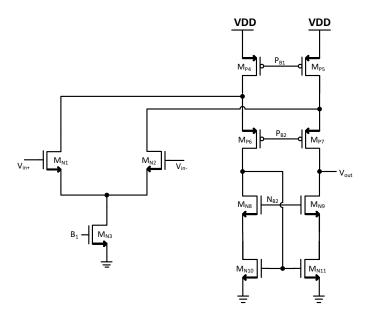

Folded cascode Op Amp is the type of op-amp commonly referred as operational transconductance amplifier (OTA) because of the ratio of the output current to the input voltage. This amplifier topology has a very high impedance output node while the other nodes in the circuit are low impedance and hence these amplifiers have higher speed. The low impedance nodes within the op-amp can result in reduced voltage signals at them but the current signals can be large. Moreover, these amplifiers do not require additional compensation mechanism for stability as the compensation for them comes from the load capacitance. The Op Amp becomes more

Figure 34: Folded cascode Operational Amplifier

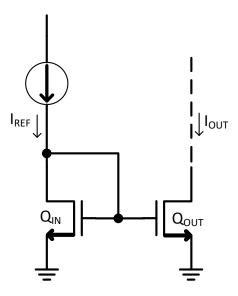

stable as the load capacitance increases but its speed decreases. In these amplifiers, cascode transistors opposite in channel type to the input differential pair follows the input differential pair. These Op Amps uses wide-swing current mirrors rather than the conventional current mirror. With the conventional current mirror it is difficult to obtain large output swing and high gain because of the their lower output impedance. The wide swing current mirror provide better gain and higher output signal swing. The main idea in wide swing current mirrors is to bias the transistors  $M_{N10}$  and  $M_{N11}$  with lowest bias voltage which prevents them from operating the transistors in the triode region. The transistor  $M_{N10}$  and  $M_{N8}$  provides diode connection for the current mirroring through transistors  $M_{N9}$  and  $M_{N11}$ . The circuit for the folded cascode op-amp is shown in Figure 34.

The structure consists on n-channel MOS device for the input differential pair and the complementary p-channel device for the cascode. Transistor  $M_{N3}$  provides tail current for the differential pair. Depending on the input voltage signal the current through either of  $M_{N1}$  or  $M_{N2}$  starts to increase or decreases. For higher  $V_{in+}$ ,  $M_{N1}$  turns on and the gate voltage starts to increase, and near the positive peak or maximum  $V_{in+}$ , the transistor is operating near the edge of the saturation region (for saturation Vds  $\geq$  Veff) and eventually enters into the triode region at the peak. Now when  $V_{in-}$  becomes greater it takes some time for the transistor  $M_{N1}$  to come out of the triode region. To make sure that the transistor channels always have some current flowing, the current through the transistors  $M_{P4}$  and  $M_{P5}$  is kept euqal or higher than the current through  $M_{N3}$ . The small signal model for this op amp is shown in Figure 34. All nodes except the output nodes are low impedance nodes. It is assumed that in this case almost all of the input current flows to the output through different paths. Usually, all the capacitance values except the output capacitance are very small. Therefore, the pole or zero caused by them are at frequencies higher

than the unity gain frequency defined by the load capacitance. Hence, the small signal transfer function for this topology is defined as follows,

$$\frac{V_{out}}{V_{in}} = \frac{g_{m1}R_{out}}{1 + sC_LR_{out}} \tag{41}$$

where  $R_{out}$  is the impedance seen at the output node and it value can be computed as:

$$R_{out} = (g_{m9}r_{ds9}r_{ds11})||(g_{m7}r_{ds7}(r_{ds2}||r_{ds5}))$$

(42)

which is a high value. Both of these operational amplifiers topologies are compared in Table 9.

Table 9: Operational Amplifier topologies comparison

The load for the low pass filter is purely capacitive and power consumption is one of the important target of this design. Therefore, the selected topology for the low-pass filter Op Amp design is the folded cascode Op Amp.

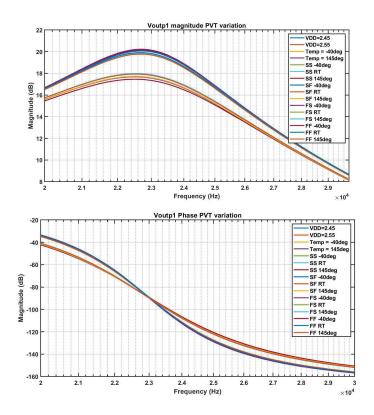

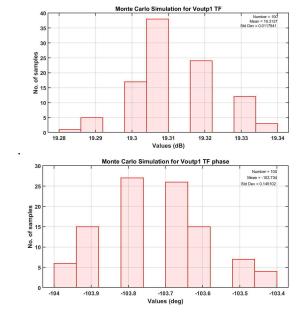

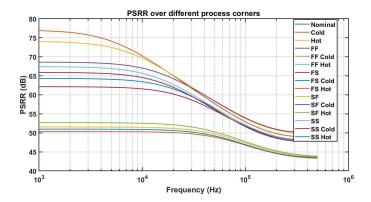

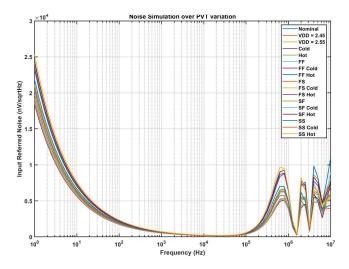

#### 3.5.3 Folded Cascode Op Amp Design