# REALIZATION OF ANALOG SIGNAL PROCESSING MODULES USING CARBON NANOTUBE FIELD EFFECT TRANSISTORS

MUHAMMAD IDREES MASUD

UNIVERSITI TEKNOLOGI MALAYSIA

# REALIZATION OF ANALOG SIGNAL PROCESSING MODULES USING CARBON NANOTUBE FIELD EFFECT TRANSISTORS

MUHAMMAD IDREES MASUD

A thesis submitted in fulfilment of the requirements for the award of the degree of Doctor of Philosophy

> School of Electrical Engineering Faculty of Engineering Universiti Teknologi Malaysia

> > JUNE 2022

#### ACKNOWLEDGEMENT

I would like to thank Allah for giving me the opportunity to undertake my studies far from home. Moreover, I thank Prof. Dr. Abu Khari Bin A'ain for his continuous guidance, tireless efforts, encouragement, and patience regarding this study. Prof. Dr. Abu Khari Bin A'ain was my first supervisor, but unfortunately he retired before my thesis submission. I am indebted for his support until the completion of my thesis.

My special gratitude is due to my supervisors Dr. Muhammad Nadzir bin Marsono, Dr. Nasir Shaikh Husin and external supervisor Dr. Iqbal A. Khan for their valuable advice and friendly help. Their critical reviews on my work and interesting suggestions have been constructive throughout this study.

My special gratitude is due to my parents and my wife for their loving support. Without their encouragement and understanding, it would have been hard for me to achieve my research objectives.

I appreciate all my friends, especially Arbab Alamgir, Dr. Ghani Ur Rehman, Yasir Ismail, Dr Waheed Younis, Dr Zubair Khalid, Dr Rashid and Dr. Touqeer Jumani, who advised and encouraged me whenever it was difficult for me.

#### ABSTRACT

This thesis presents the realization and performance analysis of several carbon nanotube field effect transistor (CNTFET) based analog signal processing (ASP) modules. CNTFET is predicted as a possible successor to conventional silicon complementary metal oxide semiconductor (CMOS), which has reached its scaling limits. The CMOS based ASP modules face significant challenges at deep nanoscale, resulting in severe performance degradations due to short channel effects. The main goal of this work is to realize CNTFET active building blocks (ABBs), and then to utilize these ABBs for realization of low-voltage, low-power, and high-frequency ASP modules. The proposed ABBs have low power dissipation, reduced parasitic components, and minimum number of CNTFETs. The proposed modules are active inductor (AI), first-order phase shifter, and second-order phase shifter. This research proposes a new CNTFET based grounded AI (GAI) circuit with high self-resonance frequency (SRF), wide tunable inductance range, and high quality factor. Simulation results demonstrate that the GAI offers tunable inductance from 4.4 nH to 287.4 nH with a maximum SRF of 101 GHz. It consumes very low power dissipation of 0.337 mW. In comparison to high performance available GAI circuits, the proposed GAI shows 34% reduction in power dissipation and nine times higher SRF. A highfrequency low-noise amplifier (LNA) circuit is also designed by utilizing the proposed GAI to showcase its application. The simulation result shows high frequency bandwidth of 17.5 GHz to 57 GHz, 15.9 dB maximum voltage gain, better than -10 dB input matching, and less than 3 dB noise figure. This research also proposes a compact wideband first-order phase shifter (FOPS) and active-only FOPS (AOFOPS). Simulation results demonstrate the FOPS has a tunable pole frequency range between 1.913 GHz and 40.2 GHz, input and output voltage noises of 4.402 nV/ $\sqrt{Hz}$  and 4.414 nV/ $\sqrt{Hz}$  respectively, and power dissipation of 0.4862 mW. The AOFOPS circuit also offers a wide tunable range of pole frequency between 34.2 GHz to 56.4 GHz with input noise and output noise of 6.822 nV/ $\sqrt{Hz}$ and 6.761 nV/ $\sqrt{Hz}$  respectively, and power dissipation of only 0.0338 mW. The AOFOPS dissipates 12.40 times less power in comparison to state-of-art FOPS circuits. This work also proposes active-only second-order phase shifter. The proposed circuit provides a tunable pole frequency between 16.2 GHz to 42.5 GHz, with input and output noises of 21.698 nV/ $\sqrt{Hz}$  and 21.593 nV/ $\sqrt{Hz}$  respectively, while consuming 0.2256 mW power. All circuit performances are verified through HSPICE simulation by utilizing the Stanford CNTFET model at 16 nm technology node with supply voltage of 0.7 V.

#### ABSTRAK

Tesis ini membentangkan realisasi dan analisis prestasi beberapa modul pemprosesan isyarat analog (ASP) berasaskan transistor kesan medan nanotiub karbon (CNTFET). CNTFET diramalkan sebagai pengganti kepada semikonduktor oksida logam pelengkap (CMOS) silikon lazim, yang sudah mencapai had penskalaannya. Modul ASP CMOS menghadapi cabaran besar pada skala-nano dalam, yang menyebabkan kemerosotan prestasi yang teruk kerana kesan saluran pendek. Tujuan utama kerja ini adalah untuk merealisasi blok binaan aktif (ABB), dan kemudiannya digunakan untuk merealisasi modul ASP voltan-rendah dan kuasarendah yang berfrekuensi tinggi. ABB yang dicadangkan mempunyai pelesapan kuasa yang rendah, kebolehtalaan yang tinggi, pengurangan komponen parasit, dan menggunakan bilangan CNTFET yang minimum. Modul yang dicadangkan adalah induktor aktif (AI), penganjak fasa tertib-pertama, dan penganjak fasa tertib-kedua. Penyelidikan ini mencadangkan litar AI terbumi (GAI) CNTFET yang baharu yang mempunyai ciri-ciri frekuensi swaresonans (SRF) yang tinggi, kearuhan yang boleh ditala dalam julat yang lebar, dan faktor kualiti yang tinggi. Hasil simulasi menunjukkan bahawa litar GAI menawarkan aruhan boleh ditala dari 4.4 nH hingga 287.4 nH dengan SRF maksimum 101 GHz. Ia melesapkan kuasa yang sangat rendah iaitu 0.337 mW. Berbandingkan dengan litar GAI berprestasi tinggi sedia ada, GAI yang dicadangkan menunjukkan pengurangan pelesapan kuasa sebanyak 34% dan peningkatan SRF sembilan kali lebih tinggi. Litar penguat rendah-hingar (LNA) berfrekuensi tinggi juga direka bentuk berdasarkan GAI yang dicadangkan untuk menunjukkan pengaplikasiannya. Hasil simulasi menunjukkan lebar jalur frekuensi yang tinggi iaitu 17.5 GHz hingga 57 GHz, gandaan voltan maksimum 15.9 dB, padanan input melebihi -10 dB, dan angka hingar kurang dari 3 dB. Penyelidikan ini juga mencadangkan penganjak fasa tertib-pertama (FOPS) dan FOPS hanya-aktif (AOFOPS). Hasil simulasi FOPS menunjukkan julat frekuensi kutub yang boleh diatur antara 1.913 GHz dan 40.2 GHz, hingar voltan masukan dan voltan keluaran masing-masing 4.402 nV/ $\sqrt{Hz}$  dan 4.414 nV/ $\sqrt{Hz}$ , dan pelesapan kuasa 0.4862 mW. Litar AOFOPS ini juga menawarkan frekuensi kutub yang dapat ditala dengan luas antara 34.2 GHz hingga 56.4 GHz dengan hingar masukan dan hingar keluaran masing-masing 6.822 nV/ $\sqrt{Hz}$  dan 6.761 nV/ $\sqrt{Hz}$  dan pelepasan kuasa hanya 0.0338 mW. Litar AOFOPS yang dicadangkan dapat mengurangkan pelesapan kuasa sebanyak 12.40 kali berbanding litar FOPS terkini. Penyelidikan ini juga mencadangkan penganjak fasa hanya-aktif tertib-kedua. Litar yang dicadangkan menyediakan frekuensi kutub yang dapat ditala antara 16.2 GHz hingga 42.5 GHz, dengan hingar masukan dan hingar keluaran masing-masing 21.698 nV/ $\sqrt{Hz}$  dan 21.593 nV/ $\sqrt{Hz}$ , dan penggunaan kuasa 0.2256 mW. Semua prestasi litar disahkan melalui simulasi HSPICE yang menggunakan model CNTFET Stanford pada nod teknologi 16 nm dengan bekalan kuasa 0.7 V.

## **TABLE OF CONTENTS**

### TITLE

| Ι               | DECLARATION |                                         |                                             | iii   |

|-----------------|-------------|-----------------------------------------|---------------------------------------------|-------|

| DEDICATION      |             |                                         |                                             | iv    |

| ACKNOWLEDGEMENT |             |                                         |                                             | V     |

| A               | ABSTI       | RACT                                    |                                             | vi    |

| A               | ABSTI       | RAK                                     |                                             | vii   |

| 7               | <b>FABL</b> | E OF (                                  | CONTENTS                                    | viii  |

| Ι               | LIST (      | OF TA                                   | BLES                                        | xi    |

| Ι               | LIST (      | OF FIG                                  | URES                                        | xii   |

| Ι               | LIST (      | OF AB                                   | BREVIATIONS                                 | xvii  |

| Ι               | LIST (      | OF SYN                                  | MBOLS                                       | xviii |

| CHAPTER         | 1           | INTRO                                   | ODUCTION                                    | 1     |

| 1               | .1          | Backgr                                  | ound                                        | 1     |

| 1               | .2          | Problem Statement                       |                                             |       |

| 1               | .3          | Research Objectives                     |                                             |       |

| 1               | .4          | Scope and Limitations                   |                                             |       |

| 1               | .5          | Research Contributions                  |                                             |       |

| 1               | .6          | Thesis Organization                     |                                             |       |

| CHAPTER         | 2           | LITEF                                   | RATURE REVIEW                               | 11    |

| 2               | 2.1         | Introduction                            |                                             | 11    |

| 2               | 2.2         | Active                                  | Inductor                                    | 11    |

|                 |             | 2.2.1                                   | Gyrator-C Active Inductor                   | 12    |

|                 |             | 2.2.2                                   | Grounded Active Inductor Circuit Topologies | 15    |

| 2               | 2.3         | Phase S                                 | Shifter                                     | 22    |

|                 |             | 2.3.1                                   | First Order Phase Shifter                   | 25    |

|                 |             | 2.3.2                                   | Second Order Phase Shifter                  | 31    |

| 2               | 2.4         | Carbon Nanotube Field Effect Transistor |                                             |       |

| 2.5       | Summary                                      | 40  |  |

|-----------|----------------------------------------------|-----|--|

| CHAPTER 3 | METHODOLOGY                                  | 41  |  |

| 3.1       | Introduction                                 | 41  |  |

| 3.2       | Research Framework                           | 42  |  |

| 3.3       | Realization of ABB                           | 44  |  |

| 3.4       | Realization of ASP Modules                   | 46  |  |

| 3.5       | Device Model                                 | 48  |  |

| 3.6       | Summary                                      | 50  |  |

| CHAPTER 4 | <b>GROUNDED ACTIVE INDUCTOR</b>              | 51  |  |

| 4.1       | Introduction                                 | 51  |  |

| 4.2       | CNTFET Based Active Building Blocks          | 52  |  |

|           | 4.2.1 CNTFET Based Inverting Voltage Buffer  | 53  |  |

|           | 4.2.2 CNTFET Based Transconductance Elements | 59  |  |

| 4.3       | PTE and NTE Based GAI Circuit Topology       | 63  |  |

| 4.4       | GAI Design and Verification                  | 70  |  |

| 4.5       | LNA Design Using Proposed CNTFET GAI         | 78  |  |

|           | 4.5.1 Circuit Description                    | 79  |  |

|           | 4.5.2 LNA Simulations Results                | 81  |  |

| 4.6       | GAI Comparative Study                        | 85  |  |

| 4.7       | Summary                                      |     |  |

| CHAPTER 5 | IVB BASED FIRST ORDER PHASE SHIFTERS         | 87  |  |

| 5.1       | Introduction                                 | 87  |  |

| 5.2       | IVB Based FOPS                               | 88  |  |

|           | 5.2.1 FOPS Circuit Description               | 88  |  |

|           | 5.2.2 FOPS Design and Verification           | 92  |  |

| 5.3       | IVB Based AOFOPS                             | 101 |  |

|           | 5.3.1 AOSOPS Circuit Description             | 102 |  |

|           | 5.3.2 AOSOPS Design and Verification         | 105 |  |

| 5.4       | FOPS Comparative Study                       | 110 |  |

| 5.5       | Summary                                      | 110 |  |

| CHAPTER 6     | ACTIVE ONLY SECOND ORDER PHASE SHIFTER | 113 |  |

|---------------|----------------------------------------|-----|--|

| 6.1           | Introduction                           |     |  |

| 6.2           | AOSOPS Circuit Description             |     |  |

| 6.3           | AOSOPS Design and Verification         |     |  |

| 6.4           | AOSOPS Comparative Study               | 129 |  |

| 6.5           | Summary                                | 130 |  |

| CHAPTER 7     | CONCLUSION                             | 131 |  |

| 7.1           | Research Summary                       | 131 |  |

| 7.2           | Future Work                            | 132 |  |

| REFERENCES    |                                        | 135 |  |

| LIST OF PUBLI | LIST OF PUBLICATIONS                   |     |  |

# LIST OF TABLES

| TABLE NO. | TITLE                                                  | PAGE |

|-----------|--------------------------------------------------------|------|

| Table 2.1 | Summary of related GAI circuits                        | 23   |

| Table 2.2 | Summary of related FOPS circuits                       | 30   |

| Table 2.3 | Summary of related SOPS circuits                       | 35   |

| Table 3.1 | The CNTFET parameters                                  | 49   |

| Table 4.1 | Design parameter values for dual negative feedback LNA | 82   |

| Table 4.2 | Design parameter values for GAI of Figure 4.18         | 82   |

| Table 4.3 | GAI performance comparison                             | 86   |

| Table 5.1 | Comparison with reported FOPS topologies               | 111  |

| Table 6.1 | Comparison with reported SOPS topologies               | 129  |

# LIST OF FIGURES

| FIGURE NO.  | TITLE                                                                                                                                         | PAGE |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|

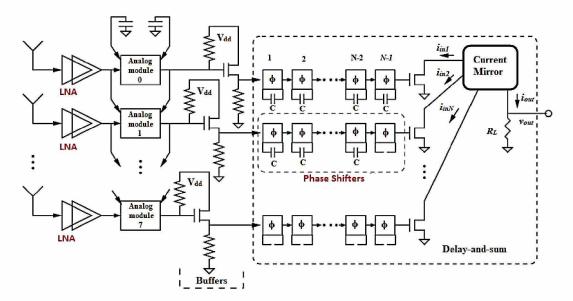

| Figure 1.1  | Beamforming scheme [17]                                                                                                                       | 3    |

| Figure 2.1  | Gyrator-C GAI [24]                                                                                                                            | 12   |

| Figure 2.2  | Bode plot of gyrator-C AI input impedance $(Z_{in})$ [25]                                                                                     | 14   |

| Figure 2.3  | GAI topologies reported in [35] (a) Basic flipped-AI (b)<br>Cascoded flipped-AI (c) Small signal equivalent circuit<br>of cascoded flipped-AI | 16   |

| Figure 2.4  | GAI reported in [36]                                                                                                                          | 17   |

| Figure 2.5  | GAI reported in [37]                                                                                                                          | 18   |

| Figure 2.6  | GAI reported in [43]                                                                                                                          | 19   |

| Figure 2.7  | GAI reported in [45]                                                                                                                          | 21   |

| Figure 2.8  | GAI reported in [46]                                                                                                                          | 22   |

| Figure 2.9  | FOPS reported in [70]                                                                                                                         | 26   |

| Figure 2.10 | FOPS reported in [71]                                                                                                                         | 26   |

| Figure 2.11 | FOPS reported in [72]                                                                                                                         | 27   |

| Figure 2.12 | FOPS reported in [73]                                                                                                                         | 28   |

| Figure 2.13 | FOPS reported in [79]                                                                                                                         | 28   |

| Figure 2.14 | FOPS reported in [80]                                                                                                                         | 29   |

| Figure 2.15 | SOPS reported in [48]                                                                                                                         | 32   |

| Figure 2.16 | SOPS reported in [49]                                                                                                                         | 32   |

| Figure 2.17 | SOPS reported in [85] (a) Topology-1 (b) Topology-2                                                                                           | 33   |

| Figure 2.18 | SOPS reported in [86]                                                                                                                         | 34   |

| Figure 2.19 | CNT structure (a) Single-wall (a) Multi-wall                                                                                                  | 36   |

| Figure 2.20 | CNTFET structure                                                                                                                              | 37   |

| Figure 2.21 | A graphene sheet rolled to demonstrate formation of various types of single-wall CNTs [88]                                                    | 38   |

| Figure 3.1  | Research framework                                                                                                                            | 43   |

| Figure 3.2  | Roadmap to realization of ABB                                                                                                                 | 45   |

| Figure 3.3  | Roadmap to realization of ASP module                                         | 47 |

|-------------|------------------------------------------------------------------------------|----|

| Figure 4.1  | IVB (a) CNTFET implementation (b) Symbol                                     | 54 |

| Figure 4.2  | IVB non-ideal parasitic model                                                | 54 |

| Figure 4.3  | Frequency response of IVB output impedance                                   | 55 |

| Figure 4.4  | Impact of variation of $N_T$ on $R_o$                                        | 56 |

| Figure 4.5  | Impact of variation of $N_T$ on $C_i$ and $C_o$                              | 56 |

| Figure 4.6  | Impact of variation of $N_T$ on power dissipation                            | 56 |

| Figure 4.7  | Impact of variation of $D_T$ on $R_o$                                        | 57 |

| Figure 4.8  | Impact of variation of $D_T$ on power dissipation                            | 57 |

| Figure 4.9  | Impact of variation of $S_T$ on $R_o$                                        | 58 |

| Figure 4.10 | Impact of variation of $S_T$ on power dissipation                            | 58 |

| Figure 4.11 | NTE (a) CNTFET implementation (b) Symbol                                     | 59 |

| Figure 4.12 | NTE non-ideal parasitic model                                                | 59 |

| Figure 4.13 | PTE (a) CNTFET implementation (b) Symbol                                     | 60 |

| Figure 4.14 | PTE non-ideal parasitic model                                                | 60 |

| Figure 4.15 | Frequency response of transconductance of PTE and NTE with different $N_T s$ | 61 |

| Figure 4.16 | Impact of variation of $N_T$ on $g_m$                                        | 62 |

| Figure 4.17 | Impact of variation of $N_T$ on power dissipation                            | 63 |

| Figure 4.18 | Proposed CNTFET based GAI topology                                           | 63 |

| Figure 4.19 | Varactor transistor level realization with its symbol                        | 64 |

| Figure 4.20 | Equivalent small signal model at node $V_1$                                  | 64 |

| Figure 4.21 | Equivalent small signal model at node $V_2$                                  | 64 |

| Figure 4.22 | Equivalent small signal model at node $V_i$                                  | 65 |

| Figure 4.23 | RLC equivalent circuit for proposed CNTFET based GAI                         | 69 |

| Figure 4.24 | Frequency response of $Z_{in}$ magnitude at $V_{tune} = -0.60 V$             | 72 |

| Figure 4.25 | Frequency response of $Z_{in}$ phase at $V_{tune} = -0.60 V$                 | 72 |

| Figure 4.26 | Frequency response of GAI inductance (for positive values only)              | 73 |

| Figure 4.27 | Frequency response of GAI QF at $V_{tune} = -0.60 V$                                              | 74 |  |

|-------------|---------------------------------------------------------------------------------------------------|----|--|

| Figure 4.28 | Impact of variation of $k$ on inductance $L$                                                      |    |  |

| Figure 4.29 | Impact of variation of k on SRF                                                                   | 75 |  |

| Figure 4.30 | Frequency response of $Z_{in}$ magnitude at different values of $V_{tune}$                        | 76 |  |

| Figure 4.31 | Frequency response of GAI inductance at different values of $V_{tune}$ (for positive values only) | 76 |  |

| Figure 4.32 | Variation of GAI inductance versus V <sub>tune</sub>                                              | 77 |  |

| Figure 4.33 | Variation of GAI SRF versus V <sub>tune</sub>                                                     | 77 |  |

| Figure 4.34 | Dual negative feedback LNA [113]                                                                  | 79 |  |

| Figure 4.35 | Dual negative feedback LNA                                                                        | 80 |  |

| Figure 4.36 | GAI based LNA gain versus frequency                                                               | 83 |  |

| Figure 4.37 | GAI based LNA NF versus frequency                                                                 | 83 |  |

| Figure 4.38 | $S_{11}$ versus frequency                                                                         | 84 |  |

| Figure 4.39 | $S_{22}$ versus frequency                                                                         | 84 |  |

| Figure 4.40 | $S_{12}$ versus frequency                                                                         | 85 |  |

| Figure 5.1  | CNTFET-C FOPS topology-1                                                                          | 89 |  |

| Figure 5.2  | CNTFET-C FOPS topology-2                                                                          | 91 |  |

| Figure 5.3  | Calculated and simulated frequency response of gain of the proposed FOPS topology-1               | 93 |  |

| Figure 5.4  | Calculated and simulated frequency response of phase angle of the proposed FOPS topology-1        | 93 |  |

| Figure 5.5  | Frequency response of input output noise of the proposed FOPS topology-1                          | 94 |  |

| Figure 5.6  | Output resistance $R_{OT}$ variations with different values of $V_C$                              | 95 |  |

| Figure 5.7  | Calculated and simulated frequency response of gain of the proposed FOPS topology-2               | 95 |  |

| Figure 5.8  | Calculated and simulated frequency response of phase angle of the proposed FOPS topology-2        | 96 |  |

| Figure 5.9  | Frequency response of input output noise of the proposed FOPS topology-2                          | 96 |  |

| Figure 5.10 | Frequency response of gain of the FOPS topology-2 at different $V_C$                                  | 97  |

|-------------|-------------------------------------------------------------------------------------------------------|-----|

| Figure 5.11 | Frequency response of phase angle of the FOPS topology-2 at different $V_C$                           | 97  |

| Figure 5.12 | Monte Carlo simulations of FOPS topology-2 for gain at $V_C = 0.40 V$                                 | 98  |

| Figure 5.13 | Monte Carlo simulations of FOPS topology-2 for phase at $V_C = 0.40 V$                                | 99  |

| Figure 5.14 | Frequency response of FOPS topology-2 gain with different supply voltages $V_{DD}$ at $V_C = 0.40 V$  | 99  |

| Figure 5.15 | Frequency response of FOPS topology-2 phase with different supply voltages $V_{DD}$ at $V_C = 0.40 V$ | 100 |

| Figure 5.16 | Frequency response of FOPS topology-2 gain with different temperatures at $V_C = 0.40 V$              | 100 |

| Figure 5.17 | Frequency response of FOPS topology-2 phase with different temperatures at $V_C = 0.40 V$             | 101 |

| Figure 5.18 | CNTFET-AOFOPS transistor level realization                                                            | 102 |

| Figure 5.19 | CNTFET based varactor (a) Transistor level realization (b) Symbol                                     | 102 |

| Figure 5.20 | C-V characteristics of varactor with different $\ensuremath{N_{T}}$                                   | 105 |

| Figure 5.21 | Calculated and simulated frequency response of gain of the AOFOPS at $V_{tune} = -0.32 V$             | 106 |

| Figure 5.22 | Calculated and simulated frequency response of phase of<br>the AOFOPS at $V_{tune} = -0.32 V$         | 106 |

| Figure 5.23 | Frequency response of input and output noises of AOFOPS at $V_{tune} = -0.32 V$                       | 107 |

| Figure 5.24 | Monte Carlo simulations of AOFOPS for gain at $V_{tune} = -0.32 V$                                    | 108 |

| Figure 5.25 | Monte Carlo simulations of AOFOPS for phase at $V_{tune} = -0.32 V$                                   | 108 |

| Figure 5.26 | Frequency response of gain of the AOFOPS for different control voltages <i>Vtune</i>                  | 109 |

| Figure 5.27 | Frequency response of phase of the AOFOPS for different control voltages <i>Vtune</i>                 | 109 |

| Figure 6.1  | CNTFET based AOSOPS                                                                                   | 114 |

| Figure 6.2  | CNTFET based VCR (a) Transistor level realization (b) Symbol                                                                               | 115 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 6.3  | CNTFET based AOSOPS with NTE and PTE parasitics                                                                                            | 117 |

| Figure 6.4  | Simplified circuit for AOSOPS with parasitics                                                                                              | 118 |

| Figure 6.5  | Frequency response of PTE and NTE transconductance with $N_T=2$                                                                            | 120 |

| Figure 6.6  | CV characteristics of varactor with $N_T = 150$                                                                                            | 122 |

| Figure 6.7  | Calculated (obtained from Equation 6.17) and simulated frequency response of gain of the AOSOPS at $V_{tune}$ =-0.308 V and $V_Q$ =0.68 V  | 122 |

| Figure 6.8  | Calculated (obtained from Equation 6.17) and simulated frequency response of phase of the AOSOPS at $V_{tune}$ =-0.308 V and $V_Q$ =0.68 V | 123 |

| Figure 6.9  | Frequency response of gain of the AOSOPS with $V_Q=0.68$ V and different values of $V_{tune}$                                              | 124 |

| Figure 6.10 | Frequency response of phase of the AOSOPS with $V_Q=0.68$ V and different values of $V_{tune}$                                             | 124 |

| Figure 6.11 | Frequency response of input output noise of AOSOPS at $V_{tune} = -0.40 V$ and $V_Q = 0.68 V$                                              | 125 |

| Figure 6.12 | Monte Carlo simulations of AOSOPS for gain at $V_{tune} = -0.40 V$ and $V_Q = 0.68 V$                                                      | 126 |

| Figure 6.13 | Monte Carlo simulations of AOSOPS for phase at $V_{tune} = -0.40$ V and $V_Q = 0.68$ V                                                     | 126 |

| Figure 6.14 | Frequency response of AOSOPS gain with different supply voltages $V_{DD}$ at $V_{tune} = -0.40$ V and $V_Q = 0.68$ V                       | 127 |

| Figure 6.15 | Frequency response of AOSOPS phase with different supply voltages $V_{DD}$ at $V_{tune}$ =-0.40 V and $V_Q$ =0.68 V                        | 127 |

| Figure 6.16 | Frequency response of AOSOPS gain with different temperatures at $V_{tune} = -40$ V and $V_Q = 0.68$ V                                     | 128 |

| Figure 6.17 | Frequency response of AOSOPS phase with different temperatures at $V_{tune} = -0.40$ V and $V_Q = 0.68$ V                                  | 128 |

# LIST OF ABBREVIATIONS

| ABBs      | - | Active Building Blocks                   |

|-----------|---|------------------------------------------|

| AI        | - | Active Inductor                          |

| AOFOPS    | - | Active Only First Order Phase Shifter    |

| AOSOPS    | - | Active Only Second Order Phase Shifter   |

| ASP       | - | Analog Signal Processing                 |

| CG        | - | Common Gate                              |

| CMOS      | - | Complementary Metal Oxide Semiconductor  |

| CNTFET    | - | Carbon Nanotube Field Effect Transisitor |

| CS        | - | Common Source                            |

| DSP       | - | Digital Signal processing                |

| FOPS      | - | First Order Phase Shifter                |

| GAI       | - | Grounded Active Inductor                 |

| GCS       | - | Graphite Cylindrical Sheets              |

| Gyrator-C | - | Gyrator-Capacitance                      |

| IC        | - | Integrated Circuit                       |

| IVB       | - | Inverting Voltage Buffer                 |

| LNA       | - | Low Noise Amplifier                      |

| NF        | - | Noise Figure                             |

| NTE       | - | Negative Transconductance Element        |

| OTA       | - | Operational Transconductance Amplifier   |

| PTE       | - | Positive Transconductance Element        |

| QF        | - | Quality Factor                           |

| SRF       | - | Self Resonance Frequency                 |

| VCO       | - | Voltage Controlled Oscillator            |

| VCR       | - | Voltage Controlled Resistor              |

# LIST OF SYMBOLS

| π        | - | Pi                         |

|----------|---|----------------------------|

| Ω        | - | Ohm                        |

| ω        | - | Pole frequency             |

| σ        | - | Mho                        |

| $C_{gs}$ | - | Gate to source capacitance |

| dB       | - | Decibel                    |

| $D_T$    | - | Diameter of CNT            |

| $g_{ds}$ | - | Output conductance         |

| GHz      | - | Gigahertz                  |

| $g_m$    | - | Transconductance           |

| MHz      | - | Megahertz                  |

| nH       | - | Nanohenry                  |

| nm       | - | Nanometer                  |

| $N_T$    | - | Number of CNTs             |

| $S_T$    | - | CNT pitch                  |

#### **CHAPTER 1**

### **INTRODUCTION**

### 1.1 Background

For future data processing and high speed telecommunication solutions, analog signal processing (ASP) techniques are considered as a promising alternative to digital signal processing (DSP) techniques, as analog devices outperform their digital-counterparts in terms of power dissipation, cost and the maximum achievable bandwidth [1]. Thus, ASP modules are considered as unavoidable and significant component of system on chip. They play vital role in a variety of high-performance applications such as a low noise amplifier (LNA) [2], continuous time filters [3], voltage controlled oscillators (VCOs) [4] and phase shifters [5].

Due to persistent focus on Moore's law transistor scaling and continuous technological advancements, complementary metal oxide semiconductor (CMOS) based ASP modules are prominent in the last four decades. However, reduction of channel length below 32 nm complicates designing for present CMOS technologies due to short channel effects, increased leakage current, decreased gate control and sensitivity to process variations in integrated circuit (IC) manufacturing [6]. Therefore, it is extremely imperative for IC industry to explore new materials as well as devices that equally works well for more-than-Moore technologies and beyond CMOS as coined by International Roadmap for Devices and Systems (IRDS) [7, 8]. The latest report by IRDS for 2021 [8] predicts that CNTFET is a possible replacement for CMOS technology from 2025 onwards.

To find replacements for CMOS technology, many devices and techniques are introduced and evaluated by researchers such as double gate field effect transistor (FET), single electron transistor, fin FET and carbon nanotube FET (CNTFET) [9]. Among these solutions, CNTFETs are considered front runners for further continuation of scaling down the feature length and extension of the saturated Moore's law [8, 10, 11]. Since the operational principle and the device structure of CNTFET is similar to CMOS device, it is possible that CNTFET can use efficiently the existing CMOS design infrastructure and CMOS fabrication process [12].

Since CNTFET introduction as an alternative for CMOS technology, circuit level realization in the digital domain has been demonstrated by many researchers; however, limited works have been done on the design and analysis of CNTFET based ASP modules [13]. This unexplored territory of CNTFET based ASP modules opens a new research area, which needs to be explored for the future demands of ASP applications in nanometer regime. For IC designers, the cost and integration of ASP chip for smaller chip area, low power dissipation and larger bandwidth are emerging issues. The recent push towards 5G/6G communication systems and other similar applications further aggravate these design challenges [14].

Inductors are important components that play a key role in the design of these ASP modules. Majority of ASP modules utilizes on-chip passive spiral inductors. However, spiral inductor faces several disadvantages like larger chip area, low and fixed inductance, low self-resonance frequency (SRF), low quality factor (QF) and incompatibility with low-cost standard semiconductor process [15, 16]. In consequence, the use of active inductors (AIs) instead of passive spiral inductors improve the design of ASP modules by reducing the cost and size of chips [16]. Moreover, the tunability of AI further improves the design of these modules and helps designers to adapt specifications for different ASP applications. However, the design of AI with low power dissipation, large inductive bandwidth, large inductance magnitude and high QF is a challenging task. If these design challenges are solved, the applications of AI will be expanded in the development of several other ASP modules such as VCO, LNA, power dividers and frequency selective filters.

State-of-the-art continuous time signal processing applications utilize one or more types of ASP module, as it is not possible to use a single type of module to cater for the needs of different systems with diversified inputs/outputs. Figure 1.1 demonstrates an example of beamforming scheme where different types of ASP module are utilized for their intended goals [17]. Like AI, phase shifter is another important multipurpose ASP module that functions as a fundamental building block of many analog signal processors [18]. It finds applications in the realization of various high-Q frequency selective circuits, beamforming, radar systems as well as oscillators [19, 20]. Design of area efficient, low voltage, low power phase shifter with tunable pole frequency is another challenging task.

ASP modules are mostly based on different active building blocks (ABBs) that best suit the desired applications. Design of AI and phase shifter for broadband high frequency applications is a very challenging task, especially when dealing with CNTFET based ABBs. For high frequency applications, ABBs are very sensitive to device parasitics and their power dissipation may affect the performance of desired ASP module [21]. Thus realization/selection of an efficient active device that contributes less parasitics and low power dissipation to the ASP module is a crucial requirement.

Figure 1.1 Beamforming scheme [17]

The system design of CNTFET based ASP modules for multipurpose high frequency broadband applications must provide desired functionality with improved performance, reduced active and passive devices, and minimize parasitic effect by choosing suitable and efficient topology.

#### **1.2 Problem Statement**

Designing low voltage, low power CNTFET based ASP modules for broadband high frequency applications is not a straightforward task, as performance of an ASP module is very much dependent on high frequency parasitic effects [21, 22]. The first crucial requirement in the design of such ASP module is to explore different application specific ABBs, which provide low power consumption, lower parasitic design effects, large signal bandwidth and arithmetic operation capability.

In design of ASP modules for high frequency applications, non-ideal port parasitics of used ABBs ultimately increase the design complexity of the modules and also impose serious frequency limitations on the operation and performance [22, 16]. These limitations can be minimized by realization of efficient circuit topology during the design phase of specific ASP module. Moreover, selection of the most appropriate CNTFET design parameters (inter CNT pitch, CNT diameter/chirality vector and number of CNTs) is another critical task of the design phase [6, 10-12].

ABB based AI with high inductance, high SRF, high tunability within an acceptable QF are the most challenging tasks for high frequency broadband applications [23]. Tunability of AI is an important feature that enables designers to adapt specification of different broadband applications. This desirable feature helps in the frequency band selection of filters, VCOs and so many other applications [5, 15, 24-31]. Many recently published high QF AI topologies do not have tunability feature [32-34]. Thus, these AIs are not suitable for broadband applications and can be used only for specific applications with fixed inductance and QF value. High inductance AI with acceptable QF is another important requirement [25]. In RF

circuits such as LNA, high inductance is necessary for high gain as LNA gain is dependent on magnitude of output inductance [23].

Although most AI circuit topologies presented to date are compact and achieve acceptably larger QF than its spiral counterpart, their application in low voltage, low power broadband ASP modules has been limited because of their narrow inductive bandwidth [35-46]. As a result, to the best of our knowledge, no AI circuit topology has been utilized for a high frequency (> 11 GHz) and wideband (> 7 GHz bandwidth) ASP module [47]. This comparatively narrow inductive bandwidth ultimately excludes AI for the design of broadband high frequency ASP modules.

For flexibility, the pole frequency of a phase shifter should be widely tunable. Tunability of pole frequency enables a phase shifter to be used in broadband applications [48, 49]. Low power dissipation of a phase shifter can be obtained by minimizing number of active and passive devices [50]. Moreover, the ABB power dissipation will be added to the total phase shifter power consumption, so use of ABB with less power dissipation is needed.

Based on AI and phase shifter examples, in summary, the design challenges involve low power dissipation, high tunability, minimization of parasitic components (which degrade high frequency performance) and selection of appropriate CNTFET design parameters (inter CNT pitch, CNT diameter/chirality vector and number of CNTs). In addition, high SRF and highly tunable AI with acceptable QF are other research challenges.

### **1.3** Research Objectives

The objectives of this research work are:

- To design CNTFET based ABBs suitable for the realization of low power and high frequency ASP modules. These ABBs are inverting voltage buffer (IVB), negative transconductance element (NTE) and positive transconductance element (PTE). The ASP modules to be realized using designed ABBs are AI, first order phase shifter (FOPS) and second order phase shifter (SOPS). The CNTFET ABBs are targeted to operate up to 100 GHz and with less then 1 mW power dissipation.

- ii. To design CNTFET based AI circuit topology for high frequency broadband applications. The AI circuit will be realized using the designed ABBs to achieve high QF, high tunable inductance, high SRF and low power dissipation. The target performance is for the AI circuit to be inductive up to 100 GHz with a power dissipation less than 1 mW.

- iii. To design CNTFET based FOPS and SOPS topologies for high frequency applications. The phase shifter circuits will be realized using the designed ABBs to achieve large tunable pole frequency with less than 1 mW power dissipation.

### **1.4 Scope and Limitations**

The major scope and limitations of this research work are as follows:

- This study is mainly concerned with the design of ASP modules for high frequency broadband applications using CNTFET ABBs. These modules only include CNTFET based AI and phase shifters.

- HSPICE simulation tool will be used for design and analysis of ABB and the ASP modules. This work will be purely based on simulation at transistor level due to the unavailability of CNTFET circuit fabrication facility.

iii. Stanford CNTFET model at 16 nm technology node will be utilized for design of AI and phase shifter circuits.

### **1.5** Research Contributions

Contributions of this thesis are listed as follows:

- i. The first contribution of this work is the proposal for a new compact CNTFET based ABB known as PTE. Circuit analysis shows that the proposed ABB is a suitable candidate for low voltage, low power broadband applications, with voltage supply as low as 0.7 V and power dissipation in the uW range.

- ii. The second contribution of this research work is proposal for CNTFET based grounded AI (GAI) circuit. The GAI was designed and simulated using 16 nm CNTFET technology node using HSPICE. Simulation results demonstrate that realized GAI circuit offers high tunable inductance from 4.4 nH to 287.4 nH with a maximum SRF of 101 GHz. It offers low power dissipation of 0.337 mW. Tunability of the GAI has been achieved by utilizing CNTFET varactor. A broadband LNA circuit was also designed and simulated by utilizing the proposed GAI topology. The simulation result shows very high frequency bandwidth of 17.5 GHz to 57 GHz and dissipates 6.961 mW from 0.7 V supply. Moreover, the GAI based LNA provides a 15.9 dB maximum gain. In addition, better than -10 dB input matching and less than 3 dB noise figure (NF) over the entire bandwidth is observed.

- iii. The third contribution of this research is the proposal for a compact wideband FOPS using CNTFET based Inverting Voltage Buffer (IVB) and Voltage Controlled Resistor (VCR). Simulation results demonstrate a tunable pole frequency range between 1.913 GHz and 40.2 GHz with input and output voltage noises of 4.402  $nV/\sqrt{Hz}$  and 4.414  $nV/\sqrt{Hz}$  respectively, and power dissipation of 0.4862 mW.

- iv. The fourth contribution of this research is the design of an active only first order phase shifter (AOFOPS) using IVB and CNTFET varactor. The active only circuit topology offers a wide tunable range of pole frequency between 34.2 GHz to 56.4 GHz. Simulation results show that the equivalent input noise and output noise for the realized all active phase shifter at a designed pole frequency of 49.26 GHz are  $6.822 \ nV/\sqrt{Hz}$  and  $6.761 \ nV/\sqrt{Hz}$ respectively, while it dissipates 0.0338 mW.

- v. The fifth contribution of this research is the design of an active only second order phase shifter (AOSOPS) by utilizing two negative transconductance elements (NTE), one PTE, two varactors and one VCR. The AOSOPS topology provides a tunable pole frequency between 16.2 GHz to 42.5 GHz with input and output noise of 21.698  $nV/\sqrt{Hz}$  and 21.593  $nV/\sqrt{Hz}$  respectively. The power dissipation of AOSOPS is 0.2256 mW.

#### 1.6 Thesis Organization

This dissertation is organized into seven chapters. Chapter 1 discusses the background, problem statement, objectives and scope of this research work. Moreover, this chapter also highlights the contributions of this research work.

Chapter 2 of this dissertation provides a summary of advanced AI and phase shifter circuit topologies available in the open literature. The performance of these available ASP modules is discussed and investigated thoroughly.

Chapter 3 of this thesis discusses the methodology adopted in this research work. Moreover, the flow of the complete design process steps is discussed thoroughly for the realization of CNTFET ABBs and ASP modules. Chapter 4 introduces the proposed GAI circuit. The GAI equivalent parasitic model will be explained in this chapter. Also, equations for inductance and QF will be analyzed. Simulation results of the GAI topology will also be explained thoroughly. Moreover, the application of the proposed GAI in the design of broadband LNA will be demonstrated.

Chapter 5 introduces the proposed FOPS topologies. The realized circuit description, analysis and simulation results will be explained in this chapter. Moreover, a brief comparison of the proposed circuits with other available FOPS topologies in the open literature will be discussed.

Chapter 6 introduces the AOSOPS circuit. The proposed AOSOPS circuit design and simulation results are discussed in this chapter. In addition, a comparison study with other SOPS circuits is conducted and discussed. Lastly, the conclusion and recommendations for further research is presented in Chapter 7.

#### REFERENCES

- [1] de França Ferreira, João Alberto, Emilie Avignon-Meseldzija, Pietro Maris Ferreira, Julien Sarrazin, and Philippe Bénabès. (2020). "Design of integrated all-pass filters with linear group delay for analog signal processing applications." *International Journal of Circuit Theory and Applications*, 48(5), 658-673.

- [2] Yaghouti, Behnam Dorostkar, and Javad Yavandhasani. (2021). "A high linearity low power low-noise amplifier designed for ultra-wide-band receivers." *Analog Integrated Circuits and Signal Processing*, 107, 109-120.

- [3] Yesil, Abdullah, Erkan Yuce, and Shahram Minaei. (2020), "MOSFET-Cbased grounded active inductors with electronically tunable properties." *International Journal of RF and Microwave Computer-Aided Engineering*, 30(8), 1-13, e22274.

- [4] Kumar, Nitin, and Manoj Kumar. (2021). "Low Power CMOS Differential Ring VCO Designs using Dual Delay Stages in 0.13 μm Technology for Wireless Applications." *Microelectronics Journal*, 111, 1-12, 105025.

- [5] Aghazadeh, Seyed Rasoul, Herminio Martínez García, Alireza Saberkari, and Eduardo José Alarcón Cot. (2018). "Tunable wide-band second-order allpass filter-based time delay cell using active inductor." 32<sup>nd</sup> Conference on Design of Circuits and Integrated Systems, (DCIS). IEEE. 1-5.

- [6] Loan, Sajad A., M. Nizamuddin, Abdul R. Alamoud, and Shuja A. Abbasi. (2015). "Design and comparative analysis of high performance carbon nanotube-based operational transconductance amplifiers." Nano 10(03), 1-11, 1550039.

- [7] Obite, Felix, Geoffrey Ijeomah, and Joseph Stephen Bassi. (2019) "Carbon nanotube field effect transistors: toward future nanoscale electronics." *International Journal of Computers and Applications*, 41(2), 149-164.

- [8] IRDS 2021 edition, Available at: https://irds.ieee.org/editions/2021/beyondcmos.

- [9] Cen, Mingcan, Shuxiang Song, and Chaobo Cai. (2017). "A high performance CNFET-based operational transconductance amplifier and its applications." *Analog Integrated Circuits and Signal Processing*, 91(3), 463-472.

- [10] Imran, Ale, Mohd Hasan, Aminul Islam, and Shuja Ahmad Abbasi. (2012)."Optimized design of a 32-nm CNFET-based low-power ultrawideband CCII." *IEEE transactions on Nanotechnology*, 11(6), 1100-1109.

- [11] Jogad, Seema, Sajad A. Loan, Neelofer Afzal, and Abdullah G. Alharbi. (2021). "CNTFET based class AB current conveyor II: Design, analysis and waveform generator applications." *International Journal of Numerical Modelling: Electronic Networks, Devices and Fields*, 34(1), 1-15, e2783.

- [12] Nizamuddin, M., Sajad A. Loan, Abdul R. Alamoud, and Shuja A. Abbassi.

(2015). "Design, simulation and comparative analysis of CNT based cascode operational transconductance amplifiers." *Nanotechnology*, 26(39), 1-13, 395201.

- [13] Prakash, P., K. Mohana Sundaram, and M. Anto Bennet. (2018). "A review on carbon nanotube field effect transistors (CNTFETs) for ultra-low power applications." *Renewable and Sustainable Energy Reviews*, 89, 194-203.

- [14] Tsai, Ching-Han, Chun-Yi Lin, Ching-Piao Liang, Shyh-Jong Chung, and Jenn-Hwan Tarng. (2021). "Switched Low-Noise Amplifier Using Gyrator-Based Matching Network for TD-LTE/LTE-U/Mid-Band 5G and WLAN Applications." *Applied Sciences*, 11(4), 1-13, 1477.

- [15] Saad, Sehmi, Aymen Ben Hammadi, and Fayrouz Haddad. (2021). "An Ultra-Compact Multi-Band VCO Achieving- 196 dB FoM A with Single-Ended Tunable Active Inductor." *BioNanoScience*, 11(2), 390-400.

- [16] Jaikla, Winai, Sirigul Bunrueangsak, Fabian Khateb, Tomasz Kulej, Peerawut Suwanjan, and Piya Supavarasuwat. (2021). "Inductance Simulators and Their Application to the 4<sup>th</sup> Order Elliptic Lowpass Ladder Filter Using CMOS VD-DIBAs." *Electronics*, 10(6), 1-30, 684.

- [17] Wijenayake, Chamith, Arjuna Madanayake, Leonid Belostotski, Yongsheng Xu, and Len Bruton. (2014)."All-pass filter-based 2-D IIR filter-enhanced beamformers for AESA receivers." *IEEE Transactions on Circuits and Systems*, 61(5), 1331-1342.

- [18] Osuch, Piotr Jan, and Tinus Stander. (2018). "High-Q second-order all-pass delay network in CMOS." IET Circuits, Devices & Systems, 13(2), 153-162.

- [19] Yuce, Erkan, Leila Safari, Shahram Minaei, Giuseppe Ferri, and Vincenzo Stornelli. (2020). "New mixed-mode second-generation voltage conveyor based first-order all-pass filter." *IET Circuits, Devices & Systems*, 14(6), 901-907.

- [20] Elamien, Mohamed B., Brent J. Maundy, Leonid Belostotski, and Ahmed S. Elwakil. (2020). "Synthesis of Wideband High-Quality Factor Delay-Tunable Fully Differential All-Pass Filters." *IEEE Transactions on Microwave Theory* and Techniques, 68(10), 4348-4360.

- [21] Yuce, Erkan, Leila Safari, Shahram Minaei, Giuseppe Ferri, Gianluca Barile, and Vincenzo Stornelli. (2021). "A New Simulated Inductor with Reduced Series Resistor Using a Single VCII±." *Electronics*, 10(14), 1-15, 1693.

- [22] Mehra, Rishab, Vikash Kumar, and Aminul Islam. (2018). "Reliable and Q-Enhanced Floating Active Inductors and Their Application in RF Bandpass Filters." *IEEE Access*, 6, 48181-48194.

- [23] Kia, Hojjat Babaei, and Abu Khari A'ain. (2013). "A single-to-differential LNA using differential active inductor for GPS applications." *Frequenz*, 67(1-2), 27-34.

- [24] Momen, Hadi Ghasemzadeh, Metin Yazgi, and Ramazan Kopru. (2015).

"Designing a new high Q fully CMOS tunable floating active inductor based on modified tunable grounded active inductor." 9<sup>th</sup> international conference on electrical and electronics engineering (ELECO). IEEE. 1-15.

- [25] Momen, Hadi Ghasemzadeh, Metin Yazgi, Ramazan Kopru, and Ali Naderi Saatlo. (2016). "Design of a new low loss fully CMOS tunable floating active inductor." *Analog Integrated Circuits and Signal Processing*, 89(3), 727-737.

- [26] Agrawal, Deepak, and Sudhanshu Maheshwari. (2020). "Electronically tunable grounded immittance simulators using an EX-CCCII." *International Journal of Electronics*, 107(10), 1625-1648.

- [27] Abaci, Ahmet, and Erkan Yuce. (2019). "Single DDCC based new immittance function simulators employing only grounded passive elements and their applications." *Microelectronics journal*, 83, 94-103.

- [28] Tangsrirat, Worapong. (2017). "Synthetic grounded lossy inductance simulators using single VDIBA." *IETE Journal of research*, 63(1), 134-141.

- [29] Kumar, Navnit, John Vista, and Ashish Ranjan. (2019), "A tuneable active inductor employing DXCCTA: grounded and floating operation." *Microelectronics Journal*, 90, 1-11.

- [30] Tarunkumar, Huirem, Yumnam Shantikumar Singh, and Ashish Ranjan. (2020). "An active inductor employing a new four terminal floating nullor transconductance amplifier (FTFNTA)." *International Journal of Electronics*, 107(5), 683-702.

- [31] Mamatov, İslombek, Yasin Özçelep, and Fırat Kaçar. (2022). "CNTFET based inductance simulator circuits employing single CFOA and its filter applications." *Analog Integrated Circuits and Signal Processing*, 1-8.

- [32] Dogan, Mehmet, and Erkan Yuce. (2019), "CFOA based a new grounded inductor simulator and its applications." *Microelectronics Journal*, 90, 297-305.

- [33] Yesil, Abdullah, Erkan Yuce, and Shahram Minaei. (2018). "Inverting voltage buffer based lossless grounded inductor simulators." AEU-International Journal of Electronics and Communications, 83, 131-137.

- [34] Jogad, Seema, Hend I. Alkhammash, Neelofer Afzal, and Sajad A. Loan.

(2021). "CNTFET-based active grounded inductor using positive and negative current conveyors and applications." *International Journal of Numerical Modelling: Electronic Networks, Devices and Fields*, 34(5), e2895.

- [35] Saberkari, Alireza, Saman Ziabakhsh, Herminio Martinez, and Eduard Alarcón. (2016). "Active inductor-based tunable impedance matching network for RF power amplifier application." *Integration*, 52, 301-308.

- [36] Manjula, J., and S. Malarvizhi.(2018). "Active inductor based tunable multiband RF front end design for UWB applications." *Analog Integrated Circuits and Signal Processing*, 95(2), 195-207.

- [37] Mhiri, Mongia, Aymen Ben Hammadi, Fayrouz Haddad, Sehmi Saad, and Kamel Besbes. (2018), "Power and Noise Optimization Techniques of RF Active Inductor Using Multi-Finger Gate Transistors." *BioNanoScience*, 8(1), 264-271.

- [38] Hammadi, Aymen Ben, Mongia Mhiri, Fayrouz Haddad, Sehmi Saad, and Kamel Besbes. (2017). "An enhanced design of multi-band RF band pass filter based on tunable high-Q active inductor for nano-satellite applications." *Journal of Circuits, Systems and Computers*, 26(4), 1-20, 1750055.

- [39] Bhattacharya, Ritabrata, Ananjan Basu, and Shiban K. Koul. (2015), "A highly linear CMOS active inductor and its application in filters and power dividers." *IEEE Microwave and Wireless Components Letters*, 25(11), 715-717.

- [40] Kia, Hojjat Babaei, and Abu Khari A'ain. (2014). "A wide tuning range voltage controlled oscillator with a high tunable active inductor." *Wireless personal communications*, 79(1), 31-41.

- [41] Saad, Sehmi, Mongia Mhiri, Aymen Ben Hammadi, and Kamel Besbes. (2016) "A new low-power, high-Q, wide tunable CMOS active inductor for RF applications." *IETE journal of research*, 62(2), 265-273.

- [42] Momen, Hadi Ghasemzadeh, Metin Yazgi, and Ramazan Kopru. (2015). "A low loss, low voltage and high Q active inductor with multi-regulated cascade stage for RF applications." 2015 IEEE International Conference on Electronics, Circuits, and Systems (ICECS). IEEE. 149-152.

- [43] Uyanik, H. Ugur, and Nil Tarim. (2007). "Compact low voltage high-Q CMOS active inductor suitable for RF applications." *Analog integrated circuits and signal processing*, 51(3), 191-194.

- [44] Vema Krishnamurthy, Santosh, Kamal El-Sankary, and Ezz El-Masry.(2010),

"Noise-cancelling CMOS active inductor and its application in RF band-pass filter design." *International Journal of Microwave Science and Technology*, 2010, 1-8.

- [45] Nair, M. U., Y. J. Zheng, and Y. Lian. (2008). "1 V, 0.18 μm-area and power efficient UWB LNA utilising active inductors." *Electronics Letters*, 44(19), 1127-1129.

- [46] Momen, Hadi Ghasemzadeh, Metin Yazgi, R. Kopru, and Ali Naderi Saatlo. (2017). "Low-loss active inductor with independently adjustable selfresonance frequency and quality factor parameters." *Integration*, 58, 22-26.

- [47] Saberkari, Alireza, Sh Kazemi, Vahideh Shirmohammadli, and Mustapha CE Yagoub. (2016). "gm-boosted flat gain UWB low noise amplifier with active inductor-based input matching network." *Integration 52*, 323-333.

- [48] Aghazadeh, Seyed Rasoul, Herminio Martinez, Alireza Saberkari, and Eduard Alarcon. (2019). "Tunable active inductor-based second-order allpass filter as a time delay cell for multi-GHz operation." *Circuits, Systems, and Signal Processing*, 38(8), 3644-3660.

- [49] Chen, Yang, and Wenyuan Li. (2017). "An ultra-wideband pico-second truetime-delay circuit with differential tunable active inductor." Analog Integrated Circuits and Signal Processing, 91(1), 9-19.

- [50] Kumar, Pradeep, Ali Umit Keskin, and Kirat Pal. (2007). "Wide-band resistorless all-pass sections with single element tuning." *International Journal of Electronics*, 94(6), 597-604.

- [51] Faruqe, Omar, Aniqa Ibnat Lim, and Md Tawfiq Amin. (2020). "Tunable active inductor based VCO and BPF in a single integrated design for wireless applications in 90 nm CMOS process." *Engineering Reports*, 2(8), 1-21, e12220.

- [52] Faruqe, Omar, and Md Tawfiq Amin. (2020). "Design and Performance Analysis of Active Inductor Based VCO for IEEE 802.11 a/b/g/n/ac Applications." *International Journal of Electronics*, 107(3), 494-511.

- [53] Roobert, A. Andrew, and D. Gracia Nirmala Rani. (2021). "Design and analysis of a sleep and wake-up CMOS low noise amplifier for 5G applications." *Telecommunication Systems*, 76(3), 461-470.

- [54] Zhang, Jingzhi, Yixuan Cheng, Chenxi Zhao, Yunqiu Wu, and Kai Kang. (2018). "Analysis and design of ultra-wideband mm-wave injection-locked frequency dividers using transformer-based high-order resonators." *IEEE Journal of Solid-State Circuits*, 53(8), 2177-2189.

- [55] Kazan, Oguz, Onur Memioglu, Fatih Kocer, Adnan Gundel, and Canan Toker. (2019). "A Lumped-Element Wideband 3-dB Quadrature Hybrid." *IEEE Microwave and Wireless Components Letters*, 29(6), 385-387.

- [56] Momen, Hadi Ghasemzadeh, Metin Yazgi, R. Kopru, and A. Naderi Saatlo. (2017). "An accurate CMOS interface small capacitance variation sensing circuit for capacitive sensor applications." *Circuits, Systems, and Signal Processing*, 36(12), 4908-4918.

- [57] Faruqe, Omar, and Md Tawfiq Amin. (2019). "Wide Tuning Range Varactorless Tunable Active Inductor-Based Voltage Controlled Oscillator for Wireless Applications." *Journal of Circuits, Systems and Computers*, 28(14), 1-15, 1950242.

- [58] Elamien, Mohamed B., Brent J. Maundy, Leonid Belostotski, and Ahmed S. Elwakil. (2020). "Wideband third-order single-transistor all-pass filter." *International Journal of Circuit Theory and Applications*, 48(7), 1201-1208.

- [59] Nandi, Rabindranath, Koushick Mathur, and Sandhya Pattanayak. (2016).

"Single-CFA first-order allpass filter." *IEICE Electronics Express*, 13(4), 1-8, 20151039.

- [60] Maheshwari, Sudhanshu. (2018). "Some analog filters of reduced complexity with shelving and multifunctional characteristics." *Journal of Circuits, Systems and Computers*, 27(10), 1-19, 1850150.

- [61] Herencsar, Norbert, Jaroslav Koton, Jan Jerabek, Kamil Vrba, and Oguzhan Cicekoglu. (2011). "Voltage-mode all-pass filters using universal voltage conveyor and MOSFET-based electronic resistors." *Radioengineering*, 20(1), 10-18.

- [62] Channumsin, Orapin, and Worapong Tangsrirat. (2017). "Single VDBAbased phase shifter with low output impedance." 14<sup>th</sup> International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology (ECTI-CON). IEEE. 427-430.

- [63] Metin, Bilgin, Kirat Pal, and Oguzhan Cicekoglu. (2011). "All-pass filters using DDCC-and MOSFET-based electronic resistor." *International Journal* of Circuit Theory and Applications, 39(8), 881-891.

- [64] Yuce, Erkan, Rakesh Verma, Neeta Pandey, and Shahram Minaei. (2019).

"New CFOA-based first-order all-pass filters and their applications." *AEU-International Journal of Electronics and Communications*, 103, 57-63.

- [65] Chhabra, Jitender, Jitendra Mohan, and Bhartendu Chaturvedi. (2020). "All-Pass Frequency Selective Structures: Application for Analog Domain." *Journal of Circuits, Systems and Computers*, 30(8), 1-23, 2150152.

- [66] Kumar, Ashok, and Sajal K. Paul. (2016). "Cascadable voltage-mode all-pass filter with single DXCCII and grounded capacitor." *International Conference*

*on Microelectronics, Computing and Communications (MicroCom). IEEE.* 1-4.

- [67] Metin, Bilgin, and Kirat Pal. (2010). "New all-pass filter circuit compensating for C-CDBA non-idealities." Journal of Circuits, Systems, and *Computers*, 19(02), 381-391.

- [68] Kumngern, Montree, Jirasak Chanwutitum, and Kobchai Dejhan. (2008)

"Electronically tunable voltage-mode all-pass filter using simple CMOS OTAs." 2008 International Symposium on Communications and Information Technologies. IEEE. 1-5.

- [69] Jaikla, Winai, Pruedchawat Talabthong, Surapong Siripongdee, Piya Supavarasuwat, Peerawut Suwanjan, and Amornchai Chaichana. (2019).

"Electronically controlled voltage mode first order multifunction filter using low-voltage low-power bulk-driven OTAs." *Microelectronics Journal*, 91, 22-35.

- [70] Yuce, Erkan, and Shahram Minaei. (2010). "A novel phase shifter using two NMOS transistors and passive elements." Analog Integrated Circuits and *Signal Processing*, 62(1), 77-81.

- [71] Metin, Bilgin, Norbert Herencsar, and Oguzhan Cicekoglu. (2013). "A low-voltage electronically tunable MOSFET-C voltage-mode first-order all-pass filter design." *Radioengineering*, 22(4), 985-994.

- [72] Minaei, Shahram, and Erkan Yuce. (2012). "High input impedance NMOSbased phase shifter with minimum number of passive elements." *Circuits, Systems, and Signal Processing*, 31(1), 51-60.

- [73] YÜCEL, FIRAT, and Erkan Yuce. (2016). "A new electronically tunable first-order all-pass filter using only three NMOS transistors and a capacitor." *Turkish Journal of Electrical Engineering & Computer Sciences*, 24(4), 3286-3292.

- [74] Maundy, Brent J., and Peter Aronhime. (2002), "A novel CMOS first-order all-pass filter." *International journal of electronics*, 89(9), 739-743.

- [75] Yuce, Erkan. (2010). "A novel CMOS-based voltage-mode first-order phase shifter employing a grounded capacitor." *Circuits, Systems and Signal Processing*, 29(2), 235-245.

- [76] Metin, Bilgin, and Oguzhan Cicekoglu. (2008). "Tunable all-pass filter with a single inverting voltage buffer." 2008 Ph. D. Research in Microelectronics and Electronics. IEEE. 261-263.

- [77] Toker, Ali, and S. Özoğuz. (2003). "Tunable allpass filter for low voltage operation." *Electronics Letters*, 39(2), 175-176.

- [78] Herencsar, Norbert, Shahram Minaei, Jaroslav Koton, Erkan Yuce, and Kamil Vrba. (2013), "New resistorless and electronically tunable realization of dual-output VM all-pass filter using VDIBA." *Analog Integrated Circuits and Signal Processing*, 74(1), 141-154.

- [79] Garakoui, Seyed Kasra, Eric AM Klumperink, Bram Nauta, and Frank E. van Vliet. (2015). "Compact cascadable gm-C all-pass true time delay cell with reduced delay variation over frequency." *IEEE Journal of Solid-State Circuits*, 50(3), 693-703.

- [80] Aghazadeh, Seyed Rasoul, Herminio Martinez, and Alireza Saberkari.

(2019). "5GHz CMOS all-pass filter-based true time delay cell." *Electronics*, 8(1), 1-10, 16.

- [81] Yildiz, Hacer A., Serdar Ozoguz, Ali Toker, and Oguzhan Cicekoglu. (2013).

"On the realization of MOS-only allpass filters." *Circuits, Systems, and Signal Processing*, 32(3), 1455-1465.

- [82] Yıldız, Hacer A., Ali Toker, Ahmed S. Elwakil, and Serdar Ozoguz. (2014).

"MOS-only allpass filters with extended operating frequency range." *Analog Integrated Circuits and Signal Processing*, 81(1), 17-22.

- [83] Metin, Bilgin, Emre Arslan, Norbert Herencsar, and Oguzhan Cicekoglu.

(2011). "Voltage-mode MOS-only all-pass filter." 34<sup>th</sup> International Conference on Telecommunications and Signal Processing (TSP). IEEE. 317-318.

- [84] Yıldız, Hacer Atar, Ali Toker, Selçuk Kılınç, and Serdar Ozoguz. (2016).

"Low frequency active only filters with small chip area." *Analog Integrated Circuits and Signal Processing*, 89(3), 739-747.

- [85] Elamien, Mohamed B., Brent J. Maundy, Leonid Belostotski, and Ahmed S.

Elwakil. (2019). "Single-transistor second-order allpass filters." 62<sup>nd</sup> International Midwest Symposium on Circuits and Systems (MWSCAS). IEEE. 369-372.

- [86] Maundy, Brent J., Ahmed S. Elwakil, Leonid Belostotski, and Norbert Herencsar. (2019). "Single transistor RC-only second-order allpass filters." *International Journal of Circuit Theory and Applications*, 48(2), 162-169.

- [87] Faseehuddin, Mohammad, Jahariah Sampe, Sadia Shireen, and Sawal Hamid Md Ali. (2020). "Minimum component all pass filters using a new versatile active element." *Journal of Circuits, Systems and Computers*, 29(5), 1-31, 2050078.

- [88] Choudhary, Veena, and Anju Gupta. (2011). "Polymer/carbon nanotube nanocomposites." *Carbon nanotubes-polymer nanocomposites*, 10.5772/18423, 65-90.

- [89] Zanjani, S. Mohammad Ali, Massoud Dousti, and Mehdi Dolatshahi. (2019).

"A new low-power, universal, multi-mode Gm-C filter in CNTFET technology." *Microelectronics Journal*, 90, 342-352.

- [90] Mamatov, Islombek, Yasin Özçelep, and Fırat Kaçar. (2022). "CNTFET based voltage differencing current conveyor low power and universal filter." *Analog Integrated Circuits and Signal Processing*, 110(1), 127-137.

- [91] Sayed, Shimaa Ibrahim, Mostafa Mamdouh Abutaleb, and Zaki Bassuoni Nossair. (2016). "Optimization of CNFET parameters for high performance digital circuits." *Advances in Materials Science and Engineering*, 1-10, 6303725.

- [92] Sun, Yanan, and Volkan Kursun. (2011). "N-type carbon-nanotube MOSFET device profile optimization for very large scale integration." *Transactions on Electrical and Electronic Materials*, 12(2), 43-50.

- [93] Saberkari, Alireza, Omid Khorgami, Javad Bagheri, Morgan Madec, Seyed Mohsen Hosseini-Golgoo, and Eduard Alarcón-Cot. (2018). "Design of Broadband CNFET LNA Based on Extracted I–V Closed-Form Equation." *IEEE Transactions on Nanotechnology*, 17(4), 731-742.

- [94] Patil, Nishant, Albert Lin, Edward R. Myers, Koungmin Ryu, Alexander Badmaev, Chongwu Zhou, H-S. Philip Wong, and Subhasish Mitra. (2009).

"Wafer-scale growth and transfer of aligned single-walled carbon nanotubes." *IEEE Transactions on Nanotechnology*, 8(4), 498-504.

- [95] Jin, Sung Hun, Simon N. Dunham, Jizhou Song, Xu Xie, Ji-Hun Kim, Chaofeng Lu, Ahmad Islam et al. (2013). "Using nanoscale thermocapillary

flows to create arrays of purely semiconducting single-walled carbon nanotubes." *Nature nanotechnology*, 8(5), 347-355.

- [96] Patil, Nishant, Jie Deng, Subhasish Mitra, and H-S. Philip Wong. (2008).

"Circuit-level performance benchmarking and scalability analysis of carbon nanotube transistor circuits." *IEEE Transactions on Nanotechnology*, 8(1), 37-45.

- [97] Franklin, Aaron D., Mathieu Luisier, Shu-Jen Han, George Tulevski, Chris M. Breslin, Lynne Gignac, Mark S. Lundstrom, and Wilfried Haensch. (2012). "Sub-10 nm carbon nanotube transistor." *Nano letters*, 12(2), 758-762.

- [98] Taghavi, A., C. Carta, F. Ellinger, M. Haferlach, M. Claus, and M. Schroter.

(2015). "A CNTFET amplifier with 5.6 dB gain operating at 460–590 MHz." *International Microwave and Optoelectronics Conference (IMOC), IEEE.* 1-4.

- [99] Khorram, Hamidreza Ghanbari, and Alireza Kokabi. (2020). "Proposed 3.5 μW CNTFET-MOSFET hybrid CSVCO for power-efficient gigahertz applications." *Circuit World*, 46(3), 193-202.

- [100] Jooq, Mohammad Khaleqi Qaleh, Ali Mir, Sattar Mirzakuchaki, and Ali Farmani. (2020). "Design and performance analysis of wrap-gate CNTFETbased ring oscillators for IoT applications." *Integration*, 70, 116-125.

- [101] Steiner, Mathias, Michael Engel, Yu-Ming Lin, Yanqing Wu, Keith Jenkins, Damon B. Farmer, Jefford J. Humes et al. (2012). "High-frequency performance of scaled carbon nanotube array field-effect transistors." *Applied Physics Letters*, 101(5), 1-4, 053123.

- [102] Taghavi, A., C. Carta, T. Meister, F. Ellinger, M. Claus, and M. Schroter. (2017). "A CNTFET oscillator at 461 MHz." *IEEE Microwave and Wireless Components Letters*, 27(6), 578-580.

- [103] Brady, Gerald J., Yongho Joo, Meng-Yin Wu, Matthew J. Shea, Padma Gopalan, and Michael S. Arnold. (2014). "Polyfluorene-sorted, carbon nanotube array field-effect transistors with increased current density and high on/off ratio." ACS nano, 8(11), 11614-11621.

- [104] Zou, Jianping, and Qing Zhang. (2021). "Advances and Frontiers in Single-Walled Carbon Nanotube Electronics." *Advanced Science*, 8(23), 1-19, 2102860.

- [105] Deng, Jie, and H-S. Philip Wong. (2007). "A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application—Part II: Full device model and circuit performance benchmarking." *IEEE Transactions on Electron Devices*, 54(12), 3195-3205.

- [106] Zheng, You, and Carlos E. Saavedra. (2008). "Feedforward-regulated cascode OTA for gigahertz applications." *IEEE Transactions on Circuits and System*, 55(11), 3373-3382.

- [107] Yuce, Erkan, Shahram Minaei, Norbert Herencsar, and Jaroslav Koton.

(2013). "Realization of first-order current-mode filters with low number of MOS transistors." *Journal of Circuits, Systems and Computers*, 22(01), 1-14, 1250071.

- [108] Avignon-Meseldzija, Emilie, Thomas Lepetit, Pietro Maris Ferreira, and Fabrice Boust. (2017). "Negative inductance circuits for metamaterial bandwidth enhancement." *EPJ Applied Metamaterials*, 4(11), 1-13.

- [109] Zhuo, Wei, Xiaoyong Li, Sudip Shekhar, Sherif HK Embabi, José Pineda de Gyvez, David J. Allstot, and Edgar Sanchez-Sinencio. (2005). "A capacitor cross-coupled common-gate low-noise amplifier." *IEEE Transactions on Circuits and Systems II: Express Briefs*, 52(12), 875-879.

- [110] Liscidini, Antonio, Brandolini Massimo, Sanzogni Davide, Castello Rinaldo. (2006). "A 0.13 um CMOS front-end, for DCS1800/UMTS/802.11 bg with multiband positive feedback low-noise amplifier." *IEEE Journal of Solid-State Circuits*, 41(4), 981-989.

- [111] Rossi, Paolo, Antonio Liscidini, Massimo Brandolini, and Francesco Svelto.

(2005). "A variable gain RF front-end, based on a voltage-voltage feedback LNA, for multistandard applications." *IEEE journal of Solid-State circuits*, 40(3), 690-697.

- [112] Woo, Sanghyun, Woonyun Kim, Chang-Ho Lee, Kyutae Lim, and Joy Laskar (2009). "A 3.6 mW differential common-gate CMOS LNA with positivenegative feedback." 2009 IEEE International Solid-State Circuits Conference-Digest of Technical Papers. IEEE. 218-219.

- [113] Kim, Jusung, Sebastian Hoyos, and Jose Silva-Martinez. (2010). "Wideband common-gate CMOS LNA employing dual negative feedback with simultaneous noise, gain, and bandwidth optimization." *IEEE Transactions* on microwave theory and techniques, 58(8), 2340-2351.

#### LIST OF PUBLICATIONS

- [1] Muhammad I. Masud, Abu Khari Bin A'ain, Iqbal A. Khan, and Nasir Shaikh-Husin. (2019). "A CNTFET-C first order all pass filter." Analog Integrated Circuits and Signal Processing, 100(2), 257-268. (ISI Index, IF 1.337).

- [2] Muhammad I. Masud, Abu Khari Bin A'ain, Iqbal A. Khan, and Nasir Shaikh-Husin. (2019). "Design of Voltage Mode Electronically Tunable First Order All Pass Filter in ±0.7 V 16 nm CNFET Technology." *Electronics*, 8(1), 95. (ISI Index, IF 2.397).

- [3] Muhammad I. Masud, Abu Khari Bin A'ain, Iqbal A. Khan, and Nasir Shaikh-Husin. (2021). "CNTFET based Voltage Mode MISO Active only Biquadratic Filter for Multi-GHz Frequency Applications." *Circuits, Systems,* and Signal Processing, 40, 1-20. (ISI Index, IF 2.225).

- [4] M. I. Masud, Nasir Shaikh-Husin, I. A. Khan, and A. K. Bin A'ain. (2022).

"CNTFET based grounded active inductor for broadband applications." Computers, Materials & Continua, 73(1), 2135-2149. (ISI Index, IF 3.772).

- [5] Masud, M. I., Abu Khari Bin A'ain, and Iqbal A. Khan. (2017). "Reconfigurable CNTFET based fully differential first order multifunctional filter." 2017 International Conference on Multimedia, Signal Processing and Communication Technologies (IMPACT). IEEE. 55-59.

- [6] Masud, M. I., Abu Khari Bin A'ain, and Iqbal A. Khan. (2017). "CNFET based reconfigurable first order filter." 2017 9th IEEE-GCC Conference and Exhibition (GCCCE). IEEE. 1-9.