## Input-Layer Neuron Design for Spiking Neural Network Application

Seyed Amirhossein Nasrollahi

A Thesis

in

The Department

of

**Electrical and Computer Engineering**

Presented in Partial Fulfillment of the Requirements

for the Degree of

Master of Applied Science (Electrical Engineering) at

**Concordia University**

Montréal, Québec, Canada

January 2023

© Seyed Amirhossein Nasrollahi, 2023

#### CONCORDIA UNIVERSITY

#### School of Graduate Studies

This is to certify that the thesis prepared

By: Seyed Amirhossein Nasrollahi

Entitled: Input-Layer Neuron Design for Spiking Neural Network Application

and submitted in partial fulfillment of the requirements for the degree of

#### Master of Applied Science (Electrical Engineering)

complies with the regulations of this University and meets the accepted standards with respect to originality and quality.

Signed by the Final Examining Committee:

|                                                  | Chair             |

|--------------------------------------------------|-------------------|

| Dr. Sébastien Le Beux                            |                   |

|                                                  | External Examiner |

| Dr. Andrew Delong                                |                   |

|                                                  | Examiner          |

| Dr. Sébastien Le Beux                            |                   |

|                                                  | Supervisor        |

| Dr. Glenn Cowan                                  |                   |

|                                                  |                   |

| Dr. Yousef R. Shayan, Chair                      |                   |

| Department of Electrical and Computer Engineerin | a                 |

| Department of Electrical and Computer Engineerin | lg                |

\_\_\_\_ 2023

Approved by

Mourad Debbabi, Dean Faculty of Engineering and Computer Science

#### Abstract

Input-Layer Neuron Design for Spiking Neural Network Application

Seyed Amirhossein Nasrollahi

Artificial Intelligence and Machine Learning algorithms help humans in various applications. Neural Networks systems are one of this area's most important research topics, inspired by the human brain. In this field, Spiking Neural Networks (SNN) use spikes to communicate between neurons mimicking the brain's algorithm. The input data produced by sensors has to be converted to spikes for training and testing these systems. Rate encoding is a popular method that encodes the input signal into the spiking frequency.

This work presents two methods to design an analog input encoder that receives the information and converts them to spiking output. Both ways use a  $\Delta\Sigma$  modulator to create a digital output from the input signal. The first input encoder, called synchronous  $\Delta\Sigma$  analog to spike converter, reads the digital output of the  $\Delta\Sigma$  and produces a spike for every '1' bit. The second design is called neuromorphic  $\Delta\Sigma$  analog to spike converter, which uses a synapse and neuron model to produce the rate-encoded spiking output. The synapse converts the  $\Delta\Sigma$  output to a current, and the neuron receives this current at its input.

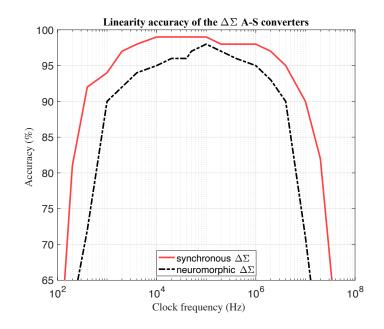

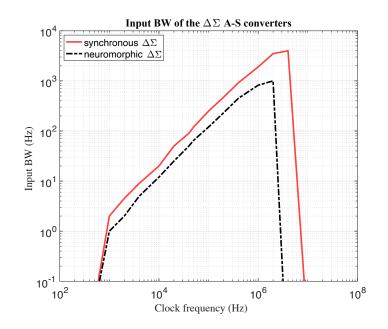

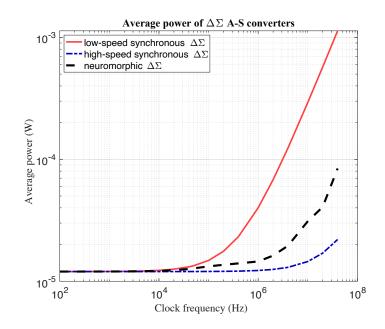

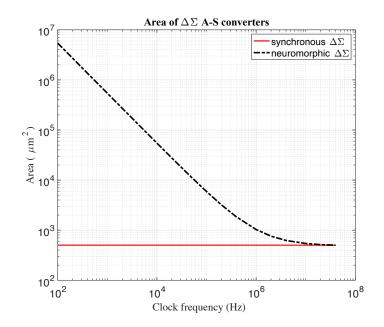

This thesis is the first design to build a general input encoder that can be used in most SNN systems. A clock signal can change the firing frequency of both encoders. The synchronous  $\Delta\Sigma$  A-S converter can perform for clock signals between 1 kHz and 4 MHz while the neuromorphic one can perform between 1 kHz and 2 MHz. The optimized clock frequency is 50 kHz for both of them. With this clock, the synchronous one's accuracy is 99.2% encoding a DC input, and its input can have a maximum bandwidth of 120 Hz to achieve an SNR higher than 50 dB. It consumes 13.4  $\mu$ W average power with 500  $\mu$ m<sup>2</sup> area. The neuromorphic one's accuracy for DC inputs is 97.3%, and its maximum bandwidth is 65 Hz. It consumes 12.7  $\mu$ W average power with 0.011 mm<sup>2</sup> area.

## Acknowledgments

I would like to thank the following people and organizations for helping with this research project:

My supervisor, Glenn Cowan for guidance and support during my MASc program.

Concordia, FRQNT, and NSERC for research opportunities, facilities, and financial support.

Ted Obuchowicz for CAD tool support, and Terry Stewart for general advice.

and finally, my family, friends, and everyone in the Research Lab for their help in different circumstances.

## Contents

| List of | Figures                                            | viii |

|---------|----------------------------------------------------|------|

| List of | Tables                                             | xiii |

| 1 In    | roduction                                          | 1    |

| 1.1     | Input Neuron Architecture                          | 3    |

| 1.2     | Thesis Organization                                | 4    |

| 1.3     | Contribution                                       | 5    |

| 2 Li    | erature Review                                     | 7    |

| 2.1     | Silicon Neurons                                    | 7    |

|         | 2.1.1 Biological Neuron Model                      | 7    |

|         | 2.1.2 Integrate-and-Fire Neuron Model              | 10   |

|         | 2.1.3 IF Neuron Implementation                     | 11   |

| 2.2     | Silicon Synapses                                   | 16   |

| 2.3     | Spiking Neural Network System                      | 20   |

| 2.4     | $\Delta\Sigma$ Encoder                             | 22   |

|         | 2.4.1 $\Delta\Sigma$ System                        | 22   |

|         | 2.4.2 $\Delta\Sigma$ Common Circuit Implementation | 26   |

| 2.5     | Analog Input to Spike Converters                   | 28   |

|         | 2.5.1 Voltage to Current (V-I) Conversion          | 28   |

|         | 2.5.2 $\triangle$ Modulation                       | 30   |

| 2.6  | Literature Conclusion                                              | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Desi | ign Methodology                                                    | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.1  | Synchronous $\Delta\Sigma$ Analog to Spike (A-S) Converter         | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 3.1.1 Block Diagram                                                | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 3.1.2 Circuit Design                                               | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.2  | Neuromorphic $\Delta\Sigma$ Analog to Spike Converter              | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 3.2.1 Block Diagram                                                | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 3.2.2 Circuit Design                                               | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.3  | Design Comparison                                                  | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Sim  | ulation Results                                                    | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |                                                                    | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | *                                                                  | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |                                                                    | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.2  |                                                                    | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |                                                                    | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |                                                                    | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.3  |                                                                    | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |                                                                    | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | · ·                                                                | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.4  |                                                                    | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |                                                                    | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |                                                                    | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.5  |                                                                    | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |                                                                    | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |                                                                    | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 4.5.3 Power                                                        | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 4.5.4 Area                                                         | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.6  |                                                                    | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | Des<br>3.1<br>3.2<br>3.3<br>Sim<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5 | Design Methodology         3.1       Synchronous ΔΣ Analog to Spike (A-S) Converter         3.1.1       Block Diagram         3.1.2       Circuit Design         3.2       Neuromorphic ΔΣ Analog to Spike Converter         3.2.1       Block Diagram         3.2.2       Circuit Design         3.3       Design Comparison         Simulation Results         4.1       DC Input         4.1.1       Synchronous ΔΣ A-S Converter         4.1.2       Neuromorphic ΔΣ A-S Converter         4.1.2       Neuromorphic ΔΣ A-S Converter         4.2.1       Synchronous ΔΣ A-S Converter         4.2.1       Synchronous ΔΣ A-S Converter         4.2.2       Neuromorphic ΔΣ A-S Converter         4.3.1       Synchronous ΔΣ A-S Converter         4.3.1       Synchronous ΔΣ A-S Converter         4.3.2       Neuromorphic ΔΣ A-S Converter         4.3.4       Area         4.4.1       Synchronous ΔΣ A-S Converter         4.5.1       DC Input         < |

| 5  | Con    | clusion and Discussion | 79 |

|----|--------|------------------------|----|

|    | 5.1    | Conclusion             | 79 |

|    | 5.2    | Discussion             | 80 |

| Bi | bliogi | raphy                  | 83 |

# **List of Figures**

| Figure 1.1 | Input-layer neurons interfacing sensors and SNN                                                      | 4  |

|------------|------------------------------------------------------------------------------------------------------|----|

| Figure 2.1 | Circuit model of Hodgkin-Huxley neuron model [1]                                                     | 8  |

| Figure 2.2 | Steady-state value and time constant of $m$ , $n$ , and $h$ with respect to the                      |    |

| mem        | brane potential in the Hodgkin-Huxley neuron model calculated in [2]                                 | 9  |

| Figure 2.3 | The entire process of creating a spike.                                                              | 10 |

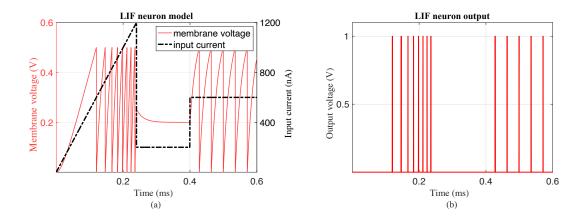

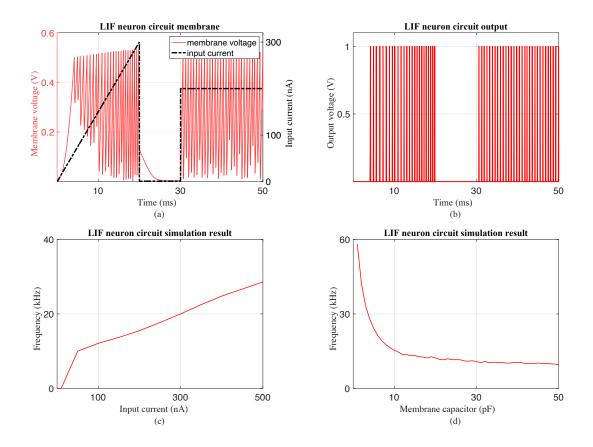

| Figure 2.4 | a) The input current and the membrane potential in the LIF differential equa-                        |    |

| tion s     | simulated in MATLAB b) The resulting output spiking voltage                                          | 11 |

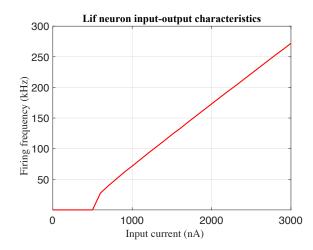

| Figure 2.5 | Output firing frequency of an LIF neuron to DC input current. ( $I_{\theta}$ =500 nA)                | 12 |

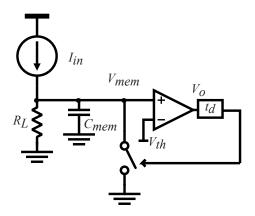

| Figure 2.6 | LIF neuron circuit, implementing equation (2.4) [3].                                                 | 12 |

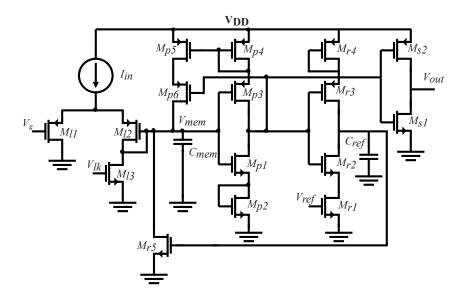

| Figure 2.7 | Complete LIF neuron circuit with positive feedback and reset current from [4].                       | 13 |

| Figure 2.8 | a) LIF neuron's circuit membrane voltage response to the ramp and step                               |    |

| input      | <b>b</b> ) LIF neuron's spiking output to the same input <b>c</b> ) Output firing frequency          |    |

| of an      | LIF neuron's circuit to the DC input current ( $I_{\theta} = 10$ nA) d) Output firing                |    |

| frequ      | ency to the membrane capacitor's value.                                                              | 15 |

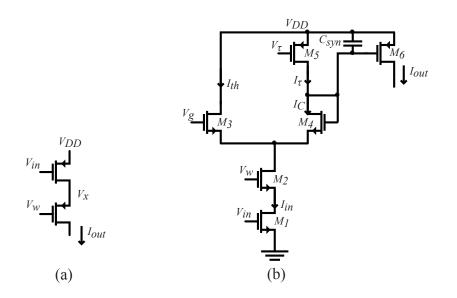

| Figure 2.9 | a) Simple two transistor synapse circuit [5] b) Differential-pair integrator                         |    |

| synaj      | pse circuit [6].                                                                                     | 17 |

| Figure 2.1 | 0 The maximum output current and time constant of the filter for different                           |    |

| value      | is of: a) $V_{\tau}$ , $V_{g}$ , and $V_{w}$ b) $C_{syn}$ (In both figures, the black lines show the |    |

| chan       | ge in the maximum output current, and the red lines show the change in the                           |    |

| time       | constant of the filter, which is $1/f_{3dB}$ ).                                                      | 19 |

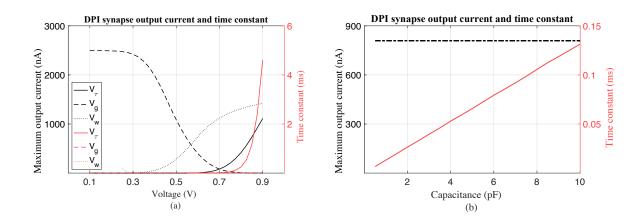

| Figure 2.11 a) The magnitude of the output current with AC input in different frequencies             |    |

|-------------------------------------------------------------------------------------------------------|----|

| <b>b</b> ) The average of output current with spiking input in different firing frequencies.          | 20 |

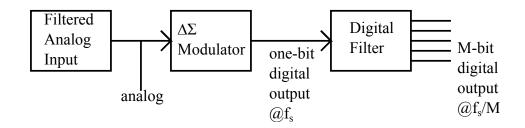

| Figure 2.12 $\Delta\Sigma$ system converting an analog signal to digital [7]                          | 23 |

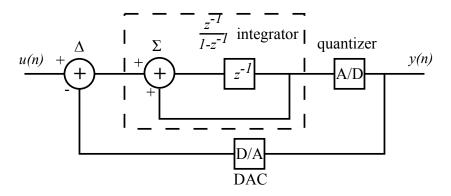

| Figure 2.13 $\Delta\Sigma$ encoder block diagram [7]                                                  | 23 |

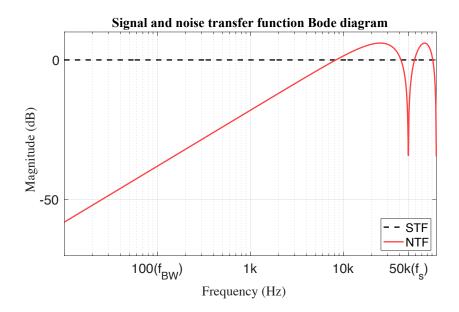

| Figure 2.14 Bode diagram magnitude of signal and noise transfer functions. (signal band-              |    |

| width = $100$ Hz, sampling frequency = $50$ kHz)                                                      | 24 |

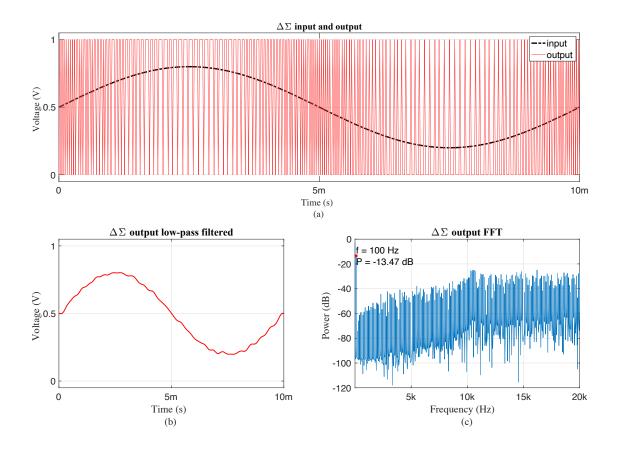

| Figure 2.15 a) Input and output signal of the $\Delta\Sigma$ encoder b) First-order low-pass filtered |    |

| output c) Power spectral density of the $\Delta\Sigma$ output signal                                  | 25 |

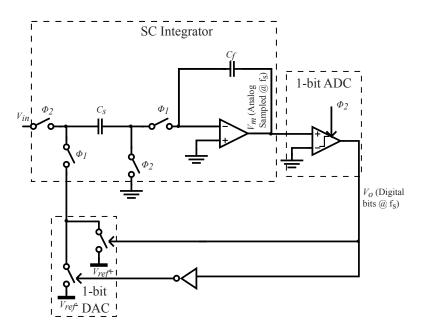

| Figure 2.16 Circuit implementation of the $\Delta\Sigma$ system with an SC integrator, a compara-     |    |

| tor, and single-bit switching DAC [8].                                                                | 27 |

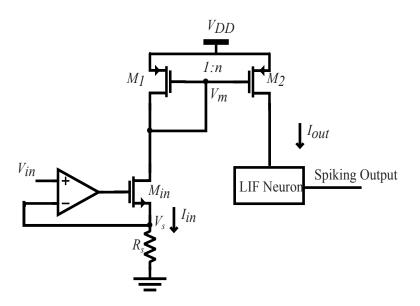

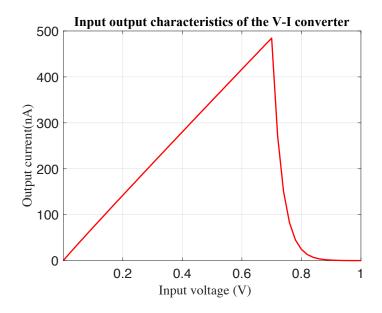

| Figure 2.17 The linear V-I converter used in the input interface of an LIF neuron intro-              |    |

| duced in [9]                                                                                          | 29 |

| Figure 2.18 Input-output characteristics of the linear V-I converter of Figure 2.17                   | 30 |

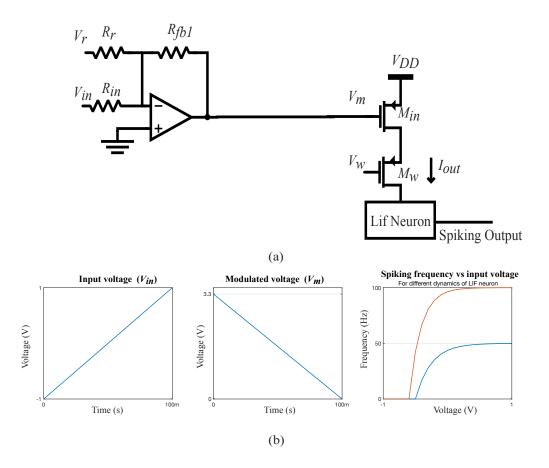

| Figure 2.19 a) The input encoder designed in [5] b) Input, modulated signal and the                   |    |

| corresponding spiking frequency of the circuit [5]                                                    | 31 |

| Figure 2.20 Encoding the changes in input in UP and DOWN signals by $\Delta$ modulation               |    |

| corresponding to increase or decrease of the input value [10]                                         | 32 |

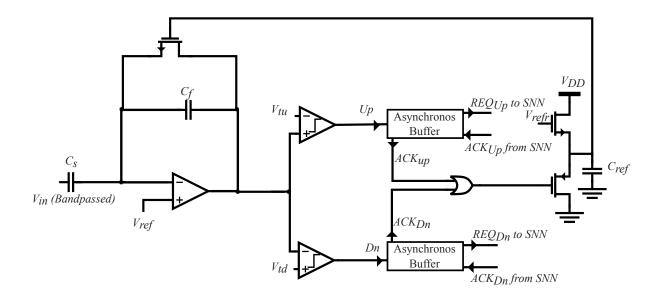

| Figure 2.21 Input EEG signal, Up and down spikes encoding change slope of the input [10].             | 32 |

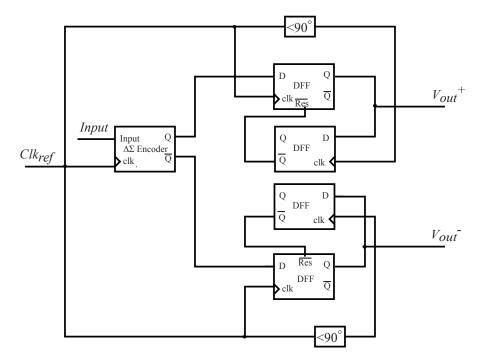

| Figure 3.1 Block diagram of the synchronous $\Delta\Sigma$ A-S converter, and example signals         |    |

| at each node.                                                                                         | 35 |

| Figure 3.2 The output signal of the Synchronous $\Delta\Sigma$ A-S converter with respect to a        |    |

| ramp and step input ( $f_{clk} = 50 \text{ kHz}$ ).                                                   | 35 |

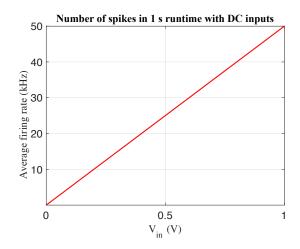

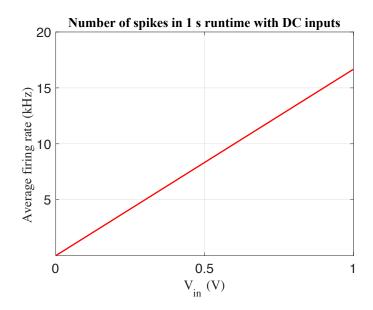

| Figure 3.3 The number of spikes in 1 s runtime with respect to different DC input values              |    |

| $(f_{clk} = 50 \text{ kHz}).$                                                                         | 36 |

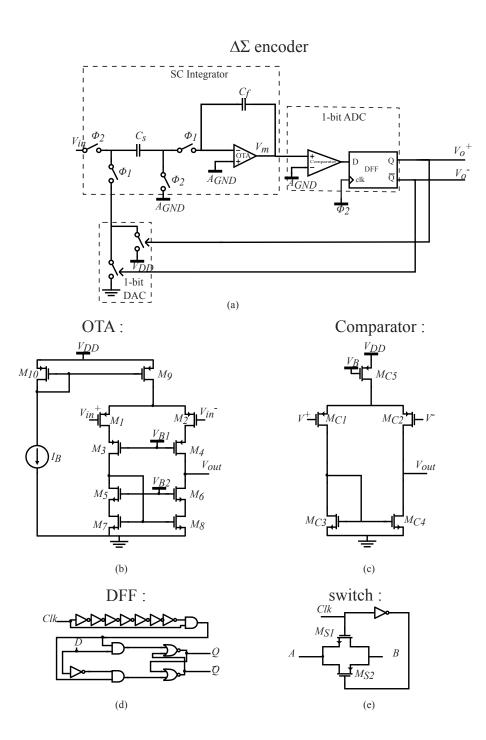

| Figure 3.4 a) The $\Delta\Sigma$ circuit b) The single-stage differential-input OTA c) The single-    |    |

| stage analog comparator with differential input d) The DFF designed with AND,                         |    |

| NOR, and inverter gates e) Transmission gate switch design.                                           | 38 |

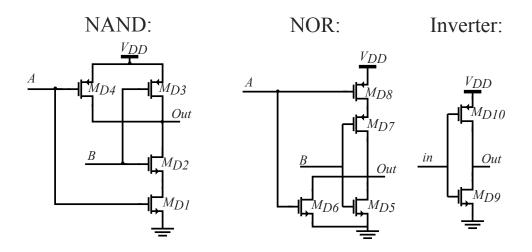

| Figure 3.5 Digital gates design used in every digital circuit.                                        | 41 |

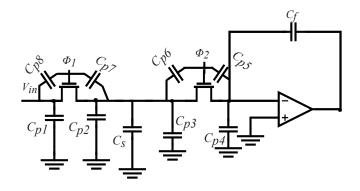

| Figure 3.6 The simplest switch-capacitor discrete-time integrator with parasitic capaci-                   |      |

|------------------------------------------------------------------------------------------------------------|------|

| tors [7]                                                                                                   | . 41 |

| Figure 3.7 Circuit design of creating two non-overlapping clock signals from a clock                       |      |

| reference                                                                                                  | . 42 |

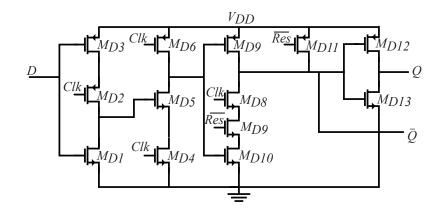

| Figure 3.8 Synchronous $\Delta\Sigma$ A-S converter complete circuit design                                | . 42 |

| Figure 3.9 Clock-edge triggered DFF circuit with asynchronous active-low reset                             | . 43 |

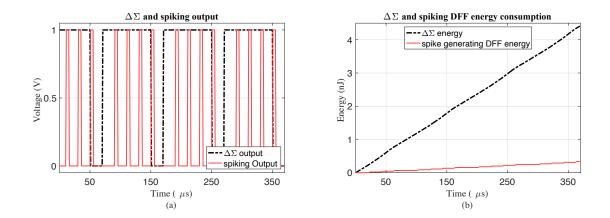

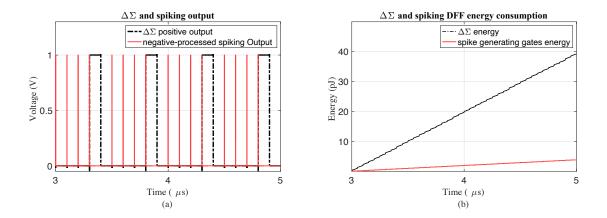

| Figure 3.10 a) Positive-processed $\Delta\Sigma$ and spiking output with 0.8 V DC input. b) $\Delta\Sigma$ |      |

| encoder and spike generating DFF's energy consumption in 370 $\mu$ s with the same                         |      |

| input                                                                                                      | . 44 |

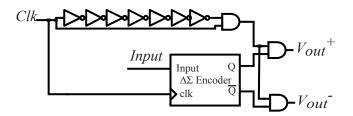

| Figure 3.11 Low energy consumption spike generating circuit for high-frequency appli-                      |      |

| cations.                                                                                                   | . 44 |

| Figure 3.12 a) $\Delta\Sigma$ output signal and negative-processed spiking output with 0.2 V DC            |      |

| input <b>b</b> ) $\Delta\Sigma$ encoder and spike generating AND gate's energy consumption in 2 $\mu$ s    |      |

| with 0.2 V DC input                                                                                        | . 44 |

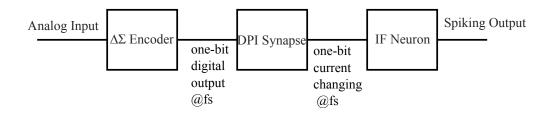

| Figure 3.13 Block diagram of the neuromorphic $\Delta\Sigma$ A-S converter                                 | . 46 |

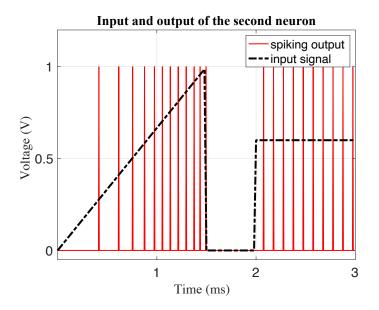

| Figure 3.14 The output signal of the neuromorphic $\Delta\Sigma$ A-S converter with respect to a           |      |

| ramp and step input ( $f_{clk} = 50 \text{ kHz}$ ).                                                        | . 47 |

| Figure 3.15 The average spiking frequency produced by the neuromorphic $\Delta\Sigma$ A-S con-             |      |

| verter in 1 s runtime with respect to different DC input values ( $f_{clk} = 50 \text{ kHz}$ )             | . 48 |

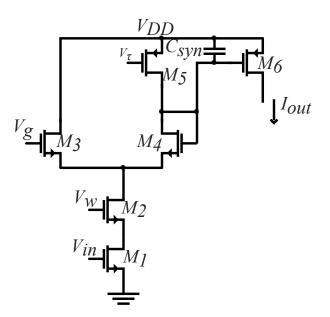

| Figure 3.16 Differential-pair integrator synapse circuit.                                                  | . 49 |

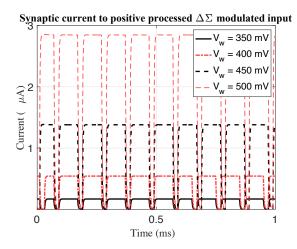

| Figure 3.17 The output current of DPI synapse measured in different weight values. The                     |      |

| input voltage of the synapse is the $\Delta\Sigma$ modulation of a 0.8 V DC voltage                        | . 50 |

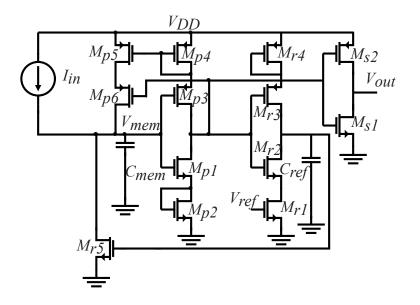

| Figure 3.18 The IF neuron circuit design without a leakage.                                                | . 51 |

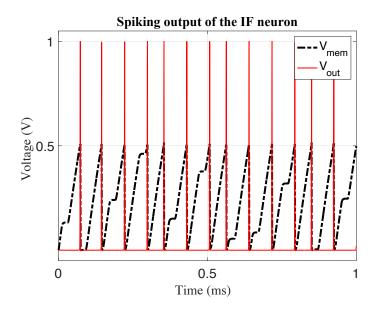

| Figure 3.19 The IF neuron circuit membrane potential and spiking output. The input is                      |      |

| negative-processed $\Delta\Sigma$ modulated current to 0.2 V DC voltage.                                   | . 52 |

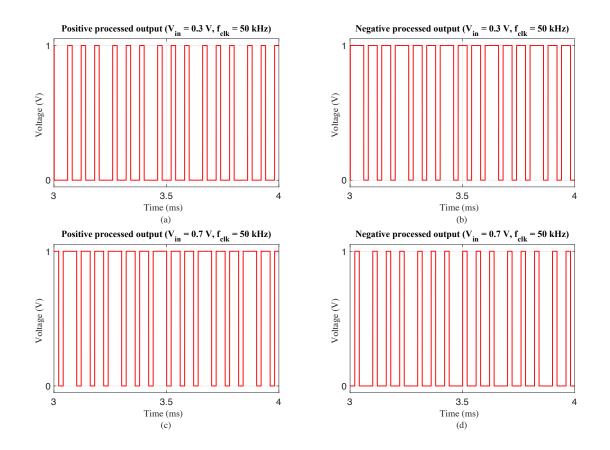

| Figure 4.1 $\Delta\Sigma$ encoder's output digital signal to: <b>a</b> ) positive-processed 300 mV DC      |      |

| input b) negative-processed 300 mV DC input c) positive-processed 700 mV DC                                |      |

| input <b>d</b> ) negative-processed 700 mV DC input.                                                       | . 55 |

|                                                                                                            |      |

| Figure 4.2 Spiking output of the synchronous $\Delta\Sigma$ neuron to: <b>a</b> ) positive-processed |    |

|------------------------------------------------------------------------------------------------------|----|

| 300 mV DC input b) negative-processed 300 mV DC input c) positive-processed                          |    |

| 700 mV DC input d) negative-processed 700 mV DC input                                                | 56 |

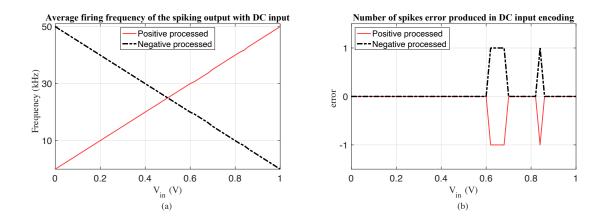

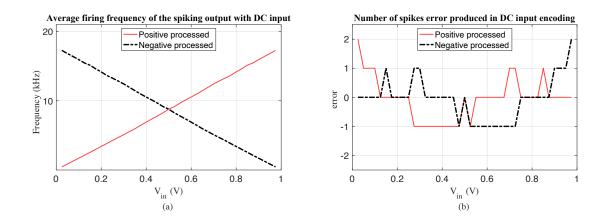

| Figure 4.3 a) The average spiking frequency of the synchronous $\Delta\Sigma$ neuron's circuit in    |    |

| 10  ms runtime with respect to different DC input voltages <b>b</b> ) The encoding error in          |    |

| spike numbers in 10 ms runtime                                                                       | 57 |

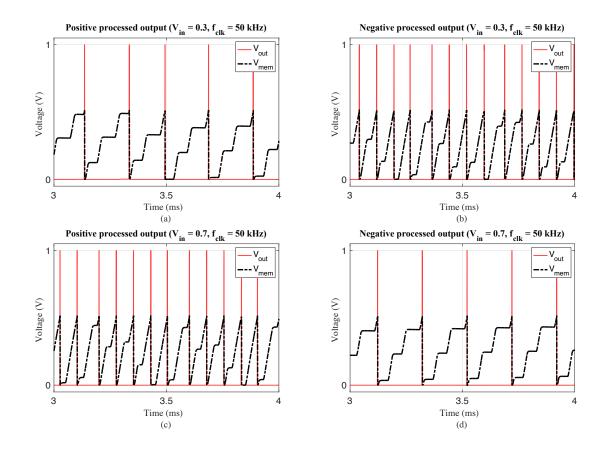

| Figure 4.4 Spiking output and membrane voltage of the neuromorphic input neuron to:                  |    |

| a) positive-processed 300 mV DC input b) negative-processed 300 mV DC input                          |    |

| c) positive-processed 700 mV DC input d) negative-processed 700 mV DC input.                         | 59 |

| Figure 4.5 a) The average spiking frequency of the neuromorphic $\Delta\Sigma$ neuron's circuit      |    |

| in 10 ms runtime with respect to different DC input voltages b) The encoding error                   |    |

| in spike numbers in 10 ms runtime                                                                    | 59 |

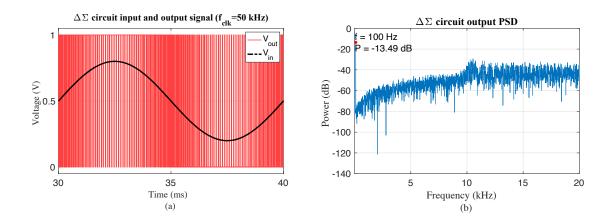

| Figure 4.6 a) The output signal of the $\Delta\Sigma$ circuit to a sinusoidal input with frequency   |    |

| of 100 Hz. b) The PSD of the $\Delta\Sigma$ circuit's output with main harmonic at 100 Hz $$ .       | 61 |

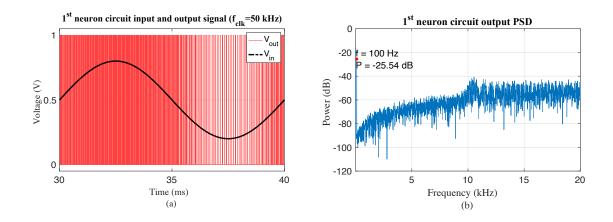

| Figure 4.7 a) The output signal of the synchronous $\Delta\Sigma$ input neuron's circuit to a si-    |    |

| nusoidal input with a frequency of 100 Hz. b) The PSD of the spiking output with                     |    |

| main harmonic at 100 Hz                                                                              | 62 |

| Figure 4.8 SNR of the synchronous $\Delta\Sigma$ input neuron calculated with sinusoidal inputs      |    |

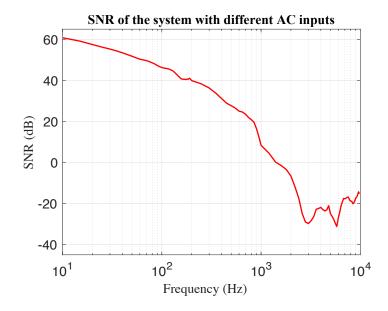

| at different frequencies ( $f_{clk} = 50 \text{ kHz}$ )                                              | 62 |

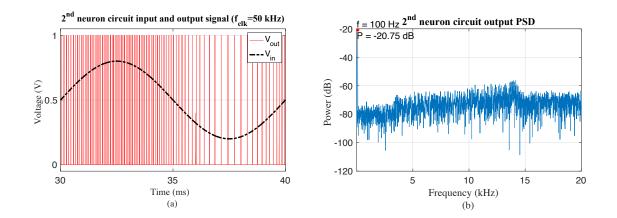

| Figure 4.9 a) The output signal of the neuromorphic $\Delta\Sigma$ A-S converter's circuit to a      |    |

| sinusoidal input with a frequency of 100 Hz. b) The PSD of the spiking output with                   |    |

| main harmonic at 100 Hz                                                                              | 64 |

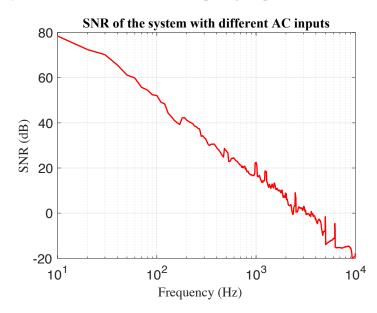

| Figure 4.10 SNR of the neuromorphic $\Delta\Sigma$ A-S converter calculated with sinusoidal in-      |    |

| puts at different frequencies $(f_{clk} = 50 \text{ kHz})$                                           | 64 |

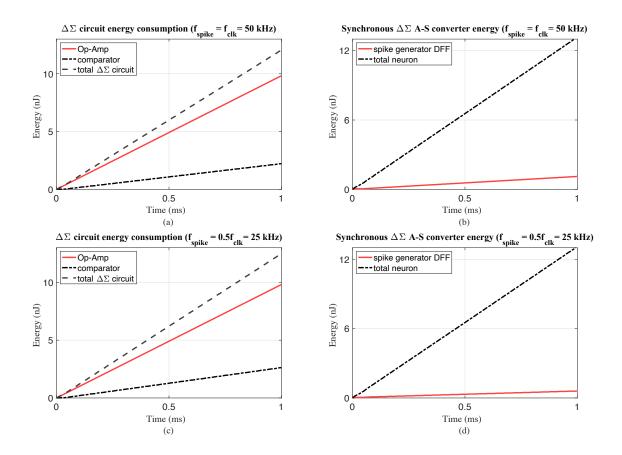

| Figure 4.11 Transient energy consumption of: a) $\Delta\Sigma$ circuit's components when firing      |    |

| at the maximum frequency <b>b</b> ) spike generator DFF and complete synchronous $\Delta\Sigma$      |    |

| neuron when firing at the maximum frequency c) $\Delta\Sigma$ circuit's components when              |    |

| firing at half of the maximum frequency <b>d</b> ) spike generator DFF and complete syn-             |    |

| chronous $\Delta\Sigma$ neuron when firing at half of the maximum frequency $\ldots$ .               | 66 |

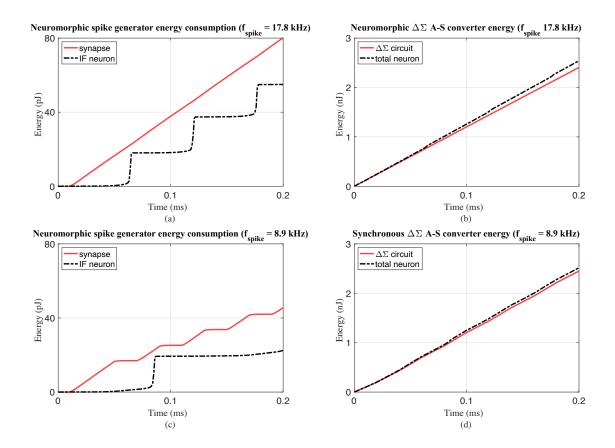

| Figure 4.12 Transient energy consumption of <b>a</b> ) the DPI synapse and the IF neuron fir-   |    |

|-------------------------------------------------------------------------------------------------|----|

| ing at the maximum frequency b) $\Delta\Sigma$ circuit and complete A-S converter at the        |    |

| maximum frequency c) the DPI synapse and the IF neuron firing at half of the max-               |    |

| imum frequency d) $\Delta\Sigma$ circuit and complete A-S converter at half of the maximum      |    |

| frequency                                                                                       | 68 |

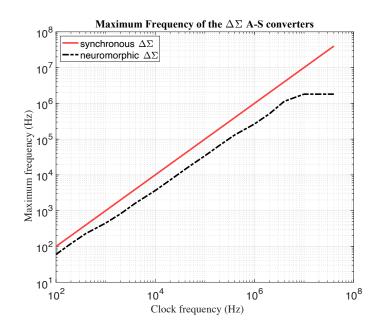

| Figure 4.13 Maximum firing frequency of both $\Delta\Sigma$ A-S converters with respect to dif- |    |

| ferent clock frequencies.                                                                       | 71 |

| Figure 4.14 Positive-processed DC input encoding accuracy of each $\Delta\Sigma$ A-S converter  |    |

| with respect to different clock frequencies                                                     | 72 |

| Figure 4.15 The input BW in which the neurons can encode the changing input with an             |    |

| SNR higher than 50 dB in different clock frequencies                                            | 74 |

| Figure 4.16 The average power consumed by each A-S converter while firing at the max-           |    |

| imum frequency                                                                                  | 75 |

| Figure 4.17 The area occupied by each A-S converter in different clock frequencies              | 76 |

## **List of Tables**

| Table 2.1 | Control parameters of the differential-pair integrator LIF neuron                    | 15 |

|-----------|--------------------------------------------------------------------------------------|----|

| Table 2.2 | Control parameters of the DPI synapse                                                | 19 |

| Table 3.1 | Capacitor values in the $\Delta\Sigma$ system                                        | 39 |

| Table 3.2 | Design parameters of the differential-pair input OTA in Figure 3.4b                  | 39 |

| Table 3.3 | OTA simulated results                                                                | 40 |

| Table 3.4 | Design parameters of the analog comparator in Figure 3.4c                            | 40 |

| Table 3.5 | Design parameters of the DPI synapse                                                 | 49 |

| Table 3.6 | Design parameters of the IF neuron                                                   | 51 |

| Table 4.1 | Power and energy of the synchronous $\Delta\Sigma$ A-S converter in 1 ms             | 67 |

| Table 4.2 | Power and energy of the neuromorphic $\Delta\Sigma$ A-S converter in 1 ms $\ldots$ . | 68 |

| Table 4.3 | Area of different parts of synchronous $\Delta\Sigma$ A-S converter                  | 69 |

| Table 4.4 | Area of different parts of neuromorphic $\Delta \Sigma$ A-S converter                | 69 |

| Table 4.5 | Simulation result's summary of synchronous and neuromorphic $\Delta\Sigma$ A-S con-  |    |

| verte     | rs                                                                                   | 77 |

| Table 4.6 | Performance comparison                                                               | 77 |

## Chapter 1

## Introduction

Since the early stages of Artificial Intelligence (AI), the human brain has inspired many engineers. A fascinating ability of the brain is that it can handle data processing, calculating, control, classification, and cognition tasks with 86 billion neurons and trillions of synapses, consuming an average power of 20W [11, 12]. An artificial Neural Network (ANN) is a graph in which each node represents a neuron, and each connection is only a static number (weight). There are input, hidden, and output layers of neurons in the system. Each neuron receives weighted inputs from its previous layer. Then after applying a function to the sum of these inputs, it produces an output received by the next layer of neurons. Although the ANN method is significantly different from the brain's functionality, both are based on computations of neurons and their interconnectivity [13].

Our brain's energy-efficient processing is in the analog domain. An analog neural network, like the brain, processes, stores, and reads data in the same unit to save energy [14]. On the other hand, ANNs are usually built digitally using the processing power of a CPU or GPU with an external memory unit. Von Neumann's digital architectures in neural networks consume a lot of energy [15]. The challenging part is to process and train an analog system with data and update the existing data in the memory, which is much easier in digital systems [16].

Deep learning is evolved to a point where low-latency energy-efficient computation is needed for complex applications and large datasets. Therefore, traditional Von Neumann's architectures face a bottleneck in these areas [17]. Some solutions in AI have been proposed for this problem. One of these solutions is Optical Neural Networks which can be implemented on-chip with silicon or

with fiber-based optical circuitry [18]. These Optical NNs support a large bandwidth and calculate with high-speed and low power. On the other hand, there are limitations in both silicon and fiber-based Optical NNs. For instance, silicon-based ones suffer from the limitations of Optical-Electrical conversion, and fiber-based ones need a massive system occupying a large area [18].

IBM proposes another solution to the conventional Von-Neumann architectures' problem. Their TrueNorth Spiking Neural Network (SNN) chip functions with a pre-trained network's weights and consumes ultra-low power [17]. Digital synaptic weights are stored in static random access memory (SRAM) arrays on TrueNorth, which faces obstacles in training [19]. They resolved this problem using analog CMOS devices that encode the synaptic weights in their conductances [19]. Although this method's accuracy is smaller than conventional DNN systems, it speeds up the computations in training and forward path while consuming much lower power [19].

One of the most promising solutions is analog Spiking Neural Network systems that are beneficial compared to Artificial ones in terms of power efficiency, and biological plausibility [20]. They can replace the existing ANN systems with almost the same computation power in some applications while consuming much less energy. [21–24] prove that SNNs trained by MNIST dataset classify different digits with an accuracy comparable to ANN systems while consuming fewer resources. In addition, [25] shows that by using proper techniques, the SNN accuracy reaches the ANN counterparts in more sophisticated VGG and Residual Network (ResNet) architectures. Moreover, studying the learning and decision-making process in the brain's biological neural networks is possible with SNN systems [26]. These benefits of SNNs motivate this research and study, in addition to their feasibility of implementation with analog/mixed-signal silicon circuitry.

In the brain, neurons communicate by sending action potentials through the synapses. An action potential, also called a spike, is a pulse signal with narrow width. Spiking Neural Networks (SNN) are neural networks that communicate using spikes, a dynamic signal, instead of static signals used in ANNs. Building blocks of this system are neurons and synapses like our brain. Neurons receive the information and create a spiking output sent to connected neurons using synapses.

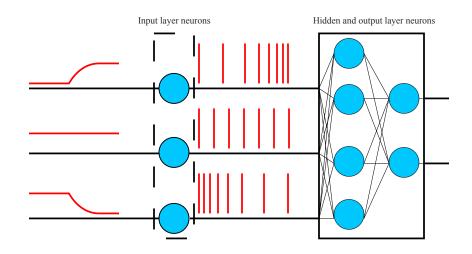

There are two popular methods of information encoding in SNN systems [21]. The first one is rate-encoding, where the information is coded in the firing rate of the neurons. In this method, the output signal's average spiking frequency is proportional to the signal's level. Figure 1.1 shows

how the input layer neurons use rate-encoding to convert the analog input information into spiking signals. The other encoding method is time encoding, where the exact timing of spike arrivals encodes the data. There are different models of temporal encoding. In most of them, the period is divided into discrete times, and the neurons can extract patterns in the arrival time of spikes, which usually applies in pattern recognition algorithms [27]. Although time encoding is utilized more in biological neurons, analyzing and implementing it on silicon is more complex than rate encoding.

The Leaky Integrate-and-Fire (LIF) model describes the mathematics of a simplified biologically plausible neuron [4]. In this model, the neuron receives its input in a current form and integrates this current. Furthermore, a leakage slowly decreases the integrated value. The output of this neuron is in the voltage domain creating a spike train that encodes the information in its firing rate.

Input layer neurons function differently than other layers because they receive analog voltages produced by sensors, whereas other layers receive spiking signals. As shown in Figure 1.1, the input layer neurons must be able to encode the sensory data into spikes with an acceptable resolution and then communicate the spikes to other layers. Since the received data are analog, the neurons' input range must match the sensors' output range. Furthermore, these neurons' spiking frequencies must change linearly with respect to input signals. Finally, the encoders' outputs must follow the changes in the input signals at an acceptable speed. Therefore, an architecture that satisfies the mentioned characteristics must be designed for the input layer neurons, which differ from other layers' structures.

This work proposes two approaches to designing input-layer analog to spike (A-S) converter neurons using a  $\Delta\Sigma$  modulator. Each design is simulated and tested with different test benches in Cadence Virtuoso environment using the TSMC 65nm technology.

#### **1.1 Input Neuron Architecture**

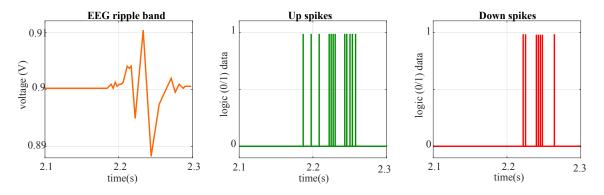

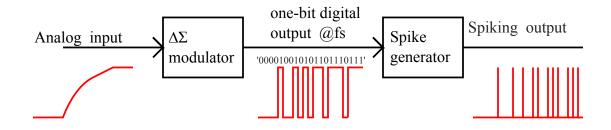

In this work, two different input neurons are proposed. Both consist of a  $\Delta\Sigma$  modulator and a spike-generating mechanism. The  $\Delta\Sigma$  modulator is a popular choice in designing various types of Analog-to-Digital-Converters (ADC). They encode the analog input information in densities of '1's and '0's. The larger the input size, the higher the density of '1's. As a result, the mean value of the

Figure 1.1: Input-layer neurons interfacing sensors and SNN

output represents the input signal. This behavior is similar to what we want as our input neuron, and the remaining part of the design is to convert this one-bit density of '1's to a density of spikes. So, a spike-generating mechanism is needed for this conversion. The difference between the two proposed architectures is the spike generator.

The first design produces spikes directly from the output signal of the  $\Delta\Sigma$  encoder. It converts each '1' bit on the digital output signal of the  $\Delta\Sigma$  into a spike. As a result, the density of spikes represents the density of '1's in which the input signal is encoded.

The second design produces spikes from the output signal of the  $\Delta\Sigma$  using a neuromorphic spike generating circuit. This system uses the same neuron and synapse design as other layers of neurons and includes them after a  $\Delta\Sigma$  encoder. The synapse is responsible for receiving the digital output signal of the  $\Delta\Sigma$ , then creating a current that encodes this digital signal. The neuron receives the encoded current produced by the synapse and fires spikes based on this current. Hence, having a higher '1' density at the  $\Delta\Sigma$  output, which encodes the input signal, results in a larger spiking frequency at the neuron's output.

#### **1.2 Thesis Organization**

Chapter 2 provides the background and literature review, which discusses the theory of spiking neuromorphic models and  $\Delta\Sigma$  converters.

Chapter 3 describes the design methodology and the architectures designed in this work.

Chapter 4 shows the simulation results of two designed neurons and compares them.

Chapter 5 concludes the work and presents further improvements that can be made to the design.

#### **1.3** Contribution

In neuromorphic circuits, it is better if sensory interface, computation, and memory are implemented on a single chip [28]. The input interface is a crucial part of every SNN system. There are limitations in the designed circuits that are supposed to receive the data from the sensory system and convert it to spikes. The neurons' input data is a current. A standard method is to convert the data into spikes outside the chip and feed those spikes into the SNN system [24]. Another common way is that each system has a specific encoding circuit that can only be used on that particular SNN system like a high-frequency oscillation detection system in [10] that only encodes the changes in input. This work's main contribution is to introduce a new architecture for input layers of neurons. It utilizes the prior designs of the  $\Delta\Sigma$  encoder, neuron, and synapse and combines them with some modifications to operate as an input encoder. It can be used in every SNN system to encode the input sensory data into spiking patterns.

A benefit of using the  $\Delta\Sigma$  encoder is that it comes with a clock frequency set by the designer to fulfill the system's requirements. The average firing frequency in an SNN system can vary from biological frequency (~ 100 Hz) up to tens of MHz. The maximum firing frequency required by the system is determined by the clock frequency of the  $\Delta\Sigma$  encoder. If the clock frequency changes, nothing needs to be changed in the circuit except for the capacitor values to adapt to the new firing frequency. Therefore, this design can be used in different frequency applications.

This work can replace any voltage-to-current (V-I) converters used in the input of the SNN system to read the sensory data. The current feeding into the neuron is very low to keep the transistors of the neuron at sub-threshold. A V-I converter that creates a sub-threshold current must consume a large area because of the large resistors and transistors or lose conversion accuracy. This input-layer neuron uses the one-bit output of the  $\Delta\Sigma$  to create a spiking output. Although its building blocks are not the same as other layers, it does not consume a larger area than other neurons and can provide much better accuracy than any V-C converters.

$\Delta\Sigma$  encoder is well-known in ADC design with great conversion accuracy. The resolution of the  $\Delta\Sigma$  can be preserved while creating spiking voltage from its output. Both input neurons encode the input signal with accuracy higher than 97% in their optimized frequency using a  $\Delta\Sigma$  encoder. We can use this ADC in a wider variety of applications related to neuromorphic encoding and achieve the same level of data encoding accuracy as ADCs.

This work is the first analog/mixed-signal architecture in designing encoders for the input data of any SNN systems by using the basic structures of the  $\Delta\Sigma$  encoder and the Integrate-and-Fire (IF) neuron model. The result of this work is shown with different types of input signals in accuracy, linearity error, power, area, input signal bandwidth, and Signal-to-Noise Ratio (SNR). In the future, researchers can investigate what improvements can be made in each criterion by changing the looporder (number of integrators) or design of the  $\Delta\Sigma$  encoder. Moreover, all neuron models, such as adaptive LIF [29], Izhekevich [30], AdExpIF [31], ... can be tested in the framework of the second proposed architecture, and their pros and cons be evaluated.

The results of this work are also published at the IEEE NEWCAS 2022 conference [32].

## **Chapter 2**

## **Literature Review**

This work presents two architectures that encode the input signal for SNN systems. The building blocks are  $\Delta\Sigma$  modulator, silicon neuron, and synapse.

#### 2.1 Silicon Neurons

#### 2.1.1 Biological Neuron Model

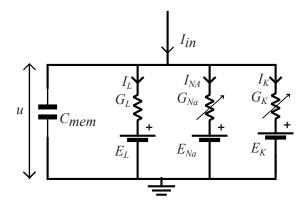

In ANN systems, neurons have a static processing model, whereas, in SNNs, the neurons communicate with each other using spike signals. The brain inspires this method of communication. In the brain, a neuron's inside is separated from the outside of it by a membrane. A sudden increase in the membrane potential and resetting to the initial value after a short period is called an action potential or a spike. A voltage over a capacitor in the neuron can model the membrane potential. Hodgkin and Huxley's neuron model is the first attempt to calculate neurons' dynamic behavior by measuring the flow of ions between the inside and outside of a membrane [1, 33]. As shown in Figure 2.1, voltage-dependent resistors model the ion channels, and an independent resistor models the leakage of the neuron. A voltage source is set for the resting potential of each channel.

Figure 2.1: Circuit model of Hodgkin-Huxley neuron model [1].

Mathematical equations of (2.1) describe the behavior of the electronic circuit shown in Figure 2.1:

$$I_{in}(t) = I_{C_{mem}}(t) + \sum_{j} I_j(t)$$

$$C_{mem} \frac{du}{dt} = -\sum_{j} G_j(u - E_j) + I_{in}(t)$$

(2.1)

where  $I_j$ ,  $G_j$ , and  $E_j$  represent each branch's current, conductance, and voltage source values.

The objective of Hodgkin and Huxley was to measure the changes of channel resistors with respect to time and the membrane voltage [34]. In their work, sodium (Na) and potassium (K) conductances are voltage-dependent, where  $G_{Na} = g_{Na}m^3h$  and  $G_K = g_K n^4$ , whereas  $G_L$  is a constant. The changes of these resistors to time and voltage are modeled in constant variables  $g_{Na}$  and  $g_K$ , and probability variables m, n, and h that are between 0 and 1 and alter the channel resistors in time. (2.2) describes the dynamics of these probability variables:

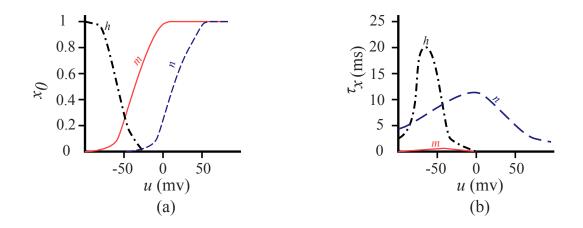

$$\frac{dx}{dt} = -\frac{1}{\tau_x(u)} [x - x_0(u)]$$

(2.2)

where x has a value between 0 and 1 and can be replaced by  $m, n, \text{ and } h. \tau_x$  is its time constant, and  $x_0$  is its steady-state value which are shown in Figure 2.2. The Hodgkin and Huxley neuron model is described in 4 dimensions with 4 differential equations calculating  $\dot{u}, \dot{m}, \dot{h}$ , and  $\dot{n}$  shown in (2.1) and (2.2). Detailed analysis of these equations is in [1].

The simple description of this 4-dimensional equation is that the input current is integrated into

Figure 2.2: Steady-state value and time constant of m, n, and h with respect to the membrane potential in the Hodgkin-Huxley neuron model calculated in [2]

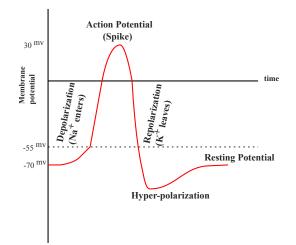

the membrane capacitor. The sodium channel conductance is  $G_{Na} = g_{Na}m^3h$ , which changes with the membrane potential, u. As shown in Figure 2.2b, the time constant of m is tiny. Therefore, we can assume that the change in m is instantaneous. When membrane potential increases, m rapidly changes and increases  $G_{Na}$ ; therefore,  $I_{Na}$  also rises. Since  $u < E_{Na} = 55$  mv [33], the rise of  $I_{Na}$  increases the membrane potential known as the depolarization phase in Figure 2.3. Afterward, with a rise of u, h decreases and starts to close the Na channel slowly. Then, the potassium channel,  $G_K = g_K n^4$ , opens when n increases. Since  $\tau_n > \tau_m$  and  $u > E_K = -77$  mv, the K channel's effect appears later than the Na channel, and its current decreases the membrane potential. This effect is known as the repolarization phase, shown in Figure 2.3. When  $u < E_L = 65$  mV, known as the hyperpolarization phase, m = n = 0 and therefore both Na and K channel are closed, and  $G_L$  resets the membrane potential to its resting voltage. Figure 2.3 shows this entire process of producing an action potential or spike resulting from the mentioned differential equations.

Implementing Hodgkin and Huxley neuron model on silicon for computational purposes is complex and inefficient. There is a trade-off between biological plausibility and computation cost in SNN systems. Integrate-and-Fire (IF) and Izhekevich [30] neurons describe the spiking model of neurons in an uncomplicated way with a fixed threshold, which can help us for a simpler and cheaper circuit simulation of neurons [33].

Figure 2.3: The entire process of creating a spike.

#### 2.1.2 Integrate-and-Fire Neuron Model

W

In the Integrate-and-Fire (IF) model, a biological neuron's four-dimensional dynamic equations are reduced to one equation and a resetting mechanism. In general, the IF neuron is described as equation (2.3) [33]:

$$\tau \frac{du}{dt} = R(u)I_{in} + f(u)$$

(2.3)

hen  $u \ge u_{\theta} \Rightarrow$  spike and  $u \to u_{rest}$

where  $\tau$  is the time constant, R(u) is the leakage resistor model, f(u) is the neuron model's function,  $u_{\theta}$  is the threshold voltage and  $u_{rest}$  is the membrane's resting potential. In the linear IF model, known as Leaky IF (LIF), R(u) is a constant resistor, and f(u) is linear as (2.4):

$$\tau \frac{du}{dt} = RI_{in} - (u - u_{rest})$$

(2.4)

when  $u \ge u_{\theta} \Rightarrow$  spike and  $u \to u_{rest}$

where R(u) and f(u) are replaced by a constant resistor R and the linear function  $-(u - u_{rest})$ .

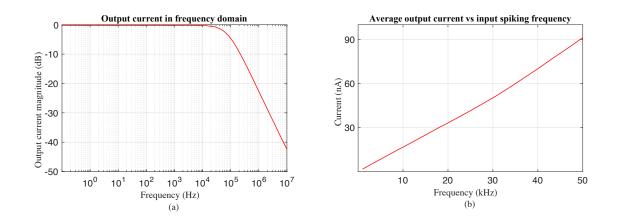

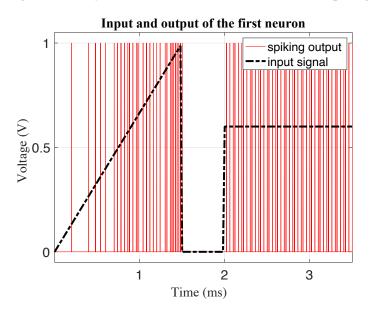

In electronic circuits, we usually want to imitate the behavior of biological neurons for computational purposes. We have to scale the biological values for better computational accuracy on electronic circuits. In biological neurons, the threshold and resting potential are around -55 mV and -70 mV and the spike peaks at 30 mV as shown in Figure 2.3. First, we defined an output

Figure 2.4: **a**) The input current and the membrane potential in the LIF differential equation simulated in MATLAB **b**) The resulting output spiking voltage.

voltage of  $V_{out}$  that changes from 0 V to V<sub>DD</sub> at each spike time and resets after a delay. Then, the resting potential is set to 0 V, and the threshold is changed to V<sub>DD</sub>/2. The time constant and the leakage resistor is set to 20  $\mu$ s and 1 M $\Omega$ , respectively resulting in a membrane capacitance of 20 pF and achieving kHz range spiking frequency. With this setup, the membrane potential and output voltage are shown in Figure 2.4.

When we increase the input current, the neuron fires more rapidly, as expected from the differential equations of (2.4). If the input current is below  $I_{\theta}$ , the membrane voltage settles at a voltage below the threshold, and the neuron does not fire spikes. As a result, a threshold current is calculated in (2.5):

$$\tau \frac{du}{dt} = 0 \Rightarrow RI_{in} = u - u_{rest} \Rightarrow I_{\theta} = \frac{u_{\theta} - u_{rest}}{R}$$

(2.5)

where  $I_{\theta}$  is the firing threshold current which is 500 nA for the setup of Figure 2.5. The firing frequency of the neuron rises linearly with respect to the input current increase if the current is above its threshold. The output firing frequency with respect to the input current is shown in Figure 2.5.

#### 2.1.3 IF Neuron Implementation