### Analog Filtering of EEG signals in the Presence of Artifact

### Signals

Kwabena Asamoah

### A Thesis

in

### The Department

of

**Electrical and Computer Engineering**

### Presented in Partial Fulfilment of the Requirements

for the Degree of Master of Applied Science (Electrical and Computer Engineering) at

Concordia University

Montreal, Quebec, Canada

October 2022

© Kwabena Asamoah, 2022

### **CONCORDIA UNIVERSITY**

### **School of Graduate Studies**

This is to certify that the thesis prepared

By: Kwabena Asamoah

Entitled: Analog Filtering of EEG signals in the Presence of Artifact Signals and submitted in partial fulfilment of the requirements for the degree of

### Master of Applied Science (Electrical and Computer Engineering)

complies with the regulations of the University and meets the accepted standards with respect to originality and quality.

Signed by the final examining committee:

Chair

Dr. A. Bhowmick

Chair

Chair

Chair

Chair

Chair

Chair

External Examiner

Dr. A. Bhowmick

Internal Examiner

Dr. C. Wang

Thesis Supervisor

Dr. Rabin Raut

Thesis Supervisor

Dr. M.N.S. Swamy

Approved by\_

Dr. Y. R. Shayan, Chair Department of Electrical and Computer Engineering

2022

Dr. Mourad Debabbi, Interim Dean, Gina Cody School of Engineering and Computer Science

### Abstract

### Analog Filtering of EEG signals in the Presence of Artifact Signals

### Kwabena Asamoah

Recovery of bio-electric signals, such as EEG, ECG, have been routinely done in the past via sophisticated numerical algorithms and extensive computing resources. Current works on filtering of EEG signals does not clearly reveal the electronic circuit operations by which the artifact signals can be obtained to serve as a reference signal for filtering operation. A technique to isolate the artifact signals mixed with intended bio-electric signals (i.e., EEG), by using analog circuit components has been proposed in the thesis. The artifact signal band is assumed to be separated from the intended signal bands.

The novelty of the approach lies in recovering the artifact signal from the mixture of contaminated biomedical signals and then re-using it to recover the intended signals. Prior knowledge about the artifact signal is not needed, except for demonstration of the principles through simulation work. Data base of CMOSP 18 technology available in the VLSI laboratory of Concordia University has been used for all simulations.

The use of recovered artifact signal as a reference signal for the filtering process by elimination of the intended signal, is presented in the thesis. All these operations were easily implemented with analog circuit components. Further work along this direction will be very useful in developing wearable electronic devices for communication of point-of-care health data from a human body, wirelessly to distant medical center locations for further processing. This is expected to provide relatively inexpensive solutions toward current day trend of wireless point-of-care electronic circuits and systems for public health monitoring.

### Acknowledgements

First and foremost, I would like to sincerely thank my supervisors, Dr. Rabin Raut and Dr. M.N.S Swamy for their direct contributions and rich expertise that has motivated the output of this research. It is my pleasure to know them and their major contribution towards the widespread domains of electrical and computer engineering. It would not have been possible to pursue my master's degree without the financial support provided by them through the research bursary program of Concordia University. I am very thankful to them for this. I am highly indebted for their invaluable advice, immense support and great personality that created a thriving relationship for the success of this research and my daily academic life.

I shall remain thankful to the Graduate Studies Entrance Scholarship Committee for their help in beginning my studies in Concordia. I would also like to thank Mr. Ted Obuchowicz, Engineering Specialist, VLSI laboratory for his support during my work with the CAD tools of the VLSI laboratory. I am thankful to my friends in the laboratory for providing their support and creating a peaceful environment in the laboratory. I also appreciate all friends and families whose kind help and diverse supports made my study and life in Canada a great success.

## **Table of Contents**

| List of Figures  | ix   |

|------------------|------|

| List of Tables   | xiii |

| List of Acronyms | xiv  |

| List of Symbols  | xvi  |

| Chapter 1   | Introduction                             | 1  |

|-------------|------------------------------------------|----|

| 1.1: Existi | ng Practices for Recovery of EEG signals | 3  |

| 1.1.1:      | Regression algorithm                     | 4  |

| 1.1.2:      | Blind source separation                  | 5  |

| 1.1.3:      | Adaptive filtering Methods               | 6  |

| 1.2: Objec  | tives and Direction of Current Research  | 9  |

| 1.3: Outlin | ne of the Thesis                         | 11 |

| ( | Chapter 2 Review of Notch Filter                | .13  |

|---|-------------------------------------------------|------|

|   | 2.1: Analytical Model of Analog filters         | .13  |

|   | 2.2: Introduction to Notch Filters              | . 15 |

|   | 2.3: Seconder Order Notch Filter                | 15   |

|   | 2.4: Further Characteristics of a Notch Filters | 19   |

|   | 2.5: Typical Application of a Notch Filter      | .22  |

|   | 2.6: Conclusion                                 | .23  |

| Chapt | ter 3 Am   | plifiers in the Proposed System                                     | 24   |

|-------|------------|---------------------------------------------------------------------|------|

| 3.1:  | Operation  | al Amplifiers                                                       | 24   |

| 3.2:  | Design of  | the Operational Amplifier (OPAMP)                                   | .25  |

|       | 3.2.1:     | Differential input stage                                            | 27   |

|       | 3.2.2:     | Output gain stage                                                   | 29   |

|       | 3.2.3:     | Overall gain of the OPAMP (at low frequencies)                      | 30   |

|       | 3.2.4:     | Design of the compensation circuit                                  | 30   |

|       | 3.2.5:     | Biasing and start up circuit                                        | 33   |

| 3.3:  | Realizatio | n of Passive Resistors from MOS Transistors                         | 34   |

| 3.4:  | Transistor | s Size Data and the Performance Parameters of the OPAMP             | .35  |

| 3.5:  | Summing    | Amplifier                                                           | 37   |

| 3.6:  | Difference | e Amplifier                                                         | . 40 |

|       | 3.6.1:     | Implementation of MOS pseudo resistor                               | 43   |

| 3.7:  | Conclusio  | n                                                                   | .46  |

|       |            |                                                                     |      |

| Chapt | ter 4 Sul  | osystems of the Proposed Analog System                              | .47  |

| 4.1:  | The Com    | pander                                                              | . 47 |

|       | 4.1.1:     | Compressor and expander circuit                                     | 48   |

|       | 4.1.2:     | Results and performance parameters of the compander                 | 51   |

| 4.2:  | ARTI Sys   | tem                                                                 | .53  |

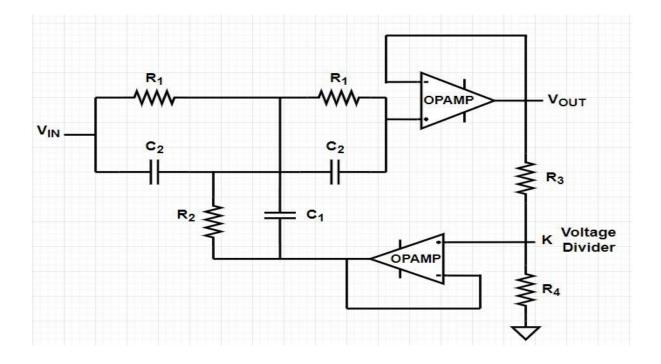

|       | 4.2.1:     | Design and implementation of the notch filters                      | 54   |

|       | 4.2.2:     | Investigation related to the notch frequencies of the notch filters | 55   |

|       | 4.2.3:     | Components design for the notch filters                             | 57   |

|       |            |                                                                     |      |

| 4.3: Conclusion |  |

|-----------------|--|

|-----------------|--|

| Chapter 5  | Validation Results for the Proposed System6                                       | 2  |

|------------|-----------------------------------------------------------------------------------|----|

| 5.1: Valid | ation of the Operating Principles of the Proposed System                          | 2  |

| 5.2: A Mi  | xture of Two Sinusoidal Signals as the Artifact Signal6                           | 3  |

| 5.3: Arbit | rary Signal as Artifact Signal6                                                   | 7  |

| 5.4: Band  | Pass Filter Array (BPFA)7                                                         | 2  |

| 5.4.1      | : Output of <b>BF1and BF2</b>                                                     | 3  |

| 5.5: Conc  | lusion7                                                                           | 5  |

| Chapter 6  | Conclusion and Future Works7                                                      | 6  |

| 6.1: Conc  | lusion7                                                                           | 6  |

| 6.2: Possi | ble Future Work                                                                   | 9  |

| References |                                                                                   | 1  |

| Appendices |                                                                                   | 5  |

| A.1. MA7   | LAB codes used to simulate the magnitude response of the notch filter at differen | ıt |

| values of  | Q <sub>P</sub>                                                                    | 5  |

| A.2. MA    | TLAB codes used to simulate the phase response of the notch filter at differen    | ıt |

| values of  | Q <sub>P</sub>                                                                    | 6  |

| A.3. MA    | TLAB codes used to simulate the pure EEG and contaminated EEG data8               | 8  |

| A.4. MA7   | LAB codes used in characterisation of pseudo resistors                            | 9  |

| A.5. Path address for operational amplifier design                        |

|---------------------------------------------------------------------------|

| A.6. Path address for CMOS summing amplifier design90                     |

| A.7. Path address for pseudo resistor configuration90                     |

| A.8. Path address for compressor circuit design90                         |

| A.9. Path address for expander circuit design                             |

| A.10. Path address for notch filter design with null frequency of 0.5Hz90 |

| A.11. Path address for notch filter design with null frequency of 10Hz91  |

| A.12. Path address for unity gain difference amplifier design             |

| A.13. Path address for the proposed filtering system                      |

| A.14. Path address for arbitrary signal (ECG signal) generation           |

# **List of Figures**

| Figure 1.1.      | Artifact components in EEG signals [3]2                                    |

|------------------|----------------------------------------------------------------------------|

| Figure 1. 2(a).  | General framework of artifact removal [5]3                                 |

| Figure 1. 2(b).  | Linear framework of artifact removal [5]4                                  |

| Figure 1. 3.     | Schematic of ICA [2]6                                                      |

| Figure 1. 4.     | Noise canceller system using adaptive filtering [2]7                       |

| Figure 1. 5.     | The placement of the electrodes for recording of VEOG and HEOG [8]. 8      |

| Figure 1. 6.     | Algorithm of EEG data pre-processing [8]9                                  |

| Figure 1. 7.     | The proposed system10                                                      |

| Figure 2. 1.     | Schematic representation of an analog filter13                             |

| Figure 2. 2.     | Types of notch filters [12]16                                              |

| Figure 2. 3 (a). | Output of notch filter                                                     |

| Figure 2. 3 (b). | Output of the notch filter                                                 |

| Figure 2. 4 (a). | Phase response of notch filter (60Hz) at different Q <sub>P</sub> values19 |

| Figure 2. 4 (b). | Magnitude response of notch filter (60Hz) at different $Q_P$ values20      |

| Figure 2. 5.     | Internal structure of LMF90 [15]22                                         |

| Figure 3. 1.     | Schematic representation of a two-stage OPAMP25                            |

| Figure 3. 2.     | Schematic representation of the OPAMP [17]26                               |

| Figure 3. 3.     | Schematic representation of the differential input stage28                 |

| Figure 3. 4.     | Schematic representation of the output gain stage                          |

| Figure 3. 5.     | A small signal model of the OPAMP for compensation analysis [19]31        |

|------------------|---------------------------------------------------------------------------|

| Figure 3. 6.     | Biasing circuit [17]                                                      |

| Figure 3. 7.     | Summing amplifier                                                         |

| Figure 3. 8.     | CMOS Summing amplifier                                                    |

| Figure 3. 9.     | Instrumentation amplifier [17]41                                          |

| Figure 3. 10.    | Unity gain difference amplifier (D_AMP)42                                 |

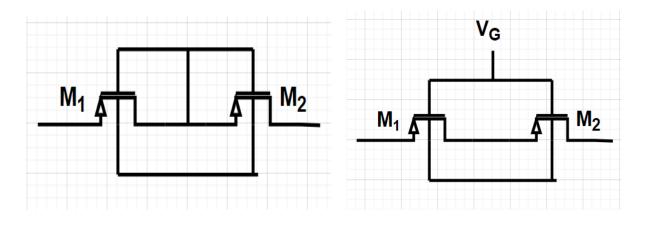

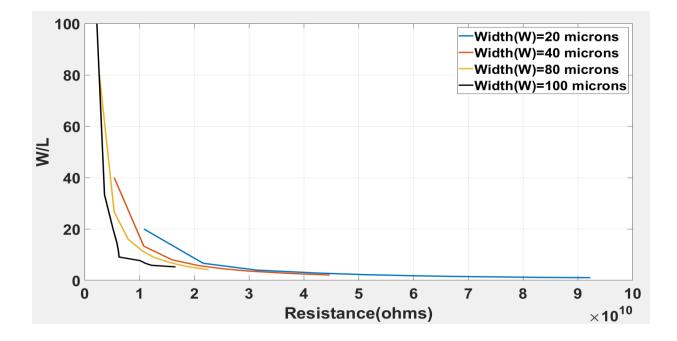

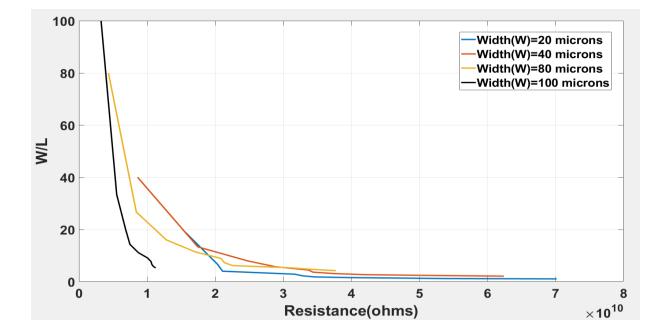

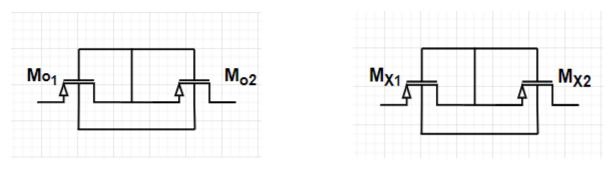

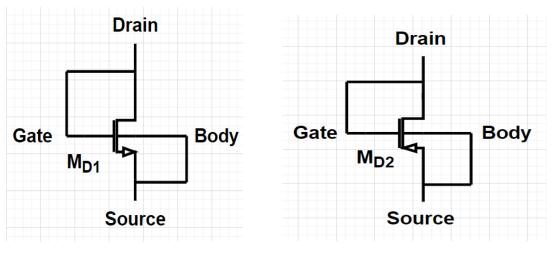

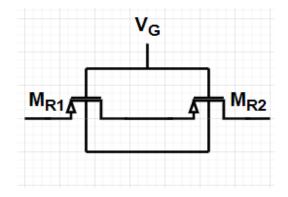

| Figure 3.11      | Pseudo resistor configurations43                                          |

| Figure 3.12      | AC resistance characterisation of self-biased pseudo resistor44           |

| Figure 3.13      | AC resistance characterisation of pseudo resistor with an external biased |

| voltage          |                                                                           |

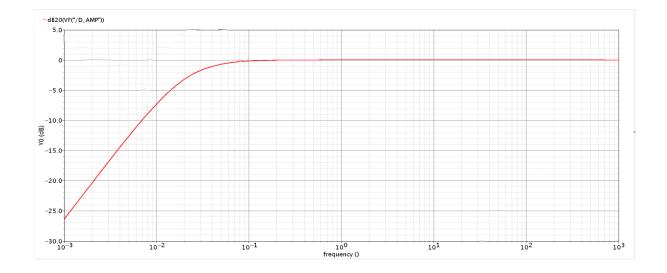

| Figure 3.14      | Frequency response of the unity gain amplifier45                          |

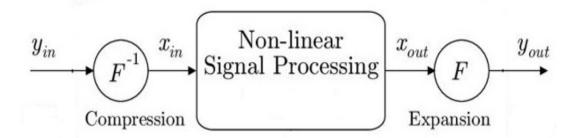

| Figure 4. 1.     | Generalized companding principles [23]48                                  |

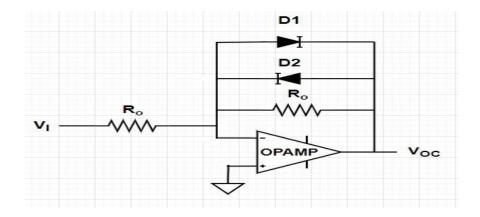

| Figure 4. 2 (a). | Compressor circuit (COMPR)49                                              |

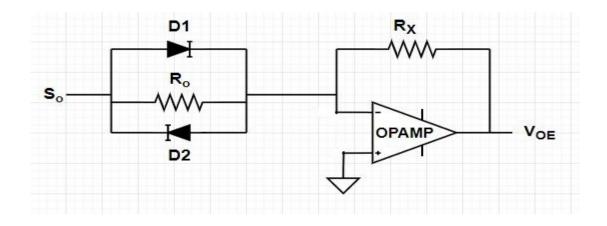

| Figure 4. 2 (b). | Expander circuit (EXPDR)                                                  |

| Figure 4. 3.     | Pseudo resistor [22]50                                                    |

| Figure 4. 4.     | MOS diode51                                                               |

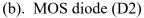

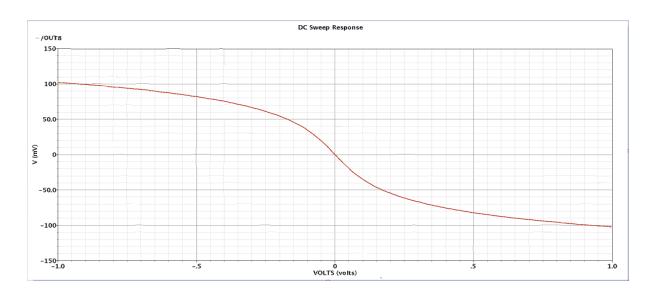

| Figure 4. 5 (a). | Output-input voltage characteristics of the compressor                    |

| Figure 4. 5 (b). | Output-input voltage characteristics of the expander                      |

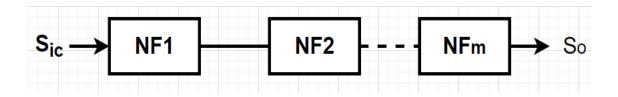

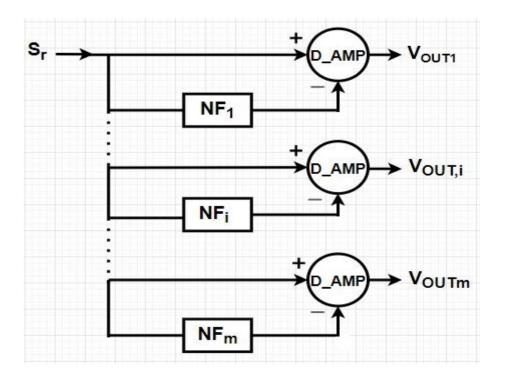

| Figure 4. 6.     | ARTI block consisting of m notch filters53                                |

| Figure 4. 7.     | Active twin T notch filter [25]54                                         |

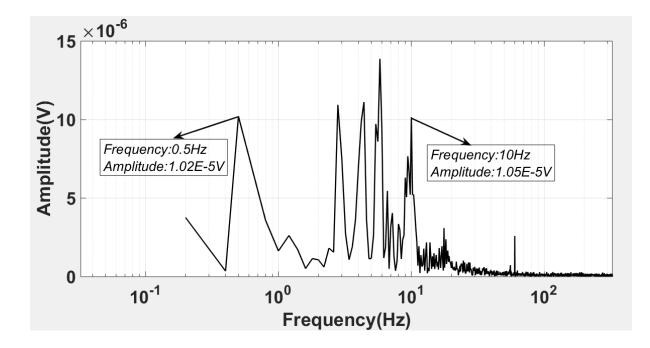

| Figure 4. 8 (a). | Spectral density plot of the contaminated signal56                        |

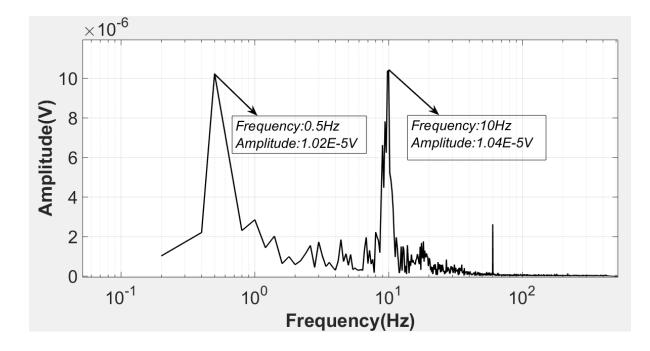

| Figure 4. 8 (b). | Spectral density plot of the desired signal                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------|

| Figure 4. 9.     | Pseudo resistor                                                                                                       |

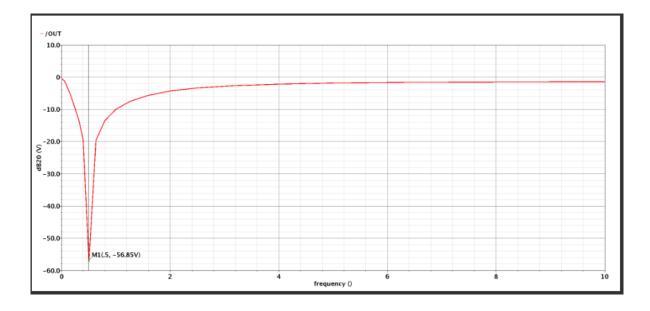

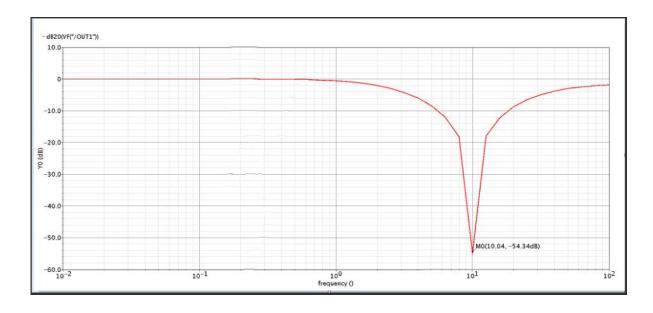

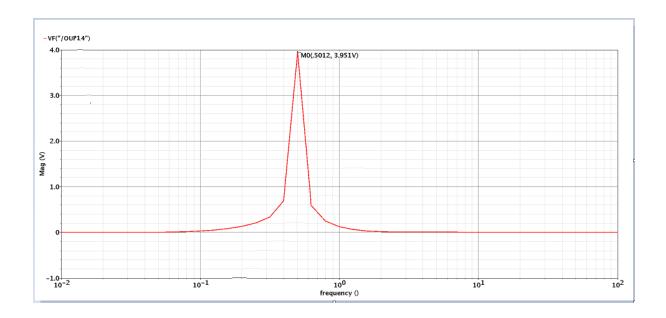

| Figure 4. 10.    | Frequency response of notch filter with $f_n = 0.5$ Hz                                                                |

| Figure 4. 11.    | Frequency response of notch filter with $f_n = 10$ Hz59                                                               |

| Figure 5. 1.     | Proposed system                                                                                                       |

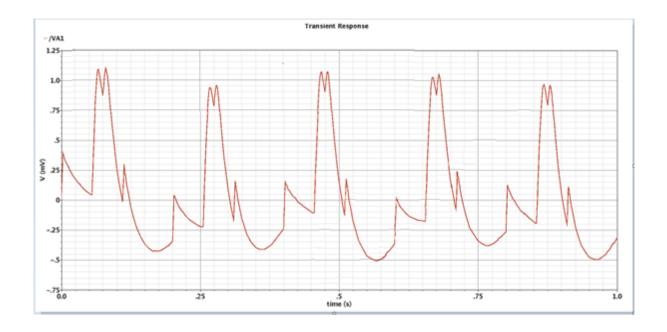

| Figure 5. 2.     | Artifact signal Sart applied to the terminal V3 in Fig. 5.164                                                         |

| Figure 5. 3.     | Contaminated (desired plus artifact) signal S <sub>i</sub> at the output of the sensors array (S_ARRAY) in the system |

| Figure 5. 4.     | Contaminated signal Sic at the output of the compressor (COMPR)65                                                     |

| Figure 5. 5.     | Artifact signal $S_{oc}$ at the output of the cascaded notch filters in ARTI65                                        |

| Figure 5. 6.     | Recovered artifact signal $S_0$ at the output of the expander (EXPDR)66                                               |

| Figure 5. 7.     | Recovered desired signal Sr at the output of D_AMP in Fig.5.1                                                         |

| Figure 5. 8.     | Frequency spectrum at the output of D_AMP in Fig.5.167                                                                |

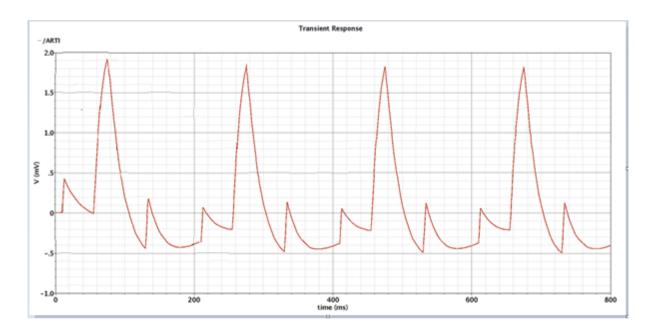

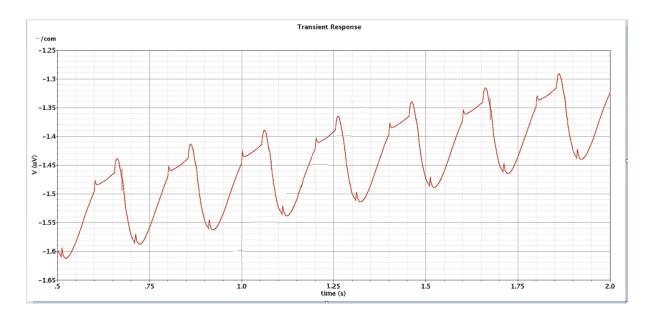

| Figure 5. 9.     | Mimic ECG waveform as the artifact signal S <sub>art</sub> fed at terminal V <sub>3</sub> in Fig. 5.1                 |

| Figure 5. 10.    | Contaminated (desired plus artifact) signal S <sub>i</sub> at the output of the summer (S_ARRAY)69                    |

| Figure 5. 11.    | Contaminated signal S <sub>ic</sub> at the output of the compressor (COMPR)69                                         |

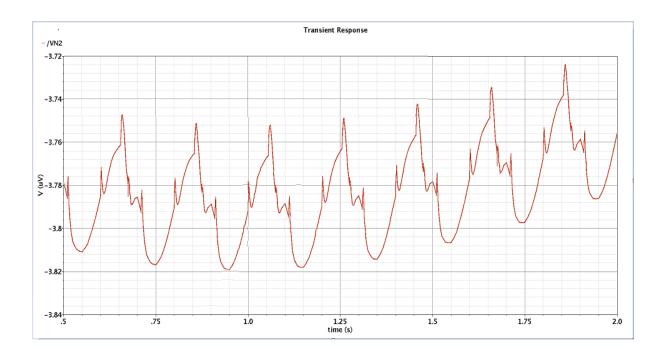

| Figure 5. 12.    | Artifact signal $S_{oc}$ at the output of the cascaded notch filters in ARTI70                                        |

| Figure 5. 13.    | Recovered artifact signal So at the output of the expander (EXPDR)70                                                  |

| Figure 5. 14.    | Recovered desired signal Sr at the output of D_AMP in Fig.5.171                                                       |

| Figure 5. 15. | Frequency spectrum at the output of D_AMP in Fig.1.5   | 71 |

|---------------|--------------------------------------------------------|----|

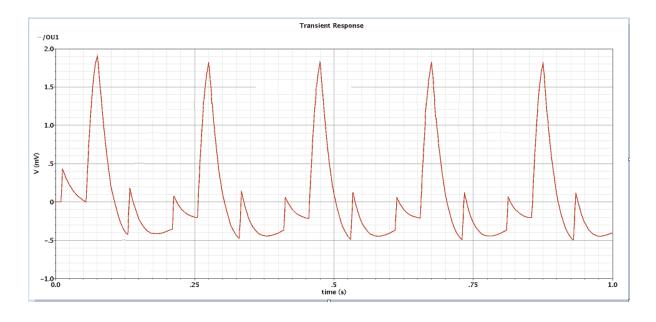

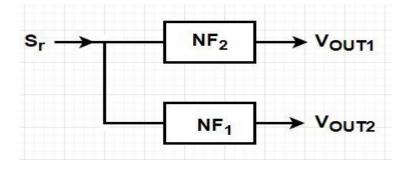

| Figure 5. 16. | Realization of the bandpass filters                    | 72 |

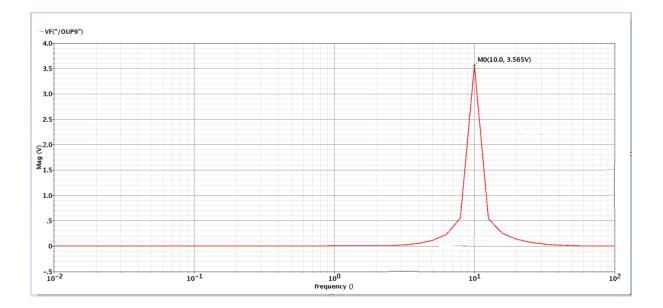

| Figure 5. 17. | Frequency spectrum of the output of $V_{OUT1}$ (10Hz)  | 73 |

| Figure 5. 18. | Frequency spectrum of the output of $V_{OUT2}$ (0.5Hz) | 74 |

| Figure 5. 19. | Separation of the $\delta$ and $\alpha$ waves          | 74 |

## List of Tables

| e 2. 1. Standard biquad transfer functions                                              | 14 |

|-----------------------------------------------------------------------------------------|----|

| e 2. 2. Phase angle for different values of $Q_P$ ( $f_0 = 60$ Hz)                      | 20 |

| e 2. 3. Magnitudes for different values of $Q_P$ ( $f_0 = 60$ Hz)                       | 21 |

| EEG rhythms with their corresponding frequency                                          | 23 |

| e 3. 1. AC Parameters of transistors (a) M2, (b) M4, (c) M6, (d) M9 and (e) M11?        | 26 |

| e 3. 2. Design parameters for the OPAMP shown in Figure 3.2                             | 36 |

| e 3. 3. Simulated results of the OPAMP                                                  | 37 |

| e 3. 4. Design parameters of the CMOS summing amplifier shown in Figure 3.8             | 40 |

| e 3. 5. Design parameters of the unity-gain difference amplifier                        | 45 |

| e 4. 1. Design parameters of the compander (refer to Figures 4.2, 4.3 and 4.4)          | 53 |

| e 4. 2. Design parameters and simulation results for the notch filter with $f_n = 0.51$ | Hz |

|                                                                                         | 60 |

| e 4. 3. Design parameters and simulation results for the notch filter with $f_n = 101$  | Hz |

|                                                                                         | 60 |

# List of Acronyms

| AC    | Alternating Current                      |  |  |  |

|-------|------------------------------------------|--|--|--|

| ANFIS | Adaptive Neuro Fuzzy Interference System |  |  |  |

| BPFA  | Array of Bandpass Filters                |  |  |  |

| BSS   | Blind Source Separation                  |  |  |  |

| CMOS  | Complementary Metal-Oxide Semiconductor  |  |  |  |

| CMRR  | Common Mode Rejection Ratio              |  |  |  |

| COMPR | Compressor block                         |  |  |  |

| DC    | Direct current                           |  |  |  |

| D_AMP | Difference Amplifier block               |  |  |  |

| ECG   | Electrocardiogram                        |  |  |  |

| EEG   | Electroencephalogram                     |  |  |  |

| EGG   | Electrogastrogram                        |  |  |  |

| EOG   | Electrooculogram                         |  |  |  |

| EXPDR | Expander block                           |  |  |  |

| IA    | Instrumentational Amplifier              |  |  |  |

| IC    | Integrated Circuit                       |  |  |  |

| ICA   | Independent Component Analysis           |  |  |  |

| L     | Channel length of a MOS transistor       |  |  |  |

| LMS   | Least Mean Square                 |  |  |  |

|-------|-----------------------------------|--|--|--|

| MOS   | Metal Oxide Semiconductor         |  |  |  |

| NF    | Array of Notch Filters            |  |  |  |

| NMOS  | Negative channel MOS              |  |  |  |

| OA    | Ocular Artifact                   |  |  |  |

| OPAMP | Operational Amplifier             |  |  |  |

| PFE   | Partial Fraction Expansion        |  |  |  |

| PMOS  | Positive Channel MOS              |  |  |  |

| RLS   | Recursive Least mean Square       |  |  |  |

| SSE   | Sum of the Squared Error          |  |  |  |

| S_AMP | Summing Amplifier block           |  |  |  |

| W     | Channel Width of a MOS transistor |  |  |  |

| VLSI  | Very Large-Scale Integration      |  |  |  |

# List of Symbols

| C <sub>ox</sub> | Channel Oxide Capacitance of a MOS transistor |

|-----------------|-----------------------------------------------|

| dB              | Decibels                                      |

| H(s)            | Transfer Function                             |

| D(s)            | Denominator                                   |

| N(s)            | Numerator                                     |

| $g_m$           | Transconductance                              |

| V <sub>DD</sub> | Positive Supply Voltage                       |

| V <sub>SS</sub> | Negative Supply Voltage                       |

| V <sub>TH</sub> | Threshold voltage of a MOS transistor         |

| Q <sub>p</sub>  | Quality Factor                                |

| ω               | Frequency in radians                          |

| ω <sub>n</sub>  | Zero frequency                                |

| $\omega_{p}$    | Pole frequency                                |

| $\mu_n$         | Carrier mobility through the channel          |

| α               | Alpha                                         |

| β               | Beta                                          |

| δ               | Delta                                         |

| γ               | Gamma                                         |

### **Chapter 1**

### Introduction

Electronic circuits and systems pervade the modern world in diverse ways. One of these areas is human health care. While human health was at the realms of scientists in biology, physiology and medicine, advent of computers ushered in significant collaborations of activities among the above fronts. The computational power could be efficiently exploited to process data about various electromagnetic signals that are generated within the human body. Physiological signals are a sub-class of these electromagnetic signals. These can be detected by special sensors that deliver electrical signals corresponding to the body signals. Once the knowledge of the electrical signals is obtained, scores of electronic signal processing principles could be used to diagnose the health conditions of a human subject. This area of activities exploiting electronics in studying physiological signals forms the basis of the subject of bioelectronics and biomedical engineering.

An important aspect of working with bioelectronics signals is the availability of human subjects, electronic equipment, computers all in neighbouring locations. Advent of sub-micron transistors technology has led to the development of electronic devices that could be positioned inside a human body and communicate the status of the physiological signals inside the body to electronic and computing peripherals that are positioned outside the body. Since the sensors can be located inside a human body, the possibility of analysing the signals from a distance by using well-known radio communication principles exists. This is the underlying principle of point of health care systems. The bulky electronic and computing machineries need not be adjacent to the human subject whose body signals are the subject of investigation. Among the various physiological signals, a sub-class that is electrical by nature can be designated as EXG, where  $E \rightarrow$  Electro,  $X \rightarrow$ Gastro or, Cardio or, Retino or, Oculo or, Encephalo,  $G \rightarrow$  Graphic [1]. When we are interested in only one signal from the above list, the others could coexist as disturbances. The signal of interest is referred to as the 'intended' signal, while the disturbing signals are named as artifact signals. In this thesis, EEG signals have been chosen as the intended signal.

Physiological and non-physiological artifacts form the major types of artifact signals depending on the sources of generation. Physiological artifacts are mainly caused by biological activities from the human body such as eye movement and blinking, cardiac potential, muscular potential from the muscle activity, sweating and others [2]. Non-physiological artifacts are other interferences generated outside the human body, which includes power line noises, electromagnetic noises from the electrical components, etc. Figure 1.1 [3] present the summary of some of the various artifact signals that interfere with the EEG signals.

| Physiological/internal                                |           |                                                                                   | Extra-physiological/external         |                                                                             |                                                        |                                                                                          |

|-------------------------------------------------------|-----------|-----------------------------------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------|

| Ocular                                                | Cardiac   | Muscle                                                                            | Others                               | Instrumental                                                                | Interference                                           | Movement                                                                                 |

| Eye blink<br>Eye movement<br>Eye flatter<br>REM sleep | ECG pulse | Chewing<br>Swallowing<br>Clenching<br>Sniffing<br>Talking<br>Scalp<br>contraction | Gloss kinetic<br>Skin<br>Respiration | Electrode<br>Displacement<br>and pop-up<br>Cable<br>movement<br>Poor ground | Electrical<br>Magnetic<br>Sound<br>Optical<br>EM waves | Head<br>movement<br>Body<br>movement<br>Limbs<br>movement<br>Tremor<br>Other<br>movement |

Figure 1. 1. Artifact components in EEG signals [3]

#### 1.1: Existing Practices for Recovery of EEG signals

The subject of monitoring and analyzing electrical signals generated in human brains (Electroencephalography, EEG) has been of interest to scientists and medical professionals to quantify the state of consciousness such as sleep, and to the study of neurological disorders such as epilepsy, since nearly one hundred years [4]. The work has traditionally been carried out in well established hospitals with expensive computing resources and human specialists. The EEG signals are invariably contaminated by the presence of electrical signals arising out of parts of the human body other than the brain. As mentioned earlier, these are termed artifact signals. The artifact signals are stochastic in nature and hence, cannot be suppressed effectively by a frequency selective system, such as bandpass filters. Hence, other alternative techniques much be adopted to suppress the artifact signals present in the biomedical signal of interest. Fig. 1.2(a) [5] represent the general overview of the artifact removal techniques.

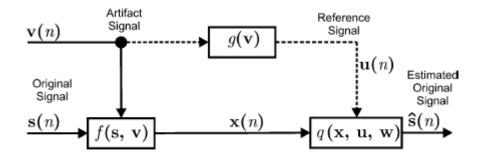

Figure 1. 2 (a). General framework of artifact removal [5]

In [5], the signal x(n) recorded during an experiment is a combination of the original desired signal s(n) contaminated with the artifact signal v(n). The function f represents as to how the two signals are combined to produce the signal at the recording site. This leads to tractable problem formulations as [5],

$$x(n) = s(n) + v(n)$$

(1.1)

Therefore, Fig.1.2(a) evolves to Fig.1.2b). Label (i) depicts the case when a reference signal u(n) is used to estimate v(n) (for instance, adaptive filtering) and (ii) the case when v(n) is estimated directly from x(n) (for example, blind source separation techniques) [5].

Figure 1. 2(b). Linear framework of artifact removal [5]

The use of adaptive cancellation of interfering signals using analog circuits and digital computer interface have been elaborated and demonstrated over fifty years ago [6,7]. Extensive research about the removal of artifact signals has been (and are still being) carried out by many interested researchers [2]– [8]. The other approaches used by these researchers involved the use of numerical algorithms such as regression [2], [3]-[9], and blind source separation [2]-[3], together with the deployment of mixed mode digital and analog signal processing sub-systems and adaptive filtering techniques [2], [3]-[8]. A brief review of these techniques in EEG data processing is presented below.

### 1.1.1: Regression algorithm

Regression analysis is a traditional way of identifying artifact samples and then removing sample that do not belong to the model. Observed artifact contaminated EEG signal and an artifact reference signal are common methods for removing some physiological artifacts such as ocular artifacts. The procedure includes estimating and removing the proportion of EOG components that appear in EEG signal using a least square criterion. The estimation process of EOG components using the determined coefficients is performed either in the time domain or in the frequency domain. However, such regression analysis often fails when there is no reference channel available. In addition, EEG signal being a nonlinear and non-stationary process, linear regression is not the best choice in such application. Moreover, it can only be used to treat few particular types of artifacts, not all types.

#### **1.1.2: Blind source separation**

Blind source separation (BSS) is one of the most used methods, which focuses on the extraction the individual unknown source signals from their mixtures and possibly to estimate the unknown mixing channels using only the information within the mixtures observed at the output of each channel with no, or very limited, knowledge about the source signals and mixing channel.

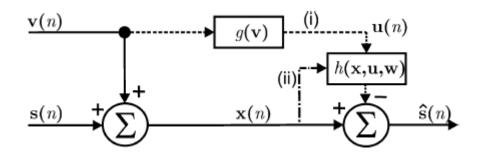

Independent component analysis (ICA) is one of the techniques mostly used BSS in biomedical data analysis [2]. ICA isolates the noise from the EEG signals by decomposing signals into several independent components depending on the statistical independence of the signals. A standard linear ICA model is defined as,

$$\mathbf{x}(\mathbf{t}) = \mathbf{A}.\,\mathbf{s}(\mathbf{t}) \tag{1.2}$$

The goal of the ICA algorithm is to retrieve the original sources s(t) from the observations x(t) by finding the estimation of A inverse matrix ( $A^{-1} = W$ ) such that,

$$\mathbf{y}(\mathbf{t}) = \mathbf{W}\mathbf{x}(\mathbf{t}) \tag{1.3}$$

Fig. 1.3 presents the fundamental model of the ICA principle.

Figure 1. 3. Schematic of ICA [2]

One of the advantages of ICA is that it does not require additional signals for reference, since the algorithm itself does not require prior information. One of the major limitations is that the independent sources must be non gaussian in which the sources are assumed to be statistically independent. Also, ICA requires a manual visual inspection that makes it time consuming.

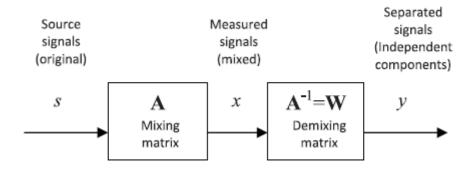

#### 1.1.3: Adaptive filtering Methods

Conventional filtering methods are not very promising since they may attenuate not only the artifact signal component, but also the EEG signal due to overlapping frequency spectra [2]. Adaptive filtering can be used to overcome the time invariance characteristics of conventional filtering techniques. The main aim of adaptive filtering is to predict the cluster of artifact signal in the primary signal (i.e., contaminated biomedical signal) and then subtract that artifact from it. The recovered artifact signal used for adaptive filtering is referred to as a reference signal [2]. Technically, the reference signal is picked up by an additional channel that directly refers to the artifact sources. A reference input separated from the primary input is used to realize the noise canceller system (Fig. 1.4). Likewise, a reference signal is used for adaptive filtering operation reported in [6], [10].

Figure 1. 4. Noise canceller system using adaptive filtering [2]

Adaptive filtering algorithm for noise removal can be classified in two categories [2]. These are linear and non-linear algorithms.

### a) Linear algorithm

The linear algorithm mostly uses least mean square (LMS) algorithm for the adaptive filtering. The advantages of LMS are its computational simplicity, low memory usage and ease of implementation. LMS algorithm has the ability to adjust the filter coefficients to minimise the error. The recursive least mean square (RLS) is another algorithm that can be adopted in a linear algorithm for adaptive filtering. RLS algorithm uses a matrix operation which requires higher computational complexity, unlike LMS algorithm. This makes the implementation of RLS algorithm more complex and difficult to implement than the LMS algorithm.

#### b) Non-linear algorithm

The adaptive neuro fuzzy interference system (ANFIS) is one of the major categories of the non-linear algorithm [2]. ANFIS is a combination of a fuzzy interference system and artificial neural network. ANFIS comprises of five layers. ANFIS minimizes the sum of the squared error (SSE) by using hybrid learning algorithm, which combines least squares and back propagation gradient descent methods together.

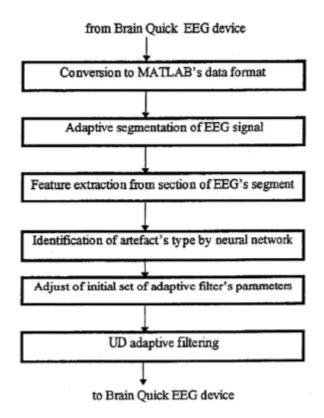

In adaptive filtering of ocular artifact signals from human EEG [8], the authors focus on the removal of Ocular artifacts from EEG data by deploying adaptive segmentation of each segment of the signal to adaptive filtering. Estimates of ocular artifacts (OA) are obtained by suitably scaling the EOG. The OA estimates are then subtracted from the contaminated EEGs to yield artifact-free EEG signals using the UD algorithm [8]. UD algorithm is a numerically stable formulation of the RLS algorithm which is preferred to the LMS because of its superior convergence time, thus enabling it to cope better with different OAs each of which requires a different optimum set of the coefficient for effective removal.

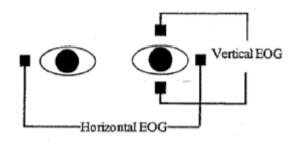

The algorithm is used with MATLAB to separate the EEG signals from the artifact signals. Preliminary observations are carried out on vertical and horizontal EOG signals with suitably placed electrodes (Fig. 1.5). These are used in MATLAB simulation to recover the EEG signal data (Fig.1.6 on the next page).

Figure 1. 5. The placement of the electrodes for recording of VEOG and HEOG [8]

Availability of a reference signal for adaptive filtering is not plausible in a point of care scenario. The subject is not supposed to be present physically in a medical clinic or hospital room to enable/assist in the extraction of the reference artifact signal. The subject will most likely be wearing a device which will sense the EEG signals of interest mixed with other artifact signals, such as EOG, ECG, and extraneous signals like motion signal due to walking, and the like.

Figure 1. 6. Algorithm of EEG data pre-processing [8]

### **1.2: Objectives and Direction of Current Research**

Artifact signals usually overlap with the EEG signals in both the spectral and temporal domains, which makes it difficult to use simple filtering or straight forward signal processing techniques [3]. From the previous studies, we know that a lot of algorithms have been developed in biomedical signal processing. Our objective is to develop a biomedical device which can be used for EEG signal detection and study as in a point of care system (i.e., mobile device in which a human subject can wear on the body). This will be achieved by using analog (or analog plus digital mixed mode) circuit techniques and principles. In our research, we will be proposing a system and provide results to give us the confidence that in near future we can create a device which can be fabricated in an integrated circuit technological laboratory and eventually distribute the knowledge and findings to industries who might be interested in developing the device into an industrial product.

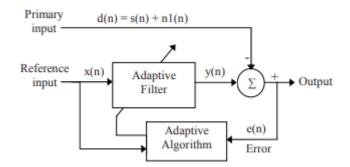

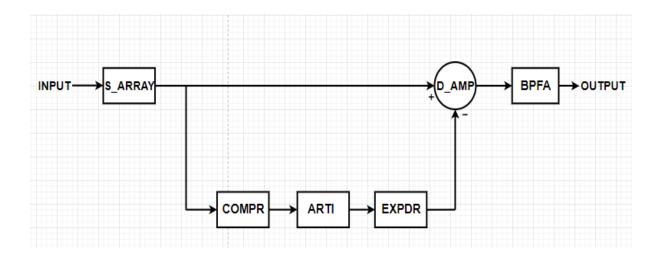

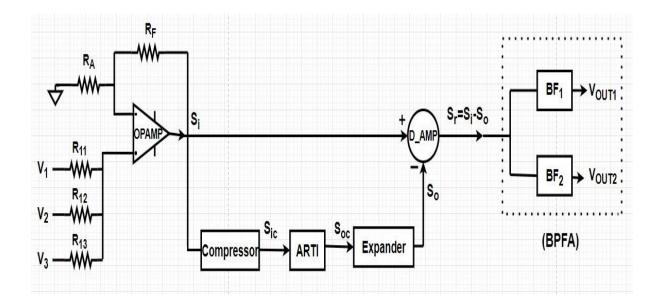

The use of adaptive cancellation of interfering signals using analog circuits and digital computer interface with special impetus on EEG signal processing have been elaborated and demonstrated over fifty years ago [6,7]. Here, we embark on using a not yet published principle to recover the intended signal (i.e., EEG) mixed with artifact signals by separating the artifact signals from the mixture. This is made possible by passing the mixed signals through several notch filters where the notch filters are tuned to the respective intended signals. Thus, the system operates entirely in analog domain. A block diagram of our proposed system is shown in Fig. 1.7. A brief explanation of the operation of the several sub-systems follows. More details are provided in the upcoming chapters of the thesis.

Figure 1. 7. The proposed system

S\_ARRAY: This sub-block presents sensor devices (i.e., an array of EEG recording electrodes) mounted on a human mannequin. This node serves as the spot where the intended signal (i.e., EEG) and the artifact signals are combined as a natural mixture of physiological signals. In our experimental verification of the proposed system, we replace this function by a summing amplifier.

COMPR: This is a compressor system. The purpose of this unit is to compress high valued signals relative to low and moderate valued signals in the mixture of the intended and the

artifact signals. In reality, most of the artifact signals happens to be several times (10 or more) higher than the intended signals.

ARTI: This unit separates the artifact signals from the intended signals by utilizing of a bank of appropriate notch filters.

EXPDR: The expander block compensates for the effect of the COMPR on the magnitudes of the artifact signals. The output from the EXPDR is thus the artifact signals originally present with the intended signals in the sensor devices (S\_AMP).

D\_AMP: This functions as a difference amplifier which subtracts the artifact signals from the output of the S\_AMP, thereby delivering the intended signals only.

BPFA: This contains an array of bandpass filters to selectively deliver the group of intended signals, present in the S\_AMP to the OUTPUT. For good tracking performance, the bandpass filters are realized from the same group of notch filters present in the ARTI block.

### **1.3: Outline of the Thesis**

The thesis is structured as given below.

Chapter 2 represents the basic theory and analytical model of several kinds of second order filters (i.e., low pass, high pass, band pass and notch filters). This chapter mainly focuses on the numerical analysis and implementation of a second order notch filter. The detailed effect of how the characteristics of the notch filter affect the signals passing through the notch system is also presented. Furthermore, a typical application of notch filters in processing of biomedical signal is elaborated in this chapter.

In Chapter 3, the detailed design and implementation of the various amplifiers (i.e., operational amplifier, summing amplifier, difference amplifier etc.) used in the proposed work are presented. This chapter focuses on the realization of passive resistors using MOS

transistors, which includes the implementation of high valued resistors (i.e., in giga-ohms range). Finally, the overall performance of these various amplifiers and MOS resistors using CMOS180 technology are also included in this chapter for validation purposes.

Chapter 4 focuses on the detailed analysis and implementation of the artifact recovery system used to retrieve the reference band of signals for adaptive filtering. The designs of the notch filters are also presented. Moreover, analysis of typical pure and contaminated EEG data is included in this chapter. This helps us to knows the various bands (i.e., Delta, Theta, Alpha, Beta band, etc.) present in the EEG data. Furthermore, the design of the compressor and expander circuits are also elaborated.

Chapter 5 present the verification of the proposed work using the same CMOS180 technology. Furthermore, this chapter also focuses on the generation of the ECG signal as an artifact signal to test the performance of the proposed system. The design and implementation of bandpass filters using the same notch filters presented in Chapter 4 to isolate the individual EEG bands are presented.

The thesis concludes with summary of the work done and some suggestions for possible future work in Chapter 6.

### **Chapter 2**

### **Review of Notch Filter**

In this chapter, we provide a general introduction to analog filters with special impetus on notch filters. The notch filters are the principal components of the adaptive filtering system that is the subject matter of the research work reported in this thesis.

### 2.1: Analytical Model of Analog filters

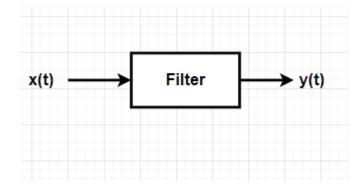

Analog filters are frequency selective networks that allow certain band of frequencies to pass and attenuate other frequencies. Filters as a linear system can be easily analysed and synthesized using network transformation in frequency domain. In continuous time domain, Laplace transform technique can be used to model the transfer function.

Figure 2. 1. Schematic representation of an analog filter

The schematic representation of a filter system in continuous time domain is shown in Figure 2.1. The filter transfer function can be defined in terms of Laplace transformed excitation X(s) and zero state response Y(s).

$$H(s) = \frac{L[y(t)]}{L[x(t)]} = \frac{Y(s)}{X(s)} = \frac{N(s)}{D(s)} = \frac{a_m s^m + a_{m-1} s^{m-1} + \dots + a_0}{b_n s^n + b_{n-1} s^{n-1} + \dots + b_0}$$

where  $m \le n$  for any realizable physical network, N(s) and D(s) are the numerator and denominator polynomial respectively and n is the order of the filter.

Filters are classified according to the filtering function they perform. If our aim is on the magnitude or attenuation characteristics, then we can categorize them as low pass, high pass, band pass and band reject filters. In some applications, if our consideration is only on the phase or delay specifications with no change in magnitude, the filters are considered as all pass networks or delay equalizers.

Table 2.1 shows the analytical expressions for the numerators N(s) of standard second order filter transfer functions (biquads) and is different for different kinds of filters [11]. The denominator function D(s) is the same for all filter types and given by

$$D(s) = s^{2} + {\omega_{p} / Q_{P}} s + \omega_{p}^{2}$$

(1.2)

where  $\omega_p$  is called as the pole frequency and  $Q_P$  as the pole-Q or quality factor.

| Type of Filters | N(s)                                        |

|-----------------|---------------------------------------------|

| Low pass        | $H_0 \omega_p^2$                            |

| High pass       | H <sub>o</sub> s <sup>2</sup>               |

| Band pass       | $H_o \left( \frac{\omega_p}{Q_p} \right) s$ |

| Band stop       | $H_{o}(s^{2}+\omega_{n}^{2})$               |

| All-pass        | $s^2 - {\omega_p / Q_p} s + \omega_p^2$     |

Table 2.1. Standard biquad transfer functions

#### 2.2: Introduction to Notch Filters

In this section, we will introduce the characteristics of notch filters. The property of notch filter is to eliminate a specific frequency among several frequencies present in a complex signal. In biomedical applications, the notch filter is used principally to eliminate the power line frequency signal. In general, the notch filter could be a broadband elimination filter. In that case we do not call it as a notch filter but rather as band stop or band reject filter. Thus, a narrow band reject filter can be called a notch filter and wide band reject filter will be referred to as a band reject filter.

#### 2.3: Seconder Order Notch Filter

The transfer function of a second order notch filter is given by

$$H(s) = \frac{s^{2} + \omega_{n}^{2}}{s^{2} + \frac{\omega_{p}}{Q_{p}} s + \omega_{p}^{2}}$$

(2.2)

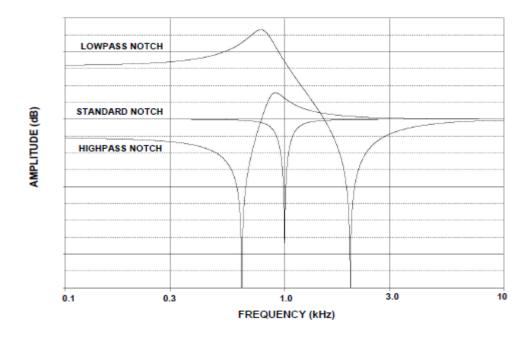

where  $\omega_n$  is the zero frequency of the filter. The relationships of the pole frequency and the zero frequency bring about the three notch filter characteristics which are standard notch, lowpass notch and high pass notch filter. Standard notch is achieved when the  $\omega_p$  is equal  $\omega_n$ . In the notch when  $\omega_n$  is less than  $\omega_p$  the filter is known as high pass notch. If the  $\omega_n$  is higher than  $\omega_p$ , the filter is referred as lowpass notch filter. These characteristics are illustrated in Figure 2.2 [12] on the next page.

Figure 2. 2. Types of notch filters [12]

For example, a seconder order standard notch for a 60Hz power line will have the transfer function,

$$H(s) = \frac{s^2 + (2\pi \times 60)^2}{s^2 + 60\pi s + (2\pi \times 60)^2}$$

(2.3)

assuming  $Q_p = 2$ .

For instance, if a signal at frequency  $\omega_1$  is input to a standard notch filter with notch frequency of  $\omega_n$ , the overall output of the notch filter in frequency domain will be given by (assuming  $\omega_n = \omega_p$ )

$$Y_1(s) = \left(\frac{\omega_1}{s^2 + \omega_1^2}\right) \times \left(\frac{s^2 + \omega_n^2}{s^2 + \frac{\omega_n}{Q_P} + \omega_n^2}\right)$$

(2.4)

Using the principle of partial fraction expansion (PFE) [14], the overall output of the standard notch filter for a single frequency input at  $\omega_1$ , given by

$$Y_1(s) = \frac{As}{s^2 + \omega_1^2} + \frac{B}{s^2 + \omega_1^2} + \frac{Cs}{s^2 + 0.5\omega_n s + \omega_n^2} + \frac{D}{s^2 + 0.5\omega_n s + \omega_n^2}$$

(2.5)

The time domain response associated with  $Y_1(s)$  in (2.5) will be [13],

$$y_{1}(t) = (A\cos\omega_{1}t + B\sin\omega_{1}t + Ce^{-\frac{1}{4}\omega_{n}t}\cos\left(\frac{\sqrt{15}}{4}\omega_{n}t\right) + \frac{4\sqrt{15}}{15}De^{-\frac{1}{4}\omega_{0}t}\sin\left(\frac{\sqrt{15}}{4}\omega_{n}t\right)$$

(2.6)

where

$$A = \frac{0.5\omega_{n}\omega_{1}^{3} - 0.5\omega_{n}^{3}\omega_{1}}{\omega_{1}^{4} - 1.75\omega_{n}^{2}\omega_{1}^{2} + \omega_{n}^{4}}$$

(2.7a)

$$B = \frac{\omega_1^{5} - \omega_n^{2} \omega_1^{3} + \omega_n^{2} \omega_n^{2} \omega_1 + \omega_n^{2} \omega_1^{3}}{\omega_1^{4} - 1.75 \omega_n^{2} \omega_1^{2} + \omega_n^{4}}$$

(2.7b)

$$C = -\frac{0.5\omega_{n}\omega_{1}(\omega_{1}^{2} - \omega_{n}^{2})}{\omega_{1}^{4} - 1.75\omega_{n}^{2}\omega_{1}^{2} + \omega_{n}^{4}}$$

(2.7c)

$$D = \frac{\omega_n^2 \omega_1^3 - \omega_n^2 \omega_1^3 - 0.75 \omega_n^4 \omega_1 + \omega_1 \omega_n^4}{\omega_1^4 - 1.75 \omega_n^2 \omega_1^2 + \omega_n^4}$$

(2.7d)

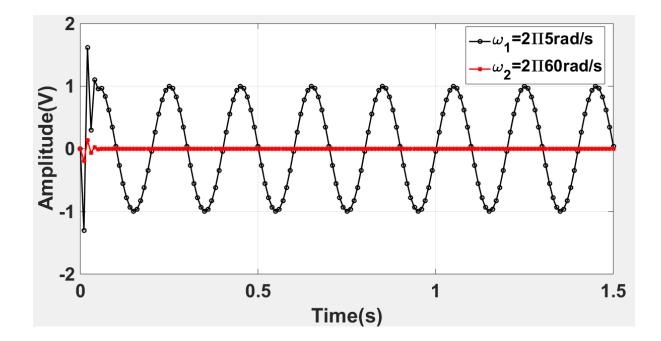

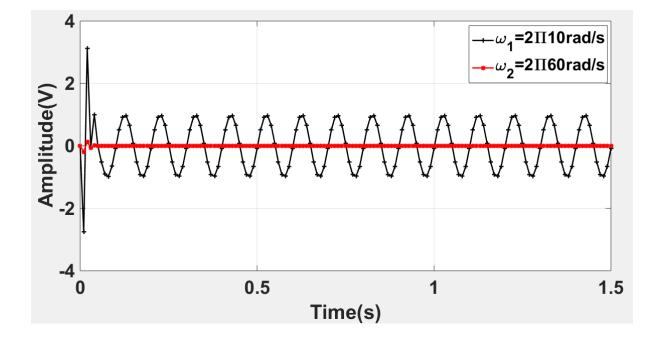

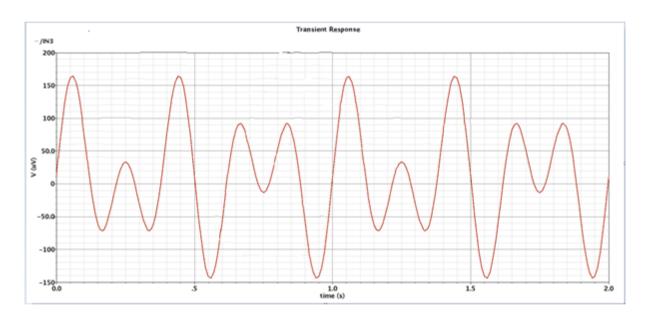

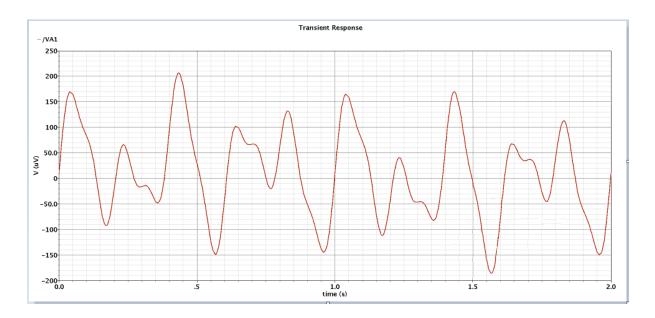

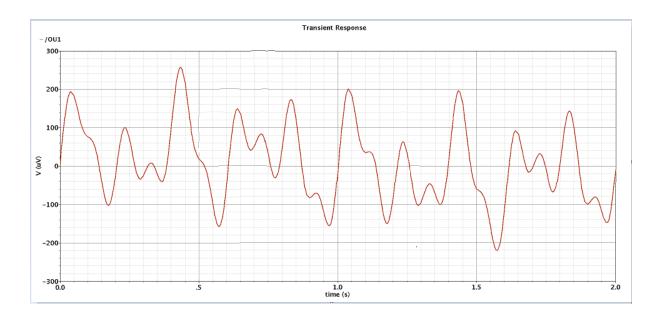

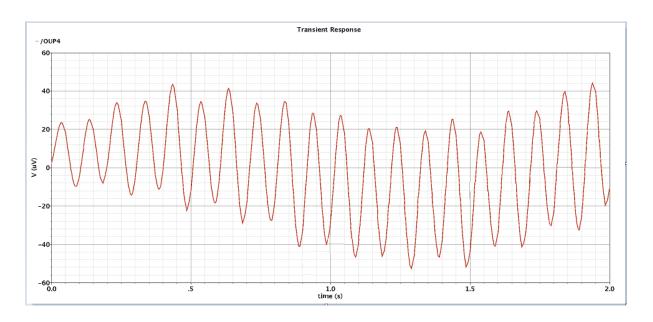

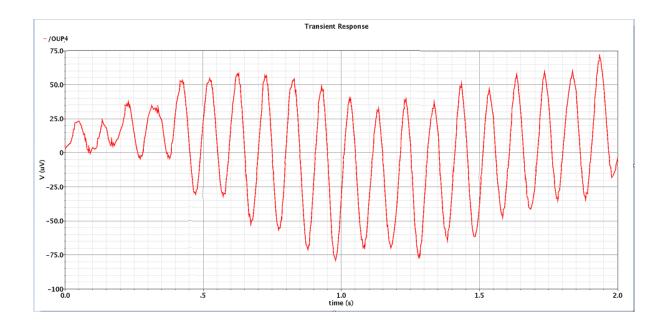

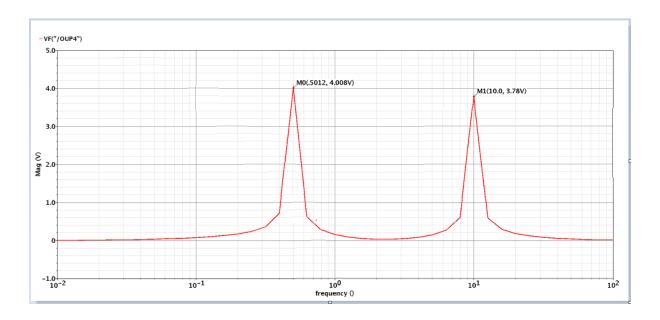

For a standard notch filter at 60 Hz (i.e.,  $\omega_p = \omega_n = 2 \times \pi \times 60$  rad/secs) and setting input signal values at  $\omega_2$  equal to  $2 \times \pi \times 60$  rad/secs and  $\omega_1$  equal to  $2 \times \pi \times 5$  rad/secs, and  $2 \times \pi \times 10$  rad/secs successively, we can obtain the time domain responses of the filter using MATLAB. The graphical results are shown in Figures 2.3 (a) and (b), respectively. The red lines correspond to the input signal at 60 Hz (i.e., the null frequency). The output at the notch frequency, (i.e., 60Hz) remains nearly zero, as expected.

Figure 2. 3(a). Output of notch filter

Figure 2. 3(b). Output of the notch filter

Thus, when input signal frequency is equal to the notch frequency, the signal is completely suppressed. However, if the signal frequency is not equal to the notch frequency, the signal is passed through the notch filter.

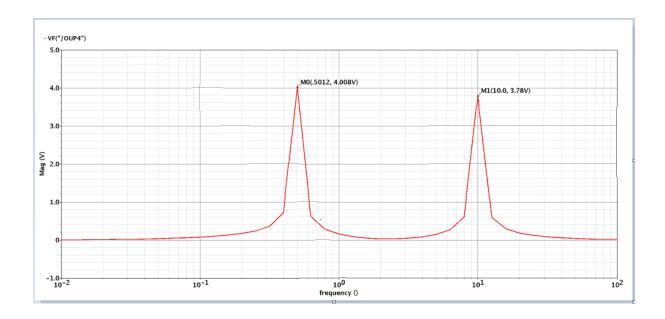

#### 2.4: Further Characteristics of a Notch Filters

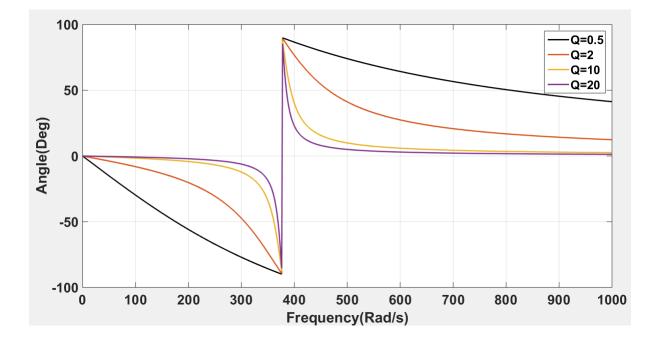

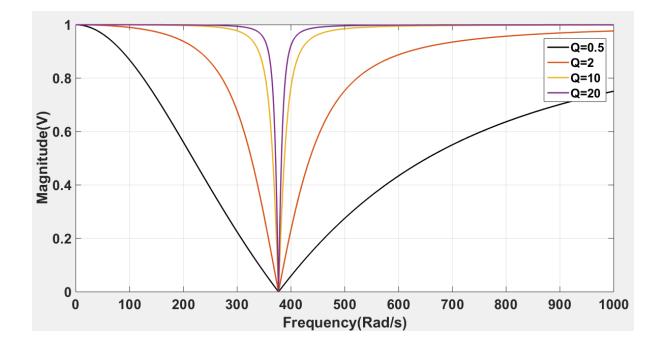

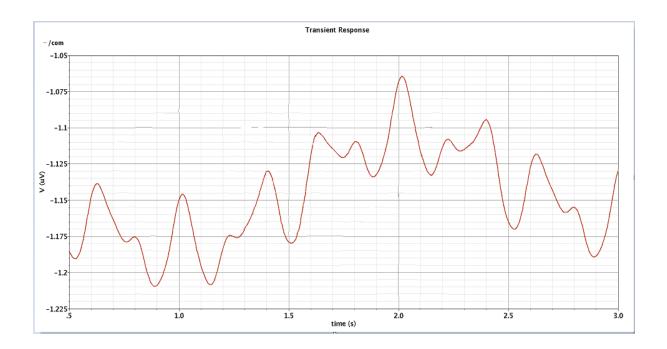

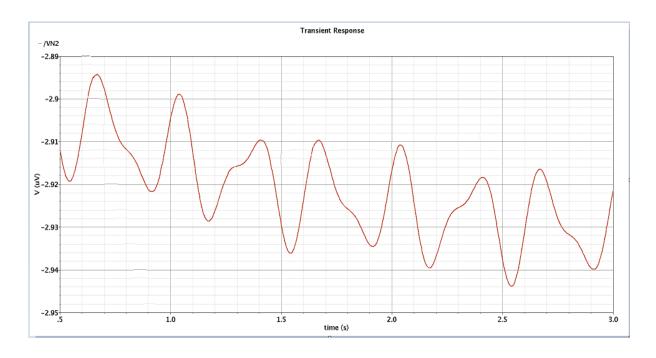

We have already seen that all input signals frequencies that are not equal to the notch frequency, the signals are transmitted. However, there are some changes in their magnitudes and in phases. These changes are small. For simple analysis we assume such changes as negligible. Figures 2.4(a)-(b) show the relative characteristics of a second order notch filter with different choices of  $Q_p$  values. The notch frequency is 60Hz ( $2\pi \times 60$  rad/s). For high  $Q_p$  (i.e., 10, 20) the phase angle remains close to zero over wider frequency spans on either side of the null frequency. Similarly, the magnitude remains close to 1 (i.e., zero loss) over wider frequency spans on either side of the null frequency spans on either side of the null frequency with higher values of  $Q_p$ . This is closer to an ideal behaviour.

Tables 2.2 and 2.3 present several numerical values of the phase angles associated with the graphs in Fig. 2.4(a) - (b).

Figure 2. 4(a). Phase response of notch filter (60Hz) at different QP values

Figure 2. 4(b). Magnitude response of notch filter (60Hz) at different  $Q_P$  values

| Frequency (Hz) | Phase Angles in degrees (°) |           |              |                     |

|----------------|-----------------------------|-----------|--------------|---------------------|

|                | Q <sub>p</sub> = 0.5        | $Q_p = 2$ | $Q_{p} = 10$ | Q <sub>p</sub> = 20 |

| 10             | -19.23                      | -4.80     | -0.90        | -0.48               |

| 20             | -38.10                      | -11.10    | -2.20        | -1.10               |

| 30             | -53.50                      | -18.70    | -3.60        | -1.82               |

| 40             | -69.20                      | -30.60    | -6.90        | -3.40               |

| 50             | -78.90                      | 56.60     | -16.90       | -8.60               |

| 60             | <u>+</u> 89.90              | ±88.20    | ±81.4        | ±78.20              |

| Table 2. 2. | Phase angle for | different values | of Q <sub>P</sub> | $(f_0 = 60 Hz)$ |

|-------------|-----------------|------------------|-------------------|-----------------|

|-------------|-----------------|------------------|-------------------|-----------------|

| 70  | 82.50 | 58.20 | 17.9 | 9.20 |

|-----|-------|-------|------|------|

| 80  | 70.80 | 35.20 | 8.70 | 4.40 |

| 90  | 67.00 | 30.40 | 6.85 | 3.40 |

| 100 | 61.80 | 25.10 | 5.00 | 2.60 |

Table 2. 3. Magnitudes for different values of  $Q_P$  ( $f_0 = 60$ Hz)

| Frequency (Hz) | Magnitude (V)        |                    |                     |                     |  |

|----------------|----------------------|--------------------|---------------------|---------------------|--|

|                | Q <sub>p</sub> = 0.5 | Q <sub>p</sub> = 2 | Q <sub>p</sub> = 10 | Q <sub>p</sub> = 20 |  |

| 10             | 1.00                 | 1.00               | 1.00                | 1.00                |  |

| 20             | 0.80                 | 1.00               | 1.00                | 1.00                |  |

| 30             | 0.60                 | 0.90               | 1.00                | 1.00                |  |

| 40             | 0.40                 | 0.89               | 0.98                | 0.99                |  |

| 50             | 0.20                 | 0.55               | 0.90                | 0.98                |  |

| 60             | 0.00                 | 0.00               | 0.0001              | 0.0002              |  |

| 70             | 0.20                 | 0.50               | 1.00                | 1.00                |  |

| 80             | 0.30                 | 0.80               | 1.00                | 1.00                |  |

| 90             | 0.40                 | 0.90               | 1.00                | 1.00                |  |

| 100 | 0.50 | 0.90 | 1.00 | 1.00 |  |

|-----|------|------|------|------|--|

| 100 | 0.50 | 0.90 | 1.00 | 1.00 |  |

The graphs in Fig. 2.4(a)-(b) show that signals away from the null frequency do not suffer substantial changes in magnitude or phase. So, these pass through the system unaltered. This can help estimating the range of signal frequencies that remain unaltered after passage through the notch filter. This objective is achieved by the ARTI subsystem shown in Fig.1.7 of the thesis. Details of the ARTI subsystem will be presented in Chapter 4 of the thesis.

# 2.5: Typical Application of a Notch Filter

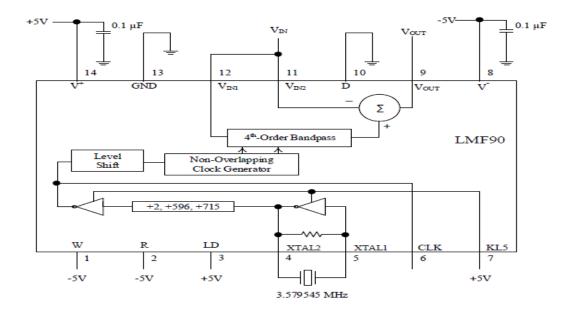

In most biomedical signal processing, notch filters are mostly used in the elimination of 50Hz/60Hz power line frequency signal especially in the processing of electrocardiogram and electroencephalogram data for clinical purposes. Power line noise get easily picked up through electrode cables, electrical devices and the patient being monitored [15].

For instance, Fig.2.5 demonstrates the use of a 4<sup>th</sup> order LMF90 elliptic notch filter [15] to suppress the 60Hz power line frequency signal present in a typical EEG data.

Figure 2. 5. Internal structure of LMF90 [15]

In contrast to eliminating the artifact signal data prior to the intended signal data with the subject in a hospital setup, it is possible to separate the artifact signal from the intended signal by notch filtering and then re-applying the artifact signal in the adaptive filtering loop to recover the intended signal. The recovered signal (i.e., EEG bands) can be Delta, Theta, or Alpha band etc. (as shown in Table 2.4[18]). The detailed design and analysis of how the notch filters are used in the proposed system (Fig.1.7) to retrieve the desired signals of interest will be addressed in the upcoming chapters of the thesis.

Table 2. 4. EEG rhythms with their corresponding frequency

| Rhythm            | Delta   | Theta | Alpha | Beta    | Gamma |

|-------------------|---------|-------|-------|---------|-------|

| Frequency<br>(Hz) | 0.5 - 4 | 4 - 8 | 8 -13 | 13 - 30 | ≥ 30  |

# 2.6: Conclusion

In this chapter, we introduced the basic features and analytical characteristics of a notch filter and its utility in isolating a certain signal from other signals. We also elaborated as to how different  $Q_p$  values of the notch filter affect the phase of the signals at frequencies other than the notch frequency. This will help us to develop a novel filtering system to eliminate the artifact signals in the mixture of desired and artifact signals. In the coming chapters, the analysis and implementation of the various subsystems shown in Fig. 1.7 using the modern CMOS technological process (TSMC 0.18mircon CMOS) will be addressed.

# **Chapter 3**

# **Amplifiers in the Proposed System**

The system proposed in Chapter 1 has several amplifiers. All these special-use amplifiers are realized using a basic Operational Amplifier (OPAMP) with additional circuitry to meet the special requirements. In this chapter, we will present the case of a typical OPAMP that has been introduced in [19] with application to EEG signals processing. This chapter also focuses on the analysis and design of the various typical amplifiers using CMOS180 technology. The simulation results of the various amplifiers are included to validate and confirm their operations.

#### **3.1: Operational Amplifiers**

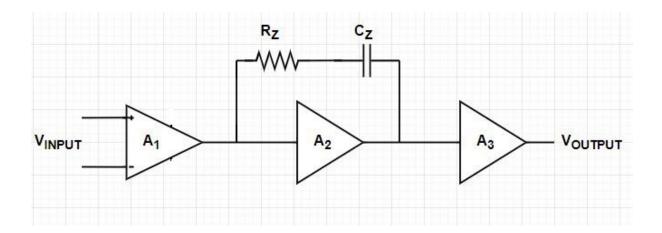

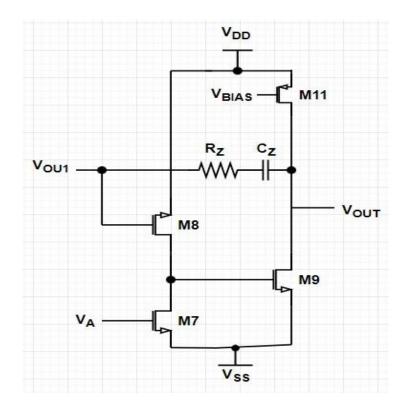

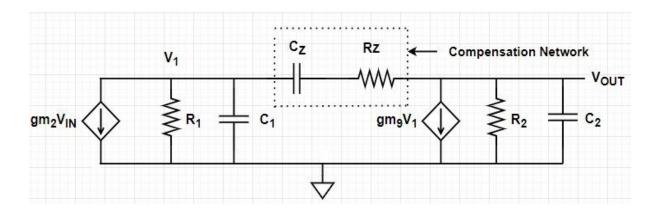

The operational amplifier is the principal component in designing and implementing most of the analog circuits for signal processing. Some of the analog signal processing functions are amplification, integration, summation, etc. In this section, we will elaborate on the architecture, characteristics, and implementation of general two-stage operational amplifiers. The general architecture of operational amplifiers mostly consists of a differential stage ( $A_1$ ), gain stage( $A_2$ ), and sometimes a unity gain output ( $A_3$ ) stage as illustrated in Figure 3.1. Generally, operational amplifiers are designed to have very high differential input resistance and very low output resistance.

Figure 3.1. Schematic representation of a two-stage OPAMP

The differential stage is mostly designed and implemented to have a high Common Mode Rejection Ratio (CMRR) to reject any interference signal common between the input terminals before it is further subjected to the gain stage for amplification. The introduction of the resistor  $(R_Z)$  and capacitor  $(C_Z)$  connected between the output of the differential stage and the gain stage output represents a compensational circuit for phase stability of the operational amplifiers.

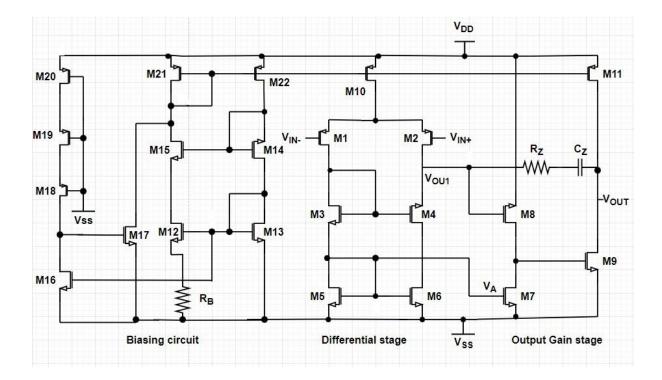

#### **3.2: Design of the Operational Amplifier (OPAMP)**

In this section, we are going into the detailed design and implementation of the operational amplifier used in the proposed work, as has been addressed in [17]. The operational amplifier is implemented and simulated in CMOS18 (180 nano meter) technology. The schematic representation of the operational amplifier is shown in Figure 3.2 [17]. The operational amplifier comprises of three parts that include the bias circuit, the differential input stage, and the output gain stage. The OPAMP works from the voltage supplies  $V_{DD} = +900$ mV, and  $V_{SS} = -900$ mV. Table 3.1(a)-(e) present the AC parameters of the transistors M2, M4, M6, M9 and M11, respectively. These parameters are needed to calculate the gains of the differential input stage and of the output stage of the OPAMP. We denote the

transconductance and the drain to source resistance of the MOS transistor  $M_i$ , respectively (i = 1,2,3 .....22) by  $gm_i$  and  $r_{dsi}$ , respectively.

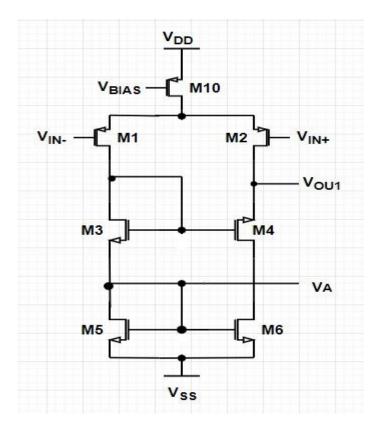

Figure 3. 2. Schematic representation of the OPAMP [17]

Table 3. 1. AC Parameters of transistors (a) M2, (b) M4, (c) M6, (d) M9 and (e) M11

|         |         |         |         | hata    | 250 0      |

|---------|---------|---------|---------|---------|------------|

| beta    | 85.74u  | beta    | 352.4u  | beta    | 359. 2u    |

| cbtot   | 62.11f  | cbtot   | 43.96f  | cbtot   | 54.11f     |

| cdtot   | 5.212f  | cdtot   | 3.707£  | cdtot   | 4.048f     |

| cqd     | 2.143f  | cgd     | 1.792f  | cgd     | 1.81f      |

| cgs     | 168.7f  | cgs     | 88.48f  | cgs     | 84.39f     |

| cqtot   | 182.1f  | cgtot   | 108.9f  | cqtot   | 109.9f     |

| cstot   | 204.3f  | cstot   | 115.3f  | cstot   | 118f       |

| gam-eff | 468.1m  | gam-eff | 490.6m  | gam-eff | 496.2m     |

| gds     | 21.53n  | gds     | 22. 9n  | gds     | 25.51n     |

| gn      | 11.56u  | gn      | 18.93u  | gn      | 18.82u     |

| ցուն    | 3.443u  | ցուն    | 4.495u  | gnb     | 5.461u     |

| ibd     | 1.888a  | ibd     | -27.13a | ibd     |            |

| ibs     | 1.884a  | ibs     | -2.215a |         | -2.226a    |

| id      | -1.125u | id      | 1.125u  | ibs     | -969.7e-30 |

| vbs     | 233.5n  | vbs     | -479.8m | id      | 1.125u     |

| vds     | -481.7n | vds     | 605m    | vbs     | 0          |

| vdsat   | -165.2m | vdsat   | 104m    | vds     | 479.8m     |

| vgs     | -666.5m | vqs     | 604.9m  | vdsat   | 102.4m     |

| vod     | -155.4n | vod     | 38.22m  | vgs     | 479.8m     |

| vth     | -511.1m | vth     | 566.6m  | vod     | 37.13m     |

|         |         |         | 000.04  | vth     | 442.6m     |

(a)

**(**b)

(c)

| beta    | 713.5u     | beta    | 116. 1u |

|---------|------------|---------|---------|

| cbtot   | 103.9f     | cbtot   | 100.1f  |

| cdtot   | 6.795f     | cdtot   | 13.08f  |

| ogd     | 3.49f      | cqd     | 3.46f   |

| cgs     | 165.9f     | cgs     | 226.5f  |

| cgtot   | 215.1f     | cqtot   | 245.3f  |

| cstot   | 231.7f     | cstot   | 284.4f  |

| gam-eff | 490.2m     | gam-eff | 475.1n  |

| gds     | 41.91n     | gds     | 89.65n  |

| gm      | 38.1u      | gn      | 19.38u  |

| ցուն    | 11.04u     | ցուծ    | 6.357u  |

| ibd     | -213.8p    | ibd     | 21.32a  |

| ibs     | -2.679e-27 | ibs     | 461.7y  |

| id      | 2.29u      | id      | -2.291u |

| vbs     | 0          | vbs     | 0       |

| vds     | 1.426      | vds     | -374.1n |

| vdsat   | 102.8m     | vdsat   | -195.6n |

| vgs     | 480.1m     | Vqs     | -641.1n |

| vod     | 37.71m     | vod     | -200.5n |

| vth     | 442.4m     | vth     | -440.6n |

|         |            |         |         |

|         |            |         |         |

(d)

(e)

# **3.2.1: Differential input stage**

The PMOS transistors M1 and M2 form the differential input of the operational amplifier, which has the capability of suppressing common-mode interference signals and reducing the harmonic distortions that might be generated. The cascode structure formed by NMOS transistors M3 to M6 in the first stage helps in boosting the gain [17]. The differential input stage is a single-ended output stage providing a differential to single-ended conversion as shown in Figure 3.3.

Figure 3. 3. Schematic representation of the differential input stage

Using nodal analysis at low frequency, the amount of gain  $A_{V1}$  associated with differential

input stage is given by

$$A_{V1} = \frac{V_{OU1}}{V_{IN}} = -gm_2R_1$$

(3.1a)

where

$$R_{1} = r_{ds2} ||r_{ds4} + \frac{1}{gm_{6}} = \frac{r_{ds4} \times r_{ds2}}{r_{ds4} + r_{ds2}} + \frac{1}{gm_{6}}$$

(3.1b)

$$V_{IN} = V_{IN+} - V_{IN-}$$

(3.1c)

From Table 3.1(a) and (b), we have

$$r_{ds2} = \frac{1}{g_{ds2}} = \frac{1}{21..54 \times 10^{-9}} = 46.425 M\Omega$$

$$r_{ds4} = \frac{1}{g_{ds4}} = \frac{1}{22.9 \times 10^{-9}} = 43.687 M\Omega$$

g<sub>ds4</sub>

$$R_1 = \frac{r_{ds2} \times r_{ds4}}{r_{ds2} + r_{ds4}} + \frac{1}{gm_6} = 22.56M\Omega$$

Hence,

$$A_{V1} = 22.56 \times 10^6 \times 11.56 \times 10^{-6} = 260.79 \,\text{V/V} \tag{3.2}$$

# 3.2.2: Output gain stage

The output gain stage is a common source amplifier, as shown in Figure 3.4, principally designed to further enhance the gain of the operational amplifier. Transistors M7 and M8 play a major role in the output stage by reducing the overdrive voltage at the output of M9. The transistors M10 and M11 in the differential and the output stage respectively form the current sink to produce proper bias [17]. The elements  $R_Z$  and  $C_Z$  form the compensation circuit, which is responsible for the phase margin stability. The detailed design of the compensation circuit will be addressed in Section 3.2.4.

Figure 3. 4. Schematic representation of the output gain stage

The gain provided by the output gain stage at low frequency is given by

$$A_{V2} = \frac{V_{OUT}}{V_{OU1}} = +gm_9R_2$$

(3.3a)

where

$$R_2 = r_{ds11} || r_{ds9} = \frac{r_{ds9} \times r_{ds11}}{r_{ds9} + r_{ds11}}$$

(3.3b)

From Table 3.1(d) and (e), we also have

$$r_{ds9} = \frac{1}{g_{ds9}} = \frac{1}{41.91 \times 10^{-9}} = 23.86M\Omega$$

$$r_{ds11} = \frac{1}{g_{ds11}} = \frac{1}{89.65 \times 10^{-9}} = 11.15M\Omega$$

$$R_2 = \frac{r_{ds9} \times r_{ds11}}{r_{ds9} + r_{ds11}} = 7.59M\Omega$$

$$A_{v2} = 7.59 \times 10^6 \times 38.1 \times 10^{-6} = 289.18 \,\text{V/V}$$

(3.4)

### **3.2.3:** Overall gain of the OPAMP (at low frequencies)

The overall gain  $(A_V)$  of the operational amplifier shown in Fig.3.2 is given by

$$A_{v} = \frac{V_{OUT}}{V_{IN}}$$

$$A_{v} = \frac{V_{OU1}}{V_{IN}} \times \frac{V_{OUT}}{V_{OU1}} = A_{v1} \times A_{v2}$$

(3.5)

Using the values of  $A_{v1}$  and  $A_{v2}$  from (3.2) and (3.4) respectively, we have

$$A_{vdB} = 20 \log(289.18 \times 260.79) = 97.58 dB.$$

### **3.2.4:** Design of the compensation circuit

Since the two-stage architecture has the disadvantage of having high impedances at the output of the differential stage ( $V_{OU1}$ ) and the output gain stage ( $V_{OUT}$ ), this will deteriorate the

phase margin of the OPAMP [19]. To rectify this situation, a compensation circuit is introduced with a series combination of  $C_Z$  and  $R_Z$ , as shown in Figure 3.5. The detailed analysis is presented below.

Figure 3. 5. A small signal model of the OPAMP for compensation analysis [19]

Consider the small signal model of the two stage OPAMP shown in Fig. 3.5, initially, we assume  $R_Z = 0$  and perform nodal analysis concerning the input and output. The following transfer function is obtained [19], [20]:

$$\frac{V_{OUT}}{V_{IN}} = \frac{gm_2 gm_9 R_1 R_2 (1 - \frac{sc_Z}{gm_6})}{1 + sa + s^2 b}$$

(3.6)

where  $R_1$  and  $R_2$  have already been defined in (3.1b) and (3.3b), and

$$a = (c_2 + c_Z)R_2 + (c_1 + c_Z)R_1 + gm_9R_1R_2c_Z$$

(3.7a)

$$b = R_1 R_2 (c_1 c_2 + c_1 c_2 + c_2 c_2)$$

(3.7b)

$$c_1 = c_{db3} + c_{db5} + c_{gs6}$$

(3.7c)

$$c_2 = c_{db6} + c_{db1}$$

(3.7d)

In the above equations,  $C_{db}$ ,  $C_{gs}$ , and  $C_{gd}$  are the drain to bulk, gate to source, the gate to drain capacitances of the transistors (i.e., M2, M4 and M9) under consideration respectively. It is

possible to find approximate equations for the two poles based on the assumption that the poles are real and widely separated. This assumption allows us to express the denominator of (3.6) as [20]

$$D(s) = \left(1 + \frac{s}{\omega_{p1}}\right) \left(1 + \frac{s}{\omega_{p2}}\right)$$

(3.8)

The dominant pole,  $\omega_{p1}$  is given by

$$\omega_{p1} = \frac{1}{gm_9R_1R_2C_Z} \tag{3.9a}$$

whereas the non-dominant pole,  $\omega_{p2},$  is given by

$$\omega_{p2} = \frac{gm_9}{c_1 + c_2} \tag{3.9b}$$

A resistor ( $R_Z$ ) is connected in series to the Miller capacitor ( $C_Z$ ) to move the right half-plane zero into the left half-plane to cancel the non-dominant pole,  $\omega_{p2}$ .

The zero is now determined by the relationship,

$$\omega_{\rm z} = \frac{-1}{c_{\rm Z}(\frac{1}{\rm gm_9} - \rm R_Z)}$$

(3.10)

Therefore, we can choose (3.10) to eliminate the right half-plane zero altogether.

$$R_Z \ge \frac{1}{gm_9} \tag{3.11}$$

$$c_{Z} = (2c_{gd2} + c_{db2}) + (2c_{gd4} + c_{db4}) + 2c_{gs9}$$

(3.12)

From Table 3.1 (a), (b) and (d) we have,

$$c_{Z} = (2 \times 2.143 \times 10^{-15} + 5.21 \times 10^{-15}) + (2 \times 1.792 \times 10^{-15} + 3.70 \times 10^{-15}) + 2 \times 165.5 \times 10^{-15} = 374.65 \text{fF}.$$

From (3.11), we have

$$R_{\rm Z} \ge \frac{1}{30.13 \times 10^{-6}} \ge 33.20 {\rm K}\Omega$$

The concept of designing and implementing compensation circuits (lead compensation) in a two-stage operational amplifier for phase margin stability has been adopted from [19], [20].

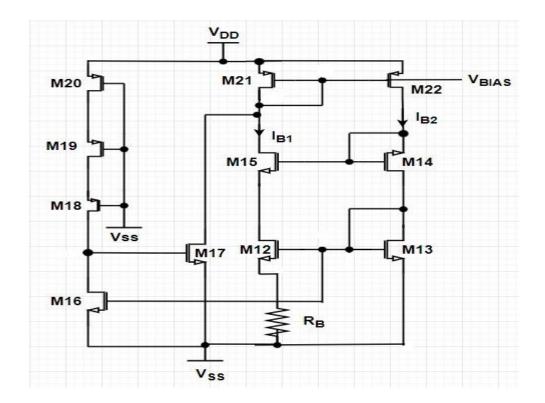

#### 3.2.5: Biasing and start up circuit

Bias circuits are principal components of analog circuits for producing voltage or current references. The bias and start up circuit shown in Figure 3.6 is composed of transistors M12 to M22 and  $R_B$ , while the start-up circuit consists of transistors from M16 to M20. The transistors M21 and M22 form the current mirror to ensure that their DC drain currents are forced to be equal. The cascode structure of the bias circuit reduces the channel length modulation effect and ensures that the bias current is accurately equal on both sides (i.e.,  $I_{B1}$  and  $I_{B2}$  as shown in Fig.3.6) [17].

Figure 3. 6. Biasing circuit [17]

A start up circuit is required to bring up the bias current from zero current to its normal operating point. The start-up circuit is no longer used once the bias circuit is operating properly [18]. The aspect ratio of the transistors M18 to M20 is chosen carefully to provide very high channel resistance. Similarly, the aspect ratios of M16 and M17 are also chosen properly to provide very low resistance to the channels. Hence, there will be zero current in the start-up circuit when the bias circuit is functioning properly. The concept of getting very high and low channel resistances using MOS is addressed Section 3.3. To get appropriate bias voltage ( $V_{BIAS} = 258.9$ mV), the aspect ratio of the transistors and  $R_B$  (1K) of the bias circuit is properly chosen to set the current  $I_B = 1.17\mu$ A.

#### 3.3: Realization of Passive Resistors from MOS Transistors

Passive resistors occupy a very large area in integrated circuit (IC) design. Thus, passive resistors are not preferable in IC, since they cause compatibility problem in modern integrated circuit design.

However, the passive resistors  $R_z$  and  $R_B$  present in the compensation and the bias circuit are replaced by MOS transistors by choosing suitable aspect ratios (W/L) of the transistors. MOS transistors have four regions of operation, which include cut-off, subthreshold, linear, and saturation region.

The MOS transistors used to replace  $R_z$  and  $R_B$  were set to operate under linear region by applying a reasonable bias voltage to its gate terminal. Further details in this respect are provided below.

The classical model equation for n-channel transistor operating in the triode region is given by

$$I_{DS} = \mu_n C_{OX} W / (V_{ov} - 1 / 2 V_{DS}) V_{DS} \quad V_{DS} < V_{GS} - V_{TH}$$

(3.13)

where  $\mu_n$  is the carriers' mobility through the transistor channel, W is the width of the transistor, L is the length of the channel,  $V_{DS}$  is the drain to source voltage,  $V_{GS}$  is the gate to source voltage of the transistor, and  $V_{TH}$  is the threshold voltage of the transistor.

Considering that a small  $V_{DS}$  is used, then we can model the channel resistance  $(r_{ds})$  of the transistor by

$$r_{\rm ds} = \left(\frac{\partial I_{\rm D}}{\partial V_{\rm DS}}\right)^{-1} \tag{3.14}$$

Hence, in the linear region we can define the effective channel resistance  $(r_{ds})$  between the drain and the source of an n-channel transistor as

$$r_{ds} = \frac{L}{\mu_n C_{OX} W(V_{GS} - V_{TH})}$$

(3.15)

It can be noticed from (3.15) that,  $r_{ds}$  is mainly dependent on the aspect ratio of the transistor, if a fixed  $V_{GS}$  is applied. Thus, the resistance of any transistor increases when the aspect ratio decreases and vice versa.  $\mu_n C_{OX}$  is the process transconductance parameter value of the transistor and  $V_{TH}$  is always a constant value mainly depending on the CMOS technology being used.

#### 3.4: Transistors Size Data and the Performance Parameters of the OPAMP

In this section, we present the various design parameters such as the aspect ratio of the transistors, power supply, etc., and the simulated results including the voltage gain, CMMR, phase margin, etc. of the operational amplifier used. The performance parameters and results are presented in Tables 3.2 and 3.3, respectively. The overall configuration of the OPAMP has been shown in Fig.3.2.

| Transistors                                                 | W(microns) | L(microns) | w/L                             |  |  |

|-------------------------------------------------------------|------------|------------|---------------------------------|--|--|

| M1, M2                                                      | 6.1        | 5          | <sup>6.1</sup> / <sub>5</sub>   |  |  |

| M3-M6                                                       | 4.9        | 5          | <sup>4.9</sup> / <sub>5</sub>   |  |  |

| M7, M8                                                      | 1          | 5          | <sup>1</sup> / <sub>5</sub>     |  |  |

| M9                                                          | 9.6        | 5          | <sup>9.6</sup> / <sub>5</sub>   |  |  |

| M10, M11                                                    | 8          | 5          | <sup>8</sup> / <sub>5</sub>     |  |  |

| M12, M13                                                    | 4.9        | 5          | <sup>4.9</sup> / <sub>5</sub>   |  |  |

| M14-M17                                                     | 4.5        | 0.5        | <sup>4.5</sup> / <sub>0.5</sub> |  |  |

| M18-M20                                                     | 0.5        | 17         | <sup>0.5</sup> / <sub>17</sub>  |  |  |

| M21, M22                                                    | 2          | 5          | <sup>2</sup> / <sub>5</sub>     |  |  |

| $V_{DD} = 900 \text{mV}$ , $V_{SS} = -900 \text{mV}$        |            |            |                                 |  |  |

| $C_Z = 0.376 pF$ , $R_Z = 32.2 K\Omega$ , $R_B = 1 K\Omega$ |            |            |                                 |  |  |

Table 3. 2. Design parameters for the OPAMP shown in Figure 3.2

| Parameters            | Values   |

|-----------------------|----------|

| Voltage Gain          | 97.7 dB  |

| Unity Gain Bandwidth  | 30.2 MHz |

| Phase Margin          | 53.5 deg |

| CMRR                  | 95.26 dB |

| Output Offset Voltage | 241.1 mV |

| Power Dissipation     | 13.61 µW |

Table 3. 3. Simulated results of the OPAMP

#### **3.5: Summing Amplifier**

In order to demonstrate the effectiveness of our proposed system to eliminate the artifacts, we use a summing amplifier to add artifact signals to the intended EEG signals to simulate a natural mixture of physiological signals. The summing amplifier emulates the sensor node that receives the intended EEG signal and the artifact signals as a natural mixture. In our case, a non-inverting summing amplifier is preferable to ensure that the combined output signal (contaminated EEG signal) is in phase with the input signals (artifact and intended signals).

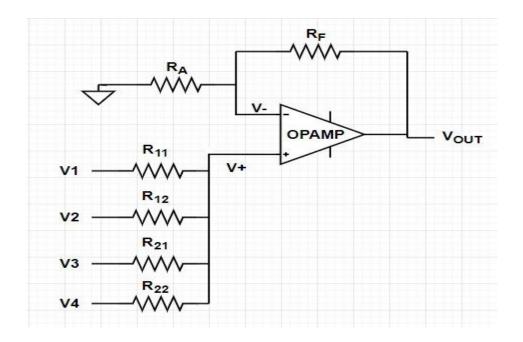

In the case of a non-inverting summing amplifier, the inputs are applied to the non-inverting terminal (+) while the required negative feedback and gain ( $A_V$ ) is achieved by feeding back some portion of the output signal to the inverting terminal (-) of the OPAMP as shown in Fig 3.7 [21].

Figure 3. 7. Summing amplifier

If we consider four inputs to the non-inverting summing amplifier as shown in Figure 3.7, the current passing into the input terminal can be written as

$$I_{R11} + I_{R12} + I_{R21} + I_{R22} = 0 (3.16)$$

$$\frac{V_1 - V_+}{R_{11}} + \frac{V_2 - V_+}{R_{12}} + \frac{V_3 - V_+}{R_{21}} + \frac{V_4 - V_+}{R_{22}} = 0$$

(3.17)

If we set all input resistances to be equal i.e.,  $R_{11} = R_{12} = R_{21} = R_{22} = R$ , then (3.17) can be simplified as

$$V_{+} = \frac{V_{1} + V_{2} + V_{4} + V_{4}}{4} \tag{3.18}$$

The standard equation for voltage gain of a non-inverting summing amplifier is given as

$$A_{v} = \frac{V_{OUT}}{V_{IN}} = \frac{V_{OUT}}{V_{+}} = 1 + \frac{R_{F}}{R_{A}}$$

(3.19)

$$V_{OUT} = \left(1 + \frac{R_F}{R_A}\right) \left(\frac{V_1 + V_2 + V_3 + V_4}{4}\right)$$

(3.20)

For the four inputs non-inverting summing amplifier configurations shown in Figure 3.7, setting the closed-loop voltage gain ( $A_V$ ) to 4 V/V such that  $R_F = 3R_A$  will make  $V_{OUT}$  equal to the sum of four inputs voltages  $V_1$ ,  $V_2$ ,  $V_3$ , and  $V_4$ .

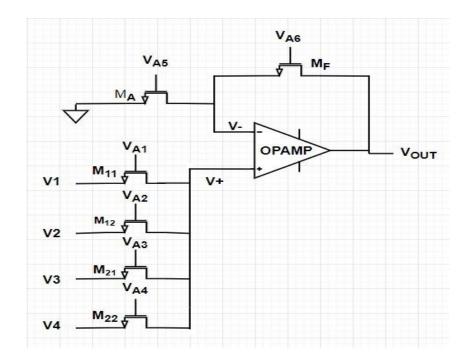

In our case, we set  $R_{11} = R_{12} = R_{21} = R_{22} = R = 1K\Omega$ . In (3.20),  $R_A$  and  $R_F$  are also set to 1K $\Omega$  and 3K $\Omega$ , respectively, to ensure that the input signals combine appropriately at the output of the summer amplifier. In CMOS implementation of the summing amplifier, the passive resistances shown in Figure 3.7 are replaced by NMOS transistors operating under the triode region as discussed under Section 3.3. The exact channel resistances are obtained by varying the aspect ratio and applying a reasonable voltage supply to the various gate terminals of the MOS transistors. Figure 3.8 shows a schematic representation of the CMOS summing amplifier.

Figure 3. 8. CMOS Summing amplifier

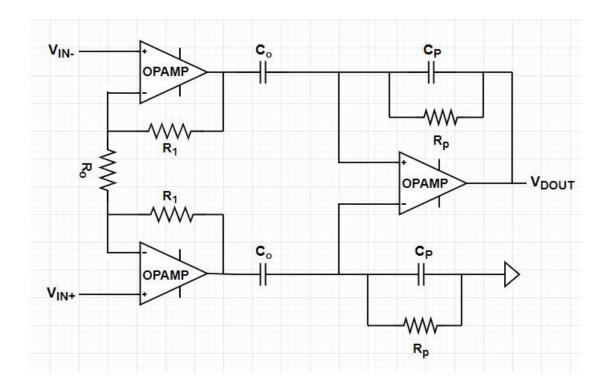

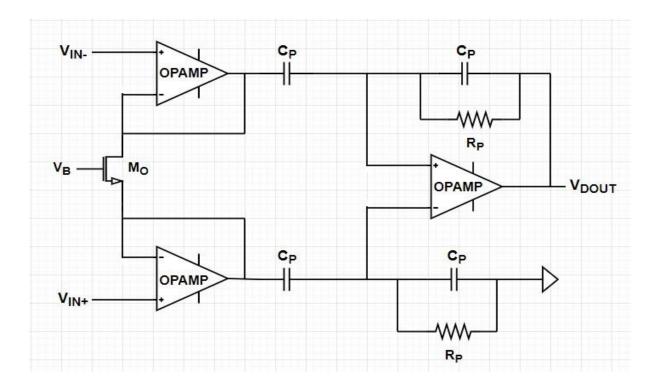

In the above CMOS summing amplifier design, equal voltage supply  $(V_A)$  is applied to various gate terminals of the NMOS transistors such that  $V_{A1} = V_{A2} = V_{A3} = V_{A4} = V_{A5} =$   $V_{A6} = V_A$  as shown in Figure 3.8. The design parameters of the CMOS summing amplifier are listed in Table 3.4.