# CRITICAL DESIGN ISSUES FOR GALLIUM ARSENIDE VLSI CIRCUITS

# E. BUSHEHRI

# Ph.D.

### The copying of this thesis in any way or form is illegal. YOU MUST NOT COPY DISSERTATIONS

Anybody found making illegal copies of any part of this thesis will be dealt with in accordance to University regulations.

Your borrowing rights will be revoked.

م الله بيغ عاديتها المالية الله ا

Please sign the copyright declaration below.

The copyright of this thesis rests with the author or the University. No part will be photocopied or published without prior written consent from one of the above. Any quotation or information derived from this thesis will be fully acknowledged and fully cited and that failure to do so will constitute plagiarism. I agree to abide by this declaration.

| Date      | <u>Name</u>                            | <u>Signature</u>                      | <u>Student</u><br>ID                  |

|-----------|----------------------------------------|---------------------------------------|---------------------------------------|

|           |                                        |                                       |                                       |

|           | ······                                 |                                       |                                       |

|           | ×                                      |                                       |                                       |

|           |                                        |                                       |                                       |

|           | /<br>                                  |                                       |                                       |

|           | ······································ |                                       |                                       |

|           |                                        |                                       |                                       |

|           |                                        |                                       | · · · · · · · · · · · · · · · · · · · |

| . <u></u> |                                        |                                       | ·                                     |

|           |                                        |                                       |                                       |

|           |                                        |                                       |                                       |

|           |                                        |                                       |                                       |

|           |                                        |                                       |                                       |

|           | · · · · · · · · · · · · · · · · · · ·  |                                       |                                       |

|           |                                        |                                       |                                       |

|           |                                        |                                       |                                       |

|           |                                        |                                       |                                       |

|           |                                        |                                       | <br>                                  |

|           |                                        |                                       |                                       |

|           |                                        |                                       |                                       |

|           |                                        | · · · · · · · · · · · · · · · · · · · |                                       |

|           |                                        | · · · · · · · · · · · · · · · · · · · |                                       |

|           |                                        | · · · · · · · · · · · · · · · · · · · |                                       |

|           |                                        | <u> </u>                              | <u> </u>                              |

MX 7187119 5 The Sheppard Library Middlesex University The Burroughs London NW4 4BT 020 8411 5852 http://library.mdx.ac.uk PGED MIDDLESEX UNIVERSITY SHORT LOAN COLLECTION . .. 19-14 1.17 7110/93 20/5/96 15/10/02 (14.28) LF/26 Lib/3

### CRITICAL DESIGN ISSUES FOR GALLIUM ARSENIDE VLSI CIRCUITS

#### A thesis submitted to the Council for National Academic Awards

by

### Ebrahim Bushehri

### in partial fulfilment of the requirements for the degree of Doctor of Philosophy

#### April 1992

Microelectronics Centre, Middlesex Polytechnic

|                       | y9430558          |

|-----------------------|-------------------|

| Site                  |                   |

| HE BY                 | LIBRARY           |

| Accession<br>No.      | 71871195          |

| Class<br>No.          | 621.395 BUS       |

| Special<br>Collection | Thesis<br>Greenen |

-

ABSTRACT

### ACKNOWLEDGEMENTS

#### GLOSSARY

### **CHAPTER 1** Introduction

- 1.1 Review of Silicon Technology

- 1.2 Limitations of Silicon Technology

for High Speed Applications

- 1.3 Gallium Arsenide as an Alternative Substrate

- 1.4 Current Developments and Future Trends

- 1.5 Scope of this Thesis

### **CHAPTER 2 GaAs Device Fabrication**

### and Modelling

2.1 Suitable Devices for VLSI Imple

2.2 GaAs MESFET Structure

2.3 Planar Processing Steps for GaA

### INDEX

|             | ۰. |

|-------------|----|

| lementation | 15 |

|             | 16 |

| As MESFETs  | 17 |

| 2.4 Self-Aligned Gate Process Technology              | 20 |

|-------------------------------------------------------|----|

| 2.5 GaAs MESFET Design Rules and Layer Representation | 22 |

| 2.6 An Appropriate Device Model for GaAs VLSI         | 22 |

| 2.7 Important Effects Included in the Device Model    | 26 |

| 2.8 Interconnect Modelling                            | 27 |

### **Chapter 3 MESFET Logic Families**

### for GaAs VLSI Circuits

| 3.1 Types of MESFET Logic Gate                         | 30 |

|--------------------------------------------------------|----|

| 3.2 Normally-ON Logic Gates                            | 30 |

| 3.3 Normally-OFF Logic Gates                           | 34 |

| 3.4 Suitable Logic Gates for GaAs VLSI                 | 37 |

| 3.5 First Order Design of DCFL and SDCFL Gates         | 37 |

| 3.6 Definition of Design Parameters                    | 41 |

| 3.7 Detailed Analysis of DCFL and SDCFL Gates          | 43 |

| 3.8 Design of Buffering Schemes for GaAs VLSI Circuits | 49 |

### **CHAPTER 4 Analysis of Adder Circuits**

### for GaAs VLSI Implementation

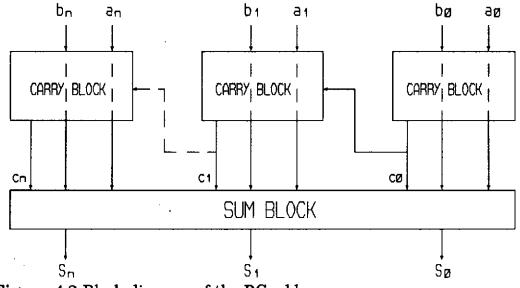

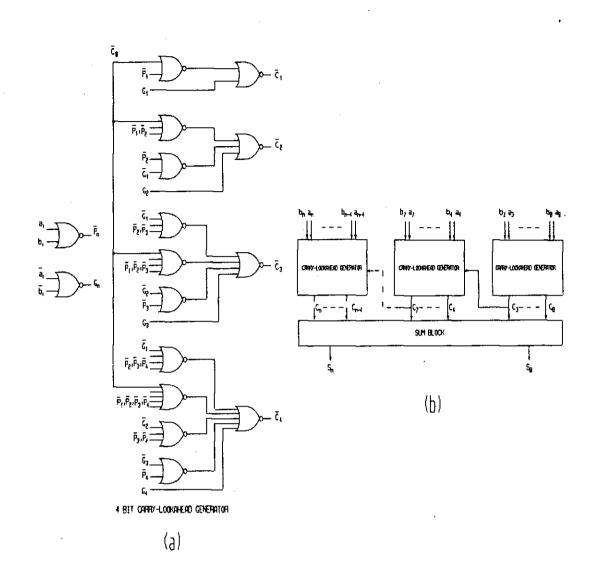

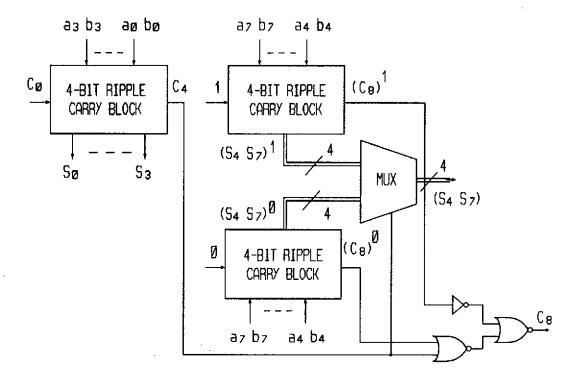

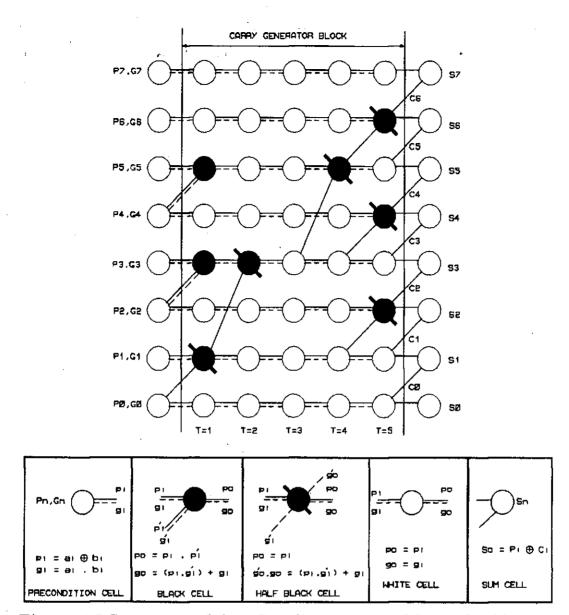

| 4.1 Adder Design Approach                      | 59 |

|------------------------------------------------|----|

| 4.2 Types of Adder                             | 62 |

| 4.3 Evaluation of Adder Circuits for GaAs VLSI | 69 |

| 4.4 Summain of Important Points                | 77 |

### CHAPTER 5 A High Speed GaAs Multiplier

| 5.1 A Suitable Multiplier for GaAs Implementation | 81 |

|---------------------------------------------------|----|

| 5.2 The Algorithm                                 | 82 |

| 5.3 The Overall Architecture                      | 85 |

| 5.4 Implementation Issues                         | 94 |

| 5.5 Performance Evaluation                        | 96 |

## CHAPTER 6 A Novel Design and Layout Approach for GaAs VLSI Circuits

| 6.1 Architectural Decomposition of GaAs VLSI Circuits  | 99  |

|--------------------------------------------------------|-----|

| 6.2 Ring Notation for the Layout of GaAs VLSI Circuits | 100 |

| 6.3 Important Issues in Ring Notation Layouts          | 106 |

| 6.4 Design of BLC Adders using the Ring Notation       | 110 |

| 6.5 Evaluation of the Ring Notation Adders             | 115 |

| and Multiplier Circuits                                |     |

#### **CHAPTER 7 Conclusions**

| 7.1 Summary and Conclusions | 119 |

|-----------------------------|-----|

| 7.2 Recommendations         | 124 |

### Appendices

| A | Layer Representation and Design Rules        | 126 |

|---|----------------------------------------------|-----|

| в | Derivation of Gate Delay Formula             | 138 |

| С | Brief Description of the Design Tool         | 141 |

| D | CPS and CPW Models for the Estimation of     | 143 |

|   | the Inductances in the Supply Rails          |     |

| E | Logic and Ring Notation Diagrams of the DCFL | 147 |

|   | and SDCFL BLC Adders                         |     |

References

### Critical Design Issues for Gallium Arsenide VLSI Circuits

#### Abstract

The aim of this research was to design and evaluate various Gallium Arsenide circuit elements such as logic gates, adders and multipliers suitable for high speed VLSI circuits. The issues addressed are the logic gate design and optimisation, evaluation of various buffering schemes and the impact of the algorithm on adder and multiplier performance for digital signal processing applications. This has led to the development of a design approach to produce high speed and low power dissipation Gallium Arsenide VLSI circuits. This is achieved by :

Evaluating the well established Direct Coupled Logic (DCFL) gates and proposing an alternative gate, namely the Source Follower DCFL (SDCFL), to improve the noise margin and speed.

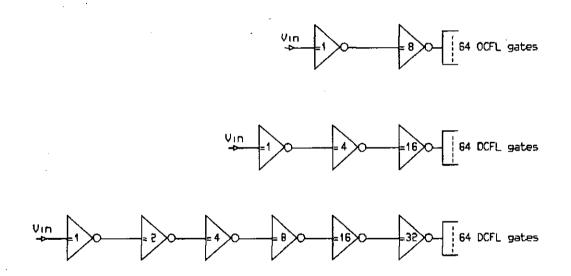

Suggesting various buffering schemes to maintain high speed in areas where the fanout loading is high (eg. clock drivers).

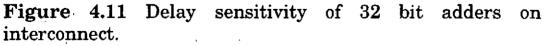

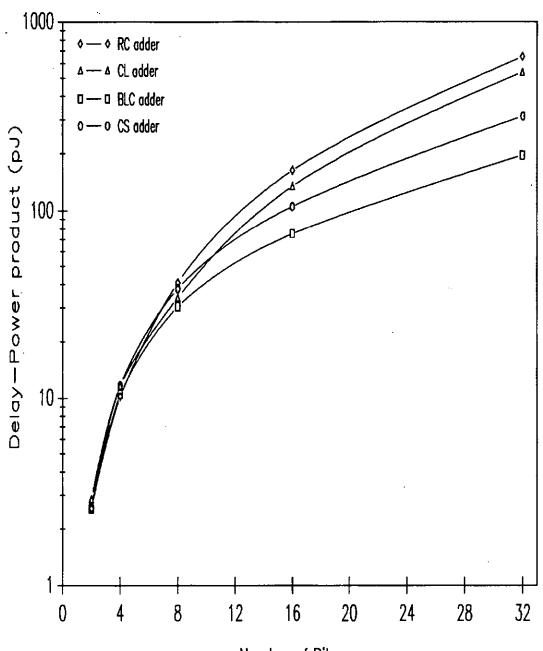

Comparing various adder types in terms of delay-power and delay-area products to arrive at a suitable architecture for Gallium Arsenide implementation and to determine the influence of the algorithm and layout approach on circuit performance. To investigate this further, a multiplier was also designed to assess the performance at higher levels of integration.

Applying a new layout approach, called the 'ring notation', to the adder and multiplier circuits in order to improve their delay-area product.

Finally, the critical factors influencing the performance of the circuits are reviewed and a number of suggestions are given to maintain reliable operation at high speed.

| 2.4 Self-Aligned Gate Process Technology              | 20 |

|-------------------------------------------------------|----|

| 2.5 GaAs MESFET Design Rules and Layer Representation | 22 |

| 2.6 An Appropriate Device Model for GaAs VLSI         | 22 |

| 2.7 Important Effects Included in the Device Model    | 26 |

| 2.8 Interconnect Modelling                            | 27 |

| 2.9 Effect of Process Variations                      | 29 |

| <b>Chapter 3 MESFET Logic Families</b>                |    |

| for GaAs VLSI Circuits                                |    |

|                                                       |    |

| 3.1 Types of MESFET Logic Gate                        | 30 |

| 3.2 Normally-ON Logic Gates                           | 30 |

| 3.3 Normally-OFF Logic Gates                          | 34 |

| 3.4 Suitable Logic Gates for GaAs VLSI                | 37 |

| 3.5 First Order Design of DCFL and SDCFL Gates        | 37 |

|                                                        | ••• |

|--------------------------------------------------------|-----|

| 3.6 Definition of Design Parameters                    | 41  |

| 3.7 Detailed Analysis of DCFL and SDCFL Gates          | 43  |

| 3.8 Design of Buffering Schemes for GaAs VLSI Circuits | 49  |

### **CHAPTER 4 Analysis of Adder Circuits**

### for GaAs VLSI Implementation

| 4.1 Adder Design Approach                      | 59     |

|------------------------------------------------|--------|

| 4.2 Types of Adder                             | 62     |

| 4.3 Evaluation of Adder Circuits for GaAs VLSI | · • 69 |

| 4.4 Summary of Important Points                | 77     |

### Acknowledgements

I would like to express my gratitude to the following people at Middlesex Polytechnic.

Professor John Butcher, my director of studies, for his valuable guidance and support throughout this research programme. His much needed comments and constructive criticisms on the draft of the key chapters are also greatly appreciated.

My supervisors Mr Richard Bayford and Dr Robert Paul Camp for their help, advice and technical input to the project.

Mr Paul Burn, managing director of the Integrated Circuit Design Centre (ICDC), for his support and encouragement throughout the project.

My colleagues Mr Divya Pujara and Mr Majid Saber with whom I had many useful discussions on various aspects of the project.

I would like to acknowledge the support and help of the following people at the University of Adelaide, South Australia.

Dr Kamran Eshraghian, Head of the Centre for Gallium Arsenide VLSI Technology, for his direct influence on many areas of the project. His novel idea of 'ring notation layout' methodology has formed the basis of the results presented in chapter 6 of this thesis.

Mr Derek Abbott, research officer, for his guidance, especially in the initial stages of the project.

Mr Andrew Beaumont-Smith for providing much of the software support for the design tools and the design rules for the particular GaAs process used in this research.

This work has been partially supported by the Sir Keith and Sir Ross Smith Foundation of the Australian Council for Research.

Acknowledgements

I would like to express my gratitude to the following people at Middlesex Polytechnic.

Professor John Butcher, my director of studies, for his valuable guidance and support throughout this research programme. His much needed comments and constructive criticisms on the draft of the key chapters are also greatly appreciated.

My supervisors Mr Richard Bayford and Dr Robert Paul Camp for their help, advice and technical input to the project.

Mr Paul Burn, managing director of the Integrated Circuit Design Centre (ICDC), for his support and encouragement throughout the project.

My colleagues Mr Divya Pujara and Mr Majid Saber with whom I had many useful discussions on various aspects of the project.

I would like to acknowledge the support and help of the following people at the University of Adelaide, South Australia.

Dr Kamran Eshraghian, Head of the Centre for Gallium Arsenide VLSI Technology, for his direct influence on many areas of the project. His novel idea of 'ring notation layout' methodology has formed the basis of the results presented in chapter 6 of this thesis.

Mr Derek Abbott, research officer, for his guidance, especially in the initial stages of the project.

Mr Andrew Beaumont-Smith for providing much of the software support for the design tools and the design rules for the particular GaAs process used in this research.

This work has been partially supported by the Sir Keith and Sir Ross Foundation of the Australian Council for Research.

### GLOSSARY

| $\tau_d$                                          | Gate delay (ps)                                                    |

|---------------------------------------------------|--------------------------------------------------------------------|

| ${ m L_{eff}}$                                    | Effective channel length (µm)                                      |

| w                                                 | Width of the FET channel (µm)                                      |

| ρ                                                 | Resistivity ( $\Omega cm$ )                                        |

| $\mu_n$ , $\mu_p$                                 | Electron and hole mobilities (cm²/Vs)                              |

| V <sub>bi</sub>                                   | Schottky barrier height (V)                                        |

| V <sub>t</sub>                                    | Threshold voltage (V)                                              |

| V <sub>p</sub>                                    | Pinch-off voltage (V)                                              |

| λ                                                 | Channel length modulation parameter (1/V)                          |

| β                                                 | Transconductance parameter (amp/V <sup>2</sup> )                   |

| N                                                 | Effective channel doping density (atom/cm <sup>3</sup> )           |

| $\varepsilon = \varepsilon_0 \cdot \varepsilon_r$ | where $\varepsilon_0$ is the permittivity of free space (F/cm) and |

|                                                   | $\varepsilon_r$ is the relative permittivity of GaAs (13.1)        |

| $C_{g0}$                                          | Zero bias gate capacitance (F)                                     |

| $C_{gd}$ , $C_{gs}$                               | Gate-drain and gate-source capacitances (F)                        |

| R <sub>d</sub> , R <sub>e</sub>                   | Drain and source resistances (ohm)                                 |

| a                                                 | Effective channel implant depth (Å)                                |

| <b>q</b> .                                        | Electron charge (C)                                                |

| α                                                 | Hyperbolic tangent drain multiplier (1/V)                          |

| F <sub>c</sub>                                    | Average clocking frequency                                         |

| F.                                                | Fanin                                                              |

### F<sub>o</sub> Fanout

ł

BFL Buffered FET Logic

SDFL Schottky Diode FET Logic

CCFL Capacitor-Coupled FET Logic

QFL Quasi-FET Logic

DCFL Direct Coupled FET Logic

SDCFL Source Follower DCFL

RDCFL Ring notation DCFL

RSDCFL Ring notation SDCFL

## CHAPTER 1 INTRODUCTION

#### **1.1 Review of Silicon Technology**

Silicon is the most widely used semiconductor material for integrated circuits. The main reasons for this choice are the ease of purification, the ease of forming single crystals and the device considerations such as the ease of epitaxial growth and the growth of high integrity oxide [1]. As a result many device types have been proposed in silicon for integrated circuits. Initially the main workhorse in the IC industry was the bipolar technology and more recently the MOS process.

MOS integrated circuit technology has progressed tremendously because of the huge demand for digital electronics applications. As shown in Table 1.1, it is now possible to fabricate integrated circuits containing up to 1 million or more transistors [2]. This trend is likely to continue (Moore's law) such that by the end of 1990's the level of complexity will probably exceed 10 million transistors per chip.

The advantages of this increased level of integration are reflected in the cost reduction, higher reliability, higher speed and low power dissipation of systems which are also extremely small and light weight. To achieve these results there has been a systematic approach to improving the process technology and also major efforts have been directed towards solving the problems of device scaling. Apart from the higher packing densities achievable from the fabrication of smaller devices, it is possible to make devices with higher operating frequencies in order to fulfil the speed requirements of state-of-the-art computer systems [3] [4] [5].

| Year | Technology             | No. of Trans.<br>per Chip | Typical Products                                   |

|------|------------------------|---------------------------|----------------------------------------------------|

| 1950 | Discrete<br>Components | 1                         | Junction Trans. and<br>diodes.                     |

| 1961 | SSI                    | 10                        | Logic gates, Flip-Flops.                           |

| 1966 | MSI                    | 100-1000                  | Counters, Adders,<br>Multiplexers.                 |

| 1971 | LSI                    | 1000-20,000               | 8 bit microprocessors,<br>ROM, RAM.                |

| 1980 | VLSI                   | 20,000-500,000            | 16 and 32 bit<br>Microprocessors.                  |

| 1985 | ULSI                   | > 500,000                 | Special Processors, Real<br>time image processors. |

| 1990 | GSI                    | >10,000,000               | WSI                                                |

Table 1.1 Microelectronics Evolution.

#### **1.2 Limitations of Silicon for High Speed Applications**

Super fast computers with sub-nanosecond cycle times, and multi-gigabit per second telecommunication and instrumentation systems are the driving forces behind the development of high speed VLSI circuits. The emphasis is on increasing the level of integration and the speed of these circuits to achieve the computational power required by the application areas mentioned above [6].

The principal requirements of high speed VLSI circuits are: small feature size, high process yield and, most important of all, extremely low dynamic switching energy [7] [8] [9].

The origins of the first two requirements are obvious. Clearly, large numbers of gates can not be placed on a reasonably sized chip unless the gate areas are small. For instance if a  $1 \text{cm}^2$  chip is to accommodate

100,000 transistors, the size of the individual gates must be less than  $1000 \mu m^2$ . The process yield should also be sufficient to produce economically such complex parts.

The dynamic switching energy or power-delay product,  $2P_d \times \tau_d$ , is the minimum energy that a gate can dissipate during a clock cycle. The power dissipation for a chip with N<sub>g</sub> gates with an average gate clocking frequency F<sub>c</sub> will therefore be :

$$P_{(CHIP)} = 2 \times N_{g} \times F_{c} \times (P_{d} \times \tau_{d})$$

(1.1)

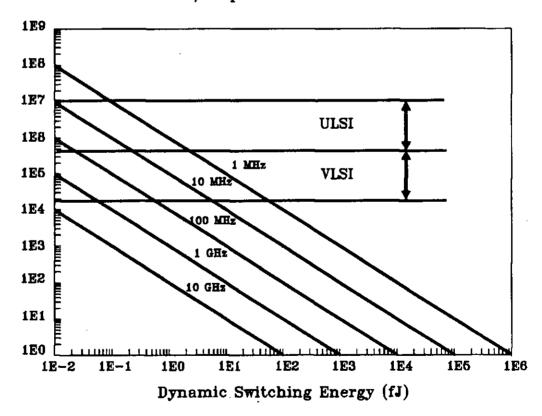

This relation is illustrated in Figure 1.1, for a typically 'large' total input power of 2 Watts [10].

Number of Gates/Chip

Figure 1.1 Switching energy as a function of the number of gates per chip for a practical power of 2 Watts.

The requirement on dynamic switching energy for high speed VLSI is quite severe. Even allowing for the fact that power dissipation for large chips could safely be somewhat higher than 2 Watts, dynamic switching energies of much less than 0.1pJ appear essential for achieving practical very high speed VLSI [11]. Therefore, it is of critical importance to evaluate the existing technologies and choose the one with the lowest speed-power product in order to be able to combine high levels of integration with high speed performance.

As mentioned in section 1.1, MOS is by far the most often used technology for VLSI circuits and will continue to fill this role. In order to obtain high speed and high density MOS ICs, the device geometries need to be continuously scaled to smaller sizes [12]. This means that the theoretical and practical limits associated with the scaling of MOS circuits must be investigated to find the limitations of existing technologies.

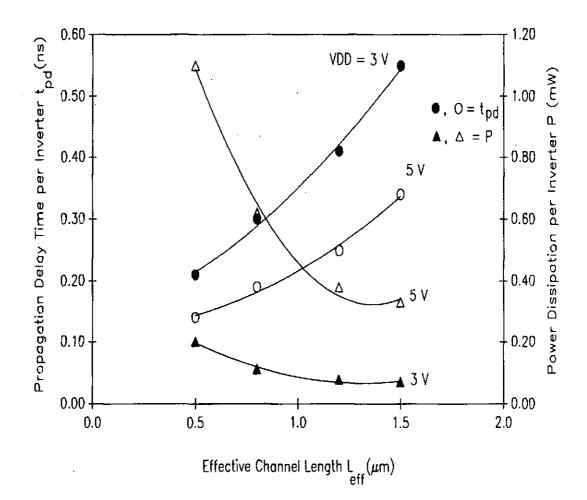

Figure 1.2 shows the gate propagation delay and power dissipation against the channel length of fabricated CMOS inverters [13] [14]. At  $0.5 \mu m$  (state-of-the-art commercial device size) and standard power supply of 5V, the delay is about 120ps with power dissipation of 1.1mW. The speed-power product of the gate is therefore about 0.1pJ, enabling the realisation of high speed, medium scale integrated circuits. The expected circuit performance with scaling for different technologies has also been investigated by P.A.H Hart, et al [15]. They have considered a range of devices such as ECL, I<sup>2</sup>L and MOS. The scaling process most benefits the MOS technology, with speeds higher than that of ECL and speed-power product even lower than I<sup>2</sup>L. Below  $1\mu m$  gate width, a delay time of 100ps and a power-delay product of 0.02pJ should theoretically be possible. However when device miniaturisation is continued, the second order effects on device characteristics become so significant that simple scaling of the technology becomes a non-viable approach at a certain geometry [16]. For example, the encroachment of the field oxide (the socalled bird's beak created during the local oxidation stage of the normal

silicon process) makes the effective channel width smaller than the design size and degrades the drain current significantly. In addition hot carriers generated by the high electric field across the channel and the drain pinch-off region cause unacceptable device instabilities unless the power supply voltage is scaled down along with the channel length reduction. Scaling down the supply voltage results in the loss of a marked distinction between the logic 'low' and logic 'high' levels. For example scaling a  $2\mu m$  technology to  $0.2\mu m$  would require the supply voltage to be lowered from 5 to 0.5V with a consequent narrow noise margin and high sensitivity to variations in the supply voltage.

Figure 1.2 Delay and power dissipation of scaled inverters for power supplies of 3 and 5 volts.

Another problem encountered in CMOS is the latch-up susceptibility

which becomes a serious drawback in sub-micron geometries.

Therefore as the device geometry is reduced, we are quickly reaching the limits of silicon technology for ultra high speed, VLSI circuits. We are hence prompted to seek other technologies to provide for faster devices which will be a prerequisite for even more sophisticated system design capabilities.

#### **1.3 Gallium Arsenide as an Alternative Substrate**

Before assessing the suitability of GaAs as a substrate for VLSI circuits it is important to note that our concern is only with ultra-high speed applications. Then, in order to explore the potential of the technology, it is necessary to make a direct comparison between GaAs and silicon. First we concentrate on the two materials and their electrical properties, a summary of which is given in Table 1.2 [17].

| Properties                                               | GaAs               | silicon            |

|----------------------------------------------------------|--------------------|--------------------|

| Electron mobility (cm²/Vs)                               | 5000               | 800                |

| Maximum electron drift velocity (cm/s)                   | $2 \times 10^7$    | $1 \times 10^7$    |

| Hole mobility (cm <sup>2</sup> /Vs)                      | 250                | 350                |

| Energy gap (eV)                                          | 1.43               | 1.12               |

| Type of gap                                              | Direct             | Indirect           |

| Density of states in conduction band (cm <sup>-3</sup> ) | $5 \times 10^{17}$ | 3×10 <sup>19</sup> |

| Maximum resistivity $(\Omega cm)$                        | 10 <sup>9</sup>    | 105                |

| Minority carrier life time (s)                           | 10.8               | 10 <sup>-3</sup>   |

| Breakdown field (V/cm)                                   | 4×10 <sup>5</sup>  | 3×10 <sup>5</sup>  |

| Schottky barrier height (V)                              | 0.7-0.8            | 0.4-0.6            |

Table 1.2 Properties of GaAs and silicon at 300 K.

The advantages of GaAs over silicon as a base material for ICs are [18] [19] [20]:

- a) At normal doping levels the saturated drift velocity for GaAs and silicon are almost equal with values of  $1.4 \times 10^7$  and  $1 \times 10^7$  cm/s respectively. However the saturation velocity in GaAs is achieved at electric fields about four times lower than in silicon.

- b) Electron mobility in GaAs is six to seven times higher than in silicon. Therefore, transit times as short as 15-10ps, corresponding to current gain-bandwidth products in the range 15-25GHz can be obtained for GaAs transistors for typical gate lengths of  $0.5-1\mu m$  (a three to five times improvement over silicon devices).

- c) The semi-insulating property of GaAs material (resistivity in the range of  $10^7$ - $10^9\Omega cm$  at room temperature) is another advantage for high performance devices. It not only minimises the parasitic capacitances but also allows for easy electrical isolation of multiple devices on a single substrate.

- d) Schottky barriers can be realised on GaAs with a large variety of metals (e.g. aluminium, platinum, titanium) leading to high quality Schottky junctions with excellent ideality factors (n less than 1.1) and fairly low reverse currents  $J_s < 1\mu A/cm^2$ .

- e) GaAs is more radiation resistant than silicon due to the absence of gate oxide and can operate over a wider temperature range (-200 to 200°C) because of its larger band gap, and finally :

- f) The direct band gap of GaAs allows efficient radiative recombination of electrons and holes, meaning that forward-biased pn junctions can be used as light emitters. Thus, efficient integration of electrical and optical functions is possible.

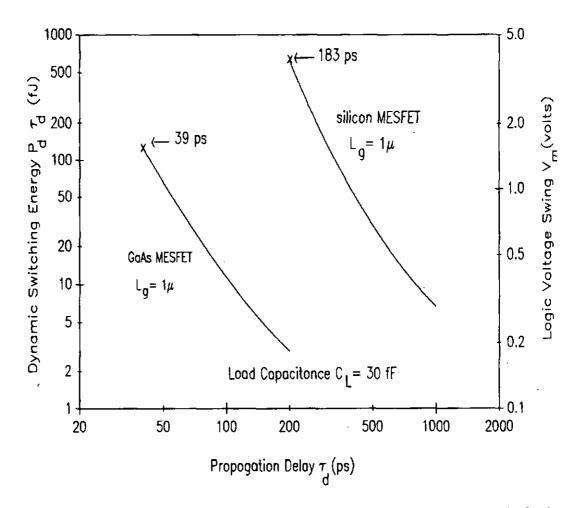

The expected higher performance of GaAs compared with silicon should be studied not only on the basis of the material properties but also in terms of the actual logic gates and integrated circuits implemented in either technology. As explained in section 1.2, the most important figure of merit for logic gates in high-speed VLSI circuit applications is the dynamic switching energy. Figure 1.3 shows the calculated dynamic switching energy versus propagation delay relationships for GaAs and silicon MESFETs (W=  $10 \mu m$ , L=  $1 \mu m$ ), with a load capacitance of 30fF [21].

Figure 1.3 Optimised switching performances of silicon and GaAs MESFETs with a load capacitance of 30fF.

It is evident that the logic switching speeds and speed-power products of the FET gate are dramatically improved in GaAs. For the same logic voltage swing, a GaAs MESFET (L=  $1\mu m$ ) would give about 4-6 times higher switching speeds than its silicon counterpart. For a logic voltage swing of 3.5V, the silicon MESFET should achieve a switching speed of 183ps. With the same gate length a GaAs MESFET, should achieve the same switching speed with only a 300mV logic swing. This is reflected in the figures for the dynamic switching energies of the gates. For the GaAs MESFET, it is only about 3fJ, whereas for the silicon MESFET, its value is about 150 times higher (0.45pJ), restricting the level of integration.

Having discussed the superior performance potential of GaAs material and logic gates compared with silicon, we must also consider the performance of GaAs integrated circuits with reasonable complexity, and compare them with their silicon counterparts. Tables 1.3 through 1.5 list some of the GaAs and Si multipliers, memories and gate arrays [22] [23] [24]. The performance trade-off between speed and power is evident within each technology as well as the effect of design rules. For the same device dimensions, GaAs devices perform better either in terms of power dissipation or propagation delay. The results show that GaAs IC technology will have a significant impact on the performance of digital signal processing systems. A factor of 2 to 5 times the system clock frequency over present systems is projected for digital GaAs ICs.

| Technology               | Size  | Delay<br>(ns) | Power<br>(mW) | Comments          |

|--------------------------|-------|---------------|---------------|-------------------|

| Si NMOS (TRW)            | 8x8   | 45            | 1000          | 2 µm design rule  |

| Si ECL (NEC)             | 8x8   | 5             | 1400          | 2×6µm emitter     |

| Si NMOS (BELL)           | 16x16 | 20            | 1000          | 1.5µm design rule |

| Si SOS (TOSHIBA)         | 16x16 | 27            | 150           |                   |

| Si CMOS (NEC)            | 16x16 | 45            | 100           |                   |

| GaAs DCFL<br>(FUJITSU)   | 16x16 | 10.5          | 952           | 2µm gate length   |

| GaAs DCFL<br>(TOSHIBA)   | 8x8   | 12            | 160           |                   |

| GaAs SDCFL<br>(ROCKWELL) | 8x8   | 5.25          | 2200          |                   |

Table 1.3 IC technologies comparison (for multiplier circuit).

| Technology                | Size<br>bits | Access<br>time<br>(ns) | Power<br>(mW)<br>per 1K | Comments          |

|---------------------------|--------------|------------------------|-------------------------|-------------------|

| Si ECL (FUJITSU)          | <b>4</b> K   | 3.2                    | 750                     |                   |

| Si ECL (NEC)              | 4K           | 2.3                    | 400                     |                   |

| Si NMOS (BELL)            | <b>4</b> K   | 5.0                    | 100                     | 1µm design rule   |

| Si CMOS (NIPPON)          | 1K           | 25.0                   | low                     | 1.5µm design rule |

| GaAs DCFL<br>(FUJITSU)    | 1K<br>4K     | 1.3<br>3.0             | 300<br>175              | 2μm gate length   |

| GaAs DCFL<br>(NIPPON)     | 1K           | 2.0<br>6.0             | 459<br>38               | 1µm gate length   |

| GaAs DCFL<br>MC D-DOUGLAS | 256          | 5.0                    | 35                      |                   |

| GaAs HEMT<br>(FUJITSU)    | 1K           | 3.4<br>0.9             | 290<br>360              | JFET technology   |

Table 1.4 IC technologies comparison (for memory circuit).

| Technology                | Size<br>(gates) | Gate delay<br>(ps)                        | Power<br>(mW/gate) |

|---------------------------|-----------------|-------------------------------------------|--------------------|

| Si ECL (NIPPON)           | 5000            | 500 (average)                             | 1.0                |

| Si BIPOLAR (IBM)          | 10000           | 1700 loaded<br>1400 loaded                | 0.34<br>0.57       |

| Si SOS (TOSHIBA)          | 8000            | 870 loaded                                | 0.45               |

| Si ECL<br>(COMMERCIAL)    | 170-1500        | 3500-1500                                 | 29-0.85            |

| GaAs DCFL<br>(TOSHIBA)    | 1000            | 300 loaded                                | 0.2                |

| GaAs DCFL<br>(TEKTRONIX)  | 1224            | 100 (fo=1) <sup>*</sup><br>200-250 (fo=3) | 0.25               |

| GaAs SDCFL<br>(HONEYWELL) | 432             | 250 (r.o)*                                | 3.0                |

| GaAs SDCFL<br>(LOCKHEED)  | 320             | 184 (r.o)                                 | > 1.0 (Est.)       |

(fo=N) is a gate with fanout of N.

(r.o) is the results obtained from ring oscillators.

Table 1.5 IC technologies comparison (for gate array).

#### **1.4 Current Developments and Future Trends**

GaAs technology maturity in the processing of digital integrated circuits in 1991 is equivalent to silicon technology maturity of the mid 1970's. However, improvements seen with GaAs processing technology are occurring at a rate which is three times that which occurred in silicon processing during the 1970's and early 1980's [25]. The turning point came in 1986 with the development of a new method of manufacturing digital GaAs ICs. The process employs the usual metal-semiconductor field-effect transistors (MESFETs), except that a refractory metal replaces gold in the MESFET self-aligned gates [26]. This innovation not only eases manufacture but also permits the use of a logic family which trades off some of gallium arsenide's high speed for lower power consumption. The result is a high yield and relatively low cost solution to the needs of very high speed digital integrated circuits.

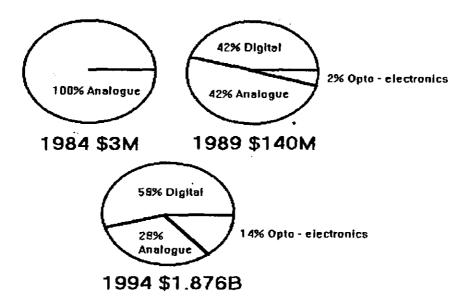

The market for digital GaAs ICs is growing very fast. Figure 1.4 shows the perceived European GaAs IC market in 1984, 1989 and 1994 [27]. This demonstrates that the leading sector until the late 1980's was analogue MMICs, but that both digital and optoelectronic ICs will be employed increasingly in systems. By the end of 1994, the European market will mostly be devoted to GaAs digital applications. The same progress is happening world-wide, with most of the newly available VLSI products in GaAs being application specific integrated circuits (ASICs). The most dramatic impact on the computer market will occur when GaAs microprocessors begin to appear. These chips will bring the power of today's supercomputer to the desktop workstation. Because of their relatively low power dissipation, clock frequencies in excess of 250MHz could be accommodated in an office environment enclosure which contains only a fan for cooling [28]. In sharp contrast, today's supercomputers require exotic liquid or refrigerated-air cooling.

Figure 1.4 Market sectors for GaAs ICs in Europe from 1984 to 1994.

#### **1.5 Scope of this Thesis**

This chapter has shown the superior performance of digital GaAs circuits in terms of speed and power dissipation and has predicted an ever growing use of this technology for high speed digital applications.

The ultimate success of GaAs as a base for digital integrated circuits depends on various factors, the most important of which are the process and design issues.

The process maturity of GaAs is reaching the stage where the implementation of true VLSI circuits ( $\geq 20,000$  transistors) is possible. This is brought about by the constant improvement in the preparation of defect free crystals as well as in production of devices with very small parameter variations. At such levels of integration, a design approach must be developed to ensure reliable operation whilst maintaining the high speed and low power dissipation offered by the technology.

The subject of this thesis is to identify the critical design issues, ranging from the optimisation of basic gates to the impact of the algorithms and overall architecture on the performance of GaAs VLSI circuits. This is achieved by designing a range of test circuits such as logic gates, buffers, storage elements, adders and multipliers based on existing design ideas to identify potential problem areas. The data provided from this design exercise are then used to develop novel techniques to improve the performance of GaAs circuits at high levels of integration. Although the designs are primarily targeted for image processing applications, in principle they could have much wider applications.

In chapter 2 various GaAs devices are introduced and their suitability for VLSI applications is assessed. The manufacturing sequence of the devices is then explained to provide a better understanding of their structures. The layers and their associated layout rules are subsequently defined in order to be able to identify them on the circuit layouts and to show the minimum feature sizes for the GaAs process used. Also, in this chapter, the device models and process parameters are discussed in some detail. These are important issues as they directly determine the validity of the simulation results.

The GaAs MESFET logic families are discussed in chapter 3. A detailed comparison between the logic gates is presented to select the most appropriate one for GaAs VLSI applications, namely the Direct Coupled FET Logic (DCFL) gate. An alternative gate configuration called the Source follower DCFL (SDCFL) is also proposed in an attempt to improve the noise margin and speed of GaAs circuits. This is followed by suggesting a number of buffering schemes to improve the speed where the fanout loading is high. This is particularly important for the clock drivers required in any synchronous VLSI circuit.

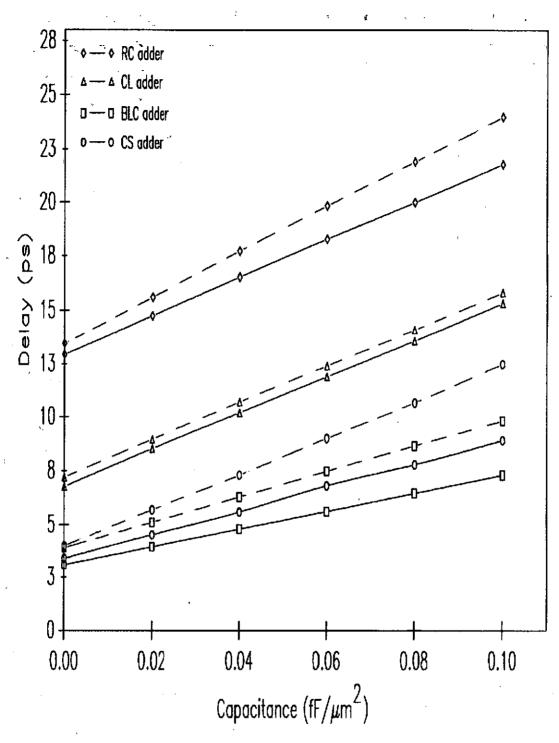

The fourth chapter gives a review of various adder circuits. These adders are designed, laid out and simulated to find the best adder architecture for GaAs implementation. The effects of algorithm and design technique on the performance of the adder circuits are fully demonstrated. The effects of various interconnect technologies on the overall delay are also investigated to suggest adder architectures which would be least sensitive

to interconnect. The design and evaluation of a GaAs multiplier circuit is presented in chapter 5. This is a natural progression towards the implementation of a VLSI circuit for digital signal processing applications. The multiplier circuit is used to demonstrate further the effectiveness and identify the limitations of conventional circuit design approaches for GaAs digital circuits.

A hierarchical design procedure and a novel layout method are proposed in chapter 6 to minimise the delay and area of circuits. This novel design technique is applied to the same circuit examples in chapters 4 and 5 which are then re-evaluated. A comparison between the results obtained from the circuits in this chapter and those achieved by using the conventional design techniques is given to show the improvements in performance.

Finally, the overall objectives and the work carried out during the course of the project are summarised in chapter 7. The outcomes together with the conclusions drawn from the research are also presented.

### CHAPTER 2

### **GaAs DEVICE FABRICATION AND MODELLING**

#### 2.1 Suitable Devices for VLSI Implementation

A number of different devices have been developed for GaAs. They fall into two categories, the first and second generation devices [30]. First generation devices are the Depletion-mode MESFET (DFET), Enhancement-mode MESFET (EFET), Enhancement-mode Junction FET (EJFET) and Complementary EJFET (CE-JFET). The second generation devices include the High Electron Mobility Transistor (HEMT) and Heterojunction Bipolar Transistor (HBT). Second generation devices are faster than the first generation devices due to better exploitation of the GaAs. For example the operating frequency of DFETs, in general, is between 20 to 80GHz and for HEMTs it can vary from 70 to 100GHz [31].

There are also more exotic devices being invented in the research labs which attempt to reach the ultimate performance of GaAs. However for high speed VLSI circuits the most important factor, apart from high operating frequency, is the maturity of the process. At present the first generation MESFETs are the most widely used devices for VLSI applications. Even at sub-micron level they can still be easily manufactured and provide high operating frequencies.

The designs and analyses of the circuits presented in this thesis are based on MESFETs. Therefore the results and the final conclusions are specific to MESFETs, although the fundamental design and implementation issues are believed to be applicable to circuits using other GaAs devices. The following section presents a detailed description of MESFETs, their fabrication process and design rules as well as the equivalent circuit models used in all the simulations.

#### 2.2 GaAs MESFET Structure

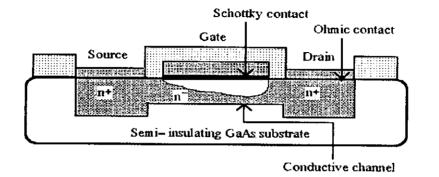

Figure 2.1 shows the basic structure of a GaAs MESFET. It consists of a chromium doped, semi-insulating substrate into which source, drain and channel are made by n-type dopant implantation [32].

Figure 2.1 Cross section of an ion-implanted MESFET.

The gate is formed when a metal such as aluminium is deposited over the channel. Conduction in the channel is confined to the region between the gate depletion-edge and the substrate and may be modulated by the gate voltage.

GaAs MESFETs are somewhat similar to silicon MOSFETs. The major difference is the presence of a Schottky diode at the gate-channel interface. The detailed device operation is also different in that in GaAs the electron velocity saturates for an electron field roughly ten times lower than in silicon. Thus, the saturation in drain current, for GaAs MESFETs occurs due to the carrier-velocity saturation, whereas channel pinch off causes this in silicon [33].

The threshold voltage of the GaAs MESFET can be adjusted by varying the channel thickness and the concentration of the implanted impurity. The normally 'ON' DFET is characterised by its thick and highly doped channel exhibiting a negative threshold voltage. By reducing the channel thickness a normally 'OFF' EFET with positive threshold voltage can be fabricated. For the DFETs the channel thickness is in the range of 1000 to 2000Å, whereas for the EFETs it ranges from 500 to 1000Å. There are many ways of fabricating MESFETs and the process can be adapted to the application for which they are intended. For high performance GaAs VLSI circuits the most dominant approaches in device fabrication are the planar and self-aligned gate processes [34].

#### 2.3 Planar Processing Steps for GaAs MESFETs

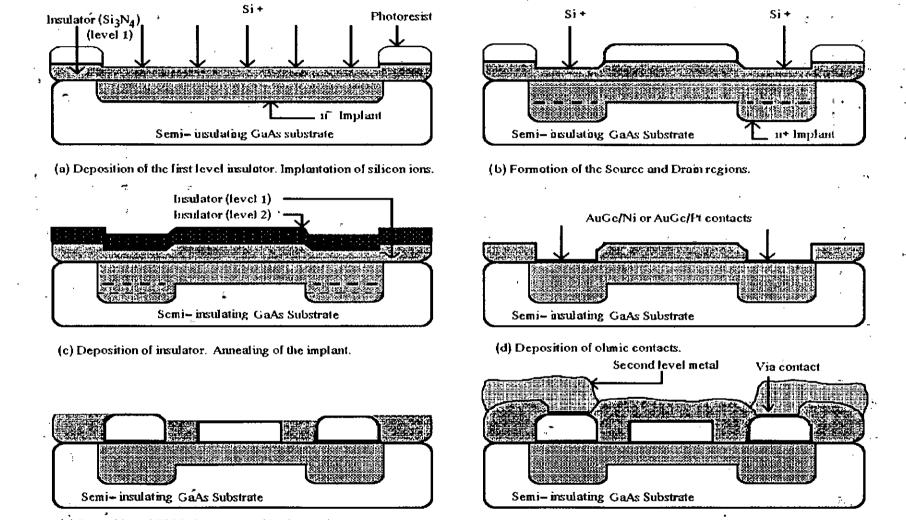

Figure 2.2 shows a generalised manufacturing sequence for a discrete planar GaAs DFET process. It is presented here to show the steps in transistor fabrication without the complications of simultaneous fabrication of other components (the same process applies to EFETs).

As shown in Figure 2.2a, initially the GaAs substrate is coated with the first level of insulator which is a thin layer of silicon nitride  $(Si_3N_4)$ . This thin film of insulator remains on the wafer throughout the processing steps that are to follow. A photoresist is then applied and selectively removed to define a shallow high resistivity n- channel layer. The channel is formed by direct implantation of silicon ions through the silicon nitride layer, into the GaAs substrate.

Figure 2.2b shows the formation of the deep and heavily doped n<sup>+</sup> layer for the source and drain regions, after a second application of photoresist and the selective removal process. The resultant channel resistance is in the range of 1000 to  $2500 \Omega/square$ , which is too high for source and drain contacts. Therefore the surface concentration of the n<sup>+</sup> is kept relatively high to minimise the resistance seen by the ohmic metal contacts.

In the next step, namely the cap and anneal process (Figure 2.2c), the wafer is capped with a suitable material such as silicon dioxide  $(SiO_2)$  by chemical vapour deposition. This layer of silicon dioxide is particularly important as it prevents arsenic out-diffusion, brought about by the high vapour pressure associated with GaAs when subject to temperatures in excess of about  $600C^{\circ}$ , during the anneal step. The anneal step is performed in a hydrogen ambient to activate electrically the implanted

regions.

The ohmic contact metallisation step in which contact areas for the source and drain are formed uses a process known as the lift off technique (figure 2.2d).

In the lift off process the deposited metal adheres to the underlying material where there is no cap layer while the remaining metal on the cap layer is removed when the layer is stripped. This allows precise metal definition without an etch back process. The metals used in the ohmic metallisation are gold-germanium-nickel or gold-germanium-platinum alloy.

An important point to note is that the semi-insulating nature of the GaAs substrate can not be used alone to provide good isolation between devices (back-gating) [35] [36]. In fact, it is usual to implant H<sup>+</sup> ions into the field areas to reduce the effect of the parasitic interactions between the nearby devices.

One of the most critical steps in the fabrication process is the gate metallisation. Schottky gates together with the first level interconnect are formed by multi-layer gold and refractory metal thin films such as titanium/platinum/gold alloy, deposited by electron beam evaporation (Figure 2.2e). Second and higher level metals are not in contact with the GaAs substrate, therefore platinum which is used to prevent the interaction of gold with the GaAs surface can sometimes be eliminated from this step.

The final step of the process is the passivation step which is used to protect against moisture and contamination (Figure 2.2f). This entails a thick layer of silicon nitride being deposited on the gate, source and drain metallisation, using a low temperature plasma enhanced chemical vapour deposition process.

Figure 2.2 A typical planar manufacturing process for a GaAs MESFET.

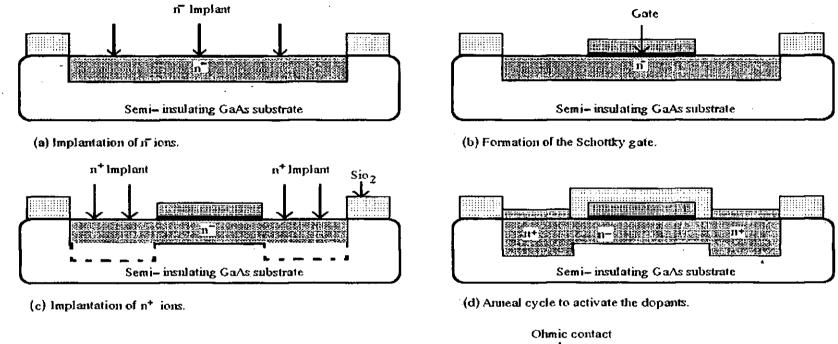

#### 2.4 Self-Aligned Gate Process Technology

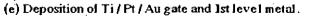

In order to improve fabrication technology, the self- aligned gate method was borrowed from silicon NMOS process. In this method, the Schottky gate is used as a mask for implanting the source and drain regions of the devices. The  $n^+$  source and drain layers are embedded close to the gates. Therefore the parasitic source resistance of the FETs is greatly reduced and as a consequence the transconductance of the device is increased. In addition the process offers improved pinch-off voltage uniformity, which is of crucial importance for the manufacture of VLSI circuits based on normally-off EFETs.

The fabrication steps for a self-aligned gate process are shown in Figure 2.3. Just as for the planar process the first step is to form the channel area by selective implantation of silicon ions into the GaAs substrate (Figure 2.3a). Next, a high temperature stable material such as Tungsten Nitride is deposited over the substrate and is patterned by an etching process to define the gate area (Figure 2.3b). The gate acts as a mask for the next step in the process which is the formation of source and drain by the high dose implantation of ions (Figure 2.3c). This step is followed by capping of the substrate with silicon dioxide so that the sample can be annealed without any arsenic out-diffusion due to the high vapour pressure.

It is important to note that the gate material must withstand the high temperatures (about  $800C^{\circ}$ ) during the annealing process. Tungsten Nitride has been found to be satisfactory as a gate material. It has a typical film resistivity of  $70\mu\Omega$ -cm and Schottky barrier height of 0.8 V to n-type GaAs.

After the annealing (Figure 2.3d), the final stage of the process is the ohmic metallisation of the source and drain regions (Figure 2.3e). As in the case of the planar process, the metals used in the ohmic metallisation are gold-germanium-nickel alloy or gold-germanium-platinum.

<sup>(</sup>e) Formation of olmic contacts.

The formation of the second and higher level metals together with the final passivation stage is similar to that of the planar process, described in the previous section.

#### 2.5 GaAs MESFET Design Rules and Layer Representation

The layout and design rules are intended to ensure reliable circuits with optimum yield and size. They are set by the designer and the process engineer to provide the best compromise between yield and performance.

The layout rules must define: a) the geometry of the features that can be reproduced by the mask and lithography process and, b) the interaction between different layers. There are two main approaches to achieve this: the lambda-based and micron-based rules. In lambda-based rules, every feature is expressed in terms of the parameter lambda. The micron rules, on the other hand, are given as a list of minimum feature sizes and spacings, according to the capabilities of the process technology.

The lambda-based rules are simple and somewhat relaxed to ensure high yield circuits. This, however, results in performance degradation due to the increase in area. For high speed GaAs VLSI circuits, micron-based rules must be used to achieve optimum performance [37].

The layout rule set used throughout the work presented in this thesis is given in appendix A, so that it can be used for further circuit design and implementation work, if required. The set includes the width and spacing rules for different layers together with some special rules for MESFETs. The colour coding of the layers together with the layer patterns are also provided so that each layer in the circuit can easily be identified [38] [39].

#### 2.6 An Appropriate Device Model for GaAs VLSI

In the following chapters a considerable amount of computer simulation is described, in order to present a novel design approach for GaAs MESFETs. The validity of the results and final conclusions depend totally on: a) the accuracy of the model for the individual devices and b) the accuracy of the parameters, extracted for the model [40]. The deciding factor in choosing a particular model must arise from the comparison of the simulated results with the measured data to provide reliable results.

For VLSI circuit simulation, another important factor in choosing a particular model is that it should be CPU time efficient. Clearly complex models can not be used for circuits with many thousands of MESFETs. On the other hand MESFETs are complex internally and simple equations can not describe their behaviour under all possible conditions.

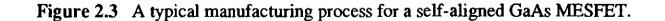

The most commonly used MESFET model is based on the JFET model, consisting of a parallel diode and capacitor between gate-source  $(D_{gs}, C_{gs})$ and gate-drain  $(D_{gd}, C_{gd})$ , plus a controlled current source  $(I_{ds})$  between drain-source. For anything other than the most approximate simulations it is necessary to add resistors  $R_d$ ,  $R_s$  and  $R_g$  in series with the drain, source and gate respectively, add a drain-source resistor  $(R_{ds})$  and drainsource capacitor  $(C_{ds})$ . The complete equivalent circuit model is shown in Figure 2.4 [41] [42].

Figure 2.4 The equivalent circuit model for GaAs MESFETs.

The problem is to define a formula for the  $I_{ds}$  current. The simplest formula is given by the Schichman and Hodges model [43], which is implemented in most versions of SPICE programs.

The model has a number of inadequacies when it comes to modelling short channel MESFETs (which is the case for most MESFETs) [44].

These are as follows.

- a) The square-law relationship of  $I_{d_s}$  to  $V_{g_s}$  is often significantly different from the behaviour of the actual device.

- b) The approximately linear dependence of output conductance on  $I_{d_{4}}$  is often not observed (they are more often independent).

- c) The saturation of  $I_{ds}$  is assumed to be at  $V_{ds} V_{gs} V_t$ , whereas the actual device exhibits early saturation at a significantly lower voltage than the formula suggests.

A simple, more accurate, model was proposed by W.R. Curtice in 1980 [45], which incorporates a tanh function in the formula. It allows the linear and saturation regions to be modelled by the same equation. This model is used for all the simulations presented in this thesis and apart from the accuracy and simplicity, having access to the foundry measured parameters for this model was the main reason for choosing it.

The drain-to-source current  $[I_{d_s}]$ , described by the Curtice equation is as follows:

$$I_{ds} = \beta \left( V_{gs} - V_{t} \right)^{2} \left( 1 + \lambda V_{ds} \right) \tanh(\alpha V_{ds})$$

(2.1)

where  $\beta$  is the transconductance parameter,  $V_{gs}$  is the gate-source voltage,  $V_t$  is the threshold voltage,  $\lambda$  is the channel length modulation parameter,  $\alpha$  is the hyperbolic tangent drain voltage multiplier and  $V_{ds}$  is the drain-source voltage.

DC characteristics are defined by the model parameters  $V_t$  and  $\beta$  (which

determine the drain current with gate voltage), by  $\lambda$  (which determines the output conductance) and by the saturation current of the two gate junctions.

The following equations describe the threshold voltage and transconductance parameters [46]:

$$V_{t} = V_{bi} - \frac{qNa^{2}}{2\varepsilon}$$

(2.2)

$$\beta = \left(\frac{\mu_n \varepsilon}{2a}\right) \left(\frac{W}{L}\right)$$

(2.3)

where  $V_{bi}$  is the built-in potential, N is the effective channel doping density, q is the electron charge, a is the effective channel implant depth,  $\varepsilon$  is the permittivity,  $\mu_n$  is the electron mobility, W is the gate width and L is the channel length.

Charge storage is modelled by non-linear capacitances, defined by the parameters  $C_{gs}$  and  $C_{gd}$ . They are considered as Schottky-barrier diodes and modelled as :

$$C_{gs} = \frac{C_{go}}{\sqrt{1 - \frac{V_{gs}}{V_{bi}}}}$$

(2.4a)

$$C_{gd} = \frac{C_{go}}{\sqrt{1 - \frac{V_{gd}}{V_{bi}}}}$$

(2.4b)

where  $V_{gs}$  and  $V_{gd}$  are the gate-drain and gate-source voltages, and  $C_{go}$  is the zero bias capacitance.

The parameter values used in the model are given in Table 2.1 [47]. They are derived from an n-channel self-aligned GaAs MESFET process.

| Parameters used in the model        | Sym-<br>bol     | unit             | Values for<br>EFET    | Values for<br>DFET    |

|-------------------------------------|-----------------|------------------|-----------------------|-----------------------|

| Threshold voltage                   | V <sub>t</sub>  | .V               | 0.15                  | -0.5                  |

| Transconductance parameter          | β               | $A/V^2$          | 3.63×10 <sup>-4</sup> | $2.13 \times 10^{-4}$ |

| Channel length modulation           | λ               | 1/V              | 0.1                   | 0.13                  |

| Drain voltage multiplier            | α               | -                | 2                     | 2                     |

| Built-in voltage                    | V <sub>bi</sub> | v                | 0.6                   | 0.6                   |

| Effective channel doping<br>density | N               | cm <sup>-3</sup> | 1017                  | 1017                  |

| Implant depth                       | a               | Å                | 700                   | 1500                  |

| Dielectric permittivity             | ε               | F/cm             | $1.16 \times 10^{-2}$ | $1.16 \times 10^{-2}$ |

| Gate-source capacitance             | C <sub>gs</sub> | F                | $1.5 \times 10^{-15}$ | 1.3×10 <sup>-15</sup> |

| Gate-drain capacitance              | C <sub>gd</sub> | F                | $7.5 \times 10^{-16}$ | $6.5 \times 10^{-16}$ |

| Source and drain resistances        | $R_s, R_d$      | Ω                | 1500                  | 1150                  |

Table 2.1 Parameter values used in the MESFET model.

## 2.7 Important Effects Included in the Device Model

1

Having introduced the equations for the  $I_{ds}$  current and the gate capacitances, there are two important effects which have to be modelled. a) Transit-time effects

Transit-time is brought about by a finite delay in a change in  $I_{d_{\pm}}$  when the voltage at the gate is changed. This is due to the fact that charge transport occurs at a maximum velocity of  $10^7$  cm/s. Therefore, for a  $1\mu m$  channel length, it takes about 10ps for the current to change when the gate voltage is altered. This time delay is very important in delay calculation of GaAs circuits and can be included in the model by substituting the  $V_{gs}(t) = (V_{gs}(t-\tau))$  for  $V_{gs}$ , where  $\tau$  is the time delay.

b) Dispersion effects [48] [49]

There are a number of undesirable effects in GaAs MESFETs which may be significant in the performance of the overall circuits. One of the most dominant effects is the transconductance dispersion which is brought about by the non-ideal semi-insulating substrate and surface. This results in higher output conductance (order of 2-3 times) in saturation for high frequency signals than would be predicted from curve tracer or parameter analyser measurements.

One of the easiest way to model this effect is simply to increase the value of  $\lambda$  in the Curtice model from the value extracted for the low-frequency measurement to its high frequency value. Typically the high-frequency value is three orders of magnitude larger than the low-frequency value. Although this simple model ignores the effect of overshoot and phase shift due to dispersion effects, it is adequate for the performance evaluation of digital circuits presented in this thesis.

#### 2.8 Interconnect Modelling

The switching speed of MESFET circuits depends on both the device and interconnect lines. The propagation of a signal along an interconnect line is dependent on a number of factors. They include the distributed line resistance, capacitance and inductance, the impedance of the driving source and the cross-talk between the lines [50].

The interconnect for digital GaAs circuits can still be treated as purely capacitive provided the effective ON resistance of the driver gate is larger than that of the line by at least 2 orders of magnitude [51]. This is the case with the MESFET gates used in our circuits (see chapter three for design and analysis of logic gates).

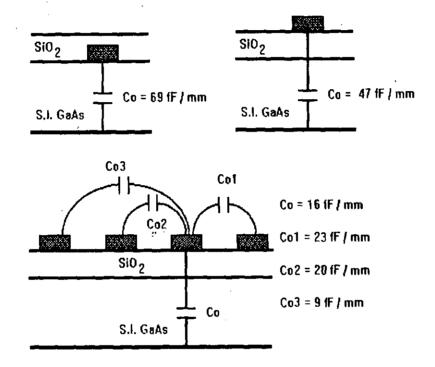

The capacitance of the lines can be derived using the parallel plate model

[52], but this simple model ignores the influence of the cross-talk (coupling) which can severely degrade the speed of GaAs VLSI circuits. There are several methods to reduce the effect of cross-talk. For example using a thick interlayer with low dielectric constant between the lines and the GaAs substrate can reduce the cross-talk by as much as 13%. A further 8% reduction can be achieved by using an air bridge technology where the interconnect lines are suspended in the air [53].

Figure 5.5 Line capacitance calculation.

In order to be able to predict accurately the performance of the overall GaAs circuits the effect of coupling must be included in the computer simulation. One effective method is to use Green's function to provide an electrode capacitance matrix for self and mutual capacitances of the lines by determining their total electron charge. This method provides accurate values for the capacitance of both the device and interconnect lines [54]. However as the number of conductors increases, the size of the capacitance matrix continues to grow and results in excessive CPU time and memory allocation to compute the capacitances and store the final values. Therefore in the computer simulation of the circuits presented in the following chapters the parasitic capacitances due to coupling are manually added to the capacitance of the lines in the critical paths and are based on the calculated results given in Figure 2.5. This provides a crude estimation, but sufficiently accurate results without any sacrifice in CPU time or memory allocation [55].

## **2.9 Effect of Process Variations**

Another important issue is the effect of process variation on circuit performance. The simulations performed in this research are all based on parameters for a commercial GaAs process. The parameters were also varied by as much as 50% to ensure that the results were valid for a large change in parameters. Therefore the proposed design approaches are believed to show a good tolerance to process spread. A detailed analyses of the process parameter spread is beyond the scope of this thesis and is not presented.

# CHAPTER 3 MESFET LOGIC FAMILIES FOR GaAs VLSI CIRCUITS

#### **3.1 Types of MESFET Logic Gate** [56] [57]

There are two main approaches to the design of MESFET logic gates. They are categorised as either Normally-ON or Normally-OFF logic gates. The Normally-ON logic gates consist of DFETs and were the first generation devices developed for GaAs digital circuits. The main reason for the development of this class of logic was the process maturity of DFETs. Later, when the yield and threshold voltage uniformity of EFETs were improved the Normally-OFF logic gates were introduced. They consist of both types of device (DFETs and EFETs) and possess characteristics essential for the implementation of VLSI circuits on GaAs (eg small area, low power dissipation etc).

Gate configurations based on these logic classes are described in this chapter. They are intended to show the trends and developments in GaAs logic design and further aid the choosing of a particular gate configuration best suited to VLSI implementation.

## **3.2 Normally-ON Logic Gates**

A number of approaches have been proposed for the design of this class of logic. They are: the Buffered FET Logic (BFL), Schottky Diode FET Logic (SDFL) and Capacitor-Coupled FET Logic (CCFL).

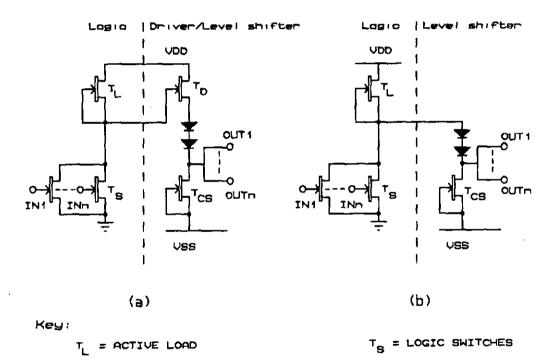

a) Buffered FET Logic (BFL) [58] [59] [60]

The basic structure for the BFL gate is shown in Figure 3.1a. It consists of two sections, the logic input and the driver/level Shifter output.

Different logic functions are implemented by modifying the logic input. The output driver is used to ensure input and output logic level compatibility between the gates. Also, in order to be able to turn off the DFET logic switch  $(T_s)$  of the driven gate, a negative supply voltage (VSS) is required which adds to the complexity of the gate.

This type of gate is considered to be one of the fastest, but is expensive in terms of power and area. Most of the power is dissipated in the driver section, therefore to reduce the power it is possible to remove the load driver DFET  $(T_D)$  in the output stage of the BFL gate, as shown in Figure 3.1b. This new configuration is called the Unbuffered FET Logic (UFL) and is more suitable for LSI applications. The absence of  $T_D$ , however, reduces the speed and fanout capability of the gate.

$T_D$  = LOAD DRIVER (SOURCE FOLLOWER)  $T_{CS}$  = CURRENT SINK Figure 3.1 (a) BFL gate with the load driver. (b) UFL gate without the load driver.

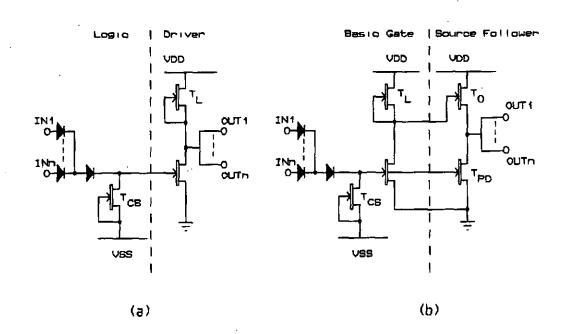

#### b) Schottky Diode-FET Logic (SDFL) [61] [62]

In this logic approach Schottky diodes are used to perform the logic

operations. They are followed by a Schottky diode for level shifting and a buffer stage. A possible configuration of the gate is shown in Figure 3.2a. The power consumption and area of this type of gate are less than the BFL gate but with lower speed and drive capability.

It is possible to increase the drive capability of the gate without excessive increase in power dissipation by adding a push-pull source follower at the output, as shown in Figure 3.2b. To improve the noise immunity of the gate, the power supply for the logic is normally isolated from the source follower.

Figure 3.2 (a) The basic SDFL gate. (b) SDFL gate with a source follower output stage.

## c) Capacitor-Coupled FET Logic (CCFL) [63] [64]

۰ţ

In order to overcome the problem of level shifting in the Normally-ON gates the natural choice is to use a capacitor to couple the input and output stages. Figure 3.3a shows a typical CCFL gate, where a reversebiased diode is used as the capacitor  $(D_{CAP})$ .

The gate has a very simple structure and requires only one supply rail.

In addition the power dissipation of the gate is low compared with BFL and SDFL gates. This is due to the fact that there is no power consumed in the capacitors. As soon as they are charged, the action thereafter is to transfer the charge between successive stages. Also, as the capacitor is placed in series with the DFET gate  $(T_{PD})$ , the capacitive loading is reduced and hence the speed of the gate is improved.

The use of a capacitor implies a minimum operational frequency of the circuit. This frequency is determined by the leakage currents and relative sizes of the coupling capacitor and reverse biased gate-source junction of the  $T_{PD}$ . For applications where the low frequency cutoff point is not acceptable, a combination of reverse and forward biased diodes is used to provide both the level shifting and capacitive coupling between the stages [65]. Figure 3.3b shows the basic structure of such a gate, called Capacitor-Diode FET Logic (CDFL). The gate area is increased as a result of adding the level shifting diodes but the low power dissipation is still maintained since the current through them can be made very small.

D = CAPACITOR DIODE

Figure 3.3 (a) CCFL gate configuration. (b) CDFL gate configuration.

## **3.3 Normally-OFF Logic Gates**

Normally-OFF logic includes Quasi-FET Logic (QFL) and the Direct-Coupled FET Logic (DCFL). These utilise EFETs as switching devices and have become increasingly popular as their yield is constantly being improved.

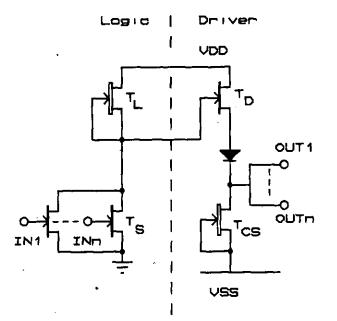

a) Quasi-FET Logic (QFL) [66]

The development of the Normally-OFF logic gates was hampered by the lack of maturity of GaAs processing in the 70's and early 80's. The major obstacle was the variation in threshold voltage across the wafer. The QFL gate was invented to allow for a wider spread in threshold voltage (-0.4 to 0.1V) with little effect on the noise margin of the gate. The gate consists of a logic and level shift circuit, as shown in Figure 3.4. The insensitivity of the gate performance to process variation is due to the level shift circuit. However, the circuit is operated in strong overdrive, with the supply voltage set at 2.5V, resulting in an increase in power dissipation. Unlike the Normally-ON logic gate (with the exception of the CCFL gate), the QFL gate requires only one supply rail but achieves comparable dynamic performance.

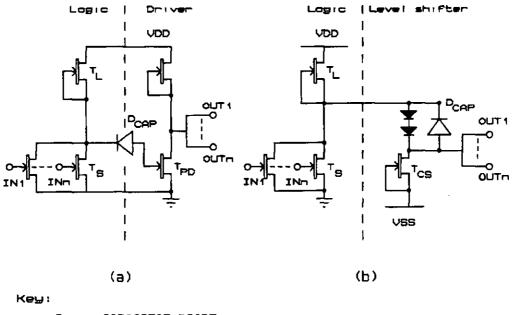

#### b) Direct-Coupled FET Logic (DCFL) [67] [68] [69] [70]

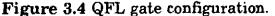

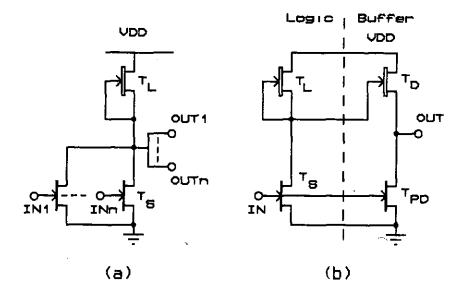

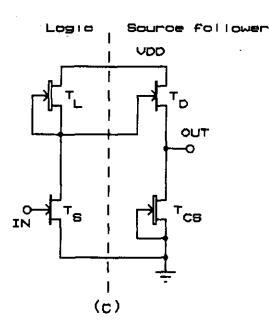

Figure 3.5a shows the basic structure of a DCFL gate. It consists of a DFET load (pull-up,  $T_1$ ) and an EFET switch (pull-down,  $T_s$ ), and closely resembles an nMOS gate. DCFL is much simpler than others mentioned so far, which leads to a higher packing density. DCFL gates with faster switching speeds (about 15ps) than any other GaAs logic gate have been fabricated. These results are however obtained with a large power supply voltage of 4V which causes the pull-down FET to be heavily forward biased, reducing the reliability of the gate. At a more realistic supply voltage ranges between 1 and 2V DCFL gate delays are slightly greater than that of the BFL gate. The main drawback with this type of gate is that the allowable output voltage swing is about 0.8V, equal to the barrier height of the Schottky gate diode of the driven EFET. Therefore, only small voltage swing can be expected from DCFL circuits, resulting in small noise margins. Also DCFL gates have a poor load drive capability which could severely limit the performance of large circuits with high fanout and long interconnect lines.

A possible solution to low noise margin and poor fanout capability is to use a super-buffer configuration as shown in Figure 3.5b. The output stage consists of a load driver ( $T_D$ , connected as a source follower) and a pull-down ( $T_{PD}$ ) EFET. They can be appropriately sized to drive a given capacitive load. The problem with the super-buffer configuration is that when the output logic level is to switch from a logic 'high' to a logic 'low', both the  $T_D$  and  $T_{PD}$  transistors are hard ON for a short period of time. Therefore a current spike appears with a momentary voltage drop in the supply line [71]. With many of these gates in a VLSI circuit switching at the same time, large voltage drops could be observed in the supply rail, giving rise to an incorrect logic operation. Therefore the use of superbuffer configuration necessitates a careful design of the supply lines.

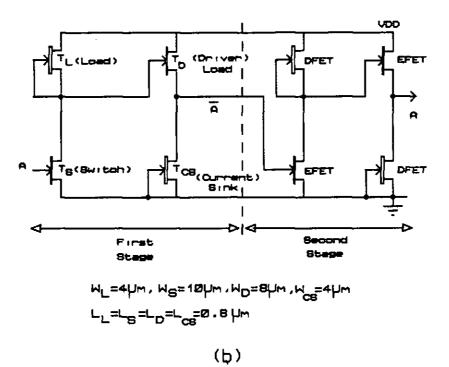

Another approach to improving the noise margin and fanout of the DCFL gate is to use the Source follower DCFL (SDCFL) gate [72]. Figure 3.5c

shows the SDCFL gate configuration. The source follower stage can be sized to drive a given load and due to the action of the  $T_D$  high values of noise margin can be obtained.

t

Figure 3.5 (a) DCFL gate configuration. (b) Super-buffer inverter. (c) SDCFL inverter.

## 3.4 Suitable Logic Gates for GaAs VLSI

The logic gate requirements for high speed VLSI circuits are explained in chapter one. They are, apart from high speed, low power dissipation and small area. The prospects of such gates for VLSI implementation are summarised by K. Lehovec et al. [46]. Taking the area of the logic gates into consideration, BFL and CCFL (>  $1000\mu m^2$ ) are limited to MSI complexity and the SDFL (>  $500\mu m^2$ ) gate can be used only for LSI structures. In other words Normally-ON logic gates are not suitable for VLSI on the basis of area alone.

Even with a larger chip area, these gates can not satisfy the power requirements for VLSI. The high power dissipation of the BFL gate (40mW) limits the integration level to MSI. CCFL and SDFL gates, with power dissipations of 2.5mW and 3.5mW respectively, can achieve only LSI complexity. According to H.C. Josephs [73] the power restriction for a high speed VLSI circuit would require logic swings of less than 1.8V. Further increase in the level of integration to Ultra Large Scale would require a voltage swing of 0.8V or less.

Therefore the DCFL gate with small area ( $\approx 200 \mu m^2$ ), low power dissipation (0.1-0.2mW) and low voltage supply level (1-2V), as well as circuit simplicity, is by far the strongest contender for GaAs VLSI implementation. SDCFL gate of comparable delay and power dissipation can also be used in conjunction with the DCFL to improve the fanout and interconnect drive capability. To show this, a detailed analysis of the SDCFL and DCFL gates is presented in section 3.7. They form the basis of the designs presented in the following chapters.

#### 3.5 First Order Design of DCFL and SDCFL Gates

The design of logic gates involves the determination of optimum transistor sizes. This stage is very important in the design process as the performance of the overall circuit is directly determined by the performance of the logic gates.

We begin by using the device model to give a first order approximation and an insight to the parameters influencing the choice of transistor sizes for DCFL and SDCFL gates. This is followed by a detailed computer simulation for various input/output conditions, supply voltage, etc to find the optimum transistor ratios.

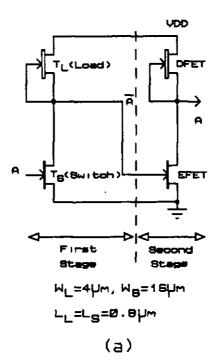

Figure 3.6a shows two basic DCFL inverters, with their typical interconnections. The current equation for the load DFET  $(I_L)$  and the switch EFET  $(I_s)$  are as follows [74]:

$$I_{L} = \beta_{L} (-V_{tL})^{2} \tanh(\alpha [VDD - V_{o}])$$

(3.1a)

$$I_{s} = \beta_{s} (V_{in} - V_{ts})^{2} \tanh(\alpha V_{o})$$

(3.1b)

Equating the two currents and using equation 2.3 we obtain :

$$\frac{W_s}{W_L} = \frac{a_L}{a_s} \frac{(V_{in} - V_{ts})^2}{(-V_{tL})^2} \frac{\tanh(\alpha V_o)}{\tanh(\alpha [VDD - V_o])}$$

(3.2)

For  $V_{in} = V_{\sigma} = \frac{VDD}{2} = 0.4V$ , equation 3.2 reduces to the form :

$$\frac{W_S}{W_L} = \frac{a_L}{a_S} \frac{(0.4 - V_{tS})^2}{(-V_{tL})^2}$$

(3.3)

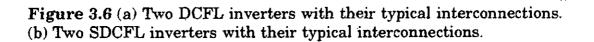

From equation 3.3 the ratio of the transistor widths can be determined for various values of load and switch threshold voltages, as shown in Figure-3.7. For an implant depth ratio  $(a_L/a_s)$  of 2:1 the transistor width ratio is reduced by a factor of three when the switch threshold voltage is varied from 250 to 150mV. The same effect is observed when the load threshold voltage is reduced from 900 to 500mV. The smaller device ratio results in smaller logic gates and ultimately smaller overall circuit. This justifies the choice of the threshold voltages given in table 2.1.

Figure 3.7 The gate width ratio  $(W_s/W_L)$  as a function of  $V_t$ . The solid lines are for the implant depth ratio of 2:1 and the dashed lines are for a ratio of 4:1.

The effect of the supply voltage derived from equation 3.2 is also shown in Figure 3.7 (dashed-dotted line). Above the gate built-in potential (0.8V) the effect of the supply voltage is minimal. Therefore the supply voltage can be set at 0.8V. However to account for the supply voltage variations, in practice, it is set to a higher value (1-2V).

Figure 3.6b shows two SDCFL inverters, with their typical interconnections. The logic part is the same as the DCFL gate and equation 3.2 can be used to determine the ratio of the active load  $(T_D)$  to logic switch  $(T_s)$ . The driver is added to improve the noise margin and the speed of the gate. The size of this stage is determined by the output drive requirement. Therefore, the input transistor sizing is independent of the

output drive requirements. However, the size ratio of the input switch to that of the driver load influences the gate intrinsic delay. The smaller the ratio the longer is the gate intrinsic delay.

## **3.6 Definition of Design Parameters**

In the following section the gates are evaluated in terms of noise margin, propagation delay and power dissipation. There are various definitions for these parameters. In order to avoid confusion, the definitions used in our analysis are given below.

a) Noise margin

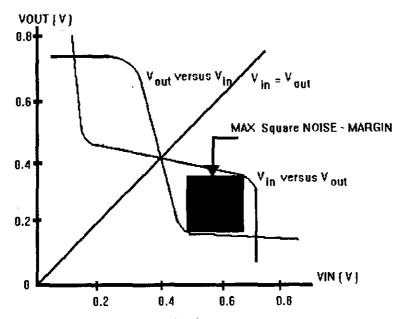

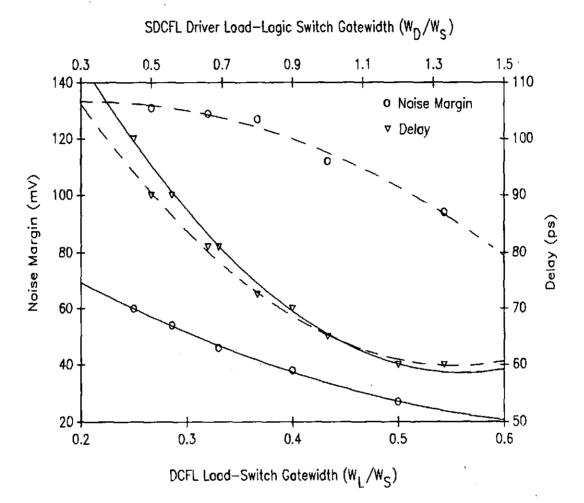

In the evaluation of the gates, we are interested in the worst case noise margin. Therefore only the static noise margin is considered which is found graphically using the 'mirror-and-maximum-square' method [75] [76]. In this approach, noise of equal and opposite amplitude is applied to the inputs of a flip-flop and the noise margin is measured as shown in Figure 3.8.

Figure 3.8 Noise margin calculation.

There are several other definitions of noise margin which can give results

slightly conflicting with the above method [77] [78]. In our analysis however, a detailed comparison of the gates is presented and only the relative values of the noise margins are of interest. Therefore, irrespective of the method used, the final conclusions should be the same. Indeed, the absolute values should also be confirmed by measurements on real devices.

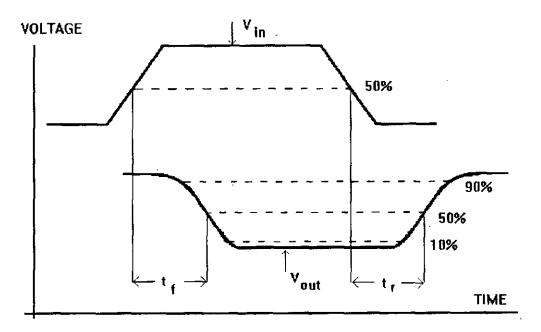

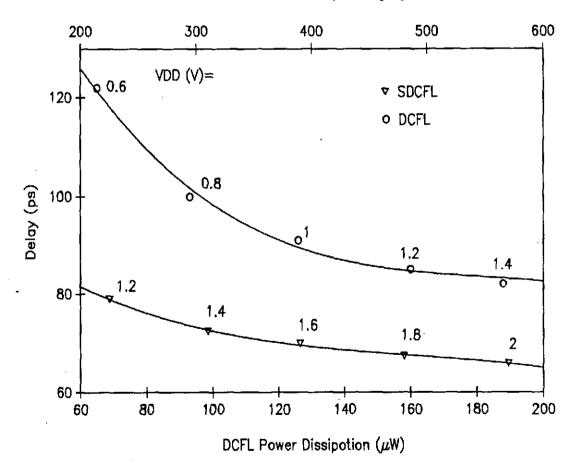

b) Propagation delay

The propagation delay is defined as the average of  $t_r$  and  $t_f(t_{\delta} = \frac{t_r + t_f}{2})$ , where  $t_r$  and  $t_f$  are shown graphically in Figure 3.9 [79].

Figure 3.9 Delay time calculation.

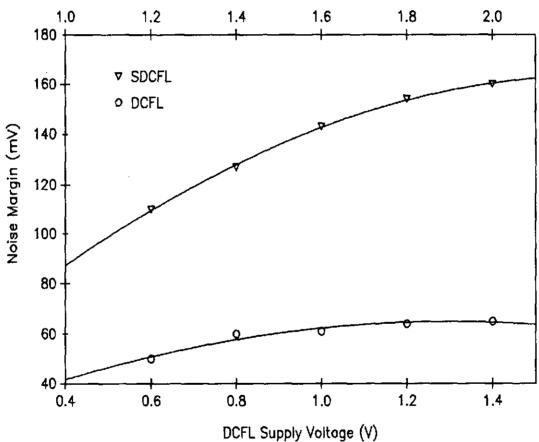

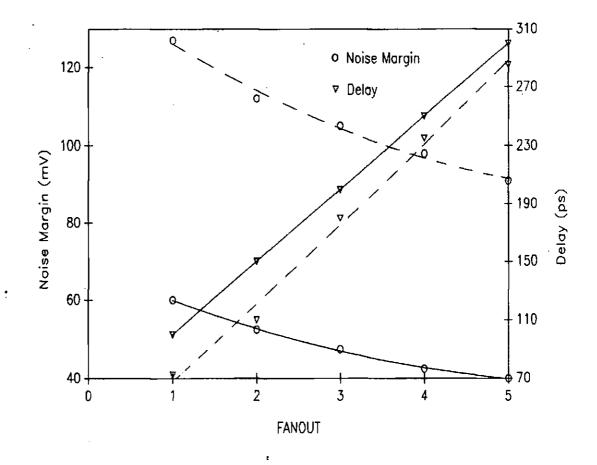

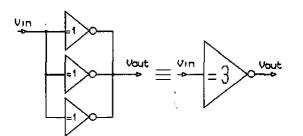

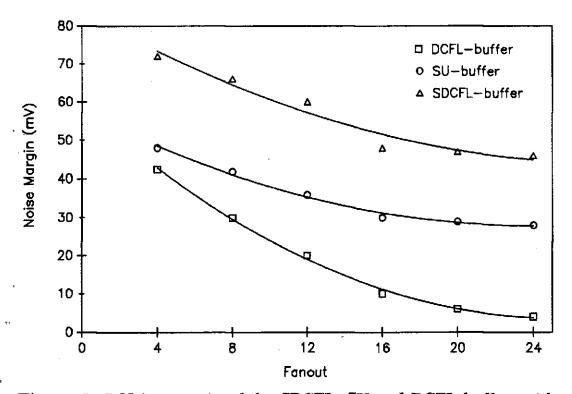

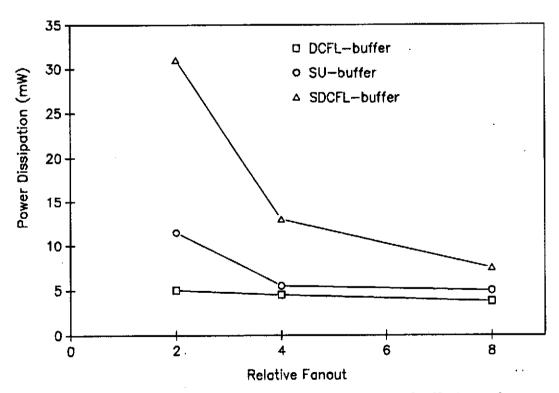

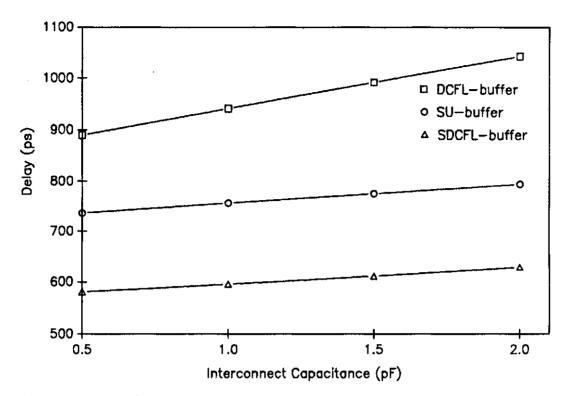

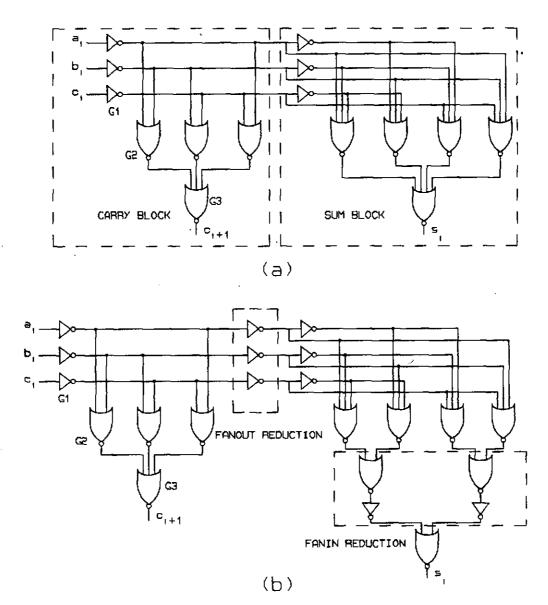

#### c) Power dissipation