# Middlesex University Research Repository:

an open access repository of Middlesex University research

http://eprints.mdx.ac.uk

Rajan, Amala Vijaya Selvi, 2009.

Formal semantics for LIPS (language for implementing parallel/distributed systems).

Available from Middlesex University's Research Repository.

#### Copyright:

Middlesex University Research Repository makes the University's research available electronically.

Copyright and moral rights to this thesis/research project are retained by the author and/or other copyright owners. The work is supplied on the understanding that any use for commercial gain is strictly forbidden. A copy may be downloaded for personal, non-commercial, research or study without prior permission and without charge. Any use of the thesis/research project for private study or research must be properly acknowledged with reference to the work's full bibliographic details.

This thesis/research project may not be reproduced in any format or medium, or extensive quotations taken from it, or its content changed in any way, without first obtaining permission in writing from the copyright holder(s).

If you believe that any material held in the repository infringes copyright law, please contact the Repository Team at Middlesex University via the following email address: <a href="mailto:eprints@mdx.ac.uk">eprints@mdx.ac.uk</a>

The item will be removed from the repository while any claim is being investigated.

# Formal Semantics for LIPS

(Language for Implementing Parallel/distributed Systems)

A thesis submitted to Middlesex University in partial fulfilment of the requirements for the degree of Doctor of Philosophy

Amala Vijaya Selvi Rajan

School of Engineering and Information Sciences Middlesex University Dedicated to Almighty

## Abstract

This thesis presents operational semantics and an abstract machine for a point-to-point asynchronous message passing language called LIPS (Language for Implementing Parallel/distributed Systems). One of the distinctive features of LIPS is its capability to handle computation and communication independently. Taking advantage of this capability, a two steps strategy has been adopted to define the operational semantics. The two steps are as follows:

- A big-step semantics with single-step re-writes is used to relate the expressions and their evaluated results (computational part of LIPS).

- The developed big-step semantics has been extended with Structural Operational Semantics (SOS) to describe the asynchronous message passing of LIPS (communication part of LIPS).

The communication in LIPS has been implemented using Asynchronous Message Passing System (AMPS). It makes use of very simple data structures and avoids the use of buffers.

While operational semantics is used to specify the meaning of programs, abstract machines are used to provide intermediate representation of the language's implementation. LIPS Abstract Machine (LAM) is defined to execute LIPS programs. The correctness of the execution of the LIPS program/expression written using the operational semantics is verified by comparing it with its equivalent code generated using the abstract machine.

Specification of Asynchronous Communicating Systems (SACS) is a process algebra developed to specify the communication in LIPS programs. It is an asynchronous variant of Synchronous Calculus of Communicating Systems (SCCS). This research presents the SOS for SACS and looks at the bisimulation equivalence properties for SACS which can be used to verify the behaviour of a specified process.

An implementation is said to be complete when it is equivalent to its specifications. SACS has been used for the high level specification of the communication part of LIPS programs and is implemented using AMPS. This research proves that SACS and AMPS are equivalent by defining a weak bisimulation equivalence relation between the SOS of both SACS and AMPS.

## Acknowledgements

I express my deep and sincere gratitude to my supervisors Dr. Geetha Abeysinghe and Dr. Siri Bavan for their outstanding guidance and encouragement throughout all the stages of this work. Both of them have been wonderful supervisors. Throughout this work, they provided encouragement, sound advice, good teaching, good company, and lots of valuable ideas. I would have been lost without their supervision and support. They taught me how to write and patiently guided me regardless of their very busy schedules. I am most grateful to both of them.

I am thankful to the School of Engineering and Information Sciences, Middlesex University, for their financial support during my study.

I am grateful to Dr. Foster, Dmitri, Dr. Ever, and Niveditha for their feedback on the draft of this thesis.

I thank my friends Dhawal, Satish, Yoney, Anjum, Lindsey, Yan, David, Yonal, and Aju. The friendship I have with them is what kept me going through tough times.

I owe my parents, Mary and Santiago, much of what I have become. I thank them for their patience, love and support. They took over a large part of my family responsibilities and encouraged me to concentrate on my studies.

I am deeply indebted to my husband Rajan for his friendship, trust, encouragement, and endurance of my bad temper.

My daughter Roshni Benedicta is my powerful source of inspiration and energy. Special gratitude is due to my nephew Rohit.

I fondly thank my sister, Jasmine and my brothers, Babu, Armstrong and Christopher and their families for their loving support.

I also thank my in-laws for their support.

## List of Publications

The results presented in this thesis have also appeared in the following publications:

- A.V.S. Rajan, A. S. Bavan, and G. Abeysinghe (2008), "An Equivalence Theorem for the Specification of Asynchronous Communication Systems (SACS) and Asynchronous Message Passing System (AMPS)", accepted for the International Joint Conferences on Computer, Information, and Systems Sciences, and Engineering (CISSE 2008) to be held in December 5 13, 2008, to be published in Springer.

- A.V.S. Rajan, A. S. Bavan, and G. Abeysinghe (2008), "Semantics for the Specification of Asynchronous Communicating Systems (SACS)", Advances in Computer and Information Sciences and Engineering, Springer, Sobh, Tarek (Ed.), 2008, pp. 33-38, ISBN: 978-1-4020-8740-0.

- A.V.S. Rajan, A. S. Bavan, and G. Abeysinghe (2007), "Semantics for a Distributed Programming Language Using SACS and Weakest Pre-Conditions", International Journal on Information Processing (IJIP), I K International Publisher, New Delhi - 110 016, India.

- A.V.S. Rajan, A. S. Bavan, and G. Abeysinghe (2007), "Semantics for an Asynchronous Message Passing System", Advances and Innovations in Systems, Computing Sciences and Software Engineering, Springer, Elleithy, Khaled (Ed.), pp. 83-88, ISBN: 978-1-4020-6263-6.

- S. Bavan, E. Illingworth, A.V.S. Rajan, and G. Abeysinghe (2007), "Specification of Asynchronous Communicating Systems", In Proceedings of IADIS Applied Computing 2007, Nuno Guimaraes and Pedro Isaias(Ed.), pp. 274-281, ISBN: 978-972-8924-30-0.

- S. Bavan, A.V.S. Rajan, and G. Abeysinghe (2007), "Asynchronous Message Passing Architecture for a Distributed Programming Language", In Proceedings of IADIS Applied Computing 2007, Nuno Guimaraes and Pedro Isaias (Ed.), pp. 674-678, ISBN: 978-972-8924-30-0.

- A.V.S. Rajan, A. S. Bavan, and G. Abeysinghe (2006), "Semantics for a Distributed Programming Language Using SACS and Weakest Pre-Conditions", in the Proceedings of the 14th International conference on Advanced Computing and Communications, IEEE Press, pp. 434-439, ISBN: 1-4244-0715-X.

# Contents

| 1 | Intr                         | oducti                                                        | ion                                                                  | 1  |  |

|---|------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------|----|--|

|   | 1.1                          | Distri                                                        | buted Programming Languages                                          | 1  |  |

|   | 1.2                          | Language for Implementing Parallel/distributed Systems (LIPS) |                                                                      |    |  |

|   | 1.3                          | Formal Semantics of Programming Languages                     |                                                                      |    |  |

|   | 1.4                          | Scope of Work                                                 |                                                                      | 6  |  |

|   |                              | 1.4.1                                                         | Operational Semantics for LIPS                                       | 6  |  |

|   |                              | 1.4.2                                                         | Operational Semantics for the Specification of Asynchronous Com-     |    |  |

|   |                              |                                                               | municating Systems (SACS)                                            | 8  |  |

|   | 1.5                          | Contr                                                         | ibution                                                              | 9  |  |

|   | 1.6                          | Struct                                                        | ture of the Thesis                                                   | 10 |  |

| 2 | $\operatorname{Lit}\epsilon$ | erature                                                       | e Review                                                             | 11 |  |

|   | 2.1                          | Parall                                                        | el/Distributed Programming Languages                                 | 11 |  |

|   |                              | 2.1.1                                                         | Occam                                                                | 16 |  |

|   |                              | 2.1.2                                                         | Ada                                                                  | 17 |  |

|   |                              | 2.1.3                                                         | Concurrent C                                                         | 19 |  |

|   |                              | 2.1.4                                                         | NIL                                                                  | 20 |  |

|   | 2.2                          | Opera                                                         | tional Semantics and Abstract Machine                                | 22 |  |

|   |                              | 2.2.1                                                         | Big-step semantics                                                   | 24 |  |

|   |                              | 2.2.2                                                         | Small-step semantics                                                 | 24 |  |

|   | 2.3                          | Forma                                                         | alism for High Level Specification of Parallel/Distributed Languages | 27 |  |

|   |                              | 2.3.1                                                         | Specification of Communication Part of Distributed Languages         | 28 |  |

|   |                              | 2.3.2                                                         | Formal Semantics for SACS                                            | 31 |  |

|   |                              | 2.3.3                                                         | Verifying the correctness of SACS specification                      | 32 |  |

|   | 2.4                          | Summ                                                          | nary                                                                 | 33 |  |

| 3 | An                           | Introd                                                        | luction to LIPS and AMPS                                             | 34 |  |

|   | 3.1                          | Struct                                                        | ture of a LIPS Program                                               | 35 |  |

|   |                              | 3.1.1                                                         | Network Definition                                                   | 35 |  |

|   |                              | 3.1.2                                                         | Nodes Definition                                                     | 37 |  |

|   | 3.2                          | Progra                                                        | amming LIPS                                                          | 40 |  |

|   |     | 3.2.1                            | Programming the Network Definition                                   |  |  |

|---|-----|----------------------------------|----------------------------------------------------------------------|--|--|

|   |     | 3.2.2                            | Programming the Nodes Definition                                     |  |  |

|   |     | 3.2.3                            | Compiling and Running a LIPS program                                 |  |  |

|   | 3.3 | Archit                           | ecture of the Asynchronous Message Passing System (AMPS) 43          |  |  |

|   |     | 3.3.1                            | The Data Structure of the AMPS                                       |  |  |

|   |     | 3.3.2                            | The Driver Matrix of the AMPS                                        |  |  |

|   | 3.4 | The O                            | peration of the AMPS                                                 |  |  |

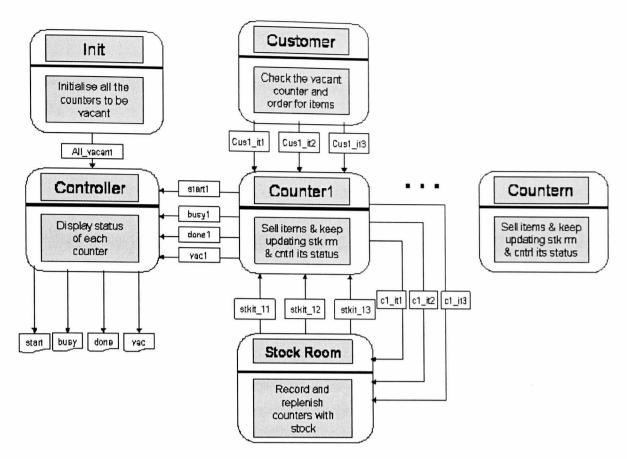

|   | 3.5 | Case S                           | Studies                                                              |  |  |

|   |     | 3.5.1                            | Case Study 1: Vending Machine Problem                                |  |  |

|   | 3.6 | Summ                             | ary                                                                  |  |  |

| 4 | Ope | eration                          | al Semantics for LIPS 50                                             |  |  |

|   | 4.1 | Opera                            | tional Semantics for the Computational Part of LIPS                  |  |  |

|   |     | 4.1.1                            | Abstract Syntax for the Computational Part of LIPS 55                |  |  |

|   |     | 4.1.2                            | Types in LIPS                                                        |  |  |

|   |     | 4.1.3                            | Operational Semantics for the Computational part of LIPS 59          |  |  |

|   | 4.2 | Abstra                           | act Machine for the Computational Part of LIPS 6                     |  |  |

|   |     | 4.2.1                            | Compilation of LIPS Program Expressions into LAM Codes 6             |  |  |

|   | 4.3 | Opera                            | tional Semantics for the Communication Part of LIPS 6                |  |  |

|   |     | 4.3.1                            | Primitives and Communication Schema for the Asynchronous Mes-        |  |  |

|   |     |                                  | sage Passing in the LIPS                                             |  |  |

|   |     | 4.3.2                            | Communication Schema for Asynchronous Communication                  |  |  |

|   |     | 4.3.3                            | Syntactic Categories for Asynchronous Communication                  |  |  |

|   |     | 4.3.4                            | Structural Operational Semantics (SOS) for the Asynchronous Com-     |  |  |

|   |     |                                  | munication                                                           |  |  |

|   | 4.4 | Re-wr                            | ite Rules and LAM Codes for the Communication Part of LIPS $$ . $$ 8 |  |  |

|   |     | 4.4.1                            | Compilation of Communication Part of LIPS into the LAM codes 8       |  |  |

|   |     | 4.4.2                            | Correctness of the LAM                                               |  |  |

|   |     | 4.4.3                            | Executing the LAM Code                                               |  |  |

|   | 4.5 | Summ                             | ary                                                                  |  |  |

| 5 | Ope | Operational Semantics for SACS 9 |                                                                      |  |  |

|   | 5.1 | 1 SACS - An Introduction         |                                                                      |  |  |

|   | 5.2 | Struct                           | ural Operational Semantics for SACS                                  |  |  |

|   |     | 5.2.1                            | Syntactic Categories of SACS                                         |  |  |

|   |     | 5.2.2                            | Labelled Transition System Configurations for SACS 10                |  |  |

|   | 5.3 | Equiva                           | alence Relation Properties of SACS                                   |  |  |

|   |     | 5.3.1                            | Trace Equivalence                                                    |  |  |

|   |     | 5.3.2                            | Bisimulation Equivalence                                             |  |  |

|   | 5.4 | An Eo                            | nuivalence Relation for the SACS and AMPS                            |  |  |

|                  | 5.5        | Summary                                                                 | <b>1</b> 25 |

|------------------|------------|-------------------------------------------------------------------------|-------------|

| 6                | Conclusion |                                                                         |             |

|                  | 6.1        | Contributions to the Knowledge                                          | 127         |

|                  | 6.2        | Future Work                                                             | 129         |

| $\mathbf{A}_{]}$ | ppen       | dices                                                                   | 132         |

| A                | San        | Sample LIPS Programs                                                    |             |

|                  | A.1        | Sample LIPS program - 1: Finding the area under a curve using Simpson's |             |

|                  |            | rule                                                                    | 133         |

|                  | A.2        | Sample LIPS program - 2: Vending Machine Problem                        | 134         |

| В                | Cas        | se Study - 2 - Post Office Scenario                                     | 136         |

# List of Figures

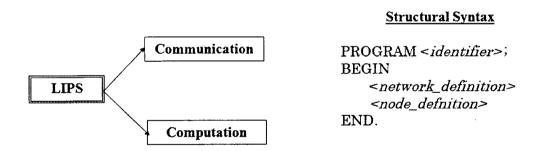

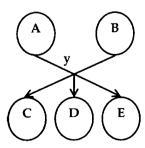

| 1.1  | Syntactic Structure of a LIPS Program                                                                | 4   |

|------|------------------------------------------------------------------------------------------------------|-----|

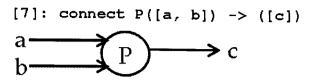

| 3.1  | Connect process                                                                                      | 36  |

| 3.2  | Data flow graph illustrating fan-in and fan-out effect via connect                                   | 36  |

| 3.3  | Channel with Multiple Outputs                                                                        | 37  |

| 3.4  | Channel with Multiple Inputs                                                                         | 37  |

| 3.5  | Looping Channel                                                                                      | 38  |

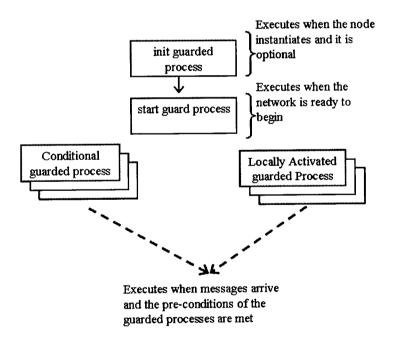

| 3.6  | Execution Sequence of Guards                                                                         | 39  |

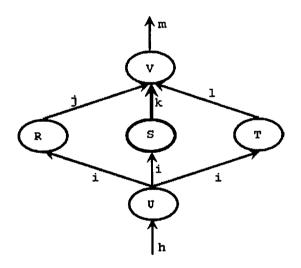

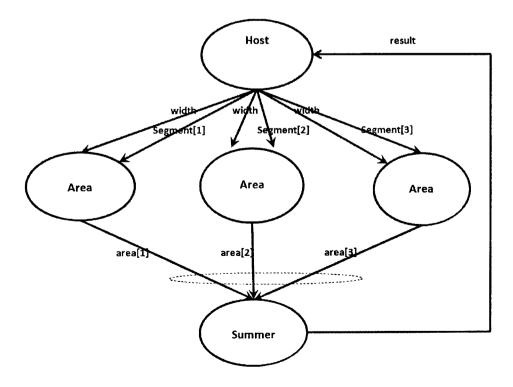

| 3.7  | Network Diagram for the Simpson's Rule problem                                                       | 40  |

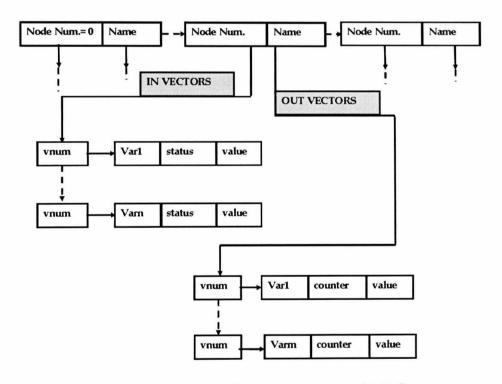

| 3.8  | Data Structure of the AMPS                                                                           | 44  |

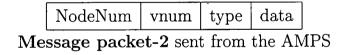

| 3.9  | Data Structure of the AMPS                                                                           | 45  |

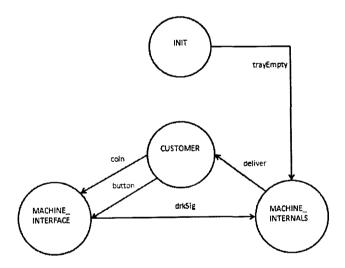

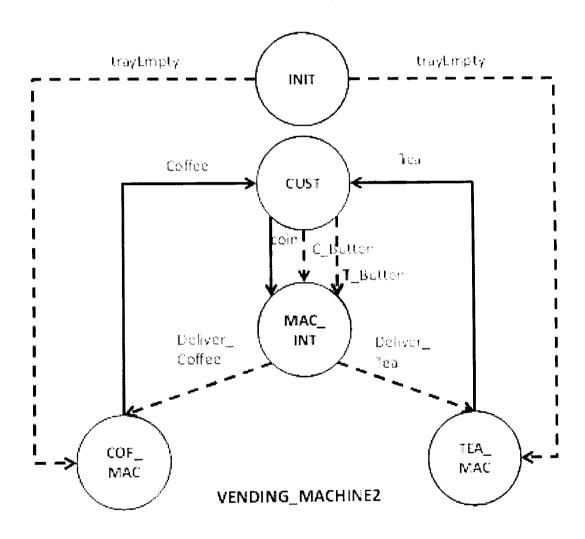

| 3.10 | Vending Machine                                                                                      | 47  |

| 3.11 | Data Structure for the Vending Machine Problem                                                       | 48  |

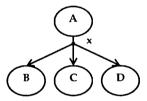

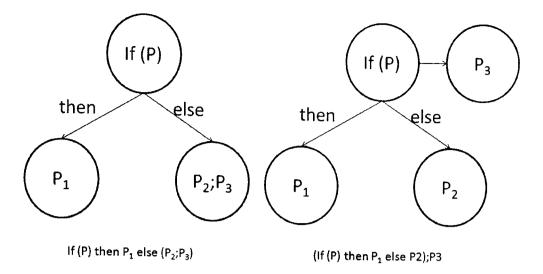

| 4.1  | Syntax Trees for "if P then P1 else (P2;P3)" and "(if P then P1 else                                 |     |

|      | P2);P3"                                                                                              | 56  |

| 5.1  | SACS specification for Simpson's Rule                                                                | 96  |

| 5.2  | SACS specification for the vending Machine Problem                                                   | 97  |

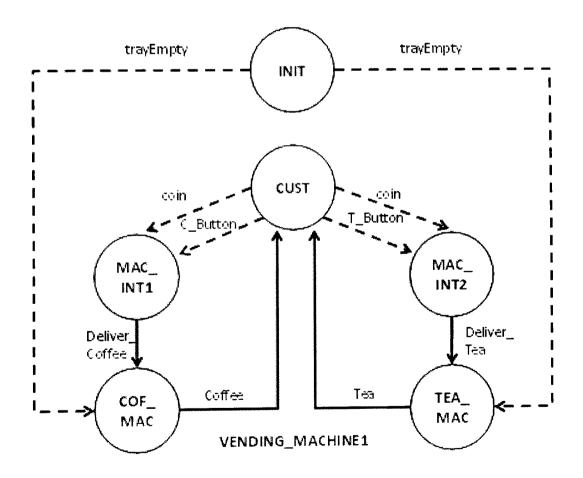

| 5.3  | VENDING_MACHINE1                                                                                     | 103 |

| 5.4  | SACS specification for VENDING_MACHINE1                                                              | 104 |

| 5.5  | VENDING_MACHINE2                                                                                     | 106 |

| 5.6  | SACS specification for VENDING_MACHINE2                                                              | 107 |

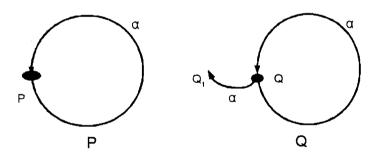

| 5.7  | Example - Trace Equivalence                                                                          | 110 |

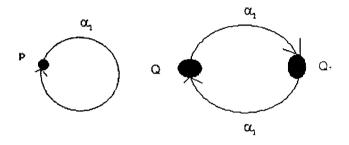

| 5.8  | Example - Strong Bisimulation                                                                        | 112 |

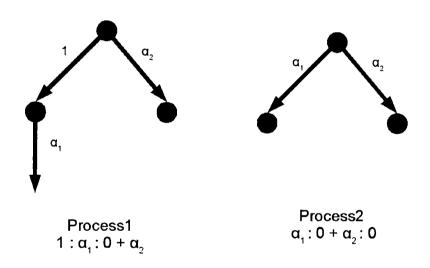

| 5.9  | $1: \alpha_1: 0+\alpha_2: 0 \text{ and } \alpha_1: 0+\alpha_2: 0 \ldots \ldots \ldots \ldots \ldots$ | 117 |

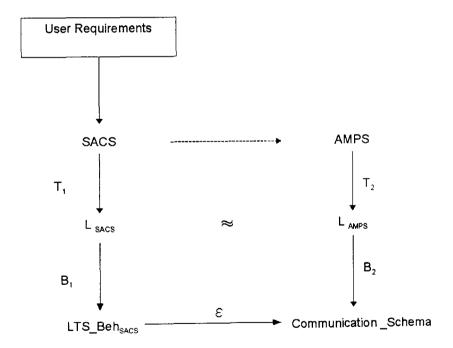

| 5.10 | Summary of the proof of equivalence between SACS and AMPS                                            | 120 |

| B.1  | Pictorial representation for the Post Office Problem                                                 | 137 |

| RЭ   | Data Structure of the AMPS                                                                           | 139 |

# List of Tables

| 2.1  | Comparison big-step semantics and small-step semantics  | 26  |

|------|---------------------------------------------------------|-----|

| 3.1  | Input and Output Channel table for the Simpson's rule   | 40  |

| 3.2  | Driver Matrix for the Vending Machine Problem           | 48  |

| 4.1  | Syntactic Categories for the Computational Part of LIPS | 53  |

| 4.2  | Set of Operators of LIPS                                | 53  |

| 4.3  | LIPS Statements/Expressions                             | 54  |

| 4.4  | Set of Operators of LIPS                                | 54  |

| 4.5  | Exp of LIPS Program Expressions                         | 55  |

| 4.6  | Type Assignments P :: $\sigma$ of LIPS                  | 57  |

| 4.7  | Compilation of LIPS Expressions into LAM Code           | 68  |

| 4.8  | Extended Data Types for the Communication Part of LIPS  | 69  |

| 4.9  | Functions Used in the AMPS of LIPS                      | 70  |

| 4.10 | Extended Type Assignments P :: $\sigma$ of LIPS         | 78  |

| 5.1  | Operators used in SACS                                  | 95  |

| 5.2  | Syntactic Categories of the SACS                        | 99  |

| B.1  | Driver Matrix for the Post Office Problem               | 138 |

# Chapter 1

# Introduction

The software industry is continuously making efforts to improve the quality of distributed programming languages. Formally specifying the syntax and semantics of programming languages offer a solution towards this goal. Formal specifications present a worthwhile subject of study due to the following reasons:

- They are used in requirement specification.

- They serve as a precise standard for compiler implementation.

- They provide a vehicle for verification and validation.

- They assist in language design.

- They provide useful user documentation.

This research aims to develop formal semantics for Language for Implementing Parallel/distrubuted Systems (LIPS) [Bavan and Illingworth, 2001].

## 1.1 Distributed Programming Languages

Programming languages can be classified into two main groups: sequential and distributed. Sequential programming languages such as FORTRAN, Pascal, and C are executed on a single processor. Distributed programming languages such as Occam [Inmos, 1988], Ada [Ledgard, 1983], NIL [Strom and Yemini, 1983, 1985], and Concurrent C [Gehani, 1990, Gehani and Roome, 1992] consist of number of simultaneous sequential processes which can be executed on a number of processors.

Different distributed programming languages exhibit different distinct features which include parallelism, communication, fault tolerance, architecture independency, understandability, implementability, optimality, functionality, and security [Bal et al., 1989, Skillicorn and Talia, 1998, Haridi et al., 1998]. This work considers three main issues

that distinguish a distributed language from a sequential language namely: ability to handle parallelism, communication, and separation of communication and computational components. They are considered briefly below:

- 1. **Parallelism**: This refers to the possible methods of running more than one part of program simultaneously. One important factor to be considered while designing a programming language is what to use as the unit of parallelism. A unit of parallelism can be expressed in terms of processes, objects, statements, expressions, and AND/OR clauses [Bal, 1990].

- For example, Ada handles parallelism through sequential processes called tasks, Emerald and Smalltalk use objects, while Occam uses statements. This work views parallelism as a set of processes executing simultaneously on different processors co-operating closely by communicating with each other.

- 2. **Communication**: This involves interaction between processes and their synchronisation. Communication between processes can be achieved by either shared memory or message passing.

- Shared memory multi-processor systems: Shared memory multi-processor systems provide a shared memory abstraction in which an application is written as if it were using a global address space. In other words, these systems are built using multiple high performance microprocessors which logically share a common memory [Stenstram and Dahlgren, 1996]. The fundamental features of shared memory are that the inter-process communication is implicit, synchronisation is explicit and the physical location of the data is completely unspecified [Kubiatowicz, 1998]. Though it is easy to program distributed applications using global address space which results in fast data sharing, shared memory systems require major communication overheads which degrade the efficiency of message passing and increase the cost. Concurrent Pascal [Brinch-Hansen, 1975], Algol 68 [Wijngaarden, 1981], Linda [Ahuja et al., 1986], Split-C [Culler et al., 1993], and Orca [Bal, 1996] are a few languages which use shared memory for inter-process communication.

- Message passing: Message passing is a paradigm used to establish interprocess communications via messages explicitly [Kubiatowicz, 1998]. The processors have their own local memory. They send and receive data independently to other processors directly or through an intermediate process that mimics point-to-point transfer of data. A defining feature of the message passing model is that data (the message) transfer from the local memory of one process to the local memory of another process requires operations to be performed by both processes. Languages such as Distributed Processes (DP) [Hansen, 1978], NIL, Occam, Ada, concurrent C, Fortran M [Foster and

Chandy, 1995], PFL [Holmstrom, 1983], and Bulk Synchronous Parallel (BSP) model [Krizanc and Saarimaki, 1996] employ message passing for communication.

Both shared-memory and message passing are dominant communication paradigms. Each approach has its own advantages and disadvantages. Several studies have been carried out analysing the performance of shared memory and message passing programming [Lin and Snyder, 1990, Ngo and Snyder, 1992, Klaiber and Levy, 1994, Kubiatowicz, 1998] and researchers have come up with a hybrid distributed shared memory communication model by combining the advantages of both paradigms.

There is also another type of system based on distributed data structure. A distributed data structure is a data structure that can be manipulated by many parallel processes simultaneously [Carriero et al., 1986]. Languages such as Linda [Carriero et al., 1986] and Orca [Bal, 1996] use distributed data structures.

The work presented in this report is based on message passing and does not delve much into either shared-memory or distributed data structures. There are four main message passing models: point-to-point, rendezvous, Remote Procedure Call (RPC), and one-to-many. Point-to-point communication can be either *synchronous* or *asynchronous*. Occam passes messages in a point-to-point synchronous fashion. Ada and Concurrent C pass messages in rendezvous manner. NIL uses point-to-point message passing in either a queued synchronous or an asynchronous fashion.

In *synchronous* communications, the sender waits for the receiver to receive the message. The sender and receiver must synchronise to exchange data. In *asynchronous* communication, the sender does not wait after sending data. The communication between processes is usually buffered using buffers of unlimited size. The need for large buffers results in memory overheads and loss of data. To address this issue, Bavan et al. [2007b] have introduced a new message passing strategy, AMPS (Asynchronous Message Passing System). It makes use of very simple data structures and avoids the use of buffers. A detailed description of AMPS is given in Chapter 3.

3. Separation of communication and computation: Yet a further issue, when developing a distributed programming environment, is the separation of the communication and computational components. Such separation better accommodates multiple communication and computational components. Most of the languages which achieve such separation employ different techniques/tools/language constructs for each of the two parts.

In the programming language Regis [Magee et al., 1994] the communication and computation are handled independently as below:

- the communication components are expressed using Darwin [Magee et al., 1993] and

- the computational elements are designed using C++.

Java has been extended with CORBA to provide a tool for developing concurrent systems [Hasselbring, 2000].

Considering the above issues, Bavan and Illingworth [2001] have taken a constructive approach to developing a distributed language to express parallelism using processes, pass messages asynchronously without message buffers, and handle communication and computational parts independently. This has led to the development of LIPS.

# 1.2 Language for Implementing Parallel/distributed Systems (LIPS)

Language for Implementing Parallel/distributed Systems (LIPS) is an asynchronous message passing distributed programming language which is simple and portable. One of the distinct feature of LIPS is that it handles communication and computation independently. A LIPS program consists of a network of nodes described by a network definition and node definitions. The syntactic structure of a LIPS program is shown in Figure 1.1.

Figure 1.1: Syntactic Structure of a LIPS Program.

The network definition describes the topology of the program by naming each node/process and its relationships (in terms of input and output data) to other nodes in the system. A node consists of one or more guarded processes which perform computations using the data that arrive as input and produces outputs that are sent to other relevant nodes.

LIPS offers distinct advantages: it is simple, portable, and it handles communication efficiently so that it avoids deadlock and livelock problems. Detailed description on LIPS can be found in [Bavan and Illingworth, 2001]. This research continues on the work already done on LIPS and seeks to develop the formal semantics and specifications which are currently lacking. This topic is expanded upon in subsequent sections.

## 1.3 Formal Semantics of Programming Languages

Formal semantics of a programming language is concerned with the rigorous mathematical study of meanings to programming languages and models of computation. Work on defining formal semantics for programming languages started in early 1960s [Papaspyrou, 1998, Jones, 2001]. There are number of approaches to formally specify the semantics of programming languages. They can be grouped into three categories [Andrew and Andrew, 1998] as given below:

1. **Denotational Semantics** defines the meaning of programs using suitable mathematical notations, typically functions from inputs to outputs. Denotational semantics maps a program directly to its meaning, its denotation [Schmidt, 1986].

Denotational semantics was originally described by Scott and Strachey [1971]. It was used to devise methods for the analysis of programming languages. Further developments helped it to be used as a powerful tool for the design and implementation of programming languages [Slonneger and Kurtz, 1995].

2. Axiomatic Semantics defines the meaning by describing the properties about the language constructs which hold before and after the execution of the programming constructs. The properties of the language constructs are expressed in terms of predicates and deduction rules using symbolic logic and they support program verification.

Floyd [1967] proposed a method to verify the correctness of programs by representing a program as a directed graph. Instead of specifying the programs as graphs, Hoare [1969] proposed a method of program verification which describes programs using axioms. This formed the basis for axiomatic specification. Even though Hoare's work was successful, it supported only partial correctness<sup>1</sup> as opposed to total correctness<sup>2</sup>. Dijkstra's [1976] work on weakest precondition algebra overcomes this problem as it supports total correctness.

3. Operational Semantics defines the meaning of programs in terms of their behaviour. For example, it describes the executional behaviour of a programming language for implementation purposes and gives a computational model for the programmers to refer to. Operational semantics, where a language is represented as an abstract machine, is used to define and implement the language [Kramer, 1994].

Denotational semantics is more abstract than operational semantics. Operational semantics gives the computational steps in the form of an algorithm whereas denotational semantics does not. Axiomatic semantics is far more abstract than denotational and

<sup>&</sup>lt;sup>1</sup>Partial correctness requires that if a result is returned it will be correct

<sup>&</sup>lt;sup>2</sup>Total correctness requires a result to be returned along with termination of the program

operational. Assertions and inference rules are used to define the language constructs. It is suitable for program verification. These three semantics are not in competition but they complement each other and serve different purposes. While denotational semantics and axiomatic semantics are used to reason about the programs and prove properties of programs, operational semantics is used to implement a language and prove the correctness of compiler implementation. Operational semantics is mainly used for a theoretical implementation of a language.

A relatively higher level of description of the semantics is acheived by translating the abstract syntax of a language into instructions of a simple machine using a finite collection of rules. Such a machine is called an abstract machine [Prasad and Arun-Kumar, 2002]. An abstract machine is a model of a computer system constructed to analyse how the computer system works [Hannan and Miller, 1992]. It can be proved that abstract machine is correct for its operational semantics. The correctness can be verified by checking whether the result of executing a program expression using the operational semantics matches with that of the abstract machine [Crole, 2006].

## 1.4 Scope of Work

This work considers the development of formal semantics for the language LIPS. In this context, we present the operational semantics and abstract machine for LIPS.

## 1.4.1 Operational Semantics for LIPS

Work on operational semantics started in 1960s. Landin [1963, 1965] created an abstract machine called the SECD (Stack, Environment, Code, Dump) machine to specify ISWIM (If you See What I Mean), a functional programming language [taken from [Prasad and Arun-Kumar, 2002]]. The SECD machine has been used to evaluate the Lambda expressions and formed a basis for the prototype implementations of functional programming languages [Danvy, 2003]. McCarthy's [1963, 1962, 1967] contributions during the same time period include the introduction of abstract syntax which has formed the basis for all the approaches to the semantics of programming languages.

Operational semantics was not highly regarded until radical changes were proposed by Khan, Milner, Plotkin, and others which led to a Structural approach to Operational Semantics (SOS) [Andrew and Andrew, 1998].

There are many styles of operational semantics with different terminologies and naming conventions. Natural semantics, big-step semantics, small-step semantics, transitional semantics, structural operational semantics are few example terminologies. Generally big-step semantics refers to natural semantics. But, Glesner [2003] refers to both big-step and small-step semantics as natural semantics. Peralta et al. [1998] group operational

semantics in to two categories: big-step/natural semantics and small-step or Structural Operational Semantics (SOS).

Big-step semantics describe the computations as large steps providing direct relation between initial and final states of computation [Slonneger and Kurtz, 1995] whereas, SOS describe how the individual steps of computation takes place. Big-step semantics is simple and easy to implement but it can only specify configurations related to the finite computations which makes it less suitable to specify parallelism.

#### SOS can

- 1. convey the order of execution,

- 2. express the properties of looping programs, and

- 3. reveal concurrency.

Due to these capabilities, it can be used to specify the communication part of a distributed language.

Combining the advantages of big-step and Structural Operational Semantics, a mixed two step strategy has been adopted to develop the operational semantics for LIPS. The two steps are as below:

- Firstly, big-step semantics is used to specify the expressions and their evaluated results (computational part of LIPS).

- Secondly, the developed big-step semantics is extended with Structural Operational Semantics (SOS) to describe the asynchronous message passing of LIPS (communication part of LIPS implemented using AMPS).

While operational semantics is used to specify the meaning of programs, abstract machines are used to provide intermediate representation of the language's implementation. An abstract machine is a re-writing system consisting of re-write rules to explicitly state the steps involved in the process of execution [Hutton and Wright, 2005]. It can be used to specify a way of implementing a language on some low-level computing machine or translating it to a lower-level or machine level language. The correctness of the defined abstract machine can be verified against its operational semantics. An abstract machine is considered to be correctly implemented against its operational semantics when an expression executed according to the operational semantics matches with the result of executing it with the abstract machine and vice versa.

An abstract machine called the LIPS Abstract Machine (LAM) has been defined to execute LIPS programs. The LAM was inspired by Crole [2006] and it works on the principle of re-write rules. Re-write rules are used to describe an abstract machine that maintains

a state and transforms it into a final state by repeatedly applying a given set of rules [Pingali and Ekanadham, 1988]. They explicitly show individual steps of execution and provide an intermediate level of representation for many practical implementations of programming languages [Hannan and Miller, 1992].

Using LAM the research proves the correctness of LIPS programs. This will be done by comparing the result of the code written using the LAM with the result of executing the same code written using the operational semantics.

# 1.4.2 Operational Semantics for the Specification of Asynchronous Communicating Systems (SACS)

Process algebra can be used to specify the communication between processes in a distributed environment. Because of its expressiveness and strong theoretical foundations, process algebra not only refers to algebraic specification but also to a method of verifying concurrent processes. Few of the well known process algebraic tools include Communicating Sequential Processes (CSP) [Hoare, 1978], Calculus of Communicating Systems (CCS) [Milner, 1982], Synchronous Calculus of Communicating Systems (SCCS) [Gray, 2000], and Language of Temporal Ordering Specifications (LOTOS) [Logrippo et al., 1990].

Since its development many extensions have been proposed for CCS to model different aspects of concurrent processing [Galpin, 1998] and Specification of Asynchronous Communicating Systems (SACS) [Bavan and Illingworth, 2000, Bavan et al., 2007a] is one of them. SACS is an asynchronous variant of SCCS which uses a point-to-point message passing system. It is developed to specify the communicating part of LIPS programs so that the communication and computation parts of LIPS can be handled independently. SACS uses the same syntax as that of SCCS but its semantics are different and governed by four design rules. It is developed by applying restrictions to the manner in which the SCCS is used and these restrictions are given in the form of design rules. These rules guarantee reliable message passing. The design rules are stated in Section 2.3.1 of Chapter 2.

Operational semantics is defined for CCS and other process algebras to precisely define the

- 1. set of rules for each operator in CCS,

- 2. execution steps that processes may engage in [Cleaveland and Smolka, 1990].

The semantics may be used to characterise the behaviour of the process algebraic description. Also, operational semantics can be used as the basis of bisimulation equivalence. Milner has introduced the concept of bisimilarities which have influenced the development of process calculi [Gordon, 1998]. Two processes are said to be bisimilar if there exists a

binary relation between the two processes such that whenever two processes are related and one can do an action, the other can match the action in such a way that the resulting processes remain related. Bisimulation is based on the idea of processes mimicking each other's behaviour [Fencott, 1996]. For example, Cleaveland and Smolka [1990] have defined an Structural Operational Semantics for CCS and shown how the defined semantics characterises the behaviour of CCS. Similarly, Fencott [1996] has defined operational semantics for CCS and Timed Calculus of Communicating Systems (TCCS) [Chen et al., 1990]. The behaviour is described using a set of Labelled Transition Systems (LTS) which consist of a collection of possible system states and transitions which have been used to study the equivalences. As the operational semantics and equivalences relations are not defined for SACS, this research considers defining the operational semantics and studying various bisimulation equivalence properties applicable to SACS.

An implementation is said to be complete one only when we prove that it meets its specifications and to prove that we need to prove an equivalence relation between the specification and its implementation. SACS has been used for the high level specification of the communication part of LIPS programs and is implemented using the Asynchronous Message Passing Systems (AMPS). It is necessary to study the proof of equivalence of SACS and AMPS to prove the completeness of AMPS. The operational semantics of both SACS and AMPS are based on Structural Operational Semantics (SOS) using Labelled Transition Systems. We then have two labelled transition system semantics: one for SACS and one for AMPS. To prove that they are equivalent, it is enough if we can prove the bisimilarity of these two labelled transition systems.

So, by defining the operational semantics for LIPS and SACS, we try to address the research question,

"Can operational semantics and SACS in combination be a suitable tool to describe the formal semantics for LIPS?"

## 1.5 Contribution

The main contribution of this thesis is a formal description for the semantics of the LIPS programming language. The formal semantics developed has been verified for its correctness with the main focus on the communication part. This can be found in Chapter 5 where a proof of equivalence of SACS, a tool to specify the asynchronous communication, and AMPS, its implementation, has been derived using labelled transitions. An abstract machine has also been developed and it is tested for correctness with its operational semantics. This can be found in Chapter 4. Additional contributions made as a result of this research are listed below:

- Structural Operational Semantics (SOS) and study of equivalence relation properties for SACS are described in Chapter 5. This study reveals that SACS with minor changes can be used to specify any asynchronous communicating system.

- The SOS for the Asynchronous Message Passing System (AMPS) of LIPS defined as part of the operational semantics for LIPS described in Chapter 4 will make AMPS a stand alone virtual machine which can be implemented in any asynchronous communicating applications without buffers.

- A compiler has been developed using JFlex, CUP and java. It has been tested with simple applications for its capability to implement AMPS and pass messages asynchronously.

## 1.6 Structure of the Thesis

The thesis is structured in the following way:

- Chapter 2 reviews the literature most relevant to the subject of investigation. This includes the following areas:

- 1. Few distributed programming languages which involve message passing,

- 2. Operational Semantics and abstract machine which can be used to describe distributed programming languages,

- 3. Specification of Asynchronous Communicating Systems and its formal semantics.

- Chapter 3 introduces the fundamental concepts of LIPS, the language under consideration. It also gives an introduction to the Asynchronous Message Passing System (AMPS) proposed for LIPS. The AMPS of LIPS has been developed to achieve asynchronous message passing across platforms without any message buffers.

- Chapter 4 describes the operational semantics of LIPS and its abstract machine, LAM. The chapter demonstrates the correctness of the LAM with respect to the defined operational semantics.

- Chapter 5 gives a brief introduction to SACS, defines the Structural Operational Semantics (SOS) for SACS and discusses the equivalence relation properties for SACS. This chapter also verifies the asynchronous message passing implemented using AMPS against SACS.

- Chapter 6 summarises the findings and contributions of this work and discusses directions for future research.

# Chapter 2

# Literature Review

Designing a distributed language which can pass messages asynchronously, and handle communication and computation independently has always been a challenge and formal methods of specification are generally used for this purpose. This research is concerned with the development of operational semantics for LIPS, a Language for Implementing Parallel/distributed Systems and SACS, the Specification for Asynchronous Communicating Systems. SACS is a process algebraic framework used to specify the asynchronous communicating processes in a LIPS program.

In this chapter we review the literature relevant to the subject and is divided into the following subsections:

- Section 2.1 gives an overview on some of the parallel/distributed programming languages which use message passing for communication and justify the need for a distributed programming language like LIPS.

- Section 2.2 discusses the existing operational semantics that have been used to specify parallel/distributed programming languages and analyses the necessity for a mixed approach to specify the semantics of a distributed programming language.

- Section 2.3: discusses about the Specification of Asynchronous Communicating Systems (SACS). It also considers the correctness of specification using SACS with its implementation. The objective is to prove that the implementation created for a system involving asynchronous communication in a LIPS program meets its requirement specification created using SACS.

- Section 2.4: This section concludes the literature review.

# 2.1 Parallel/Distributed Programming Languages

A number of parallel/distributed languages have been proposed that employ message passing for communication. Bal's [1990] survey on programming languages for distributed

computing has discussed three main issues that distinguish parallel/distributed languages from sequential languages, namely parallelism, communication, and partial failures. Work on languages for parallel computation by Skillicorn and Talia [1998] has listed six properties that a useful parallel programming language should have, which are, programmability, efficient methodologies, architectural independence, understandability, implementability and optimality. Haridi et al.'s [1998] survey on programming languages for distributed applications is concerned with five issues while designing a distributed programming language, namely, functionality, distribution structure, open computing<sup>1</sup>, fault tolerance and security. Haridi et al. also have proposed a design for a distributed programming language called Distributed Oz which separates the application functionality from its distribution structure. A review on the issues listed by these authors would be beyond the scope of this thesis. This work therefore will consider three main issues namely: ability to handle parallelism, communication, and separation of communication from computation.

This section describes these issues and reviews some of the popular parallel/distributed programming languages.

#### 1. Parallelism:

As stated in Chapter 1 parallelism refers to the possible methods of running more than one part of a program simultaneously. A unit of parallelism can be expressed in terms of processes, objects, statements, expressions, AND/OR clauses [Bal, 1990] and they are described below:

(a) **Processes**: A process is a logic unit consisting of a set of instructions to be executed sequentially and has its state and own data. Parallelism is based on processes in many procedural languages for distributed programming [Bal et al., 1989].

Ada [Ledgard, 1983], concurrent C [Gehani, 1990, Gehani and Roome, 1992], Linda [Carriero et al., 1986, Ahuja et al., 1986], Erlang [Armstrong, 2007], and NIL [Strom and Yemini, 1983, 1985] are some of the languages which use process as a unit of parallelism. Using the notion of process gives greater flexibility to the programmer as they can preset the communication channels between processes. But individual mechanisms are needed to set up the communication channels for passing messages and extra efforts are needed to prevent processes communicating with terminated processes. Some of the techniques used are setting the status of the channels and guarding the processes, which can be used independently or in combination.

<sup>&</sup>lt;sup>1</sup>Open computing is a general and inclusive term that is used to describe a philosophy of building IT systems. In hardware, open computing manifests itself in the standardization of plug and card interfaces; and in software, through communication and programming interfaces. Open computing allows for considerable flexibility in modular integration of function and vendor independence [Heintzman, 2003].

(b) **Objects**: They are self contained units with associated data and method. Languages that use objects to structure their programs are called as object oriented languages. These languages express parallelism in two ways. One way is to use an object to express a unit of parallelism and the another way is to use the tradition notion of processes to express parallelism.

Emerald [Hutchinson, 1987] is an object-based language that allows objects fixed on a specific processor to be unfixed and moved to a different processor at runtime. Smalltalk [Horwat, 1988], an object oriented programming language, allows both objects and processes to express parallelism. Handling objects as parallel units is similar to using processes as parallel units.

(c) **Statements**: Statements can be grouped so that they can be used express a unit of parallelism. There are programming languages which allow statements to be executed either sequentially or in parallel.

Occam [Inmos, 1988] uses the keywords SEQ (sequential) and PAR (parallel) before a group of statements to express sequential and parallel executions respectively.

For example, the following code will execute statements S1 and S2 sequentially:

SEQ

S1

S2

The following code will execute statements S1 and S2 parallely:

PAR

S1

S2

It is an easy to use but an uncommon method of achieving parallelism.

(d) Functions: A function is a program unit which returns a single value whenever called by the main program. Functions are used in both procedural and functional languages. In functional languages like Haskell [Jones, 2003], the result of a function depends only on its input values. But in procedural languages, the result of one function may depend on one or more other functions. All function calls in a program can be executed in parallel with the exception to functions which use the result of other functions. It is not a popular method as it is not good practice to evaluate all the functions in parallel. If a parallel function is doing a simple task, the overheads involved in parallel execution may outweigh the savings in computer time.

Data flow languages such as VAL (Value-oriented Algorithmic Language) [Acherman et al., 1979] are based on this principle [Bal et al., 1989].

(e) AND/OR clauses: There are two methods of implementing parallelism in logic programming namely, OR and AND parallelism. OR parallelism is used when several alternative clauses for a goal are executed in parallel. AND parallelism is used when two or more goals of the same clause are executed simultaneously Ertel [1991]. This method of achieving parallelism is used in parallel logic languages such as Concurrent Prolog [Shapiro, 1986]. Apart from AND/OR parallelism, processes are also used to implement parallelism in logic programming.

Considering the above methods of achieving parallelism, it can be inferred that using processes to express parallelism is the most commonly used method which is also used by object oriented and logic programming languages.

Assigning the processes to processors can be fixed at compile time, runtime or anytime [Bal, 1990]. The advantage of assigning processes at compile time is that the developer knows which process will be running on a specific processor. But it suffers from a limitation that this method of mapping is less flexible and restricted. StarMod is a concurrent language which uses this concept [Cook, 1980]. Assigning processes for parallel processing during runtime may seem to be a flexible method but it needs extra programming to allocate and reallocate the processes to processors automatically. Concurrent PROLOG achieves parallelism using Logo-like<sup>2</sup> turtle programs developed by Shapiro Shapiro [1986] where each processor can communicate with four neighbour processors. Assigning processes to processors anytime allows high flexibility as one can switch between compile time and runtime methods. For example, the language Emerald [Hutchinson, 1987] uses this concept of non-mapping. Emerald is an object-based language that allows objects fixed on a specific processor to be relocated to different processors at runtime.

#### ii. Communication:

In order for the parallel/distributed programming languages to execute the processes, they must communicate and synchronise. The inter-process communication in a parallel/distributed language may take place using *shared memory* or by *message passing* which are two opposing communication models.

#### (a) Shared memory multi-processor systems:

These systems provide a shared memory abstraction in which an application

<sup>&</sup>lt;sup>2</sup>Logo, a dialect of the Lisp language, is a programming language created in 1967. It was used to control a simple robot called turtle which is represented as a screen turtle on the computer screen in the recent versions [Friendly, 1988]. Each turtle has state with a position on the screen and a heading showing the direction it is facing. There are methods for moving the turtle in steps in just four directions around a grid, and for moving the turtle in all directions with pixel or better accuracy.

is written as if it were using a global address space. In other words, these systems are built using multiple high performance microprocessors which logically share a common memory [Stenstram and Dahlgren, 1996]. Languages implemented using shared memory multi-processor systems include Concurrent Pascal (Brinch-Hansen, 1975), Linda [Ahuja et al., 1986, Carriero and Gelernter, 1989], Algol 68 [Wijngaarden, 1981], Split-C[Culler et al., 1993], Orca [Bal, 1996], and Mesa [Geschke et al., 1977, Andrews and Schneider, 1983, Bal et al., 1989]. The fundamental features of shared memory are that the inter-process communication is implicit, synchronisation is explicit and the physical location of the data is completely unspecified [Kubiatowicz, 1998]. Though it is easy to program distributed applications using a global address space which results in fast data sharing, shared memory systems require major communication overheads which degrade the efficiency of communication and increase the cost.

#### (b) Message Passing:

Message passing is a paradigm used to establish inter-process communications via messages explicitly [Kubiatowicz, 1998]. The processors have their own local memory and they send and receive data independently to other processors directly or through an intermediate process that mimics point-to-point transfer of data. Languages such as Distributed Processes (DP) [Hansen, 1978], NIL [Strom and Yemini, 1983, 1985], Occam [Inmos, 1988], Ada [Elsom, 1989], concurrent C [Gehani, 1990], Fortran M [Foster and Chandy, 1995], PFL [Holmstrom, 1983], and Bulk Synchronous Parallel (BSP) model [Krizanc and Saarimaki, 1996] employ message passing for communication. The basic component of message passing is the point-to-point communication to send and receive data between two processes. Typical point-to-point communication can be either synchronous or asynchronous.

In synchronous communications, the sender waits until the complete message can be accepted by the receiving process and the receiver waits until the expected message arrives. This type of message passing is also referred as blocking. Synchronous message passing does not require buffer storage. Communicating Sequential Processes (CSP) [Hoare, 1978], which is the basic message passing paradigm is an example of synchronous message passing.

Asynchronous or non-blocking message passing refers to the type of communication in which data can be transmitted intermittently. The communication between processes is buffered using buffers of unlimited size. The sender does not wait after sending the data. The receiver waits only when the buffer is empty. Most of the latest distributed programming languages have adopted

asynchronous communication. The major disadvantage of these asynchronous message passing technique is the necessity for large buffers. These message buffers must be protected, notified or interrupted when message passing is complete. Another major problem of buffering is the memory overhead. It would be ideal to develop a reliable asynchronous message passing system which does not depend on message buffers.

## iii. Separation of communication and computation:

Another issue to be considered while developing a distributed programming environment is the separation of the communication and computational components within the program structure. Such separation better accommodates multiple communication and computation components and primitives. Most of the languages which achieve such separation employ different techniques/tools/language constructs for each of the two parts. For example, Regis [Magee et al., 1994] is a programming environment aimed at supporting the development and execution of distributed programs. The computational elements of a Regis program are designed using C++ and the communication is expressed using Darwin [Magee et al., 1993]. Distributed Oz has been designed to handle the application functionality and distribution structures separately. Java is extended with CORBA to provide a tool for developing concurrent systems [Hasselbring, 2000]. However, more research is required to improve the efficiency of such separation.

There are a number of parallel/distributed programming languages that have been developed. These languages are generally grouped based on their ability to express parallelism, pass messages, resource sharing, reliability, performance, and simple design [Tel, 2000]. Following sections review some of the popular distributed programming languages which demonstrate various ways of message passing.

#### 2.1.1 Occam

Occam, [Inmos, 1988], is a simple concurrent low level programming language developed for transputers. Although Occam has been developed for transputers, it has also been implemented on other platforms such as VAX VMS, IBM PC compatibles and SUN workstations [Hyde, 1995, Tanenbaum et al., 1989]. The implementation is achieved by installing an additional board containing one or more transputers. Occam was derived from Communicating Sequential Processes (CSP) [Hoare, 1978] which allows the behaviour of the language to be specified more formally. CSP aims at having both guarded inputs and outputs for communication. Implementing communications that are guarded at both ends poses serious design difficulties which is one of the major setbacks of CSP. Therefore, Occam provides only guarded inputs.

The execution of processes can be either parallel (PAR) or sequential (SEQ) and must

be explicitly stated in Occam. Unlike other mechanisms which express parallelism, PAR is not a common method even though it is a natural and easy construct to use.

Communication in Occam is achieved indirectly through channels. A channel in Occam has a unidirectional link between two processes which is only available to one process at a time. The channels are typed and their names can be passed as parameters to procedure calls. The message passing is via point-to-point communication and is synchronous. It is well known that synchronous message passing causes delay in communication which may in turn affect the overall performance of the system. Though Occam is constructed as a synchronous message passing language, research to support asynchronous communication has been carried out [Serbedzija, 1988, Theodoropoulos et al., 1997, Illingworth et al., 1995].

Due to its static nature of modelling, the mapping between the processors and channels in Occam are fixed at compile time. Despite the fact that programmers take advantage of this mapping by knowing about the availability of shared memory for the various processes [Bal et al., 1989], it enforces severe restrictions on the communication and affects the flexibility of its programs [Demaine, 1996] and this is due to the fact that Occam does not permit new processors to be created dynamically during run time [Carriero and Gelernter, 1989].

To summarise, Occam is a simple language for embedded systems which,

- Communicates concurrently using channels;

- Mapping between processors and computations are fixed at compile time:

- Passes message between processes synchronously.

Occam has been used extensively for programming applications in the area of signal processing, image processing, simulation, numerical analysis and neural computing and efforts are being made to improve its performance in terms of its message passing features and static nature [Bal et al., 1989, Bal, 1996, Theodoropoulos et al., 1997, Welch and Barnes, 2005]. The explicit nature of expressing parallelism using the PAR statement increases the responsibility of the developers during the designing phase. Security in concurrent systems is an important aspect and it is supported in Occam by not having some of the widely used functions of other programming languages such as pointers, dynamic memory allocation, dynamic process allocation and recursive functions of programming languages.

### 2.1.2 Ada

Ada, [Ledgard, 1983], is a language designed to be used by the US Government for use in embedded systems. It is loosely based on Pascal with similar syntax and strong-typing.

Similar to Occam, Ada also is formally based on CSP [Fidge, 1993] but not too closely due to its rendezvous nature of communication. The rendezvous model of communication<sup>3</sup> is based on three constructs which are the entry declaration, the entry call and the accept statement.

Parallelism is achieved through sequential processes known as tasks. The tasks in Ada are typed. Each task is defined using two parts:

- Task specification specifies the name of the task and formal parameters that define the communications interface of tasks of that type

- Task body defines its execution

Tasks can be created dynamically. Ada was intended to generate embedded systems and there is no notation to map the tasks to processors, [Jansohn, 1988, Bal et al., 1989]. The main disadvantage of this type of mapping is that it will be expensive to identify the operations that may need inter-process communication. Therefore, Jansohn [1988] proposed to write several Ada programs, one for each processor and implement the required communication software.

Communication between the tasks is defined and synchronized by the rendezvous model. A task may call (entry call) another task by specifying the entry point. The caller task synchronises with the called task using the accept statement. This is similar to the Remote Procedure Call (RPC) where the entry point and the accept statement are on the server side and the entry call is on the client side, where the entry call is similar to a procedure call. Java and concurrent C support this type of rendezvous communication. When the entry call synchronises with the entry point, the two tasks merge to execute a guarded code [Carlson et al., 1980]. Tasks can be terminated if the rendezvous does not occur. Several tasks may call an entry before a corresponding 'accept' statement is reached and in that case the calls are queued. Each execution of an accept statement will remove a call from the queue in a First In First Out order (FIFO) of arrival [Brauer et al., 1981].

Failure detection is possible with Ada's exception handling mechanism. The standard library of Ada supports portability and it gives the flexibility to the user to add user defined libraries into the language.

Burns et al. [1987] referenced in [Bal et al., 1989] has reviewed the problems of parallel and distributed programming in Ada. One of the issues criticised by Burns is the synchronisation mechanism as it is asymmetric, entry calls are served in FIFO order and

<sup>&</sup>lt;sup>3</sup>An interaction between two processes S and R is called rendezvous when S calls an entry of R, and R executes an accept statement for that entry. The interaction is fully synchronous so that the first process that is ready to interact waits for the other. When the two processes are synchronised, R executes the do part of the accept statement [Bal, 1990]

cannot be accepted conditionally.

According to Bal et al. [1989] and Andrews [1982], implementing some of the aspects of concurrent programming of Ada is complex. Rising [1988] has identified that the complexity in developing concurrent applications stem from the interaction between the tasks. Burns et al. [2001] acknowledged the problem of tasking in Ada and proposed design abstractions such as atomic actions, conversations etc to handle it. The logical correctness of these abstractions has been validated using Petri nets.

#### 2.1.3 Concurrent C

Concurrent C, [Gehani, 1990, Gehani and Roome, 1992], is an extension of C to implement distributed processing based on rendezvous message passing. This is one of the first concurrent languages based on C which has been influenced by the concurrent facilities of Ada. The C compiler is added with run-time and system libraries which are used to translate the Concurrent C programs to C programs. The local C compiler then compiles the converted programs.

Parallelism in Concurrent C is achieved through sequential processes similar to tasks in Ada. Each process consists of a specification part and a body. The specification part consists of the name of the process, a list of formal parameters and a list of transactions. Processes are created explicitly and a newly created process can be given a priority and assigned to a specific processor.

A program in Concurrent C comprises one or more processes working together to reach a solution. Two processes interact by synchronising with each other and then exchanging information between them and continuing with their individual activities. This synchronisation to exchange information is called rendezvous communication and it is similar to Ada. A transaction in Concurrent C is different from Ada by its capability to return values. That is, Concurrent C permits two way information transfer during rendezvous communication which is called extended rendezvous. In addition, it supports asynchronous message passing. Concurrent C allows its processes to use shared memory without portability.

Concurrent C can [Bal et al., 1989, Gehani, 1990, Gehani and Roome, 1992]

- Define and create processes the creative primitive is used to create processes explicitly and pass the parameter to the created process. The process which gets created can be prioritised and can be assigned to a specific processor;

- Specify querying and changing process priorities and accepting transactions in a

user-defined order accepting transactions conditionally based on the values of their

parameters which is not the case in Ada as it has no conditional accept statement

and it strictly follows FIFO queuing;

- Specify timed bidirectional synchronous transactions similar to Ada's timed entry call and ordinary/non-timed unidirectional asynchronous transactions with no return value;

- Handle interrupts and terminate processes collectively Ada uses declarations to associate interrupts with transaction calls whereas Concurrent C uses library functions to make this association. This feature makes it possible to change or discontinue the association at any time which is not the case in Ada;

Similar to Ada, parallelism, decomposition of programs into distributed processes, mapping of processes with computations, and communication and synchronisation have to be specified explicitly. This makes the process of developing programs difficult as correctness and performance of programs must be achieved by considering a number of factors [Skillicorn and Talia, 1998].

In summary, Concurrent C is like Ada in expressing parallelism using processes and it supports both rendezvous type of message passing and asynchronous message passing. Designers of the language tried to avoid the complexity of Ada and maintain the concurrent features but Concurrent C does not support shared memory communication and therefore, it does not have semaphores, condition variables and monitors [Kamran, 1996]. It has been implemented on a UNIX operating system where it is considered as a sequential program. Context switching and scheduling have to be provided separately apart from the UNIX scheduler. In order to add object oriented programming capabilities to its concurrent programming capabilities, Concurrent C has been merged with C++ [Gehani and Roome, 1992]. But Kamran [1996] has found that integrating data abstraction facilities of C++ and concurrency features of Concurrent C was not a successful experience.

#### 2.1.4 NIL

NIL [Strom and Yemini, 1983, 1985] is a general purpose high level programming language developed at IBM to support the construction of distributed programs. Programs developed using NIL have no pointers or data models. The inter-process communication can be either synchronous (rendezvous or RPC) or asynchronous [Strom and Yemini, 1983].

Parallelism is achieved through inter-process communication. A NIL program consists of dynamically evolving network of loosely coupled processes which encapsulate the data and its state. NIL supports point-to-point communication through channels. The communication channels in NIL are unidirectional and are created dynamically by connecting input ports with output ports. The synchronous and asynchronous communications are different from the concepts of CSP and CCS as all communications are queued and there is no sharing of data across the communication channels [Strom and Yemini, 1983]. At

any time a data object can only belong to exactly one process and a data object can be passed from one process to another. Processes contain only local data which also includes the input/output ports. Communication ports can be created by the interconnection of these ports and NIL processes can interact with each other only by these communication ports. For a NIL program, the environment is determined at run-time and therefore the choice of which modules to load into a component is also made during run-time.

NIL supports exception handling to manage software failures and it helps the developer in detecting the errors automatically. This is not the case in Occam where there is very little information available through static examination of the program. The process model of NIL is similar to Ada and Occam. The mapping of processors to processes is dynamic in NIL whereas it is fixed and static in the case of Ada and Occam [Goldszmidt et al., 1988].

To summarise, NIL is a general purpose distributed programming language which supports inter-process communication through point-to-point message passing. NIL supports only queued synchronous and asynchronous communication. Despite all these useful features, NIL needs substantial amount of run-time support and there is no evidence of a broader range of applications developed using NIL.

This section briefly looked into some of the distributed/parallel programming languages that have influenced the way in which distributed and parallel systems can be programmed. Although the languages listed here have their own short comings, each of them offer a number of features, which allow programmers to develop distributed applications. These features include:

- Point-to-point communication through inter-process communication;

- Dynamic mapping of parallel processes to physical processors;

- Simple and reliable asynchronous message passing without using buffers.

Considering all the above issues, a constructive approach to developing a distributed language is to incorporate all of the above properties into a single programming language together with additional properties like simplicity, expressiveness and support of portability.

LIPS (Language for Implementing Parallel/distributed Systems) has been developed to address these issues but currently fails to address the problem of dynamic mapping of processes to processors. However, LIPS offers many distinct advantages which includes asynchronous message passing capability, avoidance of deadlock and livelock, ability to handle communication and computation independently, and portability. The Asynchronous Message Passing System (AMPS) [Bavan et al., 2007b] implemented in LIPS allows it to pass messages asynchronously without buffers. A detailed description of LIPS can be found

in [Bavan and Illingworth, 2001]. This research continues on the work done already on LIPS and seeks to develop the formal semantics and specifications which are currently lacking. The subsequent sections look at the methods to define the formal semantics and high level specification of a distributed language such as LIPS.

# 2.2 Operational Semantics and Abstract Machine

Having identified the need for a distributed programming language like LIPS, this section gives the background information on operational semantics and analyses the necessity for a mixed approach to specify the semantics of a distributed programming language.