# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e. g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

# DESIGN OF POWER CONVERTERS WITH EMBEDDED ENERGY STORAGE FOR HYBRID DC-AC APPLICATIONS

# SEBASTIAN NEIRA CASTILLO

Thesis submitted to the Pontificia Universidad Católica de Chile in partial fulfilment of the requirements for the degree of Doctor in Engineering Sciences

Thesis submitted to the University of Edinburgh in partial fulfilment of the requirements for the degree of Doctor of Philosophy

Supervisors: JAVIER PEREDA TORRES MICHAEL M. C. MERLIN

Santiago de Chile, June 2023

$\odot$  MMXXII, Sebastian Neira Castillo

# DESIGN OF POWER CONVERTERS WITH EMBEDDED ENERGY STORAGE FOR HYBRID DC-AC APPLICATIONS

SEBASTIAN NEIRA CASTILLO

Members of the Committee: JAVIER PEREDA TORRES MICHAEL M. C. MERLIN FELIPE NUÑEZ RETAMAL SAMIR KOURO RENAER LUCA TARISCIOTTI STEPHEN J. FINNEY IGNACIO LIRA CANGUILHEM

Santiago de Chile, June 2023

Gratefully to my family

#### ACKNOWLEDGEMENTS

I would like to thank my supervisors Dr. Javier Pereda and Dr. Michael Merlin for giving me the opportunity of entering to the dual-degree program and for giving me their constant guidance and support over the last four years. I would also like to thank the Agencia Nacional de Investigacion y Desarrollo (ANID) for funding my PhD studies under the grant ANID/Doctorado Nacional/21200865. Furthermore, the work in this thesis was partially supported through Fondecyt projects 1220928, ANID/FONDEF ID22I10031, and FONDAP/1522A0006 SERC Chile.

I am grateful for all the colleagues I have met in both laboratories and I would like to express my thanks to all the people that helped and supported me with the research during these years. I would especially like to mention Rodrigo and Pablo in Chile for all the interesting discussions and work in modelling and control that we used for keeping us busy while going to the laboratory was not possible; and to Zoe in Edinburgh for all the work we did planning and building the hardware demonstrator. Special thanks to Dr. Paul Judge and Prof. Stephen Finney for all the valuable advice on hardware design and development.

I would also like to thank my parents and my sister for all their support and belief in me all these years. Special mention to all the friends that have been with me these years, making life easier and more enjoyable.

# CONTENTS

| ACKNOWI    | LEDGEMENTS                                                        | iv    |

|------------|-------------------------------------------------------------------|-------|

| LIST OF FI | GURES                                                             | ix    |

| LIST OF TA | ABLES                                                             | XV    |

| ABSTRAC    | Γ                                                                 | xvi   |

| RESUMEN    | ·                                                                 | xviii |

| 1. Introdu | ction                                                             | 1     |

| 1.1. Hy    | brid DC-AC Applications with Energy Storage                       | 3     |

| 1.1.1.     | Low and Medium Power Applications                                 | 3     |

| 1.1.2.     | High Power Applications                                           | 5     |

| 1.1.3.     | Energy Storage Systems                                            | 5     |

| 1.2. Pov   | wer Electronics for Hybrid DC-AC Applications with Energy Storage | 8     |

| 1.2.1.     | Low and Medium Power Topologies                                   | 8     |

| 1.2.2.     | High Power Topologies                                             | 16    |

| 1.3. Ori   | ginal Contributions and Layout of the Thesis                      | 22    |

| 1.3.1.     | Original Contributions                                            | 23    |

| 1.3.2.     | Thesis Objectives                                                 | 24    |

| 1.3.3.     | Hypotheses                                                        | 24    |

| 1.3.4.     | Thesis Structure                                                  | 25    |

### PART I: CONVERTER PROPOSAL FOR INTEGRATING ESS INTO LOW- AND

#### MEDIUM-VOLTAGE SYSTEMS

| 2. Review of single-stage three-port DC-DC-AC converters | 28 |

|----------------------------------------------------------|----|

| 2.1. Topologies Classification                           | 28 |

| 2.1.1. Integrated dual-source dc-ac converters           | 29 |

| 2.1.2. Impedance source dual-input inverters             | 34 |

| 2.1.3. Partially isolated dual-input inverters                             | 36 |

|----------------------------------------------------------------------------|----|

| 2.2. Applications                                                          | 38 |

| 2.3. Discussion                                                            | 40 |

| 2.4. Chapter Conclusions                                                   | 44 |

|                                                                            |    |

| 3. Three-port full-bridge DC-DC-AC converter                               | 46 |

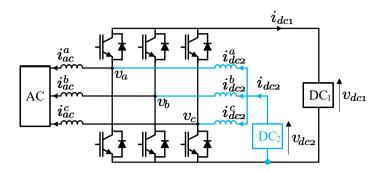

| 3.1. Topology and Operation Principle                                      | 46 |

| 3.2. Modelling and Control of the Converter                                | 48 |

| 3.2.1. Dynamical Modelling of the Topology                                 | 49 |

| 3.2.2. Multi-variable Control of the Converter                             | 50 |

| 3.3. Design of the Converter                                               | 57 |

| 3.3.1. Voltage and Power Characteristics                                   | 57 |

| 3.3.2. Current Load Characteristics                                        | 62 |

| 3.4. Chapter Conclusions                                                   | 64 |

|                                                                            |    |

| 4. Coupled inductor three-port full-bridge DC-DC-AC converter              | 66 |

| 4.1. Topology and Operation Principle                                      | 67 |

| 4.2. Modelling and Control of the Converter                                | 70 |

| 4.3. Design of the Converter                                               | 73 |

| 4.3.1. Coupled Inductor Impact on the Current Load Characteristics         | 73 |

| 4.3.2. Coupled Inductor Design                                             | 75 |

| 4.4. Chapter Conclusions                                                   | 79 |

|                                                                            |    |

| 5. Results and assessment of the three-port full-bridge DC-DC-AC converter | 81 |

| 5.1. Simulation Results                                                    | 81 |

| 5.1.1. Single-phase TPC                                                    | 81 |

| 5.1.2. Three-phase TPC                                                     | 87 |

| 5.1.3. Single-phase TPC with coupled inductors                             | 89 |

| 5.2. Experimental Results                                                  | 92 |

| 5.3. Assessment of the proposed converter                                  | 94 |

| 5.4. Chapter Conclusions | - 98 | 8 |

|--------------------------|------|---|

|--------------------------|------|---|

### PART II: CONVERTER PROPOSAL FOR INTEGRATING ESS INTO HIGH-VOLTAGE

#### SYSTEMS

| 6. | Mo   | dular Multilevel Converter with Integrated Energy Storage                      | 101  |

|----|------|--------------------------------------------------------------------------------|------|

|    | 6.1. | Topology and Operation Principle                                               | 102  |

|    | 6.2. | Modelling of the converter                                                     | 106  |

|    | 6.3. | MMC Stack Analysis                                                             | 107  |

|    | 6.4. | ES Stack Analysis                                                              | 114  |

|    | 6.5. | Chapter Conclusions                                                            | 116  |

| 7. | Des  | sign Study for the Modular Multilevel Converter with Integrated Energy Storage | e117 |

|    | 7.1. | Control Scheme                                                                 | 117  |

|    | 7.1  | .1. MMC operation related blocks                                               | 117  |

|    | 7.1  | .2. ESS branches operation related blocks                                      | 121  |

|    | 7.2. | Case Study Design and Analysis                                                 | 124  |

|    | 7.2  | 2.1. Power Capability Analysis                                                 | 124  |

|    | 7.2  | 2.2. Power Losses Analysis                                                     | 128  |

|    | 7.3. | Simulation Results                                                             | 133  |

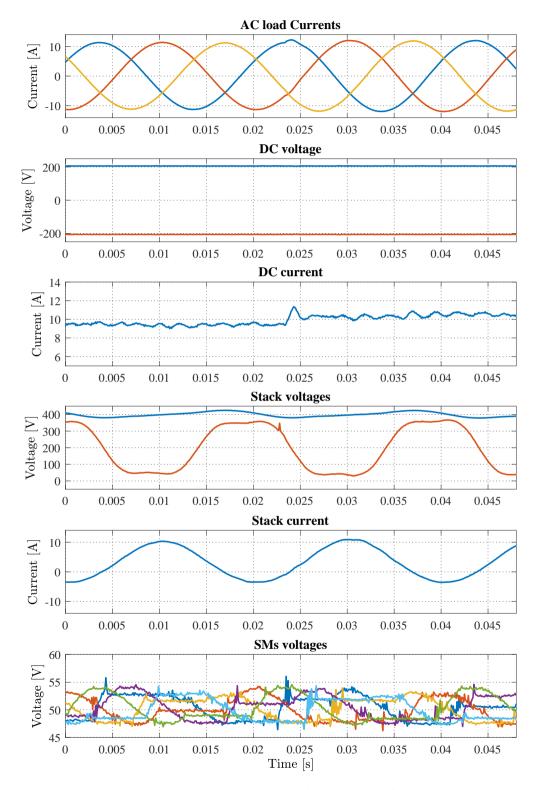

|    | 7.3  | 3.1. General Waveforms for Both Configurations                                 | 134  |

|    | 7.3  | 3.2. Dynamic Response                                                          | 134  |

|    | 7.4. | Chapter Conclusions                                                            | 137  |

| 8. | Exp  | perimental prototype for the Modular Multilevel Converter with integrated      |      |

|    | ener | gy storage                                                                     | 139  |

|    | 8.1. | Converter Specification                                                        | 139  |

|    | 8.2. | Overall Hardware Setup                                                         | 141  |

|    | 8.3. | Controller Structure                                                           | 144  |

|    | 8.4. | Experimental Results                                                           | 148  |

|    | 8.4  | 1.1. Operation as MMC                                                          | 148  |

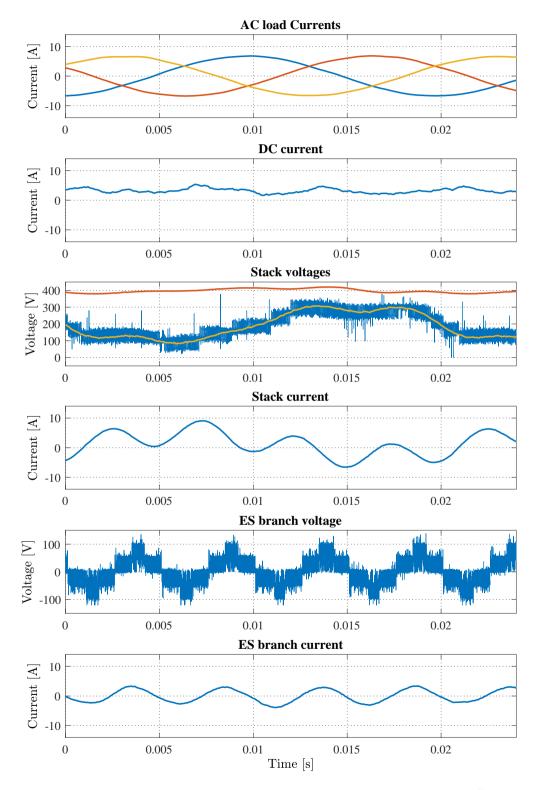

| 8.4.2. Operation as MMC with Energy Storage | 153 |

|---------------------------------------------|-----|

| 8.5. Chapter Conclusions                    | 155 |

| 9. Conclusion and future research           | 157 |

| 9.1. General Conclusions                    | 157 |

| 9.2. Publications arising from this thesis  | 160 |

| 9.3. Future research topics                 | 161 |

| REFERENCES                                  | 163 |

# LIST OF FIGURES

| 1.1  | Required electrification and renewable generation share to achieve Net-Zero     |    |

|------|---------------------------------------------------------------------------------|----|

|      | goal                                                                            | 1  |

| 1.2  | Battery Energy Storage Systems Worldwide Installed Capacity.                    | 2  |

| 1.3  | Inclusion trend of main DERs technologies.                                      | 4  |

| 1.4  | ESS technologies with power ratings and energy capacity.                        | 6  |

| 1.5  | DC-AC Voltage source converters. (a) Two-levels topology. (b) Three-levels      |    |

|      | topology                                                                        | 9  |

| 1.6  | Classification of DC-DC-AC Power Conversion Systems.                            | 10 |

| 1.7  | Example of a three power conversion stages system with common DC-link.          | 11 |

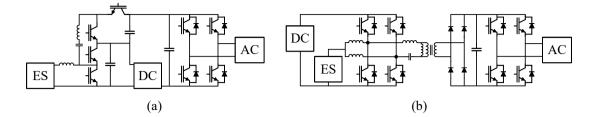

| 1.8  | Examples of a three power conversion stages system with common AC-link. (a)     |    |

|      | Non-Isolated. (b) Isolated                                                      | 12 |

| 1.9  | Example of a two power conversion stages system with DC-DC + DC-AC              |    |

|      | converters                                                                      | 13 |

| 1.10 | Examples of a two power conversion stages system with DC-DC-DC + DC-AC          |    |

|      | converters. (a) Non-Isolated. (b) Partially-Isolated.                           | 14 |

| 1.11 | Example of a HVDC 12-pulse Line-Commutated Converter.                           | 17 |

| 1.12 | Modular Multilevel Converter.                                                   | 18 |

| 1.13 | Classification of configurations to integrate ESS into MMC substations.         | 19 |

| 1.14 | MMC substation with ESS on the DC side.                                         | 20 |

| 1.15 | MMC substation with ESS on the AC side.                                         | 20 |

| 1.16 | MMC substation with embedded ESS.                                               | 21 |

| 2.1  | Classification of single-stage three-port DC-DC-AC converters                   | 29 |

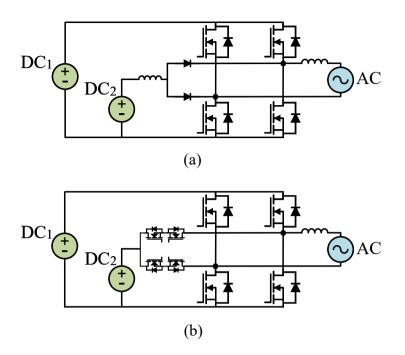

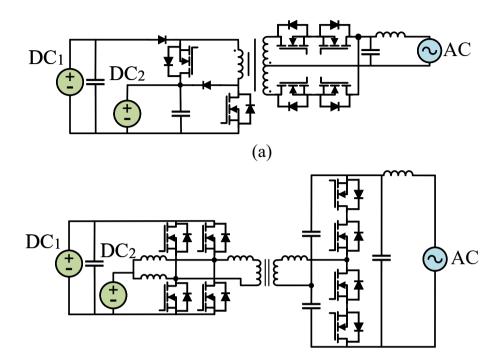

| 2.2  | Integrated dual-source dc-ac converter examples. (a) Split-source inverter. (b) |    |

|      | Dual-port asymmetrical converter.                                               | 30 |

| 2.3  | Split-source inverter variations. (a) Original Split-source inverter. (b) Reduced   |    |

|------|-------------------------------------------------------------------------------------|----|

|      | Split-source inverter. (c) Split-source inverter with common-cathode diodes. (d)    |    |

|      | Improved split-source inverter. (e) Active split-source inverter (f) Simplified     |    |

|      | split-source inverter.                                                              | 31 |

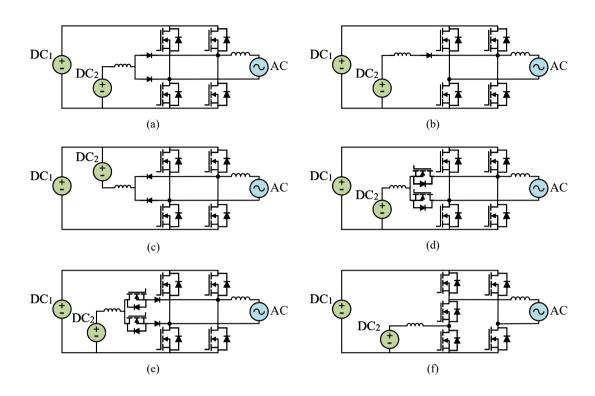

| 2.4  | Dual-port asymmetrical converter variations. (a) T-Type DP-AMC. (b) Simplified      |    |

|      | T-Type DP-AMC. (c) NPC-Type DP-AMC. (d) ANPC Type DP-AMC                            | 33 |

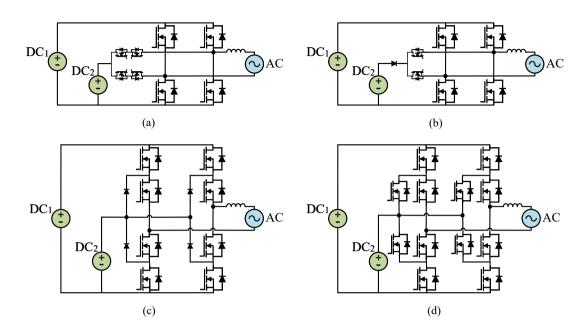

| 2.5  | Impedance source dual-input inverter examples. (a) Z-source inverter. (b) qZ-       |    |

|      | source inverter.                                                                    | 35 |

| 2.6  | Partially isolated dual-input inverter examples. (a) Flyback-based TPC. (b) Dual-   |    |

|      | active Bridge-based TPC.                                                            | 37 |

| 2.7  | Three-port converter applications and key features for their operation              | 39 |

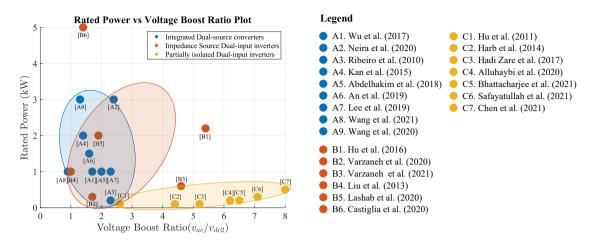

| 2.8  | Rated power against voltage boost capability for DC-DC-AC converters                | 41 |

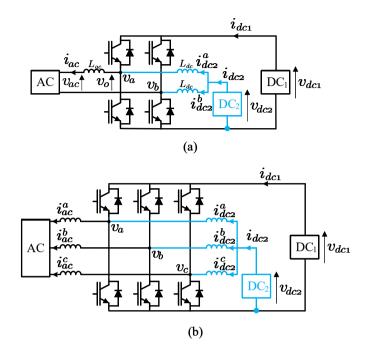

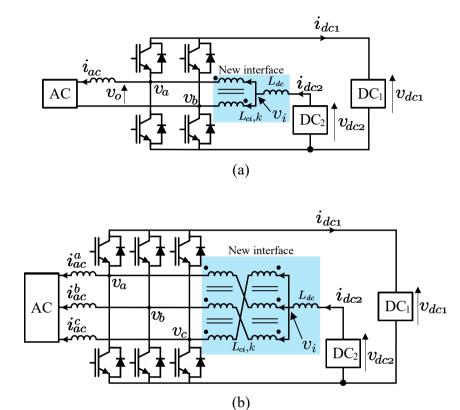

| 3.1  | Topology of the proposed three-port converter. (a) Single-phase implementation.     |    |

|      | (b) Three-phase implementation                                                      | 47 |

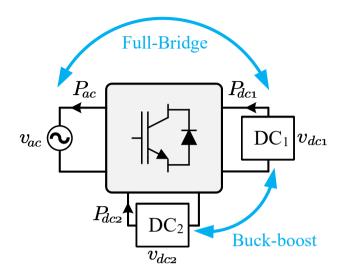

| 3.2  | High-level operation of the proposed TPC.                                           | 48 |

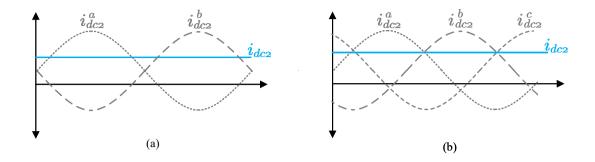

| 3.3  | Current waveforms of the second DC port inductors. (a) Single-phase TPC.            |    |

|      | (b) Three-phase TPC.                                                                | 50 |

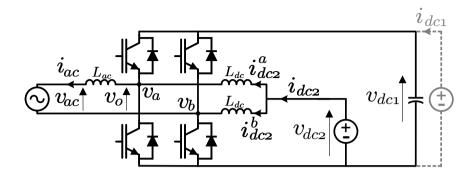

| 3.4  | TPC configuration with energy storage unit on port $DC_2$                           | 51 |

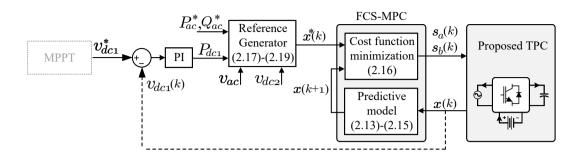

| 3.5  | Control Scheme of FCS-MPC for the proposed TPC.                                     | 54 |

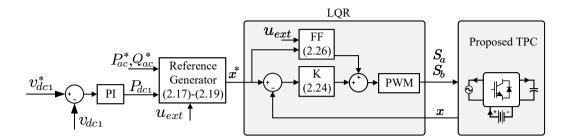

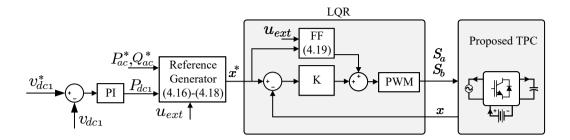

| 3.6  | Control Scheme of LQR for the proposed TPC.                                         | 56 |

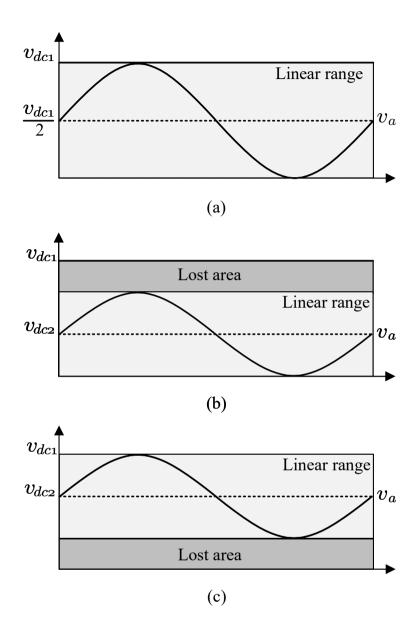

| 3.7  | Operating range for leg voltages. (a) Regular h-bridge. (b) Proposed TPC with       |    |

|      | $v_{dc2} < 0.5 \cdot v_{dc1}$ . (c) Proposed TPC with $v_{dc2} > 0.5 \cdot v_{dc1}$ | 58 |

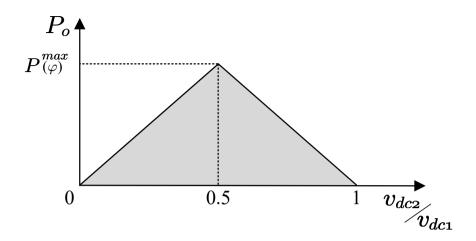

| 3.8  | Output power range vs. $v_{dc2}/v_{dc1}$ ratio                                      | 59 |

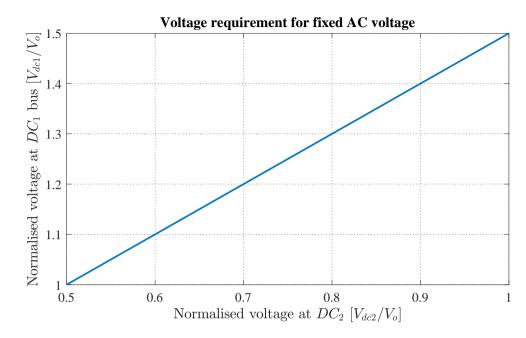

| 3.9  | Voltage requirement at $DC_1$ bus for fixed AC voltage and varying $DC_2$ voltages. | 61 |

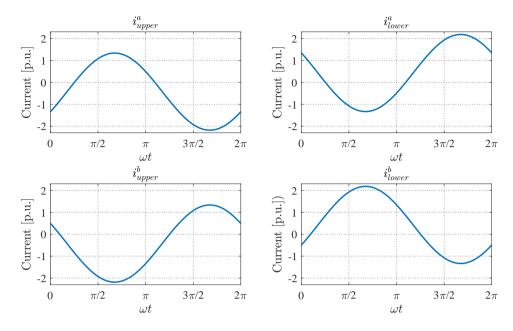

| 3.10 | Current load of the TPC switching devices.                                          | 63 |

| 4.1  | Topology of the modified three-port converter. (a) Single-phase implementation.     |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | (b) Three-phase implementation                                                      | 67  |

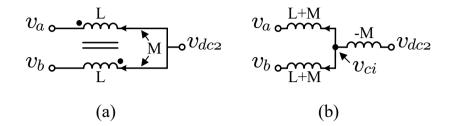

| 4.2  | Coupled inductors analysis. (a) Single-phase circuit. (b) Single-phase equivalent   |     |

|      | circuit                                                                             | 68  |

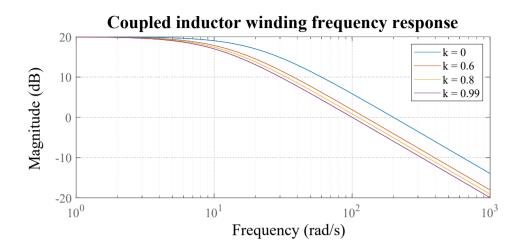

| 4.3  | Coupled inductor winding frequency response for different coupling factors          | 69  |

| 4.4  | Control Scheme of LQR for the proposed TPC with coupled inductors                   | 73  |

| 4.5  | Comparison of current load of the TPC switching devices for cases with and          |     |

|      | without coupling.                                                                   | 75  |

| 4.6  | Flowchart illustrating the coupled inductor magnetic design.                        | 78  |

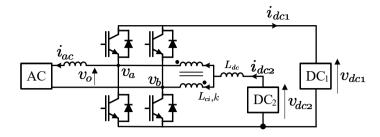

| 5.1  | Single-phase implementation of the TPC.                                             | 82  |

| 5.2  | Simulation results for the single-phase TPC used as a boost inverter. (a) Battery   |     |

|      | current. (b) Capacitor voltage. (c) Grid current.                                   | 83  |

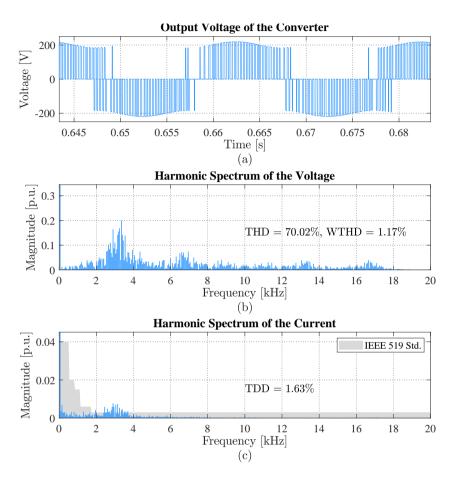

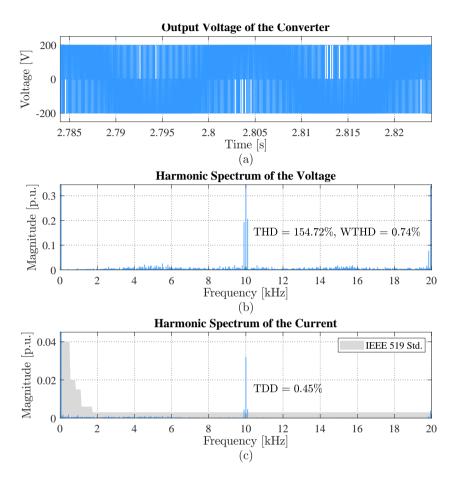

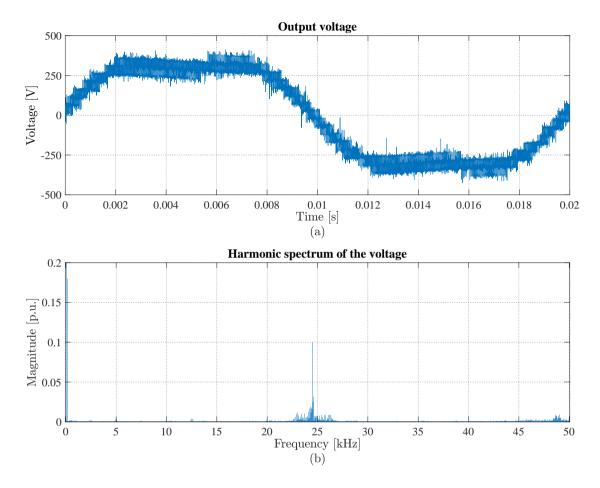

| 5.3  | Simulation results at 3kW. (a) Output voltage. (b) Harmonic spectrum of the         |     |

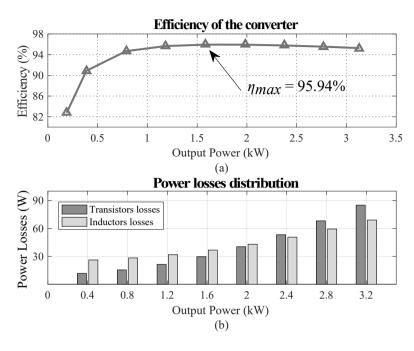

|      | output voltage. (c) Harmonic spectrum of the output current.                        | 84  |

| 5.4  | (a) Simulated power efficiency for the converter. (b) Distribution of power losses. | 85  |

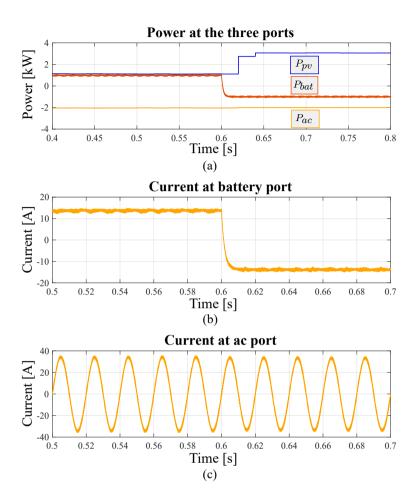

| 5.5  | Simulation results for the single-phase TPC used in a hybrid PV-BESS configuration  | on. |

|      | (a) Power at the three ports. (b) Current at the battery port. (c) Grid current.    | 86  |

| 5.6  | Three-phase implementation of the TPC.                                              | 87  |

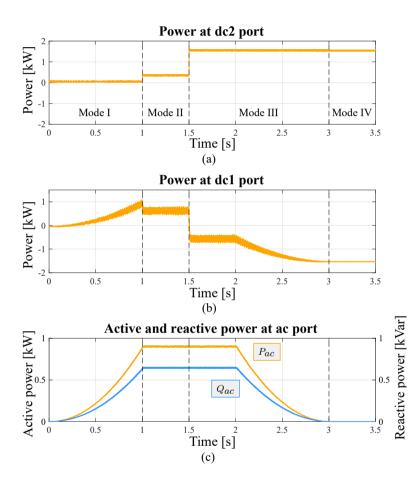

| 5.7  | Simulation results for the three-phase TPC at 50 Hz. (a) Power at $dc_2$ port. (b)  |     |

|      | Power at $dc_1$ port. (c) Power at AC port                                          | 88  |

| 5.8  | Single-phase implementation of the TPC with coupled inductors interface             | 89  |

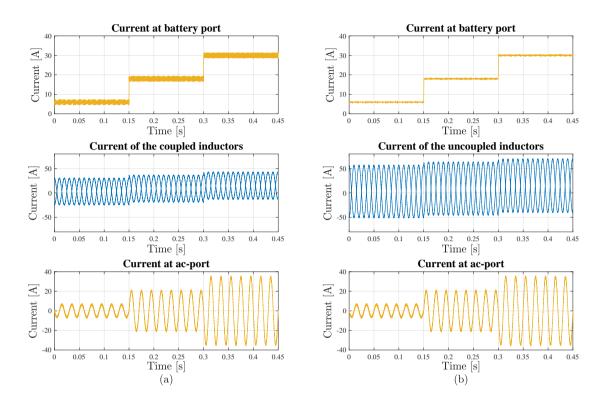

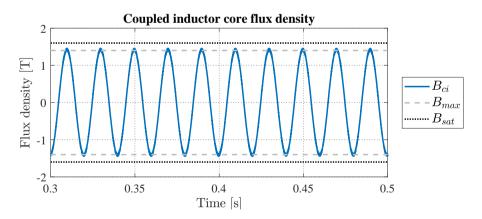

| 5.9  | Simulation results for the single-phase TPC used as a boost inverter. (a) Results   |     |

|      | with coupled inductors. (b) Results without coupled inductors                       | 91  |

| 5.10 | Simulation results for the flux density of the designed coupled inductor            | 91  |

| 5.11 | Simulation results at 3kW. (a) Output voltage. (b) Harmonic spectrum of the         |     |

|      | output voltage. (c) Harmonic spectrum of the output current.                        | 92  |

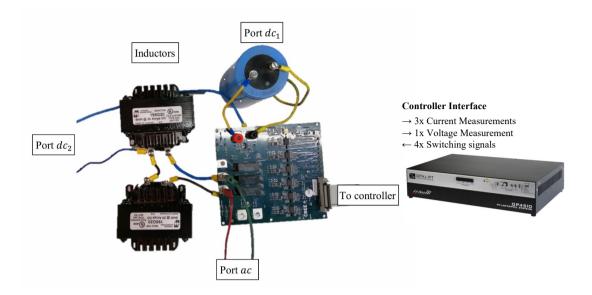

| 5.12 | Experimental TPC cell using CREE CMF20102D.                                                                                                                                                                                                        | 94  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

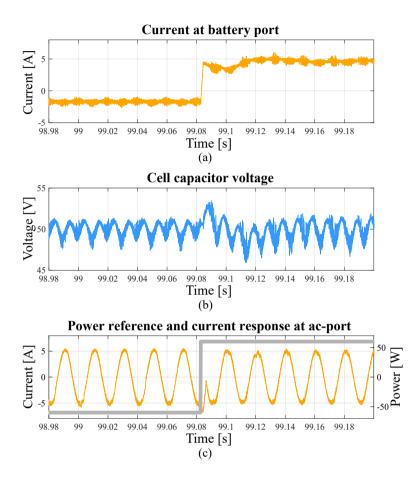

| 5.13 | Experimental results. (a) Current at battery port. (b) Voltage at capacitor port. (c) Power and current at grid port.                                                                                                                              | 95  |

| 5.14 | Experimental results at 60 W. (a) Output voltage. (b) Harmonic spectrum of the output voltage                                                                                                                                                      | 96  |

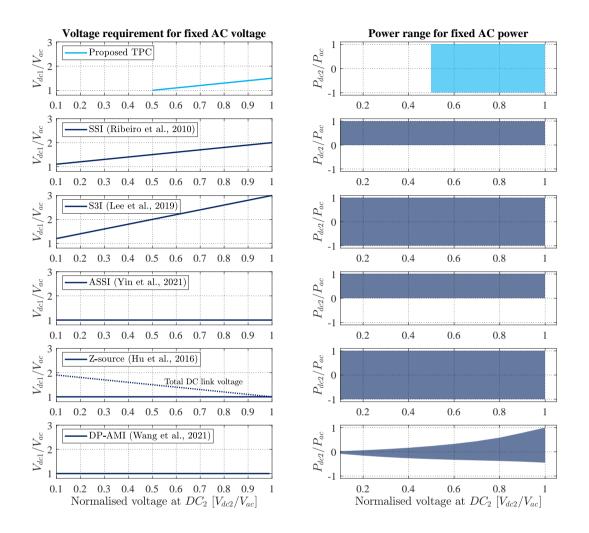

| 5.15 | Characterisation of different single-stage three-port DC-DC-AC topologies. Left column: Voltage requirement on port $DC_1$ for different boost characteristics. Right column: Power capability of port $DC_2$ for different boost characteristics. | 97  |

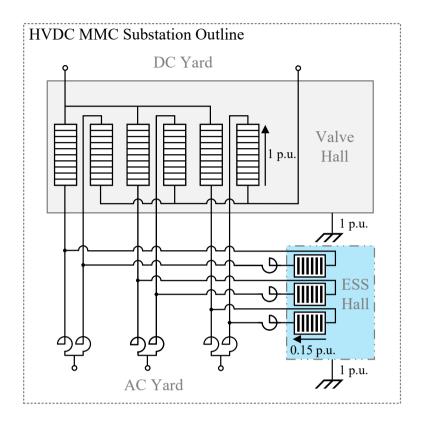

| 6.1  | Example of the proposed outline for the upgraded MMC substation with ES.                                                                                                                                                                           | 103 |

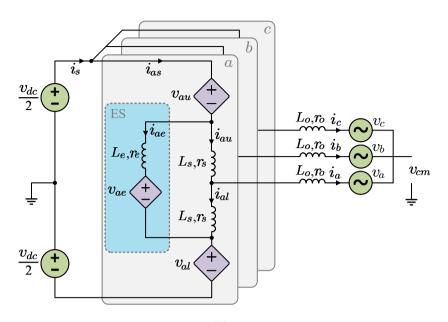

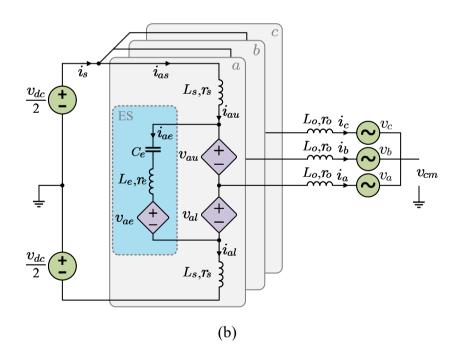

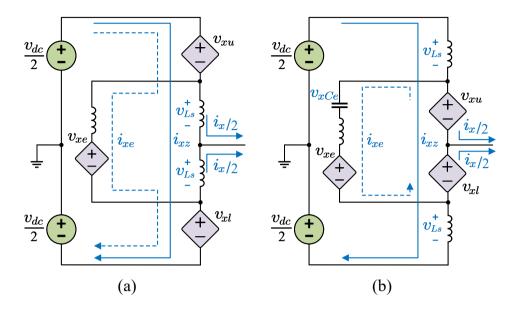

| 6.2  | Proposed MMC with Parallel ES Branches. (a) Configuration with inductors at the ac side. (b) Configuration with the inductors at the dc side.                                                                                                      | 104 |

| 6.3  | Currents through one phase of the converter. (a) Configuration with inductors at the ac side. (b) Configuration with the inductors at the dc side                                                                                                  | 105 |

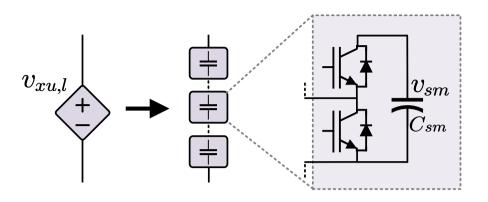

| 6.4  | Stack equivalent model (left) and SM topology (right) for the MMC branches.                                                                                                                                                                        | 107 |

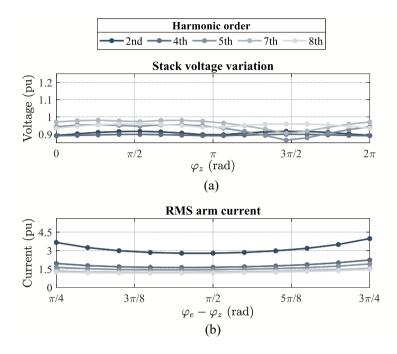

| 6.5  | Effect of the circulating current magnitude on the converter variables for different frequencies.                                                                                                                                                  |     |

| 6.6  | Effect of the harmonic phase angles for different frequencies. (a) Stack voltage variation for different circulating current phase angles. (b) Arm current variation for different phase-shift angles.                                             |     |

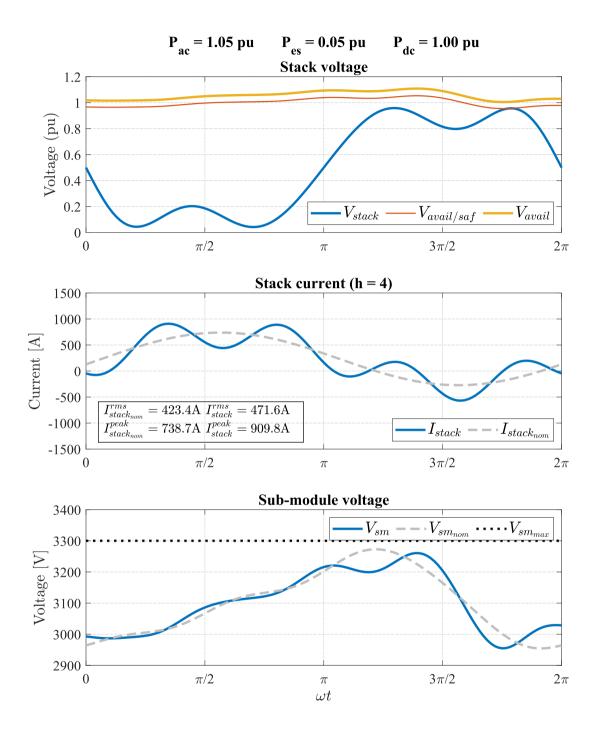

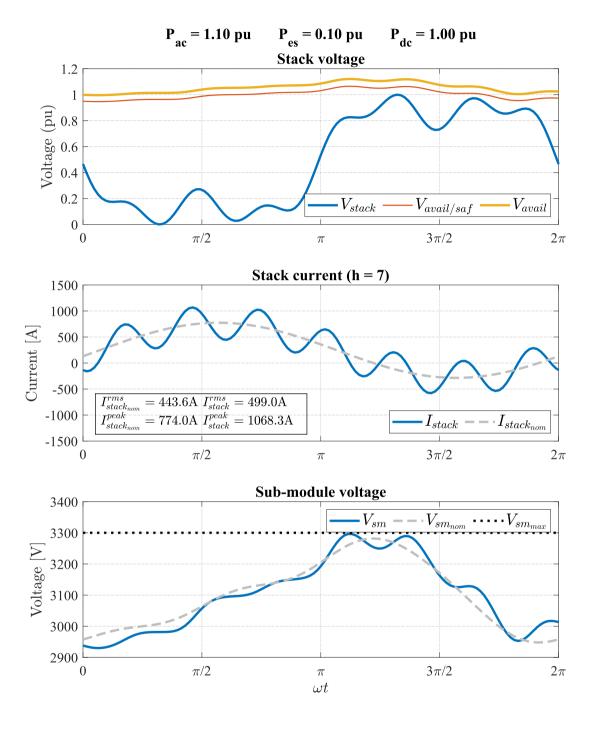

| 6.7  | Operation of one arm of the proposed converter compared to a conventional MMC. (a) MMC-IPB with $P_{es} = 0.05$ p.u. and $h = 4$ . (b) MMC-IPB with $P_{es} = 0.1$ p.u. and $h = 7$ .                                                              | 113 |

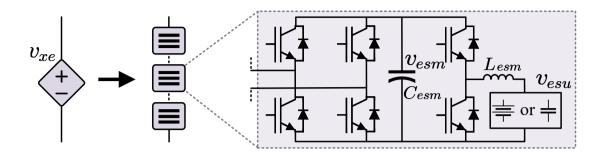

| 6.8  | Stack equivalent model (left) and SM topology (right) for the ES branch                                                                                                                                                                            | 115 |

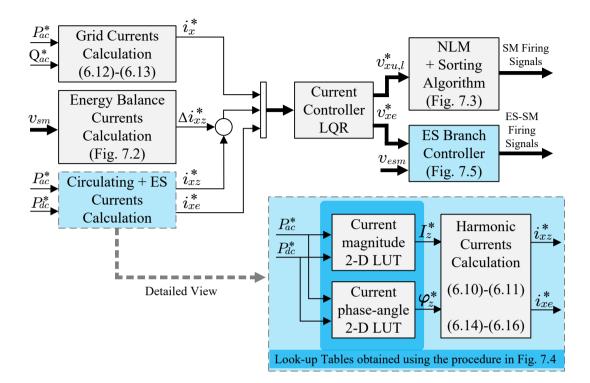

| 7.1  | Overall control scheme.                                                                                                                                                                                                                            | 118 |

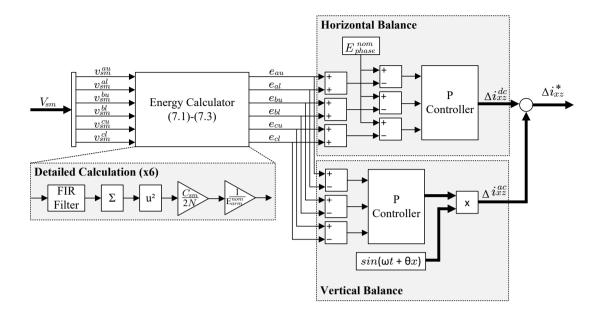

| 7.2  | Detailed Energy Balance Block.                                                                                                                                                                                                                     | 119 |

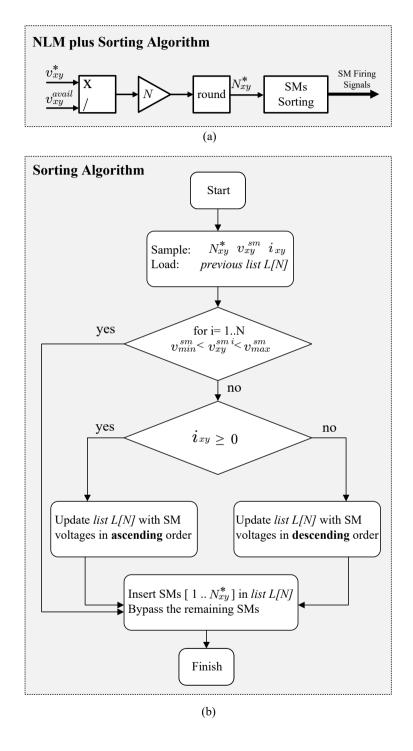

| 7.3  | Nearest Level Modulation plus Sorting Scheme. (a) Overall scheme. (b) Sorting                                                                |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | algorithm flowchart.                                                                                                                         | 120 |

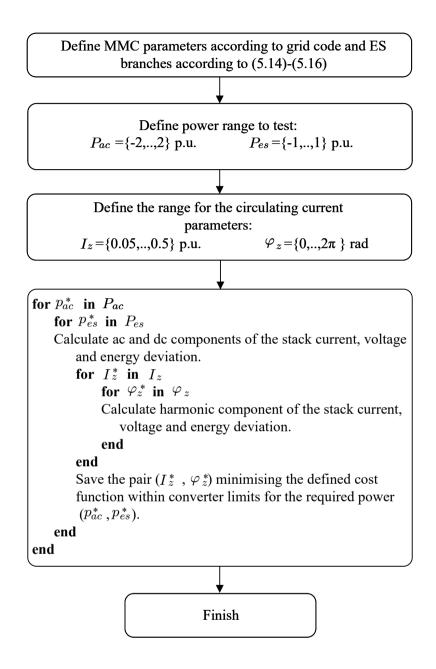

| 7.4  | Flowchart illustrating the method to generate the circulating current parameters                                                             |     |

|      | lookup tables.                                                                                                                               | 122 |

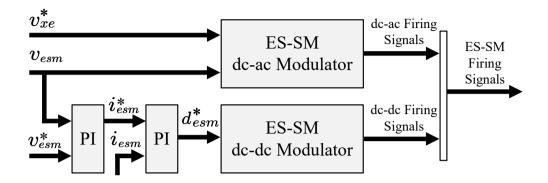

| 7.5  | ES branches control scheme.                                                                                                                  | 123 |

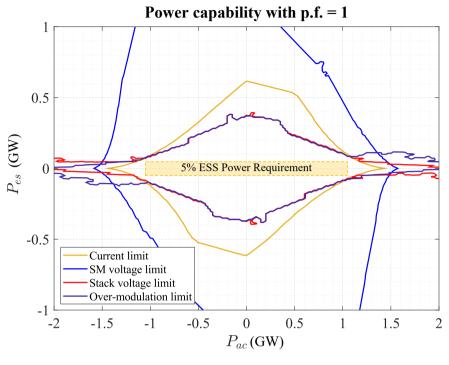

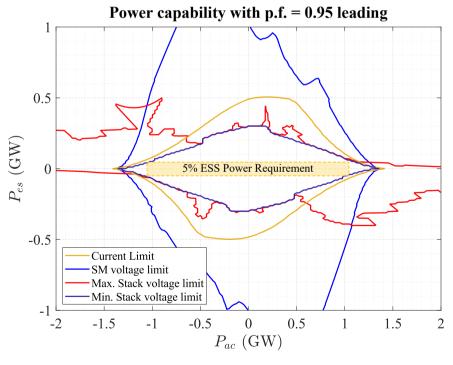

| 7.6  | Power capability plot of the converter for $h = 8$ with different power factors                                                              |     |

|      | $(P_{dc} = P_{ac} - P_{es})$ . (a) Operation with $\cos(\varphi_{ac}) = 0$ . (b) Operation with                                              |     |

|      | $\cos(\varphi_{ac}) = 0.95$ . (c) Operation with $\cos(\varphi_{ac}) = -0.95$                                                                | 127 |

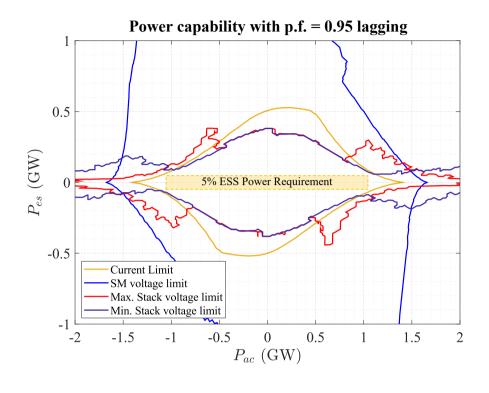

| 7.7  | Conduction and switching losses characteristic for the selected device ABB                                                                   |     |

|      | 5SNA2000K450300 working at a reference voltage $V_{CE} = 2.8 \ kV$                                                                           | 129 |

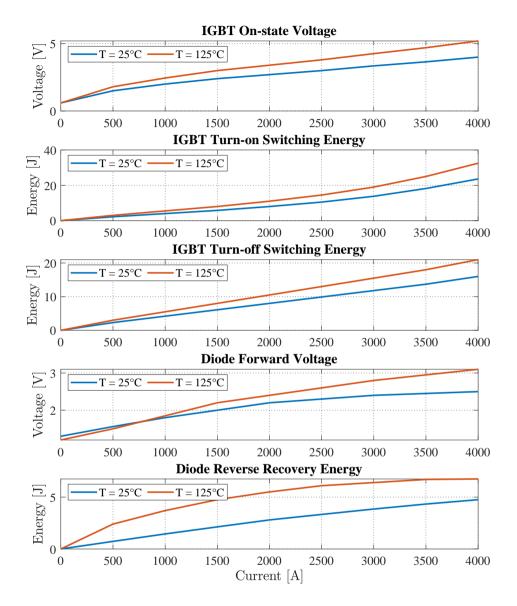

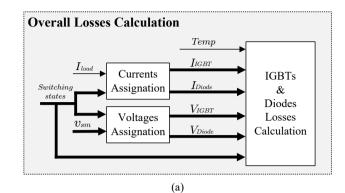

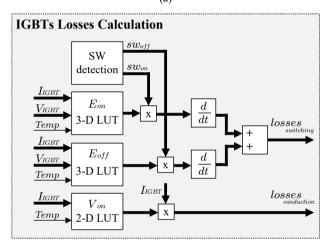

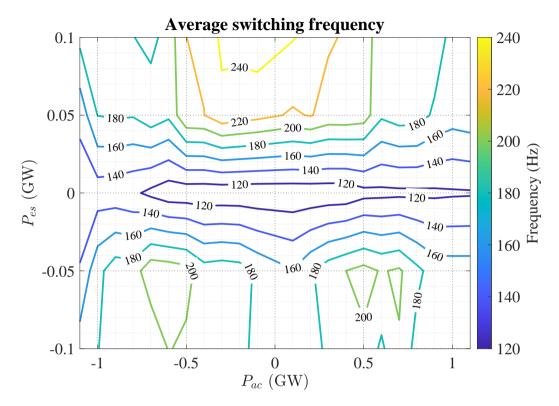

| 7.8  | Losses calculation diagram. (a) Overall losses calculation scheme. (b) IGBT-                                                                 |     |

|      | associated losses calculation. (c) Diodes-associated losses calculation                                                                      | 130 |

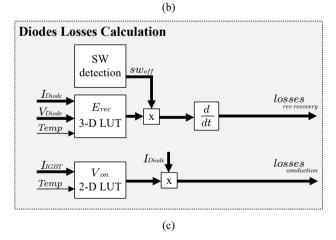

| 7.9  | Losses associated to the switching devices for different power scenarios, where                                                              |     |

|      | $P_{dc} = P_{ac} - P_{es} \dots \dots$ | 132 |

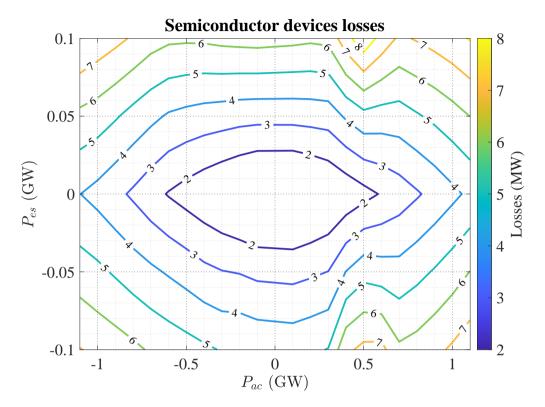

| 7.10 | Resulting switching frequency of the MMC SMs for different power scenarios,                                                                  |     |

|      | where $P_{dc} = P_{ac} - P_{es}$ .                                                                                                           | 133 |

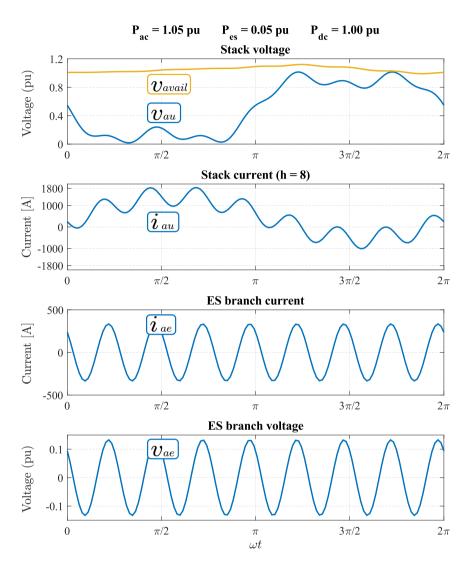

| 7.11 | Steady-state waveforms for the converter injecting 5% of extra power from the                                                                |     |

|      | ESS                                                                                                                                          | 135 |

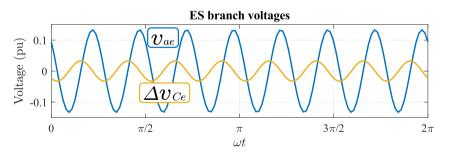

| 7.12 | ES branch voltages for an injection of 5% extra power from the ESS with a                                                                    |     |

|      | branch type b (inductors at the dc side).                                                                                                    | 135 |

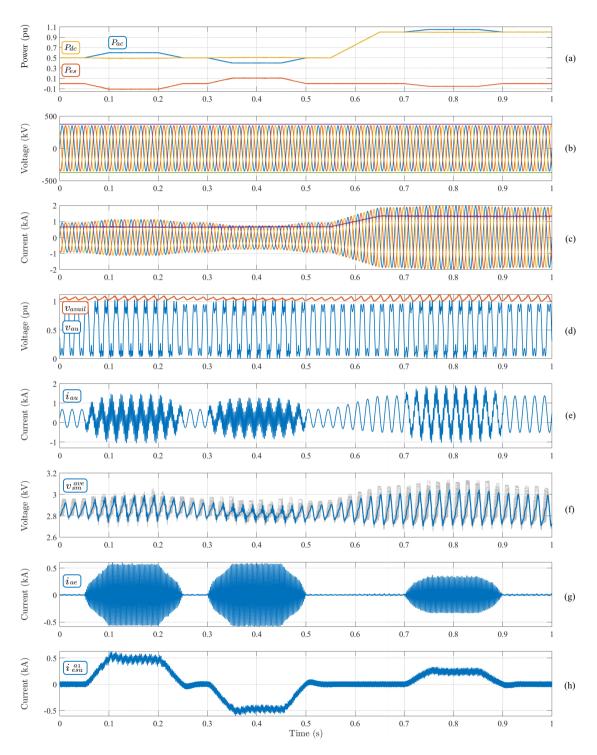

| 7.13 | Dynamic response of the converter for different power reference levels. (a)                                                                  |     |

|      | Power requirements at ac, dc and ES sides. (b) ac and dc voltages. (c) ac and dc                                                             |     |

|      | currents. (d) Stack voltages. (e) Stack current. (f) SMs voltages and average. (g)                                                           |     |

|      | ES branch current. (h) ES-SM dc current.                                                                                                     | 136 |

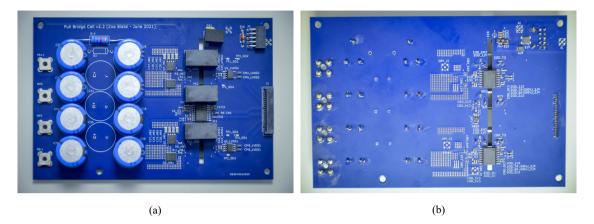

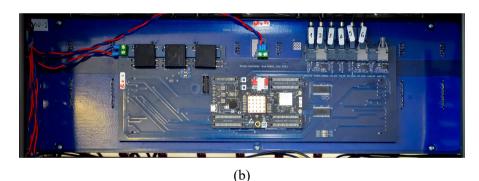

| 8.1  | MMC Experimental Setup. (a) Rear View. (b) Front View.                                                                                       | 140 |

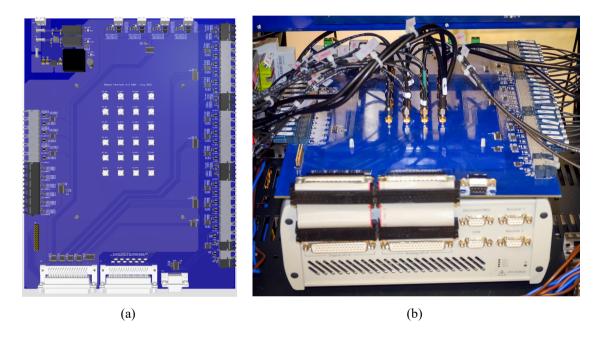

| 8.2  | Sub-module board. (a) Top View. (b) Bottom View.                                                                                             | 141 |

| 8.3  | Stack back-plane board with 10 SMs. (a) Front View. (b) Rear View                                                                            | 142 |

|      |                                                                                                                                              |     |

| 8.4  | dSPACE Interface Board. (a) Altium Designer 3D model. (b) Manufactured                |     |

|------|---------------------------------------------------------------------------------------|-----|

|      | Board.                                                                                | 143 |

| 8.5  | Designed Current Measurement Board.                                                   | 144 |

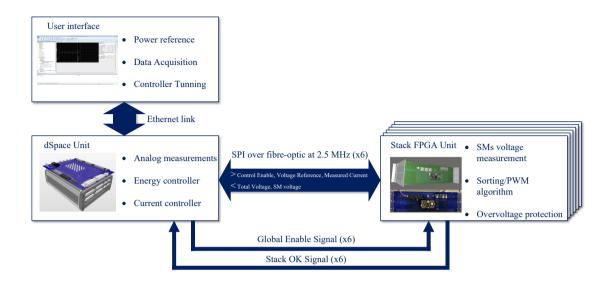

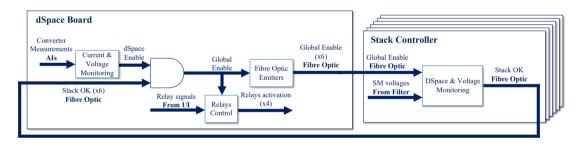

| 8.6  | Overall Hardware Control Scheme.                                                      | 145 |

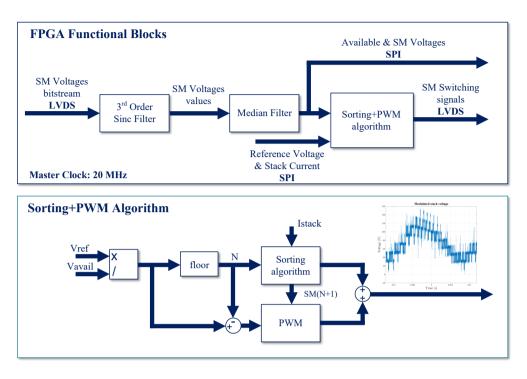

| 8.7  | Central Controller Functional Blocks.                                                 | 146 |

| 8.8  | Local Controller Functional Blocks.                                                   | 147 |

| 8.9  | Closed-loop Health Monitoring.                                                        | 147 |

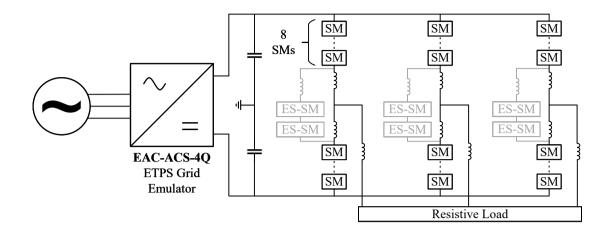

| 8.10 | Experimental setup configuration including ES branches optionally connected.          | 148 |

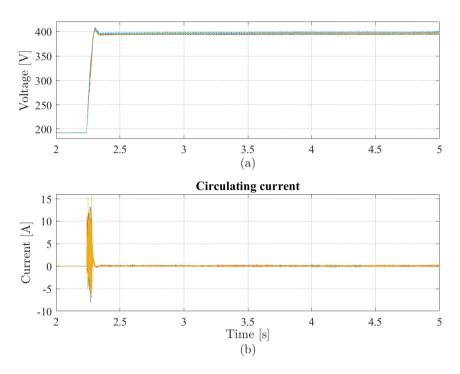

| 8.11 | Initial charge of the MMC capacitors. (a) Total available voltage charging up to      |     |

|      | 400 V. (b) Circulating currents charging the stacks.                                  | 149 |

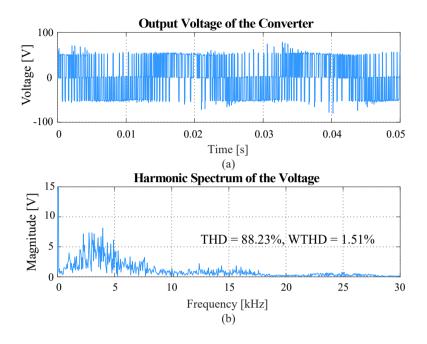

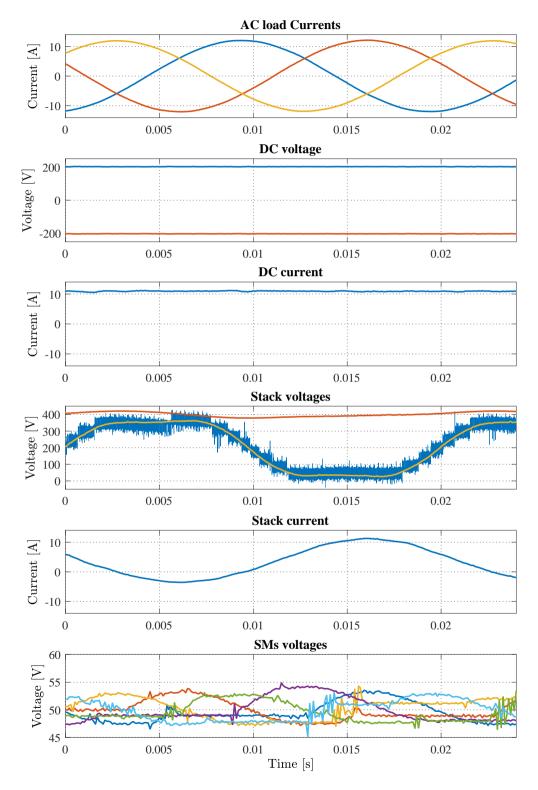

| 8.12 | Steady-state results for the MMC operating at 3.8 kW                                  | 150 |

| 8.13 | Output voltage of one phase of the MMC. (a) Output voltage of the converter. (b)      |     |

|      | Harmonic spectrum of the output voltage                                               | 151 |

| 8.14 | Dynamical response results for the MMC for a step on the AC power from 3.4            |     |

|      | kW to 3.8 kW.                                                                         | 152 |

| 8.15 | Steady-state results for the MMC with ESS operating at $P_{ac} = 1.2 \mathrm{kW}$ and |     |

|      | $P_{es} = 0.2 \text{kW}.$                                                             | 154 |

# LIST OF TABLES

| 2.1 | Summary for single-phase implementations of integrated dual-source dc-ac     |     |

|-----|------------------------------------------------------------------------------|-----|

|     | converters.                                                                  | 34  |

| 2.2 | Summary for three-phase implementations of impedance source dual-input dc-ac |     |

|     | converters                                                                   | 36  |

| 2.3 | Single-stage three-port dc-dc-ac topologies comparison                       | 43  |

| 4.1 | Parameters of the Analysed TPC for the Coupled Inductor Design.              | 76  |

| 4.2 | Parameters used in the Inductor Design.                                      | 77  |

| 4.3 | Obtained Coupled Inductor Design.                                            | 79  |

| 5.1 | Parameters of the simulated single-phase converter                           | 82  |

| 5.2 | Parameters of the simulated three-phase converter                            | 87  |

| 5.3 | Operation modes for the three-phase converter                                | 88  |

| 5.4 | Parameters of the simulated single-phase converter with coupled inductors    | 90  |

| 5.5 | Parameters of the Experimental Setup                                         | 93  |

| 5.6 | Specifications of the OPAL OP4510 Unit                                       | 93  |

| 5.7 | Comparison of single-phase integrated dual-source DC-AC converters including |     |

|     | the proposed TPC.                                                            | 96  |

| 7.1 | Parameters of the Simulated Converter                                        | 125 |

| 8.1 | Specifications of the MMC Setup                                              | 139 |

| 8.2 | Specifications of the Sub-Module                                             | 142 |

| 8.3 | Specifications of the dSPACE MicroLabBox Unit                                | 143 |

| 8.4 | Specifications of the ES branches of the MMC Setup                           | 155 |

#### ABSTRACT

The high penetration of renewable energies into power systems is leading to a revolution in the structure of modern power grids. In this context, the present thesis investigates the design of power electronics converters with extended capabilities due to the embedding of energy storage within the topologies. Thus, the research objective is to propose power converters with capabilities of integrating energy storage technologies to provide further services required for the operation of hybrid dc-ac systems. The thesis contains two parts, first part shows the work developed for low- and medium-power applications, while the second part describes the investigation performed for high-power systems.

The first part of this thesis explains the design and operation of a three-port dc-dcac converter developed for integrating energy storage into hybrid dc-ac applications. The topology is based on a conventional two-level dc-ac converter, and it uses a single power conversion stage to control the power flow between three ports, minimising the required components. Simulation and experimental results validate the operation of the proposal, showing that a multi-variable control system allows exploiting the degrees of freedom to manage power interactions of multiple elements without needing extra power converters. Furthermore, a comparative analysis is carried on to showcase the advantages and limitations of the proposal as opposed to state-of-the-art solutions in the same context. The study concludes that the proposed topology is suitable for low- and medium-power systems with bidirectional power flow capabilities among all ports and limited voltage boost needs. Simulation analysis shows that efficiencies up to 95.94% can be reached for a 3 kW design, which compares to efficiencies of similar state-of-the-art topologies. Moreover, the operation is also validated in a reduced-scale prototype allowing to test the multi-variable control scheme in a real-time implementation.

The second part of the thesis focuses on the design and operation of a Modular Multilevel Converter (MMC) topology with integrated energy storage using new parallel branches in the phases of the converter. This topology allows the integration of partially-rated Energy Storage Systems (ESS) to decouple the ac and dc sides of a High Voltage Direct Current (HVDC) substation. Thus, it enables the provision of ancillary services such as fast frequency response, black-start capabilities and load-levelling, which are required by modern hybrid dc-ac power grids. Results show that the proposal allows the addition of up to 37% power from the ESS considering similarly rated power semiconductors in a simulated 1 GW MMC substation. Analysis shows that extra device losses remain under 1% for an additional  $\pm 10\%$  of ESS power on top of the nominal substation-rated power. Furthermore, a laboratory-scale experimental rig was built to demonstrate the operation of the proposed design.

In conclusion, two different topologies are proposed and analysed for integrating energy storage into hybrid dc-ac applications depending on the power rating required. The study is supported by simulation and experimental results obtained during the project to validate both proposals.

**Keywords:** DC-AC Power Conversion, Multi-port Converters, Modular Multilevel Converters (MMC), Energy Storage Systems (ESS), Hybrid Power Integration, Multi-variable Control Systems.

#### RESUMEN

La creciente inclusión de energías renovables en los sistemas eléctricos está provocando una revolución en la estructura de las redes eléctricas modernas. En este contexto, la presente tesis investiga el diseño de conversores de potencia con capacidades extendidas debido a la incorporación de almacenamiento de energía dentro de las topologías. Así, el objetivo de la investigación es proponer conversores de potencia con capacidades de integración de tecnologías de almacenamiento de energía para brindar servicios adicionales requeridos para la operación de sistemas híbridos CC-CA. La tesis consta de dos partes, la primera parte muestra el trabajo desarrollado para aplicaciones de baja y media potencia, mientras que la segunda parte describe la investigación realizada para sistemas de alta potencia.

La primera parte de esta tesis explica el diseño y operación de un conversor CC-CC-CA de tres puertos desarrollado para integrar el almacenamiento de energía en aplicaciones híbridas CC-CA. La topología se basa en un convertidor CC-CA convencional de dos niveles y utiliza una sola etapa de conversión de energía para controlar el flujo de energía entre tres puertos, lo que minimiza los componentes necesarios. Los resultados de simulación y experimentales validan el funcionamiento de la propuesta, mostrando que un sistema de control multivariable permite explotar los grados de libertad para gestionar interacciones de potencia de múltiples elementos sin necesidad de conversores de potencia adicionales. Además, se realiza un análisis comparativo para mostrar las ventajas y limitaciones de la propuesta frente a soluciones de vanguardia en el mismo contexto. El estudio concluye que la topología propuesta es adecuada para sistemas de potencia media con capacidades de flujo de potencia bidireccional entre todos los puertos y necesidades limitadas de aumento de voltaje.

La segunda parte de la tesis se centra en el diseño y operación de una topología de Conversor Modular Multinivel (MMC) con almacenamiento de energía integrado utilizando nuevas ramas paralelas en las fases del conversor. Esta topología permite la integración de sistemas de almacenamiento de energía (ESS) de potencia limitada para desacoplar los lados de CA y CC de una subestación HVDC. Por lo tanto, permite la provisión de servicios auxiliares como respuesta de frecuencia rápida, capacidades de arranque en negro y nivelación de carga, que son requeridos por las redes eléctricas híbridas de CC-CA. Los resultados muestran que la propuesta permite agregar hasta un 37% de potencia desde el ESS considerando semiconductores de potencia de clasificación similar en una subestación MMC simulada de 1 GW. El análisis muestra que las pérdidas de dispositivos adicionales se mantienen por debajo del 1% por un  $\pm 10\%$  adicional de energía desde ESS.

En conclusión, esta tesis propone y analiza dos topologías diferentes para integrar el almacenamiento de energía en aplicaciones híbridas de CC-CA según la potencia nominal requerida. El estudio se apoya en resultados de simulación y experimentales obtenidos durante el proyecto para validar ambas propuestas.

Palabras Claves: Conversión de energía CC-CA, Conversores Multipuerto, Conversores Modulares Multinivel (MMC), Sistemas de Almacenamiento de Energía (ESS), Sistemas Híbridos de Potencia, Sistemas de Control Multivariable.

#### 1. INTRODUCTION

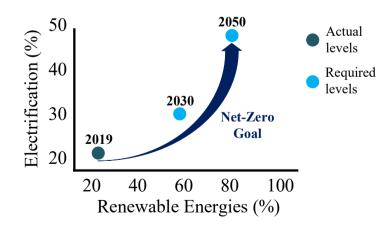

The energy transition towards a carbon-neutral world is key to the sustainability of humanity and also, and urgent need due to accelerated climate changes. Thus, most countries around the world aim to reach the carbon-neutral goal by 2050 (Evans et al., 2022; Guterres, 2020; McKinsey & Company, 2022). Consequently, there is a growing need for the inclusion of renewable energies into the grid at both industrial and residential levels. Additionally, the electrification of final energy uses, such as heating and transport, also needs to increase drastically to achieve the Net-Zero goal. Specifically, renewable participation in electricity generation should rise to 86% and electrification of end uses should go from the current 20% to around 50% by 2050 to achieve the goal (International Renewable Energy Agency (IRENA), 2020), as shown in Fig. 1.1. Therefore, the development of power converters for using renewable sources and replacing fossil fuel systems achieving high density, efficiency and reliability is one of the main challenges in reaching the zero net emissions goal.

The use of power converters is fundamental to increase electrification based on renewable energies, as this challenge imposes the use of Direct Current (DC) technologies in

FIGURE 1.1. Required electrification and renewable generation share to achieve Net-Zero goal.

FIGURE 1.2. Battery Energy Storage Systems Worldwide Installed Capacity.

conjunction with the existing Alternate Current (AC) systems (Rodriguez et al., 2009). Examples of these hybrid DC-AC systems requiring power converters are solar photovoltaic (PV) generation connected to the AC grid, HVDC interconnections between two or more AC grids and Electric Vehicles (EV) powertrains (Clement-Nyns et al., 2010; Eftekharnejad et al., 2013; Kroposki et al., 2017; MacDowell et al., 2019; Shen et al., 2019). However, the inclusion of power converters raises a stability problem for the grids, as inherently these technologies do not contribute to the system inertia as large synchronous generators (Gevorgian et al., 2015; Lasseter et al., 2020; Y. Liu et al., 2017). Thus, the latest research trends have focused on implementing grid-forming capabilities in power converters to address the stability issues on small and large-scale systems (Fang et al., 2019; Rathnayake et al., 2021; Serban & Marinescu, 2014). The lack of kinetic energy in power converter systems leads to the use of different energy storage sources (Batteries, super-capacitors and hydrogen-based systems) to provide the required services maintaining the grid operation (Fang et al., 2018; Renaudineau et al., 2022). Therefore, the use of Energy Storage Systems (ESS) has increased rapidly in the last years, with studies showing a growth factor of 6 for utility-scale ESS to 2026 (International Energy Agency (IEA), 2021), as shown in Fig. 1.2.

Consequently, the transformation of power systems to comply with a sustainable development path presents two main technical challenges to be tackled with the use of power electronics systems:

• Co-existence of AC and DC technologies to increase the electrification of all sectors based on renewable energy sources.

• Integration of ESS into hybrid DC-AC systems to support the operation, addressing the variability of renewable resources and replacing fossil fuel-powered technologies.

#### 1.1. Hybrid DC-AC Applications with Energy Storage

Different technologies will drive the transformation of modern power systems to face the rising inclusion of clean energy sources and decommissioning of fossil fuel systems. Applications can be classified according to their operation characteristics, such as power and voltage levels, as these define the requirements for the needed power conversion stage. Thus, this section will describe the main hybrid DC-AC technologies playing a role in the energy transition to a carbon-neutral society according to their power levels.

#### 1.1.1. Low and Medium Power Applications

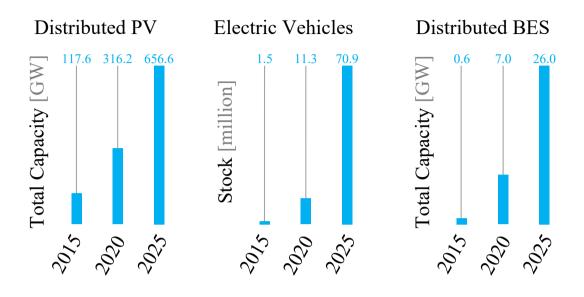

The inclusion of Distributed Energy Resources (DER) is a major change in the operation of modern electrical grids, which used to be highly unidirectional and dominated by utility-scale generators. DERs consist of units located close to the end-users that are able to generate, store and use energy in a controlled manner. Thus, they cover a wide spectrum of technologies as PV generation, ESS (based on batteries, supercapacitors or hydrogen systems) and EVs. These applications usually connect to the grid at the distribution level with rated powers of less than 10 MW. Then, DERs play a fundamental role in the electrification of different sectors and the integration of renewable energy sources into the grid. Additionally, analysis shows that they allow avoiding and/or deferring investment in network infrastructure when used in highly saturated areas at the distribution level (Energy Networks Australia, 2017; National Renewable Energy Laboratory (NREL), 2021). Therefore, the inclusion of DERs has been increasing in the later years and it is projected to keep the trend in the following years, as it is shown in Fig. 1.3.

Distributed PV systems are a well-deployed technology, with significant participation on the renewable generation matrix during the last 10 years. Therefore, the technology seems mature with continuously decreasing prices and a set of relevant actors providing

FIGURE 1.3. Inclusion trend of main DERs technologies.

power electronics solutions to connect the PV arrays to the grid. However, there is an opportunity for innovation due to the trend of complementing solar installations with energy storage. This integration allows for improving the overall performance of the system by enabling extra frequency and voltage regulation services using the battery as an energy buffer (Kouro et al., 2015). The penetration of this hybrid configuration is increasing, with countries such as Germany and Hawaii having close to 50% and 100% respectively of their residential solar installed capacity with energy storage units (Bloomberg NEF, 2022).

The share of EVs in the transport market has also increased rapidly in the last years, with projections showing that they should represent more than 60% of the sold vehicles by 2030 (IEA, 2022b). EVs are classified into two major groups, Battery Electric Vehicles (BEV) and Plug-in Hybrid Electric Vehicles (PHEV) depending on the energy source of the powertrain (Habib et al., 2018; Martinez et al., 2017). BEVs power the traction motor exclusively from a battery and dominate the market reaching 68% of the EVs share by 2021 (IEA, 2022a). However, IEA also projects a continuous increment in the PHEV use, having a stock 10 times bigger by 2030 from the present numbers. PHEVs use more than

one energy source, with vehicles using hydrogen fuel cells together with Li-ion batteries showing a promising example for future models.

#### **1.1.2. High Power Applications**

The principal change driving the modernisation of the electrical grid at a high-power level is the inclusion of HVDC links in the transmission system. This technology allows integrating remotely located renewable energy sources with the main loads of the grid and also interconnecting different asynchronous AC systems (Barnes et al., 2017; X. Chen et al., 2011; Feng et al., 2014; Flourentzou et al., 2009; L. Zhang et al., 2017). The technical advantages supporting the inclusion of HVDC links into AC systems are the elimination of reactive power, higher power transfer density and the ability to connect asynchronous systems (European Network of Transmission System Operators for Electricity (ENTSO-E), 2019). Therefore, it is projected that the installed capacity of HVDC links evolves from 277 GW in 2017 to over 500 GW by 2025 (Alassi et al., 2019; IEA, 2016).

The main importance of HVDC links is related to enabling the deployment of hybrid DC-AC grids and the connection of large-scale offshore wind energy supplies to the grid, which are two of the flagships defined in the Research, Development, and Innovation Roadmap to 2030 stated by ENTSO-E (2020). Additionally, they should also be able to provide ancillary services to the grid to face the stability issues generated by the decommissioning of fossil fuel-based rotating plants (Aouini et al., 2016; Junyent-Ferr et al., 2015; H. Liu & Chen, 2015). In this regard, the inclusion of energy storage sources appears as a suitable alternative to enable the provision of these services and increase the flexibility of the hybrid DC/AC grids (Errigo, Morel, et al., 2022).

#### 1.1.3. Energy Storage Systems

Energy storage systems appear as a fundamental technology enabling the modernisation of power grids to include the required renewable energy sources and to increase the electrification of end-user applications. ESS work at all power levels providing services to

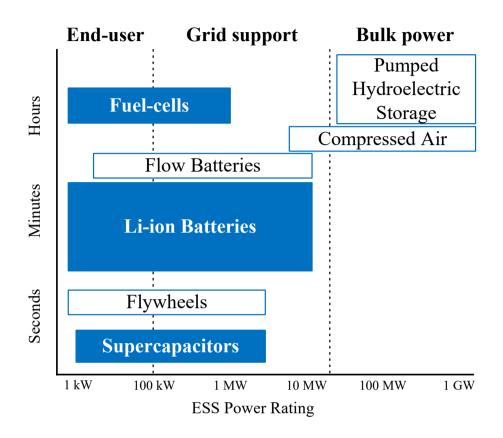

FIGURE 1.4. ESS technologies with power ratings and energy capacity.

improve the grid resilience and add more flexibility to the grid operation. The main principle is to store generated energy from any source into the unit, to then be able of using it when the system requires to. Thus, the main parameters defining the ES units are power rating and the energy capacity defining for how long they can provide the rated power. These parameters vary depending on the selected energy storage technology, as shown in Fig. 1.4 (Boicea, 2014; Farhadi & Mohammed, 2016; Grainger et al., 2014; Stynski et al., 2020). The figure also shows that different ESS technologies are suitable for providing different services, depending on the power and energy capacity. Furthermore, the main three technologies related to the development of the converters in this research are highlighted: Li-ion batteries, supercapacitors and fuel cells. Li-ion batteries are the most mature energy storage technology and it is expected for them to keep increasing their penetration into power systems, as illustrated in Fig. 1.2 and Fig. 1.3. The main advantages of these batteries are high energy density, fast response, low self-discharge and continuously decreasing manufacturing costs (Lukic et al., 2008; Vazquez et al., 2010). The main applications for Li-ion batteries are EVs, residential ESS, and utility-scale ESS providing regulation services to the grid.

Supercapacitors (SCs) stand out in ES technologies because of their very high power density (1000-10000 W/kg), energy efficiency up to 95% and long cycle life (>50000 cycles) (Fang et al., 2019; Vazquez et al., 2010). Therefore, industry vendors have already started implementing systems based on SCs to provide grid services (ABB, 2012). The main downside of SCs is the reduced energy density compared to other ES technologies, limiting their use for applications with short operational times. However, the latter has motivated the research for hybrid systems, aiming to complement the high power capabilities of SCs with high energy technologies as batteries or fuel cells (Choi et al., 2012; Fang et al., 2018; Thounthong et al., 2007; L. Zhang et al., 2019). Thus, the main use for SCs is related to hybrid EV powertrains and low-energy demanding grid services, such as voltage regulation.

Finally, hydrogen-based ESS are meant to play an important role in the decarbonisation of sectors where fossil-fuel systems are still the standard, such as heavy-duty transport and heavy industry (IEA, 2021). Additionally, hydrogen appears as an emerging technology for seasonal storage of renewable energy due to it very high energy density. The operation of low-emissions hydrogen ESS is based on two main elements: the electrolysers for producing hydrogen from renewable sources, such as PV systems (Renaudineau et al., 2022); and the fuel-cells to generate electricity from the generated hydrogen. The fuel-cell technology has been developed in the last decade, with its main use related to EVs (Bauman & Kazerani, 2008; Zandi et al., 2011).

The common characteristic for the three ES technologies presented is that they operate in DC, therefore they require the use of power converters to be connected to conventional AC grids and loads. Thus, for the purpose of the present research project, the ESS sources will be modelled as DC power supplies indicating the operational power and energy parameters when required.

#### **1.2.** Power Electronics for Hybrid DC-AC Applications with Energy Storage

This section provides a review of the state-of-the-art Power Electronics (PE) systems that have been proposed to address the challenges presented by the applications of the last section. The inclusion of the described applications to enable the net-zero goal by 2050 is strongly attached to the development of new PE topologies. Therefore, research has focused on developing efficient, reliable, and power-dense solutions for these systems in the latter years. The topologies are presented in two different groups, according to their power levels.

#### 1.2.1. Low and Medium Power Topologies

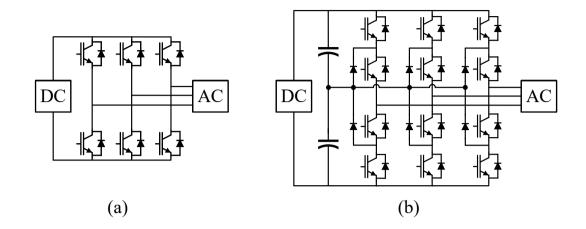

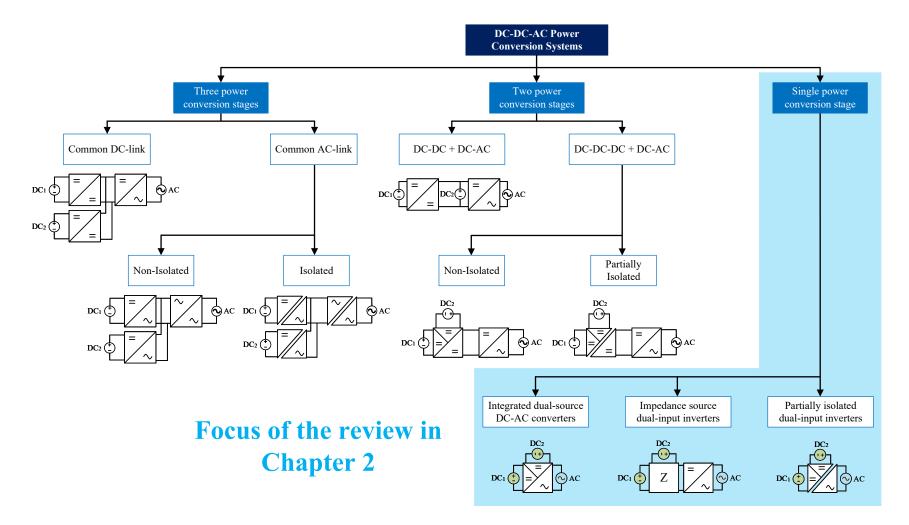

The PE technology to connect DC systems with AC ones is mature, with the Voltage Source Converters (VSC) having crucial importance in the integration of DC technologies to the existing AC grids. For low- and medium-power applications, the most accepted topologies are the two or three-levels converters shown in Figure 1.5. However, section 1.1.1 showed that new applications require the inclusion of energy storage units to complement the operation of the DC-AC power conversion. Therefore, this section presents a review of different power conversion systems aiming to operate with the hybrid DC-AC applications with energy storage, which in this case also operate in DC (either battery, supercapacitor or fuel cell depending on the power and energy needs). Then, it covers power conversion systems connecting two DC ports with one AC port. These systems can be categorised into three main groups depending on the Power Conversion Stages (PCS) used to perform the connection of the three elements. Fig. 1.6 summarises the proposed classification, showing that three major groups exist depending on whether they use three, two or a single PCS. The following subsections present a description of each category addressing the way they work with their advantages and disadvantages.

FIGURE 1.5. DC-AC Voltage source converters. (a) Two-levels topology. (b) Three-levels topology.

FIGURE 1.6. Classification of DC-DC-AC Power Conversion Systems.

FIGURE 1.7. Example of a three power conversion stages system with common DC-link.

#### A. Three power conversion stages: Common DC link

The most straightforward solution to connect the three elements is to use one power converter interfacing each element. These solutions are used today in commercially available systems as they are based on well-known DC-AC and DC-DC topologies. Then, this category covers solutions using three power converters connected in a common DC link, therefore they contain two DC-DC converters plus a DC-AC one (F. Liu et al., 2014; Locment et al., 2012; Moré et al., 2015; Saxena et al., 2018; K. Sun et al., 2011; Thang et al., 2015; Thounthong et al., 2009). Fig. 1.7 shows an example of this approach, using two bidirectional buck-boost converter is attached. Depending on the application, DC-DC converters can be simplified to be unidirectional and DC-AC converters can be extended to a three-levels implementation.

The solution with three PCS allows controlling independently the currents flowing through each port, always considering the overall power balance of the system. Therefore, each converter is regulated by a separate single-variable control loop, which simplifies the implementation as it enables the use of classical control schemes. The main drawback of this solution is that connecting converters in cascade generates cumulative losses that reduce the overall efficiency of the system (A. K. Bhattacharjee et al., 2019). Furthermore,

FIGURE 1.8. Examples of a three power conversion stages system with common AC-link. (a) Non-Isolated. (b) Isolated.

the use of multiple converters increases the components count and consequently the overall cost and failure probability grow.

#### **B.** Three power conversion stages: Common AC link

The common DC link is the dominant group in the category of solutions using three PCS, however, the need for a bulky electrolytic capacitor at the point of connection has motivated the research on using an AC link instead. Electrolytic capacitors can reduce the reliability of the solution, as they are very sensitive to temperature changes that can highly reduce their lifetime (Amirabadi et al., 2014). Thus, the use of an AC link appears as an alternative solution for eliminating the need for capacitors, aiming to improve the reliability of the system. The AC link requires the use of Current Source Converters (CSC) instead of VSC, as the element storing energy in the link is now an inductor replacing the capacitor. Consequently, the solutions in this category include two DC-AC converters plus an AC-AC converter (Amirabadi et al., 2013; Bilakanti et al., 2017; Haque et al., 2017).

Fig. 1.8 shows examples of the implementation of common AC link solutions for both non-isolated and isolated cases. The non-isolated case uses three CSC and it regulates the power flow by changing the time that every port charges or discharges the inductor.

FIGURE 1.9. Example of a two power conversion stages system with DC-DC + DC-AC converters.

The frequency of charging/discharging is several orders higher than the one at the AC port. Additionally, a small capacitor is included in the link to allow resonance periods that enable the zero voltage turn-on of the switches. The isolated case replaces the inductor with a high-frequency three-winding transformer and operates in a similar manner to the non-isolated alternative. The main advantage of these solutions is a reduction in size and possible increment in efficiency by using a high-frequency AC link with soft-switching techniques. However, the control becomes more complex, as the soft-switching techniques impose restrictions to be met the same time of regulating the power through each port. Additionally, the number of active semiconductors escalates as bidirectional switches are needed for implementing the CSC.

#### C. Two power conversion stages: DC-DC + DC-AC

There are applications where the accurate control of the current at one of the DC ports is not highly relevant, for example when capacitors or super-capacitors are used o interface a DC source with the DC-AC converter. Relevant applications include ripple mitigation for PV systems and using of supercapacitors or batteries as secondary energy sources. Then, one of the DC-DC converters in the three PCS common DC-link implementations can be avoided, leading to a topology as the one shown in Fig. 1.9 (Dong, Cvetkovic, et al., 2013; Dong, Luo, et al., 2013; Gautam et al., 2020; Gautam et al., 2018; B. Liu et al., 2018; L. Zhang et al., 2015).

This group presents the same advantages as the common DC-link category, as it also allows using well-known topologies for the connection of the three ports. Moreover, the elimination of one DC-DC converter leads to a reduction in the required components, thus

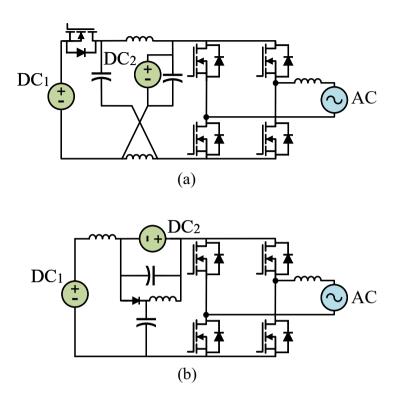

FIGURE 1.10. Examples of a two power conversion stages system with DC-DC-DC + DC-AC converters. (a) Non-Isolated. (b) Partially-Isolated.

improving the efficiency and overall cost of the solution. The control is implemented with two independent loops regulating the currents at the AC side and one of the DC ports connecting an element that could be affected by transient and oscillatory behaviours as a fuel cell or a PV array. The second DC element (namely ES in the Figures) is regulated by the overall power balance of the system, but the current can contain harmonics and/or transient spikes. Therefore, usually this element would be a capacitive element or a battery able to withstand this performance.

#### D. Two power conversion stages: DC-DC-DC + DC-AC

Multi-port converters have emerged as an attractive alternative to replace multiple PCS and therefore improve the efficiency and power density of the power electronics needed to integrate different renewable energy technologies. In this context, three-port DC-DC-DC converters appear as a suitable solution to connect elements such as PV arrays, batteries and fuel cells with loads in a compact manner. N. Zhang et al. (2016) and A. K. Bhattacharjee et al. (2019) present throughout studies, indicating how these converters can optimise the integration of ESS with variable renewable resources or the operation of Hybrid ESS. Therefore, these DC-DC-DC converters also represent a viable solution when complemented with DC-AC converters to connect two DC elements with the grid or an AC load.

Fig. 1.10 illustrate two examples of topologies in this group for non-isolated and partially-isolated sub-categories. Non-isolated solutions implement the DC-DC-DC converter using a combination of Buck/Buck-Boost/Boost cells in series, cascaded or stacked

configurations to perform the power flow between the three ports (Chien et al., 2014; Moradisizkoohi, Elsayad, & Mohammed, 2019; Moradisizkoohi, Elsayad, Shojaie, et al., 2019). Then, a conventional DC-AC converter interfaces the AC port, controlling the power flow from the DC sources. Partially-isolated configurations use a high-frequency link to connect with the load, similar to the AC-link isolated solutions. However, in this group, the two DC ports are connected through a single stage to the load side by merging a boost converter with a phase-shifted full-bridge (Deng et al., 2019; Lu et al., 2019; X. Sun et al., 2015; K. Wang et al., 2019; J. Zhang et al., 2015). The secondary side considers a rectifier interfacing with the DC-AC converter at the DC link.

Both sub-categories present a similar control scheme with two specific loops regulating the operation of each PCS. The first controller regulates the currents in the three-port DC-DC converter, using the duty cycle and the phase-shift variables to set the currents of the two DC sources. Then, the second controller regulates the DC-AC converter to achieve the power balance of the entire system. Analysis from A. K. Bhattacharjee et al. (2019) indicates that non-isolated solutions work better for lower power ( $\leq 600$  W), while isolated topologies are more suitable for powers above 600 W.

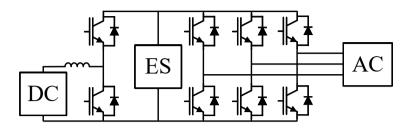

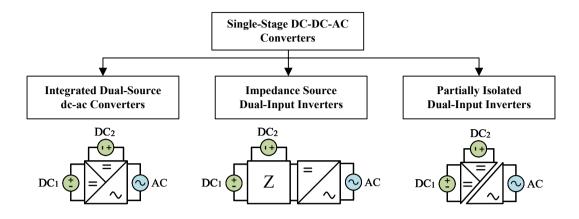

#### E. Single power conversion stage: DC-DC-AC converters

Following the same motivation behind the development of multi-port DC-DC-DC converters, single-stage DC-DC-AC power converters have been proposed by researchers during the last decade, looking to further optimise the PCS interfacing the three ports. These topologies perform the tasks of two or three separated converters, allowing the power flow control between three sources/loads with an optimised single power processing stage. The motivation behind these topologies is to reduce the required components, thus improving the efficiency and reliability of the power conversion system (Wu et al., 2017). Additionally, they can provide extra features such as embedded boost capabilities, continuous current at the dc elements or galvanic isolation with the ac port (A. K. Bhattacharjee & Batarseh, 2021; Ribeiro et al., 2010). However, they also present some limitations, such as restricted power regulation capabilities and the need for advanced control and modulation techniques. Nevertheless, better-suited topologies for different applications can be determined, considering the mentioned limitations at the design stage. Thus, a comparative analysis of these single-stage three-port topologies is fundamental to classify them according to their features and possible applications.

The proposed converter described and analysed in Chapters 3 and 4 belongs to this group, as it allows connecting two DC ports with an AC one using the minimum amount of active semiconductors. Thus, it is especially suited for applications where energy storage needs to be embedded into the power electronics operating hybrid DC-AC systems. This group will be described in depth in Chapter 2 to further analyse the closest solutions, in terms of power density, to the proposed topology in the first part of this thesis.

#### 1.2.2. High Power Topologies

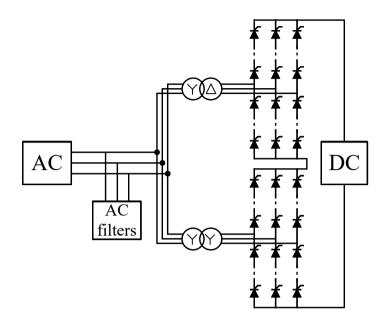

HVDC technology using semiconductor devices has been implemented for more than 50 years, when thyristors started replacing the mercury-arc valves (Barnes et al., 2017). These devices require the existence of an AC grid to commutate and change the conduction state, therefore the HVDC converters based on thyristors are called Line-Commutated Converters (LCC). Fig. 1.11 shows a typical implementation of an LCC based on the first benchmark HVDC system defined by CIGRE (Szechtman et al., 1991). The converter operates by regulating the firing angle of the thyristors against the AC voltage. This technology is mature, covering the majority of commissioned HVDC projects around the world because of its reliability and high-power capability. However, LCCs present several disadvantages that limit their use for modern hybrid DC-AC systems: The active and reactive powers are coupled; they require a strong AC grid to operate, thus they are unable to provide grid forming capabilities; they require a large amount of filtering and reactive power compensation; and the operation difficult the implementation of multi-terminal systems, as reversing power flow requires to change the polarity of the DC voltage. Therefore, VSCs have risen as an adequate alternative to operate in high-voltage high-power systems too, as they address the limitations of LCCs. The first HVDC projects based on VSCs considered

FIGURE 1.11. Example of a HVDC 12-pulse Line-Commutated Converter.

the use of conventional topologies as the ones shown in Fig. 1.5, replacing each device for large arrays of series connected devices to address the high-voltage levels. Then, the Modular Multilevel Converter (MMC) was implemented for the first time in an HVDC project in 2010 by Siemens in the Trans-Bay Cable project for a 400 MW,  $\pm$  200 kV, 85 km long HVDC line (Judge, 2016).

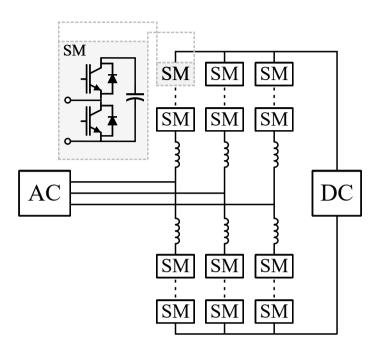

MMC stands out for High-Voltage Direct-Current (HVDC) applications because of its modularity, efficiency and reliability (Lesnicar & Marquardt, 2003; Saeedifard & Iravani, 2010; Tu et al., 2011). Fig. 1.12 presents the MMC circuit, consisting of six stacks of series connected half-bridge Sub-Modules (SM) together with an inductor to control the current through them. Each stack with the respective inductor conform an arm, and two arms compose a phase. The topology has been widely studied for applications described in Section 1.1.2, such as multi-terminals DC grids, off- and on-shore wind farms applications and AC grids interconnection (Debnath et al., 2015; Guan & Xu, 2012; Leon, 2018; Peralta et al., 2012; Saad et al., 2013; P. Wang et al., 2016). Furthermore, the use of MMC has enabled the increase in the power ratings of HVDC substations, with current projects built to operate above 1 GW. Thus, it is projected that the new capacity to be installed of these

FIGURE 1.12. Modular Multilevel Converter.

systems between 2020-2028 doubles the capacity added during 2010-2019 (Nishioka et al., 2020). The latter is driving a modernisation on the requirements that the system operators ask to the MMC developers to agree with, such as the capability to provide frequency regulation and other ancillary services to strengthen the system response to contingencies.

The ability to provide additional grid services of the MMC partially depends on the amount of energy that it can use for transferring extra power to the side requiring additional regulation. The topology inherently includes energy storage as each SM contains a capacitor that holds the voltage to get to the HVDC levels. However, the average energy of an MMC falls into the range of 30-40 kJ/MVA, thus the services to provide from this source are very limited (Spallarossa et al., 2016). Therefore, integration of ESSs into MMC substations has been proposed as a feasible alternative to enable the provision of ancillary services to the grid (Errigo, Morel, et al., 2022). Accordingly, different ways to integrate ESS within the MMC have been published in the last years, considering different approaches to integrate ESS into MMC substations published in the last years.

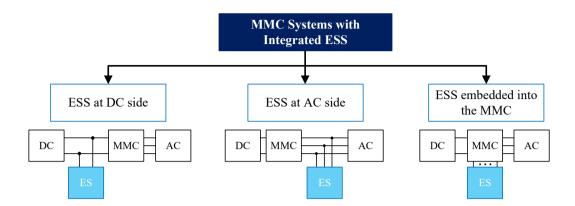

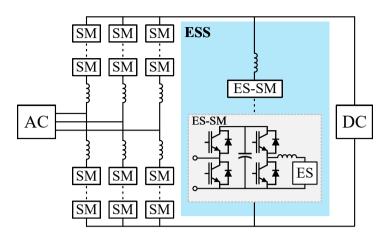

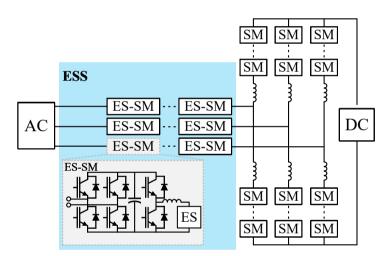

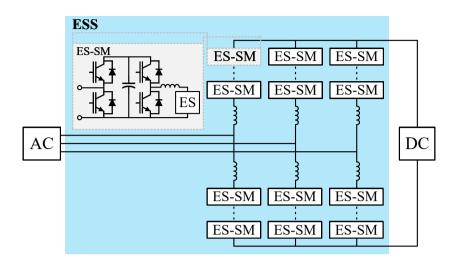

FIGURE 1.13. Classification of configurations to integrate ESS into MMC substations.

showing that three main groups can be defined based on the location of the energy storage elements.

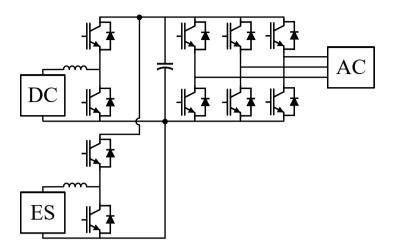

#### A. ESS on DC side

The first approach is to connect the ESS on the DC side of the substation using a shunt configuration to inject or absorb current in a controlled way on that side (Díaz-González et al., 2020; Ma et al., 2021; Mukherjee & Strickland, 2015; S. Wang et al., 2022). This is the simplest approach from the controlling point of view, as it allows to regulate directly the power exchanged between the ESS with the substation. The connection is performed using a cascaded array of sub-modules including energy storage units (ES-SM), following the same principle behind the MMC topology to address the high-voltage levels. Fig. 1.14 shows the topology for this configuration, showing that the ESS is an independent converter from the MMC and has to connect to full DC voltage. The ES-SMs consist of a DC-DC converter connected to the regular SM to interface the energy storage units, thus allowing the decoupling of the ES units voltage to the HVDC level. S. Wang et al. (2022) concludes that this implementation shows the most cost-effective solution for integrating ESS into MMC substations. However, this implementation only ensures the provision of grid services to the DC side of the substation, as the MMC should be overrated if the extra power from the ESS has to be transferred on top of the nominal power to the AC side.

B. ESS on AC side

FIGURE 1.14. MMC substation with ESS on the DC side.

FIGURE 1.15. MMC substation with ESS on the AC side.

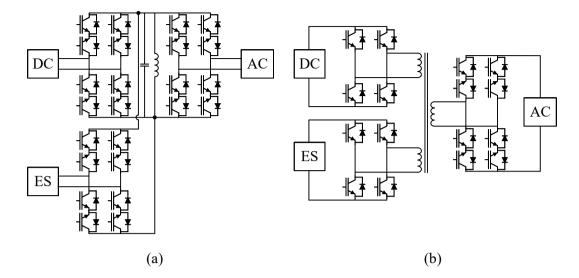

The second group also connects the ESS outside the MMC, but on the AC side using a series connection to sink or source power on that side when required (S. Wang et al., 2020; S. Wang et al., 2021). The ESS consists of a series connected array of full-bridge SM including energy storage units interfaced through a DC-DC conversion stage, as shown in Fig. 1.15. The ESS converter generates an AC voltage to control the amount of power to be exchanged with the grid, and it could be controlled separately from the MMC in the same way as the DC-side connected version. Additionally, the topology includes a set of anti-parallel connected thyristors in parallel to the ES-SMs, allowing to bypass the ESS converter when not in use. This configuration is proposed to block grid faults, and

FIGURE 1.16. MMC substation with embedded ESS.

therefore the ESS converter should be able to withstand the full AC voltage. Consequently, the implementation on the AC side uses more devices than the one on the DC side, as the ESS is implemented in the three phases and it requires full-bridge SM instead of half-bridge ones.

#### C. ESS embedded into the MMC

The first two groups implement the ESS separated from the MMC complementing its operation, but without taking advantage of the topology itself. A different approach is to embed the ES units locally into the MMC SMs, exploiting the modularity and scalability of the topology instead of adding additional modular converters either on the DC or AC sides. This configuration considers the replacement of the MMC SMs by ES-SMs (see Fig. 1.16), using either supercapacitors or batteries depending on the energy and power requirements (Chaudhary et al., 2020; Errigo, Morel, et al., 2022; Hillers et al., 2015; Novakovic & Nasiri, 2017; Pinto et al., 2021; Soong & Lehn, 2014; Vasiladiotis & Rufer, 2015; Xu et al., 2022; Zeng et al., 2022; L. Zhang et al., 2019). This solution allows to enhance the DC-AC conversion by decoupling the two sides using the ESS to exchange power according to the system needs. The management of the ESS is integrated with the MMC controller using new loops to regulate the current flowing from or to the ES units, Vasiladiotis and Rufer (2015) provides an example of the controller structure needed.

The MMC-ESS configuration is the most flexible, as it allows power exchange directly from the substation to both DC and AC sides. Nevertheless, ESS-related services often only require a small amount of extra power from the converter, making partially-rated ESS more suitable (Soong & Lehn, 2016). Thus, the inclusion of partially rated ES into HVDC MMC substations appear as a feasible solution to extend the system capabilities with a limited impact on the operational ratings (Blatsi et al., 2021; Errigo et al., 2019; Errigo, De Oliveira Porto, et al., 2022; Henke & Bakran, 2016; Judge & Green, 2019; Neira et al., 2021; Zeng et al., 2019). A promising approach is the partial insertion of ES units into a subset of SMs, leading to an hybrid topology with both SMs and ES-SMs (Errigo et al., 2019; Errigo, De Oliveira Porto, et al., 2022; Henke & Bakran, 2016; Judge & Green, 2019; Zeng et al., 2019). This allows for reducing the number of DC-DC interfaces required and therefore the overall costs and power losses can be reduced. The ES-SMs can be unevenly distributed in the converter and the energy balance is performed using circulating currents. The number of required ES-SM depends on the additional service to be provided, results from (Judge & Green, 2019) indicate that a 0.1 p.u. increase in the MMC power is achieved using only 4% of ES-SM over all SMs. Therefore, this solution can enhance the operation of MMC substations, enabling the delivery of services from frequency regulation to load levelling and fault ride-through.

The main drawback of the implementation of ESS into MMC SMs (either full or partially-rated cases) is that the topology of the classic SM is modified. Thus, the stacks are modified and then current substations designs need to be modified to implement this solution. Therefore, an alternative configuration to include partially rated ESS into MMC substations is presented and analysed in Chapters 6-8.

# 1.3. Original Contributions and Layout of the Thesis

The main contribution of this thesis is the development and analysis of power converters topologies to integrate energy storage into AC-DC systems at different power rating levels. The project was developed at the Pontificia Universidad Católica de Chile (PUC) and The University of Edinburgh (UoE), following a dual-degree agreement between the two universities. The thesis is organised in two parts: the first one describes the work developed for integrating ESS in a topology for low- and medium-power applications and; the second one presents the proposal for ESS integration in an MMC topology for high-power applications.

## **1.3.1.** Original Contributions

The first part of the thesis (Chapters 2-5) was performed during the first half of the program at the Power and Energy Conversion Laboratory (PECLAB) of the PUC. The contribution of this first half is the proposal and development of a three-port dc-dc-ac converter using a single power processing stage. The state-of-the-art analysis presented in Chapter 2 was carried out by the author considering the available publications on three-port single-stage topologies developed to operate with ESS. The topology operation and control scheme to minimise the power conversion stages required to control the power flow between three ports (Chapter 3) are solely the work of the author. The idea of using coupled inductors to reduce the current load of the devices in the three-port converter (Chapter 4) is based on similar applications in the literature, which are cited in the relevant sections. The work supporting these chapters was performed under the supervision and advice of Dr. Javier Pereda.

The second part of the thesis (Chapter 6-8) was carried out within the Power Electronics Group at UoE. The main contribution of these sections is the development of a new MMC topology integrating partially rated ESS to extend the capabilities of providing additional services in the dc-ac power conversion. The topology and control scheme definition defined in Chapter 5 were performed collaboratively with Zoe Blatsi, Dr. Michael Merlin and Dr. Paul Judge. The power capability study, together with the losses analysis shown in Chapter 7 are solely work of the author under the supervision and advice of Dr. Michael Merlin. Finally, the experimental prototype used to test the proposal at laboratory scale described in Chapter 8 was developed jointly with Zoe Blatsi, with valuable advice from Dr. Michael Merlin, Dr. Paul Judge and Prof. Stephen Finney.

# 1.3.2. Thesis Objectives

The principal objective of this thesis is to design power converter topologies with the capability of integrating energy storage units into hybrid dc-ac systems. The proposed topologies consider the inclusion of energy storage in the design stage, aiming to minimise the required power processing stages and to improve overall operation.

The specific objectives are:

- To examine the existent single-stage three-port DC-DC-AC topologies in order to group them based on their operating principle to minimise power processing stages.

- To analyse the performance of the proposed single-stage three-port DC-DC-AC topology for low- and medium-power applications based on simulations and experimental results.

- To analyse the performance of the proposed MMC topology with integrated partially-rated energy storage for high-power applications.

- To design multi-variable modelling and control methods to regulate in an optimal manner the operation of the proposed topologies.

# 1.3.3. Hypotheses

The hypotheses formulation is in relation to the inclusion of ESS in the design of power converters. Thus, three main research hypotheses are defined:

- Multi-variable modelling and control algorithms exploit all the degrees of freedom of certain topologies, minimizing the power conversion stages of DC-AC systems with integrated energy storage.

- The proposed single-stage three-port DC-DC-AC converter with embedded energy storage manages the power flow between ports in a similar or better way than multi-stage solutions, in terms of efficiency, number of components and power density.

• The proposed design for an MMC topology with integrated energy storage extends the capabilities of the converter, keeping the ratings of the components in the original design.

# 1.3.4. Thesis Structure

The thesis is structured in two parts defined by the topologies developed to integrate ESS into power converters. The first part focuses on a proposed power converter for integrating ESS into low- and medium-power systems, while the second part is related to a developed MMC variant topology embedding ESS into HVDC substations. Thus, the first part is structured as follows:

Chapter 2 presents a comprehensive analysis of three-port single-stage DC-DC-AC solutions to contextualize the features of the proposed converter for low- and medium-power applications presented in the following chapters.

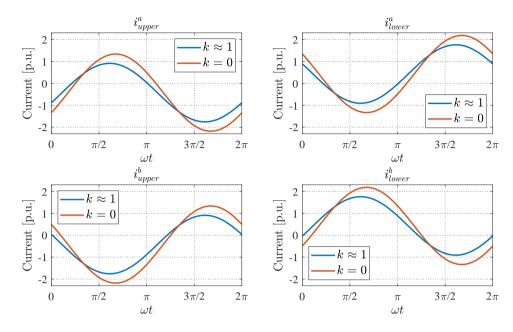

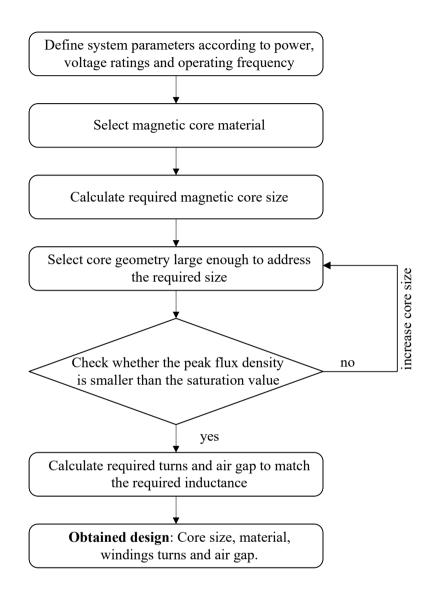

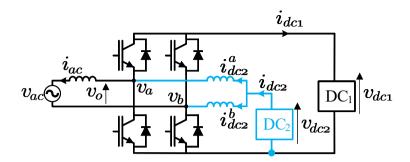

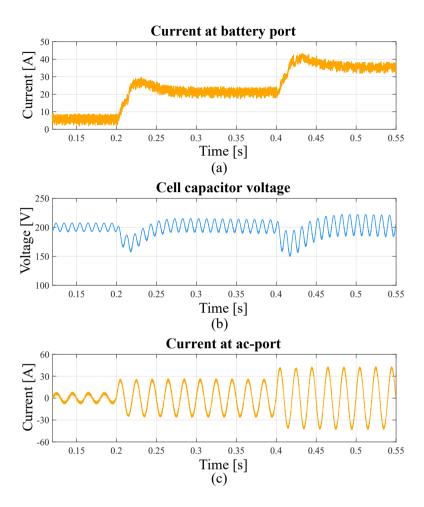

Chapter 3 introduces a proposed three-port dc-dc-ac converter with a single power processing stage to integrate ESS into DC-AC systems. The topology minimises the active components required to control the power flow between the three ports. A mathematical model is described to analyse the operation and control requirements of the proposal. Finally, the operation is validated with simulation and experimental results.