# ANALOG CIRCUITS FOR COMPUTING

by

Lauren Chun, Dillon Nguyen, Nicole Pickett

# Senior Project

#### ELECTRICAL ENGINEERING DEPARTMENT

California Polytechnic State University

San Luis Obispo

June 2023

© 2023 Lauren Chun, Dillon Nguyen, Nicole Pickett

# TABLE OF CONTENTS

| LIST OF TABLES AND FIGURES                                                    | ii |

|-------------------------------------------------------------------------------|----|

| ACKNOWLEDGEMENTS                                                              | v  |

| ABSTRACT                                                                      | 1  |

| I. INTRODUCTION                                                               | 2  |

| II. BACKGROUND                                                                | 3  |

| III. DESIGN REQUIREMENTS                                                      | 5  |

| Functional Decompositions                                                     | 5  |

| Customer Requirements                                                         | 6  |

| Engineering Specifications                                                    | 7  |

| IV. DESIGN                                                                    | 8  |

| Component Selection.                                                          | 8  |

| LTspice Circuit Schematics                                                    | 9  |

| Printed Circuit Board Designs                                                 | 12 |

| V. SIMULATION AND HARDWARE TESTS AND RESULTS                                  | 13 |

| LTspice Design, Testing, and Results                                          | 13 |

| Monte-Carlo Sensitivity Analysis on an Improved Differentiator Op-Amp Circuit |    |

| LTspice Design Simulations                                                    | 16 |

| Breadboard Testing and Results                                                | 27 |

| Printed Circuit Board Tests and Results                                       | 30 |

| Breadboard and PCB Testing Summary                                            | 34 |

| Execution Time Testing.                                                       | 35 |

| Calculation Accuracy                                                          | 39 |

| VI. CONCLUSION                                                                | 39 |

| VII. BIBLIOGRAPHY                                                             | 40 |

| IX. APPENDICES                                                                | 42 |

| A. Analysis of Senior Project Design                                          | 42 |

| B. Bill of Materials and Time Schedule Allocation                             | 50 |

| C. IC Location Diagram                                                        | 52 |

| D. Printed Circuit Board Artwork                                              | 52 |

| E. Program Listing - MATLAB® Simulation Code                                  | 54 |

| F. Hardware Configuration/Layout                                              | 63 |

# LIST OF TABLES AND FIGURES

# Tables

| Table 3-1. Analog Circuits for Computing Customer Requirements and Engineering Specifications      | 7        |

|----------------------------------------------------------------------------------------------------|----------|

| Table 3-2. Analog Circuits for Computing Engineering Specifications with Target, Tolerance, and Co | mpliance |

| Values                                                                                             |          |

| Table 5-1. Calculations for the Improved Differentiator Op-Amp Circuit Input and Feedback Resista  | nces13   |

| Table 5-2. Tabulated Breadboard Data for the Voltage Adder Circuit Test Cases                      | 26       |

| Table 5-3. Tabulated Breadboard Data for the Non-Inverting Voltage Multiplier Circuit Test Cases   | 28       |

| Table 5-4. Tabulated Breadboard Data for the Resistive Divider Circuit Test Cases                  | 29       |

| Table 5-5. Tabulated Breadboard Data for the Differentiator Circuit Test Cases                     | 29       |

| Table 5-6. Tabulated Breadboard Data for the Integrator Circuit Test Cases                         | 30       |

| Table 5-7. Tabulated PCB Data for the Voltage Adder Circuit Test Cases.                            | 31       |

| Table 5-8. Tabulated PCB Data for the Non-Inverting Voltage Multiplier Circuit Test Cases          | 32       |

| Table 5-9. Tabulated PCB Data for the Resistive Divider Circuit Test Cases                         | 33       |

| Table 5-10. Tabulated PCB Data for the Differentiator Circuit Test Cases                           | 33       |

| Table 5-11. Tabulated PCB Data for the Integrator Circuit Test Cases.                              | 34       |

| Table 5-12. MATLAB® Function Execution Time Results.                                               | 37       |

| Table A-1. Initial Cost Estimates for the Analog Circuits for Computing Project                    | 44       |

| Table B-1. Analog Circuits for Computing Project Bill of Materials                                 | 50       |

| Table B-2. Timeline of Tasks and Milestones for the Analog Circuits for Computing Project          | 51       |

| Figures                                                                                            |          |

| Figure 2-1. Conceptual Basic Arithmetic Circuits.                                                  | 3        |

| Figure 2-2. Conceptual Basic Calculus Circuits.                                                    | 3        |

| Figure 2-3. "The Analog Thing" Device by Anabrid.                                                  | 4        |

| Figure 3-1. Level 0 Functional Decomposition Block Diagram.                                        |          |

| Figure 3-2. Level 1 Functional Decomposition Block Diagram.                                        |          |

| Figure 3-3. Level 2 Functional Decomposition Block Diagram.                                        |          |

| Figure 4-1. LTspice-Designed Voltage Adder Circuit Schematic.                                      | 10       |

| Figure 4-2. LTspice-Designed Non-Inverting Voltage Multiplier Circuit Schematic                    | 10       |

| Figure 4-3. LTspice-Designed Resistive Divider Circuit Schematic                                   | 11       |

| Figure 4-4. LTspice-Designed Differentiator Circuit Schematic                                      | 11       |

| Figure 4-5. LTspice-Designed Integrator Circuit Schematic.                                              | 12     |

|---------------------------------------------------------------------------------------------------------|--------|

| Figure 4-6. PCB Layout Differentiator and 2nd-Order Differential Equation.                              | 12     |

| Figure 5-1. Block Diagram for Simulation and Hardware Testing.                                          | 13     |

| Figure 5-2. Differentiator Circuit with a Monte-Carlo Analysis Setup.                                   | 14     |

| Figure 5-3. Improved Differentiator Op-Amp Circuit Performance with Zero Tolerance at $T = 25$ °C       | 14     |

| Figure 5-4. Gain Response of the Monte-Carlo Analysis of the Differentiator Circuit                     | 15     |

| Figure 5-5. Histogram of the Gain for the Improved Differentiator Op-Amp Circuit with Respect to Varyin | ıg     |

| Temperatures from -25°C to 85°C in Intervals of 10°C.                                                   | 15     |

| Figure 5-6. Histogram of the Frequency at 0dB for the Improved Differentiator Op-Amp Circuit with Resp  | ect to |

| Varying Temperatures from -25°C to 85°C in Intervals of 10°C.                                           | 16     |

| Figure 5-7. Histogram of the Frequency at Maximum Gain for the Improved Differentiator Op-Amp Circu     | it     |

| with Respect to Varying Temperatures from -25°C to 85°C in Intervals of 10°C                            | 16     |

| Figure 5-8. LTspice Voltage Adder Simulation (Addition Test)                                            | 17     |

| Figure 5-9. LTspice Voltage Adder Simulation (Subtraction Test)                                         | 18     |

| Figure 5-10. LTspice Non-Inverting Multiplier Simulation (Gain of 2.2).                                 | 18     |

| Figure 5-11. LTspice Non-Inverting Multiplier Simulation (Gain of 6.45).                                | 19     |

| Figure 5-12. LTspice Non-Inverting Multiplier Simulation (Gain of 9.3)                                  | 19     |

| Figure 5-13. LTspice Resistive Divider Simulation for DC Waveforms.                                     | 20     |

| Figure 5-14. LTspice Resistive Divider Simulation for Sinusoidal Waveforms.                             | 20     |

| Figure 5-15. LTspice Resistive Divider Simulation for Square Waveforms.                                 | 21     |

| Figure 5-16. LTspice Resistive Divider Simulation for Triangle Waveforms.                               | 21     |

| Figure 5-17. LTspice Differentiator Simulation for Sinusoidal Waveforms.                                | 22     |

| Figure 5-18. LTspice Differentiator Simulation for Square Waveforms.                                    | 23     |

| Figure 5-19. LTspice Differentiator Simulation for Triangle Waveforms.                                  | 23     |

| Figure 5-20. LTspice Integrator Simulation for Sinusoidal Waveforms.                                    | 24     |

| Figure 5-21. LTspice Integrator Simulation for Square Waveforms.                                        | 25     |

| Figure 5-22. LTspice Integrator Simulation for Triangle Waveforms.                                      | 25     |

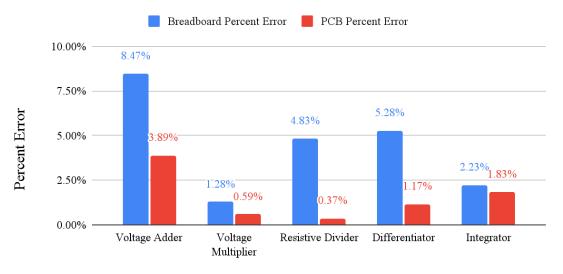

| Figure 5-23. Graphical Representation of the Breadboard Data Accuracy versus the PCB Data Accuracy      | 35     |

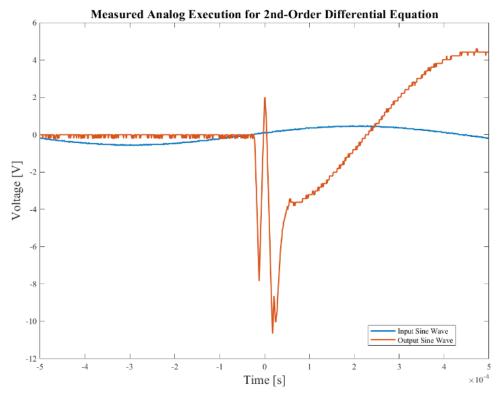

| Figure 5-24. Oscilloscope Trace of the Execution Time for Test Equation, $y'' - 10y' - y$               | 36     |

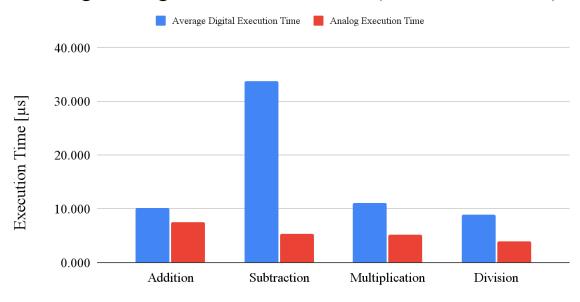

| Figure 5-25. Graphical Representation of the MATLAB® Execution Time and PCB Execution Time (Basi        | c      |

| Arithmetic Circuits)                                                                                    | 38     |

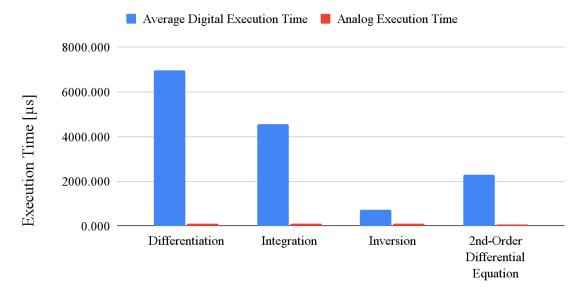

| Figure 5-26. Graphical Representation of the MATLAB® Execution Time and PCB Execution Time (Basi        | c      |

| Calculus Circuits)                                                                                      | 38     |

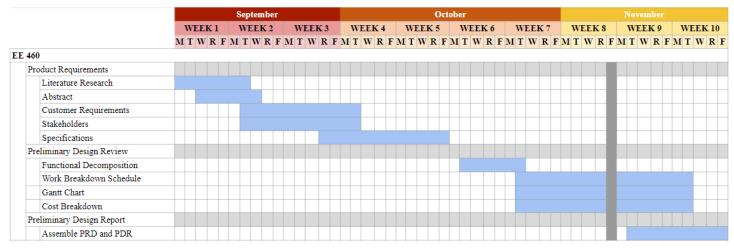

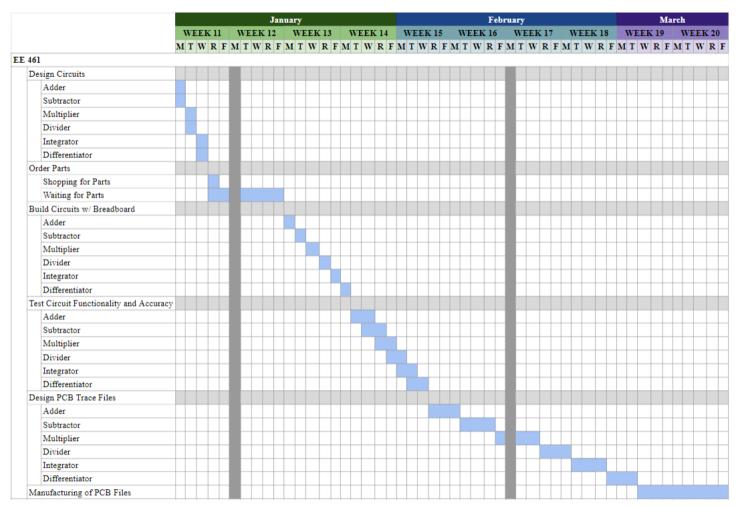

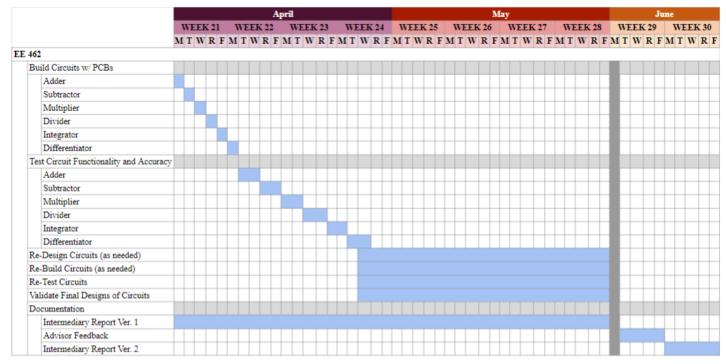

| Figure A-1. Gantt Chart for Analog Circuits for Computing Project (Project Planning Ph | nase)45              |

|----------------------------------------------------------------------------------------|----------------------|

| Figure A-2. Gantt Chart for the Analog Circuits for Computing Project (Conceptual Des  | ign and Simulation   |

| Phase)                                                                                 | 45                   |

| Figure A-3. Gantt Chart for the Analog Circuits for Computing Project (Manufacturing   | and Testing Phase)46 |

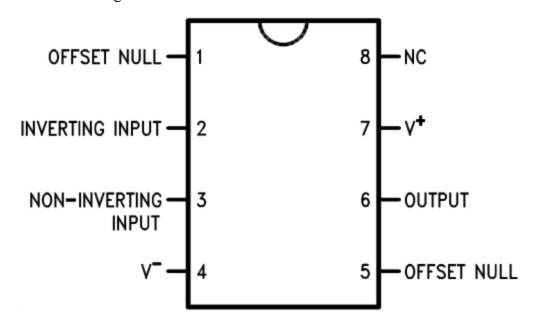

| Figure C-1. LM741 Pinout Diagram.                                                      | 52                   |

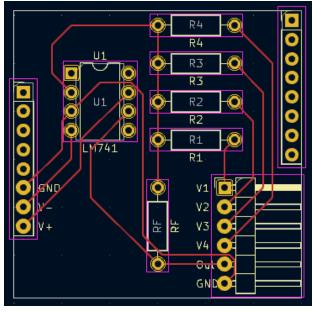

| Figure D-1. Voltage Adder PCB                                                          | 52                   |

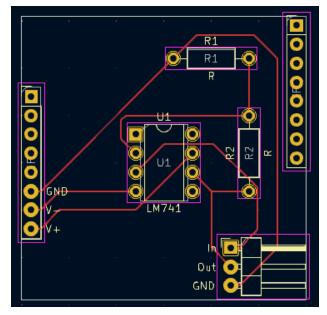

| Figure D-2. Non-Inverting Voltage Multiplier PCB.                                      | 52                   |

| Figure D-3. Inverting Voltage Multiplier PCB.                                          | 53                   |

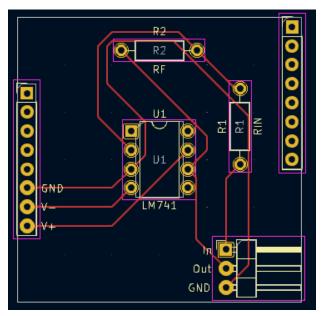

| Figure D-4. Resistive Divider PCB.                                                     | 53                   |

| Figure D-5. Differentiator PCB.                                                        | 53                   |

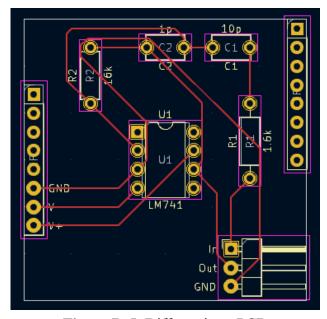

| Figure D-6. Integrator PCB.                                                            | 53                   |

| Figure F-1. Hardware Layout for the Voltage Adder (Designed for a Gain of 1)           | 63                   |

| Figure F-2. Hardware Layout for the Non-Inverting Multiplier (Designed for a Gain of 2 | 2.2)63               |

| Figure F-3. Hardware Layout for the Resistive Divider                                  | 64                   |

| Figure F-4. Hardware Layout for the Differentiator.                                    | 64                   |

| Figure F-5. Hardware Layout for the Integrator.                                        | 65                   |

| Figure F-6. Hardware Layout for the Tested Second-Order Differential Equation          | 65                   |

#### **ACKNOWLEDGEMENTS**

We would like to thank our advisor, Dr. Jason Poon, as well as Cal Poly EE Department faculty members Dr. Vladimir Prodanov, Dr. Dale Dolan, and Dr. Taufik for providing guidance and direction during the project development process. We would also like to thank the Cal Poly EE Department for providing the resources to perform extensive research and testing for the project.

# **ABSTRACT**

This project entails designing, simulating, and verifying analog circuits that can perform essential computing functions for power systems applications. The project aims to remedy critical challenges associated with handling calculations digitally, namely, time and power. This project's scope includes creating a library of circuits in SPICE that can be used to model and simulate complex mathematical equations. From these SPICE models, the circuit can be constructed physically, where the solution can be generated in less time using less power than doing the computation digitally. The performance and efficiency of analog computing will be measured and compared to conventional digital methods.

#### I. INTRODUCTION

The basis of this project started in the 1960s as analog computers were first used to calculate complex algorithms. Over time, digital computation became more favorable due to its accuracy with less noise, distortion, and interference among its results [1]. Analog circuitry, however, is re-emerging as a solution for complex calculations. It can present more refined results while consuming less power and bandwidth, suggesting that analog computing can provide the same results as digital systems but more efficiently [2, 3].

With analog computing, physical circuits can be constructed to perform various mathematical operations; signals are sent through the circuits to generate results while measuring the speed and power consumption [5]. The goal is to create a collection of circuits that handle simple arithmetic, like addition, to complex math, like nonlinear differential equations [1]. The resulting analog computation can then be transmitted to software where it can be analyzed and applied to applications, particularly power grid emulation and testing.

#### II. BACKGROUND

Analog computation is defined as computations in which the result is derived via measurement from a continuous quality, such as voltage or current [1]. From this definition, analog computation is favored by continuous-time systems, which has been seen throughout history. Analog computation in the 1940s generated many special-purpose machines that handled continuous signals, such as harmonic and power-network analyzers [1]. The one thing in common with all of these devices is this: they all handle data in real time rather than using step functions to approximate the continuous data [1]. This makes analog computation a preferred choice for specific applications, such as power grid simulations or signal processing.

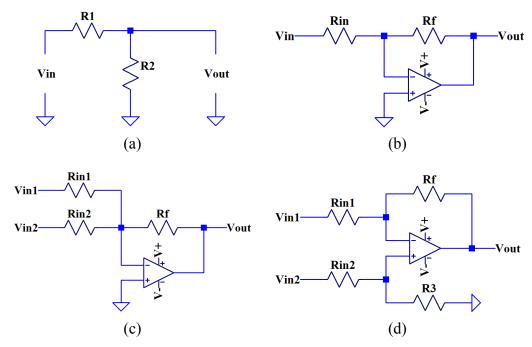

Analog computation ranges from basic to complex mathematical equations, all done with passive and active circuit configurations [1]. The basic arithmetic handled, such as those seen in Figure 2-1, uses passive circuits, such as a voltage divider, while active circuits handle addition, subtraction, and multiplication.

**Figure 2-1.** Conceptual Basic Arithmetic Circuits (a) Resistive Divider (b) Inverting Multiplier (c) Voltage Adder (d) Voltage Subtractor (Differential Amplifier)

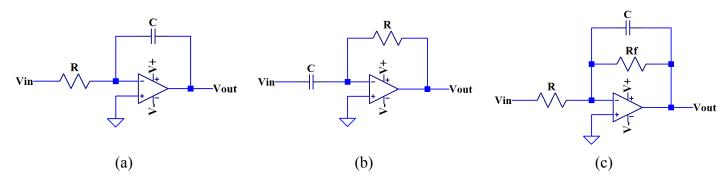

In combination with calculus, these circuits can be used to represent complex systems such as linear differential equations such as the Mathieu, Bessel, and Legendre functions [2]. Figure 2-2 shows an integrator and differentiator. What is important to note about the differentiator is that the capacitor input configuration permits too much noise, the second configuration mitigates this issue.

**Figure 2-2.** Conceptual Basic Calculus Circuits (a) Integrator (b) Differentiator (c) Noise-Reducing Differentiator

These circuits allow for complex analysis of larger-scale systems and provide high-speed solutions for systems such as power grids [3]. Traditional power grid simulations rely on numerical algorithms, which need to be faster to handle a real-time power system. Analog computation allows simulators like these to surpass the limits of numerical (discrete) algorithms as they use the measurement of power to extract data such as damping power and phase angle [3]. Circuits such as the integrator and differentiator are represented via a control system and then constructed accordingly to analyze the power grid. This results in simplification with simulation models.

Analog computation is also being furthered as it is used for power grid emulation. The difference is that analog microelectronics are used to handle these emulators [4]. In this case, it is being explored to create better emulations that will handle DC and AC emulations better. By using power as the continuous signal as the output, these emulators utilize CMOS microelectronic ASIC boards to simulate not only the power grid but each load attached to the grid as well [4]. This yields a much more comprehensive simulation, benefiting those who are optimizing and/or repairing the power grid.

The product titled "The Analog Thing" by the company Anabrid is another example of analog computation that is further expanded upon, shown in Figure 2-3. It is a low-cost, open-source analog computer with multiple inputs and connection ports to calculate mathematical functions [5]. This multipurpose analog computer can be used for applications from education to providing control to circuitry [5]. The computational analog circuits utilize the basic and calculus circuitry presented above, allowing this device to be multifaceted and provide solutions to specific problems.

Figure 2-3. "The Analog Thing" Device by Anabrid [5]

#### III. DESIGN REQUIREMENTS

#### **Functional Decompositions**

The level 0 functional decomposition displays the overall inputs and outputs of a system. For this project, the main input for the analog circuits system is the desired algorithm to be solved, supplied by the customer. The main output of the system is the PCB file representation of the desired algorithm so that the customer can manufacture their PCB-represented algorithm. Figure 3-1 illustrates the level 0 functional decomposition for this project.

# Data (Desired Algorithm) Data (PCB Files)

Figure 3-1. Level 0 Functional Decomposition Block Diagram

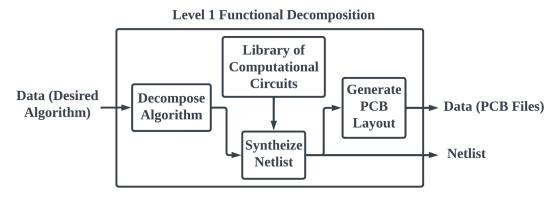

The level 1 functional decomposition elaborates on the level 0 functional decomposition, showing the internal modules within the main system as well as secondary inputs and outputs. For the analog circuits system, the internal modules include the decomposer, library of computational circuits, netlist synthesizer, and PCB layout generator. The decomposer, netlist synthesizer, and PCB layout generator modules must be done manually by the customer. The decomposer module entails the customer deconstructing their algorithm into smaller arithmetic and calculus functions that can be used to determine which circuits from the provided library are needed to solve the algorithm. The netlist synthesizer allows for open-source modeling and simulation of the customer's algorithm, providing a SPICE netlist for their algorithm. The PCB layout generator module entails customers transferring their modeled algorithm to a PCB layout format for future printing and solving via hardware testing and measurement. The library of computational circuits will be provided for the customer, which they can pull from to model their desired algorithm. Figure 3-2 provides a visual of this project's level 1 functional decomposition.

Figure 3-2. Level 1 Functional Decomposition Block Diagram

The level 2 functional decomposition elaborates on specific modules within the overall system specified in the level 1 functional decomposition. The decomposer, netlist synthesizer, and PCB layout generator are performed manually by the customer. Thus, the library of computational circuits is the only module that requires elaboration. The library of computational circuits comprises the following circuits: voltage adder, non-inverting multiplier, resistive divider, differentiator, integrator, and inverter. The library circuits selected by the customer will then be outputted as SPICE netlists to incorporate into their full algorithm model. The visual for the level 2 functional decomposition is shown in Figure 3-3.

# Library Adder Subtractor Multiplier Divider Integrator Differentiator Inverter Netlist Synthesizer

#### **Level 2 Functional Decomposition**

Figure 3-3. Level 2 Functional Decomposition Block Diagram

# **Customer Requirements**

The customer requirements for this project are selected to allow for the most inclusivity possible while ensuring the computational circuits system is highly and properly functional as well as intuitive. The following are the selected customer requirements, detailing the constraints for the project tailored to the customer:

- a) Open-source simulation and hardware files

- b) Functions must include a variety of mathematical operations (e.g., arithmetic, calculus, differential equations)

- c) Library must be intuitive to use

- d) Circuits must provide results in a short amount of time for power grids

- e) Mathematical computations from circuits must be accurate

Table 3-1 elaborates on the chosen customer requirements as well as the engineering specification derived for each requirement.

Table 3-1. Analog Circuits for Computing Customer Requirements and Engineering Specifications.

| Customer<br>Requirements | Engineering Specification                                                  | Justification                                                                                                                                                                      |

|--------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| a                        | Zero closed-source applications                                            | An open-source library will ensure it is accessible to anyone without needing to pay for access and use [6].                                                                       |

| b                        | A minimum of 5 mathematical operations completed                           | The core function of the computational analog circuits. Arithmetic and basic calculus will serve as the foundation for nonlinear computations and systems-of-equation solving. [2] |

| С                        | At least 2 hours to become familiar with the interface and resources       | An intuitive interface will allow easy use of the analog circuits for the user to carry out their desired task. [7]                                                                |

| d                        | Computations will take equivocal or less time to digital systems (in msec) | A shortened time for computations will allow for improvement in power grid development, simulation, and maintenance for the customer. [4]                                          |

| e                        | Computations are accurate with a maximum of 10% error                      | A maximum of 10% error will ensure the validity of the computations and that it will function correctly in any application. [1]                                                    |

# **Engineering Specifications**

Derived from the selected customer requirements, the engineering specifications detail the numerical target and tolerance values as well as risk and compliance assigned to each requirement. Each of the specifications is designed with the customer's needs and wants prioritized. Table 3-2 elaborates on these engineering specifications below.

*Table 3-2.* Analog Circuits for Computing Engineering Specifications with Target, Tolerance, and Compliance Values

|   | Parameter                         | Target                | Tolerance | Risk (H,M,L) | Compliance (A,T,S,I) |

|---|-----------------------------------|-----------------------|-----------|--------------|----------------------|

| 1 | Accuracy                          | 10 percent error      | Max       | M            | A, T                 |

| 2 | Number of mathematical operations | 5 operations          | Min       | M            | Ι                    |

| 3 | Closed-Source                     | 0                     | Max       | L            | Т                    |

| 4 | Intuitive                         | 2 hrs                 | Min       | M            | I                    |

| 5 | <b>Short Computation Time</b>     | <= to digital in msec | Max       | Н            | A, T, S              |

#### IV. DESIGN

# **Component Selection**

Individual passive component values differ between the various circuits, but the LM741 operational amplifier is the fundamental component for most of the mathematical operations. As the circuits are computational circuits, most require the use of some kind of active component. The LM741 was chosen due to its fairly large range of operational voltages (±18V), commonality in the market, and low-cost use.

The circuit that is the exception to using the LM741 op-amp is the resistive divider circuit, which consists of only one potentiometer. The potentiometer selected for this circuit as well as other circuits that required variable resistance (e.g. integrator and non-inverting multiplier), is the  $251B12T104A2NB\ 100k\Omega$ -knob potentiometer. This selection is because  $100k\Omega$  provides the best ohmic range for the specifications of each circuit while allowing easy adjustment, unlike other potentiometers that use flat turning mechanisms.

All other passive component values, such as single resistors and capacitors, depend on each circuit and the tolerances specified. The process for selecting each of these components is discussed in the following sections.

#### **Voltage Adder Component Selection**

The voltage adder circuit uses an arbitrary number of components that depends on the desired number of summing input nodes. Each voltage adder has at least three resistors, two for the two summing input nodes and one for the feedback resistor. For testing purposes, a minimum of three resistors are used with the system designed for a gain of 1. The following equation describes the gain for the voltage adder used to determine the summing input node and feedback resistor values:

$$\frac{-V_{out}}{(V_{in.1} + V_{in.2} + V_{in.3} + \dots + V_{in.n})} = \frac{R_F}{R_{in}}$$

To ensure a gain of 1, the summing input and feedback resistors are all  $10 \text{ k}\Omega$ . The input signals are arbitrary and do not affect the operation of the circuit as long as their sum does not exceed the  $\pm 18\text{V}$  rails of the LM741 operational amplifier.

# **Non-Inverting Multiplier Component Selection**

The non-inverting multiplier circuit uses two resistors to form an arbitrary multiplication constant represented by the gain of the LM741 op-amp. The gain of the amplifier is determined using the following equation:

$$\frac{V_{out}}{V_{in}} = 1 + \frac{R_2}{R_1}$$

The gain is dependent on the desired multiplication constant. For testing purposes, an arbitrary gain of 10 was selected; thus, the resistor values chosen are  $100 \text{ k}\Omega$  and  $10 \text{ k}\Omega$ .

# **Resistive Divider Component Selection**

The components of the resistive divider circuit are two resistors. The two resistors are arbitrary and are dictated based on the following equation:

$$V_{out} = V_{in} \left( \frac{R_2}{R_1 + R_2} \right)$$

Depending on the desired divisor for the division operation, the resistors will be changed accordingly. For purposes of simulation, resistor values of 1 k $\Omega$  for both resistors were chosen to perform division with a divisor of 2.

#### **Differentiator Component Selection**

The differentiator circuit only uses a combination of two capacitors and two resistors. The component values are chosen based on the time constant equation shown below that dictates the charging characteristics.

$$\tau = RC$$

To determine the output voltage of the circuit, the following equation is used:

$$V_{out} = -R_F C \left( \frac{dV_{in}}{dt} \right)$$

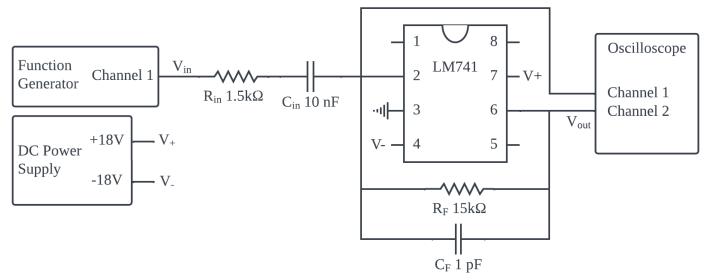

$V_{in}$  is arbitrary and dependent on the desired input signal. The component values and time constant vary depending on the type of input signal (i.e., sine wave, square wave, triangle wave, etc.) as well. For testing purposes, resistor values of 1.5 k $\Omega$  and 15 k $\Omega$  are used, and capacitor values of 1 pF and 10nF. The traditional configuration only uses a set of one resistor and capacitor (as represented in the equation). To mitigate gain increase and account for attenuation at higher frequencies, input resistor  $R_{in}$  and feedback capacitor  $C_F$  are added to the design.

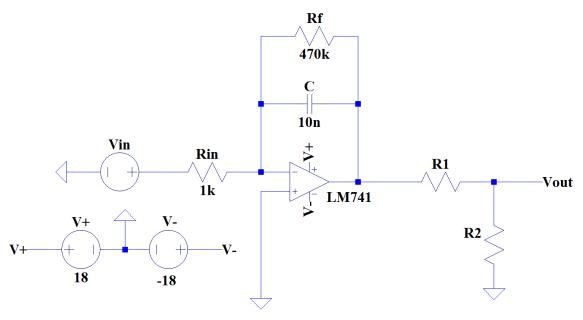

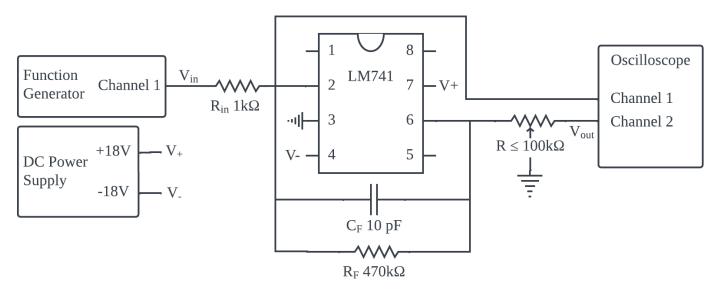

#### **Integrator Component Selection**

The integrator circuit design uses four resistors and one capacitor. The input resistor, feedback resistor, and feedback capacitor are determined by the equation:

$$V_{out} = -\frac{1}{R_{in}C} \int_{0}^{t} V_{in} dt$$

The additional two resistors are used as a resistive divider at the end of the integrator circuit as maintaining a gain of 1 became an issue during the design phase. The resistive divider allows for scaling of the output to obtain the true, desired integrated output. After trial and error, an input resistor value of  $1 \text{ k}\Omega$ , feedback resistor value of  $470 \text{ k}\Omega$ , and feedback capacitance value of 10 nF were chosen.

# LTspice Circuit Schematics

#### **Voltage Adder Design**

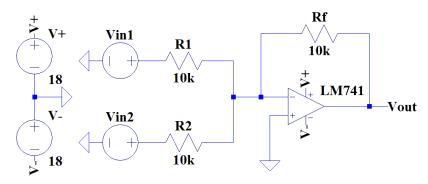

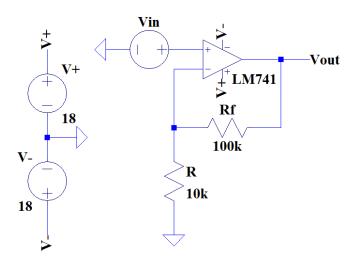

The voltage adder circuit is designed based on the traditional voltage adder circuit configuration using a standard LM741 op-amp. The voltage adder circuit allows for as many summing nodes as desired. For the project's purposes, the number of summing nodes will not exceed four nodes. This constraint is not based on the design's operation, but rather it is not cost-effective and becomes redundant to add more than four summing nodes. The traditional configuration requires the input to be fed into the inverting terminal of the op-amp, resulting in inverted results. Therefore, when the output is probed and results are recorded for this circuit, the output will always be the inverted value of the real answer. This design can also be configured for subtraction and negative numbers by applying negative voltages to one or more of the summing inputs. The supply voltages are set to ±18V to minimize clipping at the output; these supply voltage levels are maintained for all designed

active circuits. Figure 4-1 shows the finalized voltage adder circuit as simulated in LTspice, configured for only two summing nodes.

Figure 4-1. LTspice-Designed Voltage Adder Circuit Schematic

#### Non-Inverting Voltage Multiplier Design

The non-inverting multiplier circuit is designed based on the traditional non-inverting multiplier circuit configuration using a standard LM741 op-amp. The non-inverting multiplier circuit allows for multiplication between a constant (set by the gain of the op-amp) and an input signal. Multiplication can be executed using the inverting multiplier configuration and non-inverting multiplier configuration. For the project's purposes, the non-inverting configuration provided the desired results without the need to invert the measured output to obtain the true result. This design can also be configured for negative multiplication by applying negative voltages to one or more of the summing inputs. Figure 4-2 shows the finalized non-inverting multiplier circuit as simulated in LTspice, configured for a multiplication constant (gain) of 10.

Figure 4-2. LTspice-Designed Voltage Multiplier Circuit Schematic

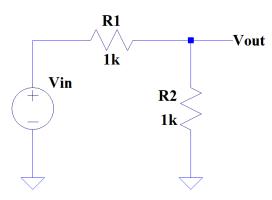

#### **Resistive Divider Design**

The resistive divider circuit is designed based on the resistive divider circuit configuration using standard resistors. The resistive divider circuit allows for division between a constant set by the two resistors and an input signal. For future purposes, a single  $100 \text{ k}\Omega$  potentiometer can be used in place for the two resistors set up. Figure 4-3 shows the finalized resistive divider circuit as simulated in LTspice, configured for a divisor of 2.

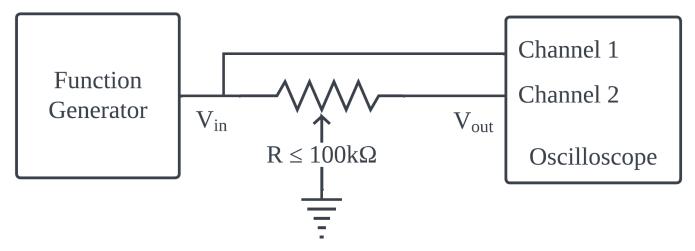

Figure 4-3. LTspice-Designed Resistive Divider Circuit Schematic

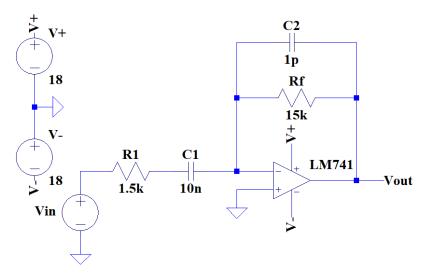

#### **Differentiator Design**

The differentiator circuit is designed based on the traditional differentiator circuit configuration using a standard LM741 op-amp with an added input resistor and feedback capacitor. The addition of the extra resistor and capacitor is to mitigate gain increase and account for attenuation at higher frequencies. The traditional configuration requires the input to be fed into the inverting terminal of the op-amp, resulting in inverted results. Therefore, when the output is probed, and results are recorded for this circuit, the output will always be the inverted value of the real answer. This design can also be configured for negative signals by applying negative voltages to the input. Figure 4-4 shows the finalized differentiator circuit as simulated in LTspice, configured for only sinusoids.

Figure 4-4. LTspice-Designed Differentiator Circuit Schematic

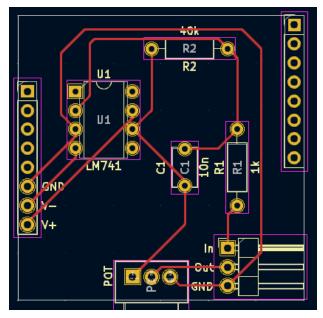

#### **Integrator Design**

The integrator circuit is designed based on the traditional integrator circuit configuration using a standard LM741 op-amp. An additional resistive divider combination is added at the end of the integrator system to maintain a gain of 1. The traditional configuration requires the input to be fed into the inverting terminal of the op-amp, resulting in inverted results. Therefore, when the output is probed, and results are recorded for this circuit, the output will always be the inverted value of the real answer. This design can also be configured for negative signals by applying negative voltages to one or more of the summing inputs. Figure 4-5 shows the finalized integrator circuit as simulated in LTspice.

Figure 4-5. LTspice-Designed Integrator Circuit Schematic

#### **Printed Circuit Board Designs**

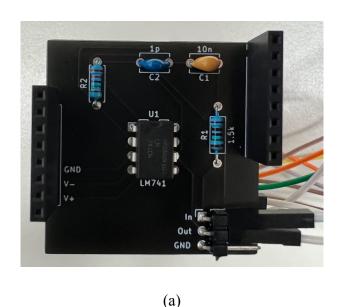

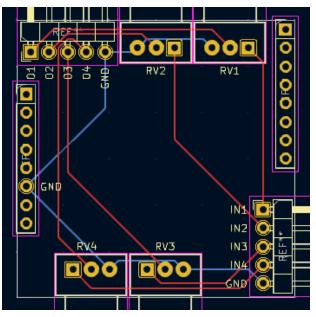

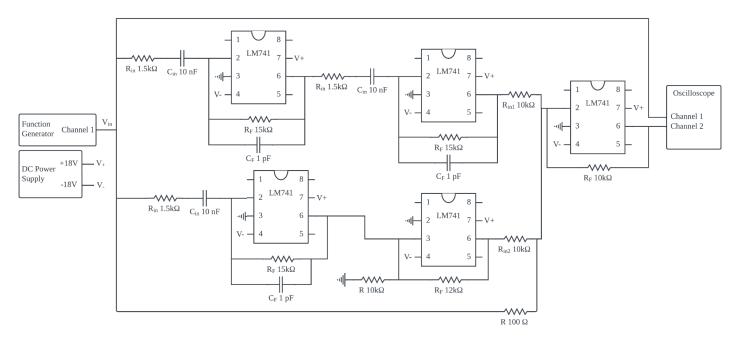

The printed circuit boards (PCBs) for the individual computational circuits were designed in the PCB software KiCad. The PCBs are designed to represent specific mathematical operations such as addition, multiplication, division, differentiation, and integration. The dimensions of each PCB are 19.05 mm x 19.05 mm, with the trace width chosen to be 0.25mm due to each PCB only needing low power and low frequency. In addition, header pins were placed on two sides of the board in order to make the PCBs stackable. This allows all of the positive and negative power supplies, along with the grounds, to be easily connected without additional wiring. With only one math operation on each PCB, it allows the customer to use the same set of PCBs to model various equations instead of needing to order a new PCB to represent a singular equation. Figures 4-6 a and b show an example of the manufactured differentiation PCB and how each of the individual PCBs cascade and stack together to form a more complex algorithm.

**Figure 4-6.** (a) Manufactured Differentiator PCB (b) Three Differentiators, One Inverting Multiplier (Gain of 10), and One Voltage Adder Manufactured and Cascaded to form a 2nd-Order Differential Equation

#### V. SIMULATION AND HARDWARE TESTS AND RESULTS

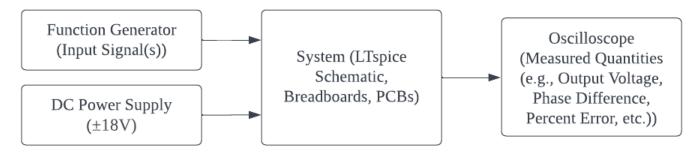

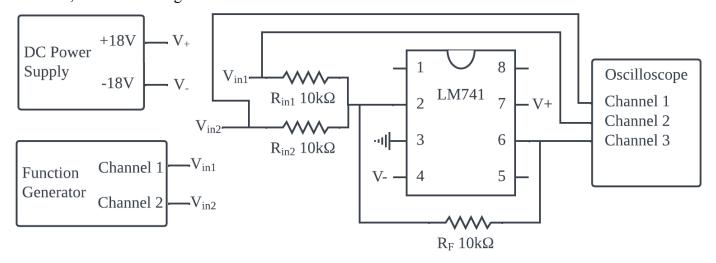

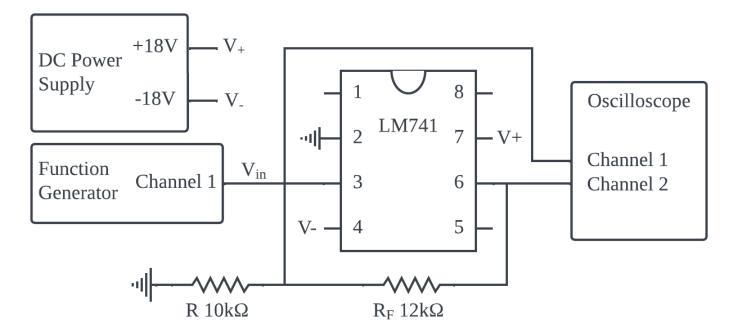

The project required both simulation and hardware testing as each circuit was designed via simulation first and then tested on breadboards. After confirming that each circuit fully operates, given the specified constraints and tolerances, the PCBs were designed and tested in the same manner. The testing setup used the same equipment in each setting: The system is powered by a function generator and DC power supply, where the outputs are observed using an oscilloscope. Figure 5-1 shows the block diagram that visualizes this process for all simulation and hardware testing.

Figure 5-1. Block Diagram for Simulation and Hardware Testing

# LTspice Design, Testing, and Results

#### Monte-Carlo Sensitivity Analysis on an Improved Differentiator Op-Amp Circuit

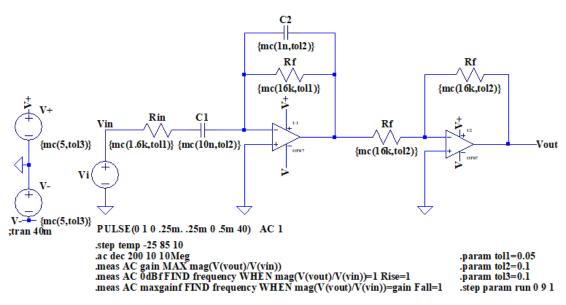

For LTSpice design and testing, each circuit was designed in LTSpice and then simulated. In addition, a Monte-Carlo analysis was performed to observe the effects of 10% on the entire system. Figure 5-2 shows a differentiator with an additional capacitor [1] to reduce noise at the sacrifice of bandwidth. This circuit is specifically designed for a bandwidth of 9kHz (from 1kHz and 10kHz). The following design equations are used where  $C_{in}$  was chosen as 10nF, and Vin is a 2kHz ramp function with an amplitude of 1V:

$$V_{out} = -R_E C_{in} \frac{dVin}{dt}$$

(Equation 1: Differentiator Gain)

Table 5-1: Calculations for the Improved Differentiator Op-Amp Circuit Input and Feedback Resistances

| Feedback Resistance Calculation                                                                                                                     | Input Resistance Calculation                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $f_L = \frac{1}{2\pi R_F C_{in}}$ (Equation 2: Lower Cutoff Frequency)                                                                              | $f_U = \frac{1}{2\pi R_{in}C_{in}}$ (Equation 3: Upper Cutoff Frequency)                                                                                         |

| $R_F = \frac{1}{2\pi f_L C_1} = \frac{1}{2\pi^* 1kHz^* 10nF} = 15.9k\Omega$ $R_F = 15.9k\Omega \approx 16k\Omega \text{ (Standard Resistor Value)}$ | $R_{in} = \frac{1}{2\pi f_{v}C_{1}} = \frac{1}{2\pi^{*}10kHz^{*}10nF} = 1.59k\Omega$ $R_{in} = 1.59k\Omega \approx 1.6k\Omega \text{ (Standard Resistor Value)}$ |

Assuming

$$R_{in}C_{in} = R_FC_F$$

, then  $C_F$  can be solved

$$C_F = \frac{R_{in} C_{in}}{R_F} = \frac{1.6k*10nF}{16k} = 1nF$$

Due to the negative sign in Equation 1, an inverting amplifier with a gain of one has been cascaded to invert the output again to yield the positive derivative of the signal.

Figure 5-2. Differentiator Circuit with a Monte-Carlo Analysis Setup [8]

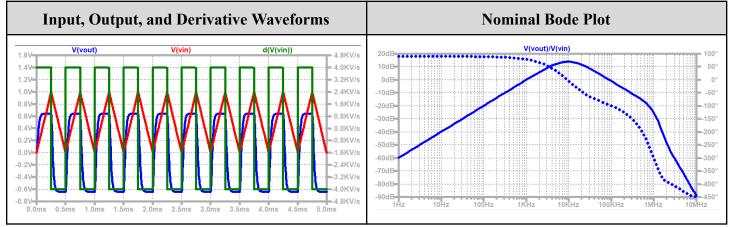

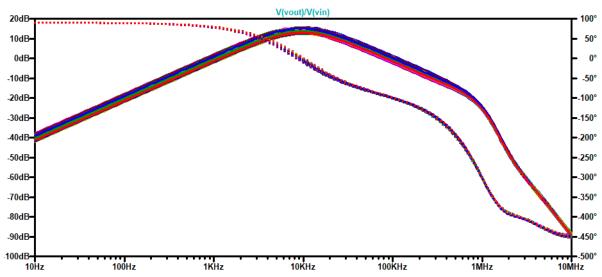

**Figure 5-3**. Improved Differentiator Op-Amp Circuit Performance with Zero Tolerance at  $T = 25^{\circ}C$

The plot above shows the input and output waveform of the differentiator. The input is a 1V 2kHz ramp function. Using cursor measurements, the output waveform amplitude is 640mV on the positive cycle. Equation 1 is used to verify the output waveform and functionality of the circuit. The derivative of the original waveform is measured to be 4kV/s (dark green).

$$V_{out} = -1 *- R_F C_{in} \frac{dVin}{dt} \rightarrow 640mV = 16k\Omega * 10nF * \frac{dVin}{dt}$$

$$640mV = 1.6 * 10^{-4} * \frac{dVin}{dt}$$

$$\frac{dVin}{dt} = \frac{4kV}{s}$$

This equals the actual derivative of the input waveform, verifying the functionality of the circuit. This shows that the parameters of all passive components will be tested from a -10% to +10% tolerance. The simulation is run in AC mode to observe the effects of the gain response of the system. As shown, the effects of the tolerance correlate to the accuracy of the system as it shows a maximum of 10% at the output. Since each component tolerance varies between -10% to +10%, it is important to observe this behavior in order to characterize the impact it will have on the output.

Figure 5-4 exhibits the improved differentiator op-amp circuit's maximum magnitude response for temperatures from -25°C to 85°C. With this variation in temperature, the maximum gain has a range of

approximately 12.27 dB to 15.74 dB. The nominal operating temperature range of this circuit is -25°C to 125°C, which is proven as the maximum gain (peak magnitude response) of this circuit at approximately in the middle of this temperature range.

Figure 5-4. Gain Response of the Monte-Carlo Analysis of the Differentiator Circuit.

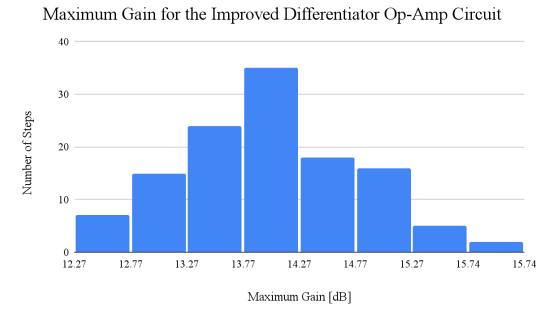

Figure 5-5 reflects the distribution for the improved differentiator op-amp circuit's maximum gain with respect to temperatures from -25°C to 85°C. The largest bin in the histogram is a maximum gain between 13.77dB and 14.27dB with a count of 35 simulation steps from a total of 120 simulation steps. This indicates that the most common maximum gain from the circuit is within this dB range under temperature changes.

**Figure 5-5.** Histogram of the Gain for the Improved Differentiator Op-Amp Circuit with Respect to Varying Temperatures from -25°C to 85°C in Intervals of 10°C

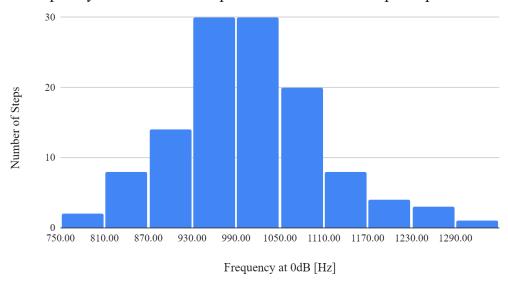

Figure 5-6 reflects the distribution for the improved differentiator op-amp circuit's frequency at 0 dB gain with respect to temperatures from -25°C to 85°C. The largest bins in the histogram are frequency ranges 930 Hz to 990 Hz and 990 Hz to 1050 Hz with counts of 30 simulation steps each from a total of 120 simulation steps. This indicates that the most common frequency values from the circuit are within these frequency ranges under temperature changes.

#### Frequency at 0dB for the Improved Differentiator Op-Amp Circuit

**Figure 5-6.** Histogram of the Frequency at 0dB for the Improved Differentiator Op-Amp Circuit with Respect to Varying Temperatures from -25°C to 85°C in Intervals of 10°C

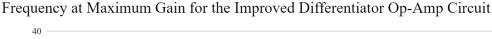

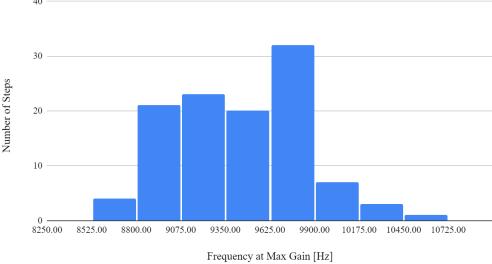

Figure 5-7 reflects the distribution for the improved differentiator op-amp circuit's frequency at 0dB gain with respect to temperatures from -25°C to 85°C. The largest bins in the histogram are frequency ranges 9.625kHz to 9.9kHz with a count of 32 simulation steps from a total of 120 simulation steps. This indicates that the most common frequency values from the circuit are within this Hz range under temperature changes.

**Figure 5-7.** Histogram of the Frequency at Maximum Gain for the Improved Differentiator Op-Amp Circuit with Respect to Varying Temperatures from -25°C to 85°C in Intervals of 10°C

# LTspice Design Simulations

Each of the designed computational circuits is tested with at least one type of input waveform (DC, sine, square, and/or triangle) with varying amplitudes, frequencies, and phase shifts. This comprehensive simulation testing is to ensure the designs' full functionality for a wide range of inputs as well as cascading compatibility with

other computational circuits. Figure 5-1 reflects the testing setup for each circuit, and the following steps describe the procedure for simulation testing:

- 1. Connect +18V, Ground, and -18V to each respective power rail input.

- 2. Configure a waveform generator (voltage source set to DC, PULSE, or SINE) to the desired input waveform.

- 3. Configure the appropriate simulation and time-axis settings, and run the simulation.

- 4. Probe the input and output waveforms and record measurements.

#### Voltage Adder Simulation

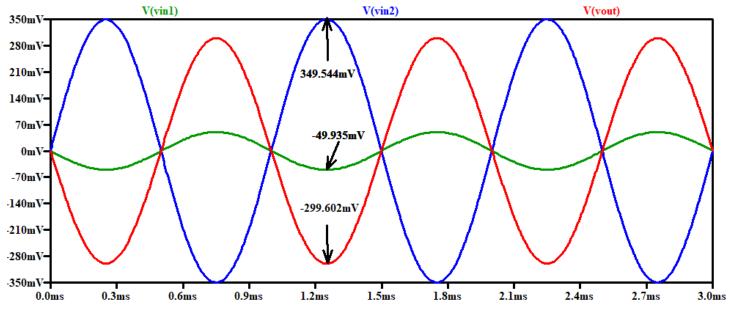

The voltage adder is capable of performing addition and subtraction by simply changing the phase delay of one or more of the inputs. The voltage adder circuit is also capable of summing multiple inputs at the same time, but for simplicity in testing and to prove design functionality, two inputs are added instead. Figure 5-8 demonstrates the addition function of the voltage adder design adding input waves  $V_{in,l} = -0.05\sin(2\pi 1000t)$  (green waveform) and  $V_{in,2} = 0.35\sin(2\pi 1000t)$  (blue waveform). The resulting red waveform,  $V_{out} = 0.3\sin(2\pi 1000t)$  is shifted  $180^{\circ}$  due to the adder's inverting nature, thus the final output is represented by  $V_{out} = -0.3\sin(2\pi 1000t + 180^{\circ})$ .

Figure 5-8. LTspice Voltage Adder Simulation (Addition Test)

The voltage adder's subtracting capability is demonstrated in Figure 5-9. For the following test performed, the second adder input is shifted by 180°. The first input (green waveform) is represented by the equation  $V_{in,1} = -0.1\sin(2\pi 1000t + 180^\circ)$ , and the second input (blue waveform) as  $V_{in,2} = 0.7\sin(2\pi 1000t)$ . The resulting output (red waveform) is  $V_{out} = -0.6\sin(2\pi 1000t + 180^\circ)$ .

Figure 5-9. LTspice Voltage Adder Simulation (Subtraction Test)

#### Non-Inverting Multiplier Simulation

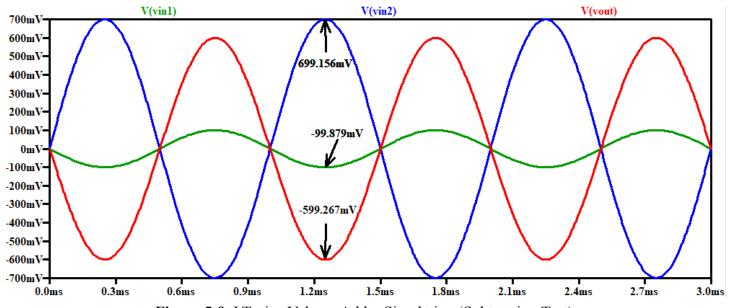

The non-inverting multiplier design allows for adjustable gain through the input and feedback resistors. Different combinations of resistors were used to test different gains. Figure 5-10 shows the input and output for a non-inverting multiplier with a gain of 2.2. The input (green) waveform is represented by  $V_{in} = \sin(2\pi 1000t)$ , and the resulting wave is approximately represented as  $V_{out} = 2.2\sin(2\pi 1000t)$ . When performing traditional multiplication,  $1 \times 2.2 = 2.2$ , thus the result is as expected and accurate. The calculation below shows the percent error for this simulation. As this configuration is a non-inverting configuration, the output is the true result without the extra inversion seen with the voltage adder or an inverting multiplier.

Percent Error =

$$\left| \frac{2.196 - 2.2}{2.2} \right| \times 100 = 0.181\%$$

Figure 5-10. LTspice Non-Inverting Multiplier Simulation (Gain of 2.2)

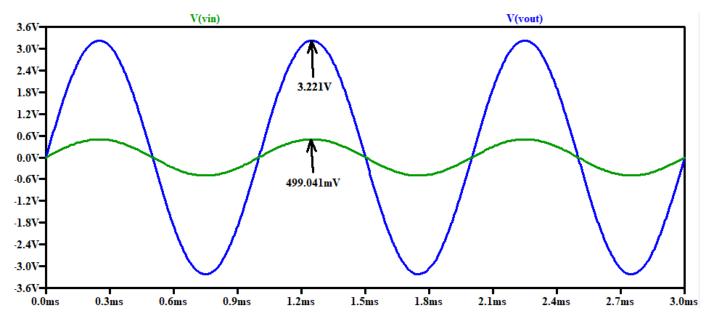

Figure 5-11 shows the input and output for a non-inverting multiplier with a gain of 2.2. The input (green) waveform is represented by  $V_{in} = 0.5\sin(2\pi 1000t)$ , and the resulting wave is approximately represented as  $V_{out} = 3.22\sin(2\pi 1000t)$ . When performing traditional multiplication,  $0.5 \times 6.45 = 3.225$ , thus the result is as expected and accurate. The calculation below shows the percent error for this simulation.

Percent Error =

$$\left| \frac{3.221 - 3.225}{3.225} \right| \times 100 = 0.124\%$$

Figure 5-11. LTspice Non-Inverting Multiplier Simulation (Gain of 6.45)

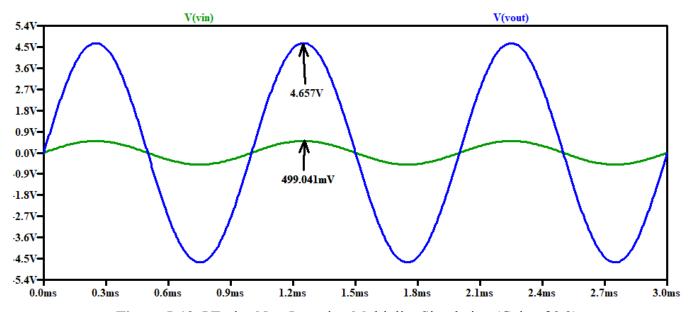

Figure 5-12 shows the input and output for a non-inverting multiplier with a gain of 9.3. The input (green) waveform is represented by  $V_{in} = 0.5\sin(2\pi 1000t)$ , and the resulting wave is approximately represented as  $V_{out} = 4.65\sin(2\pi 1000t)$ . When performing traditional multiplication,  $0.5 \times 9.3 = 4.65$ , thus the result is as expected and accurate. The calculation below shows the percent error for this simulation.

Percent Error =

$$\left| \frac{4.657 - 4.65}{4.65} \right| \times 100 = 0.151\%$$

Figure 5-12. LTspice Non-Inverting Multiplier Simulation (Gain of 9.3)

#### Resistive Divider Simulation

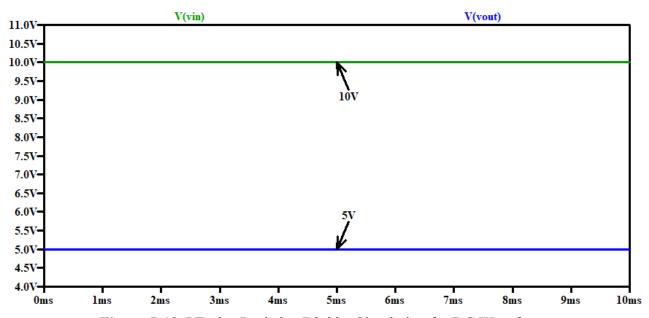

The resistive divider is capable of dividing any input signal by a divisor designated by two resistors. Four types of waveforms (DC, sine, square, and triangle) were tested to verify the circuit design's functionality. All of the following resistive divider tests use a divisor of 2 by using two 1 k $\Omega$  resistors. Figure 5-13 shows the input (green) and output (blue) waveforms for the DC waveform test. The input DC wave has a 10V offset, resulting in an output of 5V. The percent error for this test case is shown in the calculation below.

Percent Error =

$$\left| \frac{5-5}{5} \right| \times 100 = 0\%$$

Figure 5-13. LTspice Resistive Divider Simulation for DC Waveforms

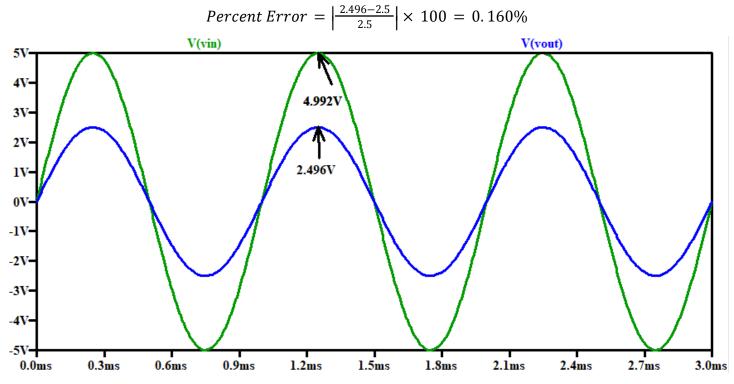

Figure 5-14 shows the input (green) and output (blue) waveforms for the sinusoidal waveform test. The input sinusoid is represented as approximately  $V_{in} = 5\sin(2\pi 1000t)$ , and with a divisor of 2, the output sinusoid is represented as approximately  $V_{out} = 2.5\sin(2\pi 1000t)$ . The percent error for this test case is shown below.

Figure 5-14. LTspice Resistive Divider Simulation for Sinusoidal Waveforms

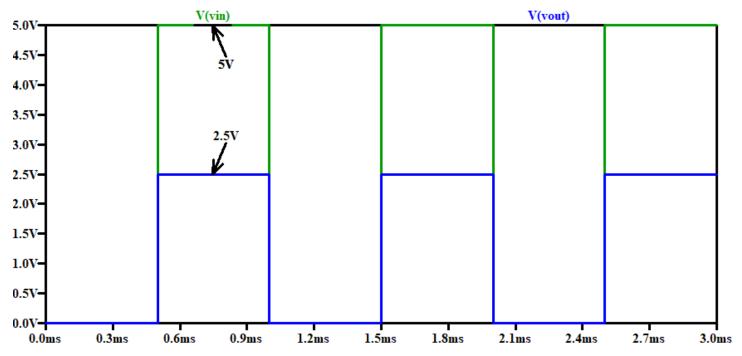

Figure 5-15 shows the input (green) and output (blue) waveforms for the sinusoidal waveform test. The input is a square wave of  $10V_{pp}$ , 1 kHz, DC offset of 2.5V, and with a divisor of 2, the output square wave is  $5V_{pp}$ , 1 kHz, DC offset of 1.25V. The percent error for this test case is shown below.

Percent Error =

$$\left| \frac{2.5 - 2.5}{2.5} \right| \times 100 = 0\%$$

Figure 5-15. LTspice Resistive Divider Simulation for Square Waveforms

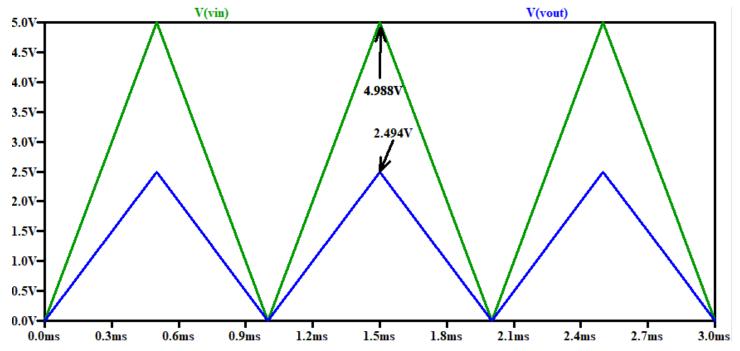

Figure 5-16 shows the input (green) and output (blue) waveforms for the sinusoidal waveform test. The input is a triangle wave of  $10V_{pp}$ , 1 kHz, DC offset of 2.5V, and with a divisor of 2, the output triangle wave is  $5V_{pp}$ , 1 kHz, DC offset of 1.25V. The percent error for this test case is shown below.

Percent Error =

$$\left| \frac{2.494-2.5}{2.5} \right| \times 100 = 0.240\%$$

Figure 5-16. LTspice Resistive Divider Simulation for Triangle Waveforms

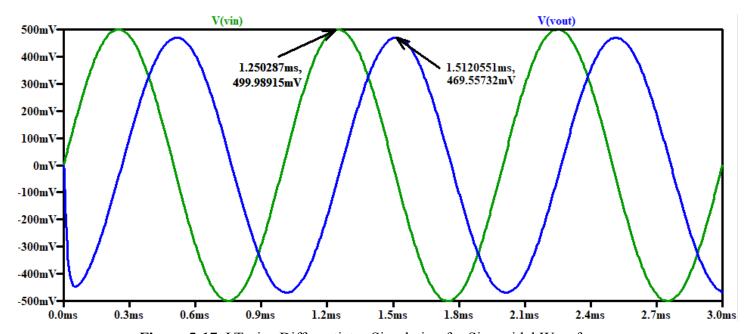

#### Differentiator Simulation

The differentiator circuit is also capable of performing the derivative of any input signal with DC waveforms as the exception. The following tests are different types of waveforms (sine, square, and triangle) inputted into the differentiator design. The output should have a 90° phase shift to the left. Figure 5-17 shows the differentiation of an input (green) sine wave of  $V_{in} = 0.5\sin(2\pi 1000t)$ . The resulting (blue) waveform is approximately represented by  $V_{out} = 0.47\sin(2\pi 1000t + 90^\circ)$ . The phase difference in degrees is calculated below as well as the percent error for this test case.

$$\Phi = \frac{360^{\circ}(time\ difference)}{frequency} = \frac{360^{\circ}((1.512-1.250)\times10^{3})}{1000\ Hz} = 94.32^{\circ}$$

$$Percent\ Error_{\Phi} = \left|\frac{94.32-90}{90}\right| \times 100 = 4.80\%$$

$$Percent\ Error_{Amplitude} = \left|\frac{2.494-2.5}{2.5}\right| \times 100 = 0.240\%$$

Figure 5-17. LTspice Differentiator Simulation for Sinusoidal Waveforms

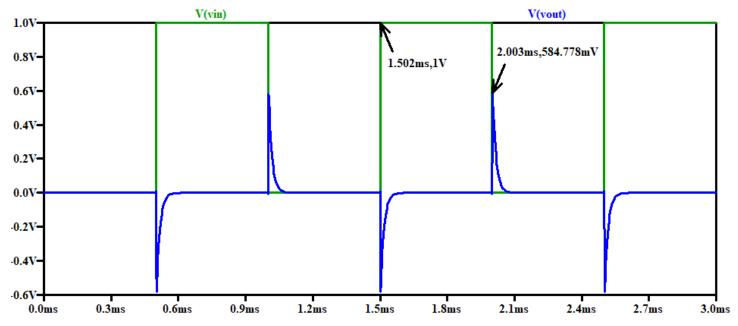

For square wave differentiation, the output shifts  $180^{\circ}$  to the left, with the waveform resembling impulses of alternating sign (positive or negative). Figure 5-18 shows the differentiation of an input (green) square wave of  $2V_{pp}$ , 1 kHz, and a DC offset of 0.5V. The resulting (blue) waveform has approximately  $1.2V_{pp}$ , 1 kHz, and a DC offset of 0V. The phase difference in degrees is calculated below as well as the percent error for this test case.

$$\Phi = \frac{360^{\circ}(time\ difference)}{frequency} = \frac{360^{\circ}((2.003 - 1.502) \times 10^{3})}{1000\ Hz} = 180.63^{\circ}$$

$$Percent\ Error_{\Phi} = \left| \frac{180.63 - 180}{180} \right| \times 100 = 0.2\%$$

Figure 5-18. LTspice Differentiator Simulation for Square Waveforms

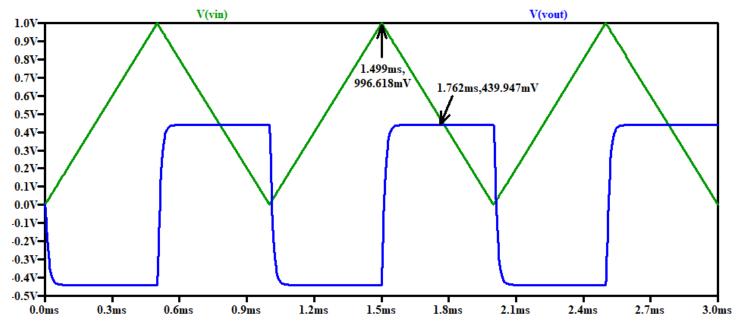

For triangle wave differentiation, the output shifts  $180^{\circ}$  to the left, with the waveform resembling a square wave. Figure 5-19 shows the differentiation of an input (green) triangle wave of  $2V_{pp}$ , 1 kHz, and a DC offset of 0.5V. The resulting (blue) waveform has approximately  $0.88V_{pp}$ , 1 kHz, and a DC offset of 0V. The phase difference in degrees is calculated below as well as the percent error for this test case.

$$\phi = \frac{360^{\circ}(time\ difference)}{frequency} = \frac{360^{\circ}((1.762 - 1.499) \times 10^{3})}{1000\ Hz} = 94.68^{\circ}$$

$$Percent\ Error_{\phi} = \left|\frac{94.68 - 90}{90}\right| \times 100 = 5.2\%$$

Figure 5-19. LTspice Differentiator Simulation for Triangle Waveforms

#### **Integrator Simulation**

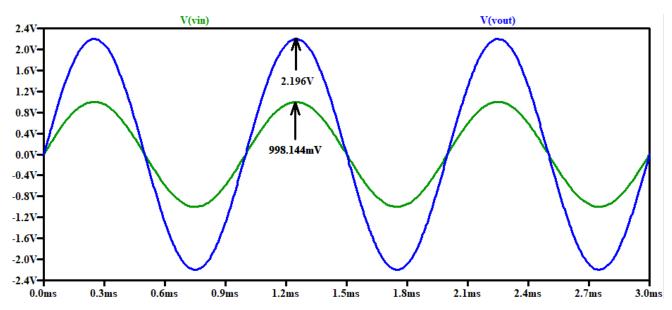

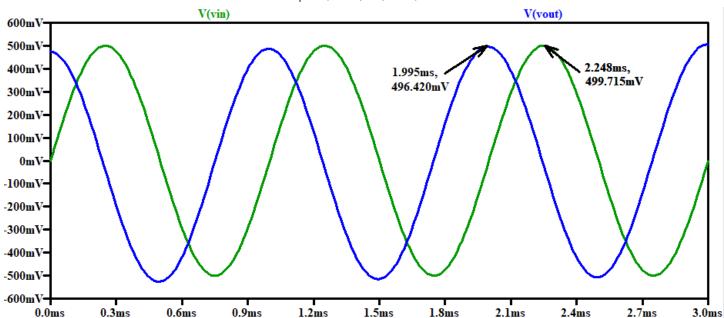

The integrator circuit is able to perform the integral of most inputs, with DC waveforms being the exception. The following integration tests include sine, square, and triangle wave inputs. The output waveform should have an approximate 90° phase shift to the right (-90°). Figure 5-20 shows the simulation for an integrated sine wave. The input (green) wave is represented by  $V_{in} = 0.5\sin(2\pi 1000t)$ , and the output is approximately represented by  $V_{out} = 0.5\sin(2\pi 1000t - 90^\circ)$ . The phase difference for this test case is calculated below as well as its percent error.

$$\phi = \frac{360^{\circ}(time\ difference)}{frequency} = \frac{360^{\circ}((1.995 - 2.248) \times 10^{3})}{1000\ Hz} = -91.\ 08^{\circ}$$

$$Percent\ Error_{\phi} = \left| \frac{-91.08 - (-90)}{(-90)} \right| \times 100 = 1.2\%$$

Figure 5-20. LTspice Integrator Simulation for Sinusoidal Waveforms

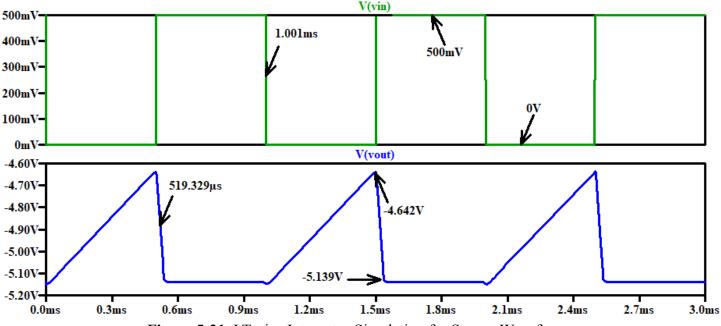

Figure 5-21 shows the simulation for an integrated square wave. The input (green) wave is  $0.5V_{pp}$  and 1 kHz with DC offset of 0V. The triangle wave output is approximately  $0.497V_{pp}$  and 1 kHz with DC offset of -4.9V. The phase difference for this test case is calculated below as well as its percent error.

$$\varphi = \frac{360^{\circ}(\text{time difference})}{\text{frequency}} = \frac{360^{\circ}((0.519329 - 1.001) \times 10^{3})}{1000 \text{ Hz}} = -173.402^{\circ}$$

Percent Error<sub>$$\phi$$</sub> =  $\left| \frac{-173.402 - (-180)}{(-180)} \right| \times 100 = 3.666\%$

Figure 5-21. LTspice Integrator Simulation for Square Waveforms

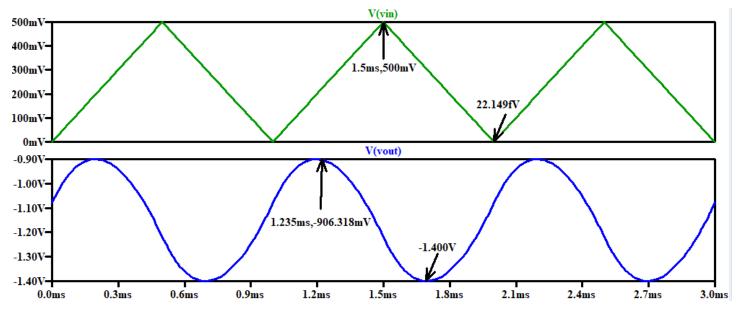

Figure 5-22 shows the simulation for an integrated triangle wave. The input (green) wave is  $0.5V_{pp}$  and 1 kHz with DC offset of 0.25V. The triangle wave output is approximately  $0.494V_{pp}$  and 1 kHz with DC offset of -1.15V. The phase difference for this test case is calculated below as well as its percent error.

Percent Error<sub>$$\phi$$</sub> =  $\left| \frac{-95.4 - (-90)}{(-90)} \right| \times 100 = 6\%$

Figure 5-22. LTspice Integrator Simulation for Triangle Waveforms

#### **Breadboard Testing and Results**

After thoroughly performing simulation testing on the LTspice circuits, the designs were constructed on breadboards to perform hardware (physical) tests. To perform the breadboard tests, the Rigol Technologies DP832 power supply, Keysight Technologies EDUX1052A function generator, and Keysight Technologies DSOX1204A oscilloscope were used to power the circuit and record measurements. The block diagram shown in Figure 5-1 shows the testing configuration for the hardware testing. The following describes the procedure for breadboard testing:

- 1. Construct the circuit based on the simulation-based design schematic.

- 2. Connect +18V, Ground, and -18V to each respective power rail input.

- 3. Set the waveform generator to the desired input waveform and set it to a high-impedance output.

- 4. Turn the power source on.

- 5. Connect the waveform generator to the circuit and turn it on.

- 5. Probe the input and output waveforms and record measurements.

#### Voltage Adder Breadboard Testing Results

Table 5-2 shows the breadboard testing results for the voltage adder circuit. For reference, the cells highlighted in blue represent DC voltage testing while white cells denote sinusoidal testing unless otherwise noted by signal type. As expected, DC voltage operations gave accurate output as the highest percent error is 4.17%, which is well below the design requirement of 10%. However, sinusoidal testing displays high inaccuracy as the highest percent error is 22%. The explanation that comes to mind is simply loose connections to the breadboard as an old breadboard used alongside jumper wires that sometimes broke during testing.

Table 5-2. Tabulated Breadboard Data for the Voltage Adder Circuit Test Cases

Operation Resistor Combination Input 1 [Vpp] Input 2 [Vpp] Output [Vpp] Expected [Vpp]

| Operation      | <b>Resistor Combination</b> | Input 1 [Vpp] | Input 2 [Vpp] | Output [Vpp] | Expected [Vpp] | Error [%] |

|----------------|-----------------------------|---------------|---------------|--------------|----------------|-----------|

|                | 100kΩ, $100$ kΩ, $100$ kΩ   | 0.1           | 0.7           | -0.8         | -0.8           | 0.00%     |

|                | 100kΩ, $100$ kΩ, $100$ kΩ   | 2.0           | 3             | -4.925       | -5.0           | 1.50%     |

| A ddition      | 100kΩ, $100$ kΩ, $100$ kΩ   | 10.0          | 5             | -14.825      | -15.0          | 1.17%     |

| Addition       | 100kΩ, $100$ kΩ, $100$ kΩ   | 0.1           | 0.7           | 0.72         | 0.8            | 10.00%    |

|                | 100kΩ, $100$ kΩ, $100$ kΩ   | 2.0           | 3             | 3.9          | 5.0            | 22.00%    |

|                | 100kΩ, $100$ kΩ, $100$ kΩ   | 10.0          | 5             | 11.7         | 15.0           | 22.00%    |

|                | 100kΩ, $100$ kΩ, $100$ kΩ   | -0.1          | 0.7           | -0.575       | -0.6           | 4.17%     |

|                | 100kΩ, $100$ kΩ, $100$ kΩ   | -2.0          | 3             | -1           | -1.0           | 0.00%     |

| Cultura ati an | 100kΩ, $100$ kΩ, $100$ kΩ   | -10.0         | 5             | 4.975        | 5.0            | 0.50%     |

| Subtraction    | 100kΩ, $100$ kΩ, $100$ kΩ   | -0.1          | 0.7           | -0.68        | -0.6           | 13.33%    |

|                | 100kΩ, 100kΩ, 100kΩ         | -2.0          | 3             | -1.12        | -1.0           | 12.00%    |

|                | 100kΩ, $100$ kΩ, $100$ kΩ   | -10.0         | 5             | -4.25        | -5.0           | 15.00%    |

#### Non-Inverting Multiplier Breadboard Testing Results

Table 5-3 displays the breadboard testing results for the non-inverting voltage multiplier circuit. The blue cells indicate the best frequency of operations. While the white cells denote different maximum frequencies of operation within the 10% error engineering specification mentioned in Chapter 3. DC testing shows the most accurate results due to the signal lacking frequency. The frequency of the signal plays a major role in accuracy

due to the LM741's gain bandwidth product. Since DC does not have a frequency, it generates the most accurate results. However, the sinusoidal signal used for testing had a frequency of 1kHz, which impacts the gain bandwidth product and in turn, increases error. In addition, this circuit amplifies the signal and it can also amplify noise generated by loose connections which also increases error.

Table 5-3. Tabulated Breadboard Data for the Non-Inverting Voltage Multiplier Circuit Test Cases

| Gain | Resistor<br>Combination            | Frequency<br>[kHz] | Phase Difference<br>[ns] | Phase Difference [°] | Input<br>[Vpp] | Output<br>[Vpp] | Expected [Vpp] | Error<br>[%] |

|------|------------------------------------|--------------------|--------------------------|----------------------|----------------|-----------------|----------------|--------------|

| 2.2  | 10kΩ, 12kΩ                         | 40                 | -357                     | -5.14080             | 2              | 4.42            | 4.4            | 0.45%        |

| 2.2  | 10kΩ, 12kΩ                         | 10                 | -105                     | -0.37800             | 10             | 22.2            | 22             | 0.91%        |

| 2.2  | 10kΩ, 12kΩ                         | 8                  | -256                     | -0.73728             | 12             | 26.9            | 26.4           | 1.89%        |

| 2.2  | 10kΩ, 12kΩ                         | 80                 | -1000                    | -28.80000            | 2              | 4.02            | 4.4            | 8.64%        |

| 2.2  | 10kΩ, 12kΩ                         | 16                 | -3297                    | -18.99072            | 10             | 21.4            | 22             | 2.73%        |

| 2.2  | 10kΩ, 12kΩ                         | 14.75              | -5300                    | -28.14300            | 12             | 23.7            | 26.4           | 10.23%       |

| 6.45 | $3.3k\Omega$ , $18k\Omega$         | 23.8               | -1087                    | -9.31342             | 1              | 6.47            | 6.45           | 0.31%        |

| 6.45 | 3.3kΩ, 18kΩ                        | 6                  | -165                     | -0.35640             | 3              | 19.5            | 19.35          | 0.78%        |

| 6.45 | $3.3k\Omega$ , $18k\Omega$         | 6                  | -1392                    | -3.00672             | 5              | 32.4            | 32.25          | 0.47%        |

| 6.45 | $3.3k\Omega$ , $18k\Omega$         | 4.685              | -1650                    | -2.78289             | 1              | 5.87            | 6.45           | 8.99%        |

| 6.45 | $3.3$ k $\Omega$ , $18$ k $\Omega$ | 19                 | -4200                    | -28.72800            | 3              | 17.5            | 19.35          | 9.56%        |

| 6.45 | $3.3$ k $\Omega$ , $18$ k $\Omega$ | 11.58              | -7256                    | -30.24881            | 5              | 29.1            | 32.25          | 9.77%        |

| 9.3  | $1.2k\Omega$ , $10k\Omega$         | 11.58              | -1757                    | -7.32458             | 1              | 9.5             | 9.3            | 2.15%        |

| 9.3  | $1.2k\Omega$ , $10k\Omega$         | 10                 | -3150                    | -11.34000            | 2              | 18.8            | 18.6           | 1.08%        |

| 9.3  | $1.2k\Omega$ , $10k\Omega$         | 8                  | -3650                    | -10.51200            | 3              | 28.87           | 27.9           | 3.48%        |

| 9.3  | $1.2k\Omega$ , $10k\Omega$         | 34                 | -2684                    | -32.85216            | 1              | 8.4             | 9.3            | 9.68%        |

| 9.3  | $1.2k\Omega$ , $10k\Omega$         | 18.8               | -5050                    | -34.17840            | 2              | 16.9            | 18.6           | 9.14%        |

| 9.3  | 1.2kΩ, 10kΩ                        | 12.9               | -7562                    | -35.11793            | 3              | 25.4            | 27.9           | 8.96%        |

#### Resistive Divider Breadboard Testing Results

As shown in Table 5-4, the resistive divider is verified to work across various waveforms. Accuracy is well within design requirements. However, the issue with using a potentiometer is that it is very sensitive to adjustments and the resistance always varies when tuning to the right divisor. This causes errors in the output due to tolerance and the sensitivity of the potentiometer, which may explain why there are varying levels of error among the results.

Table 5-4 Tabulated Breadboard Data for the Resistive Divider Circuit Test Cases

| Wave Type | <b>Resistor Combination</b> | Input [Vpp] | Divisor | Output [Vpp] | Expected [Vpp] | Error [%] |

|-----------|-----------------------------|-------------|---------|--------------|----------------|-----------|

|           | 1kΩ, 1kΩ                    | 10          | 2       | 5.1          | 5.000          | 2.00%     |

| DC        | 1kΩ, 3.9kΩ                  | 10          | 4.9     | 2.1          | 2.041          | 2.90%     |

|           | 1kΩ, 10kΩ                   | 10          | 11      | 0.979        | 0.909          | 7.69%     |

|           | 1kΩ, 1kΩ                    | 10          | 2       | 5.3          | 5.000          | 6.00%     |

| Sine      | 1kΩ, 3.9kΩ                  | 10          | 4.9     | 2.17         | 2.041          | 6.33%     |

|           | 1kΩ, 10kΩ                   | 10          | 11      | 0.96         | 0.909          | 5.60%     |

|           | 1kΩ, 1kΩ                    | 10          | 2       | 5.3          | 5.000          | 6.00%     |

| Square    | 1kΩ, 3.9kΩ                  | 10          | 4.9     | 2.21         | 2.041          | 8.29%     |

|           | 1kΩ, 10kΩ                   | 10          | 11      | 0.96         | 0.909          | 5.60%     |

|           | 1kΩ, 1kΩ                    | 10          | 2       | 5.1          | 5.000          | 2.00%     |

| Triangle  | 1kΩ, 3.9kΩ                  | 10          | 4.9     | 2.13         | 2.041          | 4.37%     |

|           | 1kΩ, 10kΩ                   | 10          | 11      | 0.92         | 0.909          | 1.20%     |

#### Differentiator Breadboard Testing Results

As shown in Table 5-5, the differentiator operated as expected with the output and phase difference error never exceeding the requirement of  $\pm 10\%$  tolerance. The frequency also shows that this circuit (and all others tested) will be in a low-frequency range. This also satisfies the requirement for the customer as the frequency of a standard US power grid of 50 Hz. This ensures that these circuits will be suitable for power grid computations.

Table 5-5. Tabulated Breadboard Data for the Differentiator Circuit Test Cases

| Input    | Resistor<br>Combination    | Frequency<br>[kHz] | Phase<br>Difference [°] | Expected | Phase Difference<br>Error [%] | Input<br>[Vpp] | Output<br>[Vpp] | Expected Output [Vpp] | Output<br>Error [%] |

|----------|----------------------------|--------------------|-------------------------|----------|-------------------------------|----------------|-----------------|-----------------------|---------------------|

|          | 1.5kΩ, 15kΩ                | 1                  | 97.79                   | 90       | 8.66%                         | 1              | 1.05            | 1                     | 5.00%               |

| Sine     | 1.5kΩ, 15kΩ                | 0.93               | 97.69                   | 90       | 8.54%                         | 6              | 6.3             | 6                     | 5.00%               |

|          | 1.5kΩ, 15kΩ                | 0.89               | 98.85                   | 90       | 9.83%                         | 12             | 12.7            | 12                    | 5.83%               |

|          | 1.5kΩ, 1kΩ                 | 1                  | 179.79                  | 180      | 0.12%                         | 1              | 1.27            | 1.21                  | 4.96%               |

| Square   | 1.5kΩ, 820Ω                | 1                  | 178.21                  | 180      | 0.99%                         | 6              | 7               | 7.2                   | 2.78%               |

|          | 1.5kΩ, $1.2$ kΩ            | 1                  | 176.51                  | 180      | 1.94%                         | 12             | 13.1            | 14.5                  | 9.66%               |

|          | $1.5k\Omega$ , $22k\Omega$ | 1                  | 94.42                   | 90       | 4.91%                         | 1              | 1.01            | 1                     | 1.00%               |

| Triangle | 1.5kΩ, 22kΩ                | 1                  | 95.62                   | 90       | 6.24%                         | 6              | 6.5             | 6                     | 8.33%               |

|          | 1.5kΩ, 18kΩ                | 1                  | 95.75                   | 90       | 6.39%                         | 12             | 11.3            | 12                    | 5.83%               |

#### **Integrator Testing Results**

Table 5-6 below displays the collected data for the various test cases performed on the integrator circuit. When testing, the potentiometer could not be probed when the circuit was active as this caused distortion on the output. To solve this issue, the potentiometer was tuned first and then the circuit was activated. Additionally, the potentiometer needed to be adjusted for different sine wave amplitudes due to the gain of the circuit. Another issue is that any resistance value of  $R_F$  below 470 k $\Omega$  would cause the phase difference to increase. However, when comparing the input and output amplitudes, the design requirement of a  $\pm 10\%$  tolerance was met successfully.

| Wave<br>Type | Resistor<br>Combination | Potentiometer<br>Resistance [kΩ] | Frequency<br>[kHz] | Expected<br>Phase<br>Difference [°] | Actual Phase<br>Difference [°] | Error<br>[%] | Expected<br>Input<br>[Vpp] | Input<br>[Vpp] | Output<br>[Vpp] | Error<br>[%] |

|--------------|-------------------------|----------------------------------|--------------------|-------------------------------------|--------------------------------|--------------|----------------------------|----------------|-----------------|--------------|

|              | 1kΩ, 470kΩ              | 97.1                             | 1                  | -90.000                             | -91.090                        | 1.21%        | 0.5                        | 0.51           | 0.51            | 0.00%        |

| Sine         | 1kΩ, 470kΩ              | 97.1                             | 1                  | -90.000                             | -93.400                        | 3.78%        | 1                          | 1.01           | 0.96            | 4.95%        |

|              | 1kΩ, 470kΩ              | 95.6                             | 1                  | -90.000                             | -92.470                        | 2.74%        | 2                          | 2.01           | 2.01            | 0.00%        |

|              | 1kΩ, 470kΩ              | 97.47                            | 1                  | -90.000                             | -93.200                        | 3.56%        | 0.5                        | 0.59           | 0.59            | 0.00%        |

| Square       | 1kΩ, 470kΩ              | 97.47                            | 1                  | -90.000                             | -94.580                        | 5.09%        | 1                          | 1.15           | 1.15            | 0.00%        |

|              | 1kΩ, 470kΩ              | 97.47                            | 1                  | -90.000                             | -93.990                        | 4.43%        | 1.8                        | 2.09           | 2.09            | 0.00%        |

|              | 1kΩ, 470kΩ              | 94.5                             | 1                  | -90.000                             | -91.770                        | 1.97%        | 0.5                        | 0.5            | 0.54            | 8.00%        |

| Triangle     | 1kΩ, 470kΩ              | 94.5                             | 1                  | -90.000                             | -90.940                        | 1.04%        | 1                          | 0.98           | 1.05            | 7.14%        |

|              | 1kΩ, 470kΩ              | 94.5                             | 1                  | -90.000                             | -94.570                        | 5.08%        | 2                          | 2.01           | 2.01            | 0.00%        |

Table 5-6. Tabulated Breadboard Data for the Integrator Circuit Test Cases

#### Printed Circuit Board Tests and Results

After testing the designed computational circuits on breadboards and confirming their functionality and compatibility with each other, the circuits were manufactured as PCBs. The appropriate components, both passive and active previously used in the breadboard testing, were soldered onto the PCBs. Once conductivity was confirmed among each of the circuits, each were tested using the same test cases used in the breadboard testing. The same aforementioned Rigol Technologies power supply, Keysight Technologies function generator, and Keysight Technologies oscilloscope were used to power the circuits and obtain data. The PCB testing apparatus is visualized in Figure 5-1, and the following describes the procedure for PCB testing:

- 1. Connect +18V, Ground, and -18V to each respective power rail input.

- 2. Set the waveform generator to the desired input waveform and set it to a high-impedance output.

- 3. Turn the power source on.

- 4. Connect the waveform generator to the circuit and turn it on.

- 5. Probe the input and output waveforms and record measurements.

#### Voltage Adder PCB Testing Results

Table 5-7 shows the test cases for the PCB voltage adder. For reference, the cells highlighted in blue represent DC voltage testing while white cells denote sinusoidal testing unless otherwise noted by signal type. Comparing these results to the breadboard testing shows massive improvements in accuracy as operations on sinusoids are well below the requirement. This also confirms the explanation for the source of error as soldering components

provide a rigid connection between components. However, the accuracy of operations with DC signals decreased as the breadboard testing showed percent errors below 5%. This displays a tradeoff as in order to improve accuracy with sinusoids, the PCB provides the best result at the cost of accuracy with DC signals.

Table 5-7. Tabulated PCB Data for the Voltage Adder Circuit Test Cases

| Operation   | <b>Resistor Combination</b> | Input 1 [Vpp] | Input 2 [Vpp] | Output [Vpp] | Expected [Vpp] | Error [%] |

|-------------|-----------------------------|---------------|---------------|--------------|----------------|-----------|

|             | 100kΩ, $100$ kΩ, $100$ kΩ   | 0.1           | 0.7           | -0.75        | -0.8           | 6.25%     |

|             | 100kΩ, $100$ kΩ, $100$ kΩ   | 2.0           | 3             | -4.72        | -5.0           | 5.60%     |

| A 44141     | 100kΩ, $100$ kΩ, $100$ kΩ   | 10.0          | 5             | -14.5        | -15.0          | 3.33%     |

| Addition    | 100kΩ, $100$ kΩ, $100$ kΩ   | 0.1           | 0.7           | 0.76         | 0.8            | 5.00%     |

|             | 100kΩ, $100$ kΩ, $100$ kΩ   | 2.0           | 3             | 4.78         | 5.0            | 4.40%     |

|             | 100kΩ, $100$ kΩ, $100$ kΩ   | 10.0          | 5             | 15.3         | 15.0           | 2.00%     |

|             | 100kΩ, $100$ kΩ, $100$ kΩ   | -0.5          | 1             | -0.473       | -0.5           | 5.40%     |

|             | 100kΩ, $100$ kΩ, $100$ kΩ   | -2.0          | 3             | -0.95        | -1.0           | 5.00%     |

| Cultraction | 100kΩ, $100$ kΩ, $100$ kΩ   | -10.0         | 5             | 5.075        | 5.0            | 1.50%     |

| Subtraction | 100kΩ, $100$ kΩ, $100$ kΩ   | -0.1          | 0.7           | -0.61        | -0.6           | 1.67%     |

|             | 100kΩ, $100$ kΩ, $100$ kΩ   | -2.0          | 3             | -0.95        | -1.0           | 5.00%     |

|             | 100kΩ, $100$ kΩ, $100$ kΩ   | -10.0         | 5             | -5.075       | -5.0           | 1.50%     |

### Non-Inverting Multiplier PCB Test Results

Table 5-8 shows the PCB Testing results for the voltage multiplier. The blue cells indicate the best frequency of operations. While the white cells denote different maximum frequencies of operation within the 10% error engineering specification mentioned in Chapter 3. The tests show that design requirements are still met, but barely so in the case of maximum operating frequencies. This is due to the gain bandwidth product of the LM741 as at higher frequencies, there is a loss of available gain. This causes inaccuracies in the output, which is clearly demonstrated in the maximum operating frequencies.

Table 5-8. Tabulated PCB Data for the Non-Inverting Voltage Multiplier Circuit Test Cases

| Gain | Resistor<br>Combination            | Frequency<br>[kHz] | Phase Difference [ns] | Phase Difference [°] | Input<br>[Vpp] | Output<br>[Vpp] | Expected<br>[Vpp] | Error<br>[%] |

|------|------------------------------------|--------------------|-----------------------|----------------------|----------------|-----------------|-------------------|--------------|

| 2.2  | 10kΩ, 12kΩ                         | 81                 | -837                  | -24.36               | 2              | 4.4             | 4.4               | 0.00%        |

| 2.2  | 10kΩ, 12kΩ                         | 17.5               | -3484                 | -21.93               | 10             | 22.1            | 22                | 0.45%        |

| 2.2  | 10kΩ, $12$ kΩ                      | 15                 | -3520                 | -19.01               | 12             | 26.5            | 26.4              | 0.38%        |

| 2.2  | 10kΩ, $12$ kΩ                      | 99.5               | -1011                 | -36.31               | 2              | 3.9             | 4.4               | 11.36%       |

| 2.2  | 10kΩ, $12$ kΩ                      | 20.6               | -3968                 | -29.43               | 10             | 20.1            | 22                | 8.64%        |

| 2.2  | 10kΩ, $12$ kΩ                      | 17.6               | -5200                 | -32.90               | 12             | 23.7            | 26.4              | 10.23%       |

| 6.45 | $3.3k\Omega$ , $18k\Omega$         | 24                 | -1304                 | -11.27               | 1              | 6.5             | 6.45              | 0.78%        |

| 6.45 | $3.3k\Omega$ , $18k\Omega$         | 19                 | -2848                 | -19.50               | 3              | 19.3            | 19.35             | 0.26%        |

| 6.45 | $3.3$ k $\Omega$ , $18$ k $\Omega$ | 6                  | -1696                 | -3.66                | 5              | 32.6            | 32.25             | 1.09%        |