### ARTICLE IN PRESS

Materials Science in Semiconductor Processing xxx (xxxx) xxx-xxx

Contents lists available at ScienceDirect

Materials Science in Semiconductor Processing

journal homepage: www.elsevier.com/locate/mssp

# Trapping phenomena and degradation mechanisms in GaN-based power HEMTs

Matteo Meneghini<sup>a,\*</sup>, Alaleh Tajalli<sup>a</sup>, Peter Moens<sup>b</sup>, Abhishek Banerjee<sup>b</sup>, Enrico Zanoni<sup>a</sup>, Gaudenzio Meneghesso<sup>a</sup>

<sup>a</sup> University of Padova, Department of Information Engineering, via Gradenigo 6/B, 35131 Padova, Italy

<sup>b</sup> ON Semiconductor, Westerring 15, 9700 Oudenaarde, Belgium

#### ABSTRACT

This paper reports an overview of the most relevant trapping and degradation mechanisms that limit the performance and lifetime of GaN-based transistors for application in power electronics. Results obtained on state-of-the-art devices are described and discussed throughout the paper, with the aim of providing a clear description of the topic. The first part of the paper deals with the issue of dynamic- $R_{on}$ : after describing a robust test strategy for the analysis of the pulsed characteristics of the devices, we discuss the voltage- and temperature-dependent pulsed I-V characteristics of 650 V-rated transistors, and the physical origin of dynamic  $R_{on}$  in these devices. The results demonstrate that through proper buffer optimization it is possible to reach negligible trapping at high voltage. The properties of the traps responsible for dynamic- $R_{on}$  are also discussed in detail in the paper, based on drain-current transient data. A specific discussion is devoted to hot-electron trapping processes, that – under hard switching conditions – may lead to significant modifications in the resistance of the 2DEG.

The second part of the paper deals with device degradation: based on a wide set of experimental results, we describe the physical mechanisms responsible for the worsening of the properties of the devices. More specifically, we demonstrate that stress in off-state conditions may result in measurable changes in the pinch-off voltage, mostly consisting in a negative-threshold instability (NBTI). The origin of this shift is discussed in detail; we also demonstrate that in a real-life cascode configuration (where a low, subthreshold leakage current flows through the device in the off-state), NBTI effects are mitigated. Finally, we discuss the stability of the gate-stack, induced by the exposure to positive gate bias.

#### 1. Introduction

Energy efficiency is one of the biggest challenges for electric and electronic engineers. Everywhere energy is generated, stored and transformed, there are losses, that must be minimized in order to reduce our environmental fingerprint. Nearly 10% of global electricity consumption goes into conversion losses. Power converters are everywhere, from laptop chargers to photovoltaic plants and electric vehicles. The key element of a switching power converter is the switch, a transistor which is continuously switched on- and off- with the aim of transferring energy from a source (mains, battery, PV modules, ...) to the load (car engine, ...). To fabricate low loss converters, it is necessary to improve and optimize the properties of the switching element. Silicon transistors have excellent structure and performance but, owing to the low breakdown field of Si (0.3 MV/cm) they have intrinsic limitations in terms of on-resistance. Recently, other semiconductors have

emerged as alternatives to silicon, including GaN, SiC, Ga2O3. These materials have a wide energy gap, and therefore can be used for power applications. Among these, GaN has shown impressive advantages: first of all, the wide energy gap (3.4 eV) allows to reach high operating temperatures (> 350 °C [1]), thus permitting to minimize the size and weight of the heat sinks. A second advantage is the high mobility  $(> 1200 \text{ cm}^2/\text{V s})$  of the 2-dimensional electron gas (2DEG) formed at the interface between AlGaN and GaN, which leads to low channel resistance and high current density (> 1 A/mm [2]). The breakdown field of GaN (3.3 MV/cm) is 11 times higher than that of silicon (0.3 MV/cm): this has a direct impact on the on-resistance of the transistors. In fact, for the same breakdown voltage, a device based on GaN can be 11 times smaller than its silicon counterpart. Finally, GaN transistors have a low  $R_{on}^*Q_g$  product (< 1  $\Omega^*nC$  [3]), and this allows the minimization of the switching losses at system level, and to increase the operating switching frequency to the 100 kHz-MHz range. This

\* Corresponding author.

E-mail address: matteo.meneghini@dei.unipd.it (M. Meneghini).

http://dx.doi.org/10.1016/j.mssp.2017.10.009

Received 12 July 2017; Received in revised form 4 October 2017; Accepted 9 October 2017 1369-8001/ @ 2017 Published by Elsevier Ltd.

permits to reduce the size of the passive components (capacitors and inductors), and thus of the power converters.

These properties of GaN have led device engineers to consider this material as an excellent candidate for the fabrication of the next generation power converters. Based on GaN, kW-range converters with efficiency in excess of 99% have already been demonstrated [4].

Several device technologies have been proposed and evaluated throughout the years. Schottky-gated HEMTs have the simplest structure, at the expense of a slightly higher gate leakage current with respect to the insulated-gate counterpart. Based on this approach, devices with breakdown voltage higher than 1100 V have been demonstrated in the literature [5]. An approach to reduce the gate leakage current while maintaining a good dynamic performance and reliability is to add a thin insulator under the gate, thus adopting a metal-insulator-semiconductor (MIS) approach. Also this approach allows to reach a high breakdown voltage, having the further advantage of permitting operation at positive gate bias without measurable gate current. MIS structures can be fabricated either by recessing the AlGaN layer under the gate (in this case, a positive threshold voltage - i.e. a normally-off behavior - is obtained) or by keeping the full AlGaN thickness both in the access regions and under the gate. In the latter case, the threshold voltage is negative. To achieve normally-off behavior, the devices are connected in cascode configuration with a silicon MOSFET [6]; both transistors are placed in the same package, to minimize space occupation and parasitic capacitances/inductances.

Normally-off operation can be obtained also by implementing specific strategies at device levels. Fluorine implantation in the gate region permits to deplete the channel under the gate, thus leading to a positive threshold voltage [7]. The stability of threshold voltage strongly depends on the optimization of the implantation process. Early papers indicated that F-ions may be unstable under bias/temperature stress [8], while more updated reports were able to demonstrate highly stable devices [9]. A further approach [10] consists in using a p-InGaN cap layer; this allows to reach normally-off operation by employing the polarization-induced field in the InGaN cap and the negative charge in the p-InGaN. Normally-off devices were also demonstrated by using a self-aligned n++GaN/InAlN/AlN/GaN MOS approach, capable of threshold voltages between 1.3 and 3.7 V depending on the gate oxide thickness [11]. Another, widely used, approach for normally-off operation consists in adding a p-GaN layer under the gate metal [12]. The use of a p-GaN layer, due to the high-acceptor doping, leads to a significant depletion of the channel beneath the gate, thus permitting to reach threshold voltage levels in the range 1-2 V.

Independently of the structure, for power devices the robustness against high voltage/high temperature stress represents the most important target to be satisfied. Several publications (see for instance [13–17]) pointed out that GaN power transistors may show a recoverable increase in on-resistance (often referred to as dynamic-Ron increase), when they are exposed to high off-state bias. This may originate to trap states located either at the surface or in the buffer. Surface trapping can be solved through a careful optimization of the surface treatments. On the other hand, buffer trapping still remains an issue, if the properties of the epitaxial structure are not carefully engineered [18]. In the first part of this paper we will discuss the physical processes responsible for buffer trapping in GaN-based power HEMTs. Without loss of generality, the results will refer to insulated-gate devices rated for 650 V operation. We demonstrate that through the optimization of device structure it is possible to achieve negligible-dynamic Ron at 600 V, 150 °C. This result indicates that GaN transistors can be highly competitive with their silicon counterpart for application in power switching devices. In addition, we discuss also the trapping processes related to the presence of hot-electrons, which may affect device performance when the transistors are operated in hard-switching conditions.

With regard to stability and reliability, we describe the impact of stress in off-state conditions, and we discuss the threshold voltage instabilities induced by off-state stress. We also analyze the impact of positive gate stress on MIS-type transistors.

The up-to-date data presented within this paper provide a detailed overview on the state-of-the-art of normally-on GaN technology for power conversion. Several considerations (e.g. those related to buffer trapping processes) can be extended also to normally-off devices, thus providing general guidelines to minimize the impact of charge trapping processes. Normally-off GaN devices may suffer from gate-related degradation processes similar to those described within this paper, if they are based on the MIS/MOS approach; other factors may affect the performance of transistors with a p-type gate, due to the specific nature of their structures and materials.

#### 2. Experimental details

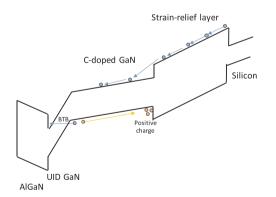

The results described within this paper were obtained on GaN-on-Silicon power transistors. The epitaxial structure was grown by metalorganic chemical vapour deposition (MOCVD), and consists of an AlN/ AlGaN/GaN strain relief layer, a thick C-doped GaN layer, an unintentionally-doped GaN channel layer, and an AlGaN barrier layer. The final step in the fabrication process was the in-situ growth of the 50 nm SiN layer, which was used both as a gate insulator and as a first passivation in the access regions. The fabricated devices have a threshold voltage around -10 V, and are designed for use in cascode configuration. The maximum voltage/current rating of this technology is 650 V/100 A, with on-resistance below 10 m $\Omega$ . For most of the experiments we used small test structures, having a gate width of 200 µm. To investigate the charge trapping processes, the devices were submitted to pulsed and transient characterization at several temperature/ current levels. Details on the measurement setup and conditions are given below. A set of stress tests was then carried out under off-state and semi-on state conditions; data on the main device parameters (onresistance, threshold current, electroluminescence signal, ...) were collected throughout the experiments, with the aim of describing the stress kinetics and gathering information on the degradation processes.

#### 3. Results and discussion

#### 3.1. Physical origin of dynamic-Ron

Several strategies have been implemented for the investigation of dynamic-R<sub>on</sub> in GaN-based power HEMTs. In our case, we developed a custom setup, which gives us the maximum freedom of changing the main measurement parameters, and the possibility of exploring different time/voltage/temperature ranges.

Fig. 1 reports a detailed schematic of the custom system used for the execution of pulsed and transient measurements on GaN-based power HEMTs. Two large bandwidth arbitrary waveforms generators (AWGs) are used to generate the control pulses to be applied to the gate and the drain. The signal is then amplified through two power amplifiers having proper dynamic response, and used as an input to the gate and drain terminals. Between the drain amplifier ( $V_{DD}$ ) and drain terminal ( $V_{DS}$ ), a load resistor is placed. This load resistor is used to measure the drain current, by evaluating its voltage drop through a differential voltage probe. The drain-source voltage is also measured, with the aim of providing a full characterization of device properties.

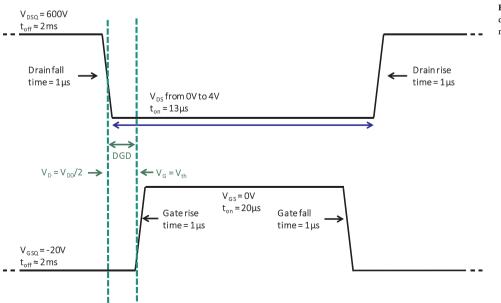

The system can operate both in pulsed and in transient mode. In pulsed mode, an off-state bias ( $V_{GSQ}$ ,  $V_{DSQ}$ ) (with a gate voltage smaller than the threshold voltage and a high drain bias) is used to induce charge trapping. A pre-trapping phase (typically 10–100 s) is applied, to fill all the traps and reach a steady-state condition. Then, a square wave bias is applied to the gate and the drain of the devices, as schematically shown in Fig. 2. The off/on ratio is typically very high, around 99%, to maximize the effects of charge trapping. During the off-state phase (which lasts 2 ms in Fig. 2), the traps are filled, while the current is measured during short (20  $\mu$ s) on-state pulses, in order to avoid charge

## ARTICLE IN PRESS

#### 1005 DRAIN AWG Ext Sync Ou 1kΩ SCOPE AMP o OUT 50 Q 0 0 x120 O VOLT. снз сн DRAIN CH2 0 O о 0 GATE AWG DUT URCE AMP 0 0 500 C C FUSE x20

de-trapping during the pulsed current-voltage (PIV) measurement. It can be easily understood that these conditions constitute a worst-case scenario. In fact, in real-life operation, the devices are operated with a much smaller off/on ratio, and may have time to de-trap part of the carriers during the on-state phase. The measurements are carried out at several trapping voltages and temperatures, in order to evaluate how the main driving forces (temperature, electric field) favor charge trapping during operation.

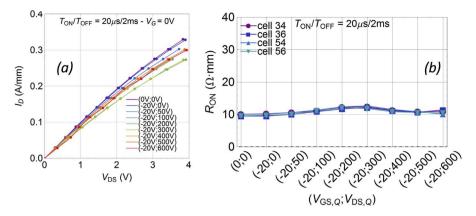

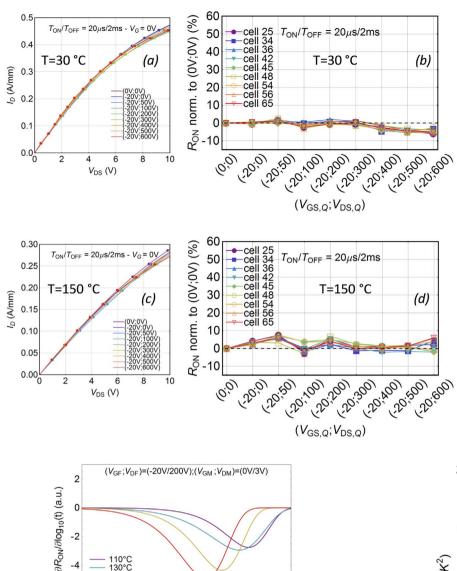

Fig. 3 reports the pulsed-IV curves measured on a state-of-the-art device at room temperature, with a maximum trapping voltage of 600 V. As can be noticed, the device shows negligible increase in on-resistance, at 600 V. The on-resistance peaks at trapping voltages near 200–300 V, and then decreases again at higher trapping bias.

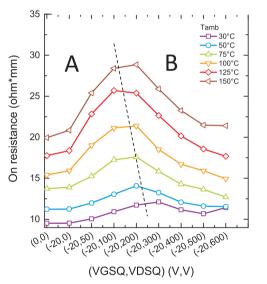

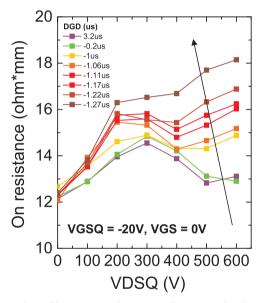

A more detailed description of dynamic- $R_{on}$  is given in Fig. 4, which reports the dependence of on-resistance on the trapping voltage and temperature, in the range 0–600 V and 30–150 °C, which is relevant for real-life operation [15]. As can be noticed, the on-resistance has a non-monotonic dependence on the trapping voltage in the whole set of measurement conditions. Such behavior can be explained by considering the schematic diagram in Fig. 5. When a moderate trapping voltage is applied to the devices in the off-state (e.g.  $V_{GSQ} = -20 V$ ,  $V_{DSQ} = 200 V$ , region A in Fig. 4), the carbon-doped buffer is partly depleted. The carbon acceptors are located at Ev + 0.9 eV, and are then ionized, thus acquiring a negative charge state. As a consequence, dynamic  $R_{on}$  increases in the voltage range up to 2–300 V.

For higher voltages (V > 200-300 V, region B in Fig. 4), charge is re-distributed within the structure due to the increase in the drain-to-

substrate leakage components. Band-to-band leakage processes may also lead to a positive charge storage at the interface with the strainrelief layer [18], due to the neutralization of the ionized acceptors or to the ionization of donor states (Fig. 5). This explains why for voltages higher than 2–300 V the dynamic- $R_{on}$  shows a decrease and recovery. It is worth noticing that this recovery is almost complete at 600 V (Fig. 4), thus indicating that current device technologies allow to reach negligible-dynamic- $R_{on}$  at high voltage levels. A lateral redistribution of charge may also take place and influence the overall dynamic on-resistance [19].

Vertical leakage current increases with temperature [20]: this explains why the transition between region A and B in Fig. 4 moves towards lower voltages at higher temperatures. The results described above provide a clear indication of the pathway for minimizing dynamic on-resistance in GaN-based transistors. First, the influence of carbon doping on 2DEG concentration must be minimized, through proper optimization of the C-doping level and of the thickness of the unintentionally-doped GaN. Second, leakage through the unintentionally-doped GaN layer must be optimized, in order to favor charge-redistribution through the structure (that leads to a complete suppression of dynamic  $R_{\rm on}$ ) without reaching an excessive vertical leakage current. Based on this optimization, devices with negligible dynamic- $R_{\rm on}$  both at room temperature and high temperature have been demonstrated within this work, as shown by the dynamic- $R_{\rm on}$  measurements in Fig. 6.

The properties of the trap levels responsible for dynamic-R<sub>on</sub> can be investigated by means of drain-current transient measurements. Here

Fig. 2. Schematic drawing of the experimental conditions used for pulsed current-voltage measurements.

# Materials Science in Semiconductor Processing xxx (xxxx) xxx-xxx

Fig. 1. Schematic drawing of the custom system used for the execution of pulsed and transient measurements on power GaN HEMTs.

#### Materials Science in Semiconductor Processing xxx (xxxx) xxx-xxx

Fig. 3. (a) Pulsed-IV curves measured at room temperature on a GaN-based power HEMT. (b) Dependence of on-resistance on the applied trapping bias (the four lines refer to four devices sitting on different locations on the wafer).

Fig. 4. Dependence of dynamic- $R_{\rm on}$  (as measured from pulsed I-V measurements) on trapping voltage and temperature.

Fig. 5. Schematic representation of the mechanisms responsible for non-monotonic dynamic- $R_{on}$  as a function of trapping voltage.

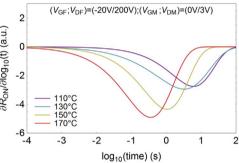

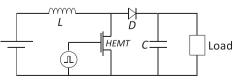

the idea is the following: an off-state (trapping) bias is applied for a relatively long time (100 s), by means of the setup in Fig. 1. The device is then switched to the on-state, and the variation of on-resistance over time is evaluated in the time-range between 100  $\mu$ s and 1000 s. The measurement is then repeated at several temperature levels, in order to extrapolate the activation energy of the traps. The derivative of the R<sub>on</sub> transients is then plotted, to describe the time constants as a series of peaks. Fig. 7 reports the results obtained on the same samples as in Fig. 4. As can be noticed, the time constant of the de-trapping process

ranges between 0.3 s and 10 s in the temperature range between 110 °C and 170 °C. A single de-trapping process is observed, having activation energy around 0.63 eV (see the Arrhenius plot in Fig. 8). Activation energies in the range 0.6–0.9 eV are typically ascribed to carbon acceptors in GaN [21,22]. The predicted energy of carbon on nitrogen site ( $C_N$ ) is 0.9 eV; however, the recovery kinetics of  $R_{on}$  may be significantly influenced by the vertical and lateral redistribution of carriers through the structures [23], and this may slightly change the activation energies with respect to theoretical predictions.

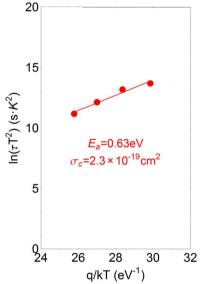

The trapping mechanisms described above are induced by the exposure to off-state conditions, i.e. by the ionization of buffer traps, or by the flow of leakage current through the structure. During real-life operation, GaN transistors can be subject also to hard-switching transitions, when they are switched from off- to on-state. A peculiar aspect of hard switching events is that the devices are simultaneously subject to high electric field and high 2DEG current. Under these conditions, a second factor promotes charge trapping: the presence of hot electrons. Hard switching conditions may be present in a boost power converter, see the schematic drawing in Fig. 9. When the transistor is turned on, its drain-source voltage is very high (600 V), and has to decrease rapidly, as the device reaches the linear region. At the same time, the transistor turns on, and current starts flowing through the channel. The electrons that flow through the 2DEG during the switching event are significantly accelerated by the electric field, thus becoming "hot", and may be injected either into the buffer or at the surface, thus leading to an increase in on-resistance.

In order to understand if under hard-switching conditions there are additional trapping processes that promote charge trapping with respect to off-state operation, we developed a specific experimental setup, whose operating principle is similar to that reported in Fig. 2, but with variable overlapping between the drain and gate pulses. The transistor has a resistive load, and the gate and drain terminals are controlled by two independent pulsers. The timing of the pulsers can be modified, by changing the delay between gate and drain (drain-gate delay, DGD), with the aim of obtaining negligible overlapping between the gate and drain waveforms (no hot electron trapping, DGD > 0), or considerable hot-electron trapping (with DGD < 0). DGD is defined as the time from when the drain voltage decreases to 50% of its maximum value to when the gate voltage increases above the threshold voltage of the device (i.e. when current starts flowing through the channel).

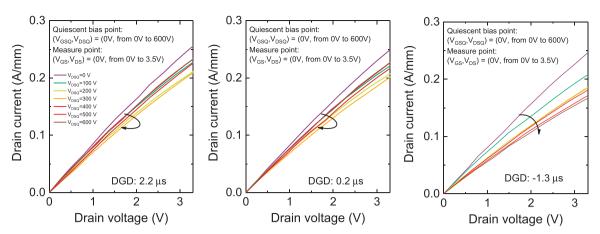

Fig. 10 reports the pulsed I-V curves measured starting from different quiescent bias points under soft switching (DGD > 0) and hard switching (DGD < 0) conditions. As can be noticed, the curves measured under soft switching conditions (DGD =  $2.2 \,\mu s$  and DGD =  $0.2 \,\mu s$ ) show the same behavior already described in Fig. 3, i.e. a nonmonotonic increase in on-resistance as trapping voltage is increased from  $V_{DSQ} = 0 V$  to  $V_{DSQ} = 600 V$ . On the other hand, when the switching transition is "hard", i.e. when there is a considerable overlapping between the drain and gate waveforms, dynamic-R<sub>on</sub> increases monotonically with voltage. A better description of this behavior is

#### Materials Science in Semiconductor Processing xxx (xxxx) xxx-xxx

Fig. 6. Results of pulsed-IV measurements carried out on an optimized device up to  $V_{DSQ}$  = 600 V, both at room temperature (a) and high temperature (c). (b) and (d) represent the dependence of dynamic-Ron (normalized to the value measured with no trapping bias) on trapping voltage. Each line refers to an individual device on the wafer. The measurements are shown both at 30 °C (b) and 150 °C (d).

Fig. 7. Drain-current transient spectra (derivatives of the dynamic on-resistance transients) measured with a trapping bias of  $V_{GSQ}$  = -20 V,  $V_{DSQ}$  = 200 V at different temperature levels.

given by Fig. 11, that reports the dependence of dynamic-Ron on the trapping voltage and on the overlapping between gate and drain waveforms DGD. As can be noticed, for DGD < 0 (i.e. for a hard switching transition) dynamic-Ron is considerably enhanced with respect to softswitching transitions, for high  $V_{DSQ} > 400$  V. It is worth noticing that the hard switching intervals reached during these tests ( $\approx 1 \, \mu s$ ) are more stressful than in real-life operation (10-100 ns). This choice was done to reproduce the worst-case scenario in our tests.

To confirm the role of hot electrons in favoring charge trapping during a hard switching transition we carried out electroluminescence measurements during pulsed operation with different values of DGD. Typically, HEMTs emit a weak electroluminescence signal, which originates from the deceleration of the highly-energetic electrons present in the channel (Bremsstrahlung). The intensity of the EL signal is proportional to both the amount of electrons in the channel (drain current, I<sub>D</sub>) and to the accelerating field. Fig. 12 reports three frames, representing the EL signal measured during pulsed operation in soft-

Fig. 8. Arrhenius plot for the de-trapping process shown in Fig. 7.

Fig. 9. Schematic representation of a boost power converter.

switching (DGD > 0) and hard switching (DGD < 0). As can be noticed, no significant EL signal is measured in soft switching operation, since no current flows through the channel of the devices. On the contrary, a

#### Materials Science in Semiconductor Processing xxx (xxxx) xxx-xxx

Fig. 10. Pulsed I-V curves collected by inducing trapping in three different conditions: soft-switching (DGD > 0 and DGD  $\approx$  0), and hard switching (DGD < 0).

Fig. 11. Dependence of dynamic- $R_{on}$  on the trapping voltage  $V_{DSQ}$  and on the overlapping (DGD) between the gate and drain waveforms.

Fig. 12. EL patterns measured during soft and hard switching transitions.

significant EL signal is emitted during hard switching transitions (DGD < 0). The luminescence signal is emitted evenly along the channel, and peaks on the gate edge on the drain side, i.e. where the electric field is maximum. Remarkably, the on-resistance increase induced by hot-electrons was found to decrease at higher temperatures (not shown here for brevity). This is consistent with the hypothesis that hot electrons are responsible for trapping. In fact, at higher temperatures the average energy of the electrons in the channel decreases, due to the increased scattering with the lattice and to the corresponding decrease in the mean-free path over which the electrons are accelerated. For this reason, hot-electron effects are less prominent at high temperature levels.

#### 3.2. Degradation processes

GaN-based transistors are designed to operate at high voltages (> 600 V) and temperature (> 125 °C) levels. For this reason, it is of fundamental importance to study the field-related and the temperatureactivated degradation processes. Degradation may be gradual or catastrophic. Typically, gradual degradation consists in a parametric shift in threshold voltage and/or in on-resistance, which is induced by the exposure to high off-state bias. Catastrophic degradation may originate from the failure of dielectric submitted to high electric field, and/or of the III-N layer subject to extremely high voltages. In this section, we describe the two most relevant degradation mechanisms that may take place in GaN-based power MIS-HEMTs submitted to stress. The first process is the threshold voltage instability induced by off-state stress at high temperatures (high-temperature, reverse bias, HTRB), while the second one is the failure of the gate dielectric under positive gate bias.

In this session, we refer to HTRB, high temperature reverse bias, as the stress condition applied to induce the degradation of the devices. NBTI means negative bias temperature instability, a negative shift in threshold voltage induced by the exposure to high bias and temperature. Typically, the robustness of GaN transistors against HTRB is evaluated by exposing the devices to a constant voltage stress experiment. The gate is kept at negative values (for normally-on devices), in our case  $V_{GS} = -20$  V, while the drain is at high voltage ( $V_{DS} > 520$  V). Our system gives us the possibility of repeatedly interrupting the stress experiment to carry out quick  $I_D$ - $V_{GS}$  and  $I_D$ - $V_{DS}$  measurements. This allows us to monitor the main device parameters, and to investigate how/if the exposure to long-term off-state bias influences the threshold voltage and the on-resistance of the devices.

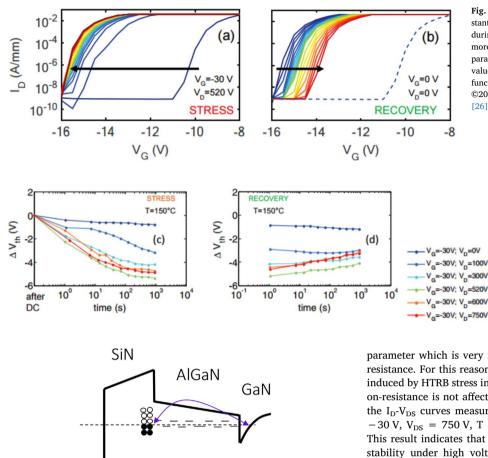

All the samples were stressed with  $V_{GS} = -30 \text{ V}$ , and different drain voltages ranging from 0 V to 750 V. Fig. 13 reports the  $I_D$ -V<sub>GS</sub> curves measured during a 1000 s stress experiment carried out at 150 °C, with a drain voltage of 520 V. Source was grounded during stress. As can be noticed, stress with  $V_{\rm DS}$  = 0 V and negative gate voltage does not result in a significant threshold voltage shift. On the contrary, when a high drain bias is applied, threshold voltage shifts towards more negative values (negative bias temperature instability, NBTI). This effect is stronger at higher drain voltages, and only slowly recoverable. At  $V_{GS}=\,-\,30$  V,  $V_{DS}=\,520$  V,  $T=\,150$  °C we measured a -5 V shift in threshold voltage (see Figs. 13 and 14). A significantly smaller variation (-1.5 V) was found at room temperature, by applying the same voltages to the devices (not shown for sake of brevity). Fig. 13(b) reports the threshold voltage variation measured during a recovery experiment, as can be noticed, the recovery of threshold voltage is very slow, even when the device is kept at zero bias and high temperature. The negative threshold shift originates from the presence of defects at the interface between the AlGaN barrier and the gate insulator and/or in the gate insulator (see the schematic drawing in

Fig. 15. Schematic representation of the process responsible for negative threshold voltage shift in GaN-based MIS-HEMTs.

Fig. 15, see also [16,24]). When a reverse bias is applied between gate and drain, the electrons trapped at these states are emitted and transferred to the channel. This results in a reduction of the net negative charge under the gate, and thus in a negative shift of the threshold voltage. During the recovery experiment, the electrons are transferred back towards the interface defects. Recovery is very slow, since the electrons have to move against the electric field. In addition, once the electrons are trapped back at the interface between SiN and AlGaN, they have a repulsive (electrostatic) action that limits the rate at which electrons are injected back from the channel to the interface. It is worth noticing that, in principle, also trapping in the buffer may affect the threshold voltage of the devices and induce NBTI/PBTI effects.

In most cases, GaN-based MIS-HEMTs are designed to be used in cascode configuration, and mounted in a double chip package along with a silicon MOSFET. The on/off-state of the cascoded ensemble is controlled by the silicon MOSFET, so a negative threshold voltage shift of the HEMT does not affect the performance of the GaN HEMT. The

20

15

10

DC

Ron (0. mm)

#### Materials Science in Semiconductor Processing xxx (xxxx) xxx-xxx

Fig. 13. I<sub>D</sub>-V<sub>GS</sub> curves measured repeatedly during a constant-voltage experiment, in off-state. The curves were taken during a stress having a total duration of 1000 s. To give a more accurate description of the variation of the main device parameters (Vth and Ron), in Figs. 14 and 16 we report the values of Vth and Ron extrapolated from these plots as a function of stress time (see the curves at  $V_{DS} = 520$  V). ©2017 IEEE. Reprinted with permission from Dalcanale et al. [26].

Fig. 14. Variation in threshold voltage during a set of constant voltage stress experiments, with different levels of  $V_{DS}$  (and the same value of  $V_{CS} = -30$  V). The frame on the left shows the stress test, the one on the right the subsequent recovery at 0 V. ©2017 IEEE. Reprinted with permission from Dalcanale et al. [26].

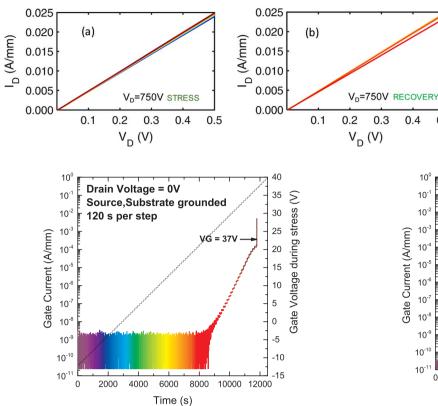

parameter which is very important for real-life applications is the onresistance. For this reason, we evaluated the variation in on-resistance induced by HTRB stress in GaN-based MIS-HEMTs. As shown in Fig. 16, on-resistance is not affected by long-term HTRB stress. Fig. 17 reports the  $I_D$ - $V_{DS}$  curves measured repeatedly during a stress test at  $V_{GS}$  =  $-30 \text{ V}, \text{ V}_{\text{DS}} = 750 \text{ V}, \text{ T} = 150 \text{ °C}.$  No significant change is detected. This result indicates that currently available technologies have a high stability under high voltage/temperature stress. This is of high importance for the development of reliable power converters.

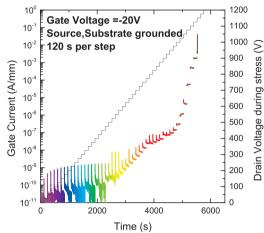

A permanent degradation of GaN-based MIS-HEMT may occur under positive gate voltage, when the gate bias is so high that the electric field in the silicon nitride insulator exceeds its breakdown field (typically higher than 6-7 MV/cm). The robustness of GaN-based MIS-HEMTs against positive gate bias can be evaluated by means of a stepstress experiment. An example is shown in Fig. 17: in this case, a GaNbased MIS-HEMT was submitted to stress at positive gate bias, with zero bias applied between drain and source. The stress voltage applied to the gate was increased by 0.5 V every 120 s, until failure was reached. The staircase line in Fig. 17 indicates the stress voltage at a given stress time, while the colored line shows the variation of device current during each step of the experiment. As can be noticed, the current flowing through the gate remains well below the measurement limit of the instrument until the stress voltage becomes higher than 22 V. This result indicates that the (thick) gate insulator can block the leakage current in a very efficient way. For higher stress voltages (22 V <  $V_{GS} < 37$  V), a significant current starts flowing through the gate. As shown by the band diagram in Fig. 17, at positive gate voltages most of the potential drops on the SiN insulator, since the 2DEG - which is at zero volt - is formed at the AlGaN/GaN interface. At high stress

Vg=-30V; Vp=0V V\_=-30V; V\_==0V STRESS RECOVERY 20 -- 30V; V\_=100V T=150°C (mm -30V; V\_=100V T=150°C =-30V; V\_=300V =-30V; V\_==300V 15 Ron (D. -30V; V\_=520V -30V; V\_=520V 10 (a) =-30V; V\_=600V (b) =-30V; V\_=600V -30V; V\_=750V 5 -30V; V\_=750V < 0 10<sup>0</sup> 10<sup>°</sup> 10<sup>2</sup> 10<sup>3</sup> 10-1  $10^{3}$ after 10 10<sup>4</sup> 10 10 10 time (s) time (s)

Fig. 16. Variation in on-resistance during a set of constant voltage stress experiments, with different levels of V<sub>DS</sub> (and the same value of  $V_{GS} = -30$  V). The frame on the left shows the stress test, the one on the right the subsequent recovery at 0 V. ©2017 IEEE. Reprinted with permission from Dalcanale et al. [26].

**Fig. 18.** Gate current measured during a gate-step stress. Gate voltage is increased every 120 s until failure is reached. The staircase line indicates the gate voltage, while the colored-line represents the gate current flowing through the structure during stress time. The stress temperature is 25 °C. (For interpretation of the references to color in this figure legend, the reader is referred to the web version of this article.)

Fig. 19. Simulated band diagram under positive gate bias ( $V_{GS} = 15$  V). The band diagram refers to a cut under the gate, and is simulated with  $V_{DS} = 0$  V. The simulation refers to a device with a SiN thickness of 50 nm.

voltages, electrons from the 2DEG can be injected towards the gate insulator, and be collected by the gate metal. This results in a measurable gate current that, for extremely high gate voltages (36 V) – may reach the level of 100  $\mu$ A/mm. The injected electrons are accelerated by

Materials Science in Semiconductor Processing xxx (xxxx) xxx-xxx

**Fig. 17.** I<sub>D</sub>-V<sub>DS</sub> curves measured during a 1000 s stress test at  $V_{GS}=-30$  V,  $V_{DS}=750$  V, T=150°C. The frame on the left shows the stress test, the one on the right the subsequent recovery at 0 V. No significant variation is observed. (For interpretation of the references to color in this figure, the reader is referred to the web version of this article.)

0.5

**Fig. 20.** Gate current measured during a drain-step stress, carried out in the off-state. Drain voltage is increased every 120 s until failure is reached. During stress time, the gate-source voltage is fixed at  $V_{\rm CS} = -20$  V. The staircase line indicates the drain voltage, while the colored-line represents the gate current flowing through the structure during stress time. Failure is reached at  $V_{\rm DS} = 1150$  V. (For interpretation of the references to color in this figure legend, the reader is referred to the web version of this article.)

the high electric field in the SiN, and this may generate a measurable electroluminescence signal due to the deceleration of these electrons at the gate metal. A catastrophic failure is reached at  $V_{GS}=37$  V, which on a 50 nm SiN layer, corresponds to an electric field of 7.4 MV/cm.

Evaluating the robustness of a MIS-HEMT at positive gate bias allows to study the breakdown limits of the gate insulator. In fact, at positive gate bias the electric field in the SiN is uniform, since the system can be assimilated to a 2-plates capacitor, where the positive plate is the gate metal, and the negative is the 2DEG. Under off-state/semi-on state conditions, the distribution of the electric field is significantly different, with the peak of the field being located at the edge of the gate on the drain side or at the drain contact [25], depending on the applied voltage. To evaluate the robustness of MIS-HEMTs in off-state conditions, we carried out a set of step-stress experiments in the off-state. The gate voltage was kept at  $V_{GS} = -20$  V, while the drain voltage was increased until failure. State-of-the-art devices rated for 650 V operation showed a catastrophic failure only for  $V_{DS} > 1150$  V (see a representative example in Fig. 17), indicating the good stability of the analyzed technology (Figs. 18–20).

#### 4. Conclusions

In summary, with this paper we have presented an extensive overview of the main trapping and degradation processes that affect the performance and reliability of GaN-based HEMTs for power applications. In the first part of the paper, we have described the physical origin of dynamic- $R_{on}$ , and its temperature dependence. In addition, we have discussed the different trapping mechanisms that may be triggered by off-state and semi-on state conditions. In the second part of the paper we have discussed both the gradual/recoverable and the permanent

#### M. Meneghini et al.

degradation mechanisms of GaN-based MIS-HEMTs. The results described within this paper indicate that through careful growth and process optimization it is possible to fabricate devices with negligible dynamic- $R_{on}$  at 600 V/150 °C, and with high robustness against HTRB stress and off-state step-stress. These devices are expected to find wide application in next generation power converters.

#### Acknowledgements

The authors kindly acknowledge Dr. Isabella Rossetto (now with ST Microelectronics) and Dr. Stefano Dalcanale (now with University of Bristol) for their contribution to the experimental activity. This research work was partly supported by H2020 Project INREL-NPower, Project ID: 720527.

#### References

- R. Gaska, M. Gaevski, J. Deng, R. Jain, Novel AlInN/GaN integrated circuits operating up to 500 °C, in: Proceedings of the 44th European Solid-State Device Research Conference (ESSDERC), 2014, pp. 142–145.

- [2] G. Meneghesso, G. Verzellesi, F. Danesin, F. Rampazzo, F. Zanon, A. Tazzoli, M. Meneghini, E. Zanoni, Reliability of GaN high-electron-mobility transistors: state of the art and perspectives, IEEE Trans. Device Mater. Reliab. 8 (2) (2008) 332.

- [3] J. Würfl, O. Hilt, R. Zhytnytska, P. Kotara, F. Brunner, O. Krueger, M. Weyers, Techniques towards GaN power transistors with improved high voltage dynamic switching properties, Int. Electron Devices Meet. (2013) 144–147.

- [4] T. Morita, S. Tamura, Y. Anda, M. Ishida, Y. Uemoto, T. Ueda, T. Tanaka, D. Ueda, 99.3% Efficiency of three-phase inverter for motor drive using GaN-based gate injection transistors, in: Proceedings of the Twenty-Sixth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), 2011, pp. 481–484.

- [5] M. Meneghini, I. Rossetto, G.A.M. Hurkx, J. Sonsky, J.A. Croon, G. Meneghesso, E. Zanoni, Extensive investigation of time – dependent breakdown of GaN – HEMTs submitted to off – state stress, IEEE Trans. Electron Devices 62 (8) (2015) 2549.

- [6] X. Huang, Z. Liu, Q. Li, F.C. Lee, Evaluation and application of 600 V GaN HEMT in cascode structure, IEEE Trans. Power Electron. 29 (5) (2014) 2453–2461.

- [7] K.J. Chen, L. Yuan, M.J. Wang, H. Chen, S. Huang, Q. Zhou, C. Zhou, B.K. Li, J.N. Wang, Physics of fluorine plasma ion implantation for GaN normally-off HEMT technology, Tech. Dig. – Int. Electron Devices Meet. IEDM 1 (2011) 465–468.

- [8] D. Bisi, M. Meneghini, A. Stocco, G. Cibin, A. Pantellini, A. Nanni, C. Lanzieri, E. Zanoni, G. Meneghesso, Influence of fluorine-based dry etching on electrical parameters of AlGaN/GaN-on-Si high electron mobility transistors, in: Proceedings of the European Solid-State Device Research Conference (ESSDERC), 2013, pp. 61–64.

- [9] K.J. Chen, Fluorine-implanted enhancement-mode transistors, power GaN devices, in: Meneghesso, Meneghini, Zanoni (Eds.), Part Ser. Power Electron. Power Syst. Springer Int. Publ., 2016, pp. 273–293.

- [10] T. Mizutani, H. Yamada, S. Kishimoto, F. Nakamura, T. Mizutani, H. Yamada, S. Kishimoto, F. Nakamura, Normally off AlGaN/GaN high electron mobility transistors with p-InGaN cap layer, J. Appl. Phys. 113 (2013) 34502.

- [11] M. Blaho, D. Gregu, M. Jurkovi, M. Tapajna, K. Fr, F. Carlin, N. Grandjean, N. Kuzm,

#### Materials Science in Semiconductor Processing xxx (xxxx) xxx-xxx

I. There, et al., Self-Aligned Normally-Off Metal – Oxide – Semiconductor n++ GaN/InAlN/GaN High Electron Mobility Transistors, 2015, pp. 1086–1090.

- [12] Y. Uemoto, M. Hikita, H. Ueno, H. Matsuo, H. Ishida, M. Yanagihara, T. Ueda, T. Tanaka, D. Ueda, Gate injection transistor (GIT) – a normally-off AlGaN/GaN power transistor using conductivity modulation, IEEE Trans. Electron Devices 54 (12) (2007) 3393–3399.

- [13] Z. Li, R. Chu, D. Zehnder, S. Khalil, M. Chen, X. Chen, K. Boutros, Improvement of the Dynamic On-Resistance Characteristics of GaN-on-Si Power Transistors with a Sloped Field-Plate, 2014, pp. 257–258.

- [14] D. Jin, J.a. Del Alamo, Methodology for the study of dynamic ON-resistance in highvoltage GaN field-effect transistors, IEEE Trans. Electron Devices 60 (10) (2013) 3190–3196.

- [15] P. Moens, P. Vanmeerbeek, A. Banerjee, J. Guo, C. Liu, P. Coppens, A. Salih, M. Tack, M. Caesar, On the impact of carbon-doping on the dynamic Ron and off-state leakage current of 650 V GaN power devices, in: Proceedings of the 27th International Symposium on Power Semiconductor Devices and ICs, 2015, pp. 37–40.

- [16] M. Meneghini, I. Rossetto, D. Bisi, M. Ruzzarin, M. Van Hove, S. Stoffels, T. Wu, D. Marcon, S. Decoutere, et al., Negative bias-induced threshold voltage instability in GaN-on-Si power HEMTs, IEEE Electron Device Lett. 37 (4) (2016) 474–477.

- [17] G. Meneghesso, M. Meneghini, D. Bisi, I. Rossetto, T. Wu, M. Van Hove, D. Marcon, S. Stoffels, S. Decoutere, et al., Trapping and reliability issues in GaN-based MIS HEMTs with partially recessed gate, Microelectron. Reliab. 58 (2016) 151–157.

- [18] M.J. Uren, S. Karboyan, I. Chatterjee, A. Pooth, P. Moens, A. Banerjee, M. Kuball, S. Member, Leaky dielectric' model for the suppression of dynamic R ON in carbondoped, IEEE Trans. Electron Devices 64 (7) (2017) 2826–2834.

- [19] P. Moens, A. Banerjee, M.J. Uren, M. Meneghini, S. Karboyan, I. Chatterjee, P. Vanmeerbeek, M. Cäsar, C. Liu, et al., Impact of buffer leakage on intrinsic reliability of 650 V AlGaN/GaN HEMTs, IEEE Electron Device Meet. IEDM 2015 Tech. Dig. (2015) 903–906.

- [20] M. Meneghini, P. Vanmeerbeek, R. Silvestri, S. Dalcanale, A. Banerjee, D. Bisi, E. Zanoni, G. Meneghesso, P. Moens, Temperature-dependent dynamic R ON in GaN-based MIS-HEMTs: role of surface traps and buffer leakage, IEEE Trans. Electron Devices 62 (3) (2015) 782–787.

- [21] J.L. Lyons, A. Janotti, C.G. Van de Walle, Effects of carbon on the electrical and optical properties of InN, GaN, and AlN, Phys. Rev. B 89 (3) (2014) 35204.

- [22] U. Honda, Y. Yamada, Y. Tokuda, K. Shiojima, Deep levels in n-GaN doped with carbon studied by deep level and minority carrier transient spectroscopies, Jpn. J. Appl. Phys. 51 (4 Part 2) (2012) 3–6.

- [23] P. Moens, A. Banerjee, M.J. Uren, M. Meneghini, S. Karboyan, I. Chatterjee, P. Vanmeerbeek, M. Cäsar, C. Liu, et al., Impact of buffer leakage on intrinsic reliability of 650 V AlGaN/GaN HEMTs, IEEE Electron Devices Meet. (2015) 903–906.

- [24] A. Guo, J.A. Alamo, Negative-bias temperature instability of GaN MOSFETs, in: Proceedings of the IEEE International Reliability Physics Symposium, 2016, pp. 4A–1–1.

- [25] M. Meneghini, C. De Santi, T. Ueda, T. Tanaka, D. Ueda, E. Zanoni, G. Meneghesso, Time-and field-dependent trapping in GaN-based enhancement-mode transistors with p-gate, IEEE Electron Device Lett. 33 (3) (2012) 375–377.

- [26] S. Dalcanale, M. Meneghini, A. Tajalli, I. Rossetto, M. Ruzzarin, E. Zanoni, G. Meneghesso, GaN-based MIS-HEMTs: impact of cascode-mode high temperature source current stress on NBTI shift, in: Proceedings of the IEEE International Reliability Physics Symposium, Monterey, 2017, pp. 4B–1.1–4B–1.5. <a href="https://dx.doi.org/10.1109/IRPS.2017.7936307">https://dx.doi.org/10.1109/IRPS.2017.7936307</a>>.