Home Search Collections Journals About Contact us My IOPscience

Fabrication of Ni/Ti/AI Schottky contact to n-type 4H-SiC under various annealing conditions

This content has been downloaded from IOPscience. Please scroll down to see the full text. 2013 J. Phys.: Conf. Ser. 439 012027 (http://iopscience.iop.org/1742-6596/439/1/012027) View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 113.172.48.28 This content was downloaded on 27/06/2016 at 06:43

Please note that terms and conditions apply.

# Fabrication of Ni/Ti/Al Schottky contact to n-type 4H-SiC under various annealing conditions

M Yousuf Zaman<sup>\*,1,3</sup>, S Ferrero<sup>1,3</sup>, D Perrone<sup>2,3</sup>, L Scaltrito<sup>1,3</sup>, N Shahzad<sup>1,2,3</sup> and D Pugliese<sup>1,2,3</sup>

<sup>1</sup>Department of Applied Science and Technology, Politecnico di Torino, 10129 TO, Italy <sup>2</sup>Italian Institute of Technology, Center for Human Robotics, C.so Trento 21 Torino, Italy <sup>3</sup>X-Lab Materials and Microsystems Laboratory, via Lungo Piazza d'Armi 6, Chivasso, Italy

E-mail: <u>\*muhammad.zaman@polito.it</u>

**Abstract:** Forward I-V characteristics of a silicon carbide Schottky diode, with triple layer metallization Ni/Ti/Al as Schottky contact, are presented. Effects of different annealing conditions on the Schottky barrier height and ideality factor are discussed. The diodes were annealed in inert Ar atmosphere for 30 minutes at temperatures ranging from 600 °C to 800 °C. The ideality factors of the four diodes, chosen out of 20 diodes, range from 1.02 to 1.13 and the Schottky barrier heights range from 1.47 eV to 3.17 eV.

### 1. Introduction

Silicon carbide (SiC) is favored as a semiconductor for the fabrication of power devices because of its wide energy band gap, high hardness, chemical inertness, high electric field breakdown strength and high thermal conductivity [1-5]. SiC based devices need Schottky as well as low resistance ohmic contacts to operate at high power and high frequencies [6-9]. Among a number of materials that can form low resistance ohmic contacts to SiC one is Ni/Ti/Al. This triple layer metallization after annealing can form low resistance ohmic contacts on both p- and n-type SiC; a very important property with potential application in the fabrication of metal-oxide field effect transistors (MOSFETs) [1]. MOSFET fabrication also requires low annealing temperatures so as to reduce the chances of any chemical reactions between the gate metal and the oxide layer. Ni/Ti/Al forms low resistance ohmic contacts with annealing temperature as low as 800 °C and is considered a suitable candidate for MOSFET fabrication [1].

The focus of this paper, however, will be on the study of Schottky behavior of Ni/Ti/Al/SiC contact which can be achieved by altering the relative thicknesses of the three constituent metals used for the contact deposition i.e. nickel, titanium and aluminum—with the aim to fabricate both Schottky and ohmic contacts simultaneously to make possible the fabrication of devices that require both Schottky and ohmic contacts at low annealing temperature (such as MESFETs). In the following sections we will elaborate the experimental setup and discuss some of the electrical parameters in view of thermionic emission theory of four Ni/Ti/Al Schottky diodes annealed at different temperatures.

<sup>&</sup>lt;sup>\*</sup> To whom any correspondence should be addressed.

#### 2. Device fabrication

The Schottky barrier diodes characterized in this work were fabricated using 3 inch diameter 4H-SiC wafers. The substrates were purchased from Cree Research Inc. (Durham, NC) and they were constituted by n-type bulk substrate (with a doping concentration  $N_d$  of  $10^{18}$  cm<sup>-3</sup> and a thickness of 360  $\mu$ m) and an epitaxial layer (also n-doped). The thickness of the epitaxial layer was 5.5  $\mu$ m, and the doping concentration  $N_d$  was  $10^{15}$  cm<sup>-3</sup>.

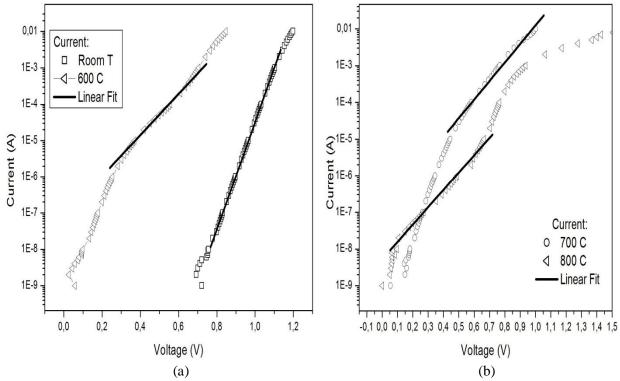

Figure 1. I-V characteristics of Ni/Ti/Al/4H-SiC Schottky diodes annealed at various temperatures.

Schottky barrier diodes were designed with a  $p^+$ -type guard ring and a mesa-type structure with an additional silicon dioxide (SiO<sub>2</sub>) passivation layer. Boron ion implantation was used for the formation of the  $p^+$ -type guard ring. This step was followed by a Rapid Thermal Process (RTP) at temperatures exceeding 1500 °C, in order to promote lattice damage recovery and to achieve a reasonable electrical activation of the implanted B<sup>+</sup> ions.

The silicon dioxide passivation layer was grown by means of a Low Temperature Oxidation (LTO) process, using TetraEthylOxySilane (TEOS) as precursor. The SiO<sub>2</sub> layer was patterned using standard UV photolithography, and etched by a buffered HF-based solution. The Schottky contact was then realized by lift-off patterning of Ni/Ti/Al triple layer (with respective thicknesses of 20, 50 and 150 nm) on the 4H-SiC epilayer surface. The Ni/Ti/Al deposition was followed by an annealing treatment performed at 600, 700 and 800 °C in inert atmosphere. The ohmic contact was obtained on the wafer's backside by means of a triple layer of Ti, Ni and Ag, without the need of a post-deposition annealing. The deposition

of both the Schottky and the ohmic contacts was performed using an electron beam evaporator (ULVAC model EBX-14D), at a pressure of about  $10^{-5}$  Pa. The electrical characterization of the SBDs was performed by acquiring the current-voltage (I-V) curves using Keithley 237 and 238 SMUs. The capacitance-voltage (C-V) characteristics were acquired by means of a HP4192A impedance analyzer.

#### 3. Discussion

Forward bias current-voltage (I-V) plots of four diodes characterized at room temperature and annealed at 600, 700 and 800 °C were applied linear fit. The forward I-V characteristics are shown in figure 1. With the help of thermionic emission theory electrical parameters such as Schottky barrier height SBH (denoted by  $\Phi_B$ ) and ideality factor n, were extracted. The thermionic emission theory relates the diode current to the applied voltage  $V_a$  as follows [10]:

$$I = I_{s} \left[ \exp \left( q V_{a} / n K_{B} T \right) - 1 \right]$$

(3.1)

$$I_{s} = AA^{*} T^{2} \exp(-\Phi_{B} / K_{B}T)$$

(3.2)

In (3.1) I<sub>s</sub> represents saturation current  $K_{B}$  Boltzmann's constant and T applied temperature. Similarly in (3.2) A represents area of the diode (1.1 mm<sup>2</sup> in our case), A\* represents Richardson's constant (A\*=146 A/cm<sup>2</sup>.K<sup>2</sup>) and  $\Phi_{B}$  represents Schottky barrier height. Figure 1 shows I-V characteristics of Ni/Ti/Al/4H-SiC Schottky diodes annealed at 600, 700 and 800 °C and one without annealing. Schottky barrier height (extracted from the intercept) is 1.47 eV for the diode without annealing and 2.37, 2.62 and 3.17 eV for the diodes annealed at 600,700 and 800 °C. For the diode without annealing ideality factor (extracted from the slope) is 1.13 and for those annealed at 600, 700 and 800 °C ideality factors are 1.02, 1.03 and 1.08 respectively. These four diodes were chosen out of a group of diodes which also contained a number of diodes with small linear region and poor rectifying behavior with average Schottky barrier height of 1.03 eV and an average ideality factor of 1.46 (extracted from forward I-V plots). Similarly an average Schottky barrier height of 1.31 eV extracted from capacitance voltage (C-V) characteristics.

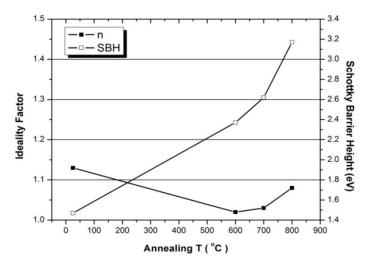

Figure 2 shows both  $\Phi_B$  and n in relation to the annealing temperature, general trend shows an increase in

the SBH with annealing temperature. For diode that was not annealed the SBH values are close to the commonly accepted values for Ni/SiC Schottky barrier but diodes which were annealed at 600 °C temperature or more show bad rectifying behavior and high Schottky barrier heights as reported also by Kestle et al. in the case of Ni/SiC Schottky diodes [11]. The ideality factor shows a decline with increasing annealing temperatures which indicates an improvement in the quality of the diodes at high annealing temperatures. The diode which was not annealed shows best Schottky behavior out of all the diodes characterized. The diode annealed at 800 °C shows very poor Schottky behavior with ideality factor of 1.08 and SBH of 3.17. The

**Figure 2.** Schottky barrier height and ideality factor versus annealing temperature.

increasing trend in SBH accounts for the varying quality of Schottky contact which is deteriorating at high annealing temperature this behavior is contrary to the normal where diodes tend to perform better after annealing at high temperatures [12]. This could be due to a number of different reasons such as structural defects, laboratory conditions or chemical reactions taking place at high annealing temperatures such as Ni<sub>2</sub>Si which itself forms a Schottky contact on n-type SiC [13].

## 4. Conclusion

Schottky behavior of four ternary Ni/Ti/Al contacts to 4H-SiC was compared for different annealing temperatures. The diode which was not annealed showed better behavior as compared to the ones annealed at 600,700 and 800 °C, with ideality factor as low as 1.13 and Schottky barrier height of 1.47 eV. All the diodes which were annealed at more than 600 °C exhibit excess forward current at low applied voltage which indicates inhomogeneous Schottky barriers. There is dire need to focus on the inhomogeneity of Schottky barrier in order to take full advantage of this ternary Schottky contact material.

## References

- [1] Tsukimoto S, Sakai T, Onishi T, Ito K and Murakami M 2005 J. Electon. Mater. 34 10

- [2] Nikitina I P, Vassilevski K V, Wright N G, Horsfall A B and O'Neill A G 2005 J. Appl. Phys. 97 083709

- [3] Haberstroh C, Helbig R and Stein R A 1996 J. Appl. Phys. 76 509

- [4] Muench W V and Pfaffeneder I 1977 J. Appl. Phys. 48 4831

- [5] Slack G A J. 1964 Appl. Phys. **35** 3460

- [6] Konishi R, Yasukochi R, Nakatsuka O, Koide Y, Moriyama M and Murakami M 2003 *Mater. Sci.* Eng. B **98** 286

- [7] Trew R J, Yan J B and Mock P M 1991 *Proc. IEEE* **79** 598

- [8] Davis R F, Kelner G, Shur M, Palmour J W and Edmond J A 1991 Proc. IEEE 79 677

- [9] Vasilevskii K V 1992 Sov. Phys. Semicond. 26 994

- [10] Tung R T 2001 Mater. Sci. Eng. R 35 1

- [11] Kestle A, Wilks S P, Dunstan P R, Prichard M and Mawby P A 2000 Electron. Lett. 36 3

- [12] Zhang Q and Sudarshan T S 2001 J. Electron. Mater. 30 11

- [13] Roccaforte F, La Via F and Raineri V 2003 J. Appl. Phys. 93 11